ISD4003中文资料

ZSPM4013AA1W33中文资料(ZMDI)中文数据手册「EasyDatasheet - 矽搜」

该ZSPM4013采用电流模式反馈 正常调节PWM模式.当稳压 被禁用(EN为低电平)时,设备将小于 10uA静态电流.

该ZSPM4013集成多种防护护电路,包括: 输入欠压锁定,输出电压软启动,限流和热关断.

该ZSPM4013包括通过PG(电源良好)开漏输出 监管报告接口等组成系统.

特征

· 固定输出电压:1.5V,1.8V,2.5V,3.3V, 并用5V +/- 2%输出容差

· ZSPM1000:5A单相,单轨,真 数字PWM控制器(24引脚4×4 QFN)

提供支持

· 评估套件 · 数据表

物理特性

· 结工作温度-40°C至125°C · 包装在一个16针QFN(3×3)

ZSPM4013应用电路

可调输出

ZSPM4013

固定输出 VCC

VOUT

ZSPM4013

EN

PG

芯片中文手册,看全文,戳

2 典型性能特性................................................................................................................... 9 3 电路说明......................................................................................................................................... 12

5 引脚配置和包装......................................................................................................................... 15 5.1.标记图& Pin-out......................................................................................................................... 16 5.2.引脚说明为16引脚3x3 QFN封装....................................................................................................... 17 5.3.详细引脚说明............................................................................................................................. 17 5.3.1.未经稳压输入,VCC(引脚#2,3)....................................... .................................................. ........... 17 5.3.2.引导控制,BST(引脚#10) ......................................................................................................... 17 5.3.3.检测反馈,FB(引脚#5) ............................................................................................................... 17 5.3.4.开关量输出,VSW(引脚#12,13)....................................... .................................................. ......... 18 5.3.5.接地,GND(引脚#4) .......................................................................................................................... 18 5.3.6.电源接地,防护护接地(引脚#14,15)....................................... .................................................. .......... 18 5.3.7.启用,高电压,EN(管脚#9) ........................................................................................................ 18 5.3.8. PG输出,PG(引脚#8) ....................................................................................................................... 18

实力专业用品-实力专业用品-实力专业用品说明书

7

DIN Adaptors

DIN Adaptor for RGS SSRs

Installation Instructions

Ordering Key

RGS1DIN

DIN rail adaptor module for mounting the RGS series on DIN rail.

Suffix H8 added to SSR part no. refers to factory mounted DIN clip. Conditions apply. Please ask your Sales representative for further details.

Ordering Key

Ordering Key

RGN - TERMRES

RGN-TERMRES termination resistor to be fitted on the last RG..N on the NRG bus chain. Packing qty. 4 pc.

Specifications are subject to change without notice (30.07.2019)

3-pin socket to mate with RM1E..V.. 4-pin socket to mate with RA2A..C 4-pin socket to mate with RA2A..C

5-pin socket to mate with RA..S 4-pin socket to mate with RKD2..C 2-pin socket to mate with RK2..C

Material Thermal resistance

ISD4004系列录放芯片在电话查询系统中的应用

图 5 是一个用 A T89C8252 构成的 48min 语音 查询系统的实例 ,该产品已在一家公司搬迁时 ,用于 公司新电话号码的查询中 。

该 系 统 采 用 三 片 ISD4004 , 控 制 器 采 用 A T89C8252 。ISD4004 的片选信号SS由控制器的脚

36 (228)

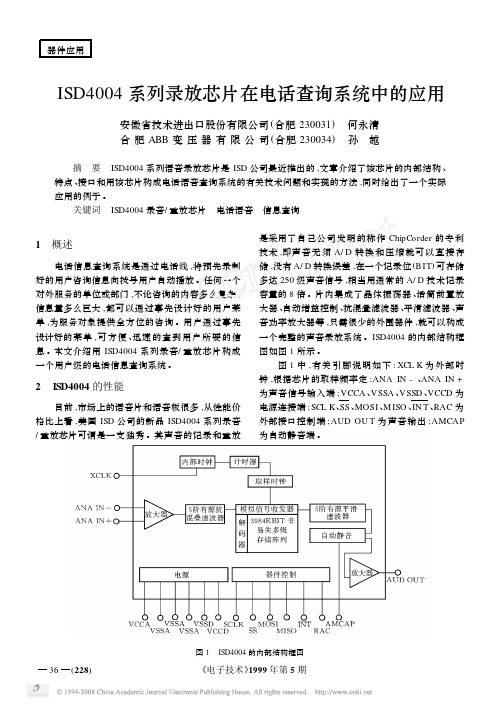

图 1 ISD4004 的内部结构框图

《电子技术》1999 年第 5 期

ISD4004 与普通的录音/ 重放芯片相比 ,有如下 特点 :

(1) 记录的声音没有段长度的限制 ; (2) 声音的记录无需 A/ D 转换和压缩 ,放音自 然 、完美 ; (3) 快速闪存作为存储介质 ,无须电源可保存 数据长达 100 年 ,重复记录 10 000 次以上 ; (4) 内置的闪速存储器 ,记录时间长达 16min ; (5) 接口简单 , SPI 接口提供全部数据和控制 操作 ; (6) 3V 电压供电 , 待机耗 电 1μA , 放 音 耗 电 30mA ,录音耗电 25mA 。

ISD4004 可以设置放音或录音的起始地址 ,但 是无法设置放音或录音的结束地址 ,给存储器的利

图 3 SPI 的控制位示意图

《电子技术》1999 年第 5 期

(229) 37

用带来了极大的不便 。但器件提供了地址计数器指 针 ,通过读 SPI 总线的 M ISO 的寄存器的 P0~ P10 位和 EOM 位 ,就知道该信息的结束地址 ,通过查询 信息的起始地址 ,就可以唯一确定一条信息的位置 。

停止当前操 作

S TO P PO WDN

ቤተ መጻሕፍቲ ባይዱ

0 X01 X〈XXXXXXXXXXX〉

停止当前操 作并进入待 机状态

ISD4004系列语音芯片中文资料

ISD4004系列单片语音录放电路一、简述●单片8至16分钟语音录放●内置微控制器串行通信接口●3V单电源工作●多段信息处理●工作电流25-30mA,维持电流1μA●不耗电信息保存100年(典型值)●高质量、自然的语音还原技术●10万次录音周期(典型值)●自动静噪功能●片内免调整时钟,可选用外部时钟ISD4004系列工作电压3V,单片录放时间8至16分钟,音质好,适用于移动电话及其他便携式电子产品中。

芯片采用CMOS技术,内含振荡器、防混淆滤波器、平滑滤波器、音频放大器、自动静噪及高密度多电平闪烁存贮陈列。

芯片设计是基于所有操作必须由微控制器控制,操作命令可通过串行通信接口(SPI或Microwire)送入。

芯片采用多电平直接模拟量存储技术, 每个采样值直接存贮在片内闪烁存贮器中,因此能够非常真实、自然地再现语音、音乐、音调和效果声,避免了一般固体录音电路因量化和压缩造成的量化噪声和"金属声"。

采样频率可为4.0,5.3,6.4,8.0kHz,频率越低,录放时间越长,而音质则有所下降,片内信息存于闪烁存贮器中,可在断电情况下保存100年(典型值),反复录音10万次。

二、引脚描述电源:(VCCA,VCCD)为使噪声最小,芯片的模拟和数字电路使用不同的电源总线,并且分别引到外封装的不同管脚上,模拟和数字电源端最好分别走线,尽可能在靠近供电端处相连,而去耦电容应尽量靠近器件。

地线:(VSSA,VSSD)芯片内部的模拟和数字电路也使用不同的地线。

同相模拟输入(ANA IN+)这是录音信号的同相输入端。

输入放大器可用单端或差分驱动。

单端输入时,信号由耦合电容输入,最大幅度为峰峰值32mV,耦合电容和本端的3KΩ电阻输入阻抗决定了芯片频带的低端截止频率。

差分驱动时,信号最大幅度为峰峰值16mV,为ISD33000系列相同。

反相模拟输入(ANA IN-)差分驱动时,这是录音信号的反相输入端。

ISD4003-08MSD中文资料

ISD/Winbond · 2727 North First Street, San Jose, CA 95134 · TEL: 408/943-6666 · FAX: 408/544-1787 · June 2000GENERAL DESCRIPTIONThe ISD4003 ChipCorder ® Products provide high-quality, 3-volt, single-chip Record/Playback solu-tions for 4- to 8-minute messaging applications which are ideal for cellular phones and other por-table products. The CMOS-based devices include an on-chip oscillator, antialiasing filter, smoothing filter, AutoMute™ feature, audio amplifier, and high density, multilevel Flash storage array. The ISD4003 series is designed to be used in a micro-processor- or microcontroller-based system. Ad-dress and control are accomplished through a Serial Peripheral Interface (SPI) or Microwire Serial Interface to minimize pin count.Recordings are stored in on-chip nonvolatile memory cells, providing zero-power message storage. This unique, single-chip solution is made possible through ISD’s patented multilevel storage technology. Voice and audio signals are stored directly into memory in their natural form, providing high-quality, solid-state voice reproduction.ISD4003 SeriesSingle-Chip Voice Record/Playback Devices4-, 5-, 6-, and 8-Minute DurationsISD4003 SeriesiiVoice Solutions in Silicon ™Table: ISD4003 Series SummaryPart NumberDuration (minutes)Input Sample Rate (KHz)Typical Filter Pass Band(KHz)ISD4003-04M 4.08.0 3.4ISD4003-05M 5.0 6.4 2.7ISD4003-06M 6.0 5.3 2.3ISD4003-08M8.04.01.7FEATURES•Single-chip voice Record/Playback solution •Single +3 volt supply •Low-power consumption–Operating current:I CC Play = 15 mA (typical)I CC Rec = 25 mA (typical)–Standby current: 1 µA (typical)•Single-chip durations of 4, 5, 6, and 8 minutes •High-quality, natural voice/audio reproduction •AutoMute feature provides background noiseattenuation during periods of silence •No algorithm development required •Microcontroller SPI or Microwire™ SerialInterface•Fully addressable to handle multiplemessages •Nonvolatile message storage •Power consumption controlled by SPIor Microwire control register •100-year message retention (typical) •100K record cycles (typical)•On-chip clock source•Available in die form, PDIP, SOIC, TSOP, andchip scale packaging (CSP)•Extended temperature (–20°C to + 70°C) andindustrial temperature (–40°C to +85°C) versions available7DEOH RI &RQWHQWVISDi,6' 6HULHV6LQJOH &KLS 9RLFH 5HFRUG 3OD\EDFN 'HYLFHV DQG 0LQXWH 'XUDWLRQV'(7$,/(' '(6&5,37,216SHHFK 6RXQG 4XDOLW\ 'XUDWLRQ )ODVK 6WRUDJH 0LFURFRQWUROOHU ,QWHUIDFH 3URJUDPPLQJ 3,1 '(6&5,37,2169ROWDJH ,QSXWV 9886 9889 *URXQG ,QSXWV 9TT6 9TT9 1RQ ,QYHUWLQJ $QDORJ ,QSXW $1$ ,1 ,QYHUWLQJ $QDORJ ,QSXW $1$ ,1r $XGLR 2XWSXW $8' 287 6ODYH 6HOHFW 66 0DVWHU 2XW 6ODYH ,Q 026, 0DVWHU ,Q 6ODYH 2XW 0,62 6HULDO &ORFN 6&/. ,QWHUUXSW ,17 5RZ $GGUHVV &ORFN 5$& ([WHUQDO &ORFN ,QSXW ;&/. $XWR0XWHu )HDWXUH $0 &$3 6(5,$/ 3(5,3+(5$/ ,17(5)$&( 63, '(6&5,37,210HVVDJH &XHLQJ 3RZHU 8S 6HTXHQFH 63, 3RUW 63, &RQWURO 5HJLVWHU 7,0,1* ',$*5$06 '(9,&( 3+<6,&$/ ',0(16,216 25'(5,1* ,1)250$7,21,6' 6HULHViiVoice Solutions in Silicon™),*85(6 &+$576 $1' 7$%/(6 ,1 7+( ,6' 6(5,(6 '$7$ 6+((7)LJXUH ,6' 6HULHV 7623 DQG 3',3 62,& 3LQRXWV )LJXUH ,6' &63 3LQRXW )LJXUH ,6' 6HULHV $1$ ,1 0RGHV )LJXUH 63, 3RUW )LJXUH 63, ,QWHUIDFH 6LPSOLILHG %ORFN 'LDJUDP )LJXUH 7LPLQJ 'LDJUDP )LJXUH %LW &RPPDQG )RUPDW )LJXUH %LW &RPPDQG )RUPDW )LJXUH 3OD\EDFN 5HFRUG DQG 6WRS &\FOH )LJXUH $SSOLFDWLRQ ([DPSOH 8VLQJ 63, )LJXUH $SSOLFDWLRQ ([DPSOH 8VLQJ 0LFURZLUH )LJXUH $SSOLFDWLRQ ([DPSOH 8VLQJ 63, 3RUW RQ 0LFURFRQWUROOHU )LJXUH $SSOLFDWLRQ ([DPSOH 8VLQJ 63, ZLWK D &KLS 6FDOH 3DFNDJHG 'HYLFH )LJXUH /HDG [ PP 3ODVWLF 7KLQ 6PDOO 2XWOLQH 3DFNDJH 7623 7\SH , ( )LJXUH /HDG ,QFK 3ODVWLF 'XDO ,QOLQH 3DFNDJH 3',3 3 )LJXUH /HDG ,QFK 3ODVWLF 6PDOO 2XWOLQH ,QWHJUDWHG &LUFXLW 62,& 6 )LJXUH ,6' 6HULHV %RQGLQJ 3K\VLFDO /D\RXW à 8QSDFNDJHG 'LH )LJXUH ,6' &KLS 6FDOH 3DFNDJH &63 = 7DEOH ([WHUQDO &ORFN ,QSXW &ORFNLQJ 7DEOH 7DEOH 2SFRGH 6XPPDU\ 7DEOH 63, &RQWURO 5HJLVWHU 7DEOH $EVROXWH 0D[LPXP 5DWLQJV 3DFNDJHG 3DUWV 7DEOH 2SHUDWLQJ &RQGLWLRQV 3DFNDJHG 3DUWV 7DEOH '& 3DUDPHWHUV 3DFNDJHG 3DUWV 7DEOH $& 3DUDPHWHUV 3DFNDJHG 3DUWV 7DEOH $EVROXWH 0D[LPXP 5DWLQJV 'LH 7DEOH 2SHUDWLQJ &RQGLWLRQV 'LH 7DEOH '& 3DUDPHWHUV 'LH 7DEOH $& 3DUDPHWHUV 'LH 7DEOH 63, $& 3DUDPHWHUV 7DEOH 3ODVWLF 7KLQ 6PDOO 2XWOLQH 3DFNDJH 7623 7\SH , ( 'LPHQVLRQV 7DEOH 3ODVWLF 'XDO ,QOLQH 3DFNDJH 3',3 3 'LPHQVLRQV 7DEOH 3ODVWLF 6PDOO 2XWOLQH ,QWHJUDWHG &LUFXLW 62,& 6 'LPHQVLRQV 7DEOH ,6' 6HULHV 'HYLFH 3LQ 3DG 'HVLJQDWLRQV 7DEOH&63 'LPHQVLRQV,6' 6HULHV1ISD'(7$,/(' '(6&5,37,2163((&+ 6281' 48$/,7<7KH ,6' &KLS&RUGHU VHULHV LQFOXGHV GHYLFHV RIIHUHG DW DQG .+] VDPSOLQJ IUH TXHQFLHV DOORZLQJ WKH XVHU D FKRLFH RI VSHHFK TXDOLW\ RSWLRQV ,QFUHDVLQJ WKH GXUDWLRQ ZLWKLQ D SURGXFW VHULHV GHFUHDVHV WKH VDPSOLQJ IUHTXHQF\DQG EDQGZLGWK ZKLFK DIIHFWV VRXQG TXDOLW\ 3OHDVH UHIHU WR WKH ,6' 6HULHV 3URGXFW 6XPPDU\WDEOH RQ WKH IURQW SDJH WR FRPSDUH ILOWHU SDVV EDQG DQG SURGXFW GXUDWLRQV7KH VSHHFK VDPSOHV DUH VWRUHG GLUHFWO\ LQWR RQ FKLS QRQYRODWLOH PHPRU\ ZLWKRXW WKH GLJLWL]DWLRQ DQG FRPSUHVVLRQ DVVRFLDWHG ZLWK RWKHU VROXWLRQV 'L UHFW DQDORJ VWRUDJH SURYLGHV D QDWXUDO VRXQGLQJ UHSURGXFWLRQ RI YRLFH PXVLF WRQHV DQG VRXQG HIIHFWV QRW DYDLODEOH ZLWK PRVW VROLG VWDWH VROX WLRQV'85$7,217R PHHW HQG V\VWHP UHTXLUHPHQWV WKH ,6' VH ULHV SURGXFWV DUH VLQJOH FKLS VROXWLRQV DW DQG PLQXWHV)/$6+ 6725$*(2QH RI WKH EHQHILWV RI ,6'nV &KLS&RUGHU WHFKQRORJ\LV WKH XVH RI RQ FKLS QRQYRODWLOH PHPRU\ ZKLFK SUR YLGHV ]HUR SRZHU PHVVDJH VWRUDJH 7KH PHVVDJH LV UHWDLQHG IRU XS WR \HDUV W\SLFDOO\ ZLWKRXW SRZHU ,Q DGGLWLRQ WKH GHYLFH FDQ EH UH UHFRUG HG W\SLFDOO\ RYHU WLPHV0,&52&21752//(5 ,17(5)$&($ IRXU ZLUH 6&/. 026, 0,62 66 63, LQWHUIDFH LV SURYLGHG IRU ,6' FRQWURO DQG DGGUHVVLQJ IXQFWLRQV 7KH ,6' LV FRQILJXUHG WR RSHUDWH DV D SHULSKHUDO VODYH GHYLFH ZLWK D PLFURFRQWUROOHU EDVHG 63, EXV LQWHUIDFH 5HDG :ULWH DFFHVV WR DOO WKH LQWHUQDO UHJLVWHUV RFFXUV WKURXJK WKLV 63, LQWHU IDFH $Q LQWHUUXSW VLJQDO ,17 DQG LQWHUQDO UHDG RQO\ 6WDWXV 5HJLVWHU DUH SURYLGHG IRU KDQGVKDNH SXUSRVHVFigure 1: ISD4003 Series TSOP and PDIP/SOIC Pinouts,6' 6HULHV2Voice Solutions in Silicon ™Figure 2: ISD4003 CSP PinoutNameBall Location TSOP Pin #W 66$6! '6H86Q 6"!!6I6ÃDI 6#!$W 66$7 &6V9PVU 7!! 6I6ÃDIr 7"!#W &&$7#!%W 66' 8 !W 66' 8!I 6W &&'8"I 6W 66$8# HPTD 9 T8GF 9!'Y8GF 9"%S689#!HDTP @ TT @!(W &&' @"&DIU@#$Name Ball Location TSOP Pin #6#6"6!7#7"7!7 8#8"8!8 9#9"9!9 @#@"@!@7 ÃWvr352*5$00,1*7KH ,6' VHULHV LV DOVR LGHDO IRU SOD\EDFN RQO\DSSOLFDWLRQV ZKHUH VLQJOH RU PXOWLSOH PHVVDJH 3OD\EDFN LV FRQWUROOHG WKURXJK WKH 63, SRUW 2QFH WKH GHVLUHG PHVVDJH FRQILJXUDWLRQ LV FUHDWHG GX SOLFDWHV FDQ HDVLO\ EH JHQHUDWHG YLD DQ ,6' SUR JUDPPHU3,1 '(6&5,37,21692/7$*( ,13876 9&&$ 9&&'7R PLQLPL]H QRLVH WKH DQDORJ DQG GLJLWDO FLUFXLWV LQ WKH ,6' GHYLFHV XVH VHSDUDWH SRZHU EXVVHV 7KHVH 9 EXVVHV DUH EURXJKW RXW WR VHSDUDWH SLQV DQG VKRXOG EH WLHG WRJHWKHU DV FORVH WR WKH VXSSO\ DV SRVVLEOH ,Q DGGLWLRQ WKHVH VXSSOLHV VKRXOG EH GHFRXSOHG DV FORVH WR WKH SDFNDJH DV SRVVLEOH*5281' ,13876 966$ 966'7KH ,6' VHULHV XWLOL]HV VHSDUDWH DQDORJ DQG GLJLWDO JURXQG EXVVHV 7KH DQDORJ JURXQG 966$ SLQV VKRXOG EH WLHG WRJHWKHU DV FORVH WR WKH SDFN DJH DV SRVVLEOH DQG FRQQHFWHG WKURXJK D ORZ LPSHGDQFH SDWK WR SRZHU VXSSO\ JURXQG 7KHGLJLWDO JURXQG 966' SLQ VKRXOG EH FRQQHFWHG WKURXJK D VHSDUDWH ORZ LPSHGDQFH SDWK WR SRZ HU VXSSO\ JURXQG 7KHVH JURXQG SDWKV VKRXOG EH ODUJH HQRXJK WR HQVXUH WKDW WKH LPSHGDQFH EH WZHHQ WKH 966$ SLQV DQG WKH 966' SLQ LV OHVV WKDQ Ω 7KH EDFNVLGH RI WKH GLH LV FRQQHFWHG WR 966WKURXJK WKH VXEVWUDWH UHVLVWDQFH ,Q D FKLS RQ ERDUG GHVLJQ WKH GLH DWWDFK DUHD PXVW EH FRQ QHFWHG WR 966 RU OHIW IORDWLQJ121 ,19(57,1* $1$/2* ,1387 $1$ ,17KLV SLQ LV WKH QRQ LQYHUWLQJ DQDORJ LQSXW WKDW WUDQV IHUV WKH VLJQDO WR WKH GHYLFH IRU UHFRUGLQJ 7KH DQ DORJ LQSXW DPSOLILHU FDQ EH GULYHQ VLQJOH HQGHG RU GLIIHUHQWLDOO\ ,Q WKH VLQJOH HQGHG LQSXW PRGH D P9S S SHDN WR SHDN PD[LPXP VLJQDO VKRXOG EH FDSDFLWLYHO\ FRQQHFWHG WR WKLV SLQ IRU RSWLPDO VLJQDO TXDOLW\ 7KLV FDSDFLWRU YDOXH WRJHWKHU ZLWK WKH .Ω LQSXW LPSHGDQFH RI $1$ ,1 LV VHOHFWHG WR JLYH FXWRII DW WKH ORZ IUHTXHQF\ HQG RI WKH YRLFH SDVVEDQG ,Q WKH GLIIHUHQWLDO LQSXW PRGH WKH PD[LPXP LQSXW VLJQDO DW $1$ ,1 VKRXOG EH P9S S IRU RSWLPDO VLJQDO TXDOLW\ 7KH FLUFXLW FRQQHFWLRQV IRU WKH WZR PRGHV DUH VKRZQ LQ )LJ XUH RQ SDJH,6' 6HULHV3ISD,19(57,1* $1$/2* ,1387 $1$ ,1¥7KLV SLQ LV WKH LQYHUWLQJ DQDORJ LQSXW WKDW WUDQVIHUV WKH VLJQDO WR WKH GHYLFH IRU UHFRUGLQJ LQ WKH GLIIHU HQWLDO LQSXW PRGH ,Q WKLV GLIIHUHQWLDO LQSXW PRGH D P9S S PD[LPXP LQSXW VLJQDO DW $1$ ,1r VKRXOG EH FDSDFLWLYHO\ FRXSOHG WR WKLV SLQ IRU RS WLPDO VLJQDO TXDOLW\ DV VKRZQ LQ WKH ,6' 6HULHV $1$ ,1 0RGHV )LJXUH 7KLV FDSDFLWRU YDOXH VKRXOG EH HTXDO WR WKH FRXSOLQJ FDSDFLWRU XVHG RQ WKH $1$ ,1 SLQ 7KH LQSXW LPSHGDQFH DW $1$ ,1r LV QRPLQDOO\ .Ω ,Q WKH VLQJOH HQGHG PRGH $1$,1r VKRXOG EH FDSDFLWLYHO\ FRXSOHG WR 966$WKURXJK D FDSDFLWRU HTXDO WR WKDW XVHG RQ WKH $1$ ,1 LQSXW$8',2 287387 $8' 2877KLV SLQ SURYLGHV WKH DXGLR RXWSXW WR WKH XVHU ,W LV FDSDEOH RI GULYLQJ D .Ω LPSHGDQFH ,W LV UHFRPPHQGHG WKDW WKLV SLQ EH $& FRXSOHGNOTE7KH $8'287 SLQ LV DOZD\V DW YROWV ZKHQ WKH GHYLFH LV SRZHUHG XS :KHQ LQ SOD\ EDFN WKH RXWSXW EXIIHU FRQQHFWHG WR WKLV SLQ FDQ GULYH D ORDG DV VPDOO DV .Ω :KHQ LQ UHFRUG D UHVLVWRU FRQQHFWV $8' 287 WR WKH LQWHUQDO YROW DQDORJ JURXQG VXSSO\ 7KLV UHVLVWRU LV DSSUR[LPDWHO\ .Ω EXW ZLOO YDU\ VRPHZKDW DFFRUGLQJ WR WKH VDPSOH UDWH RI WKH GHYLFH 7KLV UHO DWLYHO\ KLJK LPSHGDQFH DOORZV WKLV SLQ WR EH FRQQHFWHG WR DQ DXGLR EXV ZLWKRXW ORDGLQJ LW GRZQ6/$9( 6(/(&7 667KLV LQSXW ZKHQ /2: ZLOO VHOHFW WKH ,6' GHYLFHFigure 3: ISD4003 Series ANA IN Modes,6' 6HULHV4Voice Solutions in Silicon ™0$67(5 287 6/$9( ,1 026,7KLV LV WKH VHULDO LQSXW WR WKH ,6' GHYLFH 7KH PDVWHU PLFURFRQWUROOHU SODFHV GDWD RQ WKH 026,OLQH RQH KDOI F\FOH EHIRUH WKH ULVLQJ FORFN HGJH WR EH FORFNHG LQ E\ WKH ,6' GHYLFH0$67(5 ,1 6/$9( 287 0,627KLV LV WKH VHULDO RXWSXW RI WKH ,6' GHYLFH 7KLV RXWSXW JRHV LQWR D KLJK LPSHGDQFH VWDWH LI WKH GHYLFH LV QRW VHOHFWHG6(5,$/ &/2&. 6&/.7KLV LV WKH FORFN LQSXW WR WKH ,6' ,W LV JHQHUDW HG E\ WKH PDVWHU GHYLFH PLFURFRQWUROOHU DQG LV XVHG WR V\QFKURQL]H GDWD WUDQVIHUV LQ DQG RXW RI WKH GHYLFH WKURXJK WKH 0,62 DQG 026, OLQHV 'DWD LV ODWFKHG LQWR WKH ,6' RQ WKH ULVLQJ HGJH RI 6&/. DQG VKLIWHG RXW RI WKH GHYLFH RQ WKH IDOOLQJ HGJH RI 6&/.,17(55837 ,177KH ,6' LQWHUUXSW SLQ JRHV /2: DQG VWD\V /2:ZKHQ DQ 2YHUIORZ 29) RU (QG RI 0HVVDJH (20 PDUNHU LV GHWHFWHG 7KLV LV DQ RSHQ GUDLQ RXWSXW SLQ (DFK RSHUDWLRQ WKDW HQGV LQ DQ (20 RU 2YHU IORZ ZLOO JHQHUDWH DQ LQWHUUXSW LQFOXGLQJ WKH PHV VDJH FXHLQJ F\FOHV 7KH LQWHUUXSW ZLOO EH FOHDUHG WKH QH[W WLPH DQ 63, F\FOH LV LQLWLDWHG 7KH LQWHUUXSW VWDWXV FDQ EH UHDG E\ DQ 5,17 LQVWUXFWLRQ 2YHUIORZ )ODJ 29) s7KH 2YHUIORZ IODJ LQGL FDWHV WKDW WKH HQG RI WKH ,6' nV DQDORJ PHP RU\ KDV EHHQ UHDFKHG GXULQJ D UHFRUG RU SOD\EDFN RSHUDWLRQ(QG RI 0HVVDJH (20 s7KH (QG RI 0HVVDJH IODJ LV VHW RQO\ GXULQJ SOD\EDFN RSHUDWLRQ ZKHQ DQ (20 LV IRXQG 7KHUH DUH HLJKW (20 IODJ SRVLWLRQ RSWLRQV SHU URZ52: $''5(66 &/2&. 5$&7KLV LV DQ RSHQ GUDLQ RXWSXW SLQ WKDW SURYLGHV D VLJ QDO ZLWK D PV SHULRG DW WKH .+] VDPSOLQJ IUH TXHQF\ 7KLV UHSUHVHQWV D VLQJOH URZ RI PHPRU\DQG WKHUH DUH URZV RI PHPRU\ LQ WKH ,6' VHULHV GHYLFHV 7KLV VLJQDO VWD\V +,*+ IRU PV DQG VWD\V /2: IRU PV ZKHQ LW UHDFKHV WKH HQG RI D URZ7KH 5$& SLQ VWD\V +,*+ IRU µVHF DQG VWD\V /2: IRU µVHF LQ 0HVVDJH &XHLQJ PRGH VHH SDJH IRU D PRUH GHWDLOHG GHVFULSWLRQ RI 0HVVDJH &XHLQJ 5HIHU WR WKH $& 3DUDPHWHUV WD EOH IRU 5$& WLPLQJ LQIRUPDWLRQ RQ RWKHU VDPSOH UDWH SURGXFWV:KHQ D UHFRUG FRPPDQG LV ILUVW LQLWLDWHG WKH 5$&SLQ UHPDLQV +,*+ IRU DQ H[WUD 75$&/2 SHULRG 7KLV LV GXH WR WKH QHHG WR ORDG VDPSOH DQG KROG FLUFXLWV LQWHUQDO WR WKH GHYLFH 7KLV SLQ FDQ EH XVHG IRU PHVVDJH PDQDJHPHQW WHFKQLTXHV(;7(51$/ &/2&. ,1387 ;&/.7KH H[WHUQDO FORFN LQSXW IRU WKH ,6' SURGXFWV KDV DQ LQWHUQDO SXOO GRZQ GHYLFH 7KHVH SURGXFWV DUH FRQILJXUHG DW WKH IDFWRU\ ZLWK DQ LQWHUQDO VDP SOLQJ FORFN IUHTXHQF\ FHQWHUHG WR SHUFHQW RI VSHFLILFDWLRQ 7KH IUHTXHQF\ LV WKHQ PDLQWDLQHG WR D YDULDWLRQ RI SHUFHQW RYHU WKH HQWLUH FRP PHUFLDO WHPSHUDWXUH DQG RSHUDWLQJ YROWDJH UDQJHV 7KH LQWHUQDO FORFN KDV D r SHUFHQW WRO HUDQFH RYHU WKH H[WHQGHG WHPSHUDWXUH LQGXVWULDO WHPSHUDWXUH DQG YROWDJH UDQJHV $ UHJXODWHG SRZHU VXSSO\ LV UHFRPPHQGHG IRU LQGXVWULDO WHP SHUDWXUH UDQJH SDUWV ,I JUHDWHU SUHFLVLRQ LV UH TXLUHG WKH GHYLFH FDQ EH FORFNHG WKURXJK WKH ;&/. SLQ LQ 7DEOH,6' 6HULHV5ISD7KHVH UHFRPPHQGHG FORFN UDWHV VKRXOG QRW EH YDULHG EHFDXVH WKH DQWLDOLDVLQJ DQG VPRRWKLQJ ILOWHUV DUH IL[HG 7KXV DOLDVLQJ SUREOHPV FDQ RFFXU LI WKH VDPSOH UDWH GLIIHUV IURP WKH RQH UHFRPPHQGHG 7KH GXW\ F\FOH RQ WKH LQSXW FORFN LV QRW FULWLFDO DV WKH FORFN LV LPPHGLDWHO\ GLYLGHG E\ WZR LQWHUQDOO\ ,I WKH ;&/. LV QRW XVHG WKLV LQSXW VKRXOG EH FRQQHFWHG WR JURXQG$872087( )($785( $0 &$37KLV SLQ LV XVHG LQ FRQWUROOLQJ WKH $XWR0XWH IHDWXUH 7KH $XWR0XWH IHDWXUH DWWHQXDWHV WKH VLJQDO ZKHQ LW GURSV EHORZ DQ LQWHUQDOO\ VHW WKUHVKROG 7KLV KHOSV WR HOLPLQDWH QRLVH ZLWK G% RI DWWHQXDWLRQ ZKHQ WKHUH LV QR VLJQDO L H GXULQJ SHULRGV RI VLOHQFH $ µ) FDSDFLWRU WR JURXQG VKRXOG EH FRQQHFWHG WR WKH $0&$3 SLQ 7KLV FDSDFLWRU EHFRPHV D SDUW RI DQ LQWHUQDO SHDN GHWHFWRU ZKLFK VHQVHV WKH VLJQDO DPSOLWXGH SHDN 7KLV SHDN OHYHO LV FRPSDUHG WR DQ LQWHUQDOO\ VHW WKUHVKROG WR GHWHUPLQH WKH $XWR 0XWH WULS SRLQW )RU ODUJH VLJQDOV WKH $XWR0XWH DW WHQXDWLRQ LV VHW WR G% ZKLOH G% RI DWWHQXDWLRQ RFFXUV IRU VLOHQFH 7KH µ) FDSDFLWRU DOVR DIIHFWV WKH UDWH DW ZKLFK WKH $XWR0XWH IHDWXUH FKDQJHV ZLWK WKH VLJQDO DPSOLWXGH RU WKH DWWDFN WLPH 7KH $XWRPXWH IHDWXUH FDQ EH GLVDEOHG E\ FRQQHFWLQJ WKH $0&$3 SLQ WR 9&&$6(5,$/ 3(5,3+(5$/ ,17(5)$&( 63, '(6&5,37,217KH ,6' VHULHV RSHUDWHV IURP DQ 63, VHULDO LQWHU IDFH 7KH 63, LQWHUIDFH RSHUDWHV ZLWK WKH IROORZLQJ SURWRFRO7KH GDWD WUDQVIHU SURWRFRO DVVXPHV WKDW WKH PL FURFRQWUROOHUnV 63, VKLIW UHJLVWHUV DUH FORFNHG RQ WKH IDOOLQJ HGJH RI WKH 6&/. :LWK WKH ,6' GDWD LV FORFNHG LQ RQ WKH 026, SLQ RQ WKH ULVLQJ FORFN HGJH 'DWD LV FORFNHG RXW RQ WKH 0,62 SLQ RQ WKH IDOOLQJ FORFN HGJH1.$OO VHULDO GDWD WUDQVIHUV EHJLQ ZLWK WKH IDOOLQJHGJH RI 66 SLQ 2.66 LV KHOG /2: GXULQJ DOO VHULDO FRPPXQLFDWLRQV DQG KHOG +,*+ EHWZHHQ LQVWUXFWLRQV 3.'DWD LV FORFNHG LQ RQ WKH ULVLQJ FORFN HGJHDQG GDWD LV FORFNHG RXW RQ WKH IDOOLQJ FORFN HGJH 4.3OD\ DQG 5HFRUG RSHUDWLRQV DUH LQLWLDWHG E\HQDEOLQJ WKH GHYLFH E\ DVVHUWLQJ WKH 66 SLQ /2: VKLIWLQJ LQ DQ RSFRGH DQG DQ DGGUHVV ILHOG WR WKH ,6' GHYLFH UHIHU WR WKH 2S FRGH 6XPPDU\ RQ WKH IROORZLQJ SDJH 5.7KH RSFRGHV DQG DGGUHVV ILHOGV DUH DV IROORZV FRQWURO ELWV! DQG DGGUHVV ELWV! 6.(DFK RSHUDWLRQ WKDW HQGV LQ DQ (20 RU2YHUIORZ ZLOO JHQHUDWH DQ LQWHUUXSW LQFOXG LQJ WKH 0HVVDJH &XHLQJ F\FOHV 7KH ,QWHU UXSW ZLOO EH FOHDUHG WKH QH[W WLPH DQ 63,F\FOH LV LQLWLDWHG 7.$V ,QWHUUXSW GDWD LV VKLIWHG RXW RI WKH,6' 0,62 SLQ FRQWURO DQG DGGUHVV GDWD LV VLPXOWDQHRXVO\ EHLQJ VKLIWHG LQWR WKH 026, SLQ &DUH VKRXOG EH WDNHQ VXFK WKDW WKH GDWD VKLIWHG LQ LV FRPSDWLEOH ZLWK FXUUHQW V\VWHP RSHUDWLRQ ,W LV SRVVLEOH WR UHDG LQWHUUXSW GDWD DQG VWDUW D QHZ RSHUD WLRQ ZLWKLQ WKH VDPH 63, F\FOH 8.$Q RSHUDWLRQ EHJLQV ZLWK WKH 581 ELW VHWDQG HQGV ZLWK WKH 581 ELW UHVHW 9.$OO RSHUDWLRQV EHJLQ ZLWK WKH ULVLQJ HGJHRI 66Table 1:External Clock Input Clocking TablePart Number Sample Rate Required Clock,6' 0 .+] .+],6' 0 .+] .+],6' 0 .+] .+],6' 0.+].+],6' 6HULHV 6Voice Solutions in Silicon ™0(66$*( &8(,1*0HVVDJH FXHLQJ DOORZV WKH XVHU WR VNLS WKURXJK PHVVDJHV ZLWKRXW NQRZLQJ WKH DFWXDO SK\VLFDO OR FDWLRQ RI WKH PHVVDJH 7KLV RSHUDWLRQ LV XVHG GXU LQJ SOD\EDFN ,Q WKLV PRGH WKH PHVVDJHV DUHVNLSSHG WLPHV IDVWHU WKDQ LQ QRUPDO SOD\ EDFN PRGH ,W ZLOO VWRS ZKHQ DQ (20 HQG RI PHV VDJH PDUNHU LV UHDFKHG 7KHQ WKH LQWHUQDO DGGUHVV FRXQWHU ZLOO SRLQW WR WKH QH[W PHVVDJHHr htrÃ8 rv tÃph Ãirà ryrp rqà y Ãh à urÃirtv v tà sÃhà yh à r h v!6 à urÃD r Ãqh hÃv à uvs rqà à sà urÃDT9# " Ãp yÃh qÃhqq r Ãqh hÃv Ãirv tà uvs rqÃv Ã8h rà u yqÃirà hxr à puà uh à urÃqh hà uvs rqÃv Ãv Ãp h viyrà v uÃp r à r à r h v ÃD Ãv à viyrà à rhqÃv r Ãqh hÃh qà h Ãhà r à r h v Ãh à urà h rà v r ÃTrrÃAvt rÃ%à u tuÃAvt rÃ(Ãs ÃP p qrÃs h32:(5 83 6(48(1&(7KH ,6' ZLOO EH UHDG\ IRU DQ RSHUDWLRQ DIWHU 738' PV DSSUR[LPDWHO\ IRU .+] VDPSOH UDWH 7KH XVHU QHHGV WR ZDLW 738' EHIRUH LVVXLQJ DQ RSHUD WLRQDO FRPPDQG )RU H[DPSOH WR SOD\ IURP DG GUHVV WKH IROORZLQJ SURJUDPLQJ F\FOH VKRXOG EH XVHG 3OD\EDFN 0RGH6HQG 32:(583 FRPPDQG :DLW 738' SRZHU XS GHOD\6HQG 6(73/$< FRPPDQG ZLWK DGGUHVV 6HQG 3/$< FRPPDQG7KH GHYLFH ZLOO VWDUW SOD\EDFN DW DGGUHVV DQG LW ZLOO JHQHUDWH DQ LQWHUUXSW ZKHQ DQ (20 LV UHDFKHG ,W ZLOO WKHQ VWRS SOD\EDFN5HFRUG 0RGH1.6HQG 32:(583 FRPPDQG2.:DLW 738' SRZHU XS GHOD\3.6HQG 32:(583 FRPPDQG4.:DLW [738' SRZHU XS GHOD\5.6HQG 6(75(& FRPPDQG ZLWK DGGUHVV6.6HQG 5(& FRPPDQG7KH GHYLFH ZLOO VWDUW UHFRUGLQJ DW DGGUHVV DQG LW ZLOO JHQHUDWH DQ LQWHUUXSW ZKHQ DQ RYHUIORZ LV UHDFKHG HQG RI PHPRU\ DUUD\ ,W ZLOO WKHQ VWRS UH FRUGLQJTable 2: Opcode SummaryInstruction Opcode <5 bits> Address <11 bits>Operational Summary32:(583 ;;;;;;;;;;;!3RZHU 8S 'HYLFH ZLOO EH UHDG\ IRU DQ RSHUDWLRQ DIWHU 7QV9 6(73/$< $ r$ !,QLWLDWHV 3OD\EDFN IURP DGGUHVV $ r$ !3/$< ;;;;;;;;;;;!3OD\EDFN IURP WKH FXUUHQW DGGUHVV XQWLO (20 RU 29) 6(75(& $ r$ !,QLWLDWHV D 5HFRUG RSHUDWLRQ IURP DGGUHVV $ r$ ! 5(& ;;;;;;;;;;;!5HFRUGV IURP FXUUHQW DGGUHVV XQWLO 29) LV UHDFKHG 6(70& $ r$ !,QLWLDWHV 0HVVDJH &XHLQJ 0& IURP DGGUHVV $ r$ !0& ;;;;;;;;;;;!3HUIRUPV D 0HVVDJH &XH 3URFHHGV WR WKH HQG RI WKH FXUUHQW PHVVDJH (20 RU HQWHUV 29) FRQGLWLRQ LI QR PRUH PHVVDJHV DUH SUHVHQW 6723 ; ;;;;;;;;;;;!6WRSV FXUUHQW RSHUDWLRQ67233:5'1 ; ; ;;;;;;;;;;;!6WRSV FXUUHQW 2SHUDWLRQ DQG HQWHUV VWDQG E\ SRZHU GRZQ PRGH 5,17!; ;;;;;;;;;;;!5HDG ,QWHUUXSW VWDWXV ELWV 2YHUIORZ DQG (20,6' 6HULHV7ISD63, 32577KH IROORZLQJ GLDJUDP GHVFULEHV WKH 63, SRUW DQG WKH FRQWURO ELWV DVVRFLDWHG ZLWK LWFigure 4: SPI Port63, &21752/ 5(*,67(57KH 63, FRQWURO UHJLVWHU SURYLGHV FRQWURO RI LQGLYLGXDO GHYLFH IXQFWLRQV VXFK DV 3OD\ 5HFRUG 0HVVDJH &XHLQJ 3RZHU 8S DQG 3RZHU 'RZQ 6WDUW DQG 6WRS RSHUDWLRQV DQG ,JQRUH $GGUHVV SRLQWHUVXur ÃD67à Dt rÃ6qq r Ã7v Ãv à r à à Ãhà yh ihpxà à rp qà r h v à h Ãs Ãhqq r à 6(¥6 ÃA Ãp rp v rà yh ihpxà à rp q ÃD67à u yqÃirÃpuh trqà Ãhà Ãirs rà urÃr qà sà uh à à rrÃS68à v v t ÃP ur v rà urÃDT9# "à vyyà r rh à urà r h v Ãs à urà h rà Ãhqq r ÃA à r à h htr r à urÃS Ã6qq r Ã8y pxà S68 à v Ãh qÃD67Ãph Ãirà rqà à rÃh qà urà r à rt rTable 3: SPI Control RegisterControl Register Bit Device FunctionControl Register Bit Device Function581(QDEOH RU 'LVDEOH DQ RSHUDWLRQ380DVWHU SRZHU FRQWURO6WDUW 6WRS3RZHU 8S 3RZHU 'RZQ3 56HOHFWV 3OD\ RU 5HFRUG RSHUDWLRQ,$%,JQRUH DGGUHVV FRQWURO ELW3OD\5HFRUG,JQRUH LQSXW DGGUHVV UHJLVWHU $ r$ 8VH WKH LQSXW DGGUHVV UHJLVWHU FRQWHQWV IRU DQ RSHUDWLRQ $ r$ 0&(QDEOH RU 'LVDEOH 0HVVDJH &XHLQJ3 r3 2XWSXW RI WKH URZ SRLQWHU UHJLVWHU(QDEOH 0HVVDJH &XHLQJ 'LVDEOH 0HVVDJH &XHLQJ$ r$,QSXW DGGUHVV UHJLVWHU,6' 6HULHV8Voice Solutions in Silicon ™T r r Ãhi rà u rÃyv rqà h Ãph rà r h r Ãqh htrà à urÃqr vpr Ã@ rà à urÃhi y rà h v à h v t à h Ãhssrp Ãqr vprà ryvhivyv ÃA p v hyà r h v Ãv à Ãv yvrqÃh à ur rÃp qv v Ã8h rà r r h r ! W &&Ã2ÃW &&$Ã2ÃW &&' "W 66Ã2ÃW 66$Ã2ÃW 66' ÃTable 4:Absolute Maximum Ratings (Packaged Parts)(1)ConditionValue -XQFWLRQ WHPSHUDWXUH &6WRUDJH WHPSHUDWXUH UDQJH r & WR &9ROWDJH DSSOLHG WR DQ\ SLQ 9TT r 9 WR 988 9 9ROWDJH DSSOLHG WR DQ\ SLQ,QSXW FXUUHQW OLPLWHG WR P$9TT r 9 WR 988 99ROWDJH DSSOLHG WR 026, 6&/.,17 5$& DQG 66 SLQV ,QSXW FXUUHQW OLPLWHG WR P$ 9TT r 9 WR 9/HDG WHPSHUDWXUHVROGHULQJ r VHFRQGV &988 r 9TTr 9 WR 9Table 5:Operating Conditions (Packaged Parts)ConditionValue&RPPHUFLDO RSHUDWLQJ WHPSHUDWXUH UDQJH & WR &([WHQGHG RSHUDWLQJ WHPSHUDWXUH r & WR &,QGXVWULDO RSHUDWLQJ WHPSHUDWXUHr & WR &6XSSO\ YROWDJH 988 ! 9 WR 9*URXQG YROWDJH 9TT "9Figure 5: SPI Interface Simplified Block Diagram,6' 6HULHV9ISDU vphyà hy r )ÃU 6Ã2Ã!$ 8Ãh qÃ" ÃW! 6yyà v h Ãyv v Ãh rÃt h h rrqÃi ÃDT9à vhÃryrp vphyà r v tà Ãpuh hp r v h v ÃI Ãhyyà rpvsvph v Ãh rà à r pr à r rq" W 886Ãh qÃW 889Ãp rp rqà tr ur# TTÃ2ÃW 886Ã2ÃW 889 ÃY8GFÃ2ÃHPTDÃ2ÃW TT62ÃW TT9Ãh qÃhyyà ur à v Ãsy h v t $Hrh rqà v uÃ6 H rÃsrh rÃqv hiyrqTable 6: DC Parameters (Packaged Parts)Symbol ParametersMin (2)Typ (1)Max (2)UnitsConditions9DG ,QSXW /RZ 9ROWDJH 988[99DC ,QSXW +LJK 9ROWDJH 988[99PG 2XWSXW /RZ 9ROWDJH 9,PG $9PG 5$& ,17 2XWSXW /RZ 9ROWDJH9,PG P$9PC 2XWSXW +LJK 9ROWDJH 988r9,PC r $,88988 &XUUHQW 2SHUDWLQJ s 3OD\EDFN s 5HFRUGP$P$5@YU ∝ " 5@YU ∝à ",T7988 &XUUHQW 6WDQGE\$ " à #,DG ,QSXW /HDNDJH &XUUHQW $,Ca 0,62 7ULVWDWH &XUUHQW$5@YU 2XWSXW /RDG ,PSHGDQFH .Ω56I6ÃDI $1$ ,1 ,QSXW 5HVLVWDQFH .Ω56I6ÃDIr $1$ ,1r ,QSXW 5HVLVWDQFH.Ω$6SQ$1$ ,1 RU $1$ ,1r WR $8' 287 *DLQG%$Table 7: AC Parameters (Packaged Parts)Symbol CharacteristicMin (2)Typ (1)Max (2)Units Conditions)T6DPSOLQJ )UHTXHQF\,6' 0,6' 0,6' 0,6' 0 .+].+].+].+] $ $ $ $)8A)LOWHU 3DVV %DQG,6' 0,6' 0,6' 0,6' 0 .+].+].+].+] G% 5ROO 2II 3RLQW " à & G% 5ROO 2II 3RLQW " à & G% 5ROO 2II 3RLQW " à & G% 5ROO 2II 3RLQW " à &7S@85HFRUG 'XUDWLRQ,6' 0,6' 0,6' 0,6' 0PLQ PLQ PLQ PLQ% % % %ISD4003 Series10Voice Solutions in Silicon ™1.Typical values: T A = 25°C and 3.0 V.2.All min/max limits are guaranteed by ISD via electrical testing or characterization. Not all specifications are 100 percent tested.3.Low-frequency cut off depends upon the value of external capacitors (see Pin Descriptions).4.Single-ended input mode. In the differential input mode, V IN maximum for ANA IN+ and ANA IN– is 16 mVp-p.5.Sampling Frequency can vary as much as ±2.25 percent over the commercial temperature, and voltage ranges, and –6/+4 percent over the extended temperature, industrial temperature and voltage ranges. For greater stability, an external clock can be utilized (see Pin Descriptions).6.Playback and Record Duration can vary as much as ±2.25 percent over the commercial temperature and voltage ranges, and –6/+4 percent over the extended temperature, industrial temperature and voltage ranges. For greater stability, an external clock can be utilized (see Pin Descriptions).7.Filter specification applies to the antialiasing filter and the smoothing filter. Therefore, from input to output, expect a 6dB drop by nature of passing through both filters.8.The typical output voltage will be approximately 570mVp-p with V IN at 32mVp-p.9.For optimal signal quality, this maximum limit is recommended.10.When a record command is sent, T RAC =T RAC +T RACLO on the first row addressed.T PLAYPlayback DurationISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 4568min min min min (6)(6)(6)(6)T PUDPower-Up DelayISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 2531.2537.550msec msec msec msec T STOP or T PAUSEStop or Pause in Record or PlayISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 5062.575100msec msec msec msec T RACRAC Clock PeriodISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 200250300400msec msec msec msec (10)(10)(10)(10)T RACLORAC Clock Low TimeISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 2531.2537.550msec msec msec msec T RACMRAC Clock Period in Message Cueing Mode ISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M 125156.3187.5250µsec µsec µsec µsec T RACMLRAC Clock Low Time in Message Cueing ModeISD4003-04M ISD4003-05M ISD4003-06M ISD4003-08M15.6319.5323.4431.25µsec µsec µsec µsec THD Total Harmonic Distortion 12%@ 1 KHzV INANA IN Input Voltage32mVPeak-to-Peak (4) (8) (9)Table 7: AC Parameters (Packaged Parts)Symbol CharacteristicMin (2)Typ (1)Max (2)Units Conditions,6' 6HULHV11ISDT r r Ãhi rà u rÃyv rqà h Ãph rà r h r Ãqh htrà à urÃqr vpr Ã@ rà à urÃhi y rà h v à h v t à h Ãhssrp Ãqr vprà ryvhivyv ÃA p v hyà r h v Ãv à Ãv yvrqÃh à ur rÃp qv v ÃW &&Ã2ÃW &&$Ã2ÃW &&'!W 66Ã2ÃW 66$Ã2ÃW 66' ÃTable 8:Absolute Maximum Ratings (Die)(1)ConditionValue -XQFWLRQ WHPSHUDWXUH &6WRUDJH WHPSHUDWXUH UDQJH r & WR &9ROWDJH DSSOLHG WR DQ\ SDG 9TT r 9 WR 988 9 9ROWDJH DSSOLHG WR DQ\ SDG,QSXW FXUUHQW OLPLWHG WR P$9TT r 9 WR 988 99ROWDJH DSSOLHG WR 026, 6&/. ,17 5$& DQG 66 SLQV ,QSXW FXUUHQW OLPLWHG WR P$ 9TT r 9 WR 9988 r 9TTr 9 WR 9Table 9:Operating Conditions (Die)ConditionValue&RPPHUFLDO RSHUDWLQJ WHPSHUDWXUH UDQJH & WR &6XSSO\ YROWDJH 988 9 WR 9*URXQG YROWDJH 9TT !9U vphyà hy r )ÃU 6Ã2Ã!$ 8Ãh qÃ" ÃW! 6yyà v h Ãyv v Ãh rÃt h h rrqÃi ÃDT9à vhÃryrp vphyà r v tà Ãpuh hp r v h v ÃI Ãhyyà rpvsvph v Ãh rà à r pr à r rq" W 886Ãh qÃW 889Ãp rp rqà tr ur# TTÃ2ÃW 8862ÃW 889 ÃY8GFÃ2ÃHPTDÃ2ÃW TT6Ã2ÃW TT9Ãh qÃhyyà ur à v Ãsy h v t $Hrh rqà v uÃ6 H rÃsrh rÃqv hiyrqTable 10: DC Parameters (Die)Symbol ParametersMin (2)Typ (1)Max (2)UnitsConditions9DG ,QSXW /RZ 9ROWDJH 988[99DC ,QSXW +LJK 9ROWDJH 988[99PG 2XWSXW /RZ 9ROWDJH 9,PG $9PG 5$& ,17 2XWSXW /RZ 9ROWDJH9,PG P$9PC 2XWSXW +LJK 9ROWDJH 988r9,PC r $,88988 &XUUHQW 2SHUDWLQJ s 3OD\EDFN s 5HFRUGP$P$5@YU ∞ " 5@YU ∞à ",T7988 &XUUHQW 6WDQGE\$ " à #,DG ,QSXW /HDNDJH &XUUHQW $,Ca 0,62 7ULVWDWH &XUUHQW$5@YU 2XWSXW /RDG ,PSHGDQFH .Ω56I6ÃDI $1$ ,1 ,QSXW 5HVLVWDQFH .Ω56I6ÃDIr $1$ ,1r ,QSXW 5HVLVWDQFH.Ω$6SQ$1$ ,1 RU $1$ ,1r WR $8'287 *DLQG%$。

ISD4003在录放音电路中的应用及其软件设计

都在ss端上升沿开始执行(1SD4003的控制时序详

见技术手册)。

对于没有SPI接口的AT89C2051单片机来说,

可用软件来模拟SPI的操作。下面为部分程序。

Main:…

;主程序

aeall aeall

powenlp delay

;调用ISD4003上电子程序 ;ISIM003上电延时37 5脚

"“p…

[3]秦旭,语音芯片ISD33060及其应用.电了产品维修与

制作,1999,(48):23-25

嫩稿日期】2001-09-04

《电声技术)200z年第1期总第199期

万方数据

ISD4003在录放音电路中的应用及其软件设计

作者: 作者单位:

刊名: 英文刊名: 年,卷(期): 引用次数:

戴冬雪, 南立军 戴冬雪(哈尔滨工业大学电气工程系及自动化学院,黑龙江哈尔滨150001), 南立军(中国北 方车辆研究所,北京,100072)

本文链接:/Periodical_diansjs200201016.aspx

下载时间:2010年5月22日

;放音子程序

spam:clr

elf 邮邮

SPI串行数据输^子程序

l…】㈨/ elf sclk

一一一。崎

=呈 seth

clr dinz

邮~~一~

hop

邮 脯tb

……

上面给出的程序已经调试通过,

[参考文献]

f1]孟军ISD33000系列语音芯片及其特色电于技术应

用,1998,(5):50-54

[2]http:∥www isd.eom

o

万方数据

图1录放音电路 《电声技术>>2002年第1期总第199期

语音芯片

MC 11111〈×××××××××××〉从当前地址开始信息检索,直到遇到标志OVF 或EOM

STOP 0 ×110〈×××××××××××〉停止当前操作

STOP PWRDN 0 ×01 ×〈×××××××××××〉停止当前操作并进入节电状态

2 ISD4003 引脚功能及SPI 控制接口

2. 1 引脚功能简介

VCCA、VCCD :模拟、数字信号电源。

VSSA、VSSD :模拟、数字信号地线。

图1 ISD4003 系列引脚排列图

ANA IN + 、ANA IN - :录音信号输入端。可选择单端ቤተ መጻሕፍቲ ባይዱ入和差动输入两种方式。

协议假设微处理器的串行移位寄存器在串行时钟SCL K的下降沿输出数据。对于ISD4003 系列芯片,数据在串行时钟SCL K 的上升沿输入到引脚MOSI 上,在串行时钟SCL K 的下降沿输出到引脚MISO 上。具体如下:

(1) 所有的串行数据在SS的下降沿开始传输。

(2) SS在整个串行通信过程中保持低电平,在指令之间保持高电平。

器件应用

语音录放芯片ISD4003 及其应用

摘 要 文章介绍了美国ISD 公司的语音录放芯片ISD4003 ,该芯片具有存储语音时间长(4~8min) 、抗断电、低能耗、可反复录放等特点。在微控制器的控制下,组成简单的语音录放系统。

关键词 ISD4003 语音录放芯片 串行外设接口 多媒体语言学习系统

出等) 。通过以上几个引脚,微处理器就可完成对语

音芯片的控制。对于P1 (节目一) 、P2 (节目二) 、

MIC(话筒) 等录音声音源,通过微控制器控制开关

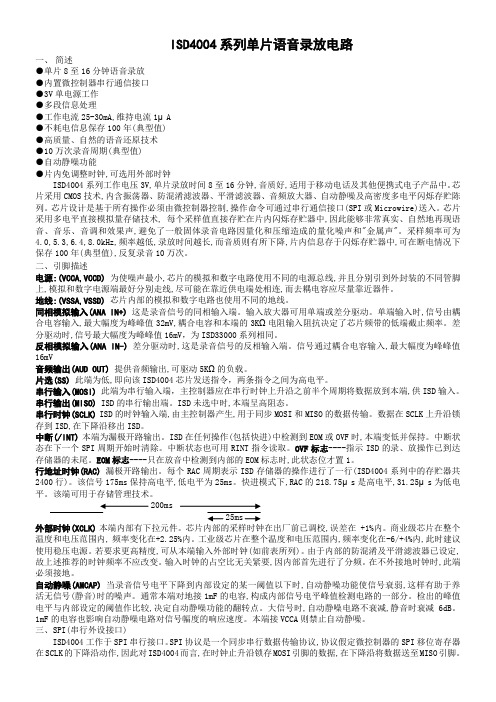

ISD4004控制命令总结

ISD4004 控制命令ISD4004使用三字节的命令字(三字节控制寄存器)SPI 控制寄存器SPI 控制寄存器控制器件的每个功能,如录放、录音、信息检索(快进)、上电/掉电、开控制命令举例:如三字节命令为:E7 F0 00H表示:RUN=1,P/R=1, PU=1, IAB=0(不忽略地址),MC=0, D12~D0=0~0 即从0地址开设放音。

指令表(P/R)(P/U) (IAB 忽略地址)(MC 信息检索)注:快进只能在放音操作开始时选择。

ISD英文资料(PDF文件)的EXAMPLE以4003(指令与4004不同,4003为两字节指令)为例列举了各种命令。

ISD4004信息管理见英文资料(PDF文件)Applications Note 7ISD4004有2400行*160列=3840K,用12位地址寻址行(要采用两个字节16位给出地址),总共可存储960秒(16分钟)语音,每行存储(16分钟)960S/2400=400ms。

如果要存放20段语音,2400/20=120, 则每段语音占120行(78H),120*400=48000=48s 寻址只能寻址行地址。

及每段录音完毕跳过120行(地址+120)4004为12位地址,因为11位地址211=2048,不能表示2400个行地址,所以需要12位地址但是12位地址没有完全用完。

4003位1200行,总共可存储480S信息,10位地址210=1024也不够,所以用11位地址单也地址没完全用完。

每段的录音由定时器定时控制录音的时间,超出每段的时间指示灯闪烁提示每段放音的结束通过语音芯片的INT引脚变为低电平来判断。

每段的录放结束都要发出stop命令,录音完成的STOP 0001 0000, 必须IAB=1忽略地址(见英文资料),才能将EOC放在录音结束处。

放音结束的STOP0000 0000.在STOP后大约需50ms左右放音和录音结束。

录音的指令顺序:1.发SETREC 16位从指定地址录音三字节10100X X X X , A16 …A8 A7 A6 A5 A4 A3 A2 A1 A0 >,其中IAB=0,不忽略地址。

ISD4004芯片资料及看法

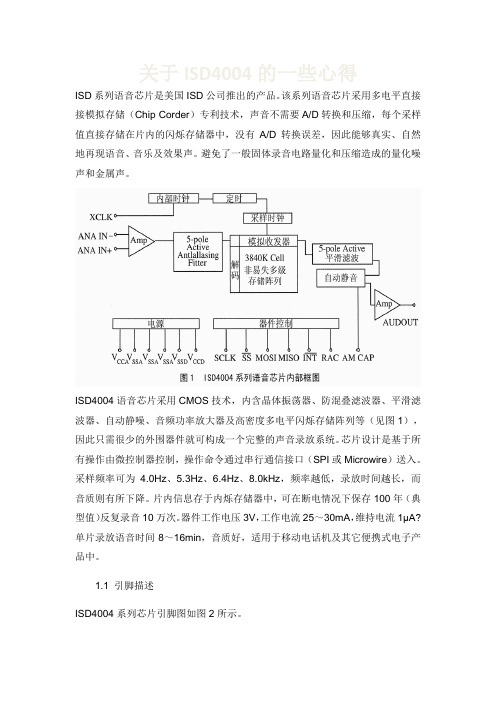

关于ISD4004的一些心得ISD系列语音芯片是美国ISD公司推出的产品。

该系列语音芯片采用多电平直接接模拟存储(Chip Corder)专利技术,声音不需要A/D转换和压缩,每个采样值直接存储在片内的闪烁存储器中,没有A/D转换误差,因此能够真实、自然地再现语音、音乐及效果声。

避免了一般固体录音电路量化和压缩造成的量化噪声和金属声。

ISD4004语音芯片采用CMOS技术,内含晶体振荡器、防混叠滤波器、平滑滤波器、自动静噪、音频功率放大器及高密度多电平闪烁存储阵列等(见图1),因此只需很少的外围器件就可构成一个完整的声音录放系统。

芯片设计是基于所有操作由微控制器控制,操作命令通过串行通信接口(SPI或Microwire)送入。

采样频率可为 4.0Hz、5.3Hz、6.4Hz、8.0kHz,频率越低,录放时间越长,而音质则有所下降。

片内信息存于内烁存储器中,可在断电情况下保存100年(典型值)反复录音10万次。

器件工作电压3V,工作电流25~30mA,维持电流1μA?单片录放语音时间8~16min,音质好,适用于移动电话机及其它便携式电子产品中。

1.1 引脚描述ISD4004系列芯片引脚图如图2所示。

二、引脚描述电源:(VCCA,VCCD) 为使噪声最小, 芯片的模拟和数字电路使用不同的电源总线, 并且分别引到外封装的不同管脚上, 模拟和数字电源端最好分别走线, 尽可能在靠近供电端处相连, 而去耦电容应尽量靠近器件。

地线:(VSSA,VSSD) 芯片内部的模拟和数字电路也使用不同的地线。

同相模拟输入(ANA IN+) 这是录音信号的同相输入端。

输入放大器可用单端或差分驱动。

单端输入时,信号由耦合电容输入, 最大幅度为峰峰值32mV, 耦合电容和本端的3KΩ电阻输入阻抗决定了芯片频带的低端截止频率。

差分驱动时, 信号最大幅度为峰峰值16mV,为ISD33000 系列相同。

反相模拟输入(ANA IN-) 差分驱动时, 这是录音信号的反相输入端。

ISD4000编程拷器使用说明

ISD4000 编程器说明书一、性能特点支持ISD 所有3V 器件:ISD4002、ISD4003、ISD4004 等器件可同时编程/拷贝两块ISD 器件,编程同时还可检测一片芯片专用拷贝软件直接通过电脑控制进行编程(即可指定任意地址写入、修改语音内容)、拷贝、地址测试,简单、易操作,拷贝音质好。

系统状态用四位数码管显示,操作过程用数码管将信息(如地址或段数)显示出来2.按键及输入、输出口说明名称功能说明“试听”位置对已录过的芯片进行试听或对此芯片测地址“拷贝1”位置放置待拷贝的芯片“拷贝2”位置放置待拷贝的芯片电源输入连接编程拷贝机专用电原232 接口将电脑和编程拷贝机用232 缆线相连结音频输入将电脑音频输出与编程拷贝机相连结监听用于实时监听电脑放音时的语音音频输出用于监听被测试芯片的语音,通过放大输出麦克风输入对“拷贝片2”用麦克风录音复位对系统进行复位状态转换开关对系统进行操作状态转换Reset 系统复位Record 录音Copy/Play 放音/测地址Bank/Mode 模式选择/芯片型号选择2.硬件连接1) 将电脑和编程拷贝机用专用的“RS232”电缆相连接2) 将电脑的音频输出和编程拷贝机的音频输入用专用的音频线相连接3) 将状态选择开关拨至“1”4) 接通专用的直流9V 电源,此时将看到数码管显示“PC-1”(地址录音方式)表示工作正常四、系统使用说明1.硬件使用说明1) 地址录音将状态选择开关拨至“1”,系统置为“PC-1”模式,点击软件中的“连续放音”键,即可对已经编缉好的语音进行拷贝工作。

此时编程拷贝机中的地址显示应与软件中的地址相一致。

拷贝的同时可对芯片进行拷贝过的芯片进行测试,此时电脑所放语音与被测试芯片所放语音应同步。

如若需要对其中某一个段进行录音,点击该段即可。

2) 模式录音将状态选择开关拨至“1”,长按“Back/Mode”键约1秒(按此键可在“PC-1”和“PC-2”两状态间切换),系统显示“PC-2”,即进入模式录音状态(模式录音:连续录制各段信息,段与段之间不会有空段存在,即某一段信息的开始地址是它前一段的结束地址)。

机器人化多功能护理床研究与探讨外文文献翻译@中英文翻译@外文翻译要点

机器人化多功能护理床研究与探讨翻译*摘要:人性化设计是现代设计的一个重要理念,它强调在设计产品时从人体工学、生态学、美学等角度达到完美,体现了科技以人为本的思想。

该护理床的设计正是基于这种理念,它不仅能够实现抬背、抬大腿,曲小腿和调整坐姿的功能,并将设计通过Pro/E三维实体建模软件进行模拟和仿真分析,进一步指导和验证设计的合理性。

为满足目前日益提高的家庭护理要求,将机器人的多轴协调控制技术应用于护理床的控制,研制了一种机器人化的多功能护理床.该护理床通过各个床面板之间的协调运动,采用单动或联动方式来实现各种位姿,并通过语音或键盘来控制进行多位姿的运动.护理床的控制系统由主控制模块和辅助控制模块两部分构成.其中主控制模块采用单片机进行控制,这样既可降低成本,又可保证护理床操作的灵活性和可靠性;辅助控制模块包括语音识别和语音回放两部分的功能.实际使用效果证明了所研制的护理床的实用性和有效性.本文由医学论文网与您分享!关键词:机器人化护理床;控制系统;语音识剐;单片机概述:目前,无论是发达国家还是发展中国家,均面临着越来越严重的人口老龄化问题。

老年人由于各项生理机能退化,健康状况普遍不佳,消耗大量医疗资源,增加了医院的负担。

世界各国均在积极探求一种新的健康服务模式,提供更高质量、更可靠、更容易被接受且成本低廉的健康服务。

因此现代远程监护系统的构建,具有很好的发展前景。

本文研究了一种面向社区的基于机器人化多功能式智能健康监护系统,用来对病人的生理参数进行连续、长时间、自动、实时检测,并经分析、处理后实现多类别自动报警、自动记录,而且可以通过网络远程监护便于医护人员及时发现病人的病情变化,随时采取必要的护理与急救措施。

随着社会经济的迅速发展,人民生活水平不断提高,人口寿命不断延长,城市人口正逐步进入老龄化.人口的老龄化对社会医疗服务体系提出了更高的要求,建立以社区为核心的健康监控和疾病预控信息化系统具有很大的现实意义”.老年人由于年龄偏大,肌体的活性逐渐降低,对疾病的抵抗力日益减弱,且疾病多以慢性病为主.对于慢性病人和瘫痪病人而言,除了配合药物和针剂的治疗外,物理方式的护理也必不可少.正确、适当的护理可以大大增强患者肌体的活性,减少并发症的产生.对于许多慢性病患者而言,通过定期服药、适当监护和正确护理,可以不必长期住院.特别是对那些因种种原因不可能长期住院治疗的患者、老年人和残疾人士而言,配置必要的护理设备和用具尤为重要“。

ISD4000系列芯片应用笔记

A Winbond Company®Applications Note 5AThe ISD4000SPI Control PortOperations,a Simplified GuideA simple but powerful command structure is built into the ISD4000 series SPI control port. It’s inherent flexibil-ity allows the software programmer to direct the op-eration of the ISD4000 device with the minimum number of control cycles while allowing full control of the device in it’s several modes. The ISD4002 and ISD4003 devices use a 2-byte control structure and the ISD4004 uses a 3-byte control structure. See Ap-plications Brief #40, “The ISD4003 vs. the ISD4004.”For simplicity, the following discussion will refer specif-ically to the ISD4003. The following paragraphs give some tips on the use of this port and suggest some methods of simplifying some operations.The SPI command registers in the ISD4003 have the following composition:Figure1:The MOSI pin of the SPI port on the device is an input. MOSI stands for Master Out, Slave In. The MISO is an output. MISO stands for Master In, Slave Out. The ISD4003 is operating as a “slave” device to the mi-crocontroller that is running the system. The SPI port also has a serial clock input called SCLK and a select input called SS. The SS stands for Slave Select and is an active LOW signal. All input command cycles in the ISD4003 start with SS pin going LOW; and end with SS pin going HIGH. The bit position of the input data at the time the SS pin goes HIGH determines how the device reacts to the command. Any number of bits may be clocked into the SPI port on an input cycle. The last 5 bits input to the MOSI pin at the time the SS pin goes HIGH deter-mine the command being input, even if many bytes were clocked into the port while the SS pin was LOW. Only the last 16 bits shifted into the SPI port are re-tained in the SPI port hardware.ISD Application Information The ISD4000 SPI Control PortThe SCLK signal clocks the data into the ISD4003. The input data to the MOSI pin must be valid on the rising edge of the SCLK. The output data from the MISO pin changes following the falling edge of the SCLK pin. Consult the data sheet on the ISD4003 for the exact timing. The examples stated below assume the initial state of the SCLK pin is LOW when the SS pin goes LOW to start the command cycle but this is not re-quired.EXAMPLE #1, POWER UP THE DEVICEThe following is an example of a simple command to the ISD4003 SPI port. In this operation, the device is to be powered up so that a Record or Playback cycle can be started later. Consult the diagram at the be-ginning of this Application Note that shows the SPI command registers. This drawing shows the bit posi-tions of the 5 bits that compose the heart of the con-trols, e.g. C0 through C4. This diagram should be used as a reference when reading the explanations below:1.The device is powered up by setting the PUbit. That is, bit C2 must be HIGH and bits C0,C1, C3 and C4 must all be LOW at the end ofthe command cycle. The 5 control bits in theSPI control register should then be set as<00100> where the bit positions are as indi-cated by the diagram above.2.In this example, an entire byte will be shiftedin, since some hardware SPI ports can onlyoperate on whole bytes. It is necessary there-fore to shift in HEX address 20, <0010 0000>just to set the C2 bit. Note that the state of theA9, A8 and “X” bits during this operation donot matter. This will be explained in more de-tail later.3.The command cycle starts by changing SS toa LOW. The input to the MOSI pin is also LOW.The input byte, <0010 0000>, is to beclocked in, right to left. The first 5 bits clockedin, therefore, are all LOW. A single HIGH bit isthen clocked in followed by two more LOWbits. This sequence is shown graphically be-low. The command ends with the SS pin goingback HIGH and the ISD4003 will then begin apower up cycle. In T PUD1 time, the device willbe powered up.The table below shows the power up bit data being shifted from the command byte in the microcontrol-ler into the MOSI pin of the ISD4003 and into byte 2 of the input side of the SPI input port register. Note that the PU bit is shifted to the right out of the microcon-troller and into the ISD4003 SPI port.1.TPUD is the power up delay time of the device.See the ISD4003 data sheet.Shift#command byte inmicrocontrollerSPI port in ISD4003after“N”shiftsShift#command byte inmicrocontrollerSPI port inISD4003after“N”shiftsInitialcondx.<00100000> ---> <00000000>1<00010000> ---> <00000000>5<00000001> ---> <00000000> 2<00001000> ---> <00000000>6<00000000> ---> <10000000> 3<00000100>---><00000000>7<00000000>---><01000000> 4<00000010>---><00000000>8<00000000>---> <00100000>I SD Application Information The ISD4000 SPI Control PortIn this first example, we did not care about the value of the address bits A0 through A9. In fact, since the Run bit, C4, was input as a LOW only the HIGH PU bit had any effect on the ISD4003 and the state of C0, C1 and C3 also did not matter. ISD recommends that anytime data is shifted into a SPI port command register bit position that “does not matter” it should be a “0” for compatibility with possible future features that may be added to the device. Also, note that in some cases, it is necessary to give an ISD device more than one power up command to fully power up the device. See the appropriate data sheet. EXAMPLE #2, RECORD AT AN ADDRESSThis second example assumes the ISD4003 is already powered up and that recording is to begin at a spe-cific address. In this example we will use address 92, or HEX address 5C, <00 0101 1100>. Each control bit in the input side of the command register of the device is set up as follows:C0—The MC bit must be LOW since a message cue-ing cycle is not desired.C1—The IAB bit must be LOW since the address is not being ignored.C2—The PU bit must remain HIGH since the device is already powered up and must remain powered up after this command cycle.C3—The P/R bit must be LOW since a Record cycle is to be started.C4—The RUN bit must be HIGH since an active cycle is to be started.A0 - A9—The address bits must be all be defined since the IAB bit is LOW.1.The transfer of the two bytes of data is begunby changing the SS pin to a LOW. The bytes tobe sent are: HEX address A0 5C, < 10100000> <0101 1100>.2.Again, we are clocking the bits in, right to left2. Therefore, the first bit clocked into the SPI portwill be the A0 address bit which is a “0,” fol-lowed by A1 which is a “0,” followed by A2which is a “1” etc.3.The last of the 16 bits clocked into the SPI portwill be the RUN bit which, of course, is a “1.”4.The command cycle ends with the SS pin go-ing back HIGH. At this time, the Record cyclestarts at the address as specified by A0through A9.NOTE After each command cycle, the data shifted into the ISD4003 remains in the chip’s SPI porthardware. As subsequent operations shift moredata in, bits shifted to the right out of the 16-bitregister space are lost. A record or play opera-tion started with only a 5 or 8 bit inputcommand, and with the IAB bit not set (i.e. at“0”) will cause the A0 through A9 data residentat the end of the operation to be treated as anaddress pointer. This will, of course, be datainput to the SPI port in the previous commandcycle mostly from the C0 through C4 bit posi-tions. This is probably not valid address data. EXAMPLE #3, PLAYBACK AT ANADDRESSThis second example assumes the ISD4003 is already powered up and that playback is to begin at a spe-cific address. In this example we will use address 92, or HEX address 5C, <00 0101 1100>. Each control bit in the input side of the command register of the device is set up as follows:C0—The MC bit must be LOW since a message cue-ing cycle is not desired.C1—The IAB bit must be LOW since the address is not being ignored.C2—The PU bit must remain HIGH since the device is already powered up and must remain powered up after this command cycle.2.Some microcontrollers with hardware SPI ports onlyhave the ability to do a left to right shift.Consult themP data sheet for details.In this case,the bit placementof the data shifted in would be inverted.In this exam-ple,the A0would become05and the5C would become3A.When doing the bit placement inversion,don’t for-get that two of the address bits fall in the"control byte"of the data sent into the device.ISD Application Information The ISD4000 SPI Control PortC3—The P/R bit must be HIGH since a Playback cycle is to be started.C4—The RUN bit must be HIGH since an active cycle is to be started.A0 - A9—The address bits must be all be defined since the IAB bit is LOW.1.The transfer of the two bytes of data is begunby changing the SS pin to a LOW. The bytes tobe sent are: HEX address E0 5C, < 11100000> <0101 1100>.2.The first bit clocked into the SPI port will be theA0 address bit which is a “0,” followed by A1which is a “0,” followed by A2 which is a “1”etc.3.The last of the 16 bits clocked into the SPI portwill be the RUN bit which, of course, is a “1.”4.The command cycle ends with the SS pin go-ing back HIGH. At this time, the Playback cy-cle starts at the address as specified by A0through A9.EXAMPLE #4, STOP RECORD OR PLAYBACK AND POWER DOWN THE DEVICEThis example assumes that a Record cycle or a Play-back cycle is underway and that the operation is to be terminated. The device is also to be powered down by this control cycle. The same command may be used to perform this function in both the Record and the Playback cycles. In this example, a full byte transfer is assumed.1. A record or playback operation is terminatedby clocking a command cycle into the SPIport with the RUN bit LOW. The PU bit is also lowin this example so that the device powersdown. The IAB bit must be HIGH at end of arecord cycle to make sure the EOM gets set inthe correct place. The rest of the bits in thecommand byte do not matter but by con-vention they are to be left LOW. The com-mand byte needed, to end and power downa record cycle is therefore HEX address 10,<0001 0000> and the command byteneeded to end and power down a playbackcycle is HEX address 00, <0000 0000>.2.Again, the transfer of the command byte ofdata is begun by changing the SS pin to aLOW followed by the byte as describedabove.3.Record or playback will end in approximately50 milliseconds (again, the data sheet willhave exact information) followed by devicepower down.EXAMPLE #5, ADDRESS JUMP DURING RECORD OR PLAYBACKOne of the ISD4003’s key features is to seamlessly jump from one address to any other address during the course of a Record or Playback cycle. This func-tion enables the Message Management operations described in Application Note #7, “Message Man-agement in the ISD4003 Series.” The following discus-sion describes how this feature works:The ISD4003 memory array may be thought of as an address map of 600 rows by 1600 columns. Only the rows may be addressed. When an operation begins on a row at address “n,” it begins in column “0” and proceeds through the row to column 1199 if not stopped by a command cycle along the way.The internal address sequencer in the ISD4003 oper-ates in one of two possible modes. As a record or playback operation proceeds through the device, at the end of each row, a decision must be made as to where to go next. If the IAB bit is set (“1”) when the end of the row is reached, then the address sequencer in-crements by 1 count and record or playback pro-ceeds to the next row in sequence. If the IAB bit is cleared (“0”) when the end of the row is reached, then the address sequencer pulls the address from the SPI command register and record or playback proceeds at the row defined by this address. This transition from the end of one row to the beginning of some other row not in sequence is seamless. No samples are lost as record or playback proceeds across the boundary without problems.INTERRUPT SERVICEThe interrupt service structure of the ISD4003 may be read with only 8 SPI clock cycles. The following exam-ple demonstrates how this is possible:I SD Application Information The ISD4000 SPI Control PortEXAMPLE #5, READ INTERRUPT STATUS AND CLEAR THE DEVICE INTERRUPT CONDITIONThe ISD4003 device has only two interrupting condi-tions: (1) End Of Message (EOM) which signifies that a set EOM bit has been found during a Playback cycle and (2) Overflow (OVF) which indicates that the end of device memory has been encountered during ei-ther a Record or a Playback cycle. Note that an Overflow interrupt can only occur at the end of the last row in the device’s memory.Both of these conditions result from the end of device operation, i.e. playback or record has ceased. Both conditions cause the INT3 pin of the device to be pulled LOW. This pin will remain LOW until the next SPI cycle in the ISD4003 device.As the interrupt condition is read and clocked out of the MISO pin, data is being simultaneously being clocked into the MOSI pin. This input data will be in-terpreted as a control input and the device will react accordingly. It is necessary, therefore, to make sure this input data leaves the ISD4003 in a desired state. Since the interrupt always results from the end off an operation, shifting in a power-up command, as illus-trated in example #1 above, is usually a safe re-sponse. In this example below, we are assuming we are shifting in HEX address 20, <0010 0000> while the interrupt data is being shifted out.The following description shows how interrupt status may be read from the ISD4003:1.The interrupt status read cycle begins with theSS pin of the device being changed to aLOW. At that time, the state of the OVF bit willbe presented to the MISO output. This level isstatic. That is, it will remain low as long as theSS pin stays LOW and the SCLK pin is notclocked.2.The first clock cycle of the input to the SCLKpin will now cause the state of the EOM bit tobe presented to the MISO output.3.Seven more clocks must be presented to theSCLK pin to insure the interrupt condition isproperly cleared.4.The interrupt status read is terminated bychanging the SS pin back to a HIGH. Whenthe SS pin goes HIGH, the INT pin output will beallowed to go back HIGH, pulled up by the ex-ternal pull-up resistor.The above examples demonstrate the ease of use of the ISD4003 family device. A Record or Playback cy-cle may be started and controlled with a minimum number of SPI clock cycles. This translates into a voice record and playback system that requires very little overhead from the controller in the system.3.INT is an active LOW open drain output.If this outputis to be used,a pull-up resistor must be installed to pull the pin up to the proper HIGH level.Application Information for ChipCorder Products APPLICATIONS BRIEF 41 — AUTOMATIC DEVICE DETECTION OF ISD33000AND ISD4000 DEVICESIt is often economical to design a product so that more than one sized ISD device may be used, as market needs dictate. Optimally, one piece of software is written to be used with multiple prod-ucts. The automatic detection of which device is installed in the PC board will help enable this sort of flexibility.But this may not be an easy task. There are cur-rently 2 array sizes available for the ISD33000 and 3 array sizes in the ISD4000 series devices. Ad-dress lengths of 9 to 12 bits are found in the vari-ous versions. Row counts of 400 to 2400 may be found. The ISD33000 and the ISD4000 devices have different row lengths. And finally, the ISD4004 requires a 3-byte control sequence while the rest of the devices in the list require only 2 bytes. This Application Brief shows a technique that may be used to determine which device is being used.The following sequence will determine whether or not a device that requires a 3-byte command (an ISD4004) is present. In each case a 2 or 3 byte sequence will be input to the device. The two Figures below describe the format of the data:Figure 37: Example 3-Byte Command Sequence Figure 38: Example 2-Byte Command SequenceApplication Information for ChipCorder Products1.Enter the 3-byte SPI command E7 F0 00(hex). The “E” sets the RUN, PLAY/REC and PU bits. The “7” sets the 3 highest order bits in a 2-byte command struc-ture.A.If the device is an ISD4004, this willbe interpreted as a 3-bytecommand. The “7” and the “F” willbe ignored as these bit locationsare all “don’t care” bits in theaddress and control decode. TheISD4004 will see this as a correctrequest to begin a play operationat address “0”.B.If the device is not an ISD4004, allother possible devices will ignorethe “00” in the highest order byte.Only the last two bytes shifted in,the E7 F0, will be contained in theSPI port registers after thecommand is shifted in.C.If the device is an ISD4003, all 11 bitspossible address bits in the 2-bytecommand will be decoded and willbe interpreted as 7F0 (hex). This isabove the highest address possiblein an ISD4003, 4AF (hex) and thedevice will immediately give anOverflow Interrupt.D.If the device is an ISD4002, then onlythe first 10 bits of the address will bedecoded. The result is address 3F0.This is above the highest addresspossible in an ISD4002, 257 (hex)and the device will immediatelygive an Overflow Interrupt.E.If the device is an ISD33000 (800-row array), the first 10 bits of theaddress will be decoded. The resultis address 3F0. This is above thehighest address possible in anISD33000 (800-row array), 31F (hex)and the device will immediatelygive an Overflow Interrupt.F.If the device is an ISD33000 (400-row array), then the first 9 bits of theaddress will be decoded. The resultis address 1F0. This is above thehighest address possible in anISD33000 (400-row array), 18F (hex)and the device will immediatelygive an Overflow Interrupt.The result of this first operation is that any device except an ISD4004 will immediately generate an Overflow Interrupt. Therefore, if an Overflow In-terrupt does not occur within a few milliseconds of the HIGH going Slave Select input, then the device must be an ISD4004. The software must log this information and any future commands will assume that this device is present. The soft-ware must additionally immediately execute a STOP command to end playback.If an Interrupt did occur, then it is one of the other possible ISD devices. We must then continue with the determination of which device is being used.2.Enter the 2-byte SPI command E3 F0.The “E” sets the RUN, PLAY/REC and PUbits. The address shifted into the devic-es being controlled is 3F0 (hex).A.If the device is an ISD4003, all 11address bits in the command will bedecoded and will be interpreted as03F0 (hex). This is a valid address forthis address and it will begin toplayback at this location.B.If the device is an ISD4002, the first10 bits of the address will bedecoded. The result is address 3F0.This is above the highest addresspossible in an ISD4002, 257 (hex)and the device will immediatelygive an Overflow Interrupt.C.If the device is an ISD33000 (800-rowarray), the first 10 bits of the addresswill be decoded. The result isaddress 3F0. This is above thehighest address possible in anISD33000 (800-row array), 31F (hex)and the device will immediatelygive an Overflow Interrupt.Application Information for ChipCorder ProductsD.If the device is an ISD33000 (400-rowarray), the first 9 bits of the addresswill be decoded. The result isaddress 1F0. This is above thehighest address possible in anISD33000 (400-row array), 18F (hex)and the device will immediatelygive an Overflow Interrupt.At this point, we have already determined that an ISD4004 is not being used in this application. After this second sequence we will have again generated an immediate interrupt, or perhaps not. If an interrupt was generated, then we have not yet determined which chip is being used and we will continue on to the next sequence. If an Overflow Interrupt did not occur, then the de-vice must be an ISD4003. The software must log this information and any future commands will assume that this device is present. Again, the software must execute a STOP command to end playback.3.Enter the SPI command E1 90. The “E”sets the RUN, PLAY/REC and PU bits. Theaddress shifted into the devices beingcontrolled is 190 (hex).A.If the device is an ISD4002, thedevice will begin to playback sincethis is a valid address.B.If the device is an ISD33000 (800-row array), the device will alsobegin playback since this is a validaddress for this device also.C.If the device is an ISD33000 (400-row array), this address is above thehighest address possible in anISD33000 (400-row array), 18F (hex)and the device will immediatelygive an Overflow Interrupt.At this point, we have already determined that the device is not an ISD4004 or ISD4003. If the in-terrupt occurs, then we must be testing an ISD33000 (400-row) device. The software must log this information and any future commands will assume that this device is present. If an inter-rupt did not occur, then software must execute a STOP command to end playback and we must test for the remaining two devices.4.Enter the SPI command E2 58. The “E”sets the RUN, PLAY/REC and PU bits. Theaddress shifted into the devices beingcontrolled is 258 (hex).A.If the device is an ISD4002, thedevice will immediately interruptsince 258 (hex) is just above itshighest address range.B.If the device is an ISD33000 (800-row array), the device will alsobegin playback since this is a validaddress for this device.We have now determined which of the original 5 devices is in use in this product and that informa-tion must be logged. If the ISD33000 (800-row ar-ray) is in use, then once again we must execute a STOP command to end the playback cycle. Figure 41 shows a flow chart of this operation.Application Information for ChipCorder ProductsFigure 39: Flow Chart of Automatic Device DetectionA Winbond Company®Applications Note 7 Message Management in Large Array ISD DevicesISD Application Note Number 2, Message Man-agement in the ISD33000 demonstrated a meth-od of recording, playing back and erasing messages in first generation 3-Volt ISD product.. Only 100 bytes of nonvolatile memory were nec-essary for a reasonable message management scheme. Since each row of memory represented only a maximum of 300 milliseconds, a message block of 8 rows still gave a resolution of 2.4 sec-onds. The 800 total rows could be addressed by 100 bytes of memory.ISD devices have continued to grow in size how-ever. Today’s ISD4004 has 2400 rows of data and each row has a maximum of 400 milliseconds of storage. It requires a 12-bit address to access all the rows of memory in this device. If the same message management scheme and a compa-rable row resolution are used, we are pushed into using 2 bytes of memory per pointer. This technique would now require over 1 Kbytes of nonvolatile memory to accomplish this function. Today’s more sophisticated applications also re-quire more features. For example, many messag-ing systems need multiple mailboxes, messages priorities, etc. Each of these added requirements increases the complexity of the message pointer bytes. This paper will demonstrate another, more memory economical way of achieving these application goals. A comparison of these two approaches will give the software designer in-sight into different methods of message man-agement. The technique described below could be used with any of the ISD33000 or ISD4000 Single-Chip Record/Playback device families. This discussion, however, will focus on the ISD4004-16, which is a member of the ISD4004 series. The ISD4004 gener-ic device has 3,840,000 cells in its Flash cell ana-log memory array. As with all curren t ISD ChipCORDER devices, the resultant record and playback time depends on the speed of the in-ternal sample rate clock. Each analog sample taken is stored away in an analog memory cell. Thus the ISD4004-8 achieves 8 minutes of storage by sampling the array at 8 KHz and the ISD4004-16 achieves 16 minutes by sampling at 4 KHz. See the ISD4004 Series Family data sheet for com-plete information on this device. MESSAGE MANAGEMENT PLANNINGThe ISD4004-16 has 2400 addressable rows, each 400 milliseconds long. This proposed message management method would group a number of rows into a message block to minimize the size of the memory necessary for pointers. Once a mes-sage is recorded into a block or a series of blocks, it cannot be moved to other address lo-cations in the chip. The blocks of memory used may not be contiguous because of previous record and erase operations. Pointers are used to keep track of the beginning address locations of each block of memory in a message. We will call this list of pointers the MAT or Message Ad-dress Table.This type of message management is made pos-sible by the ability of the ISD33000 and ISD4000 series to seamlessly jump from the end of one row to the beginning of any other row in the device’s memory during record or playback. This allows us to find unused memory during the record operation and efficiently reuse it, regardless of its location. The information in the MAT allows us to rebuild and playback the recorded message.Our message management scheme will use two types of data bytes. The first byte in the MAT for any message will be a Tag Byte. . The sign bit, i.e. bit 7 of the Tag Byte will always be a 1. Except for bit 7, this byte may be formatted as required by the needs of the messaging system. The bits in it can be used for any purpose. In our example, we will use the Tag Byte to indicate mailbox number, an unread message and priority of message. Bits 0, 1 and 2 indicate a mail box number, leaving room for 8 different mailboxes. Bit 3 will indicate that the message is new and therefore unread. Bit 4 will be used to indicate a priority message. We will always keep the priority messages ahead of non-priority messages in playback order. Bits 5 and 6 are unused for now but may be used for something else in a “future product.” Figure 1 charts the bit positions of a representative Tag Byte.Figure 1: Example Tag ByteThe Tag Byte above would indicate that our mes-sage is non-priority, has not yet been read, and is in mailbox number 2. Note that it is not necessary to keep track of a “number” for the message in this example. We will derive a number for a mes-sage by keeping them in order. For example, the first message in the MAT in Mailbox 3 will be mes-sage #1 of Mailbox #3. The second message in the MAT in Mailbox 3 will be message #2 of Mailbox #3. If we wish to change the number of a mes-sage in a mailbox, we simply reorder the mailbox entries in the MAT.The second type of byte is the Address Pointer Byte. Bit 7 is always a zero in an Address Pointer Byte. The other 7 bits contain the 7 most signifi-cant bits of the beginning address of the memo-ry block this byte points to.Figure 2:We can determine the minimum possible block size by dividing the total number of addressable rows by the 128 possible combinations in 7 active bits of the Address Pointer Byte. The result of di-viding 2400 by 128 is 18.75 rows. This is of course not an integer number so 19 rows per block is the theoretical minimum. In our example message management scheme we are going to assume a block size of 18 rows or 7.2 seconds. When we multiple 128 x 18 we get 2304. This is the number of rows we can address in the ISD4004. That leaves 94 rows or a total of 37.6 seconds we can use for prompts or other non-message storage. The only difficulty in this approach is the genera-tion of the real address for the ISD4004. This re-quires a multiply by 18 function which may require some effort in a low-end micro. But four 16 bit shifts and one 16 bit add is not a difficult task for most processors. See Figure 2.An example Address Pointer Byte is shown in Figure 3. The seven bit address 010 0010 (34 decimal) is contained in the Pointer Byte. The real address of the first byte of the message block to be address-es is 0010 0110 0100 (612 decimal) after a multiply by 18.Example Binary Multiply by 18The process of multiplying by 18 requires a multiply by 16 of the original number added to a multiply by 2 of the original number. A multiply by 2 is a single left shift operation of the original 12-bit address. A multiply by 16 is 4 bit shift left of the orig-inal number. We can then combine the two opera-tions by performing one shift left, storing off the result, then performing 3 additional shift left operations. Then add the 4 bit shifted result to the 1 bit shifted result.We now have the original number multiplied by 18.Example: 18 x 24 = 432 (= 0001 1011 0000 binary)24 = 0000 0001 1000Shift left 1 = 0000 0011 0000 (mult x 2)Shift left 4 = 0001 1000 0000 (mult x 16) Add together = 0001 1011 0000 (mult x 18)。

CDA-SDI400 3G-SDI 1 by 4 Splitter 产品说明书

CDA-SDI400 3G-SDI 1 by 4 SplitterDISCLAIMERSThe information in this manual has been carefully checked andis believed to be accurate. Comprehensive assumes no responsibility for any infringements of patents or other rights of third parties which may result from its use.Comprehensive assumes no responsibility for any inaccuracies that may be contained in this document. Comprehensive also makes no commitment to update or to keep current the information contained in this document.Comprehensive reserves the right to make improvements to this document and/or product at any time and without notice. COPYRIGHT NOTICENo part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or any of its part translated into any language or computer file, in any form or by any means— electronic, mechanical, magnetic, optical, chemical, manual, or otherwise—without express written permission and consent from Comprehensive.© Copyright 2011 by Comprehensive. AllRights Reserved.Version 1.1 August 2011TRADEMARK ACKNOWLEDGMENTSAll products or service names mentioned in this document may be trademarks of the companies with which they are associated.SAFETY PRECAUTIONSPlease read all instructions before attempting to unpack, install or operate this equipment and before connecting the power supply. Please keep the following in mind as you unpack and install this equipment:•Always follow basic safety precautions to reduce the risk of fire, electrical shock and injury to persons.•To prevent fire or shock hazard, do not expose the unit to rain, moisture or install this product near water.•Never spill liquid of any kind on or into this product.•Never push an object of any kind into this product through any openings or empty slots in the unit, as you may damage partsinside the unit.•Do not attach the power supply cabling to building surfaces.•Use only the supplied power supply unit (PSU). Do not use the PSU if it is damaged.•Do not allow anything to rest on the power cabling or allow any weight to be placed upon it or any person walk on it.•To protect the unit from overheating, do not block any vents or openings in the unit housing that provide ventilation and allow for sufficient space for air to circulate around the unit. REVISION HISTORYDATE DD/MM/YYVR008/04/11Preliminary ReleaseVS111/07/12Updated format/diagrams/SDIstandardsVS213/07/12First releaseVR309/08/12Type ErrorCONTENTS1.Introduction (1)2.Applications (1)3.Package Contents (1)4.System Requirements (1)5.Features (1)6.Operation Controls and Functions .. 26.1Front Panel (2)6.2Rear Panel (2)7.Connection Diagram (3)8. Specifications (4)9. Acronyms (5)1.INTRODUCTIONThe 3G-SDI 1 by 4 Splitter allows SD-SDI, HD-SDI and 3G-SDI signals to be split from a single SDI source to up four simultaneous SDI outputs while ensuring high bit rates of 2.970 Gbit/s to give you high bandwidth signal transmission without signal loss over long distances.2.APPLICATIONS•Video broadcasting display•Professional video program display•Film studios program monitoring•Video program switching display3.PACKAGE CONTENTS•3G-SDI 1 by 4 Splitter•5 V/2.6 A DC Power Adaptor•Operation Manual4.SYSTEM REQUIREMENTSSDI source input (such as broadcast video cameras or recording device) a nd S DI o utput d isplays (such a s T Vs o r m onitors)5.FEATURES•Split one 3G-SDI input source to four 3G-SDI displays simultaneously • Operation at 2.970Gb/s, 2.970/1.001Gb/s, 1.485Gb/s, 1.485/1.001Gb/s and 270Mb/s•Supports SMPTE 425M (Level A and Level B), SMPTE 424M, SMPTE 292M, SMPTE 259M-C•Provides e qualized a nd r e-clocked t ransmission•Supports signal input and output distances of up to 300 m for SD signals, 200 m for HD signals and 100 m for 3G signals.Note: Tested with Belden 1694A Cable. Operating distances may vary if used with cables of different specifications.16. OPERATION CONTROLS AND FUNCTIONS6.1 Front PanelPower LEDThe LED will illuminate green when the device is connected to a power supply.SDI OUTPUTConnect to up to four SDI TVs or monitors for simultaneous display or to another splitter to cascade the SDI signal to multiple displays or devices.6.2 Rear PanelSDI INPUT Connect to the SDI output of the SDI source device such as a video camcorder or SDI player.Accepts SD,HD or3G SDI signals.DC 5VPlug the 5 V DC power supply into the unit and connect the adaptor to an AC outlet. The 'POWER' LED will illuminate green when the power is ON.21127.CONNECTION DIAGRAMSDI CameraPower SupplySDI toHDMIConverterHDMIOutputCascade to another 4 SDI Displays38.SPECIFICATIONSSMPTE Standard425M Level A & B, 424M, 292M, 259M-C2.970 Gbit/s and 2.970/1.001 G bit/sSDI TransmissionRatesInput1×BNC (SD/HD/3G-SDI)Output4×BNC (SD/HD/3G-SDI)SDI Timing Support SD-SDI:SMPTE 259M-C, 270 Mbit/sHD-SDI:SMPTE 292M, 1.485 & 1.485/1.001 Gbit/s3G-SDI:SMPTE 424M/425M-AB, 2.970 &2.970/1.001 Gbit/sPower Supply 5 V DC/ 2.6 A (US/EU standards, CE/FCC/ULcertified)ESD Protection Human body m odel:±8 kV (air-gap discharge)±4 k V (contact discharge)SDI Cable Distance3G-SDI up to 100 m(BELDEN 1694A)HD-SDI up to 200 m(BELDEN 1694A)SD-SDI up to 300 m (BELDEN 1694A) Dimensions200 m m (W)×138 m m(D) x30 m m (H)Weight900 gChassis Material MetalSilkscreen Color Black0 ˚C~40˚C/32˚F~104˚FOperatingTemperature−20 ˚C~60˚C/−4˚F~140˚FStorageTemperatureRelative Humidity20~90 % RH (Non-condensing)Power Consumption 5 W49. ACRONYMS3G Bandwidth 2.97Gbps ≈3GHDMI High Definition Multimedia Interface SDI S e r i a l D i g i t a l I n t e r f a c e5Comprehensive Connectivity The Pro’s Connectivity Since 1974 80 Little Falls Rd, Fairfield NJ 07004Phone: 1-800-526-0242*************************。

SCD4003资料

FIG.5 - TYPICAL JUNCTION CAPACITANCE

TJ = 25 C

o

100 60 40

20 10 6 4 2 1 .1 .2 .4 1.0 2 4 10

20

40

100

REVERSE VOLTAGE, VOLTS

01-Jun-2002 Rev. A

元器件交易网

SCD4003 THRU SCD4007

Elektronische Bauelemente

VOLTAGE 200V ~ 1000V 1.0 AMP Glass Passivated Rectifier

A suffix of "-C" specifies halogen & lead-free

at Rated DC Blocking Voltage Ta=100℃ Typical thermal resistance (NOTE 2) Typical Junction Capacitance (Note1) Operating Temperature Range Storage Temperature Range NOTES: 1. Measured at 1.0MHz and applied reverse voltage of 4.0 Volts. 2. Mounted on P.C. board with 0.2 x 0.2"(5.0 x5.0mm) copper pad areas. 3. Marking: SCD4003 SCD4004 SCD4005 SCD4006 SCD4007 : : : : : 17ZD 17ZG 17ZJ 17ZK 17ZM

TYPE NUMBER Maximum Recurrent Peak Reverse Voltage Working Peak Reverse Voltage Maximum DC Blocking Voltage Maximum Average Forward Rectified Current Peak Forward Surge Current, 8.3ms single half sine-wave superimposed on rated load (JEDEC method) Maximum Instantaneous Forward Voltage at 1.0A Maximum DC Reverse Current (Note1) Ta=25℃

企业培训-S734控制基础培训课件117页 精品

STEP 7编程软件介绍

2、SIMATIC管理器 SIMATIC管理器管理一个自动化项目中的所有数据 (如图所示),无论其设计用于何种类型的可编程控制 系统(S7/M7/C7),编辑数据所需的工具均可由 SIMATIC管理器自动启动。

STEP 7编程软件介绍

3、符号编辑器 如图,通过符号编辑器,可以管理所有共享符号。符号属性的任何变化都可被 所有工具自动识别。

STEP 7编程软件介绍

• 此外,在硬件配置工具中可将参数分配给功能模块(FM) 和通讯处理器(CP),其分配方式与其它模块完全相同。每 个FM和CP (包含在FM/CP功能包中)都有与模块有关的 对话框和规则。系统在对话框中只提供有效选项,以防止 错误输入。

7、NetPro (网络配置)

STEP 7编程软件介绍

S7-300 PLC系统可以选择各种不同性能分级的CPU作控制器使用。通过高

效处理速率,CPU能提供比小型PLC快得多的扫描时间来执行相同的程序。根据用

户的任务要求和项目特点,S7-300的CPU还可以具有带集成式I/O、集成技术功

能和集成通讯接口。

大中型PLC模块化控制系统

大中型PLC模块化控制系统

功能块图(FBD)是STEP 7编程语言的图形表示,使用布 尔代数惯用的逻辑框表示逻辑功能。复杂功能可直接结合 逻辑框表示。功能块图使用不同的功能“盒”,盒中的符 号表示功能 。

STEP 7编程软件介绍 a) LAD编程

b) STL编程

c) FBD编程

图为STEP 7编程 语言的三种类型。

STEP 7编程软件介绍

状态及故障显示

大中型PLC模块化控制系统

4、扩展单元 如果控制系统所需的模块数大于8块时,S7-300 PLC的中央控制器可以通过

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

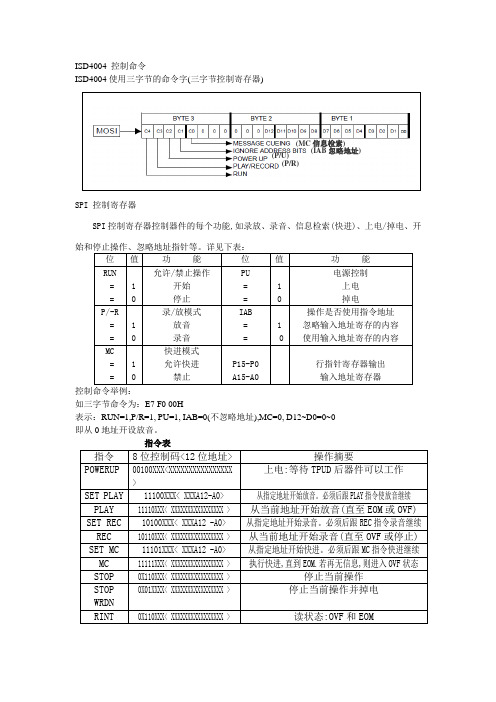

ISD4003 系列语音录放集成电路应用说明一、 简述单片4至8分钟语音录放,4、5、6及8分钟3V单电源工作工作电流25~30mA,继持电流1uA高质量、自然的语音还原技术自动静噪功能无需开发系统内置微控制器串行通信接口多段信息处理不耗电保存信息100年(典型值)100000次录放音周期(典型值)片内免调整时钟,可选用外部时钟ISD4003系列型号与性能对照表型号录放时间输入采样典型带宽最大段数最小段长外部时钟ISD4003-04M 4分钟8.0KHz 3.4KHz 1200 200ms 1024KHz ISD4003-05M 5分钟 6.4KHz 2.7KHz 1200 250ms 819.2KHz ISD4003-06M 6分钟 5.3KHz 2.3KHz 1200 300ms 682.7KHz ISD4003-08M 8分钟 4.0KHz 1.7KHz 1200 400ms 512KHzISD4003系列内部框图如下Figure:ISD4003 Series Block DiagramISD4003系列TSOP及PDIP、SOIC引脚图如下:Figure 1: ISD4003 Series TSOP and PDIP/SOIC Pin outsISD4003系列工作电压3V,单片录放语音时间4至8分钟,音质好、适应于移动电话机及其它便携式电子产品中。

芯片采用CMOS技术,内含振荡器、防混清滤波器、平滑滤波器、自动静噪、音频放大器及高密度多电平闪烁存贮陈列。

芯片高级计是基于所有操作必须由微控制器控制,操作命令通过串行通信接口(SPI或Micro wire)送入。

芯片采用多电平直接模拟量存贮技术,每个采样值直接存贮在片内的闪烁存贮器中,因此能够非常真实、自然地再现语音,音乐、音调和效果声,避免了一般固体录音电路固置化和压缩造成的量化噪声和金属声。

采样频率可为4.0,5.3,6.4,8.0KHz,频率越低,录放时间越长,而音质则有所下降,片内信息存于闪烁存贮器中,可在断电情况下保存100年(典型值),反复录音10万次。

二、 引脚描述电源(VCCA,VCCD)为使噪声最小,芯片的模拟和数字电路使用不同的电源总线,并分别引到外封装的不同管脚上,模拟和数字电源端最好分别走线,尽可能靠近供电电源处相连,而去耦电容应尽量靠近器件。

地线(VSSA,VSSD)芯片内的模拟和数字电中也使用不同的地线。

几个VSSA尽量在引脚焊盘上相连,并用低阻通路连至电源上,VSSD也用低阻通路边到电源上。

这些接地通路在足以使VSSA与VSSD之间的阴值小于3Ω。

芯片的背面是通过衬底电阻碍连接妻VSS的,在做COB时托盘须接VSS或悬空。

同相模拟输入(ANAIN+)这是录音信号的同相输入端。

输入放大器可用单元端或差分驱动。

单端输入时,信号由耦合电容输入,最大幅度为峰峰值32mV,耦合电容和本端的3KΩ电阻输入阻挠决定了芯片频率的低端截止频率。

在差分驱动时,信号最大幅度为峰峰值16mV。

这两种戏动方式见下图。

反相模拟输入(ANAIN-)差分驱动进,这是录音信号的反相输入端。

信号通过耦合电容输入,最大幅度为峰峰值16mA,本端的标知名人士输入阻挠为56KΩ,单端驱动时本端通进电容接地。

两种方式下,ANAIN+和ANAIN-端的耦合电容值应相同。

音频输出(AUDOUT)提供音频输出,可驱动5KΩ的负载。

片选(SS)此端为低,即选中ISD4003系列。

串行输入(MISO)此为串行输入端,主控制器应在串行时钟上升之前半个周期将数据放到本端,供TER输入。

串行输出(MISO)TER的串行输出端。

TER末选中时,本端呈高阻态。

串行时钟(SELK)TER的时钟输入端,由主控制器产生,用于同步MOSI和MISO的数据传输。

数据在SCLK上升沿锁存到TER,在下降沿移出TER。

中断(INI)本端为漏极开路输出,TER在任何操作(包括快进)中检测到EOM或OVF时,本端变低并保持,中断状态在下一个SPI周期开始时清除,中断状态也可用RINT指令读取。

OVF标志指示TER录放操作已到棕存贮器的末尾。

EOM标志只在放音中检测到内部的EOM标志时,此状态位置1行地址时钟(RAC)漏极开始输出。

每个RAC周期表示TER存储器的操作进行了一行,240B 存贮器的操作进行了一行(ISD4003系列中的存贮器其1200行)。

该信号175ms保持高电平,低电平为25ms。

快进模式下RAC218.75us是高电平,31.25us为低电平。

该端可用于存贮管理体制技术。

外部时钟(XCLK)本端有内部下拉元件。

芯片内部的采样时钟在出厂前已调节器校,误差在+1%内。

商业级芯片在整个温度各电压范围内,频率变化在+2.25%内。

工业级芯片在整个温度和电压范围内,频率变化为-6%+4%,此时建议使用稳压电源。

若要求更高精度或系统同步,可从本端输入外部时钟(如前表中所列)。

由于内澡的防混淆及平滑滤波器已设定,故上述推荐的时钟频率不应改变。

输入时钟的占空比无关紧要,因内部首先进行了分频,在不外接时钟时,此端必须接地。

自动静噪(AMACP)当录音信号电平下降到内部设定的某一阈值以下时,自动静噪功能使信号衰弱,这样有助于减少无信号(静音)时的噪声。

通常本端对地接1MF电容,构成内部信号电平平峰值检测是路的一部分。

检测出的峰值电平为内部设定的阈值作比较,决定自动静噪功能的翻转点,大信号时,自动静噪电路不衰减,静音是衰减6dB。

1uF电容也影响自动静噪电路时信号幅度的响应速度。

本端接VCCA则禁止自动静噪。

三、SPI(串行外部接口)ISD4003工作于SPI串行接口。

SPI协议是一个同步串行数据传输协议,协议假定微控制器的SPI移位寄存器在SCLK的下降沿动作,因此对ISD4003而言,在时钟上升沿锁存MOSI引脚数据,在下降沿将数据送至MISO引脚。

协议具体内容如下:1、所有串行数据传输开始于SS下降沿。

2、 SS在传输期间必须保持为低电平,在两条指令之间则保持为高电平。

3、数据在时钟上升沿移入,在下降沿移出。

4、 SS变低,输入指令和地址后,240B才能开始录放操作。

5、指令格式是5位控制码加11位地址码。

6、 TER任何操作(含快进)如果遇到EOM或OVF,则产生一个中断,该中断状态在一下个SPI周期开始时被清除。

7、使用“误”指令会使中断状态位移出TER的MISO引脚时,控制及地址数据也同步从MOSI端移入。

因此,要注意移入的数据是否与器件当前进行的操作兼容,当然,也允许在SPI周期里,同是执行读状态和开始新的操作(即新移入的数据与器件操作可以不兼容。

)8、所有操作在运行位(RUN)置1时开始,置0时结束。

9、所有指令都在SS端上升沿开始执行。

(1) 信息快进用户不必知道信息的确切地址,就能快进跳过一条信息。

信息快进只用于放音模式。

放音速度是正常的1600倍,遇到EOM后停止,然后内部地址计数器加1,接向下条信息的开始处。

(2) 上电顺序器件延时TPUD(8KHZ)采样查,约为25毫秒)后长能开始操作。

因此,用户发完上电指令后,必须等待TPUD,才能发出一条操作指令。

例如,从00外放音,应遵循如下时序:1、发power up命令;2、等待TPUD(上电延时);3、发地址值为00的SETPLAY命令;4、发PLAY命令。

器件会从00地址开始放音,当出现EOM时,立即中断,停止放音。

如果从00处录音,则按下时序:1发power up 命令;2、等待TPUD(上电延时);3、发power up命令;4、等待2倍TPUD;5、发地址值为00的SETREC命令;6、发REC命令。

器件便从00地址开始录音,一直到出现OVF(存贮器末尾)时,录音停止。

指令表指令5位控制码,11位地址码操作摘要POWERUP 00100(xxxxxxxxxxx)上电:等待TPUD后器件可以工作SET PLAY 11100(A10~A0)从指令地址开始放音,须后跟PLAY指令,使放音继续PLAY 11110(xxxxxxxxxxx)从当前地址开始放音(直至EOM或OVF)SET REC 10110(A10~A0)从指定地址开始录音,须后跟REC指令,使录音继续REC 110110(xxxxxxxxxxx)从当前地址开始录音(直至OVF或停止)SET MC 11101(A10~A0)从指定地址开始快进,须后跟MC指令,使快进继续MC 11111(xxxxxxxxxxx ) 执行快进,直到EOM ,若再无信息,则进入OVF状态STOP 0x110(xxxxxxxxxxx ) 停止当前操作 STOP PWRDN0X01X (xxxxxxxxxxx )停止当前的操作并掉电 RINT 0X110(xxxxxxxxxxxx )读状态;OVF 和EOM注:1、快进只能在放音操作开始选择(3) SPI 端口的控制位(4) SPI 控制寄存器SPI 控制寄存器控制器件的每处功能,如录放、录音、信息检索(快进)、上电/掉电、开始、停止操作、忽略地址指针等。

详见下表 位 值 功能位 值 功能 RUN= = 1 0 允许/禁止操作开始 停止 PU = = 1 0 电源控制 上电 掉电P/-R = = 1 0 录/放方式 放音 录音 IAB = =1 0操作是否使用指令地址 忽略输入地址寄存器的内容 使用输入地址寄存器的内容 P9~P0 行指针寄存器 MC = =1 0快进模式 允许快进 禁止快进A0~A10输入地址寄存器注:IAB 置0时,录、放操作从A9A0地址开始。

为了能连贯地录、放到后续的存储空间,在操作到达该行之前,应发出第二个SPI 指令将IAB 置1;原则器件在同一地址上反复循环。

这个特点对语音提示功能很有用,RAC 脚和IAB 位可用于信息管理。