Spartan3E-StarterBoard

EDK实验教程中文翻译lab6mb

实验6 – HW/SW 系统调试Targeting MicroBlaze™ on the Spartan-3E Starter KitHW/SW系统调试实验: MicroBlaze实验说明本实验将引导你完成处理器系统的调试。

将用到 XPS和 ChipScope实现系统软硬件的可视化。

实验目的通过实验,你将学会以下知识:∙想系统中添加 ChipScope分析器∙使用 Chipscope 分析器和SDK 调试器联合调试实验过程图1. MicroBlaze 系统打开工程步骤 1总体实验流程图:在 c :\xup\embedded\microblaze\labs\.路径下创建 lab6文件夹。

如果想继续前面的设计,你可以从lab5文件夹中复制其中的内容到lab6文件夹。

启动 Xilinx Platform Studio (XPS),打开工程,路径为c:\xup\embedded\microblaze\labs\lab6.❶在 c:\xup\embedded\microblaze\labs 路径下创建lab6 文件夹。

如果想继续实验5的设计,可以复制 lab5 中的内容到 lab6 。

❷ 点击 Start → Programs → Xilinx Platform Studio 8.2i → Xilinx Platform Studio ,打开XPS❸ 选择 Open Recent Project ,点击 OK ,浏览到C:\xup\embedded\microblaze\labs\lab6❹ 点击 system.xmp 打开工程。

ChipScope 核实例化步骤 2从IP 目录中添加 ChipScope 核到设计中,配置芯片和设计到下列端口,如图 6-2所示。

当OPB 地址,数据,控制总线上为一定的值时触发触发器。

Step 2: Instantiate Chipscope CoresStep 3: SDK and ChipscopeOperationStep 4: HW/SW DebugStep 1: Opening the ProjectStep 3:SDK and Chipscope OperationStep 4: HW/SW Debug图 6-2. ChipScope 核的连接❶从IP目录中的调试部分添加chipscope_icon 和 chipscope_opb_iba外设,并连接chipscope_opb_iba到OPB总线。

Power Circuit and Motor-mounted Apparatus Certifie

Power Circuit and Motor-mounted Apparatus Certified for CanadaAccessories, "Inrush Limiter SITOP Series", Model(s) 6EP1967-2AA00 Accessories , Model(s) 6EP4134-3AB00-0AY0, 6EP4134-3AB00-1AY0, 6EP4134-3AB00-2AY0, 6EP4136-3AB00-0AY0, 6EP4136-3AB00-1AY0, 6EP4136-3AB00-2AY0, 6EP4137-3AB00-0AY0, 6EP4137-3AB00-1AY0, 6EP4137-3AB00-2AY0Industrial control equipment, miscellaneous apparatus , Model(s) 6EP1333-1AL12, 6EP1333-3BA00, 6EP1333-3BA00-8AC0, 6EP1334-1AL12, 6EP1334-3BA00, 6EP1334-3BA00-8AB0, 6EP1336-2BA10, 6EP1336-3BA00, 6EP1336-3BA00-8AA0, 6EP1336-3BA10, 6EP1337-3BA00, 6EP1424-3BA00, 6EP1433-0AA00, 6EP1434-2BA10, 6EP1436-2BA10, 6EP1436-3BA00, 6EP1436-3BA00-8AA0, 6EP1436-3BA01, 6EP1436-3BA10, 6EP1437-2BA20, 6EP1437-3BA00, 6EP1437-3BA00-0AA0, 6EP1437-3BA00-8AA0, 6EP1437-3BA10, 6EP1437-3BA20, 6EP1456-2BA00, 6EP1456-3BA00, 6EP1457-3BA00, 6EP1457-3BA00-0AA0, 6EP1961-3BA01, 6EP1962-2BA00, 6EP1964-2BA00Industrial control equipment, miscellaneous apparatus, current monitors , Model(s) 6EP1961-2BA00Industrial control equipment, miscellaneous apparatus, hold-up modules , Model(s) 6EP1961-3BA00Industrial control equipment, miscellaneous apparatus, redundance modules , Model(s) 6EP1961-3BA20, 6EP1961-3BA21Industrial control equipment, miscellaneous apparatus, signaling modules , Model(s) 6EP1961-3BA10Miscellaneous apparatus, power supplies, open type , Model(s) 6EP1311-1SH02, 6EP1311-1SH03, 6EP1311-1SH12, 6EP1311-1SH13, 6EP1321-1SH02, 6EP1321-1SH03, 6EP1321-5BA00, 6EP1322-1SH02, 6EP1322-1SH03, 6EP1322-5BA10, 6EP1331-1SH02, 6EP1331-1SH03, 6EP1331-5BA00, 6EP1331-5BA10, 6EP1332-1SH04, 6EP1332-1SH42, 6EP1332-1SH43, 6EP1332-1SH51, 6EP1332-1SH52, 6EP1332-1SH61, 6EP1332-1SH71, 6EP1332-5BA00, 6EP1332-5BA10, 6EP1332-5BA20, 6EP1351-1SH02, 6EP1351-1SH03, 6EP1352-1SH02, 6EP1352-1SH03, 6EP1536-3AA00Miscellaneous apparatus, Power Supply Accessories, open type , Model(s) 6EP1931-2DC21, 6EP1931-2DC31, 6EP1931-2DC42, 6EP1931-2EC01, 6EP1931-2EC11, 6EP1931-2EC21, 6EP1931-2EC31, 6EP1931-2EC42, 6EP1931-2FC21, 6EP1931-2FC42, 6EP1933-2EC41, 6EP1933-2EC51, 6EP1935-5PG01Power supplies , Model(s) 6EP1321-1LD00, 6EP1332-1LD00Power supplies, open type, "AS-Interface Series", Model(s) 3RX9501-0BA00, 3RX9501-1BA00, 3RX9501-2BA00, 3RX9502-0BA00, 3RX9503-0BA00, 3RX9511-00AA00, 3RX9512-00AA00, 3RX9513-00AA00Power supplies, open type, "SITOP Series", Model(s) 6EP1322-2BA00, 6EP1322-2BA10, 6EP1323-2BA00, 6EP1332-2BA20, 6EP1333-2AA01, 6EP1333-2AA01-0AA0, 6EP1333-2BA01, 6EP1333-2BA20, 6EP1334-2AA01, 6EP1334-2AA01-0AA0, 6EP1334-2AA01-0AB0, 6EP1334-2AA01-0AC0, 6EP1334-2BA01, 6EP1334-2BA20, 6EP1332-1LB00, 6EP1333-1LB00, 6EP1334-1LB00Switch mode power supplies, open type, "SITOP EVS", Model(s) (SITOP EVP 100)6EP1232-1AA10, (SITOP EVP 150)6EP1233-1AA00, (SITOP EVP 300)6EP1234-1AA00, (SITOP EVP 60)6EP1232-1AA00Switch mode power supplies, open type, "SIYOUNG Power", Model(s) (SIYOUNG Power 100)6EP0123-2AAO-0AB0, (SIYOUNG Power 150)6EP0123-3AAO-0AB0, (SIYOUNG Power 300)6EP0123-4AAO-0AB0, (SIYOUNG Power 60)6EP0123-2AAO-0AA0Switching Power Supplies , Model(s) 6EP1322-1LD00, 6EP1331-1LD00, 6EP1332-1LD10, 6EP1333-1LD00, 6EP1334-1LD00NMTR7.E197259Power Circuit and Motor-mounted Apparatus Certified for CanadaPage BottomSee General Information for Power Circuit and Motor-mounted Apparatus Certified for CanadaSIEMENS AGE197259OESTERREICHSIMEAPOSTFACH 83, SIEMENSSTRASSE 901211 VIENNA, AUSTRIALast Updated on 2013-05-20Questions? Print this page Terms of Use Page Top© 2013 UL LLCWhen the UL Leaf Mark is on the product, or when the word "Environment" is included in the UL Mark, please search the UL Environment database for additional information regarding this product's certification.The appearance of a company's name or product in this database does not in itself assure that products so identified have been manufactured under UL's Follow-Up Service. Only those products bearing the UL Mark should be considered to be Certified and covered under UL's Follow-Up Service. Always look for the Mark on the product.UL permits the reproduction of the material contained in the Online Certification Directory subject to the following conditions: 1. The Guide Information, Assemblies, Constructions, Designs, Systems, and/or Certifications (files) must be presented in their entirety and in a non-misleading manner, without any manipulation of the data (or drawings). 2. The statement "Reprinted from the Online Certifications Directory with permission from UL" must appear adjacent to the extracted material. In addition, the reprinted material must include a copyright notice in the following format: "© 2013 UL LLC".。

Spartan 3E用户指南

Spartan-3E Starter Kit Board User GuideChapter 1: Introduction and OverviewChapter 2: Switches, Buttons, and KnobChapter 3: Clock SourcesChapter 4: FPGA Configuration OptionsChapter 5: Character LCD ScreenChapter 6: VGA Display PortChapter 7: RS-232 Serial PortsChapter 8: PS/2 Mouse/Keyboard PortChapter 9: Digital to Analog Converter (DAC)Chapter 10: Analog Capture CircuitChapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial FlashChapter 13: DDR SDRAMChapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion ConnectorsChapter 16: XC2C64A CoolRunner-II CPLDChapter 17: DS2432 1-Wire SHA-1 EEPROMChapter 1:Introduction and Overview Spartan-3E入门实验板使设计人员能够即时利用Spartan-3E系列的完整平台性能。

设备支持:Spartan-3E、CoolRunner-II关键特性:Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner™-II (XC2C64A-5VQ44C)与Platform Flash(XCF04S-VO20C)时钟:50 MHz晶体时钟振荡器存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM连接器与接口:以太网10/100 Phy, JTAG USB下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED输出, 四个瞬时接触按钮, 100管脚hirose扩展连接端口与三个6管脚扩展连接器显示器: VGA显示端口,16 字符- 2 线式LCD电源:Linear Technologies 电源供电,TPS75003三路电源管理IC市场:消费类, 电信/数据通信, 服务器, 存储器应用:可支持32位的RISC处理器,可以采用Xilinx的MicroBlaze 以及PicoBlaze嵌入式开发系统;支持DDR接口的应用;支持基于Ethernet网络的应用;支持大容量I/O扩展的应用。

迪尔Split System热水器3相4TWA7036A3000A4TWA7048A3000A4TW

May 201622-1925-1A-ENSplit System Heat Pump 3–Phase4TWA7036A3000A 4TWA7048A3000A 4TWA7060A3000A 4TWA7036A4000A 4TWA7048A4000A4TWA7060A4000AN o t e :“Graphics in this document are for representationonly.Actual model may differ in appearance.”T able of ContentsProduct Specifications (3)Sound Power Level (5)Accessory Description and Usage (6)Model Nomenclature (6)SCHEMATIC (7)Outline Drawing (9)Mechanical Specification Options (10)Product Specifications(a)Certified in accordance with the Air-Source Unitary Air-conditioner Equipment certification program,which is based on AHRI standard210/240.(b)Rated in accordance with AHRI standard270.(c)Calculated in accordance with N.E.C.Only use HACR circuit breakers or fuses.(d)This value shown for compressor RLA on the unit nameplate and on this specification sheet is used to compute minimum branch circuit ampacity and max.fuse size.The value shown is the branch circuit selection current.(e)This value approximate.For more precise value see unit nameplate.(f)Reference the outdoor unit ship-with literature for refrigerant piping length and lift guidelines.Reference the refrigerant piping software pub#32-3312-xx or refrigerant piping application guide SS-APG006-xx for long line sets or specialty applications(xx denotes latest revision).(g)Trane outdoor condensing units are factory charged with the system charge required for the outdoor condensing unit and15feet of tested connectinglines.If connecting line length exceeds15feet,then final refrigerant charge adjustment is necessary.Each additional foot over15feet requires0.6ozs of refrigerant.See the Installer’s Guide for full charging instructions.(h)This value approximate.For more precise value see unit nameplate.(i)*=15,20,25,30,40and50foot lineset available.P r o d u c t S p e c i f i c a t i o n s(a)Certified in accordance with the Air-Source Unitary Air-conditioner Equipment certification program,which is based on AHRI standard210/240.(b)Rated in accordance with AHRI standard270.(c)Calculated in accordance with N.E.C.Only use HACR circuit breakers or fuses.(d)This value shown for compressor RLA on the unit nameplate and on this specification sheet is used to compute minimum branch circuit ampacity and max.fuse size.The value shown is the branch circuit selection current.(e)This value approximate.For more precise value see unit nameplate.(f)Reference the outdoor unit ship-with literature for refrigerant piping length and lift guidelines.Reference the refrigerant piping software pub#32-3312-xx or refrigerant piping application guide SS-APG006-xx for long line sets or specialty applications(xx denotes latest revision).(g)Trane outdoor condensing units are factory charged with the system charge required for the outdoor condensing unit and15feet of tested connectinglines.If connecting line length exceeds15feet,then final refrigerant charge adjustment is necessary.Each additional foot over15feet requires0.6ozs of refrigerant.See the Installer’s Guide for full charging instructions.(h)This value approximate.For more precise value see unit nameplate.(i)*=15,20,25,30,40and50foot lineset available.Sound Power LevelAccessory Description and UsageA n t i-S h o r t C y c l e T i m e r—Solid state timing device that prevents compressor recycling untilfive(5)minutes have elapsed after satisfying call or power e in area withquestionable power delivery,commercial applications,long lineset,etc.E v a p o r a t i o n D e f r o s t C o n t r o l—SPST Temperature actuated switch that cycles the condenseroff as indoor coil reaches freeze-up ed for low ambient cooling to30°F with TXV.R u b b e r I s o l a t o r s—Five(5)large rubber donuts to isolate condensing unit from transmittingenergy into mounting frame or e on any application where sound transmission needs tobe minimized.H a r d S t a r t K i t—Start capacitor and relay to assist compressor motor e in areas withmarginal power supply,on long linesets,low ambient conditions,etc.E x t r e m e C o n d i t i o n M o u n t K i t—Bracket kits to securely mount condensing unit to a frame orpad without removing any e in areas with high winds,or on commercial roof tops,etc.A H R I S t a n d a r d C a p a c i t y R a t i n g C o n d i t i o n sAHRI Standard210/240Rating Conditions1.Cooling80°F DB,67°F WB air entering indoor coil,95°F DB air entering outdoor coil.2.High Temperature Heating47°F DB,43°F WB air entering outdoor coil,70°F DB air enteringindoor coil.3.Low Temperature Heating17°F DB air entering indoor coil.4.Rated indoor airflow for heating is the same as for cooling.A H R I S t a n d a r d270R a t i n g C o n d i t i o n s—(Noise rating numbers are determiend with the unit incooling operations.)Standard Noise Rating number is at95°F outdoor air.Model NomenclatureSCHEMATIC230V HP—D159297P02460V HP —D159194P02S C H E M A T I COutline DrawingMechanical Specification OptionsG e n e r a lThe Outdoor Units are fully charged from the factory for up to15feet of piping.This unit isdesigned to operate at outdoor ambient temperatures as high as115°F.Cooling capacities arematched with a wide selection of air handlers and furnace coils that are AHRI certified.The unit iscertified to UL1995.Exterior is designed for outdoor application.C a s i n gUnit casing is constructed of heavy gauge,galvanized steel and painted with a weather-resistantpowder paint finish on all louvered panels and the fan top panel.The corner panels areprepainted.All panels are subjected to our1,000hour salt spray test.The base is made of aCMBP-G30weatherproof material to resist corrosion.R e f r i g e r a n t C o n t r o l sRefrigeration system controls include condenser fan,compressor contactor and high pressureswitch.High and low pressure controls are inherent to the compressor.A factory supplied liquidline drier is standard.Some models may require field installation.C o m p r e s s o rThe compressor features internal over temperature,pressure protection and total dippedhermetic motor.Other features include:Centrifugal oil pump and low vibration and noise.C o n d e n s e r C o i lThe outdoor coil provides low airflow resistance and efficient heat transfer.The coil is protectedon all four sides by louvered panels.L o w A m b i e n t C o o l i n gAs manufactured,this system has a cooling capacity to55°F.The addition of an evaporatordefrost control permits operation to40°F.The addition of an evaporator defrost control with TXVpermits low ambient cooling to30°F.T h e r m o s t a t s—Cooling only and heat/cooling(manual and automatic change over).Sub-base tomatch thermostat and locking thermostat cover.E v a p o r a t o r D e f r o s t C o n t r o l—See Low Ambient Cooling.N o t e s 22-1925-1A-EN11Trane optimizes the performance of homes and buildings around the world.A business of Ingersoll Rand,the leader in creating and sustaining safe,comfortable and energy efficient environments,Trane offers a broad portfolio of advanced controls and HVAC systems,comprehensive building services,and parts.For more information,visit .Trane has a policy of continuous product and product data improvements and reserves the right to change design and specifications without notice.©2016Trane22-1925-1A-EN17May2016Supersedes(New)。

LabVIEW FPGA SPARTAN3E Starter Kit 实验指南说明书

Lab 1:Implementing a Boolean function in LabVIEW FPGA on the Xilinx SPARTAN-3E BoardKeywords: LabVIEW, LabVIEW FPGA, Xilinx SPARTAN3E Starter Kit, Implementing a Boolean Function.IntroductionWelcome to Lab1 in the serie of programming a SPARTAN3E Starter Kit by use of LabVIEW FPGA. These labs are created by Vincent Claes. If you encounter problems using this labs or want some advice/consultancy on LabVIEW and especially LabVIEW FPGA you can always contact the author.These labs are free to use however to show respect to the author please email him when you use them with your contact details (feedback is also welcome).Contact Information:Vincent Claes**********************/in/vincentclaesSoftware Requirements:•LabVIEW 8.5 or above•LabVIEW 8.5 FPGA module•XUP Spartan3E starter board: download for free from: https:///nicif/us/infolvfpgaxilsprtn/content.xhtmlHardware Requirements:•Xilinx Spartan3E Starter kit:/products/devkits/HW-SPAR3E-SK-US-G.htm•User manual:/support/documentation/boards_and_kits/ug230.pdfGetting StartedWhen you want to use this labs you have to setup your board. This labs are written for the Xilinx SPARTAN3E Starter Kit soit is quite interesting to read the user manual of the board. Be sure to plug in the USB cable, plug in the Power cord and Switch the board on before starting the lab.Step 1: Starting LabVIEWThe first step is to start the National Instruments LabVIEW 8.5 environment.Step 2: Create a LabVIEWprojectAfter we have started the LabVIEW environment we get the following screen:We have to create an Empty Project where we will add the Xilinx Spartan3E starter board on as a hardware target. In a future lab I will explain how we can create a HOST vi (this is a LabVIEW application that runs on a desktop PC) that communicates with a LabVIEW FPGA vi.Step 3: Add the Spartan3E board as a hardware targetThe next screen shows the Project Explorer view of the Empty Project that we just created.Now we have to add the Spartan3E starter board as a Hardware target. For this we do a “right click” on “My Computer” in the Project Explorer view. We select “New” and then “Targets and Devices”.In the screen that now appears we have to select the XUP starter board. Select “New target or device”.A list of “Targets and Devices” will be shown. You have to scroll down till the end and select “Spartan-3E Starter board” from the “Xilinx university Program” map.This will add the FPGA Target to the Project Explorer view. You see this target is placed under “My Computer”.Step 4: Adding FPGA I/OThe next step we make is adding “FPGA I/O’s” that we will use in this project to the Project Explorer view. For this you have to “right click” the FPGA Target you added in Step 3. Select “New” “FPGA I/O”.The next screen will appearOn the left side of this screen you see all the resources that are available on the Spartan-3E board. To add FPGA I/O to the project you have to select it in the left window and press the “Add” button. Now the FPGA I/O that you wanted to add has to show up in the window on the right side. For this project you have to add SW0, SW1 and LED0 to the project.If we go back to the “Project Explorer” view we see the FPGA I/O that we have added. With this I/O we will implement an Exclusive-OR function.Step 5: Creation of the FPGA VI The next step is the creation of a hardware program that runs on the Xilinx Spartan-3E hardware target.For this we do again a “right mouse click” on the FPGA target in the “Project Explorer” view. Select “New” VI. Be sure that you have right clicked the FPGA target and not “My Computer” because otherwise you will be creating a vi that runs not in Hardware (on the FPGA) but on your computer.This step will open the Front Panel and Block Diagram of the FPGA VI you just started creating. The code we will be implementing is an Exclusive-OR function. The view I always use in LabVIEW is the “tile left and right” view. You can select this by going to “Window” and then selecting “Tile Left and Right”. We you did all the steps right you have to see in the left corner of either the Front Panel or Block Diagram the name of the vi you created with /FPGA target behind it. This shows that the vi you are creating is aimed at the FPGA target.For now have a look at the “Functions Palette” which you can see when you click in the “Block Diagram” on “View” and then “Functions Palette”. You see that the available functions are different. You see “FPGA I/O”, “Memory & Fifo” and “FPGA Math & Analysis”. Those are specially for using on FPGA targets.Click in the Functions Palette on “FPGA I/O”.Place 2 I/O Nodes on the Block Diagram of the LabVIEW FPGA vi.Now do a “right mouse click” on one of the I/O Nodes. Select “Select FPGA I/O” then “Slide Switches” then “SW0”.You should see that the I/O node is filled with a green “SW0” label. The color green is standing for a Boolean variable. This is correct since a slider switch can only have the value of true or false.This project will be using 2 slider switches so we have to add another FPGA I/O. For this do a right click on the FPGA I/O you just filled with SW0. Select “Add Element”.The following is the screen you should have now:Try now to fill the I/O Item yourself with SW1. Try also to fill the I/O Node that is empty with LED0. This is done by right mouse clicking it then selecting “Select FPGA I/O”. In the option of “Select FPGA I/O” you see only the resources you added in the “Project Explorer” view to the project.The following screen will be created:Now we will as an example implement an exclusive-OR Boolean function into the FPGA. From the “Functions Palette” select “Programming” “Boolean” and look for the “Exclusive Or” function. Place this one on the Block diagram.Wire the “SW1” and “SW0” FPGA I/O to the Exclusive-OR inputs. Wire the output of the function to “LED0”.Your code has to look like this:When you implement the function like presented above the function will run only once. We would like to implement it that it runs continuously. For this we place a “While Loop” around it and we wire a Boolean “False constant” to the “stop condition” of this loop. This you normally don’t do on a PC because this will put your PC in a never ending loop. The “While Loop” you find on the “Functions Palette”.Now it is time to save your vi that you created for the FPGA. You do this by selecting “New” “Save As” in either the “Front Panel” or the “Block Diagram”.The name I usually use is FPGA_VI for the vi running on the FPGA.In “Project Explorer” you should see the followingIt is also a good idea to save the project file for this select in the “Project Explorer” “New” then “Save As”.I did use the name Lab1_BooleanLogicStep 5: Running the FPGA VIThis step is where we created the vi for. We designed it to run on an target. For starting the executing of this vi we have to press the “Run” arrow on either the “Block Diagram” or on the “Front Panel”.The first step LabVIEW does is “Generating Intermediate Files”. This files will be send to the Xilinx Synthesis Tools. But this is not important for us as application developers.In this step you see that LabVIEW is starting the “Compile Server”. This “Compile Server” can also be executed on another “more powerful” machine that is in your network (for this please see the information on the NI website.When the “Bitstream generation is complete” message appears and the server status is set to “Idle…” the Xilinx synthesis tools have done their job.You get a “Successful Compile Report” where you can see the implementation details of your code. You have to Press “Ok”.After you have pressed the “Ok” button your VI starts running on the FPGA target. It is indicated on your screen by the black “Run” arrow.Try to play with the switches SW0 and SW1 on the Spartan3E starter board you will see they have an XOR function; the led LD0 will be on when one of those switches is turned on.The problem with this implementation is that when you stop the VI the function is erased on the LabVIEW FPGA board. If you don’t want this effect you can download this VI to the FLASH of the Xilinx Spartan3E starter board (see next step).Step 6: Implementing the LabVIEW VI into FlashFor implementing your VI into the Flash on the Spartan3E Starter board you have to do some things. The first thing is setting the option of “Run when loaded to FPGA” on. For this you have to go to “Project Explorer”. Then “Right Mouse click” on your FPGA target. Select the “Properties” option.In this screen you see the option “Run when loaded to FPGA”. Make sure you select this option. Then press the “OK” button.We must recompile the VI because we made a change. Do this by going to the “Project Explorer” view. Click with the “Right Mouse button” on the FPGA VI you have created for thisproject. Select the “Compile” option.You will see that there are some previous explained steps executed. When the “Successful Compile Report” shows up youhave to press the “OK” button. Now we will download it to theFlash. For this you have to go to the “Project Explorer” view and do a “right mouse click” on the FPGA VI you created. Then choosing the “Download VI to Flash Memory” option will start downloading it to the Spartan-3E starter board flash.When this box appears the LabVIEW FPGA VI is downloaded to the Flash.Now you can pull out the USB cable out of the Xilinx Spartan3E board and press the PROG button on this board. You will see that the function is implemented in it.Enjoy.Vincent ClaesXIOS Hogeschool LimburgDepartment of Industrial Sciences and TechnologyUniversitaire Campus - Agoralaan – Gebouw HB-3590 DiepenbeekBelgium*********************tel.: +32 11 26 00 39fax: +32 11 26 00 54mobile: +32 478 35 38 49。

uClinux_On_MicroBlaze

uClinux On MicroBlazeAuthor:Xuyun (simux@)Summery:This document aim to introduce a quite clearly way of porting uClinux on MicroBlaze platform。

Include how to set up the hardware environment with EDK 8.2i, how to set up a toolchain, and how to compile the linux kernel 2.4.What is uClinuxuClinux is a derivative of Linux kernel intended for microcontrollers without Memory Magagement Units(MMUs). Because of its configurable property, it’s been ported to all kinds of microcontrollers or microprocessors, included ColdFire(Motorola), Blackfin(ADI), ARM7(ARM), M68000(Motorola), and of course MicroBlaze(Xilinx).The overall flow:PreparationuClinux development environment – Linux workstation, toolchain, uClinux sourceXilinx Spartan3-E 500 Starter Board(Revision D)Xilinx Platform Studio 8.2iXilinx ISE 8.2iIt turns out that Suse 10.1 and CentOS 4 would work perfectly as the compiling environment. Some other distributions of Linux may be also worked with uClinux such as RedHat 9 or Ubuntu 6.10. However the validation is not guaranteed.Thanks to the Dr. John Williams at University of Queensland, Australia. The toolchain is available at: .au/~jwilliams/mblaze-uclinux/Toolchain/toolchain_sources.htmlFor the starter, the simplest way of getting the uClinux source is to download the uClinux-dist: /pub/uClinux/dist/The version applied for this document is uClinux-dist-20070130.Hardware Environment SetupThe components for this project are needed as follow:CacheI/DMicroBlazewithTimerInterruptControllerDDR-SDRAMEMCforFlashEMCforEthernet with Scatter/Gather DMA capabilityUART – standard input/output deviceMDM – used for downloading the uClinux kernel image and for debuggingCertain core and software parameters must be set correctly in order to build a successful MicroBlaze-uCinux hardware design[1].StartStep 1:Start XPS programme – select Base System Builder wizard option and click OK;Figure 1 Create a new projectStep 2:Choose a path you want to save your project and click OK;Note 1: Some of the cores need licenses to be implemented. You may buy them via Xilinx. Fortunately, Xilinx also supply the evaluation version of license. However, the bitstream generated with this kind of license would be valid in 8 hours since it is download into the device.Figure 2 Choose a path Step 3:Select I would like to create a new design – and click Next;Figure 3 Choose a design style Step 4:Select Board vendor: XilinxSelect Board name: Spartan-3E Starter BoardSelect Board revision: DClick Next;Figure 4 Select a Board Step 5:Nothing to do but click Next;Figure 5 Module description Step 6:Setting Processor-Bus clock frequency to 66.67MHzSelect Debug I/F with On-chip H/W debug moduleSelect Data and Instruction(Use BRAM): 8KBSelect Enable cache link with Cached memory: DDR_SDRAM_32Mx16, and click Next;Figure 6 Processor configurationStep 7:Select RS232_DCE as follow:UARTLITEOPBPeripheral:Baudrate(bits per seconds): 115200Data bits: 8Parity:NONEUse interrupt option enabled, and click Next;For additional peripherals, make sure that DIP_Switches_4Bit, Buttons_4Bit and SPI_FLASH options are not selected, because we don’t use these peripherals in this project. Only FLASH_16Mx8 with OPB EMC, DDR_SDRAM_32Mx16 with MCH OPB DDR and Ethernet MAC with OPB ETHERNET options are selected. And we need the DMA mode to be Scatter gather DMA, along with Use interrupt[2].Note 2: Pay attention to the lock icon beside the OPB ETHERNET, which means it need license to be implemented.Figure 7-a Configure IO InterfacesFigure 8-a Configure Addition IO InterfacesFigure 8-b Configure Addition IO Interfaces Step 8: Click Add Peripheral;Select OPB TIMER with option:Counter bit width: 32One timer is presentSelect Use interruptClick OK;Then click Next;Figure 9 Add Internal PeripheralsStep 9:Select Instruction Cache(ICache) Size: 2KBSelect Data Cache(DCache) Size: 8KBBoth link ICache & DCache to the DDR_SDRAM_32Mx16, and click Next;Figure 10 Cache SetupStep 10:With default options on, and click Next until we come to the Address Maps(Figure 14):Figure 11 Software SetupFigure 12Figure 13Step 11:The Address Maps show how the memory space has been used. Reading the maps carefully, it will help you better understanding the memory management mechanism of your own uClinux.Click Generate to generate project related files.Figure 14 Address maps Figure 15 Base System createdAdder Fast Download Interface to the MicroBlaze ProcessorIn System Assembly view, double-click on the microblaze_0 processor instance. Enable Barrel Shifter and the Hardware Divider.In System Assembly view, double-click on the microblaze_0 processor instance. Set the Number of FSL Links to 1, and click OK .Still in System Assembly view, double click debug_module instance, Check the Enable Fast Download Write Port , uncheck the Enable the UART Interface On OPB .Add fsl_v20 bus from IP Catalog → Bus Category to System Assembly view.Add fsl_v20_0 as the bus connection for the microblaze_0 SFSL0 bus. And add fsl_v20_0 as the bus connection for the debug_module MFSL0 bus. So these two buses are linked with each other through Fast Complex Link Bus.Double click opb_intc_0, set Number of Interrupt Inputs to 4.Under the port filter expand the debug_module and enable the interrupt by changing the Net property to debug_module_interrupt – at the same time add debug_module – interrupt under opb_intc0 by clicking on the Intr. Then there are four interrupts included in the project.Again under Ports filter, expand the fsl_v20_0 instance:Set FSL_Clk = sys_clk_sSet SYS_Rst = sys_rst_sUntil now we are almost near the successfully building the hardware environment except one step! And this step is vital!Double click system.mhs file under Project Files, you will see the hardware description of every component included in the project.In microblaze section, add following line:PORT CLK = sys_clk_sIn opb_emc section, add following line:PORT CLK = sys_clk_sIn opb_ethernet section, add following line:PORT CLK = sys_clk_sIn opb_timer section, add following line:PORT OPB_CLK = sys_clk_sSave the system.mhs file.Under Device Configuration menu, select Update Bitstream. Then EDK begin to generate netlists of all the files, implement all the instances, Place & Router and finally generate bitstream – it’s really take a long time.After bitstream generated, it is time to download the bitstream file into target board.Open HyperTerminal, create a connection with any name you want, and set it as follow: ¾Set Bauderate to 115200;¾Set Data to 8;¾Set Parity to NONE;1;toStop¾ Set¾Set Flow to NONE.Power up the Spartan-3E 500 Starter Board, make sure that USB-JTAG cable & RS232 cable are connected correctly;Select Download Bitstream in Device Configuration menu. After a while, you’ll see the memory test result.Software Platform settingsFirst, we need to get the uClinux-BSP package from Petalogix, it can be downloaded at:/resources/downloads/files/edk_user_repository.tar.gzUntar the edk_user_repository.tar.gz package to the same root paths where you have your EDK installed. For example, suppose your EDK is installed at D:\EDK, then you should extract the package to D:\edk_user_repository.In XPS, select Software Platform Settings from Software menu;In OS & Library Settings, change the OS to uclinux and OS Version to 1.00.d.In Processor Parameters, set the CORE_CLOCK_FREQ_HZ of microblaze_0 to 66666667.Select OS and Libraries on the left panel.a. Change lmb_memory to dlmb_cntlr;b. Change main_memory to DDR_SDRAM_32Mx16. That’s where uClinux is running;c. Change flash_memory to FLASH_16Mx8. The image generated can be stored in it. Ifyou burn the binary file into it, there’s no necessary to download the “image.bin” throughXMD. And it’s really convenient and saving a lot of time.d. Set flash_memory_bank to 0;e. Set main_memory_bank to 0;f. Set flash_memory_start to 0x21000000. So flash_memory_start is the FLASH_16Mx8Base Address;g. Set flash_memory_size to 0x01000000. That’s how large the flash memory is(16Mbit).h. Set main_memory_start to 0x22000000. Because we set the DDR SDRAM as our mainmemory, the value for it is the Base Address of DDR SDRAM.i. Set main_memory_size to 0x02000000. That’s how large the main memory is(32Mbit).j. Set stdout and stdin to RS232_DCE;k. Set TARGET_DIR to E:/Spartan3E. That’s where auto-config.in saved. You can also name it in a different place you want. But do pay attention to the pattern of your specificpath, there exist differences between Windows & Linux.Click OK.Select Generate Libraries and BSPs from software menu. After a while, auto-config.in is generated and saved to E:\Spartan3E directory.Copy the auto-config.in file from the location in step 8 to:../uClinux-dist/ linux-2.4.x/arch/microblaze/platform/uclinux-autoOpen a terminal at present directory and type the command:dos2unix auto-config.in auto-config.inConclusionThis application note describe the procesure how to set up the MicroBlaze platform which is ready for uClinux running at step by step. It can be used for other hardware setting with necessary modification. There maybe slight differences according to the EDK and ISE version you are using.Reference[1]. Getting Started with uClinux on the MicroBlaze Processor, Xilinx./bvdocs/appnotes/xapp730.pdf[2]. Howto create a project for a simple uClinux ready MicroBlaze 4.0 design on XPS forSpartan-3E. http://www.teknologisk.dk/20356[3]. Creating a Simple uClinux ready MicroBlaze Design..au/~wu/downloads/uClinux_ready_Microblaze_design.pdfThanksZhiqing, Yao for material support! Dr John Wiliams from University of Queensland, Australia, and his leading team Petalogix. Numerous fans from uClinux-dev mailing list. Also Xilinx for providing so many application notes in detail.Revision HistoryDate VersionRevisionrelease. 9/4/07 1.0Initial。

VGA时序图

基于Verilog的VGA驱动设计(一)VGA时序分析VGA时序分析电阻DAC转换网络和640X480的VGA时序图:图1扫描频率显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT屏幕上从左到右(受水平同步信号HSYNC控制)、从上到下(受垂直同步信号VSYNC控制)做有规律的移动。

光栅扫描又分逐行扫描和隔行扫描。

电子束采用光栅扫描方式,从屏幕左上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后,形成一帧。

此后,电子束又回到左上方起点,开始下一帧的扫描。

这种方法也就是常说的逐行扫描显示。

1.Horizonal Timing图2A (us) Line Period(1040*20ns)B (us) Sync pulse lenghtC (us) Back porchD (us) Active video timeE (us) Front porch2.Vertical Timing图3O (ms) Frame Period 帧周期P (ms) Sync lengthQ (ms) Back porchR (ms) Active video timeS (ms) Front porchHorizonal timing information 水平扫描时序图4Notes:•Active area is actually an active area added with 6 overscan border pixels (in some other VGA timing tables those border pixels are included in back and front porch)Vertical timing information 垂直扫描时序图5Notes:•Active area is actually an active area added with 4 overscan border lines (in some other VGA timing tables those border lines are included in back and front porch)•Note than when the active part of VGA page is widened, it passes by the rising edge of the vertical sync signal in some modes (marked with *)根据上面的水平和垂直扫描时序可以分析显示800x600模式,FPGA系统时钟采用Spartan-3E Starter Kit板上的50MHz的有源晶振。

Spartan-3E开发板用户说明

附录:Spartan-3E开发板用户说明图1Spartan-3E多用途EDA实验开发平台(以下简称S3E实验平台),如图1所示,核心器件为XILINX公司的Spartan TM-3E器件XC3S500E,逻辑容量为50万门。

Spartan TM-3E借助于低成本的CPL,90nm工艺,满足了对大批量、I/O为核心的可编程逻辑解决方案的行业需求,是业界成本最低、性能最好的FPGA之一。

S3E实验平台在FPGA周围提供了丰富的资源,包括串口、PS/2接口、VGA接口、以太网接口、LED、LCD液晶显示、拨码旋钮开关和按钮、EPROM、A/D、D/A转换、电源、时钟等。

S3E的用户可以在PC机上通过USB JTAG电缆对FPGA进行配置,也可以通过SPI FLASH和NOR FLASH来配置。

1、S3E实验平台性能与特点●XILINX XC3S500E Spartan-3E FPGA:提供了最多232个I/O引脚和10000个逻辑单元。

●XILINX 4Mbit Flash配置PROM。

●XILINX XC2C64A CoolRunner系列CPLD:提供用户使用或辅助FPGA配置。

●64MByte、16位数据宽度、100MHz的DDR SDRAM接口。

●16MByte 并行INTEL公司的NOR FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●16Mbits ST半导体的SPI 串行FLASH:可存储FPGA配置信息或MicroBlaze指令序列。

●2行,每行可显示16个字符的LCD:用来显示FPGA输出信息。

●PS/2接口:用来外联键盘或鼠标,扩展输入设备●VGA接口:可显示64种颜色。

●10/100M以太网接口:提供了以太网物理层接口,便于MAC层IP的验证。

●两个标准RS232接口:可方便连接PC和其他工业设备进行数据传输。

●USB的下载接口配置接口。

●板载50MHz晶体振荡器。

题目1智能家居系统

题目1:智能家居系统要求:利用博创科技PXA270核心板或S3C2410核心板,设计一款智能家居控制器,要求具备电源、串口、网口、RS485、GPRS模块、液晶屏接口等资源,可以外连温度、烟雾、热释红外等传感器和电动窗帘、门禁系统等模型,并可通过短信与手机交互,构成简单的智能家居模拟系统,具体功能由参赛者自由发挥。

硬件组:制作控制器主板PCB。

其他硬件设备可以采用现成的模块或电路板或模型组装搭建。

软件组:完成控制器的操作界面、本地的自动控制、与手机交互的短信控制等功能。

题目2:基于ZigBee网络的分布监控系统要求:选择一款ZigBee模块,构成ZigBee无线通信网络,每个通信节点配置温度、电压、气体等等传感器。

由博创科技的2410平台或270平台为基础设计一个主控制器,来管理网络并处理各节点的数据。

具体节点数量、传感器种类、监控内容等由参赛者自由发挥。

硬件组:可选择现成的ZigBee模块,有实力的参赛者可自行设计PCB。

主控制器可自行设计PCB,也可利用教学平台。

软件组:完成主控制器界面和数据处理、ZigBee通信协议及应用程序。

题目3:智能车库管理系统要求:利用RFID技术,在汽车进出车库时进行记录和管理。

制作若干可自动行驶的汽车模型,每个模型贴RFID标签;利用嵌入式教学平台设计车库管理控制器,连接RFID识别设备,记录每辆车进出时间等信息,并通过语音报停车费等,另外可以检测车辆是否为未注册车辆等安全措施。

扩展功能:车库里设置引导显示屏,在车辆进入车库时由控制器分配车位并显示出来。

控制器可检测每个车位的占用情况以及车辆实际停靠位置。

硬件组:采用现成的RFID模块,或者自己设计RFID电路。

控制器可自行设计PCB,也可利用教学平台。

软件组:完成主控制器界面和时间、计价、车位分析处理、RFID通信等程序。

题目4:基于Xilinx系列平台的机器人控制系统题目5:基于Xilinx Spartan-3E Starter Board平台的Linux或uCLinux操作系统的LCD控制器题目6:使用VirtexII-pro开发上的资源,设计出基于VirtexII-pro开发板的MP3播放器题目7:基于EWARM工具的TCP/IP应用开发题目8:基于EWARM工具的跨平台开发题目9:基于Vxworks操作系统的人机交互界面题目10:Vxworks操作系统在OMAP芯片上的移植题目11:基于OMAP的手机开发系统题目12:设计一款USB声卡,利用USB CODEC芯片和一些模拟电路构成USB声卡,输出音频信号,可用耳机试听题目13:设计基于S3C2410的最小系统,包括CPU、SDRAM、FLASH、串口和网口等资源,并调试可运行题目14:设计基于电池供电和S3C2410处理器的手持设备,电池可用手机锂电池,处理器可用博创科技教学平台的核心板,液晶屏用3.5寸的TFT屏。

Easy Start 364 (3 ton) Soft Starter 368 (6 ton) So

Easy Start364 (3 ton) Soft Starter368 (6 ton) Soft StarterInstallation ManualMicro Air Corporation Phone (609) 259-2636 124 Route 526. Allentown NJ 08501 Fax (609) 259-6601Retrofit Instructions1.Read and understand these instructions completely before proceeding.2.Improper wiring can result in damage to EasyStart or connected components including but not limited towiring, compressors, and capacitors. Micro Air Corp is not responsible for damages to any of theaforementioned equipment caused by improper wiring.3.Turn off the breaker for the compressor’s electrical system.4.Consult the manufacture’s installation manual and wiring diagram for the identification of the following:a.Start capacitor (typically in a plastic can), start relay, or compressor start device. Note that thesedevices may NOT be installed on some systems.b.Run capacitor (typically in a metal can). Most have 2, multi-point terminal connections (orclusters). Some have 3 terminal connections.c.Control board switched-L1 output or main contactor compressor L1 output connecting to thecompressor common terminal (C) wire. Note some systems utilize a contactor to switch power tothe compressor, other use a power relay integrated into the main control board.5.If the system utilizes a start capacitor with a start relay, or a start assist device, disconnect all the wiringconnected to the start capacitor or the start assist and remove them from the electric box. Be aware thatsome connections to the compressor (e.g. compressor common L1 and compressor Run L2) may havejunction connections at terminals of the start relay. Therefore, it is best to NOT remove the start relayunless you are able to trace out these wiring junctions and splice them. Disconnecting and removing only the start capacitor from a system with a start cap and start relay will effectively disable the start relay, thus eliminating the need for it being removed.6.Locate the compressor run capacitor. Locate the wire connected from the run capacitor to the compressorrun winding terminal (R), and disconnect it from the run capacitor. Connect (splice) the brown wire from EasyStart to the disconnected wire.7.Connect the white wire from EasyStart to the same terminal of the run capacitor from which youdisconnected the (white) run winding (R) wire in step 6 above.8.Connect the orange wire from EasyStart to the terminal on the run capacitor that connects to thecompressor start winding terminal (S). If the run capacitor is a dual, compressor/fan type, make sure tochoose the correct capacitor terminal, typically labeled “COMP”, “C”, Herm, or “H”.9.Connect the black wire from EasyStart to the switched-L1 connection emanating from the main controlboard or main contactor that typically has a black or purple wire that connects to the compressor common(C) terminal wire.10.Wiring is now complete. Remove any remaining unused or disconnected wires and close all open electricalboxes and panels.11.Securely mount the EasyStart using the four holes provided on the mounting flange, locating it close to theoriginal system electric box (limited by wire harness length).12.Turn on the system circuit breaker using shore power. Start a heating or cooling cycle with the thermostat.13.EasyStart will now learn the characteristics of the compressor for the next five starts. This operation will bedone during normal operation and does not require any intervention or special actions. Once the learning process is completed, the EasyStart can be operated on either shore or generator power. During the learning starts, be sure to allow enough off time between starts for pressures to equalize. Equalization occurs in most systems within five minutes so we advise waiting at least five minutes between starts.IMPORTANT INSTALLATION NOTE FOR CRUISAIR® MARINE CUSTOMERS ONLY: When installing EasyStart into 230V SMX control applications that use the triac to switch power to the compressor, it is necessary to replace the triac with a relay. If the triac is not replaced, the pump relay triggers may suffer damage and ultimately fail. Please notr that this is not required for 115V SMX applications and the triac is still safe to use. See the Microair Webstore or contact Microair for details on the appropriate relay.Example EasyStart Installation Wiring Diagram:Jumper Usage:A six pin diagnostic header is located inside the EasyStart box. Most installations will not need to access this header.Jumpers may be placed on JP1 for certain special functions. Place jumpers only asshown below.Normal:Most operation should be done without a jumper installed on JP1 or with the jumperinstalled across pins 3 and 4 as shown.Default:A compressor may be operated with a factory defined start characteristic. This maynot be the optimal start for the connected compressor and is generally used for factorydiagnostics. No optimization is done with this setting.Relearn:If a compressor, start capacitor, or run capacitor is replaced, place a jumper onpins 4 and 6 as shown. Cycle power on then off again and replace the jumper in the “Normal”position. Follow step 13 of the retrofit instructions to complete the relearn process.Disable:This setting disables the microprocessor on the board so no operation can occur. Anti-Short Cycle Timer:EasyStart models incorporate a timer that prevents immediate restarts.This feature was added to prevent overheating of the start capacitor and reducefaults due to un-equalized pressures in the system. Restart will take up to 5minutes if power is removed then reapplied.Later models include a wire jumper JP2 (see picture on right) that canbe cut to eliminate this feature. System controls must be sufficient to prevent short cycling if this jumper is cut. Warning: Starts must be limited to 1 start every 5 minutes with pressures equalized if JP2 is cut.EasyStart Troubleshooting:Wiring Evaluation:A ll start components from the original installation are removed including PTC’s and startcapacitors.The Brown wire from EasyStart connects directly to the compressor run winding.The Black wire from EasyStart is spliced to the thermostat relay feeding the compressor overloadprotector on the compressor common terminal.The Orange wire from EasyStart is connected to the compressor run capacitor on the same side asthe compressor start winding.The White wire from EasyStart is connected to the AC-L2 or AC-N side of the compressor runcapacitor.Trouble Lights:Three diagnostic lights are provided inside the EasyStart box on the printed circuit board. These lights are labeled in white silkscreened letters next to the light. When a fault is detected, EasyStart willilluminate one or more lights to indicate which fault occurred. All faults except over current will reset after3 minutes. Over current is reset by removing power from EasyStart and reapplying power. Users will notnormally need to view these lights. The chard below defines the lights that are turned on for each fault.Fuses:Protection fuses are installed in the start circuit to prevent damage due to miswiring or start capacitorfailure. If this fuse fails in normal operation, there is most likely a problem with the start capacitor which should be replaced along with the fuse.364 (3 ton)1.Revision H and earlier boards: These boards incorporate a non-replaceable fuse inthe start circuit. These units must be returned to Microair for repair.2.Revision I and above boards: These boards incorporate a replaceable 15A 250Vrated, slow blow, 5mm x 20mm glass fuse.368 (6 ton)1.Revision E and earlier boards: These boards incorporate a non-replaceable fuse inthe start circuit. These units must be returned to Microair for repair.2.Revision F and above boards: These boards incorporate a replaceable 30A 250VACrated 3AB, 3AG, ¼” x 1 ¼” (6.35mm x 31.75mm) slow blow ceramic fuse.FAQ:What is re-learning?The re-learning process simply clears the EasyStart memory and returns it to as shipped condition. EasyStart should be re-learned whenever a compressor is changed or if pressures were not allowed to equalize during the learning process.To re-learn EasyStart, remove power and open the EasyStart box. Locate the 6 pin header shown in the jumper usage section of this manual and place the shorting jumper over pins 4 and 6 as shown. Start a cycle with your thermostat with the compressor powered from AC mains and allow EasyStart to start the compressor. Remove power once the compressor starts and replace the jumper to the stored position over pins 3 and 4. Replace the cover on EasyStart and complete at least 4 additional starts. Be sure to allow time for pressures to equalize between starts, usually 3 to 5 minutes.Be sure to remove the jumper from pins 4 and 6 and replace it to pins 3 and 4 immediately after the FIRST start and after power is removed.I connected everything and it just won’t start. What do I do now?First, do the wiring evaluation in this section. Wiring should be exactly as shown in the sample diagram with no left over start components. If there are any questions about wiring your unit, you can send a wiring diagram for your compressor to **************** along with your question.Be sure you are only using regular AC line power and not a generator or inverter for the first five starts. The first starts on EasyStart are usually higher than the final start and can overload marginal supplies and prevent EasyStart from learning the best start for your compressor.Check for any trouble lights. If any are illuminated, identify the reason EasyStart is not starting your compressor. Most times trouble lights point to a problem with the wiring.What does a “S talled” indication from EasyStart mean?Stalled means EasyStart is not seeing the condition where it can declare that the compressor is running and connect the compressor directly. The first thing to do is the wiring evaluation above.Stalled can also be caused by an improperly sized or bad start capacitor. 3T systems with 220 volt 12K BTU and smaller compressors may require smaller value start capacitors. Contact Microair prior to purchase to determine requirements for these systems.What d oes “Power Interruption” mean?Power was lost for several AC cycles of power and EasyStart shut down. Compressors will stall after only a few lost cycles creating a huge load when power is restored. EasyStart prevents this excessive load by preventing operation for 3 minutes. EasyStart will restart the compressor following this delay.We have found that some power conditioning equipment uses relays to switch taps on a transformer may switch too slowly to properly run a compressor.What does “Start winding not detected-EasyStart is miswired” mean?One of the following:The orange wire is not connected to the start winding.The Compressor Start winding is open.Line L2 is connected to the compressor start winding.COPYRIGHT© 2017 Micro Air Corporation, All Rights ReservedNo part of this publication may be reproduced, translated, stored in a retrieval system, or transmitted in any form or by any means electronic, mechanical, photocopying, recording or otherwise without prior written consent by Micro Air Corporation.Every precaution has been taken in the preparation of this manual to insure its accuracy. However, Micro Air Corporation assumes no responsibility for errors and omissions. Neither is any liability assumed nor implied for damages resulting from the use or misuse of this product and information contained herein.。

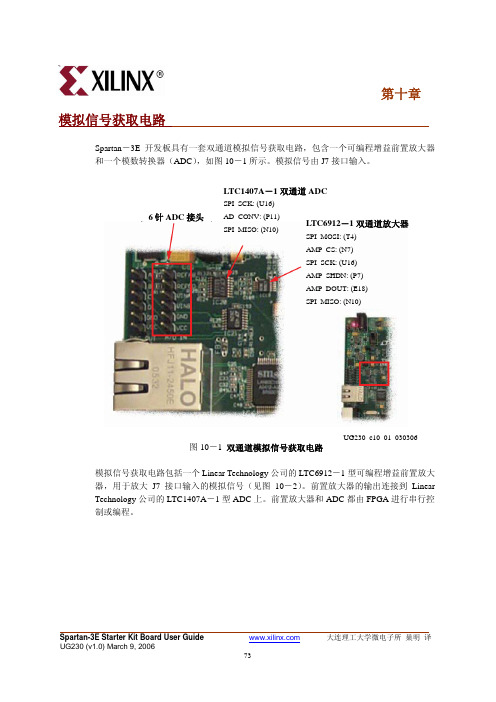

SPARTAN-3E说明书第10章

Spartan -3E 开发板具有一套双通道模拟信号获取电路,包含一个可编程增益前置放大器和一个模数转换器(ADC ),如图10-1所示。

模拟信号由J7接口输入。

图10-1 双通道模拟信号获取电路模拟信号获取电路包括一个Linear Technology 公司的LTC6912-1型可编程增益前置放大器,用于放大J7接口输入的模拟信号(见图10-2)。

前置放大器的输出连接到Linear Technology 公司的LTC1407A -1型ADC 上。

前置放大器和ADC 都由FPGA 进行串行控制或编程。

第十章模拟信号获取电路 6针ADC 接头LTC1407A -1双通道ADC SPI_SCK: (U16) AD_CONV: (P11) SPI_MISO: (N10)LTC6912-1双通道放大器SPI_MOSI: (T4) AMP_CS: (N7) SPI_SCK: (U16) AMP_SHDN: (P7) AMP_DOUT: (E18) SPI_MISO: (N10)UG230_c10_01_030306图10-2 模拟信号获取电路详图从模拟输入到数字输出模拟信号获取电路将VINA 或VINB 上输入的模拟电压信号转换为D[13:0]上的14位数字表示,见方程10-1。

[]819225.165.10:13×−×=VVV GAIN D IN方程10-1GAIN 是装入可编程前置放大器的当前增益设置。

可用的不同增益设置和允许的VINA 和VINB 输入电压范围见表10-2。

放大器和ADC 的参考电压都是1.65V ,由图10-2所示的分压器产生。

因此, VINA 和VINB 上的输入电压都被减去了1.65V 。

ADC 的最大输入范围是±1.25V ,以参考电压1.65V 为中心。

因此出现在输入模拟信号的分母上的是1.25V 。

UG230_c10_02_022306接头J7最终,ADC提供一个14位,二进制补码形式的数字输出。

ProASIC3 E Proto Kit 快速入门卡文档说明书

© 2012 Microsemi Corporation. All rights reserved.ProASIC3/E Proto KitQuickstart CardKit Contents – A3PE-PROTO-KIT, A3PE-BRD1500-SKTQuantityDescription1ProASIC ®3 Starter kit board with an A3PE1500-PQ2081FlashPro3 programmer (not included with A3PE-BRD1500-SKT)19 V power supply with international adaptersWall Mount Power Interboard ISP ConnectorLCD Display ModuleCAT5E RJ45Connectors for LVDSCommunications SMA for Optional External OscillatorRemovable Shunts to Isolate All I/Os for Prototyping Removable Shunts to Isolate All I/Os for Prototyping Oscillator forSystem Clock Manual Clock OptionFlashPro3 ISP ConnectorProASIC3/E in PQ208 Package 4 SwitchesEvery PQ208 Pin Accessible for Prototyping8 LEDsRemovable Shunts to Isolate All I/Os for Prototyping50200381-0/10.12ProASIC3/E Proto Kit Quickstart CardRunning the Test DesignTo test the board, you can program the demo design. Download it from the ProASIC3 Starter Kit page: /products/hardware/devkits_boards/proasic3_starter.aspx .Software and LicensingVisit the Actel website ( ) for the latest Libero IDE Software. Request a free gold license to activate your software.Software releases: /download/software/libero Licensing: https:///Portal/DPortal.aspx?r=1Documentation ResourcesFor further kit information, including user's guide, tutorial, and full design examples, refer to the ProASIC3 Starter Kit page:/soc/products/hardware/devkits_boards/proasic3_starter.aspx .Technical Support and ContactsTechnical support is available online at /soc/support and by email at **********************.Microsemi SoC Sales offices, including Representatives and Distributors, are located worldwide. To find your local representative visit /soc/company/contact .ActionResultsPress SW1Asynchronous clear for the whole designPress SW2Up-down control for the 8-bit counter. Press and hold SW2 for down count. Press SW3Synchronous load for the 8-bit counter. Press SW3 for loading from the Hex switches.Press SW4Switching between manual clock(SW5) and 40 MHz oscillator clock.Press SW5Manual clock (very useful for simulation)Press SW6Select for DATA_BLOCK. It allows switching LED output between the counter and flashing data.Change Hex Switchsetting (U13 and U14)Changes the loaded data for the 8-bit counter.。

自动门介绍

•

•

产品一流的质量意味着更长的使用寿命,意味着更小的操作成本,也意味着您可以更有效地运用资金。 静候您的到来,因为K推拉门驱动器在运行时完全没有噪音。 灵活简便的安装,因为无论是推门式或拉门式操作器,只要将拉杆组件相应安装于合叶的同侧或对侧,即可保证门的顺畅开启与关闭。 美观而实用,因为尺寸小巧的驱动器,设计先进、可调节的拉杆组件以及延伸轴,可以为任何条件的安装情况提供理想的解决方法。 小巧的外形,但是推拉门驱动器具有强大的功能以满足用户的不同要求。舒适的操作及产品的高可靠性是我们对用户的承诺。不同的颜色的镀铬钢驱动器罩可以满足各种建筑风格的要求。 高度安全的运行,因为推拉门驱动器具有智能监视自检功能,随时保证无误运行及最大的安全性。 基本功能 集成控制开关 实现极其简单的操作过程。 可实现的辅助功能 ●增大关门力度 ●伺服功能 ●可调净开宽度 ●通过程序开关实现"手动状态"向"夜间安全状态"的转换 ●双扇门关门顺序的自动控制 ●连锁功能 ●分步控制脉冲"开/关" ●"出口单方向"功能锁定或不锁定 电子遥控面板(BEDIS)可实现的功能 ●自动状态 ●手动状态 ●常开 ●出口单方向 ●夜间安全状态 ●自动显示运行故障代码,便于维修 根据用户要求可调节的运行参数 ●开门速度 ●关门速度 ●门扇保持打开状态的时间 ●电机功率 防火功能 具有防火功能的门 , 每座门均装有复位按钮。建筑上具有多种防火功能的门,均可连至建筑的控制中心,已达到控制功能。 后台数据处理 ●门处于"关闭"状态 ●门处于"开启"状态 ●故障信息 ●电子锁启动信息 ●声音信号 以上信息数据可以通过信号输出方式输出,送至建筑的控制中心。(其中四个信号没有电压

Spartan-14.7平台与ISE软件的入门资料

Spartan-3平台与ISE软件的入门一、快速浏览Spartan-3E Starter Kit的用户指南,便于以后进行内容查找。

中文用户指南:Spartan-3E Starter Kit Board User Guide.mht英文用户指南:Spartan-3E Starter Kit Board User Guide.pdf二、ISE软件安装。

根据资料自学完成安装(在个人电脑上),ISE推荐版本:14.7。

注意需要破解(即提供license)。

三、ISE软件的初次使用。

在Spartan-3E开发板上,使用ISE软件,完成一个最基本工程的建立、编程、仿真、下载实现。

3.11)运行ISE Design Suite软件,界面如下2)新建工程(可参考图书:Xilinx FPGA开发实用教程)File New Projecta)设置顶层文件类型Top-level source type为Schematic(原理图)b)选择工程的保存位置Location和工作目录Working Directory为fpgaxunlianc)为工程取名,如:xunlian1点击Next进行下述设置根据观察我们使用的Spartan 3E开发板上的FPGA芯片上的字,可知目标FPGA芯片的属性如下芯片系列(Family):Spartan3E芯片型号(Device):XC3S500E芯片封装(Package):FG320速度等级(Speed):-4(注:XILINX的FPGA,值越大,速度等级越高)综合工具(Systhesis Tool)选择ISE自带的XST仿真工具(Simulator)选择ISE自带的Isim编程语言(Preferred Language)选择Verilog然后,点击Next观察,然后,点击Finish 3)在工程中加入文件右键点击“xc3s500e-4fg320”,执行“New Source”如上图,先建立一个原理的源文件,取名为Topsch,注意“Add to project”复选框需选中,然后点击Next观察,然后点击Finish,到此建立一张空白原理图。

sirius 3RW55 系列软启动器产品说明书

20 ... 100 % 50 ... 50 % 0 ... 360 s 0 ... 360 s 10 ... 100 % 10 ... 100 % 20 ... 200 % 125 ... 800 % 40 ... 100 % 0 ... 2 s 3 5%

2/7/2022

Subject to change without notice © Copyright Siemens

● torque control ● combined braking ● analog output ● programmable control inputs/outputs ● condition monitoring ● automatic parameterisation ● application wizards ● alternative run-down ● emergency operation mode ● reversing operation ● soft starting at heavy starting conditions Power Electronics operational current ● at 40 °C rated value ● at 40 °C rated value minimum ● at 50 °C rated value ● at 60 °C rated value operational current at inside-delta circuit ● at 40 °C rated value ● at 50 °C rated value ● at 60 °C rated value operating voltage ● rated value ● at inside-delta circuit rated value relative negative tolerance of the operating voltage relative positive tolerance of the operating voltage relative negative tolerance of the operating voltage at inside-delta circuit relative positive tolerance of the operating voltage at inside-delta circuit operating power for 3-phase motors ● at 230 V at 40 °C rated value ● at 230 V at inside-delta circuit at 40 °C rated value ● at 400 V at 40 °C rated value ● at 400 V at inside-delta circuit at 40 °C rated value Operating frequency 1 rated value Operating frequency 2 rated value relative negative tolerance of the operating frequency relative positive tolerance of the operating frequency minimum load [%] power loss [W] for rated value of the current at AC ● at 40 °C after startup ● at 50 °C after startup ● at 60 °C after startup power loss [W] at AC at current limitation 350 % ● at 40 °C during startup ● at 50 °C during startup ● at 60 °C during startup type of the motor protection Control circuit/ Control type of voltage of the control supply voltage control supply voltage at AC ● at 50 Hz ● at 60 Hz relative negative tolerance of the control supply voltage at AC at 50 Hz relative positive tolerance of the control supply voltage at AC at 50 Hz relative negative tolerance of the control supply voltage at AC at 60 Hz relative positive tolerance of the control supply

SPARTAN-3E说明书第2章

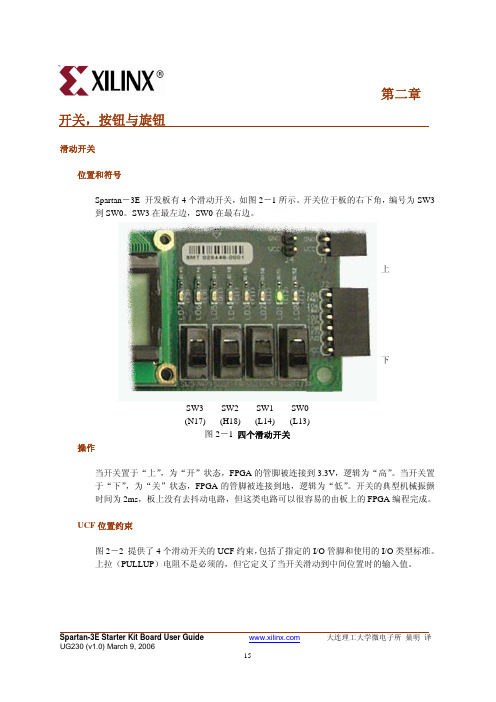

滑动开关位置和符号Spartan -3E 开发板有4个滑动开关,如图2-1所示。

开关位于板的右下角,编号为SW3到SW0。

SW3在最左边,SW0在最右边。

SW3 SW2 SW1 SW0 (N17) (H18) (L14) (L13)图2-1 四个滑动开关操作当开关置于“上”,为“开”状态,FPGA 的管脚被连接到3.3V ,逻辑为“高”。

当开关置于“下”,为“关”状态,FPGA 的管脚被连接到地,逻辑为“低”。

开关的典型机械振颤时间为2ms ,板上没有去抖动电路,但这类电路可以很容易的由板上的FPGA 编程完成。

UCF 位置约束图2-2 提供了4个滑动开关的UCF 约束,包括了指定的I/O 管脚和使用的I/O 类型标准。

上拉(PULLUP )电阻不是必须的,但它定义了当开关滑动到中间位置时的输入值。

第二章开关,按钮与旋钮 上 下NET "SW<0>" LOC = "L13" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<1>" LOC = "L14" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<2>" LOC = "H18" | IOSTANDARD = LVTTL | PULLUP ; NET "SW<3>" LOC = "N17" | IOSTANDARD = LVTTL | PULLUP ;图2-2 滑动开关的UCF 约束按钮开关位置和符号Spartan -3E 开发板有4个按钮开关,如图2-3所示。

开关位于板的左下角,编号为BTN_NORTH ,BTN_EAST ,BTN_SOUTH ,BTN_WEST 。

连接开关的FPGA 管脚见图2-3的括号内,以及图2-5的UCF 文件中。

(完整)FPGA芯片中支持不同io电平

在fpga芯片中支持不同io电平标准2008—06-06 15:15:39|分类: FPGA AND DSP | 标签: |字号大中小订阅I/O BankingSome of the I/O standards described above require VCCO and/or VREF voltages. These voltages are externally supplied and connected to device pins that serve groups of IOBs, called banks。

Consequently, restrictions exist about which I/O standards can be combined within a given bank. Eight I/O banks result from separating each edge of the FPGA into two banks (see Figure 3). The pinout tables show the bank affiliation of each I/O (see Pinout Tables, Module 4)。

Each bank has multiple VCCO pins which must be connected to the same voltage。

Voltage requirements are determined by the output standards in use。

In the TQ144 and PQ208 packages, the eight banks have VCCO connected together。

Thus, only one VCCO level is allowed in these packages, although different VREF values are allowed in each of the eight banks.Within a bank, standards may be mixed only if they use the same VCCO。

PG上嵌入式系统实例作者赵峰第7章

第7章 嵌入式Mini VOS服务器

图7.2.8 添加OPB TIMER

第7章 嵌入式Mini VOS服务器

(11) 接下来图7.2.9所示的对话框显示了Timer的配 置参数,这里,我们只需要一个Timer,并把中断打开, 然后点击“Next”按钮。

第7章 嵌入式Mini VOS服务器

图7.2.9 OPB TIMER配置

第7章 嵌入式Mini VOS服务器

图7.2.1 配置向导

第7章 嵌入式Mini VOS服务器

(2) 在弹出的对话框中,点击“Browse”按钮,选择一 个目标磁盘并建立一个自己的工程文件夹;双击进入自己 的工程文件夹后,点击保存,系统会自动为此项目命名为 system.xmp;点击“OK”按钮,进入BSB欢迎对话框。

第7章 嵌入式Mini VOS服务器

图7.2.5 I/O端口配置(一)

第7章 嵌入式Mini VOS服务器

(8) 继续配置I/O端口。由于在远程控制中需要通过LED 来测试远程控制成功与否,所以选择“LEDs_8bit”,并且打 开中断;其他外设除FLASH外,暂不需要,均不勾选,之 后点击“Next”按钮,如图7.2.6所示。

图7.2.2 开发板选择窗口

第7章 嵌入式Mini VOS服务器

图7.2.3 处理器选择窗口

第7章 嵌入式Mini VOS服务器

(6) 进入MicroBlaze配置对话框(见图7.2.4),参考时钟 频率选择默认值50 MHz即可,MicroBlaze处理器的总线时 钟频率选择为“66.67”MHz。其中参考时钟由开发板上的 时钟源提供,用来产生总线和处理器的频率,并且根据开 发板的不同而不同。“Debug I/F”选择“On-chip H/W debug module”,“Local memory”选择默认“8 KB”即可。 “Cache setup”选择“Enable cache link”。设置完成后点击 “Next”按钮。

英文软起1拖1两地控.dwg

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Spartan3E-Starter Board使用说明QQ群:34215299认准Jinms谨防盗版资料版本:Spartan3E.TCH.V1.22011-03概述此开发板采用了Xilinx FPGA芯片XC3S250E-VQG100,配有的2M大小PROM-XCF02S和50MHZ有源晶振构成了开发板的核心部分。

可以采用外部电源供电,也可以通过USB延长线,通过电脑USB 接口供电。

可以使用的资源有:1、4个按键输入2、8个LED3、蜂鸣器4、HC595驱动4位八段数码管5、232串口6、PS2接口7、VGA接口8、68个IO此开发板可以用来入门学习,配套的例程有:1、LED跑马灯2、按键控制LED3、蜂鸣器控制4、通过SPI方式驱动HC595,实现4位8段数码管计数器5、URAT串口通信程序6、其它例程此开发板也可以用来做实验,所有IO都通过排针引出来了。

Spartan3E家族是Xilinx新款高性价比的FPGA芯片。

Spartan3E FPGA资源如下图所示:开发板采用的XC3S250E-VQG100芯片如下图所示:第一部分资源介绍第二部分软件的安装一、ISE的安装2、单击3、选择后,单击4、选择后,单击5、选择后,单击6、选择全部分选框后,单击7、选择安装路径后,单击8、单击8、开始安装,整个过程大概半小时9、安装快结束的时候,出现这个对话框,单击10、提示安装license,选择,单击11、单击,选择License文件12、打开License文件13、License文件安装成功14、单击Close关闭License对话框15、单击结束安装。

二、Modelsim的安装1、双击开始安装Modelsim6.6a-se2、单击3、选择安装路径,单击4、单击5、单击6、单击7、单击8、单击,后重启电脑9、安装License,复制到安装目录下10、复制到安装目录下11、在安装目录下搜索mgls.dll和mgc.pkginfo并复制到然后去除只读属性,双击,生成license。

11、把生成的lic.dat复制到安装目录下,并把覆盖原来的文件。

12、新建环境变量如下,注册成功。

13、启动Modelsim。

第三部分操作技巧——快速入门1、ISE入门操作1.1启动ISE1.2新建一个工程1.3输入工程名字和设定工程目录后单击Next1.4如下图配置后,单击Next1.5单击Finish1.6右击鼠标,在弹出菜单后选择Add Source1.7在Add Source对话框中添加SOURCE中已经存在的源码1.8工程目录如下图所示1.9综合2、仿真2.0.1配置仿真——Modesim路径设置(只需第配置一次)2.0.2配置仿真——安装目录下,把modesim.ini文件去掉只读属性2.0.3配置仿真——双击Compile HDL Simulation Libraries产生仿真库,这个过程大概需要10-20分钟2.1双击Simulate Behavioral Model启动仿真2.2设置仿真时间1000ns单击运行,可以每次推进1000ns仿真时间2.3仿真结果3、执行并产生编程文件,之后点击Configure Target Device,启动IMPACT4、执在空白区域右击选择Initialize Chain5、生产PROM文件6、如下图配置PROM后点击OK8、双击产生PROM文件9、产生PROM文件后11、选择BIT文件12、下载BIT文件到开发板13、编译成功后14、用串口调试助手测试UART通信第四部分实验介绍1、run_led跑马灯程序实例硬件部分:Ucf:文件:NET"clk"LOC="P83";NET"led[0]"LOC="P24";NET"led[1]"LOC="P26";NET"led[2]"LOC="P27";NET"led[3]"LOC="P32";NET"led[4]"LOC="P33";NET"led[5]"LOC="P34";NET"led[6]"LOC="P35";NET"led[7]"LOC="P36";源码:module run_led_top(clk,led);input clk;//输入时钟output[7:0]led;//LEDreg[24:0]counter;//计数分频器reg[9:0]init_time=0;//初始化延时计数reg[7:0]led;reg[2:0]led_n;//指示那一路LEDalways@(posedge clk)beginif(init_time<1000)init_time=init_time+1;Endalways@(posedge clk)beginif(init_time<1000)begincounter<=0;endelse beginif(counter<25000000)counter<=counter+1;else counter<=0;endendalways@(posedge clk)beginif(init_time<1000)beginled_n<=0;endelse beginif(counter==25000000)led_n<=led_n+1;endendalways@(posedge clk)beginif(init_time<1000)led<=0;else begincase(led_n)0:led<=8'b1111_1110;1:led<=8'b1111_1101;2:led<=8'b1111_1011;3:led<=8'b1111_0111;4:led<=8'b1110_1111;5:led<=8'b1101_1111;6:led<=8'b1011_1111;7:led<=8'b0111_1111;endcaseendendendmodule2、SC_led按键控制LED实例电路部分:Ucf文件NET"clk"LOC="P83";NET"led[0]"LOC="P24";NET"led[1]"LOC="P26";NET"led[2]"LOC="P27";NET"led[3]"LOC="P32";NET"led[4]"LOC="P33";NET"led[5]"LOC="P34";NET"led[6]"LOC="P35";NET"led[7]"LOC="P36";NET"sw1_up"LOC="P40";NET"sw2_up"LOC="P41";module run_led_top(clk,sw1_up,sw2_up,led);input clk;input sw1_up;input sw2_up;output[7:0]led;reg[23:0]sw1_counter_high;//按钮1防止抖动高计数reg[23:0]sw1_counter_low;//按钮1防止抖动低计数reg[23:0]sw2_counter_high;//按钮2防止抖动高计数reg[23:0]sw2_counter_low;//按钮1防止抖动低计数reg sw1_flag=0;//按钮1按下标志reg sw2_flag=0;//按钮2按下标志reg s1_flag=0;//确保每次LED只运行一位reg s2_flag=0;//确保每次LED只运行一位reg[9:0]init_time=0;reg[7:0]led;//LED部分reg[2:0]led_n;//指示哪一位LEDalways@(posedge clk)beginif(init_time<1000)init_time=init_time+1;endalways@(posedge clk)beginif(init_time<1000)led<=0;else begincase(led_n)0:led<=8'b1111_1110;1:led<=8'b1111_1101;2:led<=8'b1111_1011;3:led<=8'b1111_0111;4:led<=8'b1110_1111;5:led<=8'b1101_1111;6:led<=8'b1011_1111;7:led<=8'b0111_1111;endcaseendendalways@(posedge clk)beginif(init_time<1000)beginsw1_counter_high<=0;endelse beginif(sw1_up)sw1_counter_high<=sw1_counter_high+1;else sw1_counter_high<=0;endendalways@(posedge clk)beginif(init_time<1000)beginsw1_counter_low<=0;endelse beginif(!sw1_up)sw1_counter_low<=sw1_counter_low+1;else sw1_counter_low<=0;endendalways@(posedge clk)beginif(init_time<1000)beginsw2_counter_high<=0;endelse beginif(sw2_up)sw2_counter_high<=sw2_counter_high+1;else sw2_counter_high<=0;endendalways@(posedge clk)beginif(init_time<1000)beginsw2_counter_low<=0;endelse beginif(!sw2_up)sw2_counter_low<=sw2_counter_low+1;else sw2_counter_low<=0;endendalways@(posedge clk)beginif(sw1_counter_high==1000000)sw1_flag<=1'b1;else if(sw1_counter_low==1000000)sw1_flag<=1'b0;endalways@(posedge clk)beginif(sw2_counter_high==1000000)sw2_flag<=1;else if(sw2_counter_low==1000000)sw2_flag<=0;endalways@(posedge clk)beginif(init_time<1000)begin led_n<=0;s1_flag<=0;s2_flag<=0;endelse beginif(sw1_flag==1)beginif(sw2_flag)if(s1_flag==1)beginled_n<=led_n+1;s1_flag<=0;endendelse s1_flag<=1;if(sw2_flag==1)beginif(sw1_flag)if(s2_flag==1)beginled_n<=led_n-1;s2_flag<=0;endendelse s2_flag<=1;endendendmodule3、alarm蜂鸣器实例Ucf文件#Created by Constraints Editor(xc3s250e-vq100-4)-2011/02/10 NET"clk"TNM_NET="clk";TIMESPEC TS_clk=PERIOD"clk"20ns HIGH50%;#PlanAhead Generated physical constraintsNET"clk"LOC=P83;NET"down"LOC=P41;NET"fclk"LOC=P47;NET"rst"LOC=P40;NET"up"LOC=P48;#PlanAhead Generated IO constraintsNET"clk"IOSTANDARD=LVCMOS33;NET"down"IOSTANDARD=LVCMOS33;NET"fclk"IOSTANDARD=LVCMOS33;NET"rst"IOSTANDARD=LVCMOS33;NET"up"IOSTANDARD=LVCMOS33;源码:module alarm_top(clk,rst,up,down,fclk);input clk;input rst;input up;input down;output reg fclk;reg[27:0]fcnt=0;//频率计数reg[27:0]rang=100000;//频率范围wire bv1_posedge,bv2_posedge;reg[2:0]bv1,bv2;//寄存器always@(posedge clk)beginbv1<={bv1[1:0],up};bv2<={bv2[1:0],down};endassign bv1_posedge=(!bv1[2])&bv1[1];assign bv2_posedge=(!bv2[2])&bv2[1];always@(posedge clk)beginif(!rst)beginrang<=100000;fcnt<=0;fcnt<=1'b0;endelse beginif(bv1_posedge&&rang<12000000)rang<=rang+10000;else if(bv2_posedge&&rang>1000000)rang<=rang-10000;if(fcnt==rang)begin fclk=!fclk;fcnt<=0;endelse fcnt<=fcnt+1;endendendmodule4、counter2SPI计数器实例电路部分Ucf文件NET"clk"TNM_NET=clk;TIMESPEC TS_clk=PERIOD"clk"20ns HIGH50%; NET"clk"LOC="P83";NET"dain"LOC="P99";NET"dclk"LOC="P94";NET"dlk"LOC="P95";NET"drst"LOC="P98";NET"rst"LOC="P40";源文件:Top文件:module counter_top(clk,dclk,dlk,dain,drst,rst);input clk;output dclk;output reg dlk=1;output dain;output reg drst=0;input rst;wire[15:0]in_data;wire busy;wire ready_fg;reg wr_r=0;reg[15:0]dpy_data=0;reg[12:0]seg=0;reg[7:0]dat=0;reg[24:0]cnt_time=0;reg[13:0]cnt=0;reg[3:0]led4=0;reg[3:0]led3=0;reg[3:0]led2=0;reg[3:0]led1=0;parameterzero=8'b1100_0000,one=8'b1111_1001,two=8'b1010_0100,three=8'b1011_0000,four=8'b1001_1001,five=8'b1001_0010,six=8'b1000_0010,seven=8'b1111_1000,eight=8'b1000_0000,nine=8'b1001_0000;assign wr=wr_r;assign in_data=dpy_data;always@(posedge clk)beginif(!rst)begindrst<=0;dpy_data<=0;seg<=0;endelse begindrst<=1;if(!busy)begindlk<=1;if(ready_fg==0)begin wr_r<=0;endelse begincase(seg[12:11])0:begincase(led1)0:dat<=zero;1:dat<=one;3:dat<=three;4:dat<=four;5:dat<=five;6:dat<=six;7:dat<=seven;8:dat<=eight;9:dat<=nine;endcasedpy_data<={8'b1111_0111,dat};end1:begincase(led2)0:dat<=zero;1:dat<=one;2:dat<=two;3:dat<=three;4:dat<=four;5:dat<=five;6:dat<=six;7:dat<=seven;8:dat<=eight;9:dat<=nine;endcasedpy_data<={8'b1111_1011,dat};end2:begincase(led3)0:dat<=zero;1:dat<=one;2:dat<=two;3:dat<=three;4:dat<=four;5:dat<=five;6:dat<=six;7:dat<=seven;8:dat<=eight;9:dat<=nine;endcasedpy_data<={8'b1111_1101,dat};end3:begincase(led4)0:dat<=zero;2:dat<=two;3:dat<=three;4:dat<=four;5:dat<=five;6:dat<=six;7:dat<=seven;8:dat<=eight;9:dat<=nine;endcasedpy_data<={8'b1111_1110,dat};endendcaseseg<=seg+1;dlk<=0;wr_r<=1;endendendendalways@(posedge clk)beginif(cnt_time<10000000)cnt_time=cnt_time+1;else begincnt_time=0;if(cnt<9999)begincnt=cnt+1;led1<=led1+1;if(led1==10)beginled2<=led2+1;led1<=0;endif(led2==10)beginled3<=led3+1;led2<=0;endif(led3==10)beginled4<=led4+1;led3<=0;endif(led4==10)beginled4<=0;endendelsecnt=0;endendSPI SPI_inst(.clk(clk),.wr(wr),.dclk(dclk),.dain(dain),.in_data(in_data),.busy(busy),.ready_fg(ready_fg));endmoduleSpi:module SPI(clk,wr,dclk,dain,in_data,busy,ready_fg);input clk;input wr;//write flag,with wr=1,one byte while be sent,and wr=0,stop to sendoutput reg dclk=0;//595latch clockoutput reg dain=0;//595serial data ininput[15:0]in_data;//the data have to been sentoutput reg busy=0;//busy flag,which figures that whether the new data can been send or not output reg ready_fg=0;//inner flagreg[15:0]in_buffer=0;reg[24:0]count_clk=0;//conter,which divide the clkreg[5:0]dat_num=0;//data number which controls the dlkparameter clk_div=2;//dclk divide timesalways@(posedge clk)beginif(!wr)ready_fg<=1'b1;//ready_flag is an inner flag which is used to write byte one bey oneelse beginif(!busy)begin//busy is an output value that shows the data have been sent,or notif(ready_fg)beginin_buffer<=in_data;//copy the data in to registerdclk<=1'b0;dain<=1'b0;busy<=1'b1;endendelse beginif(ready_fg)beginif(count_clk<clk_div)count_clk<=count_clk+1;//divide the sys clkelse begincount_clk<=0;if((dat_num%2)==0)begindain<=in_buffer[15];in_buffer<=in_buffer<<1;//put serial data on the dainendif(dat_num>0&&dat_num<33)dclk<=~dclk;//serial data lathced at the rising edge of this clkdat_num<=dat_num+1;if(dat_num>33)begindat_num<=0;busy<=1'b0;//signal figures that the data has been sentready_fg<=0;//this module inner flag which figures that this times is finished and will wait for wr lowendendendendendendEndmodule仿真测试文件:module counter_test;//Inputsreg clk;reg rst;//Outputswire dclk;wire dlk;wire dain;wire drst;//Instantiate the Unit Under Test(UUT)counter_top uut(.clk(clk),.dclk(dclk),.dlk(dlk),.dain(dain),.drst(drst),.rst(rst));initial begin//Initialize Inputsclk=0;rst=0;//Wait100ns for global reset to finish#100;rst=1;forever begin#10;clk=!clk;end//Add stimulus hereendendmodule5、uart串口通信实例电路部分Ucf文件:#Created by Constraints Editor(xc3s250e-vq100-4)-2011/01/16 NET"exclk"TNM_NET="exclk";TIMESPEC TS_exclk=PERIOD"exclk"20ns HIGH50%;#PlanAhead Generated physical constraintsNET"exclk"LOC=P83;NET"rst_p"LOC=P40;NET"button_n"LOC=P41;NET"button_s"LOC=P48;NET"rxd"LOC=P3;NET"txd"LOC=P2;NET"LED[0]"LOC=P24;NET"LED[1]"LOC=P26;NET"LED[2]"LOC=P27;NET"LED[3]"LOC=P32;NET"LED[4]"LOC=P33;NET"LED[5]"LOC=P34;NET"LED[6]"LOC=P35;NET"LED[7]"LOC=P36;#PlanAhead Generated IO constraintsNET"exclk"IOSTANDARD=LVCMOS33;NET"rst_p"IOSTANDARD=LVCMOS33;NET"button_n"IOSTANDARD=LVCMOS33; NET"button_s"IOSTANDARD=LVCMOS33; NET"rxd"IOSTANDARD=LVCMOS33; NET"txd"IOSTANDARD=LVCMOS33;NET"LED[0]"IOSTANDARD=LVCMOS33;NET"LED[1]"IOSTANDARD=LVCMOS33;NET"LED[2]"IOSTANDARD=LVCMOS33;NET"LED[3]"IOSTANDARD=LVCMOS33;NET"LED[4]"IOSTANDARD=LVCMOS33;NET"LED[5]"IOSTANDARD=LVCMOS33;NET"LED[6]"IOSTANDARD=LVCMOS33;NET"LED[7]"IOSTANDARD=LVCMOS33;Uart_top.v:module uart(exclk,rst_p,button_n,button_s,rxd,txd,LED);input exclk;input rst_p;//复位input button_n;//发送数加1input button_s;//回复初值input rxd;output txd;output[7:0]LED;//drive8LED on starter boardreg[7:0]LED=0;//define the led driver signal as reg wire[7:0]rx_dout;wire bclk;//波特率时钟wire tx_ready;//发送准备wire rx_ready;//接收准备wire bv1_posedge,bv2_posedge;reg[7:0]din=48;//输出数据reg[2:0]bv1,bv2;//寄存reg tx_cmd;//发送命令always@(posedge bclk)beginbv1<={bv1[1:0],button_n};bv2<={bv2[1:0],rx_ready};endassign bv1_posedge=(!bv1[2])&bv1[1];assign bv2_posedge=(!bv2[2])&bv2[1];always@(posedge bclk)beginif(button_s==1'b0)begindin<=48;tx_cmd<=1'b0;endelse beginif(bv1_posedge==1'b1)begindin<=din+1;tx_cmd<=1'b1&tx_ready;endelse begindin<=din;tx_cmd<=1'b0;endendendalways@(posedge bclk)beginif(bv2_posedge==1'b1)beginLED<=rx_dout;endendbaud_gen inst_baud_gen(.clk_50MHZ(exclk),.bclk(bclk));uart_tx inst_uart_tx(.bclk(bclk),.reset(rst_p),.tx_din(din),.tx_cmd(tx_cmd),.tx_ready(tx_ready),.txd(txd));uart_rx inst_uart_rx(.bclk(bclk),.reset(rst_p),.rxd(rxd),.rx_ready(rx_ready),.rx_dout(rx_dout) );endmodulebaud_gen.v波特率生成:module baud_gen(clk_50MHZ,bclk);input clk_50MHZ;output bclk;reg bclk=0;reg[9:0]cnt=0;always@(posedge clk_50MHZ)beginif(cnt>324)begincnt<=0;bclk<=1;endelse begincnt<=cnt+1;bclk<=0;endendendmoduleuart_tx.v发送部分:module uart_tx(bclk,reset,tx_din,tx_cmd,tx_ready,txd);input bclk;//send data colcokinput reset;//send data resetinput tx_cmd;//send the control commandinput[7:0]tx_din;//data prepared to sendoutput tx_ready;//data has been sentoutput txd;//serial data send from this wirereg tx_ready;//status of send dataparameter[3:0]Lfram=8;//8bit have to been sendparameter[2:0]s_idle=3'b000;//idleparameter[2:0]s_start=3'b001;//startparameter[2:0]s_wait=3'b010;//waitparameter[2:0]s_shift=3'b011;//shiftparameter[2:0]s_stop=3'b100;//stopreg[2:0]state=s_idle;reg[3:0]cnt=0;reg[3:0]dcnt=0;reg txdt;assign txd=txdt;always@(posedge bclk)beginif(!reset)beginstate<=s_idle;cnt<=0;tx_ready<=0;txdt<=1;endelse begincase(state)s_idle:begintx_ready<=1;cnt<=0;txdt<=1'b1;if(tx_cmd==1'b1)state<=s_start;elsestate<=s_idle;ends_start:begintx_ready<=0;txdt<=1'b0;state<=s_wait;ends_wait:begintx_ready<=0;if(cnt==4'b1110)begincnt<=0;if(dcnt==Lfram)beginstate<=s_stop;dcnt<=0;txdt<=1'b1;endelse beginstate<=s_shift;txdt<=txdt;endendelse beginstate<=s_wait;cnt<=cnt+1;endends_shift:begintx_ready<=0;txdt<=tx_din[dcnt];dcnt<=dcnt+1;state<=s_wait;ends_stop:begintxdt<=1'b1;if(cnt==4'b1110)beginstate<=s_idle;cnt<=0;tx_ready<=1;endelse beginstate<=s_stop;cnt<=cnt+1;endendendcaseendendendmoduleuart_rx.v接收部分:module uart_rx(bclk,reset,rxd,rx_ready,rx_dout);input bclk;//recieve data colockinput reset;//recieve data resetinput rxd;//wire for recieve dataoutput rx_ready;//recieve data ready signaloutput[7:0]rx_dout;//recieve data out putparameter[3:0]Lframe=8;//data lenthparameter[2:0]s_idle=3'b000;//idle statueparameter[2:0]s_sample=3'b010;//sample statueparameter[2:0]s_stop=3'b100;//stop statuereg rx_ready;reg[2:0]state=s_idle;reg[3:0]cnt=0;reg[4:0]num=0;reg[3:0]dcnt=0;reg[7:0]rx_doutmp=0;reg s_low=0;//test signal beginassign rx_dout=rx_doutmp;//core code for recieving dataalways@(posedge bclk)beginif(!reset)beginstate<=s_idle;cnt<=0;dcnt<=0;num<=0;rx_doutmp<=0;s_low<=0;endelse begincase(state)s_idle:beginrx_doutmp<=0;dcnt<=0;rx_ready<=1;if(cnt==4'b1111)begincnt<=0;s_low<=0;if(num>7)beginstate<=s_sample;num<=0;endelse beginstate<=s_idle;num<=0;endendelse begin/*cnt<=cnt+1;if(rxd==1'b0)beginnum<=num+1;endelse beginnum<=num;end*/if(rxd==1'b0)beginnum<=num+1;s_low<=1;endelse beginnum<=num;endif(s_low)begincnt<=cnt+1;endelse begincnt<=0;endendends_sample:beginrx_ready<=1'b0;if(dcnt==Lframe)beginstate<=s_stop;endelse beginstate<=s_sample;if(cnt==4'b1111)begindcnt<=dcnt+1;cnt<=0;if(num>7)beginnum<=0;rx_doutmp[dcnt]<=1;endelse beginrx_doutmp[dcnt]<=0;num<=0;endendelse begincnt<=cnt+1;if(rxd==1'b1)beginnum<=num+1;end。