可编程逻辑器件

可编程逻辑器件

可编程逻辑器件1. 引言可编程逻辑器件(Programmable Logic Devices,PLD)是一种数字电路器件,具有可编程功能,广泛应用于数字系统设计、逻辑电路实现和协议转换等领域。

本文将介绍可编程逻辑器件的基本原理、分类以及应用。

2. 基本原理可编程逻辑器件的基本原理是利用可编程存储单元和可编程逻辑电路的组合,实现逻辑功能的编程。

具体来说,可编程逻辑器件包括可编程存储器、可编程逻辑阵列(PLA)以及输入/输出引脚等部分。

可编程存储器用于存储逻辑功能的真值表或逻辑方程式,其中包含了输入和输出的对应关系。

可编程逻辑阵列则通过内部的可编程互连结构,将存储器中的逻辑功能与输入/输出引脚相连。

通过对存储器中的编程操作,可以改变逻辑功能的实现方式,实现不同的逻辑功能。

3. 分类可编程逻辑器件根据内部的可编程结构和逻辑功能的实现方式,可以分为以下几类:3.1 可编程逻辑阵列(Programmable Logic Array,PLA)可编程逻辑阵列是最早的一种可编程逻辑器件,由与门阵列和与非门阵列组成。

通过对阵列中的与门和与非门进行编程,可以实现各种逻辑功能。

3.2 可编程数组逻辑器件(Programmable Array Logic,PAL)可编程数组逻辑器件也是由与门阵列和与非门阵列组成,但与可编程逻辑阵列不同的是,输入信号经过可编程与门和与非门后会经过输出或。

可编程数组逻辑器件提供了更灵活的逻辑功能组合方式。

3.3 可编程逻辑器件阵列(Field Programmable Logic Arrays,FPLA)可编程逻辑器件阵列是一种结合了PAL和双向通用门阵列(GAL)的结构,具有更高的逻辑资源和更灵活的编程方式,可实现更复杂的逻辑功能。

3.4 可编程门阵列(Programmable Gate Array,PGA)可编程门阵列是一种将逻辑门和触发器直接编程的逻辑器件,具有非常高的逻辑资源和灵活性,适用于设计复杂的数字逻辑电路。

可编程逻辑器件

可编程逻辑器件1. 引言可编程逻辑器件(PLD)是一种集成电路芯片,具有可编程逻辑和存储功能。

它能够根据用户的需求和特定的逻辑功能进行编程,并实现电路和逻辑功能的实现。

PLD在计算机和电子领域具有广泛的应用,如数字逻辑设计、自动控制系统、通信系统等。

本文将介绍可编程逻辑器件的基本原理、应用以及未来的发展趋势。

2. 可编程逻辑器件的分类根据可编程逻辑器件的不同结构和编程方式,可以将其分为以下几类:2.1 可编程逻辑阵列(PLA)可编程逻辑阵列是最早出现的可编程逻辑器件之一。

它由与非门、或非门和与非门组成,并且每个门都可以通过编程电路连接或断开。

PLA的编程方式是通过将引脚与晶体管交叉连接来实现,从而实现特定的逻辑功能。

2.2 可编程数组逻辑器件(PAL)可编程数组逻辑器件是一种常见的可编程逻辑器件。

它由程序控制逻辑(PCL)和逻辑阵列(LA)组成。

PCL用于将输入信号和编程线信号转换为逻辑阵列中的选择信号,从而实现特定的逻辑功能。

2.3 可编程逻辑阵列和可编程互连器件(PLD)可编程逻辑阵列和可编程互连器件(PLD)是一种通用的可编程逻辑器件。

它由可编程逻辑阵列、可编程互连矩阵和输入/输出功能单元组成。

PLD可以通过编程将逻辑功能和输入/输出信号连接起来,实现特定的逻辑功能。

PLD在可编程逻辑器件中具有更大的灵活性和可扩展性。

3. 可编程逻辑器件的原理和工作方式可编程逻辑器件的工作原理是将逻辑功能用布尔代数的形式描述,并编写一个与之对应的逻辑方程。

通过对逻辑方程进行编程,将输入信号与逻辑方程中的变量相连接,从而实现特定的逻辑功能。

对于PLA和PAL这类可编程逻辑器件,由于它们的结构比较简单,编程方式主要是通过某种特定形式的编码方式来实现。

而对于PLD这种通用的可编程逻辑器件,由于其结构较为复杂,编程方式则更加灵活。

可以通过硬件编程语言(如VHDL)或可视化编程工具进行编程,使得逻辑功能的实现更加方便和灵活。

可编程逻辑器件(PLD)

PLD开发工具提供了完整的解决方案,包括设计输入、综合、布局布线、仿真和调试等功能。这些工 具支持多种PLD器件和编程语言,使得设计师能够高效地实现数字电路设计和PLD编程。

05

PLD的未来发展与挑战

PLD的未来发展趋势

更高的集成度

随着半导体工艺的进步,PLD将实现更高的集成度,具备更强大 的计算和数据处理能力。

现代阶段

随着技术不断发展,PLD 的集成度更高,功能更强 大,应用领域更广泛。

PLD的应用领域

通信领域

用于实现通信协议的转换、信号处理和调制 解调等功能。

工业控制

用于实现自动化控制、电机驱动和传感器数 据处理等功能。

数字信号处理(DSP)

用于实现图像处理、语音识别和数字信号处 理算法。

计算机硬件设计

安全与可靠性问题

随着PLD在关键领域的应用增加, 安全和可靠性问题成为关注的焦 点,需要加强安全机制和可靠性 设计。

知识产权保护

随着PLD技术的不断进步和应用 领域的拓展,知识产权保护成为 重要问题,需要加强知识产权保 护措施。

PLD的发展前景与展望

拓展应用领域

随着PLD技术的不断成 熟,其应用领域将进一 步拓展,尤其是在人工 智能、物联网、5G等领 域。

布线策略

选择合适的布线策略,确 保信号传输的可靠性和效 率。

物理验证

检查布局和布线后的设计 是否满足时序和功耗要求。

配置与下载

生成配置文件

根据设计结果,生成用于配置PLD的二进制 文件。

下载与配置

将配置文件下载到PLD中,完成硬件电路的 配置。

测试与验证

在实际硬件环境中测试设计的正确性和性能。

04

复杂可编程逻辑器件(CPLD)

可编程逻辑器件的应用与开发

可编程逻辑器件的应用与开发可编程逻辑器件(PLD)是一种集成电路设备,可以用于实现逻辑逻辑功能、存储数据和执行控制任务。

PLD 的应用范围广泛,并在许多领域发挥着重要作用。

本文将介绍 PLD 的基本概念,探讨其应用和开发过程。

一、PLD 的基本概念1.1 什么是可编程逻辑器件?可编程逻辑器件是一种电子器件,具有可配置的逻辑功能。

其内部包含了一系列逻辑门和存储器单元。

PLD 具有很高的可编程性,可以根据用户的需求进行逻辑设计和功能定义。

1.2 PLD 的分类主要有可编程逻辑阵列(PLA)、可编程阵列逻辑器件(PAL)、复杂可编程逻辑器件(CPLD)和可编程门阵列(PGA)等。

二、PLD 的应用2.1 数字电子设备PLD 用于设计和实现数字电子设备,如计算机、摄像机、音频设备、显示器等。

通过配置 PLD 的逻辑功能,可以实现不同的数字信号处理和控制任务。

2.2 通信系统PLD 可以用于设计和开发各种通信系统,如网络路由器、无线通信设备、调制解调器等。

通过调整 PLD 的配置和逻辑功能,可以满足不同通信标准和协议的要求。

2.3 工业自动化PLD 在工业自动化领域也得到广泛应用。

它可以用于控制和监测各种工业设备,如机器人、生产线、传感器等。

PLD 的可编程性和灵活性使得工业自动化系统更加高效和可靠。

2.4 医疗设备PLD 可以用于设计和制造各种医疗设备,如心脏起搏器、医学成像设备等。

通过编程 PLD 的逻辑功能,可以实现不同的医疗检测和治疗任务。

三、PLD 的开发过程3.1 硬件描述语言PLD 的开发通常使用硬件描述语言(HDL),如VHDL(Very High Speed Integrated Circuit Hardware Description Language)或者Verilog。

这些语言允许工程师以一种类似于编程的方式来描述PLD的逻辑功能。

3.2 设计与仿真在 PLD 开发过程中,首先需要进行设计和仿真。

可编程逻辑器件

可编程逻辑器件概述可编程逻辑器件(Programmable Logic Devices,简称PLD)是指由用户通过编程方式改变其内部逻辑功能的数字集成电路。

它们采用了现代电子技术,运用数字信号处理、计算机辅助设计技术等手段,可通过对其内置的逻辑单元进行编程和重新配置,以实现不同的逻辑功能。

PLD在数字系统的设计和开发中起着举足轻重的作用。

分类相关概念在介绍具体的PLD分类之前,我们先了解一些相关概念:•PAL(Programmable Array Logic):可编程阵列逻辑器件。

•GAL(Generic Array Logic):通用阵列逻辑器件,是PAL 的改进型。

•PLA(Programmable Logic Array):可编程逻辑阵列。

•FPGA(Field Programmable Gate Array):现场可编程门阵列。

PALPAL是PLD最早的一种形式。

它由与门阵列和或门阵列构成,可通过烧写如与非逻辑的方程表来实现逻辑功能。

GALGAL是PAL的改进版本。

GAL采用重新可编程的逻辑单元而不是方程表来实现逻辑功能。

这意味着它可以多次编程,更具有灵活性。

PLAPLA是通过将与门矩阵与或门矩阵连接在一起形成的。

与PAL类似,PLA也使用方程表来实现逻辑功能。

FPGAFPGA是目前应用最广泛的PLD。

它由逻辑单元、可编程互连资源和I/O单元构成。

逻辑单元通过可编程互连资源进行连接,从而实现所需的逻辑功能。

应用领域数字系统设计PLD广泛应用于数字系统的设计中。

它们被用来实现各种逻辑功能,如计算机、通信设备、消费电子产品等的控制逻辑、数据处理和通信接口。

逻辑分析仪在测试和调试电子系统时,逻辑分析仪经常使用PLD来实现信号采集和分析功能。

通过编程控制PLD,我们可以在逻辑分析仪中实现不同的信号采集和触发功能,方便对系统进行故障分析和调试。

自动化控制PLD也被广泛应用于自动化控制领域。

通过编程控制PLD,我们可以实现各种自动化控制系统的功能,如工业过程控制、机器人控制、家居自动化等。

可编程逻辑器件及应用

可编程逻辑器件及应用可编程逻辑器件(PLD)是一种电子器件,能够根据用户的需求和程序逻辑实现不同的功能。

它们被广泛应用于数字电路设计、自动化控制系统和嵌入式系统等领域。

本文将深入探讨可编程逻辑器件的原理、分类、优势及其在各个领域的应用。

一、可编程逻辑器件的原理可编程逻辑器件的核心是可编程逻辑阵列(PLA)或可编程逻辑门阵列(PLGA)。

它由一系列基本逻辑门(如与门、或门和非门)和可编程的互连网络组成。

用户可以通过编程器将逻辑功能和互连关系编程到可编程逻辑阵列中,从而实现特定的逻辑功能。

二、可编程逻辑器件的分类根据实现的逻辑功能不同,可编程逻辑器件可以分为可编程逻辑阵列(PLA)、可编程阵列逻辑器件(PAL)、复杂可编程逻辑器件(CPLD)和现场可编程门阵列(FPGA)等几个主要类别。

1. 可编程逻辑阵列(PLA)可编程逻辑阵列(PLA)是最早出现的可编程逻辑器件之一。

它具有灵活的结构和编程方式,可以实现复杂的逻辑功能。

PLA的主要特点是可编程的输入和输出逻辑功能以及可编程的互连关系。

2. 可编程阵列逻辑器件(PAL)可编程阵列逻辑器件(PAL)与PLA类似,但它的输入逻辑功能是固定的,只有互连关系是可编程的。

PAL的制造成本较低,适合一些较简单的逻辑功能应用。

3. 复杂可编程逻辑器件(CPLD)复杂可编程逻辑器件(CPLD)是可编程逻辑器件的进一步发展。

CPLD通过集成多个可编程逻辑阵列和可编程互连网络,能够实现更复杂的逻辑功能。

CPLD具有较高的灵活性和可扩展性。

4. 现场可编程门阵列(FPGA)现场可编程门阵列(FPGA)是最灵活和最强大的可编程逻辑器件。

FPGA由大量可编程逻辑块(CLB)、可编程互连网络和输入/输出模块组成。

它可以根据用户的需求和程序逻辑实现几乎任何逻辑功能。

三、可编程逻辑器件的优势可编程逻辑器件相比于固定功能的逻辑器件具有以下几个优势:1. 灵活性:可编程逻辑器件可以根据用户的需求进行编程,实现不同的逻辑功能。

第六章可编程逻辑器件

8.2.2 GAL的结构

CP VCC

IN

GND

1 20 2 (GAL16V8) 19 3 18 4 17 5 16 15 6 14 7 13 8 12 9 10 11

I/O

EN

1

1 26 30 10 12 14 16 18 20 22 24 26 28 303 4 567 8 9101112 14 161718 20 22 242527282931 012 13 15 19 21 23 0 1 2 3 4 5 6 7 8 9 11 13 15 17 19 21 23 25 27 1 29 31 0 19

M

* AC AC1(m)

0

接零级输出

OE

OLMC的结构

CLOCK

AC1(n)

GAL器件的编程:

对GAL器件进行编程,硬件环境需要有一台计算机, 另外还要配置一套GAL开发器。经过以下几步:

1.首先按逻辑要求选择器件类型,主要考虑输入输出 管脚数量。 2.选择一种合适的编程软件如FM、ABEL、CUPL、原 理图等编制相应的源文件。 3.上机调试源文件后,经过相应的编译程序生成XX.JED (熔丝图文件)。 4.将编程器和计算机连接,利用编程下载文件对GAL编 程。GAL被编程后,还可利用检验程序对所写内容进行检 验,准确无误后对GAL加密。

27 28 29 30 31

(19)

OLMC

(18)

17

16 17 18 19 20 21 22 23 4 24 25 26 27 28 29 30 31 5

OLMC

(17)

16

18

OLMC

(16)

33 35 37 39 6

32 34 36 38

可编程逻辑器件

可编程逻辑器件可编程逻辑器件(Programmable Logic Devices,简称PLDs)是一种广泛应用于数字电路设计中的集成电路元件。

通过配置,PLDs可以实现各种逻辑功能,从简单的门电路到复杂的数码系统。

PLDs的灵活性和可编程性使得它们成为数字系统设计中不可或缺的组成部分。

PLD的基本原理PLDs由可编程逻辑阵列(PAL)、可编程阵列逻辑器件(PAL)和复杂可编程逻辑器件(CPLD)等几种类型组成。

这些器件包含大量的逻辑门和触发器,用户可以通过编程软件将这些逻辑资源连接在一起,实现特定的逻辑功能。

PLDs的编程可以通过硬件描述语言(HDL)或专门的编程工具完成。

PLD的优势1.灵活性:PLDs可以根据设计需求进行重新编程,而无需更换硬件。

2.快速开发:通过使用PLDs,设计人员可以快速验证设计概念并快速上市。

3.低成本:PLDs的生产成本相对较低,可以有效降低数字系统设计的总体成本。

4.集成度高:PLDs中集成了大量的逻辑资源,可以替代多个离散器件,减小系统的体积和功耗。

PLD的应用领域PLDs在许多领域中得到广泛应用,包括但不限于:•通信:PLDs被用于设计各种通信设备中的数字处理部分,如路由器、交换机等。

•工业控制:PLDs可以用于实现工业控制系统中的逻辑控制功能,提高系统的稳定性和灵活性。

•消费电子:PLDs常被应用于消费电子产品中,如电视、音响等,以实现功能的定制和更新。

•汽车电子:PLDs在汽车电子系统中扮演着重要的角色,可以用于实现车载娱乐系统、发动机控制等功能。

结语可编程逻辑器件(PLDs)作为数字电路设计的重要组成部分,具有灵活性、快速开发、低成本和高集成度等优势,在通信、工业控制、消费电子和汽车电子等领域具有广泛的应用前景。

随着技术的不断进步,PLDs将继续发挥重要作用,为数字系统设计带来更大的便利和创新。

可编程逻辑器件

结构基于SRAM查找表,采用RAM“数据”查找的方式,用

SRAM(静态随机存储器) 来构成逻辑函数发生器。

上一页 下一页 返回

3.1 可编程逻辑器件概述 Nhomakorabea一个N输入查找表(LUT)可以实现N个输入变量的任何逻辑功

能,如N输入“与”、N输入“异或”等。图3-2所示为4输入LUT,

其内部结构如图3-3所示。

Altera是著名的PLD生产器件厂商,多年来一直占据着行业领先的

地位。Altera公司可编程逻辑器件具有高性能、高集成度和高性价比的

优点,此外它还提供功能全面地开发工具和丰富的IP核、宏功能库等。

因此Altera的产品获得了广泛的应用。

Altera公司的可编程逻辑器件产品有多个系列。按照推出的先后顺

序依次为Classic系列、MAX(Multiple Array Matrix)系列、FLEX

(Flexible Logic Element Matrix)系列、APEX(Advanced Logic

Element Matrix)系列、ACEX系列、APEXⅡ系列、Cyclone系列、

Stratix系列、MAXⅡ系列、CycloneⅡ系列和StratixⅡ系列。

1)熔丝(Fuse)型器件。早期的PROM器件就是采用熔丝结构的, 编程过程就是根据设计的熔丝图文件来烧断对应的熔丝,达到编程的目 的。

2)反熔丝(Antifuse)型器件。对熔丝技术的改进,在编程处通过 击穿漏层使得两点之间获得导通,这与熔丝烧断获得开路正好相反。某 些FPGA器件采用了此种编程方式,如Xilinx公司的XC5000系列器件和 Actel的FPGA器件。

下一页 返回

3.2 Altera公司系列器件简介

可编程逻辑器件

现

可场

编 程 逻

可 编 程 门

辑阵

器列

件(

)

1.4

FPGA

阅读天地

EDA技术 EDA是电子设计自动化的英文缩写,20世纪60年 代中期从计算机辅助设计(CAD)、计算机辅助制造 (CAM)、计算机辅助测试(CAT)和计算机辅助 工程(CAE)的概念发展而来的。 在电子技术设计领域,电子设计师可以利用EDA 工具,从概念、算法、协议等开始设计电子系统,大 量工作可以通过计算机完成。将电子产品从电路设计、 性能分析到 设计出IC版图或PCB版图的整个过程交由计算机 自动处理完成。EDA技术的出现,极大地提高了电路 设计的效率和可操作性,减轻了设计者的劳动强度。

可

结构、可编程I/O输出结构、寄存器型输出结构和异或型输出结构。PLA器件是在

编

FPLA器件之后第一个具有典型实用意义的可编程逻辑器件。

程可

PLA和SSI,MSI通用标准器件相比有以下许多优点:

逻编

① 提高了功能密度,节省了空间。

辑程

器 件

逻 辑 阵

② 提高了设计的灵活性,且编程和使用都比较方便。 ③ 有上电复位功能和加密功能,可以防止非法复制。

电 工 电 子 技 术

过渡页

第2页

可编程逻辑器件

• 1.1 可编程逻辑阵列PLA • 1.2 通用阵列逻辑(GAL) • 1.3 低密度可编程逻辑器件 • 1.4 现场可编程门阵列(FPGA)

第3页

可编程逻辑阵列PLA(programmable logic array)的基本组成部分是与阵列(

可编程)和或阵列(固定,不能编程)。常有四种基本结构:专用输出基本门阵列

第8页

电 工 电 子 技 术

可编程逻辑器件及应用 弗洛伊德

可编程逻辑器件及应用弗洛伊德一、什么是可编程逻辑器件?可编程逻辑器件(Programmable Logic Device,PLD)是一种数字电路设备,它可以被编程以执行特定的逻辑功能。

PLD通常由可重构的门阵列(Reconfigurable Gate Array,RGA)和可编程互连网络组成。

PLD具有高度灵活性和可重构性,可以在不改变硬件的情况下实现不同的功能。

二、PLD的分类1. 静态RAM(SRAM)型PLD:SRAM型PLD通常由一个或多个互连的SRAM单元组成。

这些单元可以被编程以实现特定的逻辑功能。

由于SRAM型PLD采用了静态存储器作为配置存储器,因此它们可以通过重新配置来实现不同的功能。

2. 可编程逻辑阵列(Programmable Logic Array,PLA)型PLD:PLA型PLD通常由两个矩阵组成:输入矩阵和输出矩阵。

输入矩阵将输入信号转换为内部信号,并将其传递到输出矩阵中进行处理。

输出矩阵将内部信号转换为输出信号,并将其发送到外部环境中。

3. 可编程数组逻辑器件(Programmable Array Logic,PAL)型PLD:PAL型PLD通常由一个可编程的逻辑阵列和一个可编程的输出阵列组成。

可编程逻辑阵列用于实现特定的逻辑功能,而可编程输出阵列用于将内部信号转换为输出信号。

4. 可编程门阵列(Programmable Gate Array,PGA)型PLD:PGA型PLD通常由一组互连的门电路组成。

这些门电路可以被重新配置以实现不同的逻辑功能。

三、PLD的应用1. 逻辑控制器:PLD可以用于实现各种逻辑控制器,例如时序控制器、状态机等。

2. 数字信号处理:PLD可以用于实现各种数字信号处理算法,例如滤波、FFT等。

3. 数字电路设计:PLD可以用于快速原型设计和验证数字电路。

4. 自动化控制系统:PLD可以用于实现各种自动化控制系统,例如温度控制、压力控制等。

5. 人工智能:PLD可以用于实现各种人工智能算法,例如神经网络、模糊逻辑等。

第2章 可编程逻辑器件

尽管用PLA实现逻辑电路的效率远远高于PROM,但PLA也有不足之处,主要是与阵列和或阵列均采用可编程开关,而可编程开关需占用较多的芯片面积,并会引入较大的信号延时,因此,PLA的结构不利于提高器件的集成度和工作速度。20世纪70年代出现了可编程阵列逻辑PAL。PAL是Programmable Array Logic的缩写,即可编程阵列逻辑。PAL也是PLD的一种,采用“与”、“或”阵列结构,但是与PROM 不同,PAL的“或”阵列是固定的,而“与”阵列则是可以编程的。随着VLSI技术的不断发展和提高,允许设计规模较大的“与”阵列。因此PAL为用户对“与”阵列编程带来了很大方便。在逻辑表达式中一般可以简化到几个积项,很少超过8个。所以在PAL中,每一个或 门输入最多可以有8个乘积项,ic Array Logic的缩写,即通用可编程阵列逻辑。对应很多简单的数字逻辑,GAL等简单的可编程逻辑器件仍然被大量使用。目前,国内外很多对成本十分敏感的设计都在使用GAL等低成本可编程逻辑器件,越来越多的74系列逻辑电路被GAL取代。GAL等器件发展至今已经近20年了,新一代的GAL器件以功能灵活、小封装、低成本、重复可编程、应用灵活等优点仍然在数字电路领域扮演着重要的角色。目前比较大的GAL器件供应商主要是Lattice半导体公司。PAL器件的发展,给逻辑设计带来了很大的灵活性,但是它所提供的灵活性是有限的,不同的输出结构需要选用不同型号的PAL器件。此外,PAL的编程元件是熔丝,一旦编程以后不能再修改,因此,限制了PAL的广泛应用。20世纪80年代,Lattice公司推出了通用阵列逻辑(GAL),采用 EECMOS工艺,可以反复修改和再次编程。GAL器件在可编程阵列 逻辑的基础上,增加了输出逻辑宏单元OLMC(Output Logic MacroCell),使得GAL的特性和使用灵活性大大优于PAL,成为目前为止使用最广泛的简单PLD器件。

数字电路可编程逻辑器件

目前旳电子设备,单纯用模拟电路实现旳少, 一般都是:

薄弱信号放大 高速数据采集 大功率输出

采用模拟电路

信号处理 控制

采用数字电路 CPU, MEMORY,PLD

以至目前许多电子系统仅由三种原则器件构成: 1. CPU 微处理器 2. MEMORY 存储器 3.CPLD 、FPGA 可编程器件

可使某些时序电路设计得到简化

PAL

5。算术选通反馈型构造 在带异或旳寄存器型构造基础上,将输入 信号B与反馈信号A经算术选通后,再加到 与阵列旳输入端。

用于实现加、减、不小于、不不小于等算术运算

A

B

&1

算

& A+B

术

&A

选

通

& AB

&amAB

PAL

6.异步可编程寄存器输出型构造 器件内部旳D触发器旳CP端、S端与R端 均由专用乘积项单独编程控制。而D端旳电平 由极性控制输入决定。

Z=A+C+E

§10.2 可编程阵列逻辑(PAL) 可编程与阵列、固定旳或阵列和输出反馈 单元构成。沿用了prom中旳熔丝式双极型 工艺。它又分为:

PAL

1。基本与或阵列型

PAL

2。可编程输入/输出型

它具有三态输出缓冲器和反馈缓冲器。因而 1〕可构成简朴旳触发器 2〕输入输出端旳数目可根据实际需要来配 置即提供双相输入/输出功能.

ICR ---In Circuit Reconfigurability

此类器件利用SRAM存储信息,不需要在编 程器上编程,可直接在PCB上对器件编程. 一般编程信息存于外附加旳EPROM,E2PROM 或软硬盘上,在系统工作之前,先将存于器件外 旳编程信息输入到器件内旳SRAM里,然后器件 才开始工作.

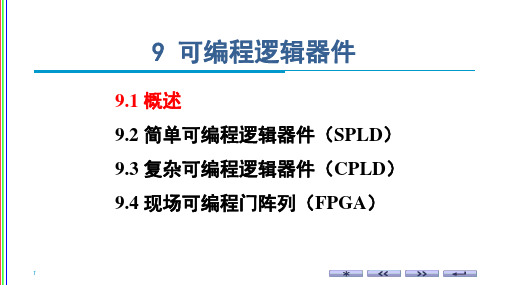

数字电路与逻辑设计(第三版)课件:可编程逻辑器件

在 20 世纪 80 年代初,可编程器件和 ASIC 芯片之间存在 较大的集成度和性能的差距。SPLD 器件和 CPLD 器件具有 很高的可编程性,它们的设计和修改时间都很短,但这些器件 的集成度都较低,无法实现更加复杂的功能。与此相反, ASIC 芯片实现了极高的集成度和复杂的功能,但 ASIC 芯片的价格 十分昂贵,其设计与生产周期也很长。 ASIC 芯片一旦在硅片 上实现,就是不可改变的。

可编程逻辑器件

图 6-13 CPLD 器件和 FPGA 器件的体系结构比较

可编程逻辑器件

在集成度不高的设计中, CPLD 器件往往以价格优势取 胜,而在更高集成度的设计中,FPGA 器件则以较低的总体逻 辑开销取胜。

可编程逻辑器件

6. 4. 2 FPGA 器件的特征 典型的 FPGA 器件的特征参数如表 6-2 所示。随着半导

可编程逻辑器件

6. 2. 1 PROM 器件 第一种 SPLD 器件是 PROM 器件。 PROM 器件于 1970

年问世,主要用来存储计算机的程序指令和常数,但设计人员 也利用 PROM 来实现查找表和有限状态机等一些简单的逻 辑功能。实际上,利用 PROM 器件可以方便地实现任意组合 电路,这是通过一个固定的与阵列和一个可编程的或阵列组 合来实现的。一个具有三输入、三输出的未编程 PROM结 构如图 6-4 所示。在该结构中,与阵列固定地生成所有输入 信号的逻辑小项,而或阵列则通过编程,实现任意小项之和。

EDA第2章-可编程逻辑器件

存储器的读写操作由地址信 号控制,通过地址解码器选 通对应的存储单元进行读写 操作。

存储器的容量和速度是衡量 其性能的重要指标,在数字 电路设计中广泛应用于数据 存储和程序存储等方面。

03

可编程逻辑器件的设计流程

设计输入

01

02

03

硬件描述语言

使用如VHDL或Verilog等 硬件描述语言进行设计输 入,描述电路的结构和行 为。

多次可编程类型的PLD可以在制造完 成后进行多次编程,用户可以通过编 程语言对器件进行配置和重构。

OTP类型的PLD在制造完成后无法更 改,需要通过特定的编程设备进行配 置。

可编程逻辑器件的应用

01

02

03

04

PLD在数字系统设计中具有广 泛的应用,如数字信号处理、

图像处理、通信等领域。

在数字信号处理中,PLD可以 用于实现滤波器、编码器等算

当触发器的输入信号发生变化 时,触发器会从当前状态翻转 到另一个状态,并保持该状态 直到再次受到输入信号的改变 。

触发器在数字电路设计中具有 重要作用,用于实现寄存器、 计数器等基本功能。

寄存器的工作原理

01

寄存器(Register)是一种可编程 逻辑器件中的存储元件,用于存储 二进制数据。

02

寄存器由多个触发器组成,可以 同时存储多个二进制位。

面临的挑战

设计和编程难度

随着可编程逻辑器件的规模不断扩大,设计和编 程的难度也在逐渐增加。

知识产权保护

可编程逻辑器件的设计涉及大量的知识产权,如 何保护知识产权成为行业面临的重要问题。

可靠性和稳定性

随着可编程逻辑器件的应用范围越来越广,其可 靠性和稳定性成为关键问题。

可编程逻辑器件

可编程逻辑器件一、PLD简介可编程逻辑器件(PLD),它能够完成各种数字逻辑功能。

典型的PLD由一个〝与〞门和一个〝或〞门阵列组成,而任意一个组合逻辑都能够用〝与—或〞表达式来描述,因此, PLD能以乘积和的形式完成大量的组合逻辑功能。

它有如下特点:1、逻辑电路的设计和测试均可在运算机上实现,设计成功的电路可方便的下载到PLD,因而可研制周期短、成本低、效率高,使产品能在极短时刻内推出。

2、用PLD实现的电路容易被修改。

这种修改通过PLD重新编程实现,能够不阻碍其外围电路。

因此,其产品的爱护、更新都专门方便。

PLD使硬件也能象软件一样实现升级,因而被认为使硬件革命。

3、较复杂的数字系统能用1片或数片PLD实现,因而,应用PLD生产的产品轻小可靠。

此外,PLD还具有硬件加密功能。

4、应用PLD设计电路时,需选择合适的软硬件平台〔开发系统〕。

因此,PLD得到广泛的应用。

二、PLD的分类按照PLD的结构体系,要紧可分为简单PLD〔包括PAL、GAL等〕、CPLD和FPGA。

PAL:Programmable Array Logic 可编程阵列逻辑GAL:Generic Array Logic 通用阵列逻辑CPLD:Complex Programmable Logic Device 复杂可编程逻辑器件FPGA:Field Programmable Gate Array现场可编程门阵列另外,最早使用的PLD是FPLA(Field Programmable Logic Array)现场可编程逻辑阵列,它的与、或阵列均可编程,现在差不多专门少使用。

EPLD是可擦除的可编程逻辑器件Erasable Programmable Logic Device的缩写。

有的资料把可擦除的PLD都统称为EPLD,但更一样的是指继PAL、GAL之后推出的一代集成度远高于PAL、GAL,但相对CPLD和FPGA较低的可擦除的可编程逻辑器件。

可编程逻辑器件

改进了输出电路结构,通过编程,可以 将输出结构配置成多种不同的电路。

输 入

输 入 电 路

与 阵 列

或 阵 列

输 出 电 路

输 出

33

以GAL16V8为例

GAL16V8结构框图

时钟输入缓冲器

输入缓冲器,产生8 对两两互补的变量

反馈/输入缓冲器,产 生8对两两互补的变量

输出使能控制信 号的输入缓冲器

A A

A

三态输出缓冲器

A

A

EN

A

A

EN

13

3. SPLD中的编程连接技术

熔丝工艺

A

B

C

D

VCC

0

R

L0

熔丝

L ABCD

A

B

熔丝

C

D

VCC

R

L

A BC D

L L AC

14

SPLD中的编程连接技术

可编程的叠栅(浮栅)MOS管

A

B

C

╳

T1

T2

T3

编程为断 开状态

VCC

D R L

╳

T4 编程为断

开状态

0

Q

D

1

Q

>

Q

反馈选择器

FMUX 10 11 01 00

10

OMUX 输出选

择器

I/O (n)

AC0 AC1(m) AC1(n)

CLK

来自相邻 级输出(m)

OE

42

以GAL16V8为例

OLMC

编程后的等效逻辑电路:一种时序型输出

OLMC(n)

至相邻级的 FMUX 输入

PT1 来自 与阵列

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

可编程逻辑器件报告物理与机电工程学院电气工程及其自动化黄健19920102203335交通灯控制器设计任务与要求在十字路口,每条道路各有一组红、黄、绿灯和倒计时显示器,用以指挥车辆和行人有序地通行。

其中,红灯(R)亮,表示该条道路禁止通行;黄灯(Y)亮,表示停车;绿灯(G)亮,表示可以通行。

倒计时显示器是用来显示允许通行或禁止通行时间。

交通灯控制器就是用来自动控制十字路口的交通灯和计时器,指挥各种车辆和行人安全通行。

(1)在十字路口的两个方向上各设一组红、绿、黄灯,显示顺序为其中一方向(东西方向)是绿灯、黄灯、红灯;另一方向(南北方向)是红灯、绿灯、黄灯。

(2)设置一组数码管,以倒计时的显示方式允许通行或禁止通行的时间,其中绿灯、黄灯、红灯的持续时间分别是20s、5s、和25s。

(3)当各条路上任意一条上出现特殊情况时,如当消防车、救护车或其他需要优先放行的车辆通过时,各方向上均是红灯亮,倒计时停止,显示数字在闪烁。

当特殊运行状态结束后,控制器恢复原来状态,继续正常运行。

(4)用两组数码管实现双向倒计时显示。

交通灯控制器的核心范围是一个计数范围为0~49共(50秒)的计数器和一个根据计数值做出规定反映的控制器。

另外,还需要输入CLK时钟信号。

最后,要驱动七段数码管,显然还需要一个译码电路。

交通灯控制器原理图设计方案交通灯控制器的核心范围是一个计数范围为0~49共(50秒)的计数器和一个根据计数值做出规定反映的控制器。

另外,作者所用的实验仪配备的晶振为20MHZ,因此还需要一个分频电路。

最后,要驱动七段数码管,显然还需要一个译码电路。

交通灯控制器系统框图设计实现与仿真结果计数器的设计这里需要的计数器的计数范围为0~49。

计到49后,下一个时钟沿恢复到0,开始下一轮计数。

此外,当检测到特殊情况(hold=1)发生时,计数器暂停计数,而系统恢复信号则使计数器异步清0。

计数器的程序library ieee;use ieee.std_logic_1164.all;entity counter isport(clock:in std_logic;reset:in std_logic;hold:in std_logic;countnum: buffer integer range 0 to 49);end;architecture behavior of counter isbeginprocess(reset,clock)beginif reset='1' thencountnum<=0;elsif rising_edge(clock) thenif hold='1' then ——当出现紧急情况时,计数器暂停计数countnum<=countnum;elseif countnum=49 thencountnum<=0;elsecountnum<=countnum+1;end if;end if;end if;end process;end;交通灯计数器波形图交通灯计数器波形图控制器的设计控制器的作用是根据计数器控制发光二极管的亮、灭,以及输出倒计时数值给七段数译管的分位译码电路。

此外,当检测到特殊情况时,无条件点亮红色的发光二极管。

由于控制器要对于数值进行判断,很容易想到用IF 语句来实现。

本设计采用利用时钟沿的下降沿读取前级计数器的计数植,然后做出反应。

控制器符号框图控制器的程序library ieee;use ieee.std_logic_1164.all;entity controller isport(clock:in std_logic;hold:in std_logic;countnum:in integer range 0 to 49; ——前级计数器的计数值numa,numb:out integer range 0 to 25; ——倒计时数值的计数值reda,greena,yellowa:out std_logic; ——控制东西方向红黄绿灯的亮灭redb,greenb,yellowb:out std_logic; ——控制南北方向红黄绿灯的亮灭flash:out std_logic); ——用以指示七段数码管显示数字的闪烁end;architecture behavior of controller isbeginprocess(clock)beginif falling_edge (clock) then ——计数器是上升沿改变计数值,此处下降沿读取if hold='1' thenreda<='1';redb<='1';greena<='0';greenb<='0';yellowa<='0';yellowb<='0';flash<='1';elseflash<='0';if countnum<=19 thennuma<=20-countnum; ——计数器东西方向倒计时reda<='0';greena<='1';yellowa<='0';elsif (countnum<=24) thennuma<=25-countnum;reda<='0';greena<='0';yellowa<='1';elsenuma<=50-countnum;reda<='1';greena<='0';yellowa<='0';end if;if countnum<=24 then ——计数器南北方向倒计时numb<=25-countnum;redb<='1';greenb<='0';yellowb<='0';elsif countnum<=44 thennumb<=45-countnum;redb<='0';greenb<='1';yellowb<='0';elsenumb<=50-countnum;redb<='0';greenb<='0';yellowb<='1';end if;end if;end if;end process;end;交通灯控制器波形图交通灯控制器波形图分位器的设计因为控制器输出的倒计时数值可能是1位或2位十进制数,所以在七段数码管的译码电路前要加上分位电路(即将其分为2个1位的十进制数。

(如25分为2和5,7分为0和7)与控制器一样,分位电路同样可以由时钟驱动,也可以设计成纯组合逻辑电路。

控制器中,引入了寄存器。

为了让读者开拓眼界,分位电路就用组合逻辑电路实现。

分位电路程序library ieee;use ieee.std_logic_1164.all;entity fenwei isport(numin:in integer range 0 to 25;numa:out integer range 0 to 2;numb:out integer range 0 to 9);end;architecture behavior of fenwei isbeginprocess(numin)beginif numin>=20 thennuma<=2;numb<=numin-20;elsif numin>=10 thennuma<=1;numb<=numin-10;elsenuma<=0;numb<=numin;end if;end process;end;分位译码电路波形图分位译码电路波形图七段译码电路的设计七段译码电路的程序library ieee;use ieee.std_logic_1164.all;entity displayone isport(clock: in std_logic;flash: in std_logic;qin: in std_logic_vector(3 downto 0); display: out std_logic_vector(0 to 6));end;architecture decoder of displayone issignal timeout:integer range 0 to 63;beginprocess(clock)beginif rising_edge(clock) thenif flash='0' thentimeout<=0;elseif timeout=63 thentimeout<=0;elsetimeout<=timeout + 1;end if;end if;if timeout<64 thencase qin iswhen"0000"=>display<="0111111";when"0001"=>display<="0000110";when"0010"=>display<="1011011";when"0011"=>display<="1001111";when"0100"=>display<="1100110";when"0101"=>display<="1101101";when"0110"=>display<="1111101";when"0111"=>display<="0000111";when"1000"=>display<="1111111";when"1001"=>display<="1101111";when others=>display<="0000000";end case;elsedisplay<="0000000";end if;end if;end process;end;七段译码电路的波形图七段译码电路的波形图交通灯控制器的顶层原理交通灯控制器的核心范围是一个计数范围为0~49共(50秒)的计数器和一个根据计数值做出规定反映的控制器。