基于Cadence的电路版图绘制及验证页PPT文档

Cadence数字集成电路版图设计与验证 实验指导书 (电子科技大学)

数字集成电路版图设计与验证实验指导书电子科技大学微电子与固体电子学院实验名称数字集成电路版图设计与验证一、实验目的与意义随着IT产业的迅猛发展,微电子集成电路在通讯、计算机及其他消费类电子产品中的重要地位日益突出,而IC的生产和设计技术水平是决定IC芯片性能的两大要素。

该实验是正向设计中电路仿真完成之后、工艺制版之前的必须环节,与其他实验相结合,可以使学生对当前国际主流的IC设计技术流程有较完整的认识。

本实验是基于微电子技术应用背景和《微电子集成电路》课程设置及其特点而设置,为IC设计性实验。

其目的在于:•根据实验任务要求,综合运用课程所学知识自主完成相应的数字集成电路版图设计,掌握基本的IC版图布局布线技巧。

•学习并掌握国际流行的EDA仿真软件Cadence的使用方法,并进行版图的自动布局布线设计与验证。

通过该实验,使学生掌握数字专用集成电路版图设计的流程,加深对课程知识的感性认识,增强学生的设计与综合分析能力,掌握自主进行数字集成电路版图设计与验证的基本方法,进而为今后从事科研、开发工作打下良好基础。

二、实验原理2. 1 Cadence 环境的调入1、在UNIX 操作系统的Terminal窗口下→ cd user/userxxx/studname/Project→ icms& 或icfb&2、出现CIW(command Interpreter window)命令解释画面3、点选在CIW窗口的上面工具列Tools→Library Manager,会出现LM窗口LM(Library Manager)2. 2 建立新的Library1.点选LM窗口上面的工具列File→New→Library2.会产生New Library画面3.出现下图画面1.在name填上Library名称2.点选下面的OK4.出现Load Technology File窗口,添加工艺文件2.3 电路版图的自动布局布线2.3.1 启动Automatic Layout Tool1.打开已经设计完成的电路图Schemic2.点选 Tools --> Design Synthesis --> Device-Level Editor ,将弹出对话框,定义版图名,最好取与前面cell view 相同的名字。

Cadence原理图库和PCB库的设计与流程PPT精选文档

➢Capture 原理图符号库的组成

元件名:30BQ040。 元件编号的关键字:D。 元件管脚:图中红色线条。 元件符号:图中蓝色符号。

注: 如果元件没有指定Value值,则软件会把元件名设为 默认的Value值。 如果元件有多个part,则每个part的编号以指定的方式表示,如U?-1,表示第一个part的编号。

注:设置管脚名时,若引线名称带有横线(例如RESET),则设置时应在每个字 母后面加“\”,如:“R\E\S\E\T”。

.11

➢直接新建元件

③ 给元件添加管脚 ⑵ 同时添加多个管脚引线:“Place” “Pin Array”

第一个管脚名 第一个管编号 共同绘制几根引线 递进步长 Pin 间距

第一个管脚名 第一个管脚名 PIN显示OR关闭

.12

➢直接新建元件

给元件添加管脚和外形,如下图,完成了第一个part的设计,其它part继续 前面步骤,并加下文字描述,最终完与这个元件的建立。

.13

➢用电子表格新建元件

使用“New Part”选项不适合创建包含大量数目管脚的元件,对于 管脚数目较多的元件,手动添加管脚和设置属性不仅费时且效率低。因此 针对管脚数目较多的元件的,我们采用电子表格来新建元件。 ⑴ 选择元件库,单击右键 从弹出的菜单中选择“New Part From Spreadsheet” 或者选择主菜单的中“Design” “New Part From Spreadsheet”。

Output、Passive、Power八项可选。 ➢ Shape:管脚形状,有Clock、Dot、Dot-Clock、Line、Short、Zero Length六项可选。 ➢ PinGroup:管脚分组。 ➢ Position:管脚在元件外框的位置,有Top、Bottom、Left、Right四项可选。 ➢ Add Pin:当表格显示管脚数目不够时,单击该按钮弹出对话框输入数字添加管脚。 ➢ Delete Pin 删除管脚,一次只能删除一行。

集成电路CAD版图设计PPT课件

§1.逻辑划分

• 布图规划过程与所用的算法和求解策略有关。一个典 型的布图规划过程一般包括:Bottom up结群并产生结 群树、Top down软模块布局、调整模块形状和确定模 块的引线位置,目标是使芯片面积、总连线长度最小 和优化输出结果。

• 布规划分为物理分级构造、分级布图规划和详细布图 构造三大部分,每个部分又分成若干过程。物理分级 构造是一个Bottom up结群和估计模块面积的过程;分 级布图规划则是个Top down软模块布局、布线区面积 估计和分配、模块形状调整以及布局修正的过程;随 后在详细布图构造中完成整个布局和布线。

(2)在A中取出一个单元a2,使Con(Ai,a2)为最大,即最相关。 如果存在两个以上连接度相同的单元,则选Dis(Ai,a2)最小 的单元,即a2与其它单元有弱的连接关系。

(3)检查

S( E(

Ai Ai

) )

S max 制条件。

如满足条件则

AAi

Ai a2 Aa2

22

• 为了简化布局,将平面划分为方格 的组成方式,这些格子用占位符

P p 1 ,p 2, ,p N 的集合描述,网表对象 M m 1 ,m 2 , ,m r 映射在占位符上。每一

个 mi M 对象与一组信号 S i 相关。

23

距离树

• 为了评估布局的质量,需要能够实施评价的量化指 标。布局决定了布线的连线总长度,距离树是一个 近似的指标,是一种互连线长度的定量方式,它和互 连线的最终长度有密切关系而且容易计算。

• Ai,Aj之间的分离度(即无关连线之和)为:

D (A ii,A s j) B (A i) B (A j) C(A o i,A jn )

12

连接度和分离度的关系

cadence软件画版图操作

cadence软件画版图操作cadence软件操作1、原理图设计电路的原理图设计和许多的电路设计软件是类似的,这⾥⼤致介绍⼀下基本的操作。

⾸先是新建⼀个cell的原理图:library manager》file》new》cellview》这⾥设置元件名以及类型。

这⾥也可以选择其他类型。

其中⽐较重要的就是schematic和layout,后⾯也会提到。

这要记住如何新建。

这⾥使⽤的tool是Composer-schematic,⽽后⾯的版图设计采⽤virtuoso即可设计版图。

新建完成后会⾃动打开编辑器。

通过编辑,可以得到所需的电路。

这⾥看⼀下设计的基本界⾯。

和Multisim等电路软件类似,左侧是菜单栏,⽤于执⾏操作。

其中重要的有四个:导⼊元件、连线、标记、输⼊输出。

分别在图中的倒数第7、6、4、3,掌握这⼏个就可以绘制基本的原理图。

其中注意该软件的通⽤快捷键:q,在使⽤esc退掉其他指令后,选中某个⽬标,按q即可得到设计的属性。

对于新⼿⽽⾔,不能修改错误是难受的。

在q内可以修改所有设置的值。

2、前仿真前仿真,⾸先要有原理图。

步骤和前⾯的操作基本⼀致。

只不过加⼊了激励信号。

由于使⽤的是模拟仿真器,所以只能采⽤模拟信号源。

(数模混合仿真有时间再记录)注意,如果想要仿真⾃⼰的原理图,需要封装。

⼀⽅⾯可以将原理图内部的标识隔离,⼀⽅⾯⽅便区分顶层和⼦模块。

封装就是在design》create cellview》from cellview即可。

注意要区分保存和检查。

保存并未导⼊⼯程,在后⾯的操作中如果提⽰某个⽂件不⼀致,很有可能就是只是保存⽽没有检查。

在原理图设计界⾯的菜单栏第⼀项tools》analog environment可以进⼊仿真界⾯。

图中配置在使⽤模拟信号仿真时可以不更改。

分析⽤于选择仿真时间。

观察点就是选择要呈现的波形。

右下⾓的红绿灯可以⽤于开始仿真。

3、板图设计先看⼀下界⾯:常⽤功能:shift+z:缩⼩ctrl+z:放⼤(⼀般采⽤右键框选可以放⼤特定的区域)shift+k:清除尺⼦q:属性o:通孔选择p:路径连接shift+f:版图视图ctrl+f:元件视图其他的功能可以在左侧菜单栏⼀⼀验证,这⾥不再多说。

cadence入门教程PPT课件

IC设计基础

• 集成电路制造过程示意图:

第2页/共163页

IC设计基础

• 集成电路设计域主要包括三个方面: 行为设计(集成电路的功能设计) 结构设计(逻辑和电路设计) 物理设计(光刻掩模版的几何特性和物 理特性的具体实现)

第3页/共163页

IC设计基础

• 集成电路设计层次主要包括五个层次:

(1)系统级 (2)算法级 (3)寄存器传输级(RTL级) (4)逻辑级 (5)电路级

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行数据交换。

第21页/共163页

EDA概述

• EDA应用于三方面: 印制电路板的设计(PCB) 可编程数字系统设计(CPLD、 FPGA、SOPC) IC设计(ASIC, Soc)

EDA概述

• Synopsys公司简介:

是为全球集成电路设计提供电子设计自动化 (EDA)软件工具的主导企业。为全球电子市场提供技 术先进的IC设计与验证平台,致力于复杂的芯片上系 统(SoCs)的开发。总部设在美国加利福尼亚州 Mountain View,有超过60家分公司分布在北美、 欧洲、日本与亚洲。

合设计,嵌入式系统设计,软硬件系统协同设计,系统芯片设计,可编程逻辑器件和可编程系统芯片设计, 专用集成电路设计等

第13页/共163页

EDA概述 • 高级硬件描述语言的完善和IP(Intellectual Property)芯核被广泛使

用,使得电子系统和设计方式发生了根本性的转变。 • IP是集成电路知识产权模块的简称,定义为:经过预先设计、预先验证,

EDA概述

3、全定制IC设计工具

Virtuos Schematic Composer Analog Design Environment Virtuos Layout Editor Spectra Virtuoso Layout Synthesizer Assura dracula Diva

Cadence原理图库和PCB库的设计与流程 ppt课件

主要内容:

1.Capture 原理图符号库 ➢ Capture原理图库的组成。 ➢ Capture原理图库建库方法。 ➢ Capture原理图库调用方法。

2.Allegro PCB封装库 ➢ Allegro 封装库与PROTEL PCB封装库的比较。 ➢ Allegro 封装库的组成。 ➢ Allegro 封装库的建库方法。 ➢ Allegro 封装库路径设置及调用方法。 ➢ 举例一些常见 PCB封装的制作。

Page 4

➢直接新建元件

① 新建元件

有几个part的元件符号是否相同

Page 5

Alias Names

元件别名: 对于新建元件,我们可以赋予它多个别名,新建的元件及其别名均出现在库文件中,

它们除了名称(对应于电路图中元件的part value值)不同外,其它方面均相同。

Page 6

Attach Implementation

➢ No.of Sections:表示该元件可以分割多少个Part。 ➢ Part Ref Prefix:元件名称前缀以。 ➢ Part Number:表示该元件每个Part是以数字(Number)还是字母(alphabetic)区分。 ➢ Number:管脚编号。 ➢ Name:元件管脚名。 ➢ Type:管脚类型,有3-Stae、Bidirectional、Input、Open collector、Open Emitter、

模型描述,供P spice仿真调用。 PSpice Stimulus:附加一个P spice激励信号描述文

件。 Verilog:附加一个Verilog文件。

Page 7

➢直接新建元件

《集成电路版图设计》(第二章)PPT课件

方式二:选择Attach

基于Cadence系统的 全定制版图设计基础

基于Cadence系统的 全定制版图设计基础

三、显示文件准备

LSW窗口:

✓ nwell是N 阱,PMOS管做在N阱中; ✓ ndiff是N型扩散区,也叫N型有源区(active),用来做NMOS管; ✓ pdiff是P型扩散区,也叫P型有源区,用来做PMOS管; ✓ nimp是N型扩散区注入层; ✓ pimp是P型扩散区注入层; ✓ poly是多晶层,主要用来做管子的栅极; ✓ cont是接触孔contact; ✓ metal1是一铝层; ✓ via1是一铝层和二铝层之间的连接孔,称为通孔; ✓ metal2是二铝层; ✓ pad是压焊点所在的层; ✓ 其它还包括一些特殊器件上的标识层等等

3、单元的宽长比设 置原则——最常见 宽长比的设置

逻辑图中每一 个管子宽长比 的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长 比设置原则— —最常见宽长 比的设置(续)

单元符号的建立和 Label的设置

基于Cadence系统的 全定制版图设计基础

3、单元的宽长比 设置原则——其它 宽长比的设置

基于Cadence系统的 全定制版图设计基础

第一部分、D508项目逻辑图的准备

一、逻辑图输入工具启动

二、一个传输门逻辑图及符 号的输入流程

三、D508项目单元逻辑图的准备 四、D508项目总体逻辑图的准备

第二部分、D508项目版图输入准备

一、设计规则准备 二、工艺文件准备 三、显示文件准备

第三部分、版图设计步骤及操作

三、显示文件准备(续)

基于Cadence系统的 全定制版图设计基础

Display Resource Editor 窗口:

Cadence新手简明教程精品PPT课件

9

10

11

需要填这两项

12

里面不需要 snap to grid

边框和引脚必须 snap to grid, 保证电气属性

13

14

15

如果需要更改原理图页大小,可以在工程文 件目录中选择相应的原理图页,右键选择 schematic page property

16

17

18

按p调出右侧的 place part窗口 从中选取需要的 元件,双击或 enter或点击面板 上的放置按钮摆 放该元件,可放 任意多个,放完 按ESC退出。

35

36

37

元器件的坐标 报告复合封装中没有使 用的元件

38

39

40

41

42

勾选了inter tool communication之后,在PCB 布局模式下,选中原理图页的一个元件, PCB中对应的封装就会高亮,并且可以移动

43

44

Allegro是Cadence公司推出的先进 PCB 设计 布线工具。 Allegro 提供了良好且交互的工 作接口和强大完善的功能,和它前端产品 Capture的结合,为当前高速、高密度、多 层的复杂 PCB 设计布线提供了最完美解决方 案。

45

制作pad 布线 检查、修改

制作symbol 设置规则 铺铜

导入网表 开摆件

删除孤岛 后处理

46

47

不要忘记这里

48

单层模式

49

50

菜单栏

工具栏

命令窗口

状态栏

标题栏 控制面板 整体视图

51

F3(开始走线) F4(显示属性) F6(完成) F8(oops,取消上一步操作) F9(cancel,取消本次命令) SF3(推挤走线)SF6(移动)SF4(测距) Ctrl+F5(color选项卡)ctrl+d(删除) 滚轮上下(或F11、F12)放大缩小

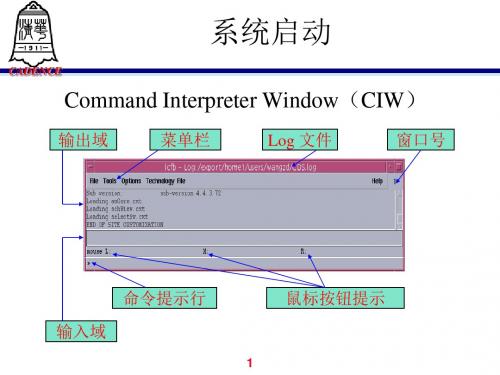

最新文档-cadence精简教程-PPT精品文档

CADENCE

Command Interpreter Window(CIW)

输出域

菜单栏

Log 文件

窗口号

命令提示行 输入域

鼠标按钮提示

1

帮助系统

CADENCE

两种方式寻求帮助 1 openbook

在UNIX提示符下输入命令 openbook: host >openbook &

2 工具在线帮助

22

版图设计工具-Virtuoso LE

CADENCE

主要创建命令

Rectangle-矩形 Polygon-多边形 Path-互联 Label-标签 Instance-例元 Contact-通孔

现在LSW中选中层,然后点击 创建命令,在画相应图形

23

绘制反相器版图

CADENCE

8

Virtuoso LE 使用介绍

CADENCE

第三步:建立版图单元

执行:LM->File->New->Cell View…

9

Virtuoso LE 使用介绍

CADENCE

第四步:打开版图单元

执行:CIW->File->Open…

选择库 选择视图

10

选择单元

版图设计工具-Virtuoso LE

46

版图验证

CADENCE

IC 后端流程图:

47

Cadence 版图验证工具

CADENCE

Diva

Diva 是 Cadence 的版图编辑大师Virtuoso集成 的交互式版图验证工具,具有使用方便、操作 快捷的特点,非常适合中小规模单元的版图验 证。

Dracula

Cadence软件使用教程 ppt课件

Allegro PCB Router 自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强, 可以在Allegro PCB Editor中用自动布线命令调出来。这个布线工 具名气很大,对于简单的电路板,布线很美观,布通率很高。

Cadence软件使用教程

Cadence软件使用教程

1、利用OrCAD Capture CIS进行原理图设计 2、利用Cadence PCB Editor进行PCB布局布线 3、光绘文件(Artwork)制作,如何生成Gerber文件

Cadence软件使用教程

Cadence软件使用教程

1、系统的原理图工程文件 2、系统的PCB图工程文件 3、原件库、封装库文件 4、板上芯片的datasheet 5、给PCB厂商的Gerber文件(Artwork) 6、DSP6713程序的C语言源代码

Padstack Designer 创建及修改焊盘padstacks Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。 DB Doctor 用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。 在生成光绘文件前必须进行DBDoctor检查。

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

Cadence软件使用教程

cadence模拟电路板图设计

实验名称:模拟电路板图设计实验者:赵静怡学号:1028401083指导老师:顾江敏实验目的:1、根据已知电路图了解模拟电路设计要求2、完成模拟电路仿真,学会加载已知数据3、绘制模拟电路板图,通过DRC以及LVS检查。

进一步熟悉和掌握cadence软件的使用实验操作介绍:一、进入操作界面1、双击“VMware Workststion”,进入虚拟机。

选择用户名“icl2012”,键入密码“Su64zhouicl”进入cadence界面。

右击“Open in Terminal”进入输入指令界面。

2、部分指令说明:ls(回车)——查找当前目录下所有文件,绿色是可执行文件、蓝色为文件夹ls—l(回车)——给出文家属性、建立时间等信息cd ..(回车)——回到icl2012./ic【Tab】(回车)——打开界面二、库管理器1、点击“library manager”,打开库管理器。

认识Schematic、layout、Symbol等每一项内容。

点击左上角“show Categories”即可看到library中的具体分类。

2、点击“File—New—library”,新建一个库。

选择“Attach to an existing techfile”与pdk一致。

“Technology Library”中选择与之匹配的库。

3、建立cell,注意名字中不要有空格、只能有字母、数字、下划线。

三、绘制Schematic1、快捷键“i”:Add Instance2、快捷键“m”:移动元器件3、快捷键“w”:连线4、快捷键“l”:标注网络名5、快捷键“p”:加port6、电路仿真四、生成Symbol1、点击“Design—Create Cell view—From Cell view”生成Symbol2、绘制完成之后“Design—Check and Save”五、绘制layout1、快捷键说明:Shift+z:缩小Ctrl+z:缩小NPLUS+NV:是指只看NPLUS这一层F:刷新Q:设置参数Ctrl+d:取消所有选中Ctrl+a:全部选中Shift+k:删除标尺K:进行标尺P:布置金属线Shift+c:删除2、从电路图生成layout(1)Tools—Design—Layout XL(2)Connectivity—Update—Components and Nets从电路图更新到layout(3)将I/O Pins修改为金属1,将Pin Label Shape修改为Label,修改Pin Label Options的参量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

查看DRC结果并调整Layout

中国科学技术大学软件学院

一致性验证LVS

DRC

Project下创建DRC、 LVS、PEX用于版图设 计不同环节,文件归类

存储

中国科学技术大学软件学院

一致性比对文件指定

中国科学技术大学软件学院

等待并查看LVS验证结果

Net描述

中国科学技术大学软件学院

(2)获取源文件

中国科学技术大学软件学院

(3)生成config图

中国科学技术大学软件学院

运行后端仿真

中国科学技术大学软件学院

实验报告

完成CMOS版图设计,DRC检查无误 完成LVS检查,获得正确结果 完成PEX,生成寄生参数图 完成后仿电路中CMOS反相器的DC、Trans仿

真,记录结果,并与实验一比对,提交至教辅系 统,截止时间 4月15日 24:00

中国科学技术exie!

Exp#3 基于Cadence的电路版图绘 制及验证

中国科学技术大学软件学院

Contents

1

版图设计流程与工艺

2

CMOS反相器版图设计

3

CMOS反相器后端仿真验证

中国科学技术大学软件学院

芯片设计流程

前端仿真

版图设计

电路设计 其它

后端仿真

中国科学技术大学软件学院

版图设计 完成集成电路加工所需的各个掩模版上的图形

硅 PT:p tub,p阱,作为nmos器件衬底

中国科学技术大学软件学院

CSMC05MS工艺库文件

中国科学技术大学软件学院

CMOS反相器版图设计与验证

中国科学技术大学软件学院

中国科学技术大学软件学院

版图绘制

中国科学技术大学软件学院

设计规则验证DRC

中国科学技术大学软件学院

指定输入输出文件

提取出包含寄生参数的spice网表,用于带有 寄生参数的后仿真

中国科学技术大学软件学院

CSMC双硅三铝混合信号工艺

TB:tub,n阱,作为pmos器件衬底 TO:Thin Oxide,有源区,作为mos的源漏区 GT:gate,多晶硅1,作为mos栅极 SP:P+注入区 SN:N+注入区 W1:接触孔,金属1到多晶硅和有源区的接触孔 A1:铝1,第一层金属 W2:通孔1,金属1和金属2的接触孔 A2:铝2,第二层金属 W3:通孔2,金属2和金属3的接触孔 CP:bond pad,pad开孔 IM:第二层多晶硅电阻阻挡层 PC:poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶

中国科学技术大学软件学院

设计规则:设计者和工艺工程师之间的接口

中国科学技术大学软件学院

基于Cadence的版图设计

工具:Virtuoso Layout Editor 设计规则检查 DRC 版图原理图一致性检查LVS

从版图中提取电路网表,然后将这个网表同 电路原理图进行比较 版图寄生参数提取LPE

参数提取PEX

中国科学技术大学软件学院

指定输出文件格式

中国科学技术大学软件学院

Map与输出布局设定

中国科学技术大学软件学院

指定提取参数与原理图中模型映射关系

中国科学技术大学软件学院

生成后仿电路config图

源文件

目标文件

中国科学技术大学软件学院

(1)指定新文件类型

中国科学技术大学软件学院