覆晶(倒装 Flip Chip LED)工艺介绍

LED倒装制程介绍

LED倒装制程介绍LED倒装制程(Flip Chip Process)是一种将LED芯片倒装在基底上的制程技术,可用于生产高亮度、高可靠性和高性能的LED芯片。

这种制程技术最早是为了满足高可靠性和高亮度LED应用的需求而开发的,随着技术的不断进步,现在已广泛应用于各种LED芯片制造过程中。

在传统的LED封装制程中,芯片是面向基底发光的,而在LED倒装制程中,芯片被倒装到基底上,面向封装外部。

这种倒装的设计能够有效提高LED的性能和可靠性,主要有以下几个优点:1.热耦合效应:由于芯片底部直接与封装基底接触,LED倒装制程可以提供更好的热耦合效应。

芯片产生的热量能够更快、更有效地传导到基底上,避免了芯片因长时间高温工作而导致的性能下降和寿命缩短问题。

2.更高的亮度和更好的颜色一致性:倒装制程能够提供更均匀的电流分布,减小了电流密度差异对亮度和颜色一致性的影响。

此外,倒装制程还可以提供更大的电流承受能力,使得LED芯片在高亮度工作时能够保持较好的亮度和颜色一致性。

3.提高了封装的可靠性:倒装芯片直接与封装基底相连,不需要通过金线进行连线,减少了因金线断裂而导致的电连接故障。

同时,倒装制程还可以提供更大的焊接面积,提高焊接接触面的可靠性。

1.基底准备:首先需要准备好封装基底,通常使用金属或陶瓷作为基底材料。

基底上需要刻蚀出与LED芯片尺寸相对应的凹槽,用于倒装芯片。

2.倒装芯片:将LED芯片倒装到基底的凹槽中,并使用适量的导热胶进行固定。

芯片与基底之间需要使用导电胶进行电连接。

3.焊接:将倒装芯片和基底进行焊接,通常使用热压焊或电压焊的方式。

焊接过程中需要保持适当的温度和压力,确保焊接的可靠性和稳定性。

4.后续工艺:完成焊接后,需要进行一系列的后续工艺,如清洗、封装、测试等。

这些工艺步骤是为了确保LED倒装产品的质量和性能。

LED倒装制程是一种高度精密的制程技术,要求制程设备和工艺能够提供高度的精确性和可重复性。

LED光电器件覆晶倒装焊产业化的关键技术研究

科技资讯2015 NO.22SCIENCE & TECHNOLOGY INFORMATION工 业 技 术73科技资讯 SCIENCE & TECHNOLOGY INFORMATION 1 国内外技术发展及现状GaN基发光二极管(LED)作为新一代的环保型固态光源,已经成为产业界的关注焦点。

1992年,有“蓝光之父”之称的中村修二成功地制备出了Mg掺杂的p型GaN ,随后在1993及1995年采用InGaN/GaN异质结结构成功制备了高亮度的蓝光LED,并因此而斩获了2014年度的诺贝尔物理学奖。

目前,大功率、高亮度的白光LED已经成为了照明领域的发展热点。

白光LED发光效率虽然已经达到了170lm/W,但离其理论值250lm/W尚有一定的差距,因此进一步提高其发光效率成为功率型白光LED的一个关键技术问题。

一般来说,提高LED的发光效率有两种途径,分别是提高其内量子效率及光提取效率。

另一方面,如何提高散热能力成为了功率型LED器件发展的另一个关键技术[1]。

随着LED功率的增大,特别是固态照明技术发展的需求,对LED封装的光学、热学、电学和机械结构等提出了新的、更高的要求。

由此可见,研究高取光效率、低热阻、高可靠性的封装技术是大功率LED走向实用及产业化的必经之路。

覆晶(Flip-Chip)技术,也称为倒晶封装法,是一种在IC封装技术领域成熟的芯片封装工艺。

因为能满足上述高性能封装的要求,基于覆晶技术的功率LED封装被认为是封装功率型高亮度LED的关键技术及发展趋势[3]。

在过去传统的水平及垂直式晶片结构中,正面电极的吸收及GaN-Air界面全反射临界角等因素会很大程度上影响光提取效率[2];另一方面,传统封装结构中,LED 芯片的热量需经由衬底蓝宝石(其热导率仅为38W/m.K)传导至导热基板,导热路径较长,从而芯片的热阻较大。

而采用覆晶技术形成的倒装结构,将蓝宝石衬底芯片进行倒置,芯片直接焊接在导热基板上,电极在底部与基板相互连接,也就避免了传统封装中芯片高低差带来的打线困难的问题。

覆晶(倒装 Flip Chip LED)工艺介绍

为什么要用覆晶LED覆晶焊技术支持的LED光源与传统封装光源相比,具有热阻低,电压低,大电流密度光效高的特点,综合研究表明覆晶LED光源在应用上有其独特的潜力和优势。

优点:(1)、高可靠性,最稳定的SMT锡制程,承受拉力是传统LED的数十倍。

(2)、低热阻(3014热阻为40℃/W,倒裝为5.8℃/W),高散热性,防止热量过高而烧坏晶片或荧光粉和封装胶。

(3)、无金线可实现多芯片的集成,特别是COB和高压LED灯源。

也有效的避免金线引起的各种风险,比如热膨胀使之断裂,外部冲击波或压力造成金钱断裂等优势。

(4)、导电面积大,内阻小,能承受大电流通过,减少因为内阻大引起的过大热量。

(5)、发光率高,发光角度大等优点。

(6)、封装工艺简化,降低封装成本,高提生产良率。

(7)、低光衰,不因为热引起的快速光衰,从而延长了芯片的寿命,是普通灯具的10倍以上一、结构优势首先,相对于正装和垂直的芯片封装方式,覆晶封装没有金线存在,可以有效避免金线可能引起的各种风险。

下表为硅胶、金线、芯片的热膨胀系数值,其数量级的差距说明了硅胶热膨胀对金线的拉扯会造成可靠性的隐患。

材料热膨胀系数其次,覆晶焊采用金属与金属直接接触的方式,其大电流散热能力比传统封装更好。

如图为传统封装与覆晶封装在散热通道方面的区别,传统正装封装通过蓝宝石和固晶银胶散热,覆晶焊通过金属通道散热,传统封装的蓝宝石和固晶胶成为散热瓶颈。

下表所示的数值为蓝宝石、固晶胶、金属三者在导热系数大小,三者对比明显可以发现覆晶焊金属导热通道的巨大优势。

材料导热系数传统封装光源散热通道覆晶焊封装光源散热通道最后,覆晶焊的封装不存在金线的焊线弧度,能够实现超薄型的平面封装。

传统封装方式金线的拉力仅10g左右,而覆晶焊的接触面推力达到500g以上,覆晶封装可以抵抗一定的表面挤压而不影响LED的光电性能,适合于狭小的应用空间内。

例如手机、摄像机、背光等领域。

同时在多芯片的集成,均能发挥超薄易安装高集成的优势。

flip chip工艺技术

flip chip工艺技术Flip chip工艺技术是一种电子封装技术,它将芯片直接倒装在基板上,通过金线、焊球或者导电胶等连接芯片和基板之间的引脚,以实现电信号的传输。

相比传统的片上线缆(wire bonding)技术,flip chip工艺具有许多优势,如更高的可靠性、更小的封装尺寸和更高的电路性能等。

Flip chip工艺技术最早出现在1961年,当时IBM公司发明了一种在芯片表面覆盖一层金球,并将其倒装在基板上的方法。

经过多年的发展,flip chip工艺技术已经成为现代电子封装领域中的一个重要技术。

首先,flip chip工艺技术可以在同一面芯片上实现更多的输入输出(I/O)引脚,从而提高了芯片的连接密度。

对于高性能芯片来说,这项技术尤为重要。

根据需要,芯片制造商可以在芯片上布置成百上千个引脚,实现更高级别的功能和更复杂的电路设计。

其次,flip chip工艺技术可以显著减小芯片封装的尺寸。

由于芯片是倒装在基板上的,消除了传统封装技术中的芯片焊线和封装间隙,使得整个封装尺寸更小。

作为结果,这种封装技术对于紧凑型电子设备的制造非常有吸引力,例如智能手机、平板电脑和可穿戴设备等。

另外,flip chip工艺技术还具有更高的可靠性。

由于芯片和基板之间的连接是直接的,没有中间电线或导线,所以连接更加牢固。

此外,由于距离更短,电信号传输速度更快,噪声也更小,因此电路性能更稳定。

然而,flip chip工艺技术也存在一些挑战。

首先,由于芯片倒装在基板上,制造过程需要更加精确和复杂的操作。

其次,倒装引脚之间的热量分布不均匀可能会导致芯片热量过量和不均匀,从而影响芯片的性能和寿命。

此外,由于芯片和基板的直接接触,其之间必须要有一层合适的介质材料来调整它们之间的电学和热学性能。

这样的介质材料需要具备良好的导热性、电性能和耐久性。

总结来说,flip chip工艺技术是一种先进的电子封装技术,具有更高的可靠性、更小的封装尺寸和更高的电路性能等优势。

覆晶技术(Flip-Chip)介绍

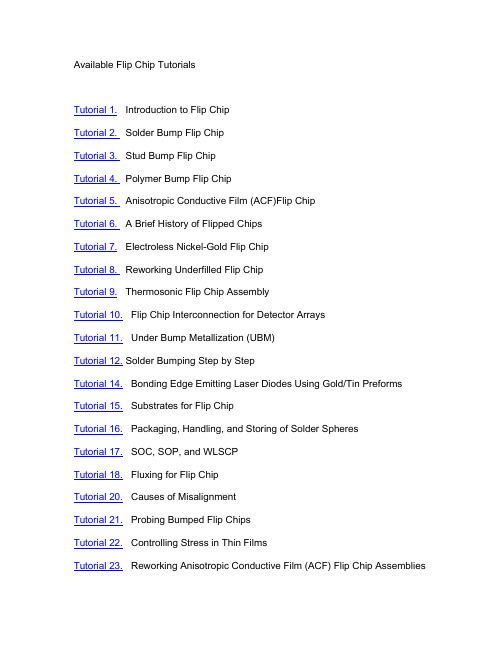

Available Flip Chip TutorialsTutorial 1. Introduction to Flip ChipTutorial 2. Solder Bump Flip ChipTutorial 3. Stud Bump Flip ChipTutorial 4. Polymer Bump Flip ChipTutorial 5. Anisotropic Conductive Film (ACF)Flip ChipTutorial 6. A Brief History of Flipped ChipsTutorial 7. Electroless Nickel-Gold Flip ChipTutorial 8. Reworking Underfilled Flip ChipTutorial 9. Thermosonic Flip Chip AssemblyTutorial 10. Flip Chip Interconnection for Detector ArraysTutorial 11. Under Bump Metallization (UBM)Tutorial 12. Solder Bumping Step by StepTutorial 14. Bonding Edge Emitting Laser Diodes Using Gold/Tin Preforms Tutorial 15. Substrates for Flip ChipTutorial 16. Packaging, Handling, and Storing of Solder SpheresTutorial 17. SOC, SOP, and WLSCPTutorial 18. Fluxing for Flip ChipTutorial 20. Causes of MisalignmentTutorial 21. Probing Bumped Flip ChipsTutorial 22. Controlling Stress in Thin FilmsTutorial 23. Reworking Anisotropic Conductive Film (ACF) Flip Chip AssembliesTutorial 24. Gold Stud Bump ApplicationsTutorial 25. Low Temperature Flip Chip for Flexible DisplaysTutorial 26. The Coming of Copper UBMTutorial 27. Shaping Gold Ball BumpsTutorial 28. Copper Bumps for Flip Chip AssemblyTutorial 29. Micro-Posts: Tall, Slender, Stud Bumps.Tutorial 30. Measuring thin films by spectral reflectance, Part 1Tutorial 31. Wafer level hermetic cavity chip scale packages for RFTutorial 32. Gold Stud Bumping - the Other Flip-Chip ProcessTutorial 33. Conductive Polymer Assembly of High Pin Count Flip Chip Tutorial 34. Sputtered nickel UBM for lead-free solder bumpingTutorial 35. Measuring thin films by spectral reflectance, Part 2Tutorial 36. MEMS Special Packaging NeedsTutorial 37. Too much gold can be a bad thing.Tutorial 38. Evaporated Indium Bumps for Flip ChipTutorial 39. Electromigration and Thermomigration in Flip Chip Solder Joints Tutorial 40. Nano-embossing reaches production.Tutorial 41. Hermeticity: much to do about nothing.Tutorial 42. Evaluating Wafer Level Solder Reflow Options to Maximize Yield Tutorial 43. Wafer-level Hermetic Cavity Packaging.Tutorial 44. Advanced Wafer-level Cleaning Method.Tutorial 45. Lead-Free Facts and Myths.Tutorial 46. Alloy Electroplating: The best solution for Au-Sn solder?Tutorial 47. Flip Chip Bonder for Assembling 3D MEMSTutorial 48. Drop-in Lead-free solderTutorial 49. Wafer-level Nano-opticsTutorial 50. Gold Stud Bump UpdateTutorial 51. Solder Bumping Single DieTutorial 52. New Generation Nano-Imprint Lithography System Tutorial 53. Probe testing differences in lead-free bumpsTutorial 54. Nano Particle AdhesivesTutorial 55. The Promise of C4NPTutorial 56. Injection Molding Solder BumpsTutorial 57. Thermosonic Bonding of 1,000-bump Flip ChipsTutorial 58. Nanosoldering electronic components at room temperature Tutorial 59. Lower temperature lead-free flip chipTutorial 60. Nanotube Heat SinksTutorial 61. Lead-Free Solder Bumping MethodsTutorial 62. Vapor Jet Deposition of Multi-Metal FilmsTutorial 63. C4NP Test DataTutorial 64. Silver Nano-platelet Precursors for Ultra-Thin Conductors Tutorial 65. Cleaning microelectronic devices by Vacuum Cavitational StreamingTutorial 66. The Folly of RoHSTutorial 67. Underfilling ProcessesTutorial 68. Plasma pretreatment of Flip Chip and CSP assemblies Tutorial 69. Resonance Sensor Technology for Bump InspectionTutorial 70. Controlled-expansion substrates for WLP Tutorial 71. Nailing ICs TogetherTutorial 72. Redistribution LayersTutorial 73. Advanced ReworkTutorial 74. High Conductivity Nickel-Fiber ACF Tutorial 75. Unique Polished Polyimide Substrate Tutorial 76. Jet Dispensing of UnderfillsTutorial 77. Solderless Copper AssemblyTutorial 78. Quilt PackagingTutorial 79. Bump CoolingTutorial 80. Nano-particle Solder PasteTutorial 81. Wafer-level CSP with Integrated Passives Tutorial 82. Putting Photons on the ChipTutorial 83. Soldering Stud BumpsTutorial 84. Avoiding Lead-Free Brittle Fractures Tutorial 85. Chip to Wafer Hermetic Cavity Sealing Tutorial 86. 3D Silicon ChipsTutorial 87. Laminated Chip PackagesTutorial 88. ElectroChemical Pattern Replication。

倒装芯片

倒装芯片

CHIP

Market

Period III

F L I P

行业情况

●璨圆2013年也积极推广其芯片级封装产 品,同样以flip chip为基础,在制程中省略导线 架与打线等步骤。 ●隆达将其芯片级封装CSP(Chip Scale Package)产品在上游晶粒也采用覆晶技术,也 同样省略导线架,幵简化封装流程。 ●Philips Lumileds推出的CSP产品 LUXEON Q就采用flip chip技术,不需在后段制 程中移除蓝宝石基板。 ●CREE的XQ-E LED产品也同样采CSP技 术,将芯片面积大幅缩小,其微型化设计可以 提升光调色品质与光学控制,扩大照明应用范 围。 综合各企业产品,共同的特点是采用倒装芯 片,使体积更小,光学、热学性能更好,同时 因省略了导线架与打线的步骤,使其后道工序 更加便捷。

部分企业的芯片级封装产品: ●晶电的芯片级封装产品称为ELC(Embedded LED Chip),制程中完成芯片生产后,仅 需要涂布荧光粉与采用封装胶,省略导线架与打线的步骤,可以直接贴片(SMT)使用,ELC 产品在没有导线架的情况下,发光角度较大,未来可能省略二次光学透镜的使用。 ●台积固态照明则的芯片级封装产品名为PoD(Phosphor on die),直接将flip chip(覆晶)芯 片打在散热基板上,省略导线架与打线等步骤,同样主打小体积,拥有更高的光通量和更大 的发光角度,幵且可以更容易混色与调控色温特性,适用于非指向性光源应用。

随着上游芯片产能不断扩产,封装行业已经步入微利时代,许多企 业为了抢夺客户大打价格牌,激烈的价格竞争和无序的业内生态链促使行 业开始需求新的封装工艺。而具有提升发光效率以及提高散热能力等优势 的倒装LED芯片技术的革新与应用正是当今封装企业专注研发的重点。

flipchip封装工艺

flipchip封装工艺Flipchip封装工艺是一种先进的微电子封装技术,它在集成电路封装领域具有重要的应用价值。

本文将从Flipchip封装工艺的基本原理、优势和应用领域等方面进行介绍。

一、Flipchip封装工艺的基本原理Flipchip封装工艺是一种将芯片直接翻转并与基板相连接的封装技术。

与传统封装工艺相比,Flipchip封装工艺具有更高的可靠性和更小的封装体积。

其基本原理是通过将芯片的电路面朝下,将芯片的引脚与基板上的金属引脚连接,从而实现芯片与基板之间的电气连接。

Flipchip封装工艺的具体步骤包括:首先,将芯片的电路面朝下,将芯片上的金属引脚与基板上的金属引脚对准;然后,通过热压或焊接等方式将芯片与基板相连接;最后,进行封装胶的填充和固化,以保护芯片和连接引脚。

二、Flipchip封装工艺的优势1. 封装密度高:由于Flipchip封装工艺将芯片的电路面朝下,可以实现更高的封装密度,从而提高芯片的性能和功能。

2. 电性能优良:Flipchip封装工艺可以实现短距离的电气连接,减少电阻和电感的影响,从而提高芯片的电性能。

3. 信号传输速度快:由于Flipchip封装工艺可以实现更短的信号传输路径,可以提高芯片的信号传输速度,从而提高芯片的运行速度和性能。

4. 散热性好:由于Flipchip封装工艺可以将芯片直接与基板相连接,可以实现更好的散热效果,提高芯片的稳定性和可靠性。

三、Flipchip封装工艺的应用领域Flipchip封装工艺在高性能计算、通信、消费电子等领域具有广泛的应用。

具体应用包括:1. 高性能处理器:Flipchip封装工艺可以实现更高的封装密度和更好的散热性能,适用于高性能处理器的封装。

2. 光通信模块:Flipchip封装工艺可以实现更短的信号传输路径和更高的信号传输速度,适用于光通信模块的封装。

3. 手机和平板电脑:Flipchip封装工艺可以实现更小的封装体积和更好的散热性能,适用于手机和平板电脑等消费电子产品的封装。

倒装芯片技术-PPT

对 UBM的要求-02

➢ 要有焊料扩散阻挡层:必须在焊料与焊盘焊区金属之 间提供一个扩散阻挡层

➢ 要有一个可以润湿焊料的表面:最后一层要直接与凸 点接触,必须润湿凸点焊料。

对 UBM的要求-03

可靠性

与一般的焊点连接一样,热压倒装芯片连接的可靠性也要 受到基板与芯片的热膨胀系数(CTE)失配的影响,此外焊点的高度 、焊点之间的最大间距亦会对可靠性造成影响。连接区的裂纹多 是在从连接温度冷却下来的过程中产生的。

由于金的熔点温度高,因此它对疲劳损伤的敏感程度远小于 焊料。因此,如果在热循环中应力没有超过凸点与焊盘之间的连 接强度,那么可靠性不会存在太大问题。

芯片与基底之间的底部填充材料使连接抵抗热疲劳的 性能显著提高,如果没有底部填充,则热疲劳将是倒装芯 片主要的可靠性问题。

生产问题

倒装芯片的连接头应该能够产生300°C 的连接温 度, 要有较高的平行对准精度,为了防止半导体材料 发生损伤,施加压力时应该保持一定的梯度。在热压倒 装芯片连接中,凸点发生变形是不可避免的,这也是形 成良好连接所必需的。另外,连接压力和温度应该尽可 能低,以免芯片和基板损坏。

点是:

• 简单,无需使用焊剂 • 工艺温度低

• 可以实现细间距连接

若干问题

对于直径为80mm的凸点, 热压压力可以达到1N。由 于压力较大,温度也较高,这种工艺仅适用于刚性基底, 如氧化铝或硅。另外,基板必须保证较高的平整度,热压 头也要有较高的平行对准精度。为了避免半导体材料受到 不必要的损害,施加压力时应该有一定的梯度。

由此模型可知:

要提高可靠性必须要求:

倒装芯片介绍

Source: Philips

一、倒装芯片技术

定义:

倒装芯片组装就是通过芯片上的凸点直接将元器件朝下 互连到基板、载体或者电路板上,芯片直接通过凸点直 接连接基板和载体上,整个芯片称为倒装芯片(Flip Chip)。

普通激光切割后wafer侧面

劈裂后wafer侧面

隐形激光切割后wafer侧面

三、工艺流程简介

Wafer 扩张:

Wafer扩张是将已经分离开的晶粒之间的距离变大,利于后面测试和分级设备 工作。

三、工艺流程简介

自动外观检测:

自动外观检测是通过AOI设备 对芯片的外观缺陷判定,尽可能 避免分级过程中外观坏品混入好 品当中。 常见的外观不良有:电极污染、 电极缺损、电极划伤、ITO区域 污染、切割不良等

曝光(MPA & STEPPER)

图1:Coating设备

显影(Developer)

图3:显微镜

检查(Inspection) 图2:Develop设备

黄光工艺流程及常见缺陷

Epi Partical

Photo defect

Scratch

Mask defect

Under develop

三、工艺流程简介

蓝宝石特性

在低于熔点温度范围内, 仍具有良好的化学稳定性和机械、物理等性能; 光学透过范围宽, 特别在1 500~7500 nm, 透过率达85%; 有与纤锌矿III 族氮化物相同的对称性, 故用于GaN 的外延衬底材料。

三、工艺流程简介

图形化蓝宝石衬底技术:

芯片封装技术——WireBond与FlipChip

芯片封装技术——WireBond与FlipChip文章目录•前言•一、COB技术——Wire bond•1.Ball Bonding(球焊)•o 1.1球焊压焊头o 1.2球焊流程示意图o 1.3球焊机•2.Wedge Bonding(平焊/楔焊)•o 2.1楔焊压焊头o 2.2平焊流程示意图o 2.3平焊机•3.金属线•o 3.1金线o 3.2铝线•4.bonding技术优势•5.常见缺陷•二、Flip Chip封装技术前言裸芯片技术主要有两种形式:一种是COB技术,另一种是倒装片技术(Flip Chip)。

COB是简单的裸芯片贴装技术,但它的封装密度远不如TAB和倒片焊技术。

板上芯片(Chip On Board, COB)工艺过程首先是在基底表面用导热环氧树脂(一般用掺银颗粒的环氧树脂)覆盖硅片安放点,然后将硅片直接安放在基底表面,热处理至硅片牢固地固定在基底为止,随后再用丝焊的方法在硅片和基底之间直接建立电气连接。

Flip Chip也叫倒晶封装或者覆晶封装,是一种先进的封装技术,有别于传统的COB技术,Flip Chip技术是将芯片连接点长凸块(bump),然后将芯片翻转过来使凸块与基板(substrate)直接连接。

wire bond图一、COB技术——Wire bond1.Ball Bonding(球焊)金线通过空心夹具的毛细管穿出,然后经过电弧放电使伸出部分熔化,并在表面张力作用下成球形,然后通过夹具将球压焊到芯片的电极上,压下后作为第一个焊点,为球焊点,然后从第一个焊点抽出弯曲的金线再压焊到相应的位置上,形成第二个焊点,为平焊(楔形)焊点,然后又形成另一个新球用作于下一个的第一个球焊点。

球焊的第一个焊点为球焊点,第二个为平焊点Ball Bonding 图1.1球焊压焊头球焊选用毛细管头,一般用陶瓷或钨制成;焊点是在热(一般为100-500°C)、超声波、压力以及时间的综合作用下形成的。

flipchip封装工艺

flipchip封装工艺

Flipchip封装是一种利用微型片上封装连接的封装技术。

它把

半导体晶片直接和基板连接,以提供较高的电性能和较高的芯片密度。

Flipchip封装通常是利用晶圆片或芯片的表面连接到基板,其中晶

圆片上有横向的电极,和基板上有纵向的电极,二者之间通过键合及焊接来连接起来。

Flipchip封装的工艺可以分为以下几个步骤:

1. 准备:首先,检查晶片和基板是否有足够的洁净度和湿度,

而且尺寸正确无误;

2. 定位:将晶片和基板放在模具中,以确定晶片在基板上的定位;

3. 键合:将晶片定位后,使用键合剂将晶片上的横向电极与基

板上的纵向电极连接;

4. 焊接:将晶片和基板定位和键合好后,使用热焊技术将晶片

和基板固定在一起,以保证晶片和基板的稳定性;

5. 检测:检测完封装工艺后,将晶片和基板进行功能测试,以

确保封装工艺是否成功。

Flipchip封装工艺是一种半导体封装技术,能够提供较高的电

性能和芯片密度,它与其他封装技术相比,有着较强的竞争力。

- 1 -。

大功率LED芯片的封装(共晶焊)及倒装芯片(flip chip)

大功率LED芯片的封装(共晶焊)及倒装芯片(flip chip)美国GREE公司的1W大功率芯片(L型电极),它的上下各有一个电极。

其碳化硅(SiC)衬底的底层首先镀一层金属,如金锡合金(一般做芯片的厂家已镀好),然后在热沉上也同样镀一层金锡合金。

将LED芯片底座上的金属和热沉上的金属熔合在一起,称为共晶焊接,如图1所示。

对于这种封装方式,一定要注意当led芯片与热沉一起加热时,二者接触要好,最好二者之间加有一定压力,而且二者接触面一定要受力均匀,两面平衡。

控制好金和锡的比例,这样焊接效果才好。

这种方法做出来的LED的热阻较小、散热较好、光效较高。

这种封装方式是上、下两面输入电流。

如果与热沉相连的一极是与热沉直接导电的,则热沉也成为一个电极。

因此连接热沉与散热片时要注意绝缘,而且需要使用导热胶把热沉与散热片粘连好。

使用这种LED要测试热沉是否与其接触的一极是零电阻,若为零电阻则是相通的,故与热沉相连加装散热片时要注意与散热片绝缘。

共晶点加热温度也称为共晶点。

温度的多少要根据金和锡的比例来定:·AuSn(金80%,锡20%):共晶点为282℃,加热时间控制在几秒钟之内。

·AuSn(金10%,锡90%):共晶点为217℃,加热时间控制在几秒钟之内。

·AgSn(银3.5%,锡96.5%):共晶点为232℃,加热时间控制在几秒钟之内。

1、倒装(Flip chip)1998年Lumileds公司封装出世界上第一个大功率LED(1W LUXOEN器件),使LED器件从以前的指示灯应用变成可以替代传统照明的新型固体光源,引发了人类历史上继白炽灯发明以来的又一场照明革命。

1WLUXOEN器件使LED的功率从几十毫瓦一跃超过1000毫瓦,单个器件的光通量也从不到1个lm飞跃达到十几个lm。

大功率LED 由于芯片的功率密度很高,器件的设计者和制造者必须在结构和材料等方面对器件的热系统进行优化设计。

FlipChip封装技术介绍

FlipChip封装技术介绍Flip Chip中文也叫倒晶封装或者覆晶封装,是一种先进的封装技术,有别于传统的将芯片放置于基板(chip pad)上,再用打线技术(wire bonding)将芯片与基板上的连接点连接。

Flip Chip技术是将芯片连接点长凸块(bump),然后将芯片翻转过来使凸块与基板(substrate)直接连接。

Flip Chip技术不是什么新技术,在上个世纪60年代由IBM研发出来,至于为什么会出现这种技术要从封装的历史说起,这里简单介绍下,传统的封装技术是将芯片(die)放置在引脚(lead frame)上,然后用金线将die上的pad和lead frame连接起来,这一步叫wire bond,但是这种技术封装出来的芯片面积会很大,已经不满足越来越小的智能设备,所以Flip Chip技术应用而生。

WB示意图提到Flip Chip封装技术,bump是不可避免要介绍下,工业上不可能把die切割出来以后再去长bump,所以在wafer切割成die之前要完成bump,因此这也被称为wafer level chip size package(WLCSP)。

FC示意图具体process steps参考维基百科上面的介绍:1.Integrated circuits are created on the wafer2.Pads are metallized on the surface of chips3.solder dot is deposited on each of the pads4.Chips are cut5.Chips are flipped and positioned so that the soler balls are facing the connectors on the external circuitry6.Solder balls are then remelted(typically using hot air reflow)7.Mounted chip is 'underfilled' using an electrically-insulating adhesive最后简单总结下Flip Chip的优点:1.更多的IO接口数量2.更小的封装尺寸3.更好的电气性能4.更好的散热性能5.更稳定的结构特性6.更简单的加工设备虽然优点很多,但是价格也很贵,主要原因是:1.芯片需要在AP层设计RDL用于连接bump,RDL的生产加工需要多一套工艺2.flip chip基板的生产加工,基板的工艺会更加精细,价格自然水涨船高。

倒装焊固晶工艺

芯片推力>2000g;

电性连接面接

触,可耐大电 流冲击

传统正装封装结构

倒装无金线封装结构

1 倒装结构LED芯片

低热阻,可大电流使用 结构及材料 大面积电极

物料 蓝宝石 银胶

导热系数(W/(m·K)) 35-36 2.5-30

蓝宝石层在芯片 下方,导热差

银胶热阻较高

`

Hale Waihona Puke 物料导热系数(W/(m·K))

金属合金

2 倒装焊固晶工艺

优点

成本低 工艺成熟 粘接强度高 效率高

工艺简单 粘接强度高 较好的导热性

优越的导热性 无焊剂

优越的导热性 工艺简单 粘接强度高

良好的导热性 良好的取光率

缺点 导热性差 挥发性

相对较低的导热性 粘度大,不均匀 挥发性 钎料溢出 孔洞 清洗 焊剂残留 孔洞 工艺复杂 效率低 粘接强度低

2 倒装焊固晶工艺

加热夹头可以显著减少孔洞 焊剂共晶在芯片中间有大的孔洞 加热夹头孔洞变得细小均匀

直接共晶 (加热焊盘)

焊剂共晶

直接共晶 (加热夹头和焊盘)

2 倒装焊固晶工艺

固晶质量

固晶方法 固晶材料

厚度

晶片倾斜

性能 孔洞 偏移

加热夹具共 AuSn20 晶焊

2μm

3μm

<10 1 mil %

晶片 支架

点胶

固晶

2 倒装焊固晶工艺

绝缘胶固晶

以绝缘胶在加热的条件下固化的方式粘合晶 片与支架 特点:1.粘接强度大2.绝缘胶透光可提升亮度

晶片 支架

绝缘胶点胶

固晶

固晶工艺

直接 共晶

焊剂 共晶

钎料 固晶

倒装芯片技术

倒装芯片工艺:通过焊料焊接 -02

回流焊接: 芯片凸点放置于沉积了焊膏或者焊剂的焊盘上,整个 基板浸入再流焊炉。

清洗 :焊剂残留。 测试:由于固化后不能维修,所以在填充前要进行测试。 底部填充:

通过挤压将低粘度的环氧类物质填充到芯片底部,然 后加热固化。

步 骤 示 意 图

底部填充示意图

倒装芯片工艺-通过热压焊接

由此模型可知:

要提高可靠性必须要求:

➢ 更高的焊点高度

➢ 更小的晶片

➢ 器件与基板的热膨胀系数(Coefficient of Thermal Expansion, CTE)相配

➢ 小的工作温度变化范围

倒装芯片工艺:通过焊料焊接-01

焊料沉积在基板焊盘上: 对于细间距连接,焊料通过电镀、焊料溅射或者 固体焊料等沉积方法。 很粘的焊剂可通过直接涂覆到基板上或者用芯片凸 点浸入的方法来保证粘附。 对于加大的间距(>0.4 mm ),可用模板印刷焊膏。

艺技术。95Pb5Sn凸点包围着电镀NiAu的铜球。后来制作 PbSn凸点,使用可控塌焊连接(Controlled collapse Component Connection, C4),无铜球包围。

2. Philoc-ford等公司制作出Ag-Sn凸点 3. Fairchield——Al凸点 4. Amelco——Au凸点 5. 目前全世界的倒装芯片消耗量超过年60万片,且以约50%的

电子制造技术基础

博士/教授 武汉光电国家实验室 光电材料与微纳制造部

倒装芯片(Flip Chip)技术

第一部分

倒装芯片简介

倒装芯片示意图

在典型的倒装芯片封装中, 芯片通过3到5个密耳 (mil)厚的焊料凸点连接到芯片载体上,底部填 充材料用来保护焊料凸点.

倒装芯片

倒装芯片:向主流制造工艺推进时间:2009-12-08来源:责任编辑:对较小外形和较多功能的低成本电子设备的需求继续在增长。

这些快速调整的市场挑战着电子制造商,降低制造成本以保证可接受的利润率。

倒装芯片装配(flip chip assembly)被认为是推进低成本、高密度便携式电子设备的制造所必须的一项技术。

在低成本应用中,倒装芯片的成功是因为它可达到相对于传统表面贴装元件包装更大的成本效益。

例如,一款新的寻呼机利用了倒装芯片技术将微控制器装配于PCB,因为倒装芯片使用较少的电路板空间,比传统的塑料球栅阵列(PBGA, plastic ball grid array)成本较低。

材料集成电路(Integraded circuit)在这款寻呼机中的集成电路(IC, integrated circuit)是一个5 x 5.6 mm 的微控制器,要求100个输入/输出(I/O)连接于PCB。

将四周I/O重新分配为2.5排减少点数(depopulated)的球栅阵列形式来接纳PCB的线/空格以及通路孔焊盘的限制。

锡球(bump)布局与间距如图一所示。

使用了电镀共晶锡/铅锡球,因为与其它的替代者比較,它的成本低得多。

锡球的直径大约为125 %26mu;m,球下金属(UBM, under bump metalization)为一个顾客要求的45%26mu;m的铜柱,如图二。

印刷电路板(PCB, printed circuit board)成本因素决定这款寻呼机的PCB的布局。

PCB是标准的FR-4,四个金属层和一个无电镀镍/金表面涂层。

因为增加材料成本和有限的可获得性,所以没有使用高密度互连(HDI, high-density interconnect)技术。

无电镀镍/金表面涂层满足所有作品的要求。

实录可靠性问题排除了选择有机可焊性保护层(OSP, organic solderability preservative),选择性镍-金的成本增加也没有吸引性。

flipchip工艺技术

flipchip工艺技术Flip Chip (反装工艺) 是一种将芯片直接与基板连接的先进封装技术,被广泛用于高性能电子产品的制造中。

Flip Chip 工艺技术具有诸多优点,包括更高的可靠性、更小的封装尺寸、更高的性能和更低的能耗。

本文将对 Flip Chip 工艺技术进行详细介绍。

Flip Chip 工艺技术通过将芯片的电路面朝下,直接与基板上的封装结构相连接,实现电气和热学性能的优化。

相比传统封装技术,Flip Chip 可以将芯片与基板紧密连接,减少了电路板上的电气和热学衰减,并且能够实现更短的信号传输路径,提高信号速度和稳定性。

此外,Flip Chip 还能够减少信号串扰和噪声,提高信号质量。

Flip Chip 工艺技术的另一个关键特点是其小封装尺寸。

由于芯片直接连接到基板上,不需要额外的封装结构,Flip Chip可以显著减小封装尺寸,提高芯片的集成度。

这对于如今越来越小型化的电子设备尤为重要。

Flip Chip 封装可以将多个芯片堆叠在一起,从而在有限的空间中实现更高的集成度,为电子产品的微型化提供了可能。

Flip Chip 工艺技术还具有更高的可靠性。

由于芯片与基板之间的连接是直接的,没有使用线缆或线路板连接器等中间元件,因此减少了信号传输的失真和可靠性问题。

此外,Flip Chip还可以通过提供更好的散热设计来延长芯片的使用寿命,降低过热导致的故障。

除了以上优点,Flip Chip 工艺技术还具有更高的性能和更低的能耗。

由于芯片与基板直接相连,Flip Chip 能够获得更短的信号路径,提高信号传输速度和稳定性。

同时,由于芯片的封装尺寸减小,信号的传输延迟也减小,从而提高整体系统性能。

此外,Flip Chip 能够实现更高的功率密度分布,降低能耗。

综上所述,Flip Chip 工艺技术在电子产品制造中具有重要的地位。

其优点包括更高的可靠性、更小的封装尺寸、更高的性能和更低的能耗。

LED倒装技术及工艺流程分析

LED倒装技术及工艺流程分析来源:光亚新世纪LED网时间:2015-02-06 【字体:大中小】1、引言发光二极管(LED)作为新型的绿色照明光源,具有节能、高效、低碳、体积小、反应快、抗震性强等优点,可以为用户提供环保、稳定、高效和安全的全新照明体验,已经逐步发展成为成熟的半导体照明产业。

近年来,全球各个国家纷纷开始禁用白炽灯泡,LED将会迎来一个黄金的增长期。

此外,近年来LED在电视机背光、手机、和平板电脑等方面的应用也迎来了爆发式的增长,LED具有广阔的应用发展前景。

2、倒装LED技术的发展及现状倒装技术在LED领域上还是一个比较新的技术概念,但在传统IC行业中已经被广泛应用且比较成熟,如各种球栅阵列封装(BGA)、芯片尺寸封装(CSP)、晶片级芯片尺寸封装(WLCSP)等技术,全部采用倒装芯片技术,其优点是生产效率高、器件成本低和可靠性高。

倒装芯片技术应用于LED器件,主要区别于IC在于,在LED芯片制造和封装过程中,除了要处理好稳定可靠的电连接以外,还需要处理光的问题,包括如何让更多的光引出来,提高出光效率,以及光空间的分布等。

针对传统正装LED存在的散热差、透明电极电流分布不均匀、表面电极焊盘和引线挡光以及金线导致的可靠性问题,1998年,J.J.Wierer等人制备出了1W倒装焊接结构的大功率AlGaInN-LED蓝光芯片,他们将金属化凸点的AIGalnN芯片倒装焊接在具有防静电保护二极管(ESD)的硅载体上。

图1是他们制备得到的LED芯片的图片和截面示意图。

他们的测试结果表明,在相同的芯片面积下,倒装LED芯片(FCLED)比正装芯片有着更大的发光面积和非常好的电学特性,在200-1000mA的电流范围,正向电压(VF)相对较低,从而导致了更高的功率转化效率。

图1 倒装结构的LED芯片图片和截面示意图2006年,O.B.Shchekin等人又报道了一种新的薄膜倒装焊接的多量子阱结构的LED(TFFC-LED)。

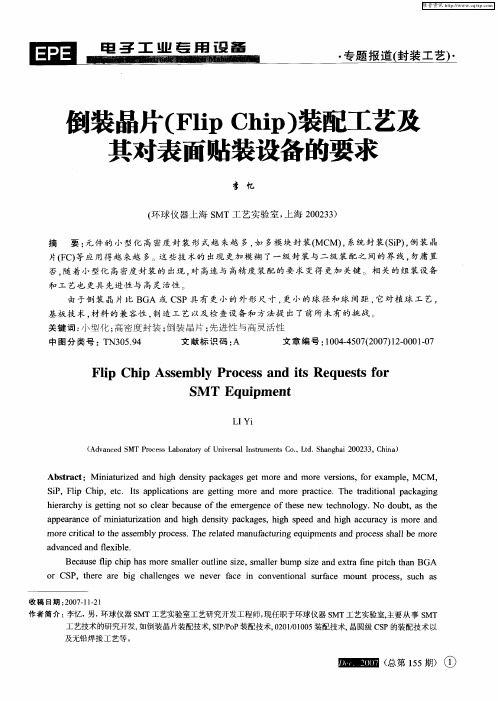

倒装晶片(Flip Chip)装配工艺及其对表面贴装设备的要求

墨■圄衄 ( 第1 期 总 5 )① 5

维普资讯

专题 报道 ( 装 工 艺) 封 ・

・

电 子 工 业 毫 用 设 备

■

b ump n e h ol g i g tc n o y,s bsr t e h o o y,t e c mpai lte ew e n m ae a s s e u tae t c n l g h o tbi i s b t e t r l,a s mbl p o e s i i y r c s ,

否 . 着 小型化 高密度 封 装 的 出现 , 高速 与 高精 度 装 配 的要 求 变得 更 加 关键 。相 关 的组 装 设备 随 对

和 工 艺也 更具 先进 性 与 高灵 活性 。

由于倒 装 晶 片比 B A 或 C P具 有 更 小 的 外 形 尺 寸 , 小 的球 径 和 球 间距 , 对植 球 工 艺 , G S 更 它 基板 技 术 , 材料 的 兼容 性 , 造 工 艺 以及 检 查 设备 和 方 法提 出 了前 所 未有 的挑 o e sL b r tr fUnv ra n t me t Co,L d S a g a 0 2 3 Ch n ) Ad a c d S r c s a o aoy o i e s lI sr u n s . t . h n h i2 0 3 , i a

摘 要 : 件 的 小 型化 高 密度 封 装 形 式越 来越 多 , 多模 块 封 装( M) 系统封 装 (i) 倒 装 晶 元 如 MC , SP ,

片fC 等应 用得 越 来越 多。这 些技 术 的 出现 更加 模 糊 了一 级 封装 与二 级 装 配之 间的界 线 , F) 勿庸 置

36.FLIP CHIP 工艺流程

Sn/Pb共晶 BUMP

FLIP CHIP 結构: 結构:

FLIP CHIP 結构: 結构:

成品舉例: 成品舉例:

Die Die

Bo ard Underfill

側面截面圖 助听器內部元件

FLIP CHIP 結构: 結构:

成品舉例: 成品舉例:

內存儲器

記憶芯片

FLIP CHIP 結构: 結构:

Foxconn

Technology

Groupபைடு நூலகம்

SMT Technology Center SMT 技術中心

SMT Technology Development Committee

目 錄

• • • • • FLIP CHIP定義 CHIP定義 FLIP CHIP技朮產生 CHIP技朮產生 FLIP CHIP結構 CHIP結構 FLIP CHIP工藝流程 CHIP工藝流程 FLIP CHIP現狀與未來 CHIP現狀與未來

FLIP CHIP技術產生

30年来,IBM生产了100亿件以上的C4产品, 30年来,IBM生产了100亿件以上的C4产品, 年来 生产了100亿件以上的C4产品 MTBF超过了10万小时,该技术采用了高铅的Pb/Sn焊 MTBF超过了10万小时,该技术采用了高铅的Pb/Sn焊 超过了10万小时 Pb/Sn 料制作凸点,如今又称焊料凸点FC。C4作为IBM的专 料制作凸点,如今又称焊料凸点FC。C4作为IBM的专 FC 作为IBM 利,一开始是用于高端领域,因此在业界并没有得到 一开始是用于高端领域, 大范围推广。直到九十年代, 大范围推广。直到九十年代, 随着各种新型封装技术的出现, 随着各种新型封装技术的出现, FC技术才真正被广泛采纳, FC技术才真正被广泛采纳,形式 技术才真正被广泛采纳 各异的FC产品也陆续登场。 各异的FC产品也陆续登场。 FC产品也陆续登场

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

为什么要用覆晶LED

覆晶焊技术支持的LED光源与传统封装光源相比,具有热阻低,电压低,大电流密度光效高的特点,综合研究表明覆晶LED光源在应用上有其独特的潜力和优势。

优点:

(1)、高可靠性,最稳定的SMT锡制程,承受拉力是传统LED的数十倍。

(2)、低热阻(3014热阻为40℃/W,倒装为5.8℃/W),高散热性,防止热量过高而烧坏晶片或荧光粉和封装胶。

(3)、无金线可实现多芯片的集成,特别是COB和高压LED灯源。

也有效的避免金线引起的各种风险,比如热膨胀使之断裂,外部冲击波或压力造成金钱断裂等优势。

(4)、导电面积大,内阻小,能承受大电流通过,减少因为内阻大引起的过大热量。

(5)、发光率高,发光角度大等优点。

(6)、封装工艺简化,降低封装成本,高提生产良率。

(7)、低光衰,不因为热引起的快速光衰,从而延长了芯片的寿命,是普通灯具的10倍以上

一、结构优势

??? 首先,相对于正装和垂直的芯片封装方式,覆晶封装没有金线存在,可以有效避免金线可能引起的各种风险。

下表为硅胶、金线、芯片的热膨胀系数值,其数量级的差距说明了硅胶热膨胀对金线的拉扯会造成可靠性的隐患。

?材料热膨胀系数

??? 其次,覆晶焊采用金属与金属直接接触的方式,其大电流散热能力比传统封装更好。

如图为传统封装与覆晶封装在散热通道方面的区别,传统正装封装通过蓝宝石和固晶银胶散热,覆晶焊通过金属通道散热,传统封装的蓝宝石和固晶胶成为散热瓶颈。

下表所示的数值为蓝宝石、固晶胶、金属三者在导热系数大小,三者对比明显可以发现覆晶焊金属导热通道的巨大优势。

材料导热系数

传统封装光源散热通道覆晶焊封装光源散热通道

??? 最后,覆晶焊的封装不存在金线的焊线弧度,能够实现超薄型的平面封装。

传统封装方式金线的拉力仅10g左右,而覆晶焊的接触面推力达到500g以上,覆晶封装可以抵抗一定的表面挤压而不影响LED的光电性能,适合于狭小的应用空间内。

例如手机、摄像机、背光等领域。

同时在多芯片的集成,均能发挥超薄易安装高集成的优势。

二、工艺优势

??? 覆晶焊技术平台的核心技术是覆晶工艺,Au80Sn20表面贴片回流共晶焊的覆晶技术有优势。

锡的导热系数为80W/m.K,可以在瞬间将大热量导出。

其次,倒装焊的芯片与支架的表面接触紧密,锡制程,是信赖度最高的制程,为倒装焊在导热率和散热接触面积上有更好的应用,适合LED快速散热的需求。

结论

结构原理上,无金线的覆晶封装技术可以有效避免金线带来的各种问题,具有更好的散热和耐大电流的性能,提供了更好的热导率和散热面积。

在此覆晶工艺基础上,可以方便实现高亮度需求的多芯片集成,COB(chip on board)模组等产品,充分发挥覆晶工艺、良率、可靠性的优势,一定是未来LED光源的主流应用。