isp往下拉就是图纸

常见的几种网络拓扑图绘制方法

常见的几种网络拓扑图绘制方法导语:常见的网络拓扑图绘制方法有哪些?其实网络图的画法主要是分为软件绘图和手工绘图。

对于新手而言,更推荐使用电脑软件绘图,只需要安装一个思维导图软件,就可以利用模板或者软件工具进行绘图,具体的请往下阅读。

免费获取网络拓扑图软件:/network/常见的几种网络拓扑图绘制方法?亿图网络图绘制作软件是由亿图软件公司推出的一款专门用来绘制电脑网络图的软件。

软件功能强大,容易上手,几乎包含所有网络图的绘制,例如基本网络图、网络拓扑图、Cisco网络图、机架图、网络通信图、3D网络图、AWS图等等,可以完美替代Visio。

软件采用拖拽的绘图方式,界面简单明了,操作方便,用户即看机即会,无需花费多少时间学习。

为了更大程度方便专业人士的使用,软件不仅提供各种专业图库,还提供海量模板,这点是其他软件无法比拟的。

强大的定制功能使得用户不仅可以自定义图形的填充和线条颜色,也可以自行绘制图库里的形状。

一键导出到PDF,Word, Visio, Png 等17种文件格式,无障碍与他人分享。

新版本不仅实现了跨平台,而且还支持云存储,使得团队协作更加容易。

亿图网络图绘制软件是您绘制网络图的不二选择。

亿图图示绘制“思科网络图”的特点1.专业的教程:亿图图示的软件为用户制作了使用教程的pdf以及视频。

2.可导出多种格式:导出的文件Html,PDF,SVG,Microsoft Word,PowerPoint,Excel等多种格式。

3.支持多系统:支持Windows,Mac 和Linux的电脑系统,版本同步更新。

4.软件特色:智能排版布局,拖曳式操作,兼容Office。

5.云存储技术:可以保存在云端,不用担心重要的数据图表丢失。

6.丰富的图形符号库助你轻松设计思科网络图如何绘制一个网络拓扑图呢?步骤一:打开绘制网络拓扑图的新页面双击打开网络拓扑图制作软件点击‘可用模板’下标题类别里的‘网络图’。

双击打开一个绘制网络拓扑图的新页面,进入编辑状态。

VISI指令介绍(DOC)

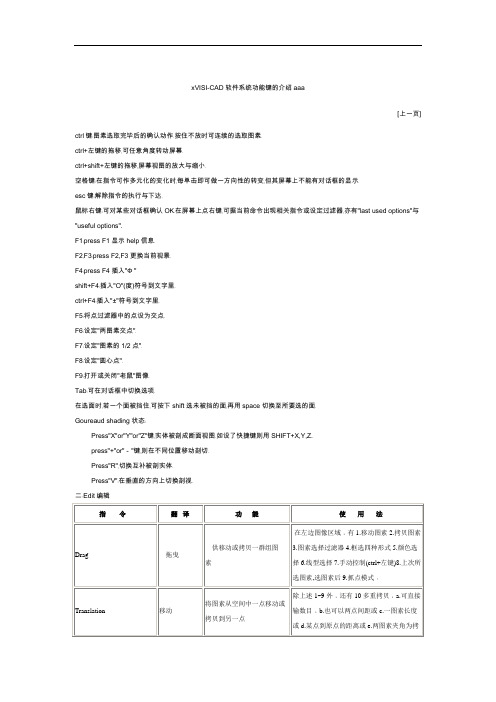

xVISI-CAD软件系统功能键的介绍aaa[上一页] ctrl键﹕图素选取完毕后的确认动作﹒按住不放时可连续的选取图素﹒ctrl+左键的拖移﹐可任意角度转动屏幕﹒ctrl+shift+左键的拖移﹐屏幕视图的放大与缩小﹒空格键﹕在指令可作多元化的变化时﹐每单击即可做一方向性的转变﹐但其屏幕上不能有对话框的显示﹒esc键﹕解除指令的执行与下达﹒鼠标右键﹕可对某些对话框确认OK﹒在屏幕上点右键﹐可据当前命令出现相关指令或设定过滤器﹐亦有"last used options"与"useful options".F1﹕press F1显示help信息﹒F2﹐F3﹕press F2,F3更换当前视景﹒F4﹕press F4插入"Ф"shift+F4﹕插入"O"(度)符号到文字里﹒ctrl+F4﹕插入"±"符号到文字里﹒F5﹕将点过滤器中的点设为交点﹒F6﹕设定"两图素交点"﹒F7﹕设定"图素的1/2点"﹒F8﹕设定"圆心点"﹒F9﹕打开或关闭"老鼠"图像﹒Tab﹕可在对话框中切换选项﹒在选面时﹐若一个面被挡住﹐可按下shift选未被挡的面﹐再用space切换至所要选的面﹒Goureaud shading状态﹕Press"X"or"Y"or"Z"键﹐实体被剖成断面视图﹒如设了快捷键则用SHIFT+X,Y,Z.press"+"or"-"键﹐则在不同位置移动剖切﹒Press"R"﹐切换互补被剖实体﹒Press"V"﹕在垂直的方向上切换剖视﹒二﹑Edit编辑三﹑Wireframe线架构四﹑solid基本实体五 Operation编辑实体六﹑ Modeling塑造实体七﹑Annotation尺寸标注八﹑ System系统九﹑Window窗口十﹒?查询返回@ 旋转﹐平移﹐镜像后的刀路如再删改将会还原到原来形状。

isp 图像处理流程

isp 图像处理流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!1. 图像传感器采集:图像传感器(如 CMOS 或 CCD)将光信号转换为电信号,生成原始的图像数据。

PCB板 烧录方式

单片机ISP、IAP和ICP几种烧录方式的区别玩单片机的都应该听说过这几个词。

一直搞不太清楚他们之间的区别。

今天查了资料后总结整理如下。

ISP:In System Programing,在系统编程IAP:In applicating Programing,在应用编程ICP:In Circuit Programing,在电路编程ISP是指可以在板级上进行编程,也就是不用拆芯片下来,写的是整个程序,一般是通过ISP接口线来写。

IAP虽然同样也是在板级上进行编程,但是是自已对自已进行编程,在应用中进行编程,也即可以只是更改某一部分而不影响系统的其它部分,另外接口程序是自已写的,这样可以进行远程升级而不影响应用。

打个比喻吧:1、ISP是把房子拆了再重造一间,那么在造好之前当然是不能住人的啦!2、IAP是在造好的房子里边进行一些装修,当然人可以继续住啦!ICP是在电路编程,是LPC芯片的编程方式,相当于ATMEL的ISP,而LPC的ISP就相当于ATMEL的IAP了。

ISP于IAP的区别ISP:in system programming, 在系统编程IAP: in applicatin programming 在应用编程但两者的操作方式,结果和应用场合有什么区别什么是ISP:用写入器将code烧入,不过,芯片可以在目标板上,不用取出来,在设计目标板的时候就将接口设计在上面,所以叫"在系统编程",即不用脱离系统;什么是IAP:在应用编程,有芯片本身(或通过外围的芯片)可以通过一系列操作将code写入,比如一款支持Iap的单片机,内分3个程序区,1作引导程序区,2作运行程序区,3作下载区,芯片通过串口接收到下载命令,进入引导区运行引导程序,在引导程序下将new code内容下载到下载区,下载完毕并校验通过后再将下载区内容复制到2区,运行复位程序,则Iap完成;应用场合:1,ISP 程序升级需要到现场解决,不过好一点的是不必拆机器了;2,IAP 如果有网管系统的话,用网管下载一切搞定,人不用跑来跑去,这可能是他们的优点或应用吧在线编程目前有两种实现方法:在系统编程(ISP)和在应用编程(IAP)。

化工工艺图识图基础知识

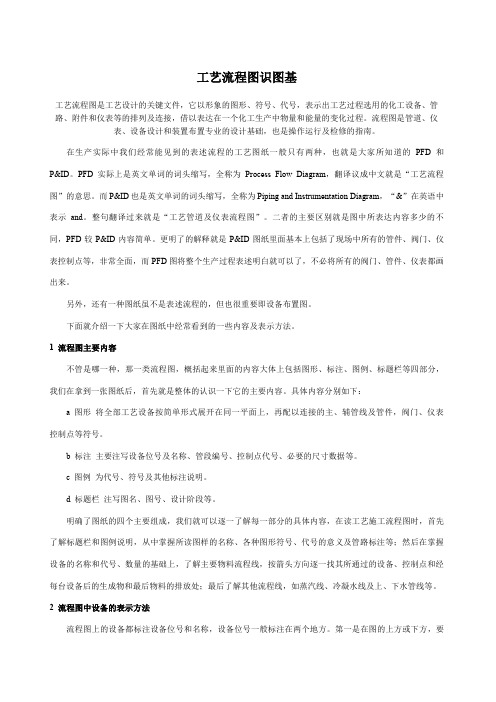

工艺流程图识图基工艺流程图是工艺设计的关键文件,它以形象的图形、符号、代号,表示出工艺过程选用的化工设备、管路、附件和仪表等的排列及连接,借以表达在一个化工生产中物量和能量的变化过程。

流程图是管道、仪表、设备设计和装置布置专业的设计基础,也是操作运行及检修的指南。

在生产实际中我们经常能见到的表述流程的工艺图纸一般只有两种,也就是大家所知道的PFD和P&ID。

PFD实际上是英文单词的词头缩写,全称为Process Flow Diagram,翻译议成中文就是“工艺流程图”的意思。

而P&ID也是英文单词的词头缩写,全称为Piping and Instrumentation Diagram,“&”在英语中表示and。

整句翻译过来就是“工艺管道及仪表流程图”。

二者的主要区别就是图中所表达内容多少的不同,PFD较P&ID内容简单。

更明了的解释就是P&ID图纸里面基本上包括了现场中所有的管件、阀门、仪表控制点等,非常全面,而PFD图将整个生产过程表述明白就可以了,不必将所有的阀门、管件、仪表都画出来。

另外,还有一种图纸虽不是表述流程的,但也很重要即设备布置图。

下面就介绍一下大家在图纸中经常看到的一些内容及表示方法。

1 流程图主要内容不管是哪一种,那一类流程图,概括起来里面的内容大体上包括图形、标注、图例、标题栏等四部分,我们在拿到一张图纸后,首先就是整体的认识一下它的主要内容。

具体内容分别如下:a 图形将全部工艺设备按简单形式展开在同一平面上,再配以连接的主、辅管线及管件,阀门、仪表控制点等符号。

b 标注主要注写设备位号及名称、管段编号、控制点代号、必要的尺寸数据等。

c 图例为代号、符号及其他标注说明。

d 标题栏注写图名、图号、设计阶段等。

明确了图纸的四个主要组成,我们就可以逐一了解每一部分的具体内容,在读工艺施工流程图时,首先了解标题栏和图例说明,从中掌握所读图样的名称、各种图形符号、代号的意义及管路标注等;然后在掌握设备的名称和代号、数量的基础上,了解主要物料流程线,按箭头方向逐一找其所通过的设备、控制点和经每台设备后的生成物和最后物料的排放处;最后了解其他流程线,如蒸汽线、冷凝水线及上、下水管线等。

PS处理图片的技巧

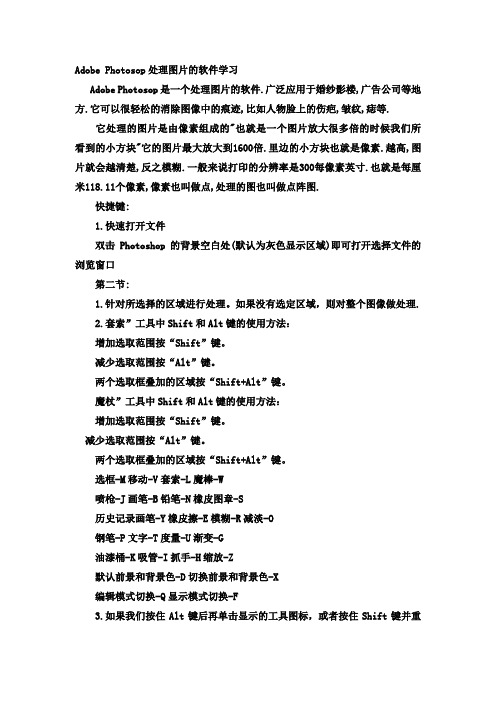

Adobe Photosop处理图片的软件学习Adobe Photosop是一个处理图片的软件.广泛应用于婚纱影楼,广告公司等地方.它可以很轻松的消除图像中的痕迹,比如人物脸上的伤疤,皱纹,痣等.它处理的图片是由像素组成的"也就是一个图片放大很多倍的时候我们所看到的小方块"它的图片最大放大到1600倍.里边的小方块也就是像素.越高,图片就会越清楚,反之模糊.一般来说打印的分辨率是300每像素英寸.也就是每厘米118.11个像素,像素也叫做点,处理的图也叫做点阵图.快捷键:1.快速打开文件双击Photoshop的背景空白处(默认为灰色显示区域)即可打开选择文件的浏览窗口第二节:1.针对所选择的区域进行处理。

如果没有选定区域,则对整个图像做处理.2.套索”工具中Shift和Alt键的使用方法:增加选取范围按“Shift”键。

减少选取范围按“Alt”键。

两个选取框叠加的区域按“Shift+Alt”键。

魔杖”工具中Shift和Alt键的使用方法:增加选取范围按“Shift”键。

减少选取范围按“Alt”键。

两个选取框叠加的区域按“Shift+Alt”键。

选框-M移动-V套索-L魔棒-W喷枪-J画笔-B铅笔-N橡皮图章-S历史记录画笔-Y橡皮擦-E模糊-R减淡-O钢笔-P文字-T度量-U渐变-G油漆桶-K吸管-I抓手-H缩放-Z默认前景和背景色-D切换前景和背景色-X编辑模式切换-Q显示模式切换-F3.如果我们按住Alt键后再单击显示的工具图标,或者按住Shift键并重复按字母快捷键则可以循环选择隐藏的工具。

4.获得精确光标按Caps Lock键可以使画笔和磁性工具的光标显示为精确十字线,再按一次可恢复原状。

5.显示/隐藏控制板按Tab键可切换显示或隐藏所有的控制板(包括工具箱),如果按Shift+Tab 则工具箱不受影响,只显示或隐藏其他的控制板。

6.快速恢复默认值点按选项栏上的工具图标,然后从上下文菜单中选取“复位工具”或者“复位所有工具”第三节:7.自由控制大小缩放工具的快捷键为“Z”,此外“Ctrl+空格键”为放大工具,“Alt+空格键”为缩小工具,但是要配合鼠标点击才可以缩放;相同按Ctrl+“+”键以及“-”键分别也可为放大和缩小图像;Ctrl+Alt+“+”和Ctrl+Alt+“-”可以自动调整窗口以满屏缩放显示使用抓手工具时,按住空格键后可转换成手形工具,即可移动视窗内图像的可见范围。

电路图纸-ISP下载线是指什么

第三届大器晚成(297258330) 14:40:37这些应该就够用的了吧。

还用到用别的仿真器?你们做的什么那么复杂的。

野原罂彩(305407212) 14:40:4846的可以软仿么?第三届大器晚成(297258330) 14:41:06能吧野原罂彩(305407212) 14:41:33东西你们都有么?第三届大器晚成(297258330) 14:41:56硬防比较好的。

有毛病直接能看出来的第三届大器晚成(297258330) 14:42:14软放有些还是做不了的。

看不出毛病来的。

用软仿373149491(373149491) 14:42:09C译器在哪下载啊科大测量(47801748) 14:42:24集成开发环境里面带的,第三届大器晚成(297258330) 14:42:30对啊科大测量(47801748) 14:42:29不喜欢软件仿真第三届大器晚成(297258330) 14:42:49对。

还是硬防比较好。

科大测量(47801748) 14:42:59大伙机器上都有并口吗?第三届大器晚成(297258330) 14:43:05有啊第三届大器晚成(297258330) 14:43:10你的没有吗第三届大器晚成(297258330) 14:43:06哈哈科大测量(47801748) 14:43:38有,被我整残废了,所以这届可能不做了第三届大器晚成(297258330) 14:44:05呵呵。

第三届大器晚成(297258330) 14:44:03呵呵。

你买个转usb的看看科大测量(47801748) 14:44:17做完上届题目后,有一天在并口上试别人做的一个电路,可能是回进去电流了,并口就伤残了科大测量(47801748) 14:44:33USB转的并口是不能用的,在HT-ICE上第三届大器晚成(297258330) 14:44:35呵呵。

倒霉啊。

第三届大器晚成(297258330) 14:44:51有的能用。

西门子 SIMATIC 组态硬件和通讯连接, STEP 7 V5.3 版本 手册

更多支持

如果有任何技术问题,请联系西门子代表或代理商。 您可以在下列网页中查找联系人: /automation/partner

培训中心

西门子提供了很多培训教程,帮助您熟悉 SIMATIC S7 自动化系统。请联系当地的 培训中心,或位于德国纽伦堡(D 90327)的培训总部,以获取详细信息。 电话: 网址: +49 (911) 895-3200.

在线帮助中的主题“新增内容?”中极好地概括和介绍了最新的 STEP 7 新内容。

组态硬件和通讯连接,STEP 7 V5.3 版本 A5E00446503-01

iii

前言

STEP 7 文档包

本手册是文档包“STEP 7 基本信息”的一部分。 下表显示了 STEP 7 文档的总览:

文档 STEP 7 基础信息 • • • • • • STEP 7 V5.3,使用入门手册 使用 STEP 7 V5.3 编程 组态硬件和通讯连接,STEP 7 V5.3 版 本 从 S5 到 S7,变频器手册 用于 S7-300/400 的梯形图(LAD)/功能 块图(FBD)/语句表(STL)手册 S7-300/400 的标准功能及系统功能 提供了参考信息,并描述了编程语 6ES7810-4CA07-8BW1 言 LAD、FBD、STL、标准功能以 及系统功能,扩充了 STEP 7 基础 信息的范围。 用途 订货号

亚洲/澳洲(北京) 技术支持和授权

当地时间: 周一至周五, 8:00 - 5:00 PM 电话: 传真: +86 10 64 75 75 75 +86 10 64 74 74 74 格林威治 标准时间: +8:00

电子邮件: adsupport@

电子邮件: simatic.hotline@

绘制拓扑图的工作原理

绘制拓扑图的工作原理

绘制拓扑图的工作原理通常包括以下步骤:

1.确定网络拓扑结构:首先需要明确所要绘制的网络的拓扑结构,包括网络中的设备和它们之间的连接方式。

2.收集设备信息:需要收集网络拓扑中的各个设备的详细信息,包括设备的名称、IP地址、MAC地址、操作系统等。

3.绘制节点:根据收集到的设备信息,绘制网络拓扑中的各个节点,如交换机、路由器、服务器等。

4.建立连接:根据设备之间的物理连接和逻辑连接,用线条或箭头等方式绘制节点之间的连接,表示它们之间的通信关系。

5.标注信息:在绘制拓扑图的同时,需要对节点和连接进行注释,包括节点的名称、IP地址、MAC地址等,以及连接的类型、速率等相关信息。

6.更新和维护:随着网络的变化,绘制的拓扑图需要不断地更新和维护,及时地反映网络的实际情况。

以上就是绘制拓扑图的基本工作原理,通过一系列步骤,可以清晰地展示网络拓

扑结构,帮助管理员和用户更好地管理和维护网络。

单片机并口下载线的原理与调试

_4下慧线的谭试和故障检惨-一-

调试下载线时.首先要保证目标板上的单片机可

最后的原因是电缆太长。

般制作下载线时都是把缓

冲芯片装在并1:3插头的壳内.而连线是在缓冲芯片和

以正常运行。也可以不断开六针插头和单片机目标板

5、保存设置。

-2.并Ⅱ镪橙飘一三|||I薯I薯2三I|

设置好了并行接口并不能保证并行接13一定能用. 最好对并行接1:3进行一下检测。有个并口调试软件对 检测并口是个很好的帮助.如图3。 分别在上面输出框的1—9、14、16、17脚前点 上勾。并用万用表测量对应的并口脚.当勾上时为高 电平(5V l,去掉勾为低电平(0v 1.就说明并行接1:3

ቤተ መጻሕፍቲ ባይዱ

出端,D0~D7为数据输^端。当三态输出允许控制端 0E为高电平时.Q0~Q7呈高阻状态.即不能驱动总 线.也不作为总线的负载,但锁存器内部的逻辑操作不 受影响。当OE为低电平时.Q0~Q7为正常逻辑状态.

可用来驱动负载或总线。此时.当锁存允许端LE为高 电平时,0随数据D而变。当LE为低电平时.0就被

指在用户设计的目标系统中或印刷电路板上配置的是 空白器件.对空白器件写人用户代码进行编程或反复 编程时.不需要把器件离开目标板插^编程器单独编 程,而是通过SP[等接1:3.接收上位机传来的数据. 并对单片机内部的Flash存储器进行编程。因为在设 计目标板的时候就将接口设计在上面,所以叫“在系 统编程”。 这个功能的优势在于编程时仅需一个非常简单的 转换电路和一条导线就可以把单片机和上位机连在一

-1

74

74LS373"F巍钱量。=…囊一≥曼矗兰

ispDesignEXPERT教程-中文

目录第一节ispDesignEXPERT 简介第二节ispDesignEXPERT System 的原理图输入第三节设计的编译与仿真第四节ABEL 语言和原理图混合输入第五节ispDesignEXPERT System 中 VHDL 和Verilog 语言的设计方法第六节在系统编程的操作方法第七节ModelSim 的使用方法附录一ispDesignEXPERT System 上机实习题附录二ispDesignEXPERT System 文件后缀及其含义第一节ispDesignEXPERT 简介ispDesignEXPERT 是一套完整的 EDA 软件设计输入可采用原理图硬件描述语言混合输入三种方式能对所设计的数字电子系统进行功能仿真和时序仿真编译器是此软件的核心能进行逻辑优化将逻辑映射到器件中去自动完成布局与布线并生成编程所需要的熔丝图文件软件支持所有 Lattice 公司的ispLSI 和 MACH 器件软件主要特征1输入方式*原理图输入*ABEL-HDL 输入*VHDL 输入*Verilog-HDL 输入2.逻辑模拟*功能模拟*时序模拟3.编译器*结构综合映射自动布局和布线4.支持的器件*含有支持 ispLSI 的宏库及 MACH 的 TTL 库*支持所有 ispLSI MACH 器件第二节 ispDesignExpert System 的原理图输入I.启动 ispDesignExpert System ( 按 Start=>Programs=>LatticeSemiconductor=>ispDesignEXPERT System 菜单)II.创建一个新的设计项目A.选择菜单 FileB.选择 New Project...C.键入项目名 c:\user\demo.synD.你可以看到默认的项目名和器件型号: Untitled and ispLSI5384V-125LB388III.项目命名A.用鼠标双击UntitledB.在 Title 文本框中输入“Demo Project”, 并选 OKIV.选择器件A.双击 ispLSI ispLSI5384V-125LB388, 你会看到 Choose Device 对话框( 如下图所示)B.在 Choose Device 窗口中选择 ispLSI1000 项C.按动器件目录中的滚动条直到找到并选中器件 ispLSI 1032E-70LJ84D.揿 OK 按钮选择这个器件V.在设计中增加源文件一个设计项目由一个或多个源文件组成这些源文件可以是原理图文件 (*.sch)ABEL HDL 文件(*.abl) VHDL 设计文件(*.vhd)Verilog HDL 设计文件(*.v)测试向量文件 (*.abv) 或者是文字文件(*.doc, *.wri, *.txt)在以下操作步骤中你要在设计项目中添加一张空白的原理图纸A.从菜单上选择 Source 项B.选择 New...C.在对话框中选择 Schematic ( 原理图)并按 OKD.选择路径: c:\ user 并输入文件名 demo.schE.确认后揿 OKVI.原理图输入你现在应该进入原理图编辑器在下面的步骤中你将要在原理图中画上几个元件符号并用引线将它们相互连接起来A.从菜单栏选择 Add , 然后选择Symbol你会看到如下图所示的对话框B.选择 GATES.LIB 库然后选择 G_2AND 元件符号C.将鼠标移回到原理图纸上注意此刻 AND 门粘连在你的光标上并随之移动D.单击鼠标左键将符号放置在合适的位置E.再在第一个 AND 门下面放置另外一个 AND 门F.将鼠标移回到元件库的对话框并选择 G_2OR 元件G.将 OR 门放置在两个 AND 门的右边H.现在选择 Add 菜单中的 Wire 项I.单击上面一个 AND 门的输出引脚并开始画引线J.随后每次单击鼠标便可弯折引线 ( 双击便终止连线)K.将引线连到 OR 门的一个输入脚L.重复上述步骤连接下面一个 AND 门VII.添加更多的元件符号和连线A.采用上述步骤从REGS.LIB库中选一个g_d寄存器并从IOPADS.LIB库中选择G_OUTPUT符号B.将它们互相连接实现如下的原理图VIII.完成你的设计在这一节通过为连线命名和标注 I/OMarkers 来完成原理图当要为连线加信号名称时你可以使用 ispDesignEXPERT 的特点同时完成两件事 ----- 同时添加连线和连线的信号名称这是一个很有用的特点可以节省设计时间 I/O Markers 是特殊的元件符号它指明了进入或离开这张原理图的信号名称注意连线不能被悬空(dangling)它们必需连接到 I/O Marker 或逻辑符号上这些标记采用与之相连的连线的名字与 I/O Pad 符号不同将在下面定义属性(Add Attributes) 的步骤中详细解释A.为了完成这个设计选择 Add 菜单中的 Net Name 项B.屏幕底下的状态栏将要提示你输入的连线名输入‘A’并按Enter 键连线名会粘连在鼠标的光标上C.将光标移到最上面的与门输入端并在引线的末连接端( 也即输入脚左端的红色方块)按鼠标左键并向左边拖动鼠标这可以在放置连线名称的同时画出一根输入连线D.输入信号名称现在应该是加注到引线的末端E.重复这一步骤直至加上全部的输入‘B’,’C’,’D’和‘CK’以及输出‘OUT’F.现在 Add 菜单的 I/O Marker 项G.将会出现一个对话框请选择 InputH.将鼠标的光标移至输入连线的末端 ( 位于连线和连线名之间)并单击鼠标的左键这时回出现一个输入 I/O Marker标记里面是连线名I.鼠标移至下一个输入重复上述步骤直至所有的输入都有I/O MarkerJ.现在请在对话框中选择 Output, 然后单击输出连线端加上一个输出 I/O MarkerK.至此原理图就基本完成它应该如下图所示IX.定义 ispLSI 器件的属性 (Attributes)你可以为任何一个元件符号或连线定义属性在这个例子中你可以为输出端口符号添加引脚锁定 LOCK 的属性请注意在ispDesignEXPERT 中引脚的属性实际上是加到 I/O Pad 符号上而不是加到 I/O Marker 上同时也请注意只有当你需要为一个引脚增加属性时才需要 I/O Pad 符号否则你只需要一个 I/O Marker.A.在菜单条上选择 Edit => Attribute => Symbol Attribute 项这时会出现一个 Symbol Attribute Editor 对话框B.单击需要定义属性的输出 I/O Pad.C.对话框里会出现一系列可供选择的属性D.选择 Synario Pin 属性并且把文本框中的‘*’替换成‘4’.E.关闭对话框F.请注意此时数字‘4’出现在 I/O Pad 符号内X.保存以完成的设计从菜单条上选择 File并选 Save 命令再选 Exit 命令第 三 节设 计 的 编 译 与 仿 真I. 建 立 仿 真 测 试 向 量 ( Simulation Test Vectors)A.在 已 选 择 ispLSI1032E-70LJ84 器 件 的 情 况 下 选 择 Source 菜 单 中的 New... 命 令B.在 对 话 框 中 选 择 ABEL Test Vectors 并 按OK C.输 入 文 件 名 demo.abv 作 为 你 的 测 试 向 量 文 件 名D. 按OKE.文 本 编 辑 器 弹 出 后 输 入 下 列 测 试 向 量 文 本F.完 成 后 选 择 File 菜 单 中 的 Save 命 令 以 保 留 你 的 测 试 向 量文 件G.再 次 选 择File 并 选 Exit 命 令H.此 时 你 的 项 目 管 理 器 (Project Navigator) 应 如 下 图 所 示module demo;c,x = .c.,.x.;CK,A,B,C,D,OUT PIN;TEST_VECTORS([CK, A, B, C, D]->[OUT])[ c , 0 , 0 , 0 ,0 ]->[ x ];[ c , 0 , 0 , 1 ,0 ]->[ x ];[ c , 1 , 1 , 0 ,0 ]->[ x ];[ c , 0 , 1 , 0 ,1 ]->[ x ];ENDII.编译原理图与测试向量现在你已为你的设计项目建立起所需的源文件下一步是执行每一个源文件所对应的处理过程选择不同的源文件你可以从项目管理器窗口中观察到该源文件所对应的可执行过程在这一步请你分别编译原理图和测试向量A.在项目管理器左边的项目源文件 ( Sources in Project ) 清单中选择原理图 (demo.sch)B.双击原理图编译 (Compile Schematic) 处理过程这时会出现一个如下的对话框C.编译通过后 Compile Schematic 过程的左边会出现一个绿色的查对记号以表明编译成功编译结果将以逻辑方程的形式表现出来D.然后从源文件清单中选择测试向量源文件 (demo.abv)E.双击测试向量编译 (Compile Test Vectors ) 处理过程这时会出现另一个状态对话框III.设计的仿真ispDesignExpert 开发系统较先前的 ISP Synario 开发系统而言在仿真功能上有了极大的改进它不但可以进行功能仿真(Functional Simulation)而且可以进行时序仿真 (Timing Simulation)在仿真过程中还提供了单步运行断点设置功能IV.一功能仿真A. 在 ispDesignEXPERT System Project Navigator 的主窗口左侧选择测试向量源文件 (demo.abv)双击右侧的 Functional Simulation 功能条将弹出如下图所示的仿真控制窗口 (Simulator ControlPanel)B. 在 Simulator Control Panel 中将根据 (*.abv) 文件中所给出的输入波形进行一步到位的仿真在 Simulator Control Panel 中按 Simulator=>Run, 再按 Tools => Waveform Viewer 菜单将打开波形观察器 Waveform Viewer 如下图所示C. 波形现在都显示在波形观察器的窗口中如下图所示D. 单步仿真选 Simulator Control Panel 窗口中的 Simulator=>Step可对您的设计进行单步仿真 ispDesignEXPERT 系统中仿真器的默认步长为 100ns您可根据需要在按 File=>Setup 菜单所激活的对话框 (Setup Simulator) 中重新设置您所需要的步长按Simulator Control Panel 窗口中的 File=>Reset 菜单可将仿真状态退回至初始状态 (0 时刻 )随后每按一次 Step 仿真器便仿真一个步长下图是按了七次 Step 钮后所显示的波形( 所选步长为 100ns )E. 设置断点 (Breakpoint)在 Simulator Control Panel 窗口中按Signal=>Breakpoints 菜单会显示如下图所示的断点设置控制的 Breakpoint 窗口在该窗口中按 New 按钮开始设置一个新的断点在 Available Signals 栏中单击鼠标选择所需的信号在窗口中间的下拉滚动条中可选择设置断点时该信号的变化要求例如 ->0指该信号变化到 0 状态!=1指该信号处于非 1状态一个断点可以用多个信号所处的状态来作为定义条件这些条件在逻辑上是与的关系最后在 Breakpoints 窗口中, 先选中 ADD再按 Arm 按钮使所设断点生效本例中选择信号 OUT->? 作为断点条件其意义是指断点条件成立的条件为 OUT 信号发生任何变化 ( 变为 01Z 或 X 状态)这样仿真过程中在 0ns,700ns,1000ns 时刻都会遇到断点F. 波形编辑 (Waveform Edit)除了用 *.abv 文件描述信号的激励波形外ispDesignEXPERT 系统还提供了直观的激励波形的图形输入工具 Waveform Editor以下是用 Waveform Editor 编辑激励波形的步骤 ( 仍以设计demo.sch 为例)1. 在 Simulator Cotrol Panel 窗口中按 Tools=>Waveform Editor 菜单进入波形编辑器窗口(Waveform Editing Tool)如下图所示2. 在上述窗口中按 Object=>Edit Mode将弹出如下图所示的波形编辑子窗口3. 在 Waveform Editing Tool 窗口中按 Edit=>New Wave 菜单弹出如下窗口在该窗口中的 Polarity 选项中选择 Input然后在窗口下部的空格中输入信号名A B C D CK每输完一个信号名按一次 Add 钮4. 在完成上述步骤 3 以后 Waveform Editing Tool 窗口中有了A B C D CK 的信号名如下图所示单击窗口左侧的信号名 A开始编辑 A 信号的激励波形单击 0 时刻右端且与 A 信号所处同一水平位置任意一点波形编辑器子窗口中将显示如下信息在 States 栏中选择 Low在 Duration 栏中填入 200ns并按回车键这时在 Waveform Editing Tool 窗口中会显示A 信号在 0-200ns 区间为 0 的波形然后在 Waveform EditingTool 窗口中单击 200ns 右侧区间任一点可在波形编辑器的子窗口中编辑 A 信号的下一个变化重复上述操作过程编辑所有输入信号 A B C D CK 的激励波形并将它存盘为 wave_in.wdl 文件完成后Waveform Editing Tool 窗口如下图所示5. 在 Waveform Editing Tool 菜单中按 File=>Consistency Check 菜单检测激励波形是否存在冲突在该例中错误信息窗口会提示 No Errors Dected6. 至此激励波形已描述完毕剩下的工作是调入该激励文件 (wave_in.wdl) 进行仿真回到 ispEXPERT System Project Navigator 主窗口按Source=>import 菜单调入激励文件 wave_in.wdl在窗口左侧的源程序区选中 Wave_in.wdl 文件双击窗口右侧的Functional Simulation 栏进入功能仿真流程以下的步骤与用 *.abv 描述激励的仿真过程完全一致在此不再赘述二时序仿真 (Timing Simulation)时序仿真的操作步骤与功能仿真基本相似以下简述其操作过程中与功能仿真的不同之处仍以设计 Demo 为例在 ispDesignEXPERT System Project Navigator 主窗口中在左侧源程序区选中 Demo.abv双击右侧的 Timing Simulation 栏进入时序仿真流程由于时序仿真需要与所选器件有关的时间参数因此双击 Timing Simulation 栏后软件会自动对器件进行适配然后打开与功能仿真时间相同的 Simulator Control Panel 窗口时序仿真与功能仿真操作步骤的不同之处在于仿真的参数设置上在时序仿真时打开 Simulator Control Panel 窗口中的 File=>Setup 菜单产生 Setup Simulator 对话框在此对话框中可设置延时参数 (Simulation Delay) 最小延时 (Minimun Delay)典型延时 (Typical Delay)最大延时(Maximun Delay) 和 0 延时 (Zero Delay)最小延时是指器件可能的最小延时时间0 延时指延时时间为 0需要注意的是在 ispDesignExpert 系统中典型延时的时间均设为 0 延时在 Setup Simulator 对话框中仿真模式 (Simulation Mode) 可设置为两种形式惯性延时 (Inertial Mode) 和传输延时 (Transport Mode)将仿真参数设置为最大延时和传输延时状态在Waveform Viewer 窗口中显示的仿真结果如下图所示由图可见与功能仿真不同的是输出信号 OUT 的变化比时钟 CK 的上升沿滞后了 8nsIV. 建立元件符号 (Symbol)ispExpert 工具的一个非常有用的特点是能够迅速地建立起一张原理图的符号通过这一步骤你可以建立一个可供反复调用的逻辑宏元件以便放置在更高一层的原理图纸上下一节将指导你如何调用这里仅教你如何建立元件符号A.双击原理图的资源文件 demo.sch把它打开B.在原理图编辑器中选择 File 菜单C.从下拉菜单中选择 Matching Symbol 命令D.关闭原理图E.至此这张原理图的宏元件符号已经建立完毕并且被加到元件表中你可以在下一节中调用这个元件第四节 ABEL 语言和原理图混合输入这一节你要建立一个简单的 ABEL HDL 语言输入的设计并且将其与上一节中完成的原理图进行合并以层次结构的方式画在顶层的原理图上然后对这个完整的设计进行仿真编译最后适配到 ispLSI 器件中现在我们就开始吧I启动 ispDesignEXPERT System如果你在上一节的练习后退出了 ispDesignEXPERT System点击Start=>Programs=>Lattice Semiconductor=>ispDesignEXPERT System 菜单屏幕上你的项目管理器应该如下图所示I.I I 建立顶层的原理图A.仍旧选择 1032E 器件从菜单条上选 SourceB.选择 New...C.在对话框中选 Schematic并按 OKD.选择路径c:\ user 然后在文本框中输入文件名 top.sch并按 OKE.现在你就进入了原理图编辑器F.调用上节中创建的元件符号选择 Add 菜单中的 Symbol项这时会出现 Symbol Libraries 对话框选择 Local 的库你会注意到在下部的文本框中有一个叫 demo 的元件符号这就是你在上一节中自行建立的元件符号G.选择 demo 元件符号并放到原理图上的合适位置II.建立内含 ABEL 语言的逻辑元件符号现在你要为 ABEL HDL 设计文件建立一个元件符号只要知道了接口信息你就可以为下一层的设计模块创建一个元件符号而实际的 ABEL 设计文件可以在以后再完成A.在原理图编辑器里选择 ADD 菜单里的 New Block Symbol...命令B.这时候会出现一个对话框提示你输入 ABEL 模块名称及其输入信号名和输出信号名请按照下图所示输入信息C.当你完成信号名的输入揿 Run 按钮就会产生一个元件符号并放在本地元件库中同时元件符号还粘连在光标上随之移动D.把这个符号放在 demo 符号的左边E.单击鼠标右键就会显示 Symbol Libraries 的对话框请注意 abeltop 符号出现在 Local 库中F.关闭对话框你的原理图应该如下图所示III.完成原理图现在请你添加必需的连线连线名称以及 I/O 标记来完成顶层原理图使其看上去如下图所示如果你需要帮助请参考第二节中有关添加连线和符号的指导方法当你画完后请存盘再退出IV.建立 ABEL-HDL 源文件现在你需要建立一个 ABEL 源文件并把它链接到顶层原理图对应的符号上项目管理器使这些步骤简化了A.你当前的管理器应该如下图所示B.请注意 abeltop 左边的红色“?”图标这意味着目前这个源文件还是个未知数因为你还没有建立它同时也请注意源文件框中的层次结构abeltop 和 demo 源文件位于 top 原理图的下面并且偏右这说明它们是 top 原理图的底层源文件这也是 ispDesignEXPERT System 项目管理器另外一个有用的特点C.为了建立所需的源文件请选择 abeltop然后选择 Source菜单中的 New... 命令D.在 New Source 对话框中选择 ABEL-HDL Module 并按 OKE.下一个对话框会问你模块名文件名以及模块的标题为了将源文件与符号相链接模块名必须与符号名一致而文件名没有必要与符号名一致但为了简单你可以给它们取相同的名字按下图所示填写相应的栏目F.按 OK你就进入了 Text Editor而且可以可见ABEL HDL 设计文件的框架已经呈现在你的面前G.输入下列的代码确保你的输入代码位于 TITLE 语句和END 语句之间H.当你完成后选择 File 菜单中的 Save 命令I.退出文本编辑器J.请注意项目管理器中 abeltop 源文件左边的图标已经改变了这就意味着你已经有了一个与此源文件相关的 ABEL文件并且已经建立了正确的链接V.编译 ABEL HDLA.选择 abeltop 源文件B.在处理过程列表中双击 Reduce Logic 过程你会看到项目管理器在执行 Reduce Logic 过程之前先去执行 Compile Logic过程当处理过程结束后你的项目管理器应该如上图所示VII. 仿真你现在可以对整个设计进行仿真为此你需要一个新的测试矢量文件在这个例子中你只需要修改当前的测试矢量文件A.双击 demo.abv 源文件就会出现文本编辑器B.按照下图修改测试矢量文件C.完成后存盘退出D.仍旧选择测试矢量源文件双击 Functional Simulation 过程进行功能仿真E.现进入 Simulation Control Panel 窗口按 Windows=> Waveform Viewer窗口打开波形观测器准备查看仿真结果F.为了看波形你必须在 Simulation Control Panel 窗口中按Debug 钮使 Simulation Control Panel 窗口进入 Debug 模式G.在 Available Signals 栏中选择 CLK, TOPIN1, TOPIN2, TOPIN3 和 TOPOUT信号并且按 Monitor 钮这些信号名都可以在波形观测器中观察到再按 Run 钮进行仿真其结果如下图所示H.在步骤 D 中如双击 Timing Simulation 过程即可进入时序仿真流程以下仿真步骤与功能仿真相同VIII. 把设计适配到 Lattice 器件中现在你已经完成了原理图和 ABEL 语言的混合设计及其仿真剩下的步骤只是将你的设计放入 Lattice ispLSI/pLSI 器件中因为你已经在第一节中选择了器件你可以直接执行下面的步骤:A.在源文件窗口中选择 ispLSI1032E-70LJ84 器件作为编译对象并注意观察对应的处理过程B.双击处理过程 Compile Design这将迫使项目管理器完成对源文件的编译然后连接所有的源文件最后进行逻辑分割布局和布线将设计适配到所选择的 Lattice 器件中C.当这些都完成后你可以双击 ispDesignEXPERT CompilerReport查看一下设计报告和有关统计数据D.祝贺!! 你现在已经完成了设计例子并且掌握了ispDesignEXPERT System 的主要功能IX.层次化操作方法层次化操作是 ispDesignEXPERT 系统项目管理器的重要功能它能够简化层次化设计的操作a) 在项目管理器的源文件窗口中选择最顶层原理图“top.sch”. 此时在项目管理器右边的操作流程清单中必定有Navigation Hierarchy 过程b) 双击 Navigation Hierarchy 过程即会弹出最顶层原理图“top.sch”c) 选择 View 菜单中的 Push/Pop 命令光标就变成十字形状d) 用十字光标单击顶层原理图中的 abeltop 符号即可弹出描述 abeltop 逻辑的文本文件 abeltop.abl此时可以浏览或编辑ABEL HDL 设计文件浏览完毕后用 File 菜单中的 Exit 命令退回顶层原理图e) 用十字光标单击顶层原理图中的 demo 符号即可弹出描述demo 逻辑的底层原理图 demo.sch此时可以浏览或编辑底层原理图f) 若欲编辑底层原理图可以利用 Edit 菜单中的 Schematic 命令进入原理图编辑器编译完毕后用 File 菜单中的 Save 和Exit 命令退出原理图编辑器g) 底层原理图浏览完毕后用十字光标单击图中任意空白处即可退回上一层原理图h) 若某一设计为多层次化结构则可在最高层逐层进入其底层直至最底一层退出时亦可以从最底层逐层退出直至最高一层i) 层次化操作结束后用 File 菜单中的 Exit 命令退回项目管理器注意将 Y1 端口定义成时钟输入端的方法ispLSI 1016 和 ispLSI 2032 两种器件的 Y1 端是功能复用的如果不加任何控制适配软件在编译时将 Y1 默认为是系统复位端口(RESET)若欲将 Y1 端用作时钟输入端必须通过编译器控制参数来进行定义第五节 ispDesignEXPERT 系统中 VHDL 和Verilog 语言的设计方法除了支持原理图和 ABEL-HDL 语言输入外商业版的ispDesignEXPERT 系统中提供了 VHDL 和 Verilog 语言的设计人口用户的VHDL 或 Verilog 设计可以经 ispDesignEXPERT 系统提供的综合器进行编译综合生成 EDIF 格式的网表文件然后可进行逻辑或时序仿真最后进行适配生成可下载的 JEDEC 文件I.VHDL 设计输入的操作步骤A.在 ispDesignEXPERT System Project Navigator 主窗口中按 File=>NewProject 菜单建立一个新的工程文件此时会弹出如下图所示的对话框请注意在该对话框中的 Project Type 栏中必须根据您的设计类型选择相应的工程文件的类型本例中选择 VHDL 类型若是 Verilog 设计输入则选择 VerilogHDL 类型将该工程文件存盘为 demo.synB.在 ispDesignEXPERT System Project Navigator 主窗口中选择Source=>New 菜单在弹出的 New Source 对话框中选择 VHDLModule 类型C.此时软件会产生一个如下图所示的 New VHDL Source 对话框在对话框的各栏中分别填入如上图所示的信息按 OK 钮后进入文本编辑器 - Text Editor 编辑 VHDL 文件D.在 Text Editor 中输入如下的 VHDL 设计并存盘library ieee;use ieee.std_logic_1164.all;entity demo isport ( A, B, C, D, CK:in std_logic;OUTP:out std_logic);end demo;architecture demo_architecture of demo issignal INP: std_logic;beginProcess (INP, CK)beginif (rising_edge(CK)) thenOUTP <= INP;end if;end process;INP <= (A and B) or (C and D);end demo_architecture;此 VHDL 设计所描述的电路与本教材第二节所输入的原理图相同只不过将输出端口 OUT 改名为 OUTP ( 因为OUT 为 VHDL 语言保留字)E.此时在 ispDesignEXPERT System Project Navigator 主窗口左侧的源程序区中demo.vhd 文件被自动调入单击源程序区中的ispLSI1032E-125LT100 栏此时的 ispDesignEXPERT System ProjectNavigator 主窗口如下图所示F.选择菜单 Tools=>Synplicity Synplify Synthesis产生如下窗口选 Add 调入 demo.vhd 然后对 demo.vhd 文件进行编译综合若整个编译综合过程无错误该窗口在综合过程结束时会自动关闭若在此过程中出错双击上述 Synplify 窗口中 Source Files 栏中的 demo.vhd 文件进行修改并存盘然后按RUN 钮重新编译G.在通过 VHDL 综合过程后可对设计进行功能和时序仿真在 ispDesignEXPERT System Project Navigator 主窗口中按 Source=>New 菜单产生并编辑如下的测试向量文件 demo.abvmodule demo;c,x = .c.,.x.;CK,A,B,C,D,OUTP PIN;TEST_VECTORS([CK, A, B, C, D]->[OUTP])[ c , 0 , 0 , 0 , 0 ]->[ x ];[ c , 0 , 0 , 1 , 0 ]->[ x ];[ c , 1 , 1 , 0 , 0 ]->[ x ];[ c , 0 , 1 , 0 , 1 ]->[ x ];ENDH.在 ispDesignEXPERT System Project Navigator 主窗口中选中左侧的demo.abv 文件双击右侧的 Functional Simulation 栏进行功能仿真在 Waveform Viewer 窗口中观测信号 A B C CK D 和OUTP其波形如下图所示I.在 ispDesignEXPERT System Project Navigator 主窗口中选中左侧的demo.abv 文件双击右侧的 Timing Simulation 栏进行时序仿真选择 Maximum Delay在 Waveform Viewer 窗口中观测信号 AB C CK D 和 OUTP其波形如下图所示J.在 ispDesignEXPERT System Project Navigator 主窗口中选中左侧的ispLSI1032E-125LT100 器件双击右侧的 Compile Design 栏进行器件适配该过程结束后会生成用于下载的 JEDEC 文件demo.jedII.Verilog 设计输入的操作步骤Verilog 设计输入的操作步骤与 VHDL 设计输入的操作步骤完全一致在此不再赘述需要注意的是在产生新的工程文件时工程文件的类型必须选择为 Verilog HDL第六节在系统编程的操作方法Lattice ISP 器件的在系统编程能够在多种平台上通过多种方法来实现在此仅介绍在教学与科研中最常用的基于 PC 机 Windows环境的菊花链式的在系统编程方法由于在系统编程的结果是非易失性的故又可将编程称为“烧写”或“烧录”利用 PC »ú Window版的 ISP 菊花链烧写软件对连接在 ISP 菊花链中的单片或多片 ISP 器件进行编程时烧写软件对运行环境的要求为*每个待编程器件的 JEDEC 文件 ( 由前面的设计过程所得)*连接于 PC 机并行口上的 ISP 烧写电缆*Microsoft Win95 或 NT*带有 ISP 接口的目标硬件 ( 如教学实验板电路板或整机)1.在 ispDesignEXPERT System Project Navigator 窗口中的源文件区选中器件名如 ispLSI1032E-70LJ84双击右侧的 ISP Daisy Chain Download栏( 或直接在 WIN95 中按 Start=>Programs=>Lattice Semiconductor=>ispDCD)打开 ISP 菊花链烧写窗口2.建立一个新的结构文件3.检查结构文件4.对菊花链进行编程首先在 Windows 中打开 ISP 菊花链烧写功能ISP 菊花链烧写软件利用结构文件来定义下列信息* 各个 ISP 器件的位置 ( 序号 ) 和型号* 对各个 ISP 器件将要进行的操作 ( 读出写入校验或无操作等 )若 PC 机已经通过在系统编程电缆连接到教学实验板或目标硬件板上那么建立结构文件最简单的方法是利用 Configuration => ScanBoard 命令这一命令执行之后就产生一个包含有菊花链中所有器件的基本结构文件然而此时结构文件中还缺乏关于进行何种操作和写入哪一个 JEDEC 文件的信息注结构文件的后缀为 *.DLD它适用于 DOS 或 Windows 两种环境。

ispLEVERr入门操作指导(可编辑)

ispLEVERr入门操作指导ispLEVER培训教程目录第一节 ispLEVER 简介第二节ispLEVER开发工具的原理图输入第三节设计的编译与仿真第四节硬件描述语言和原理图混合输入第五节ispLEVER工具中VHDL和Verilog语言的设计方法第六节ispVM System-在系统编程的软件平台第七节约束条件编辑器(Constraint Editor)的使用方法附录一ispLEVER System上机实习题附录二ispLEVER软件中文件名后缀及其含义第一节 ispLEVER 简介 Constraints Editor工具允许经由一个图形用户接口选择I/O设置和引脚分配。

软件包含Synolicity公司的“Synplify”综合工具和Lattice的ispVM器件编程工具。

ispLEVER软件提供给开发者一个简单而有力的工具,用于设计所有莱迪思可编程逻辑产品。

软件支持所有Lattice公司的ispLSI 、MACH、ispGDX、ispGAL、GAL器件。

ispLEVER工具套件还支持莱迪思新的ispXPGATM和ispXPLDTM产品系列,并集成了莱迪思ORCA Foundry设计工具的特点和功能。

这使得ispLEVER的用户能够设计新的ispXPGA 和ispXPLD产品系列,ORCA FPGA/FPSC系列和所有莱迪思的业界领先的CPLD产品而不必学习新的设计工具。

软件主要特征:1. 输入方式* 原理图输入* ABEL-HDL输入* VHDL输入* Verilog-HDL输入* 原理图和硬件描述语言混合输入逻辑模拟* 功能模拟* 时序模拟编译器* 结构综合、映射、自动布局和布线支持的器件* 含有支持ispLSI器件的宏库及MACH器件的宏库、TTL库* 支持所有ispLSI、MACH、ispGDX、ispGAL、GAL、ORCA FPGA/FPSC、ispXPGA和ispXPLD器件 5. Constraints Editor工具* I/O参数设置和引脚分配 6. ispVM工具* 对ISP器件进行编程软件支持的计算机平台:PC: Windows 98/NT/2000/XP第二节 ispLEVER开发工具的原理图输入启动ispLEVER 按Start Programs Lattice Semiconductor ispLEVER菜单创建一个新的设计项目选择菜单File。

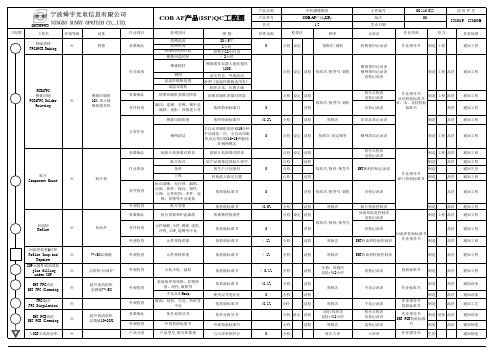

COB AF产品(ISP) QC工程图

产品名称产品件号页次工程名环境等级设备规 格管理水准频率记录法异常处理80±5℃1小时烘烤后12小时内> 2小时锡膏搅拌仪最大速度搅拌180S 品名符合,外观清洁参照《高温纤维板选用表》粘性正常,位置正确依照印刷机参数对照表点检设定巡检机台点检表巡检记录表制造工程品管通知工程依照检验标准书0首检首检记录表品管通知工程依照检验标准书<0.2%全检巡检每批次丝印品质记录表制造品管通知工程半自动印刷机每印刷15分钟手动清洗一次,全自动印刷机设定每印刷10-15拼板清洗钢网模式0点检设定巡检每班次/设定频率钢网清洁记录表制造工程品管通知工程依贴片机参数对照表点检设定巡检机台点检表巡检记录表制造工程品管通知工程依产品规格选择贴片程序点检巡检制造品管通知工程按生产计划备料点检制造通知生管料枪放入指定位置点检巡检制造品管通知工程依检验标准书0首检每班次/换型号/调机首检记录表品管通知工程依检验标准书<0.5%全检巡检每批次贴片检验控制表制造品管通知工程依锡膏焊接条件点检设定巡检回流焊温度控制表巡检记录表制造工程品管通知工程依检验标准书0首检首检记录表品管通知工程依检验标准书< 1%全检巡检每批次SMT回流焊检验控制表制造品管通知工程回流焊检查&补焊Reflow Insp.andRepaire ※7~45X显微镜依检验标准书< 1%全检巡检每批次SMT回流焊检验控制表制造品管通知工程ISP元器件底部填胶 glue filling under ISP ※点胶机/回流炉依检验标准书< 0.1%全检巡检全检:每批次巡检:每2小时巡检记录表制造品管通知工程依检验标准书<0.1%全检巡检制造品管通知设备使用记号笔作业0全检巡检制造品管通知设备FPC裁切FPC Singulation ※依检验标准书<0.1%全检巡检每批次不良记录表制造品管通知工艺依作业指导书点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备外观检验标准书全检巡检每批次巡检记录表制造品管通知制造入COB半成品仓库※与入库单相符合全检每次入库入库单生管通知制造外观检验标准书产品分类产品型号,批号和数量作业指导书外观检查破损,刮伤,毛边,折痕等不良作业指导书检验标准书SMT PCB清洗SMT PCB Cleaning ※超声波清洗机显微镜10-20X参数确认依作业指导书作业指导书SMT PCB检验标准书外观检查1/5发布日期COB AF 产品(ISP)QC 工程图手机摄像模组文件编号工程图作业项目管理项目检查法OI-110-025适 用 件 号COB AF 产品(ISP)版次00S5M01P 、S5M03B作业资料担当拼版烘烤FPC&PCB Baking※烤箱参数确认烘烤温度0点检设定通知工程每批次/调机烘箱使用记录表作业指导书制造工程正常作业首件检查烘烤时间拼版的使用时间锡膏回温时间依照印刷机参数对照表锡膏领用记录表钢网领用记录表巡检记录表作业指导书丝印检验标准书首、末、巡检检验标准书工程品管每班次/换型号/调机PCB&FPC 锡膏印刷PCB&FPC SolderPrinting※锡膏印刷机10X 放大镜锡膏搅拌机作业准备参数确认点检设定巡检漏印、连锡、多锡、锡不足、偏移、重影、异物进入等通知工程锡膏搅拌钢网高温纤维板选别高温双面胶每班次/换型号/调机每班次/换料/换型号备料上料制造锡膏印刷质量钢网清洁作业指导书贴片检验标准书SMT换料控制记录表贴片Component Mount※贴片机参数确认依贴片机参数对照表外观检查贴片质量作业准备贴片程式回流炉参数确认外观检查元件焊接质量首件检查首件检查标识清晰,无位移、漏贴、误贴、缺件、极反、错件、立碑、元件损伤、多件、连锡、异物等不良现象检验标准书SMT FPC清洗SMT FPC Cleaning ※超声波清洗机显微镜7~45X外观检查机台参数和炉温曲线每班次/换料/换型号回流焊检验标准书作业指导书回流焊Reflow※不良品作Mark元件偏移,少件,锡珠,虚焊,冷焊,立碑,连锡等不良外观检查元件焊接质量表面助焊剂残留,异物残留,刮伤,破损等外观检查点胶少胶、溢胶每批次不良记录表作业标准书DISCO DSC 141依离心清洗机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备金相显微镜100X依检验标准书<0.1%抽检每片Wafer晶圆清洗站作业记录表制造通知设备等离子清洗Plasma Cleaning Class 10Plasma依等离子清洗机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表等离子清洗站作业记录表制造设备品管通知设备ASM IS898DA依芯片贴附机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管依D/A图纸首检品管依D/A图纸首检品管依D/A图纸首检品管依D/A图纸首检品管依D/A图纸首检品管不允许有首检品管依D/A图纸首检每型号每周开班品管依产品检验标准书抽检巡检制造品管依产品检验标准书抽检巡检制造品管芯片贴附烘烤D/A Baking Class 10VSCO-2CM依芯片贴附烤箱参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备ASM ISEagle60依邦线机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依照W-B图纸首检品管依照W-B图纸首检品管依照W-B图纸首检品管依照W-B图纸首检品管依照W-B图纸首检品管依照W-B图纸首检品管依产品检验标准书0全检巡检制造品管依产品检验标准书0全检巡检制造品管DISCO DSC 141依离心清洗机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依产品检验标准书0巡检品管依产品检验标准书0巡检品管镜座检查Holder Inspection Class1000显微镜 7~45X依产品检验标准书IL IIAQL 0.65全检抽检每批次Holder检查作业记录表抽检记录表制造品管通知生管邦线清洗W/B Cleaning Class 10显微镜 7~45X参数确认产品检验标准书清洗检查金线通知设备脏点,水纹参数确认等离子清洗机参数等离子清洗站作业指导书晶圆清洗作业指导书产品检验标准书外观检查脏点,刮伤,水纹,崩碎晶圆清洗Wafer Cleaning Class 10参数确认离心清洗机参数通知设备通知设备金球大小金球厚度弧高金线拉力邦线首检记录表全检:每批次巡检:每1小时邦线站作业记录表巡检记录表邦线开、短路芯片倾斜巡检记录表芯片贴附Die Attach Class 10参数确认首件检查显微镜7~45X工具显微镜dage 4000芯片贴附机参数通知设备方向,偏移,旋转芯片推力芯片外观芯片贴附站作业指导书产品检验标准书D/A图纸通知设备芯片方向全检:每批次巡检:每1小时胶厚邦 线Wire Bonding Class 10参数确认邦线机参数邦线检查接线,线数,线弧工具显微镜dage 4000首件检查金球推力芯片贴附烘烤站作业指导书邦线站作业指导书产品检验标准书W/B图纸外观检查脏点,刮伤,崩角毛刺,IR膜方向,膜裂贴附检查芯片旋转芯片偏移吸嘴印接线、线数显微镜7~45X参数确认芯片贴附烤箱参数离心清洗机参数每班次/换型号/调机芯片贴附首检记录表邦线清洗站作业指导书产品检验标准书每1小时巡检记录表每班次/换型号/调机ASM IS898LA依镜座贴附机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依照H-A图纸首检品管依产品检验标准书首检品管不允许断胶和碰触金线首检品管依产品检验标准书首检品管依照H-A图纸首检每型号每周开班品管显微镜 7~45X依产品检验标准书0巡检巡检:每1小时巡检记录表品管通知设备芯片检查Chip InspectionClass 10CCD检查仪器/显微镜依产品检验标准书< 2%全检每批次芯片检查作业记录表制造通知品管预热preheat Class 10加热平台依产品检验标准书< 0.1%全检巡检全检:每批次巡检:每1小时镜座贴附检查作业记录表巡检记录表制造品管通知设备镜座贴附烘烤Holder AttachBaking Class 10VSCO-4CM 依镜座贴附烤箱参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备贴IR保护膜 IR film AttachClass 10Manual 方向一致,并朝向马达焊接口方向,位移不超过镜座端面,无遗漏0全检全检:每批次作业记录表制造通知品管依线路板切割机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依产品检验标准书首检品管依模组规格图纸首检品管全检巡检制造品管全检巡检制造品管依模组规格图纸抽检巡检制造品管依ACF贴附机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依产品检验标准书全检每批次制造依产品热压图纸全检每批次制造点胶机&曝光机机参数对照表点检设定巡检全检:每批次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备不得溢到金手指,需要将驱动芯片全部包住<0.01%全检巡检全检:每批次巡检:每1小时RUN CARD 制造品管通知工艺热压机依热压机参数对照表点检设定巡检点检:每班次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备CCM测试机台通断测试标准首检品管通知设备显微镜 7~45X依产品检验标准书首检品管通知设备拉力机> 0.4Kg.f 首检每周次/新型号/修机品管通知设备CCM测试机台通断测试标准全检巡检全检:每批次巡检:每1小时RUN CARD 巡检记录表制造品管通知设备方向、偏移、旋转,胶量、缝隙等尺寸镜座贴附烤箱参数胶厚,胶宽,断胶,气泡尺寸线路板切割机参数点胶机&曝光机参数粉尘热压站作业指导书产品检验标准书热压站首检记录表每班次/换型号/调机马达驱动芯片封胶作业指导书依产品检验标准书<0.1%镜座贴附机参数贴附检查贴附检查每班次/换型号/调机镜座贴附Holder Attach高精度拉力测试仪首件检查镜座贴附站作业指导书产品检验标准书H/A图纸0参数确认Class 10通知设备偏移胶线缝隙Holder推力方向、偏移、旋转,胶线、缝隙等镜座贴附首检记录表预热站作业指导书产品检验标准书镜座贴附烘烤站作业指导书首件确认无图、失真偏移、压合方向、溢胶颜色ACF胶拉力参数确认热压机参数热压Heat BondingClass 10K功能测试无图、失真ACF贴附机参数ACF贴附站作业指导书产品检验标准书每班次/换型号/调机切痕切痕全检:每批次巡检:每1小时模组分离作业记录表巡检记录表模组分离首检记录表模组分离站作业指导书产品检验标准书参数确认方向模组分离Cube SingulationClass 1K线路板切割机参数确认首件检查马达驱动芯片封胶Motor Drive Chip Sealing GlueClass 10K点胶机&UV曝光机外观检查外观检查参数确认外观检查外观检查参数确认外观检查芯片检查站作业指导书产品检验标准书ACF贴附ACF AttachClass 10KACF贴附机脏点、污点、粘胶、划伤等偏移,扯胶,缺胶,叠胶<0.1%RUN CARD方向,位移方向产品检验标准书通知品管通知设备通知设备点胶机&曝光机机参数对照表点检设定巡检全检:每批次巡检:每2小时机台点检表巡检记录表制造设备品管通知设备依产品检验标准书<0.01%全检全检:每批次RUN CARD制造通知品管削毛边Bur Cutting Class 10K Manual依产品检验标准书依模组规格图纸<0.01%全检巡检全检:每批次巡检:每1小时RUN CARD削毛边站稽查记录表制造品管通知工艺参见《CCM检测台点检表》全检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程依检验标准书0全检每批次RUN CARD制造通知品管镜头组配Lens Assembly Class 1K Manual组装后镜头端面与马达台阶面相平或下陷0.01~0.05mm全检每批次RUN CARD制造通知品管撕保护膜Film TearingClass 1K Manual依产品检验标准书< 1%全检每批次RUN CARD制造通知品管封装芯片清洁CleaningClass 1K7~45X显微镜依产品检验标准书< 1%全检全检:每批次RUN CARD制造通知品管点胶机依点胶机参数对照表点检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程Manual依产品检验标准书0全检全检:每批次RUN CARD制造通知品管马达组装Motor fitting Class 1K Manual马达焊条一侧与半成品焊盘一侧相对应0全检巡检全检:每批次巡检:每1小时RUN CARD巡检记录表制造品管通知工艺依烤箱参数对照表点检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程依产品检验标准书< 0.1%全检巡检全检:每批次巡检:每1小时RUN CARD巡检记录表制造品管通知工艺马达引脚焊接Motor PIN Jointed Class 10K烙铁依产品检验标准书< 0.1%全检巡检全检:每批次巡检:每1小时RUN CARD巡检记录表制造品管通知工艺参见《CCM检测台点检表》点检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程依软件判定0全检制造通知品管依检验标准书< 0.5%全检制造通知品管依检验标准书< 0.5%全检制造通知品管依检验标准书0全检制造通知品管点胶机依点胶机参数对照表点检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程显微镜 7~45X依检验标准书0全检每批次RUN CARD制造通知品管曝光机依曝光机参数对照表点检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程 扭力计> 220 gf*cm0首件每班次/新型号/调机巡检记录表品管通知工艺Manual依检验标准书0巡检每1小时巡检记录表品管通知工艺设备点检点胶机参数胶量、点胶位置点胶机&曝光机参数胶厚,胶宽,断胶,气泡组配高度,倾斜IR面刮伤,污染,残胶马达贴附烘烤Motor Attach Cure Class 10K烤箱Class 1K点胶Glue Dispenser产品检验标准书CCM台检定规程产品检验标准书削毛边站作业指导书产品检验标准书参见《CCM检测台点检表》烧录shanding Class10K测试工装设备点检图像质量测试软板补强站FPC Bending Strengthen Class 10K点胶机&UV曝光机参数确认外观检查扭力测试首巡检作业规范外观检查软板补强站作业指导书产品检验标准书UV点胶作业指导书产品检验标准书参数确认UV曝光作业指导书封遮点胶作业指导书IR清洁作业指导书外观检查图像质量PCB削伤,FPC削伤,Holder削伤,尺寸马达镜头组配作业指导书外观检查设备点检烤箱参数马达贴附烘烤作业指导书外观检查溢胶,缝隙,方向等外观检查IR面刮伤,污染,残胶外观检查马达引脚焊接作业指导书调焦Focus Class10KCCM检测机台测试工装设备点检参见《CCM检测台点检表》调焦远焦和近焦分辨率CCM台检定规程调焦站作业指导书曝光机参数图像质量测试图像质量检测污点污点外观检查锡量,空焊,短路等检测坏点坏点UV点胶UV Dispenser Class10K参数确认外观检查点胶机参数马达组装作业指导书扭力大小全检:每批次RUN CARD溢胶,欠胶,粘胶等UV曝光UV CureClass10K外观检测胶量,固化效果首巡检作业规范外观检查组合方向产品名称产品件号页次参见《CCM检测台点检表》全检设定巡检每班次/新型号/调机机台点检表巡检记录表制造工程品管通知工程依软件判定0全检制造通知品管依软件判定和目视0全检制造通知品管依软件判定和目视0全检制造通知品管依检验标准书0全检制造通知品管依检验标准书0全检制造通知品管依检验标准书0全检制造通知品管清晰可辨0全检巡检制造品管通知工艺依检验标准书0全检巡检制造品管通知工艺依模组规格图纸IL II AQL0.65抽检巡检制造品管通知工艺依检验标准书0全检巡检制造品管通知工艺依检验标准书0全检巡检制造品管通知工艺依检验标准书0全检巡检制造品管通知工艺依检验标准书0全检巡检制造品管通知工艺包装辅助PackageClass10KManual依各型号产品图档要求0全检巡检全检:每批次巡检:每2小时RUN CARD 巡检记录表制造品管通知工艺参见《CCM检测台点检表》设定点检每班次/新型号/调机机台点检表工程品管通知工程依检验标准书IL II AQL0.4抽检品管通知制造依检验标准书IL II AQL0.65抽检品管通知制造依检验标准书0抽检品管通知制造入成品仓库※与入库单相符合0全检每次入库入库单生管通知制造处 数更改文件号签 名编制审 核暗角、白角、黑角Class10KCCM检测机台测试工装设备点检成品检验Function Test参见《CCM检测台点检表》CCM台检定规程功能检测远焦和近焦分辨率每批次RUN CARD成品检验作业指导书产品检验标准书坏点污点、黑点FPC板部件图像质量偏色成品外观检验Visual InspectionClass10K高度测试工装、标准高度块、游标卡尺模组部件外观显微镜 7~45X外观质量产品标识CCM台检定规程功能检测全检:每批次巡检:每2小时RUN CARD 巡检记录表产品检验标准书补强胶模组尺寸附件检查镜头金手指不良记录表作业标准书包装模组放置方向,辅材粘贴质量作业标准书出货检验OQCClass10K图像检测工装、显微镜、CCM检测台设备点检参见《CCM检测台点检表》外观检测金手指,镜头端面,FPC部件,扭力,补强胶等附件检查包装,标签分辨率,坏点,污点,像糊,偏色,暗角,成像方向等每批次图示说明▽:准备 投入 ○:加工 组装 ●:关键工序更改记录更改标记日 期标 准 化- :移动 搬运 :保管 存储产品分类产品型号,批号和数量作业指导书批 准⊙:特殊工序 ◇ :QC 检验站 □:一般检验站熊益超适 用 件 号COB AF 产品(ISP)版次00S5M01P 、S5M03B5/5发布日期OI-110-025文件编号COB AF 产品(ISP)QC 工程图手机摄像模组。

AD图纸结构以及6大类网络标识

AD图纸结构以及6大类网络标识1、图纸结构图纸包括两种结构关系:一种是层次式图纸,该连接关系是纵向的,也就是某一层次的图纸只能和相邻的上级或下级有关系;另一种是扁平式图纸,该连接关系是横向的,任何两张图纸之间都可以建立信号连接。

2、网络连接方式Altium Designer提供了6类网络标识:Net Label(网络标号),Port(端口),Sheet Entry(图纸入口),Power Port(电源端口),Hidden Pin(隐匿引脚)、Off-sheet Connector(图纸外连接符)。

网络标识是通过名字来连接的,名字相同就可以传递信号。

但是特别要注意的是,除了“Port”与“Sheet Entry”这一对标识以外,其它不同类的网络标识,即使标识名字相同,相互之间也没有连接。

比如Net Label及Port两种标识,只能通过连线才能把这两个同名不同类的标识连接起来。

3、“Port”及“Net Label”的作用范围这两种网络标识的作用范围是可以变化和更改的。

方法是:打开Project\Project Option\Option标签,在Net Identifier Scope一栏的四个选项(Automatic、Flat、Hierarchical、Global)中挑一项。

“Automatic”是缺省选项,表示系统会检测项目图纸内容,从而自动调整网络标识的范围。

检测及自动调整的过程如下:如果原理图里有Sheet Entry 标识,则网络标识的范围调整为Hierarchical。

如果原理图里没有Sheet Entry标识。

但是有Port标识,则网络标识的范围调整为Flat。

如果原理图里既没有Sheet Entry标识,又没有Port标识,则Net Label 的范围调整为Global。

“Flat”代表扁平式图纸结构,这种情况下,Net Label的作用范围仍是单张图纸以内。

而Port的作用范围扩大到所有图纸,各图纸只要有相同的Port名,就可以发生信号传递。

什么是LPC芯片里的ISP...

什么是LPC芯⽚⾥的ISP...

1.ISP(In System Programming:在系统编程),当芯⽚焊接在电路板上以后,可以通过串⼝将程序下载到LPC900 系列的芯⽚中。

⽬前,LPC900 系列中20 脚以上的芯⽚才⽀持ISP 下载⽅式,如P89LPC920(20 脚),P89LPC932A1(28 脚)等。

2.ISP 是⼀种很灵活的程序下载⽅式,⽤户根据需要编写⾃⼰的ISP 驻留代码,且ISP ⽅

式可以节省⼀个编程器,所以⼀般学⽣及⼀些⽐较有时间调试串⼝的⼯程

师多使⽤这种⽅式。

如果您准备使⽤ISP ⽅式,请您关注以下细节。

搭建⼀个可靠的串⼝;

确保您的ISP 驻留代码没有被破坏;

确保芯⽚的引导向量正确;

不能擦除芯⽚最后⼀个扇区(包含ISP 驻留代码);

⼀般情况下不能更改芯⽚的引导向量(保证其为出⼚默认配置);

加密时不能勾上 “禁⽌ IAP/ISP 编程操作”;

如果您使⽤3 个脉冲⽅式进⼊ISP,请确保RST 引脚上3 个脉冲符合芯⽚要求。

3.在以下情况下,很难进⼊ISP 状态,希各位多多关注。

低频晶振条件下,如32.768KHz,此时,LPC900 的ISP 驻留程序很难产⽣合适的

波特率与PC 机通信。

当使⽤内部RC 作为MCU 时钟源,⽽⼜使⽤内部RTC 模块(并且外接晶振作为内

部RTC 时钟源),此时⽆法通过复位脉冲⽅式进⼊ISP,仅可以使⽤帧间隔⽅式/

直接跳⼊法进⼊ISP。

在有的情况下,由于硬件及软件上的原因,您有可能⽆法通过三个脉冲⽅式进⼊

ISP,此时您可以选择帧间隔⽅式。

isp下载线电路图

一、使用Altera下载线ByteBlaster或ByteBlaster MV,(在通电情况下,软件可对其进行识别),可以下载A TMEL的89S、90、mega系列单片机;

二、若使用ispdown编程器系列,可支持更多的芯片。

ByteBlaster 下载线电路图

ByteBlaster MV 下载线电路图

Ispdown下载线接口标准

ATMEL单片机

AT89S系列的ISP方法

1、AT89S系列ISP原理图如上图所示(以89S51为例,其它同)。

2、AT89S8252,AT89S8253内部还有数据EEPROM可以在线编程。

3、单片机RESET管脚的使用说明。

如果复位电路由RC电路组成则RESET管脚可以直接相连接。

4、下载接口第1,9脚输出口最好接50-200欧姆电阻Rdl1,Rdl2。

A VR系列的ISP方法

1、AVR系列ISP原理图如上图所示。

2、AVR内部还有数据EEPROM可以在线编程。

3、单片机RESET管脚的使用说明。

如果复位电路由RC电路组成则RESET管脚可以直接相连接。

4、时钟输入可以选择如89s51的形式晶振+两个小电容来产生,也可以外部时钟输入到XTAL1引脚。

6、如果芯片只有VCC电源引脚,电源接法请参照第一幅图,如果还有AVCC引脚,请参照第二幅图。

7、下载接口第1,9脚输出口最好接50-200欧姆电阻Rdl1,Rdl2。

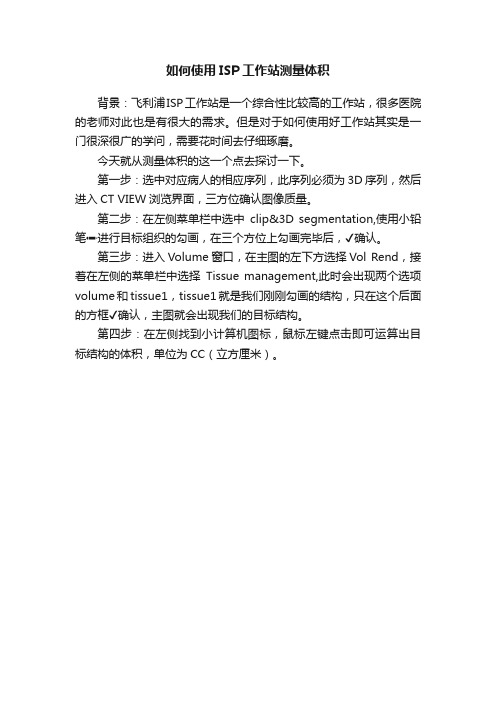

如何使用ISP工作站测量体积

如何使用ISP工作站测量体积

背景:飞利浦ISP工作站是一个综合性比较高的工作站,很多医院的老师对此也是有很大的需求。

但是对于如何使用好工作站其实是一门很深很广的学问,需要花时间去仔细琢磨。

今天就从测量体积的这一个点去探讨一下。

第一步:选中对应病人的相应序列,此序列必须为3D序列,然后进入CT VIEW浏览界面,三方位确认图像质量。

第二步:在左侧菜单栏中选中clip&3D segmentation,使用小铅笔✏进行目标组织的勾画,在三个方位上勾画完毕后,✔确认。

第三步:进入Volume窗口,在主图的左下方选择Vol Rend,接着在左侧的菜单栏中选择Tissue management,此时会出现两个选项volume和tissue1,tissue1就是我们刚刚勾画的结构,只在这个后面的方框✔确认,主图就会出现我们的目标结构。

第四步:在左侧找到小计算机图标,鼠标左键点击即可运算出目标结构的体积,单位为CC(立方厘米)。

PS基础概念之一

【PS基础概念之一】我也在学,拿来跟大家分享一下,谁有也不要另色给拿出来凉凉位图:又称光栅图,一般用于照片品质的图像处理,是由许多像小方块一样的“像素”组成的图形。

由其位置与颜色值表示,能表现出颜色阴影的变化。

在Photoshop主要用于处理位图。

矢量图:通常无法提供生成照片的图像物性,一般用于工程持术绘图。

如灯光的质量效果很难在一幅矢量图表现出来。

分辩率:每单位长度上的像素叫做图像的分辩率,简单讲即是电脑的图像给读者自己观看的清晰与模糊,分辩率有很多种。

如屏幕分辩率,扫描仪的分辩率,打印分辩率。

图像尺寸与图像大小及分辩率的关系:如图像尺寸大,分辩率大,文件较大,所占内存大,电脑处理速度会慢,相反,任意一个因素减少,处理速度都会加快。

通道:在PS中,通道是指色彩的范围,一般情况下,一种基本色为一个通道。

如RGB颜色,R为红色,所以R通道的范围为红色,G为绿色,B为蓝色。

图层:在PS中,一般都是多是用到多个图层制作每一层好象是一张透明纸,叠放在一起就是一个完整的图像。

对每一图层进行修改处理,对其它的图层不含造成任何的影响。

图像的色彩模式:1)RGB彩色模式:又叫加色模式,是屏幕显示的最佳颜色,由红、绿、蓝三种颜色组成,每一种颜色可以有0-255的亮度变化。

2)CMYK彩色模式:由品蓝,品红,品黄和黄色组成,又叫减色模式。

一般打印输出及印刷都是这种模式,所以打印图片一般都采用CMYK模式。

3)HSB彩色模式:是将色彩分解为色调,饱和度及亮度通过调整色调,饱和度及亮度得到颜色和变化。

4)Lab彩色模式:这种模式通过一个光强和两个色调来描述一个色调叫a,另一个色调叫b.它主要影响着色调的明暗。

一般RGB转换成CMYK都先经Lab的转换。

5)索引颜色:这种颜色下图像像素用一个字节表示它最多包含有256色的色表储存并索引其所用的颜色,它图像质量不高,占空间较少。

6)灰度模式:即只用黑色和白色显示图像,像素0值为黑色,像素255为白色。

3—ISPLever使用方法

在LSC ispVM™ System窗口中,双击New Scan Configuration Setup子窗口中的1032E栏,弹出Device Information对话框。在 该对话框中的Data File栏里,选择需要下载的JED文件 D:\TEST\ADD1.jed;在该对话框中的Operation栏里,选择所需 的编程操作,这里选Erase,Program,Verify,对器件进行擦除、 编程、校验。完成这些操作后,Device Information对话框如下 图所示。按OK钮,关闭该对话框。

第三节 利用ispVM System-在系统编程的 软件平台下载 1)Lattice器件的在系统编程是借助ispVM System 软件来实现的。 2)ispVM SystemTM 是一个综合的将设计下载 到器件的软件包。该软件提供一种有效的器件 编程方式,即采用由莱迪思半导体公司或其他 公司的设计软件所生成的 JEDEC 文件来对 ISP 器件编程。 3)在启动ispVM System前,先将Lattice下载电 缆连接在PC机的并行口和待下载的印刷电路板 上,并打开印刷电路板的电源。

在LSC ispVM™ System窗口中,按Project=>Download 菜单启动下载操作。

数秒钟后,下载完成,这时New Scan Configuration Setup子窗口中的Status栏显示PASS,并有一个绿色的 圆点,参见下图。

注意:在整个定义属性锁定管脚号的过程中不要敲 回车,用鼠标选择IOPAD ,从键盘上输入管脚号即可。 八、保存已完成的设计 从菜单条上选择File,并选Save命令。再选Exit命令。

第二节 编译原理图

1)建立起所需的源文件,下一步是执行每一个源文 件所对应的处理过程。 2)选择不同的源文件,从项目管理器窗口中观察到 该源文件所对应的可执行过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Application Note:

er must load \LD\LDUXXXX.BIN file to write LD Flash EPROM by H/W

writer at the first time.

Most writers allocate memory as below:

2.There are 3 ways to update your program by ISP.

2.1 H/W Reboot method:

This is a very simple method. At first, you must write "LDUxxxxx.BIN" file to LD flash by your writer. If CPU is match H/W reboot condition, CPU will enter LD flash to update your program. ISP writer S/W does not select "Program Start at AP ROM". H/W reboot condition is as below:

2.2 F/W method 1:

Please embed "\ap\auto\APAUTO.ASM" on your AP program. uC will enter ISP while CPU call this program. ISP writer S/W does not select "Switch to LD by User Command”.

2.3 F/W method 2:

Host PC send the sequent "user command" to inform uC. If uC has received the sequent "user command", uC will enter LD flash to update user's program. Please embed

"\AP\ReceiveCmd\*.asm" program on your AP program. At first, you must write your AP program on your AP flash and "LDUxxxxx.BIN" on your LD flash by your writer. ISP writer S/W must select " Switch to LD by Uer Command" and set user command on AP setting\user command field. F/W "user command" is defined by "\ap\ReceiveCmd\APU30307.ASM" file ( USER_code db "WB05D000"). Base on your crystal and baud rate to modify your F/W program.

3.You can set security bits at this time if you need protect your code. ISP function

still works OK.

4.If you needn’t have ISP function, please don’t fill “FF” code on LD memory. The

writer always writes AP and LD flashs every time.

5.It is necessary to pull up 10K resistors on these P2.6, P2.7 and P4.3 pins.

6.Please read “\doc\readme.doc” file to check LD F/W v ersion and PC S/W version.

They must be mached.

7.ISP system circuit is below

9 c on.。