数字电路逻辑设计第三章

(完整版)数字电路与逻辑设计课后习题答案蔡良伟(第三版)

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

3-6

3-7

3-8

3-9

3-10

求减数的补码,然后与被减数相加即可。电路图如下:

3-11

3-12

(1)

(2)

(3)

(4)

(5)

(6)

(7)

(8)

3-13

(1)真值表:

(2)电路图

3-14

3-15

第四章习题

4-1

4-2

4-3

4-4

4-5

4-6

4-7

4-8

4-9

4-10

RSDRSJK RST

4-11

(1)转换真值表

1 1 0 1

1 1 1 0

1 1 1 1

1 0 1 0

0 0 0 0

0 0 0 1

0 0 1 0

00 11

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

××××

××××

××××

××××

××××

1×0×1×0×

0×0×0××1

0×0××1 1×

0×0××0×1

0××1 1×1×

数字电路第三章习题答案

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B

数字电路第三章习题答案

3-11

试用六个与非门设计一个水箱控制电路。图为水箱示意图。A、B、C是三个电极。 当 电极被水浸没时,会有信号输出。水面在A,B间为正常状态,点亮绿灯G;水面在B、 C间或在A以上为异常状态,点亮黄灯Y;水面在C以下为危险状态.点亮红灯R。

3531736半加器的设计1半加器真值表2输出函数3逻辑图输入输出被加数a加数b4逻辑符号31837ab改为用与非门实现函数表达式变换形式

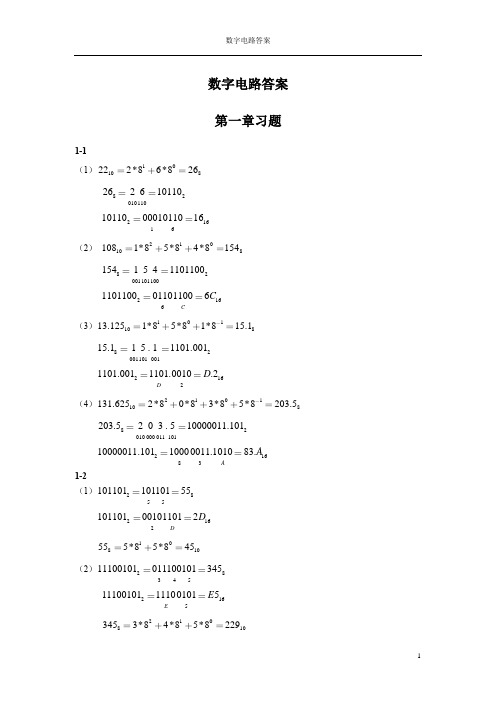

3-1 分析图示电路,分别写出M=1,M=0时的逻辑函数表达式

即M=1时,对输入取反,M=0时不取反。

数字电路第三章习题答案

3-2 分析图示补码电路,要求写出逻辑函数表达式,列出真值表。

3-10 试用与非门设计一个逻辑选择电路。

S1、S0为选择端,A、B为数据输入端。 选择电路的功能见下表。选择电路可 以有反变量输入。

数字电路第三章习题答案

3-10

F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B F F S 1 A S 0 B A S 0 B A B S 0 A B S 1 S 0 A B FS 1 S 0A B S 1 S 0(A B )S 1 S 0(A BA)B

数字电路第三章习题答案

3-5

Ai 0 0 0 0 1 1 1 1

Si Ai BiCi Ai BiCi Ai BiCi Ai BiCi

数字电路与逻辑设计课后习题答案蔡良伟(第三版)

数字电路答案 第一章习题1-1 (1)10108222*86*8268201011026261011021616101100001011016(2) 211081081*85*84*81548200110010115415411011002166110110*********6CC(3)10110813.1251*85*81*815.18200100110115.115.11101.00121621101.0011101.0010.2DD(4)211108131.6252*80*83*85*8203.582010000011101203.5203.510000011.1012168310000011.10110000011.101083.AA1-2(1)285510110110110155 2162101101001011012DD10810555*85*845(2)2834511100101011100101345 216511100101111001015EE2108103453*84*85*8229(3)28514101.0011101.0011005.14 21653101.00110101.00115.30128105.145*81*84*85.1875(4)28744100111.101100111.10147.421627100111.10100100111.101027.AA101018625.398*58*78*45.47=++=-1-3 (1)10810161*86*8148200111016161110 21611101110EE(2)218101721*87*82*812282001010111172172111101016727101001111111010A A==(3)101281061.536*81*85*83*849.6728200111010101161.5361.53110001.101011 21631110001.10101100110001.1010110031.AC AC(4)21012810126.741*82*86*87*84*886.937582001010100110111126.74126.741010110.1111216561010110.111101010110.111156.FF1-4 (1)1620010101022101010A A28521010101010105210810525*82*842(2)16210110010111122101100101111B F B F2875451011001011111011001011115457321081054575*84*85*87*82863(3)1621101111000113.3.11010011.111D E D E28732311010011.111011010011.111323.72101810323.73*82*83*87*8211.875(4)162000111111100001110011 3.913.9111000011.11111001C F C F28770362111000011.11111001111000011.111110010703.762210123810703.7627*80*83*87*86*82*8451.97261-5(1)AC AB C B A +=+)(左式=右式,得证。

数字电子技术基础第三章

二、交流噪声容限

反相器对窄脉冲 的噪声容限—交 流噪声容限远高 于直流噪声容限。

交流噪声容限受 电源电压和负载 电容的影响。

图3.3.23 CMOS反相器的交流噪声容限

三、动态功耗

动态功耗:当CMOS 反相器从一种稳定工 作状态突然转变到另 一种稳定的过程中, 将产生附加的功耗。

PD=PC+PT PD为总动态功耗 PC为对负载电容充放

图3.3.xx CMOS三态门电路结构之三 可连接成总线结构。还能实现数据的双向传输。

3.3.6 CMOS电路的正确使用

一、输入电路的静电防护

1、在存储和运输CMOS器件时最好采用金属屏蔽层 作包装材料,避免产生静电。

2、组装、调试时,应使电烙铁和其他工具、仪表、 工作台面等良好接地。操作人员的服装、手套等选用 无静电的原料制作。

图3.5.34 OC门输出并联的接法及逻辑图

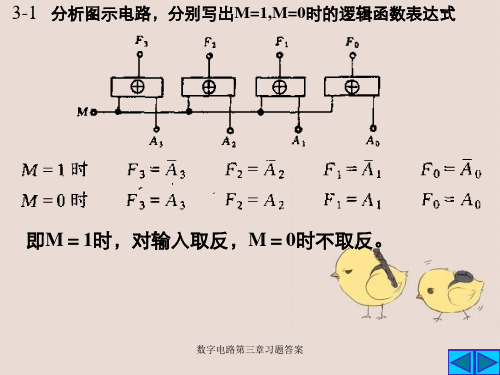

2.1 概述

常用的门电路在逻 辑功能上有: 与门、 或门、非门、与非 门、或非门、与或 非门、异或门等几 种。

单开关电路 互补开关电路

图3.1.1 获得高、低电平的基本原理

图3.1.2 正逻辑与负逻辑

一些概念

1、片上系统(SoC) 2、双极型TTL电路 3、CMOS

1961年美国TI公司,第一片数字集成电路 (Integrated Circuits, IC)。

C=1时 Vo=RL*Vi/(RL+RTG) RTG越小越好,并且希望不 受输入电压变化。

图3.3.39 CMOS模拟开关接 负载电阻的情况

四、三态输出的CMOS门电路

高阻态。 此电路结构 总是接在集 成电路的输 出端。

图3.3.40 CMOS三态门电路结构之一

数字电路教案-阎石-第三章-逻辑门电路

第3章逻辑门电路3.1 概述逻辑门电路:用以实现基本和常用逻辑运算的电子电路。

简称门电路.用逻辑1和0 分别来表示电子电路中的高、低电平的逻辑赋值方式,称为正逻辑,目前在数字技术中,大都采用正逻辑工作;若用低、高电平来表示,则称为负逻辑。

本课程采用正逻辑。

获得高、低电平的基本方法:利用半导体开关元件的导通、截止(即开、关)两种工作状态.在数字集成电路的发展过程中,同时存在着两种类型器件的发展。

一种是由三极管组成的双极型集成电路,例如晶体管-晶体管逻辑电路(简称TTL电路)及射极耦合逻辑电路(简称ECL电路).另一种是由MOS管组成的单极型集成电路,例如N-MOS逻辑电路和互补MOS(简称COMS)逻辑电路。

3。

2 分立元件门电路3。

3.1二极管的开关特性3.2.2三极管的开关特性NPN型三极管截止、放大、饱和3种工作状态的特点工作状态截止放大饱和条件i B=0 0<i B<I BS i B>I BS工作特点偏置情况发射结反偏集电结反偏u BE〈0,u BC〈0发射结正偏集电结反偏u BE>0,u BC〈0发射结正偏集电结正偏u BE〉0,u BC〉集电极电流i C=0 i C=βi B i C=I CSce间电压u CE=V CC u CE=V CC-i C R cu CE=U CES=0.3Vce间等效电阻很大,相当开关断开可变很小,相当开关闭合3.2。

3二极管门电路1、二极管与门2、二极管或门u A u B u Y D1D20V 0V 0V 5V 5V 0V 5V 5V0V4。

3V4。

3V4.3V截止截止截止导通导通截止导通导通3。

2.4三极管非门3。

2。

5组合逻辑门电路1、与非门电路2、或非门电路3.3 集成逻辑门电路一、TTL与非门1、电路结构(1)抗饱和三极管作用:使三极管工作在浅饱和状态。

因为三极管饱和越深,其工作速度越慢,为了提高工作速度,需要采用抗饱和三极管。

构成:在普通三极管的基极B和集电极C之间并接了一个肖特基二极管(简称SBD)。

数字电路与逻辑设计复习

第二章 逻辑函数及其简化 公式法化简

① F=(A⊕B)(B⊕C) ●A+B+A+C

解: F=[(A⊕B)(B⊕C) +A+B] ●(A+C) =[(AB+AB)(BC+BC)+A+B) ●(A+C)

第二章 逻辑函数及其简化 1 若A、B、C、D、E为某逻辑函数输入变量,函数的最大项表达式 所包含的最大项的个数不可能是: A 32 B 15 C 31 D 632 2 以下表达式中符合逻辑运算规则的是: A. C●C=C2 B. 1+1=10 C. 0﹤1 D. A+1=1 3 符合逻辑运算规则的是: A. 1×1=1 B. 1+1=10 C. 1+1=1 D. 1+1=2 4 逻辑函数F=AB+CD+BC的反函数F是:_____;对偶函数F﹡是:____; 5 逻辑代数的三个重要规则是:_________,__________,_________ 当逻辑函数有n个变量时,共有____种变量取值组合。 6 异或与同或在逻辑上正好相反,互为反函数,对吗? 7 逻辑变量的取值,1比0大,对吗? 8 F=A⊕B⊕C=A⊙B⊙C,对吗? 答案:1. D 2. D 3. C 4. ___ 5. ____ ____ 6. √ 7. × 8. √

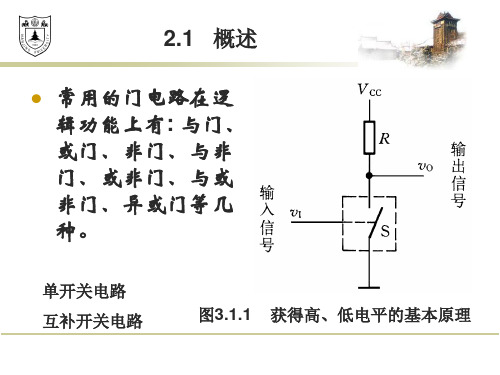

第一章 绪论 1.数制的转换 (1)任意进制→十进制(按位权展开相加) (2)十进制→任意进制(除R取余,乘R取整) (3) 二进制--八进制--十六进制(中介法) (4)精度要求(1/Ri<精度要求值) 2.常用的BCD码 有权码(8421码、2421码、5121码、631-1码) 无权码(余3码,移存码、余3循环码)。

电子技术 数字电路 第3章 组合逻辑电路

是F,多数赞成时是“1”, 否则是“0”。

0111 1000 1011

2. 根据题意列出真值表。

1101 1111

(3-13)

真值表

ABCF 0000 0010 0100 0111 1000 1011 1101 1111

3. 画出卡诺图,并用卡 诺图化简:

BC A 00

00

BC 01 11 10

010

3.4.1 编码器

所谓编码就是赋予选定的一系列二进制代码以 固定的含义。

一、二进制编码器

二进制编码器的作用:将一系列信号状态编制成 二进制代码。

n个二进制代码(n位二进制数)有2n种 不同的组合,可以表示2n个信号。

(3-17)

例:用与非门组成三位二进制编码器。 ---八线-三线编码器 设八个输入端为I1I8,八种状态,

全加器SN74LS183的管脚图

14 Ucc 2an 2bn2cn-1 2cn

2sn

SN74LS183

1 1an 1bn 1cn-11cn 1sn GND

(3-39)

例:用一片SN74LS183构成两位串行进位全加器。

D2

C

D1

串行进位

sn

cn

全加器

an bn cn-1

sn

cn

全加器

an bn cn-1

1 0 1 1 1 AB

AC

F AB BC CA

(3-14)

4. 根据逻辑表达式画出逻辑图。 (1) 若用与或门实现

F AB BC CA

A

&

B

C

&

1 F

&

(3-15)

(2) 若用与非门实现

第3章-组合逻辑电路

例:3位二进制(3线-8线)译码器框图如下所示:

图3.3.5

3线-8线译码器框图

二进制译码器可采用二极管与门阵列或三极管集 成门电路等构成。

(1)二极管与门阵列译码器电路 0(0V) 1(3V)

表3-3-4

74LS42功能表

74LS42逻辑电路图及各输出表达式如下所示:

Y 0 Y 1 Y 2 Y 3 Y 4 Y5 Y 6 Y 7 Y8 Y9 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0 A 3 A 2 A1 A 0

Y3

Y2

Y1

Y0

§3.3 若干常用的组合逻辑电路

目前,一些常用的逻辑电路已经制成了中、小 规模集成化电路产品。

§3.3.1 编码器(Encoder)

“编码”:即为了区分一系列不同的事物,将其 中的每个事物用一个二值代码表示。 编码器的逻辑功能:把输入的每一个高、低电平 信号变成一个对应的二进制代码。

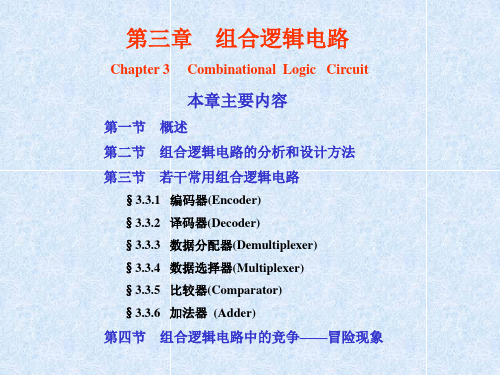

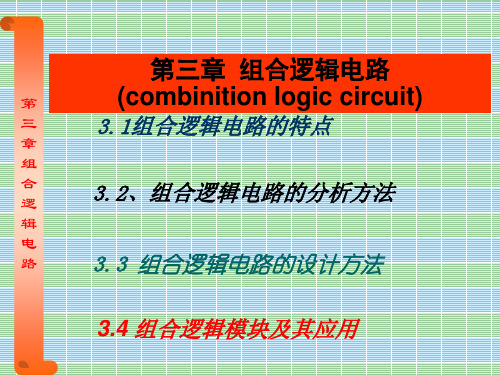

第三章

Chapter 3

组合逻辑电路

Combinational Logic Circuit

本章主要内容

第一节 第二节 第三节 概述 组合逻辑电路的分析和设计方法 若干常用组合逻辑电路

§3.3.1 编码器(Encoder) §3.3.2 译码器(Decoder) §3.3.3 数据分配器(Demultiplexer)

电子教案--数字电子技术-第三章组合逻辑电路-XXXX-1

L ABC ABC ABC ABC m1 m2 m4 m7 m1 m2 m4 m7

F ABC ABC ABC m3 m5 m6 m3 m5 m6 G ABC ABC ABC ABC m0 m2 m4 m6 m0 m2 m4 m6

G

F

=m3+m5+m6+m7

= m3 m5 m6 m7 用一片74138加一个与非门

Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0 74138

G1 G2AG2B A2 A1 A0

就可实现该逻辑函数。

1 00 AB C

中北大学电子信息工程系

第三章 组合逻辑电路

例3.4.2.2 某组合逻 辑电路的真值表如表 4.2.4所示,试用译码器 和门电路设计该逻辑电路。 解: 写出各输出的最小项 表达式,再转换成与 非—与非形式:

1.七段数字显示器原理

COM

g f ab

a fgb

e

c

d DP

COM

e d c DP

中北大学电子信息工程系

COM

a b c d e f g DP

第三章 组合逻辑电路

a b c d e f g DP

COM

按内部连接方式不同,七段数字显示器分为共阴极和共阳极两 种。

2.七段显示译码器7448 七段显示译码器7448是一种 与共阴极数字显示器配合 使用的集成译码器。

S4 S5 S6 S7 S8 S9

中北大学电子信息工程系

解:(1)列出真值表:

第三章 组合逻辑电路

(2)由真值表写出各输出的逻辑表达式为:

A S8 S9 S8S9

B S4 S5 S6 S7 S4S5S6S7 中北大学电子信息工程系

数字逻辑课后答案 第三章

第三章 时序逻辑1.写出触发器的次态方程,并根据已给波形画出输出 Q 的波形。

解:2. 说明由RS 触发器组成的防抖动电路的工作原理,画出对应输入输出波形解:3. 已知JK 信号如图,请画出负边沿JK 触发器的输出波形(设触发器的初态为0)1)(1=+++=+c b a Qa cb Q nn4. 写出下图所示个触发器次态方程,指出CP 脉冲到来时,触发器置“1”的条件。

解:(1),若使触发器置“1”,则A 、B 取值相异。

(2),若使触发器置“1”,则A 、B 、C 、D 取值为奇数个1。

5.写出各触发器的次态方程,并按所给的CP 信号,画出各触发器的输出波形(设初态为0)解:6. 设计实现8位数据的串行→并行转换器。

B A B A D +=DC B A K J ⊕⊕⊕==Q AQ B Q D Q C Q E Q F Q7. 分析下图所示同步计数电路解:先写出激励方程,然后求得状态方程状态图如下:该计数器是五进制计数器,可以自启动。

8. 作出状态转移表和状态图,确定其输出序列。

解:求得状态方程如下故输出序列为:000119. 用D 触发器构成按循环码(000→001→011→111→101→100→000)规律工作的六进制同步计数器解:先列出真值表,然后求得激励方程PS NS 输出N0 0 0 0 0 1 00 0 1 0 1 1 0 0 1 1 1 1 1 0 1 1 1 1 0 1 0 1 0 1 1 0 0 0 1 0 0 0 0 0 1化简得:逻辑电路图如下:n Q 2n Q 1n Q 012+n Q 11+n Q 10+n Q n n n nn n n n n n nnQ Q Q Q Q Q Q Q Q Q Q Q Z 121002*********+==+==+++nnn nnn nnnn QQ Q D QQ Q D QQ Q Q D 121211121122+====+==+++10. 用D 触发器设计3位二进制加法计数器,并画出波形图。

数字逻辑与计算机组成 第3章 组合逻辑电路

硬件资源:7个4输入与门、1个7输入或门

10

1.4 组合逻辑电路设计

利用布尔代数化简, 以减少逻辑门数和输入端数 X·Y+X·Y’=X

F = SN3N2N1N0(1,2,3,5,7,11,13) =N3’N0+N3’ N2’ N1 N0’+N3 N2’ N1 N0+N3 N2 N1’ N0

非法值 • 信号值不能被有效识别为高电平或低电平,处于不确定状态。 例如:下图中的信号X

不管A是0还是1,F结点都会同时 被高电平和低电平驱动,可能导 致在F结点处之间有较大电流流动 ,使电路发热而被损坏

16

1.5 无关项、非法值和高阻态

例:设计一个检测电路,当NBCD(8421)码数值大于5时,输出为1

最简输出表达式

函数转换:独立逻辑门、中间组件、可编程器件

画出逻辑电路图 逻辑器件的标准符号,输入、输出信号、器件标识

评价电路

电路分析:功能、缺陷、电气特性等

9

1.4 组合逻辑电路设计

例1:素数检测器的设计

列出真值表

• 4-bit input, N3N2N1N0

写出最小项表达式 F = SN3N2N1N0(1,2,3,5,7,11,13)

输出变量:故障信号F 正常工作为0,发生故障为1

故障状态 真 值 表 RY G F

0 0 01 0 0 10 0 1 00 0 1 11 1 0 00 1 0 11 1 1 01 1 1 11

13

1.4 组合逻辑电路设计

逻辑抽象结果

真值表

RY G F

000 1 001 0 010 0 011 1 100 0 101 1 110 1 111 1

每个输入端和输出端只有高电平、

数字电子技术基础(第3章) 组合逻辑分析与设计

第3章 组合逻辑设计

A B

&

Y

与非门的逻辑符号

L=A+B (2)或非运算:逻辑表达式为: Y A B

A 0 0 1 1 B Y 0 1 1 0 0 0 1 0 真值表

A B

≥1

Y

或非门的逻辑符号

第3章 组合逻辑设计

(3)异或运算:逻辑表达式为: Y

A 0 0 1 1 B Y 0 0 1 1 0 1 1 0 真值表

A

B F

A B

F

0 0 1 1

0 1 0 1

0 1 1 1

第3章 组合逻辑设计

功能表

开关 A 断开 断开 闭合 闭合 开关 B 断开 闭合 断开 闭合 灯Y 灭 亮 亮 亮

真值表

A 0 0 1 1

B 0 1 0 1

Y 0 1 1 1

逻辑符号 实现或逻辑的电 路称为或门。或 门的逻辑符号:

A B

≥1

第3章 组合逻辑设计

第3章 组合逻辑分析与设计

3.1 逻辑代数基础

3.2 逻辑函数的化简

3.3 组合逻辑电路的分析

3.4 组合逻辑电路的设计

3.5 VHDL硬件描述语言 3.6 基本组合逻辑电路的设计举例 3.7 组合逻辑电路中的竞争-险象

第3章 组合逻辑设计

3.1 逻辑代数基础

逻辑代数(Logic Algebra)是由英国数学家乔治· 布尔(George Boole)于1847年首先提出的,因此也称为

(A+B)(A+C)

第3章 组合逻辑设计

吸收率:

A ( A B) A B A A B A B

证明: A A B ( A A)(A B)

数字电路组合逻辑电路

2021/4/21 Y1 Y3 Y5 Y6 Y7

38

因此,正确连接控制输入端使译码器处于工 作状态,将Y1 Y、3 Y、5 Y、6 Y、7 经一个与非门 输出,A2、A1、A0分别作为输入变量A、B、C,就可 实现组合逻辑函数。

F (A, B,C) m(1,3,5,6,7)

Y1 Y3 Y5 Y6 Y7

(2)列真值表; 把逻辑关系转换成数字表示形式;

表3-2 例3-3真值表 (3) 由真值表写逻辑表 A B C Y 达式,并化简;

0000

0010 0100

化简得最简式:

0111

1000

1011

1 1 0 1 2021/4/21

12

1111

(4) 画逻辑电路图: 用与非门实现,其逻辑图与例3-1相同。 如果作以下变换:

输出:三位二进制代码

Y2Y1Y0

2021/4/21

称八线—三线编码器18

图3-4 普通编码器的方框图

设输入信号为1表示对该输入进行编码。

表3-4 编码器输入输出的对应关系

I0 I1 I2 I3 I4 I5 I6 I7 Y2 Y1 Y0 10 0 0 0 0 0 0 0 0 0

01 0 0 0 0 0 0 0 0 1

2021/4/21

2

第3章 组合逻辑电路

数字电路分类:组合逻辑电路和时序逻辑电路。 组合逻辑电路: 任意时刻的输出仅仅取决于当时 的输入信号,而与电路原来的状态无关。

本章内容提要

小规模集成电路(SSI)构成组合逻辑电路的

一般分析方法和设计方法。

常用组合逻辑电路的基本工作原理及常用中

规模集成(MSI)组合逻辑电路的逻辑功能、使

(2) 实现组合逻辑函数F(A,B,C)

数字逻辑电路第3章复习题

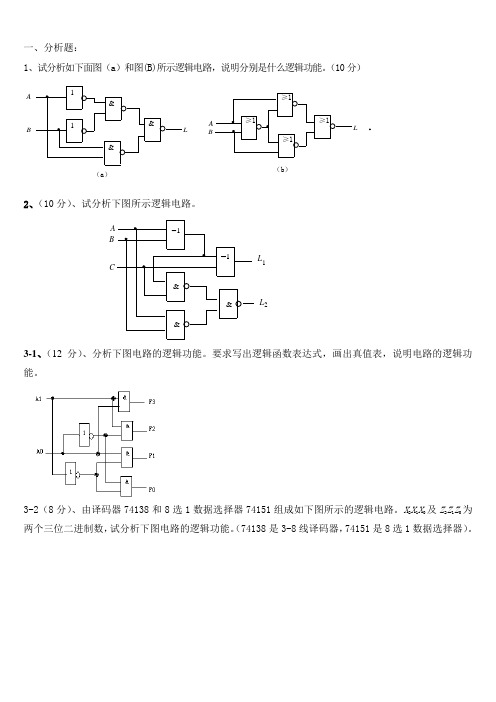

一、分析题:1、试分析如下面图(a )和图(B)所示逻辑电路,说明分别是什么逻辑功能。

(10分).2、(10分)、试分析下图所示逻辑电路。

2B L =11AC&L &=1&3-1、(12分)、分析下图电路的逻辑功能。

要求写出逻辑函数表达式,画出真值表,说明电路的逻辑功能。

3-2(8分)、由译码器74138和8选1数据选择器74151组成如下图所示的逻辑电路。

X 2X 1X 0及Z 2Z 1Z 0为两个三位二进制数,试分析下图电路的逻辑功能。

(74138是3-8线译码器,74151是8选1数据选择器)。

A1&B1&&L≥1≥1≥1≥1LAB(a)(b)5Y 6D 074138D 13401A Y 7G 0Y 13D A 52D Y D A 6G D 1Y Y Y D 274201Y2BD 74151G 2A1A A 02A Y1X 02X X 10Z Z Z 24、(6分)由译码器74138和门电路组成的电路如下图所示,试写出L 1、L 2的最简表达式。

5、6、(12分)、下图所示的TTL 门电路中,要求实现下列规定的逻辑功能时,其连接有无错误?说明正确或错误的理由。

如有错误请改正。

CD AB L ⋅=1 AB L =2 C AB L +=3+V &R PC D&L CCB A 1B&A =1V CCL 2&L 3CB A ≥1(a ) (b) (c)7、(12分)、在下图(a )(b )(c )中,所有的门电路都为TTL 门,设输入A 、B 、C 的波形如图(d )所示,试分析电路的逻辑关系,写出表达式,并定量画出各输出的波形图。

BA =1V CCL 1≥1A 2L BC &≥1EN&△B C1G L 3A &ABC(a)(b)(c)(d)8、(8分)、分析下图所示电路,求输入S 1、S 0各种取值下的输出Y ,填入下表中。

第三章组合逻辑电路 (1)

第三章组合逻辑电路一、概述1、概念逻辑电路分为两大类:组合逻辑电路和时序逻辑电路数字逻辑电路中,当其任意时刻稳定输出仅取决于该时刻的输入变量的取值,而与过去的输出状态无关,则称该电路为组合逻辑电路,简称组合电路2、组合逻辑电路的方框图和特点(1)方框图和输出函数表达式P63输出变量只与当前输入变量有关,无输出端到输入端的信号反馈网络,即组合电路无记忆性,上一次输出不对下一次输出造成影响3、组合逻辑电路逻辑功能表示方法有输出函数表达式、逻辑电路图、真值表、卡诺图4、组合逻辑电路的分类(1)按功能分类常用的有加法器、比较器、编码器、译码器等(2)按门电路类型分类有TTL、CMOS(3)按集成度分类小、中、大、超大规模集成电路二、组合逻辑电路的分析方法 由电路图---电路功能 1、分析步骤(1)分析输入输出变量、写出逻辑表达式 (2)化简逻辑表达式 (3)列出真值表(4)根据真值表说明逻辑电路的功能 例:分析下图逻辑功能第一步:Y=A ⊕B ⊕C ⊕D 第二步: 第三步:A B C D Y 0 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 0 1 0 0 1 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 10 0 0 1=1=1=1CDY1 0 0 1 01 0 1 0 01 0 1 1 11 1 0 0 01 1 0 1 11 1 1 0 11 1 1 1 0第四步:即0和1出现的个数不为偶则输出1,奇偶个数的检验器三、组合逻辑电路的设计方法1、概念根据要求,最终画出组合逻辑电路图,称为设计2、步骤(1)确定输入输出变量个数(2)输入输出变量的状态与逻辑0或1对应(3)列真值表(4)根据真值表写出输出变量的逻辑表达式(5)对逻辑表达式化简,写出最简逻辑表达式(6)根据逻辑表达式,画出逻辑电路图例:三部雷达A、B、C, 雷达A、B的功率相等,雷达C是它们的两倍,发电机X最大输出功率等于A的功率,发电机Y输出功率等于A与C的功率之和,设计一个组合逻辑电路,根据雷达启停信号以最省电的方式开关发电机第一步:输入变量3个,输出变量2个第二步:雷达启动为1、发电机发电状态为1第三步:A B C X Y0 0 0 0 00 0 1 0 10 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1第四步:卡诺图化简第五步:写逻辑表达式第六步:画逻辑电路图四、常用中规模标准组合模块电路一些常用的组合逻辑电路,如编码器、译码器、加法器等制成中规模电路,称为中规模标准组合模块电路1、半加器进行两个1位二进制数相加的加法电路称为半加器,如图3-11所示真值表如下:A B S C0 0 0 00 1 1 01 0 1 01 1 0 1根据真值表,写出逻辑表达式如下:S=AB+AB=A⊕BC=AB2、全加器即带低位上产生的进位的加法器真值表如下:A iB iC i-1S i C i0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1根据真值表,卡诺图化简后写出逻辑表达式如下:S i=A i⊕B i⊕C i-1C i=A i B i+C i-1(A i⊕B i)(为便于实现)根据逻辑表达式,画出电路图如图3-13所示3、加法器可以实现多位二进制数加法的电路(1)串行进位加法器低位全加器的进位输出端连到高位全加器的进位输入端,如图3-3所示(2)超前进位加法器C i=A i B i+C i-1(A i⊕B i)= A i B i+C i-1(A i B i+ A i B i)= A i B i C i-1+A i B i C i-1 +A i B i C i-1+ A i B i C i-1=A i B i+ B i C i-1+ A i C i-1= A i B i+C i-1(A i+B i)令P i=A i+B i,称P i为第i位的进位传输项,令G i=A i B i,称G i 为第i位的进位产生项,则第0位的进位为C0=G0+P0C-1,第1位的进位为C1=G1+P1 C0, C0带入C1,消去C0,得C1=G1+P1(G0+P0 C-1),同理,得C2= G2+P2(G1+ P1(G0+P0 C-1)),,C3= G3+ P3(G2+ P2(G1+P1(G0+P0 C-1))),即知道相加的二进制数的各位和最低位进位就可以超前确定进位,提高了速度,如图3-4所示4、乘法器完成两个二进制乘法运算的电路(1)乘法器P85(2)并行乘法器P855、数值比较器比较二进制数大小,输入信号是要比较的数,输出为比较结果(1)1位数值比较器A B M G L0 0 0 1 00 1 1 0 01 0 0 0 11 1 0 1 0M=ABG=AB+AB= AB+AB(便于逻辑实现)L=AB逻辑电路图如图3-5所示(2)4位数值比较器多位二进制数比较大小,先看最高位情况,如相等再看次高位情况,以此类推4位比较器为例,8个输入端(A3A2A1A0,B3B2B1B0),三个输出端(L,G,M)A>B,则A3>B3,或A3=B3且A2>B2,或A3=B3,A2=B2,A1>B1,或A3=B3,A2=B2,A1=B1,A0>B0设定AB的第i位比较结果为L i=A i B i,G i=A i B i+A i B i,M i=A i B i,则L=L3+G3L2+G3G2L1+G3G2G1L0同理, A=B 时,G=G3G2G1G0,A<B时,M=M3+G3M2+G3G2M1+G3G2G1M0,因A不大于也不等于B时即小于B,故M=LG=L+G(便于逻辑实现)逻辑电路图如P87图3-18所示(3)集成数值比较器4位数值比较器封装在芯片中,构成4位集成数值比较器,74ls85真值表如图3-6所示考虑到级联,增加了级联输入端(更低位的比较结果),级联时,如构成8位数值比较器,低四位比较结果为高四位数值比较器的级联输入端,而低四位的级联输入端应结为相等的情况(010),74ls85级联如图3-7所示cc14585真值表如图3-8所示,cc14585级联如图3-9所示6、编码器将输入信号用二进制编码形式输出的器件,若有N个输入信号,假设最少输出编码位数为m位,则2m-1<N<2m(1)二进制编码器以2位输出编码为例输入输出I0I1I2I3Y1Y01 0 0 0 0 00 1 0 0 0 10 0 1 0 1 00 0 0 1 1 1故Y1=I2+I3,Y0=I1+I3逻辑电路图如P89图3-22所示但当不止一个输入端有编码要求时该电路不能解决问题(2)二进制优先编码器3位二进制优先编码器为例8个输入端为I0~I7,输出端为Y2~Y1,假设I7的编码优先级最高,则对应真值表为:输入输出I0I1I2I3I4I5I6I7Y2Y1Y0×××××××0 0 0 0 ××××××0 1 0 0 1 ×××××0 110 1 0 ××××0 1110 1 1 ×××0 1111 1 0 0 ××0 11111 1 0 1 ×0 111111 1 1 0 0 1111111 1 1 1 “×”为任意值根据真值表,列出逻辑表达式如P90所示,逻辑图过于麻烦,略以上为低电平有效的情况,高电平有效真值表如图3-10所示,得A2=I4+I5+I6+I7,A1=I2+I3+I6+I7,A0=I1+I3+I5+I7, 逻辑图便于实现(3)8线-3线编码器74ls148编码器图形符号如图3-11所示,真值表如图3-12所示74ls148编码器级联,注意控制信号线的连接,级联图如图3-13所示选通信号有效,当高位芯片输入不全为1时,选通输出端为1,低位芯片不工作且二进制反码输出端为1,与门受高位芯片二进制反码输出端影响,扩展输出端为0,作为A3,根据输入情况不同,得编码0000~0111;选通信号有效,当高位芯片输入全为1时,高位芯片不工作,选通输出信号为0,低位芯片工作,高位芯片扩展输出端为1,作为A3,高位芯片二进制反码输出端全1,与门受低位芯片二进制反码输出端影响,根据输入情况不同,得编码1000~1111,即实现16线-4线编码器功能(4)9线-4线编码器74ls147编码器图形符号、真值表如图3-14所示注意,其输出对应十进制数的8421BCD码的反码(5)码组变换器将输入的一种编码转换为另一种编码的电路参见P92例3-5原理:加0011和加1011的原因7、译码器译码是编码的逆过程,将二进制代码转换成相应十进制数输出的电路(1)3线-8线译码器真值表如图3-15所示逻辑表达式如下:Y0=CBA、Y1=CBA……Y6=CBA、Y7=CBA(2)集成3线-8线译码器74LS138译码器符号如图3-16所示,真值表如图3-17所示注意三个选通信号,在级联时的作用,级联如图3-18所示74LS138译码器典型应用如图3-19所示(3)集成4线-10线译码器74LS42符号如图3-20所示,真值表如图3-21所示逻辑表达式如图3-22所示(4)显示译码器是用来驱动显示器件的译码器(A)LED数码管电能---光能(发光二极管构成)具有共阴极和共阳极两种接法,如图3-23所示,注意非公共端连接高电平或低电平时要串接限流电阻(B)显示译码器74LS47(驱动LED为共阳极接法的电路,驱动共阴极要用74LS48)引脚图如图3-24所示,真值表如图3-25所示要具有一定的带灌电流负载能力才能驱动LED相应段发光,显示效果如P99图3-35所示附加控制端用于扩展电路功能:灯测试输入LT:全亮灭零输入RBI:将不需要的“0”不显示以使得要显示的数据更醒目灭灯输入\灭零输入BI\RBO:作为输入使用,一旦为0则灯灭。

数字电路与逻辑设计 第3讲

真值表如下: 真值表如下:

输出 Y2 Y1 Y0 GS

1 × × × × × × × × × × × × × × × 0

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

1 × × × × ×

今后会经常遇到的几种控制信号:(用来增强器件的功能) 今后会经常遇到的几种控制信号: 用来增强器件的功能) EI为使能输入端 低电平有效) 有时也称作片选信号。 为使能输入端( 1 、 EI 为使能输入端 ( 低电平有效 ) , 有时也称作片选信号 。 就 74LS LS148 EI/CS=1 74LS148 来 说 , 当 EI/CS=1 时 , 该 器 件 是 不 工 作 的 , 只 有 在 EI/CS=0时才工作。 EI/CS=0时才工作。 EO为使能输出端 低电平有效) EO只有在 EI=0 为使能输出端( 只有在EI= 2 、 EO 为使能输出端 ( 低电平有效 ) : EO 只有在 EI=0 ( 器件在工 而且所有输入都为1 说明无有效输入) 输出为0 作),而且所有输入都为1(说明无有效输入)时,输出为0。 这时可以将该片的EO接到另一片的EI EO接到另一片的EI上 这时可以将该片的EO接到另一片的EI上(显然这一片的优先权 允许它工作(EI=0 因此实现了扩展。 低),允许它工作(EI=0)。因此实现了扩展。 3 、 GS 为 优 先 编 码 工 作 标 志 ( 低 电 平 有 效 ) : 用 来 区 分 011111111” 此时GS= 编码器处于编码状态) GS=0 I0I1I2…I7=“011111111”(此时GS=0,编码器处于编码状态) I =“011111111 111111111” GS=1 和 I0I1I2…I7=“111111111” 的情况 ( 此时 GS=1 , 编码器处于 I =“111111111 的情况( 此时GS= 非编码状态) 非编码状态)。

数字电路与逻辑设计第3章组合逻辑电路

(2)根据真值表,用卡诺图(图3-5 a)化简后,

可以得到该电路的逻辑函数表达式:

F AC BC AB

由于题目中没有特别要求以何种逻辑门 输出,所以可用与门和或门输出来实现 该逻辑功能,表达式形式无需转换。

(3)逻辑图 由化简后的表达式和真值 表可以看出,(图 3-5 b)即使该题的逻 辑电路图。

表 3-7 8线—3线编码器的真值表

因为任意时刻 I0 ~ I7 中只有一个值为“1”利 用约束项的知识把上述真值表化简后如表3-8 所示。

表 3-8 化简后的真值表

由真值表写出其对应的逻辑函数表达式:

Y2 I4 I5 I6 I7 I4I5I6I7 Y1 I2 I3 I6 I7 I2I3I6I7 Y0 I1 I3 I5 I7 I1I3I5I7

3) 将表达式转化成用“与非” 逻辑形式实 现的形式:

图3-9 (a)卡诺图 (b)逻辑电路

3.2 编码器

编码就是将特定的逻辑信号变换成 一组二进制的代码,而能够实现这种功 能的逻辑部件就称为编码器。编码器的 功能是将输入信号转换为对应的代码信 号,即是用输出的代码信号来表示相对 应的输入信号,以便于进行对代码进行 存储,传输及运算等处理。

FA A FB AB FC ABC FD ABCD

(3)由上述表达式可得其对应的优先编码逻辑 电路如图3-12所示。

图3-13 16线—4线优先编码器的逻辑电路

(2)根据列写出的逻辑问题的真值表,写出对应 的逻辑函数表达式。

(3)将得到的逻辑函数表达式进行变换和化简。 逻辑函数的化简可以利用我们前面所学习的代 数法或卡诺图法,从而得到逻辑函数的最简表 达式,对于一个逻辑电路,在设计时应尽可能 使用最少数量的逻辑门,逻辑门变量数也应尽 可能少用,还应根据题意变换成适当形式的表 达式。

第三章疑难问题问答

网络教材——《数字电子技术》-组合逻辑电路的分析与设计Frequently Asked Question(FAQ)1. 列举逻辑函数的四种表示方法?解:逻辑真值表、逻辑式、逻辑图、卡诺图和波形图。

2. 逻辑代数和普通代数有什么区别?解:逻辑代数和普通代数的主要区别有:a) 逻辑变量有原变量和反变量两类,普通代数中没有反变量一说。

b) 逻辑变量的取值只有“0”和“1”两个,而普通代数中变量可取任意值。

c) 逻辑代数中的各种运算都是逻辑运算,而不是普通代数中的数值运算。

同样,逻辑变量的两个取值“0”和“1”,也不代表数值的大小,而只是代表两个相反的状态而已。

d) 逻辑代数中的基本运算只有逻辑乘(“与”)、逻辑加(“或”)和逻辑“非”(求反或否定)三种,不像普通代数中有加、减、乘、除四种。

3. 能否将AB=AC,A+B=A+C,A+AB=A+AC这三个逻辑式化得为B=C?解:不能!上述三个等式只表明等式两边的逻辑运算结果相同,并不能说明等式两边的输入条件有何种关系,在逻辑代数中也没有减法和除法运算,不能将等式左边的变量或“与”项搬到右边去相减和相除。

上述三个等式中B和C只能说具有相同的逻辑效果,但并不是相同的逻辑条件,不能划等号,例如在第三个等式中B和C都是冗余项中的因子,与逻辑结果无关。

4. 二进制加法运算和逻辑加法运算的含义有何不同?解:二进制加法是一种算术运算,只是采用逢2进位法。

逻辑加法是一种“或”运算,不存在进位问题。

5. 将十进制数13,43,121转换为二进制数;将二进制数10101,11111,000011转换十进制数。

解:(13)D=(1101)B, (43)D=(101011)B(121)D=(1111001)B,(10101)B=(21)D(11111)B=(31)D, (000011)B=(3)D 6. 试说明1+1=2,1+1=10,1+1=1各式的含义。

解:1+1=2是十进制加法运算,1+1=10是二进制加法运算,1+1=1是逻辑加法运算。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

B

C

uI 增大使 uBE > Uth

时,三极管开始导通, iB > 0,三极管工作于 放大导通状态。

uBE < Uth E

三极管 截止状态 等效电路

iC 临界饱和线 M T IC(sat) uI=UIH + uBE S Q

放大区

IB(sat)

饱 和 区

截止区

O UCE(sat) B uBE < Uth A N C uCE

晶体管的开关特性

TTL集成逻辑门 MOS逻辑门电路

3.4

CMOS电路

3.1 晶体管的开关特性

3.1.1晶体三极管的开关特性 1.二极管的稳态开关特性

(a) 二极管符号表示

(b) 二极管伏安特性

二极管符号表示及伏安特性

加正向电压时导通,伏安特性很陡、压降很小(硅管为

0.7V,锗管为0.3V),可以近似看作是一个闭合的开关

截止条件 uBE < Uth 可靠截止条件为 uBE ≤ 0

VCC U CE(sat) RC VCC RC

饱和条件

iB > IB(Sat)

iB 愈大于 IB(Sat) , 则饱和愈深。

由于UCE(Sat) 0,因此饱和后 iC 基本上为恒值, iC IC(Sat) =

I B(sat) I C(sat) VCC RC

t

② Ui>UREF+Uon时,二极管正偏导 通,相当于短路,uo=

UREF+Uon;

2)钳位电路。钳位电路是将脉冲波形的顶部或底部钳定

在某一选定电平上。其实质是由二极管的通断来改变RC电

路的充放电时间常数,使得电容C实现快充慢放或者慢充 快放,达到钳位波形的目的。

3.1 晶体管的开关特性

3.1.2晶体三极管的开关特性 1. 三极管稳态开关特性

1V

导通

截止

பைடு நூலகம்

0.3V

导通

UF =UCE4

0.3V

输出低电平,与非门处于开门状态

由此可见,电路的输出和输入之间满足与非逻辑关系。

F A B C

在两种工作状态下,各晶体管工作情况如表所示: TTL与非门各级工作状态 与 非 门 状 态 开 门

A B C

Vcc

R1

4K

输

入

T1

T2

T3

D4 T4

UCE(sat) O

t

uI

UIH UIL O

iC

0.9IC(sat) IC(sat) 0.1IC(sat) O uO VCC ton toff

t

uI 正跳变到 iC 上升 到 0.9IC(sat) 所需的时间 ton 称为三极管开通时间。

uI 负跳变到 iC 下降 到 0.1IC(sat) 所需的时间 toff 称为三极管关断时间。 通常toff > ton

(2)功能分析

当VT1输入端有一个或数个 为 低电平时,输出高电平 。 输入低电平端对应的发射结 导通, 1V

5 V

截止

导通

uB1=0.3V+0.7V=1V

其他发射结因反偏而截止。

0.3 V 3.6 V 3.6 V

3.6 V

截止

VT2和VT4均截止

VT2

截止使 uC2 VCC = 5 V, VT3和VD导通。

硅管正向压降为0.7V, 锗管正向压降为0.3V。 反向截止

3.1 晶体管的开关特性

(1)加正向电压VF时,二极管导通,管压降VD可忽略。 二极管相当于一个闭合的开关。

D VR

S VR

RL

IS

RL

(a)二极管正向导通电路

(b)二极管正向导通等效电路

外加正向电压的情况

3.1 晶体管的开关特性

(2)加反向电压VR时,二极管截止,反向电流IS可忽略。

uI UIH UIL O iC IC(sat) O uO VCC

uI 从 UIH 负跳到时 UIL,

三极管不能很快由饱和转变 为截止,而需要经过一段时 t 间才能退出饱和区。

uI 从 UIL 正跳到 UIH 时,

三极管将由截止转变为饱和, iC 从 0 逐渐增大到 IC(sat), t uC 从 VCC 逐渐减小为UCE(sat)。

算电流I和输出电压uo

解:理想模型

+

R I

U REF +

ui -

uO -

恒压降模型

(2)如果ui为幅度±4V的交流三角波,波形如图(b)所示,

分别采用理想二极管模型和恒压降模型分析电路并画出相 应的输出电压波形。

R

+

ui

I

U REF +

ui -

uO -

4V 2V

t

0

-4V

解:理想模型(波形如图所示)。 uo

三极管开通的条件和等效电路 当输入 uI 为高电平,使 iB ≥ IB(sat)时,三极管饱和。

E

B UBE(sat) iB ≥ IB(sat) E C

三极管 截止状态 等效电路

uBE UCE(sat) 0.3 V 0,

C、E 间相当于开关合上。

UCE(sat)

三极管 饱和状态 等效电路

开关工作的条件

加反向电压时截止,反向电流很小可以近似看作是一 个断开的开关。

I/mA

3

正向特性

反向特性

-60 -40 -20

2 1 0.2 0.4 0.6 U/V -0.01 -0.02 -0.03

反向击穿 特性

开启电压

1、理想模型

2、恒压降模型

3、折线模型

正向压降为0,反向 电流为0(正向导通 反向截止)

三极管-----反相器电路

输入高电平时,晶体管饱和导通, UO=UCE 0.3V,输出低电平 输入低电平时,晶体管截止,

UO VCC=5V ,输出高电平

可见,该电路在输入低电平时输出高电平,输 入高电平时输出低电平,因此构成三极管非门。 由于输出信号与输入信号反相,故又称三极管 反相器。

[例]下图电路中 = 50,UBE(on) = 0.7 V,UIH = 3.6 V,UIL = 0.3 V, 为使三极管开关工作,试选择 RB 值,并对应输入波形画出输出波形。

二极管与门真值表

UA 0 0 3 3

UB 0 3 0 3

VD1 导通 导通 截止

VD2 导通 截止 导通

导通

导通

UF 0.7 0.7 0.7 3.7

UA 0 0 1 1

UB 0 1 0 1

UF 0 0 0 1

2)二极管或门

F A B

A B 二极管或门电压关系

A B Y

二极管或门真值表

UA UB 0 0 0 3 3 0 3 3

① ui<UREF时,二极管反偏截止,相当2V 于开路,回路无电流,uo=ui; ② Ui>UREF时,二极管正偏导通,相当 于短路,uo= UREF;

t

恒压降模型(波形如图所示)。 ui

R

+

I

U REF

+

4V 2.7V

t

ui -

uO -

0

-4V

uo

① ui<UREF+Uon时,二极管反偏截

止,相当于开路,回路无电 2.7V 流,uo=ui; 0

uF =VCC -UBE3-UD-IB3R2 ≈ 5V - 0.7 V - 0.7 V = 3.6 V

输出高电平,与非门处于关闭状态。

输入均为高电平时,输 出低电平 VT1 集电结导通(倒置), VT2 VT4饱和导通

2.1V uB1=0.7V+0.7V+0.7V=2.1V, 倒置放大 3.6 V 3.6 V uB3=0.7V+0.3V=1V 3.6 V VT3和VD截止,

t

•在0~t1期间,vi = VF时,D 导通,电路中有电流流过:

-I R ts tt

t

•正向(饱和)电流愈大,电荷的浓度分布梯度愈大,存储 的电荷愈多,电荷消散所需的时间也愈长。 •产生反向恢复的过程的原因:存储电荷消散需要时间

3.二极管的应用电路

1). 二极管与门

F AB

A B

Y

二极管与门电压关系

数字电路与逻辑设计

第三章 集成逻辑门

第三章 集成逻辑门

目的与要求:

了解半导体二极管、三级管和MOS的开关特性; 掌握TTL门电路和CMOS门电路的基本工作原理和外特性; 熟悉TTL门电路和CMOS门电路的主要参数,掌握门电路 的正确使用。

重点与难点:

TTL门电路和CMOS门电路的外特性。

3.1

3.2 3.3

在数字电路中,三极管作为开关元件,主要工作在饱 和和截止两种开关状态,放大区只是极短暂的过渡状态。

iC 临界饱和线 uI 增大使 iB 增大, S 为放大和饱和的交界点,这时的 放大区 从而工作点上移, iC 增 iB 称临界饱和基极电流,用 IB(sat) 表示; T M S 大,uCEI减小。 相应地,IC(sat) 为临界饱和集电极电流; IC(sat) B(sat) UBE(sat) 为饱和基极电压; 饱 Q UCE(sat) 为饱和集电极电压。对硅管, 和 截止区 UBE(sat) 0.7V, UCE(sat) 0.3V。在临 A 区 界饱和点三极管仍然具有放大作用。 O U N u

(2) 对应输入波形画出输出波形 三极管截止时, iC 0,uO +5 V 三极管饱和时, uO UCE(sat) 0.3 V 可见,该电路在输入低 电平时输出高电平,输入高 电平时输出低电平,因此构 成三极管非门。