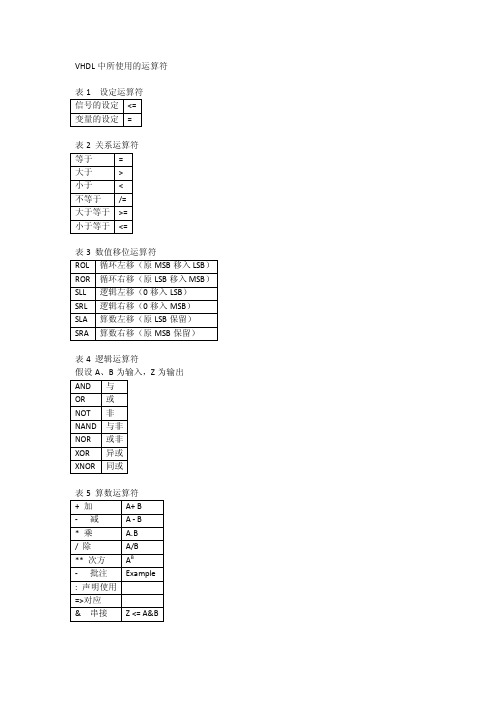

VHDL中所使用的运算符

VHDL操作符

第4讲 VHDL运算操作符

XOR

异或。 必须注意: 运算符的左边和右 边,以及代入的信号的数据类 型必须是相同的。

第4讲 VHDL运算操作符

逻辑操作符

【例1】 SIGNAL a ,b,c : STD_LOGIC_VECTOR (3 DOWNTO 0) ; SIGNAL d,e,f,g : STD_LOGIC_VECTOR (1 DOWNTO 0) ; SIGNAL h,i,j,k : STD_LOGIC ; SIGNAL l,m,n,o,p : BOOLEAN ; ... a<=b AND c; --b、c相与后向a赋值,a、b、c的数据类型同属4位长的位矢量 d<=e OR f OR g ; -- 两个操作符OR相同,不需括号 h<=(i NAND j)NAND k ; -- NAND不属上述三种算符中的一种,必须加括号 l<=(m XOR n)AND(o XOR p); -- 操作符不同,必须加括号 h<=i AND j AND k ; -- 两个操作符都是AND,不必加括号 h<=i AND j OR k ; -- 两个操作符不同,未加括号,表达错误 a<=b AND e ; -- 操作数b与 e的位矢长度不一致,表达错误 h<=i OR l ; -- i 的数据类型是位STD_LOGIC,而l的数据类型是 ... -- 布尔量BOOLEAN,因而不能相互作用,表达错误。

第4讲 VHDL运算操作符

移位操作符

SLL(逻辑左移)

SRL(逻辑右移)

SLA(算术左移)

SRA(算术右移) ROL(逻辑循环左移) ROR(逻辑循环右移) 移位操作符的语句格式是: 标识符 移位操作符 移位位数 ;

第4讲 VHDL运算操作符

VHDL的运算符号

VHDL的运算符号VHDL中主要有六类运算符号:赋值运算、逻辑运算、算术运算关系运算、连接运算、移位运算运算符号主要用于各类表达式中;运算可以分为单目运算(只有一个运算量)和双目运算(针对两个运算量);进行双目运算时,两个运算量必须类型相同;VHDL中运算没有左右优先级差别,同一表达式中进行多个运算时必须用括号表达先后差别;在同类运算中,单目运算优先;在所有运算符号中,NOT的优先级别最高;在一般运算中,优先顺序排列为:算术—关系—逻辑可以通过加括号来改变运算的优先顺序;赋值运算符<= 信号赋值:将右端值赋给左端信号;:= 变量赋值:将右端值赋给左端变量;或用于赋初始值;=> 数组内部分元素赋值;适用类型:所有数据类型;赋值号两边的数据类型原则上应该相同;逻辑运算符NOT AND OR NAND NOR XOR适用类型:STD_LOGIC STD_LOGIC_VECTORBIT BIT_VECTOR BOOLEAN逻辑运算结果为同类型逻辑量;对数组类型进行逻辑运算时,参与运算的两个数据位数必须相等,所做运算为对应位进行;算术运算:/ (除)* (乘) + (加)- (减)MOD(求模)REM(取余)**(指数) ABS(绝对值)适用类型:INTEGER REAL BIT BIT_VECTOR TIME加/减运算的结果为同类型算术量;注意:算术运算大多数只用于抽象的编程(行为设计);只有少数算术运算符能够进行综合,应尽量只使用加/减;对数组类型进行算术运算时,两边位数必须相同;关系运算:=> (大于等于)<= (小于等于)> (大于)< (小于) /= (不等于)= (等于)适用类型:等于和不等于适用于所有类型;其他运算适用于整数、实数、位、位矢量,以及枚举类型和数组类型;可比较位长度不相同的情况(从左向右逐位比较);关系运算的结果为boolean类型: false true注意:小于等于符号与信号赋值符号的写法相同,应注意使用位置和意义;连接运算:&适用类型bit bitvector character stringstd_logic std_logic_vector连接运算结果为同类型元素构成的数组;库和包集合除了实体、结构体外的第三种可编程结构Library 库编译后数据的集合,存放包集合定义、实体定义、构造体定义和配置定义,其功能相当于其他操作系统中的目录,经过说明后,设计中就可以使用库中的数据,实现共享;在前面图形输入的应用中,已多次采用库中的单元进行设计;库的使用:当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及范围;每个实体都应独立进行库的说明;库的说明应该在实体之前;经过说明后,实体和结构体就可以自动调用库中的资源;库说明语句格式library 库名;use 库名.包集合名.范围(或项目名);例: library ieee;use ieee.std_logic_1164.all;VHDL中库的主要种类:IEEE库STD库ASIC库work库用户定义库IEEE库:含有IEEE的标准包集合“STD_LOGIC_1164”以及一些大公司提供的包集合;使用前必须说明;例:library ieee;use ieee.std_logic_1164.all; 使用标准逻辑量的定义和运算;use ieee.std_logic_unsigned.all; 无符号数算术运算的定义;use ieee.std_logic_arith.all; 使用符号数算术运算的定义;STD库:含有“STANDARD”包集合和“TEXTIO”包集合,使用前者时无需说明;ASIC库:由各公司提供,存放与逻辑门一一对应的实体,用于ASIC 设计的门级仿真,使用时需加以说明;例library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;WORK库:WORK库为现行作业库,位于当前使用时设计文件的指定保存目录;WORK使用时通常无须说明;但在结构设计中进行元件的宏调用时需要说明;例:use work.all;用户定义库:由用户自定义生成,使用时需说明(指定库所在的路径);package 包集合用于罗列VHDL语言中使用的类型定义、信号定义、常数定义、元件定义、函数定义和过程定义等(类似于C语言中的include语句),方便不同模块的设计中公共定义的共享;数字电路设计中经常使用的包集合:ieee.std_logic_1164 逻辑量的定义ieee.std_logic_arith 数据转换,逻辑判断ieee.std_logic_unsigned 算术运算std.textio 文本数据输入/输出格式包集合在使用前必须采用use语句进行说明(在设计程序的最前面);包集合可以由用户自定义;包的结构与定义:(用户自定义的包集合)包集合标题+(包集合体)包集合标题:package 包集合名 is说明语句;(只有名称)end 包集合名;包集合体:package body包集合名 is说明语句;(完整定义)end 包集合名;例:(函数取自p.279 表4-38 )library ieee;use ieee.std_logic_1164.all;packge upac isconstant k: integer := 4;subtype cpu_bus is std_logic_vector(k-1downto 0); function conv_integer (x:std_logic_vector) return integer; end upac;packge body upac isfunction conv_integer (x: std_logic_vector) return integer is variable result: integer;beginresult := 0;for I in x'range loopresult :=result*2;case x(i) iswhen '0'|'L' => null;when '1'|'H' => result := result+1;when others => null;end case;end loop;return result;end conv_integer;end upac;用户自行编写的包集合将自动存放于WORK库中,使用时可采用下列语句调用use work.upac.all;configuration 配置在一个实体内可以编写多种不同的构造体,通过配置语句来进行选择;配置语句格式:configuration 配置名 of 实体名 isfor 选择的构造体名end for;end 配置名;此语句可以为设计增加更大的灵活性,可以对不同构造体进行比较。

2.3 VHDL对象、数据类型及运算符

VHDL对象:变量

例: Architecture behav of count is begin

process (clk) variable temp: integer range o to 255 := ‘0’; begin

if clk’event and clk=’1’ then temp := temp + 1;

例Hale Waihona Puke :architecture behav of counter is signal count: std_logic_vector (7 downto 0);

begin process (clk) begin if (clk’event and clk=’1’) then if en = ‘1’ then count <= data; else count <= count +1; end if; end if; end process; q<=count;

end if; end process; end behav;

-- 请写出对应的实体说明

VHDL对象:变量

变量:定义进程中或子程序中的变化量

格式: VARIABLE 变量名:数据类型 := 初始值;

例:variable tmp : std_logic := ‘0’;

用途:在PROCESS,FUNCTION,ROCEDURE 中使用,用于描述算法和方便程序中的数值运 算,是一种局部量。

例: constant VCC : real := 5.0; constant delay : time := 10ns; constant fbus : bit_vector := “0101”;

用途:在ENTITY,ARCHITECTURE,PACKAGE, PROCESS,PROCEDURE,FUNCTION中保持静态数据, 以改善程序的可读性,并使修改程序容易。

VHDL基本语法

变量不是真正的物理量 , 因此不能 出现在敏感信号表中. 出现在敏感信号表中. 在 process 语句中只作为输出存在的 信号 ( 出现在信号赋值符 " < =" 的左 边 ) 不能作为敏感信 号. 既出现在信号赋值符 "<=" 的左边 , 又出现在信号赋值符 "<=" 右边的信 号 , 可以出现在敏感信号表中 , 这是因 为这些信号既作为这块电路的输出 , 又 是电路内部的反馈信号. 是电路内部的反馈信号.

例7 2 与非门. 与非门. 参见程序' (参见程序'例7') ) 说明: 说明: 本例中 , 首先将与非门输入信号 a 和 b 并置 , 生成一个 2 位的 std_logic_vector 信号 sel .信号 C 是与非门的输出. 是与非门的输出.第一个 when 中的 "|" 代表或者 , 即 3 个条件中的任何一 语句. 个满足 , 执行 C <='1' 语句.

格式 : IF 条件 1 THEN 若干顺序执行语句 1 ELSIF 条件 2 THEN 若干顺序执行语句 2 … ELSIF 条件 n-1 THEN 若干顺序执行语句 n-1 ELSE 若干顺序执行语句 n END IF;

(5) 进程语句 进程语句(PROCESS)

进程语句是一个十分重要的语句 进程语句是一个十分重要的语句 , 本质上它描述了一个功能独立的电路 本质上它描述了一个功能独立的电路 块.

CASE语句与 语句一样也是个顺序执 语句与IF语句一样也是个顺序执 语句与 行语句,但使用上有区别. 行语句,但使用上有区别. CASE语句执行时是无序的,所有表达 语句执行时是无序的, 语句执行时是无序的 式是并行处理; 语句是有序的, 式是并行处理;而IF语句是有序的, 语句是有序的 先处理最优先的条件, 先处理最优先的条件,后处理次优先 条件. 条件. 在某种情况下,两种语句都可以使用, 在某种情况下,两种语句都可以使用, 语句比IF语句描述更简捷 但 CASE语句比 语句描述更简捷, 语句比 语句描述更简捷, 更清晰.故应优先选用CASE语句. 语句. 更清晰.故应优先选用 语句

VHDL数据类型和运算符

-(2^31-1) to +(2^31-1) -1.0E+38 to +1.0E+38 ‘0’ ‘1’ “000” true false ‘A’ “abcd” 20 us

2011/6/13

11

VHDL语言的数据类型

整数

整数范围 -(2^31-1) to +(2^31-1)

不能看作矢量, 不能单独对某一位操作

2011/6/13

22

用户定义的数据类型

TYPE 数据类型名 IS 数据类型定义;

枚举类型 数组 记录类型 文件 时间 用户自定义的整数,实数 用户自定义的子类型

2011/6/13

23

用户定义的数据类型

枚举类型

TYPE 数据类型名 IS (元素,元素…..)

Type week IS (sun,mon,tue,wed,thu,fri,sat) Type std_logic IS (‘U’, ‘X’, ‘0’, ‘1’, ‘Z’, ‘W’, ‘L’ ,‘H’, ‘-’) Type bit IS (‘0’, ‘1’)

转换为integer

31

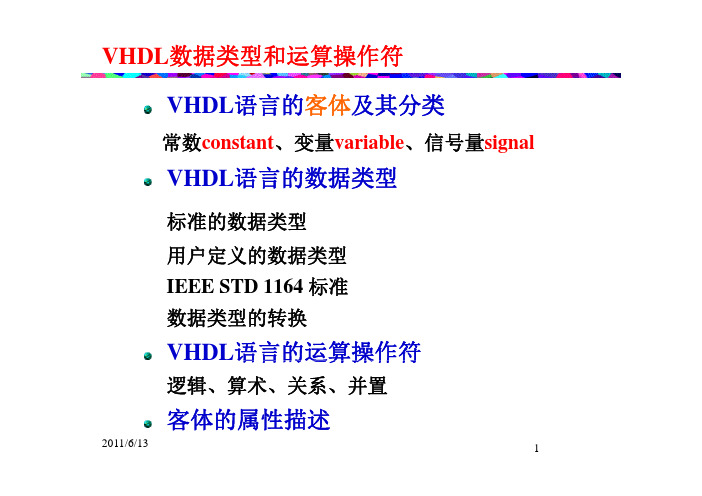

VHDL语言的客体及其分类

常数constant、变量variable、信号量signal

VHDL语言的数据类型

标准的数据类型

用户定义的数据类型

IEEE STD 1164 标准 数据类型的转换

VHDL语言的运算操作符

逻辑、算术、关系、并置

客体的属性描述

2011/6/13

32

(信号的代入)

Signal B : Std_logic; (信号的定义)

B <= ‘Z’;

(信号的代入)

B <= A(0);

第三章VHDL语言数据类型及运算操作符

实数常量的书写方式举例

65971.333333

--十进制浮点数

8#43.6E+4#

--八进制浮点数

43.6E-4

--十进制浮点数

第三章VHDL语言数据类型及运算操作符

3、位(BIT)数据类型

位数据类型也属于枚举型,取值只能是1 或0。位数据类型的数据对象,如变量、信 号等,可以参与逻辑运算,运算结果仍是 位的数据类型。VHDL综合器用一个二进制 位表示BIT。在程序包STANDARD中定义 的源代码是:

第三章VHDL语言数据类型及运算操作符

总结:

在运行中不变,若要改变必须要改变设计, 也就是说改变常量说明,重新编译。

常量必须在程序的实体、结构体或过程的 说明区中,对其标识符类型常量值进行指 定。

定义在实体中的常量仅在实体中使用。以 此类推。

第三章VHDL语言数据类型及运算操作符

3.1.2变量(Variable)

线)信号,共有16个信号元素

第三章VHDL语言数据类型及运算操作符

以下示例定义的信号数据类型是设计者自 行定义的,这是VHDL所允许的:

TYPE FOUR IS(‘X’,‘0’,‘I’, ‘Z’);

SIGNAL S1﹕FOUR; SIGNAL S2﹕FOUR:=‘X’; SIGNAL S3﹕FOUR:=‘L’;

第三章VHDL语言数据类型及运算操作符

格式: CONSTANT 常数名:数据类型:=表达式; 例: CONSTANT VCC: REAL:=5.0; CONSTANT DALY:TIME:=100ns; CONSTANT BUS:BIT_VECTOR:=“1010 ” CONSTANT G1:BIT:= ‘ 1’; 数据类型和表达式表示的数据类型应该一致。 ‘ ’表示是位信息, 而 “ ”表示的是位矢量

VHDL的运算符号

VHDL的运算符号VHDL的运算符号VHDL中主要有六类运算符号:赋值运算、逻辑运算、算术运算关系运算、连接运算、移位运算运算符号主要用于各类表达式中;运算可以分为单目运算(只有一个运算量)和双目运算(针对两个运算量);进行双目运算时,两个运算量必须类型相同;VHDL中运算没有左右优先级差别,同一表达式中进行多个运算时必须用括号表达先后差别;在同类运算中,单目运算优先;在所有运算符号中,NOT的优先级别最高;在一般运算中,优先顺序排列为:算术—关系—逻辑可以通过加括号来改变运算的优先顺序;赋值运算符<= 信号赋值:将右端值赋给左端信号;:= 变量赋值:将右端值赋给左端变量;或用于赋初始值;=> 数组内部分元素赋值;适用类型:所有数据类型;赋值号两边的数据类型原则上应该相同;逻辑运算符NOT AND OR NAND NOR XOR适用类型:STD_LOGIC STD_LOGIC_VECTORBIT BIT_VECTOR BOOLEAN逻辑运算结果为同类型逻辑量;对数组类型进行逻辑运算时,参与运算的两个数据位数必须相等,所做运算为对应位进行;算术运算:/ (除)* (乘) + (加)- (减)MOD(求模)REM(取余)**(指数)ABS(绝对值)适用类型:INTEGER REAL BIT BIT_VECTOR TIME加/减运算的结果为同类型算术量;注意:算术运算大多数只用于抽象的编程(行为设计);只有少数算术运算符能够进行综合,应尽量只使用加/减;对数组类型进行算术运算时,两边位数必须相同;关系运算:=> (大于等于)<= (小于等于)> (大于)< (小于) /= (不等于)= (等于)适用类型:等于和不等于适用于所有类型;其他运算适用于整数、实数、位、位矢量,以及枚举类型和数组类型;可比较位长度不相同的情况(从左向右逐位比较);关系运算的结果为boolean类型: false true注意:小于等于符号与信号赋值符号的写法相同,应注意使用位置和意义;连接运算:&适用类型bit bitvector character stringstd_logic std_logic_vector连接运算结果为同类型元素构成的数组;库和包集合除了实体、结构体外的第三种可编程结构Library 库编译后数据的集合,存放包集合定义、实体定义、构造体定义和配置定义,其功能相当于其他操作系统中的目录,经过说明后,设计中就可以使用库中的数据,实现共享;在前面图形输入的应用中,已多次采用库中的单元进行设计;库的使用:当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及范围;每个实体都应独立进行库的说明;库的说明应该在实体之前;经过说明后,实体和结构体就可以自动调用库中的资源;库说明语句格式library 库名;use 库名.包集合名.范围(或项目名);例: library ieee;use ieee.std_logic_1164.all;VHDL中库的主要种类:IEEE库STD库ASIC库work库用户定义库IEEE库:含有IEEE的标准包集合“STD_LOGIC_1164”以及一些大公司提供的包集合;使用前必须说明;例:library ieee;use ieee.std_logic_1164.all; 使用标准逻辑量的定义和运算;use ieee.std_logic_unsigned.all; 无符号数算术运算的定义;use ieee.std_logic_arith.all; 使用符号数算术运算的定义;STD库:含有“STANDARD”包集合和“TEXTIO”包集合,使用前者时无需说明;ASIC库:由各公司提供,存放与逻辑门一一对应的实体,用于ASIC 设计的门级仿真,使用时需加以说明;例library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;WORK库:WORK库为现行作业库,位于当前使用时设计文件的指定保存目录;WORK使用时通常无须说明;但在结构设计中进行元件的宏调用时需要说明;例:use work.all;用户定义库:由用户自定义生成,使用时需说明(指定库所在的路径);package 包集合用于罗列VHDL语言中使用的类型定义、信号定义、常数定义、元件定义、函数定义和过程定义等(类似于C语言中的include语句),方便不同模块的设计中公共定义的共享;数字电路设计中经常使用的包集合:ieee.std_logic_1164 逻辑量的定义ieee.std_logic_arith 数据转换,逻辑判断ieee.std_logic_unsigned 算术运算std.textio 文本数据输入/输出格式包集合在使用前必须采用use语句进行说明(在设计程序的最前面);包集合可以由用户自定义;包的结构与定义:(用户自定义的包集合)包集合标题+(包集合体)包集合标题:package 包集合名 is说明语句;(只有名称)end 包集合名;包集合体:package body包集合名 is说明语句;(完整定义)end 包集合名;例:(函数取自p.279 表4-38 )library ieee;use ieee.std_logic_1164.all;packge upac isconstant k: integer := 4;subtype cpu_bus is std_logic_vector(k-1downto 0); function conv_integer (x:std_logic_vector) return integer; end upac;packge body upac isfunction conv_integer (x: std_logic_vector) return integer is variable result: integer;beginresult := 0;for I in x'range loopresult :=result*2;case x(i) iswhen '0'|'L' => null;when '1'|'H' => result := result+1;when others => null;end case;end loop;return result;end conv_integer;end upac;用户自行编写的包集合将自动存放于WORK库中,使用时可采用下列语句调用use work.upac.all;configuration 配置在一个实体内可以编写多种不同的构造体,通过配置语句来进行选择;配置语句格式:configuration 配置名 of 实体名 isfor 选择的构造体名end for;end 配置名;此语句可以为设计增加更大的灵活性,可以对不同构造体进行比较。

EDA VHDL第三章 VHDL数据类型和运算操作符

illegal%name _illegalname 9illegal entity data_ _BUS Not-Ack

上一次课的内容

程序包、库和配置 VHDL四类语言要素:数据对象、词法规则与 标识符 本次课程内容:

数据类型、 运算操作符

扩展标识符

扩展标识符是VHDL‟93版增加的标识符书写规则: (1)用反斜杠来定界,免去了87标准基本标识符的一些限制。 (2) 可以数字打头,允许包含图形符号、空格符。 例如:\mode A, \$100\, \p%name\等。 (3)反斜杠之间的字符可以用关健字。 如:\buffer\, \entity\, \end\等。 (4) 标识符的界定符两个斜杠之间可用数字打头。 如: \100$\,\2chip\,\4screens\等。 (5) 允许多个下划线相连。例:\TWO_Computer_sh\等。 (6) 扩展标识符区分大小写。例如: \EDA\ 与\eda\不同。 (7) 扩展标识符与短标识符不同。 如:\COMPUTER\ 与Computer不同。

3.3.2 词法规则与标识符

1.词法规则 1) 注释 以--开头直到本行末尾(出现回 车或换行符)的文字

提高VHDL语言设计程序的可读性,

1.词法规则

2) 数字

表达方式:十进制,二进制、八进 制、十六进制等为基的数 ①十进制整数表示法 78_567(=78567) ②以基表示的数 格式: 基数符号#数值#指数部分

举例如下: VARIABLE result: std_logic:='0' ; VARIABLE x,y: integer; VARIABLE a:integer range 0 to 255 :=0 ;

VHDL的操作符号

3.重载操作符 . 为了方便各种不同数据类型间的运算, 为了方便各种不同数据类型间的运算 , VHDL允许用户对原有的基本操作符重新 允许用户对原有的基本操作符重新 定义, 赋予新的含义和功能, 定义 , 赋予新的含义和功能 , 从而建立一 种新的操作符, 这就是重载操作符, 种新的操作符 , 这就是重载操作符 , 定义 这种操作符的函数称为重载函数。 事实上, 这种操作符的函数称为重载函数 。 事实上 , 在程序包STD_LOGIC_UNSIGNED中已定 在程序包 中已定 义了多种可供不同数据类型间操作的算符 重载函数。 重载函数。

预定义的属性函数功能表

综合器支持的属性有: LEFT、RIGHT、HIGH、LOW、RANGE、REVERSE_RANGE、 LEFT、RIGHT、HIGH、LOW、RANGE、REVERSE_RANGE、 LENGTH、EVENT及STABLE。 LENGTH、EVENT及STABLE。

1) 信号类属性

CLOCK'EVENT AND CLOCK=‘1’ 是对CLOCK信号上升沿的测试。即一旦测试 信号上升沿的测试。 是对 信号上升沿的测试 有一个上升沿时, 到CLOCK有一个上升沿时,此表达式将返回一个布 有一个上升沿时 尔值TRUE。 。 尔值 CLOCK'EVE数据区间类属性 例:...

SIGNAL y1 : IN STD LOGIC VECTOR (0 TO 7) ; ... FOR i IN y1'RANGE LOOP ...

4) 用户定义属性 ATTRIBUTE 属性名 : 数据类型 数据类型; ATTRIBUTE 属性名 OF 对象名 : 对象类型 值; 对象类型IS

四、VHDL语言的操作符 VHDL语言的操作符 VHDL的各种表达式由操作数和操作符 的各种表达式由操作数和操作符 组成,其中,操作数是各种运算的对象, 组成,其中,操作数是各种运算的对象,而操 作符则规定运算的方式。 作符则规定运算的方式。 1.操作符种类及对应的操作数类型 .

VHDL对象数据及运算符

优先级 最高优先级

最低优先级

5.3.1 逻辑操作 符

【例5-4】

SIGNAL a ,b,c : STD_LOGIC_VECTOR (3 DOWNTO 0) ;

SIGNAL d,e,f,g : STD_LOGIC_VECTOR (1 DOWNTO 0) ;

SIGNAL h,I,j,k : STD_LOGIC ;

表5-1 VHDL操作符列表

功能

操作数数据类型

加

整数

减

整数

并置

一维数组

乘

整数和实数(包括浮点数)

除

整数和实数(包括浮点数)

取模

整数

取余

整数

逻辑左移

BIT 或布尔型一维数组

逻辑右移

BIT 或布尔型一维数组

算术左移

BIT 或布尔型一维数组

算术右移

BIT 或布尔型一维数组

逻辑循环左移 BIT 或布尔型一维数组

-- 秒

min = 60 sec ;

-- 分

hr = 60 min ;

-- 时

5.2 数据类型

5.2.2 IEEE预定义标准逻辑位与矢量 1. 标准逻辑位STD_LOGIC数据类型 2. 标准逻辑矢量(STD_LOGIC_VECTOR)数据类型

5.2 数据类型

5.2.3 其他预定义数据类型 1. 无符号数据类型(UNSIGNED TYPE)

END relational_ops_1 ;

“ = ”(等于)、

ARCHITECTURE example OF relational_ops_1 IS BEGIN

“/=”(不等于)、

output <= (a = b) ; END example ;

第10讲 VHDL的运算符1

本讲知识点: 算术运算符

逻辑运算符

运算符

VHale Waihona Puke DL中共有四类操作符:逻辑操作符、关系操作符、算术操作符和连接操 作符

操作符和操作数间的运算应注意: o 基本操作符间操作数是同数据类型 o 操作数的数据类型必须与操作符所要求的数据类 型一致

o

注意操作符之间的优先级

o 通常在一个表达式中有两个以上的算符时,需 要使用括号将这些运算分组,若其中的算符相同且 为AND、OR、XOR 中的一种则不需使用括号。

2、算术运算符 VHDL的算术运算符共有十几种,其中常用的有如下 几种: 操作符 功能 操作数类型 + 加法 整数 - 减法 整数 * 乘法 整数和实数 SLL等 移位 bit或布尔类型的 一维数组 (SLL SLR SLA SRA ROL ROR)

在运用算术运算符对如下的数据类型进行运算 时,应注意: (1)unsigned, signed:需打开 std_logic_arith程序包; (2)std_logic:需打开std_logic_unsigned 或std_logic_signed 程序包;

5. 移位操作符

1. 求和操作符

2. 求积操作符

*(乘)、 /(除)、 MOD(取模) 、 RED(取余)

3. 符号操作符

maxplus2不支持“MOD”、“RED”运算

“+”和“-”

4. 混合操作符

“**” “ABS”

5. 移位操作符

SLL、SRL、SLA、SRA、ROL 、ROR 移位操作符的语句格式是: 标识符 移位操作符 移位位数 ; 要求操作数的数据类型必须为1维数组,元素必须为 bit或BOOLEAN类型;操作符右边必须为整形。 逻辑左移和右移:移空的位用0填补; 逻辑左、右环移:数据内环行移动。 算术左、右移:其移空的为用最初的首位填补。

VHDL 操作符

EDA技术实用教程

VHDL操作符

1.3 算术操作符

2. 求积操作符

* (乘)、 / (除)、 MOD (取模) 、RED (取余)

3. 符号操作符

“ + ”、“ - ”

VHDL操作符

1.3 算术操作符

4. 混合操作符

“ ** ”、“ ABS ”

【例8-22】 SIGNAL a,b : INTEGER RANGE -8 to 7 ; SIGNAL c : INTEGER RANGE 0 to 15 ; SIGNAL d : INTEGER RANGE 0 to 3 ; a <= ABS(b) ;

严格遵循在基本操作符间操作数是同数据类型的规则。 严格遵循操作数的数据类型必须与操作符所要求的数据类 型完全一致。

类型 算术操作符

操作符 + - & * / MOD REM SLL SRL SLA SRA ROL ROR ** ABS

表8-1 VHDL操作符列表

功能

操作数数据类型

加整数Βιβλιοθήκη 减整数并置

一维数组

port ( input: IN STD_LOGIC_VECTOR (2 DOWNTO 0); output: OUT BIT_VECTOR (7 DOWNTO 0));

END decoder3to8; ARCHITECTURE behave OF decoder3to8 IS BEGIN output <= "00000001" SLL CONV_INTEGER(input); --被移位部分是常数! END behave;

SIGNAL l,m,n,o,p : BOOLEAN ;

...

vhdl中所使用的运算符

VHDL中所使用的运算符表2 关系运算符表3 数值移位运算符表4 逻辑运算符假设A、B为输入,Z为输出表5 算数运算符表6 其他运算符B 添加义项?文案,原指放书的桌子,后来指在桌子上写字的人。

现在指的是公司或企业中从事文字工作的职位,就是以文字来表现已经制定的创意策略。

文案它不同于设计师用画面或其他手段的表现手法,它是一个与广告创意先后相继的表现的过程、发展的过程、深化的过程,多存在于广告公司,企业宣传,新闻策划等。

基本信息中文名称文案外文名称Copy目录1发展历程2主要工作3分类构成4基本要求5工作范围6文案写法7实际应用折叠编辑本段发展历程汉字"文案"(wén àn)是指古代官衙中掌管档案、负责起草文书的幕友,亦指官署中的公文、书信等;在现代,文案的称呼主要用在商业领域,其意义与中国古代所说的文案是有区别的。

在中国古代,文案亦作" 文按"。

公文案卷。

《北堂书钞》卷六八引《汉杂事》:"先是公府掾多不视事,但以文案为务。

"《晋书·桓温传》:"机务不可停废,常行文按宜为限日。

" 唐戴叔伦《答崔载华》诗:"文案日成堆,愁眉拽不开。

"《资治通鉴·晋孝武帝太元十四年》:"诸曹皆得良吏以掌文按。

"《花月痕》第五一回:" 荷生觉得自己是替他掌文案。

"旧时衙门里草拟文牍、掌管档案的幕僚,其地位比一般属吏高。

《老残游记》第四回:"像你老这样抚台央出文案老爷来请进去谈谈,这面子有多大!"夏衍《秋瑾传》序幕:"将这阮财富带回衙门去,要文案给他补一份状子。

"文案音译文案英文:copywriter、copy、copywriting文案拼音:wén àn现代文案的概念:文案来源于广告行业,是"广告文案"的简称,由copy writer翻译而来。

VHDL的运算符号解析

VHDL的运算符号VHDL中主要有六类运算符号:赋值运算、逻辑运算、算术运算关系运算、连接运算、移位运算运算符号主要用于各类表达式中;运算可以分为单目运算(只有一个运算量)和双目运算(针对两个运算量);进行双目运算时,两个运算量必须类型相同;VHDL中运算没有左右优先级差别,同一表达式中进行多个运算时必须用括号表达先后差别;在同类运算中,单目运算优先;在所有运算符号中,NOT的优先级别最高;在一般运算中,优先顺序排列为:算术—关系—逻辑可以通过加括号来改变运算的优先顺序;赋值运算符<= 信号赋值:将右端值赋给左端信号;:= 变量赋值:将右端值赋给左端变量;或用于赋初始值;=> 数组内部分元素赋值;适用类型:所有数据类型;赋值号两边的数据类型原则上应该相同;逻辑运算符NOT AND OR NAND NOR XOR适用类型:STD_LOGIC STD_LOGIC_VECTORBIT BIT_VECTOR BOOLEAN逻辑运算结果为同类型逻辑量;对数组类型进行逻辑运算时,参与运算的两个数据位数必须相等,所做运算为对应位进行;算术运算:/ (除)* (乘) + (加)- (减)MOD(求模)REM(取余)**(指数) ABS(绝对值)适用类型:INTEGER REAL BIT BIT_VECTOR TIME加/减运算的结果为同类型算术量;注意:算术运算大多数只用于抽象的编程(行为设计);只有少数算术运算符能够进行综合,应尽量只使用加/减;对数组类型进行算术运算时,两边位数必须相同;关系运算:=> (大于等于)<= (小于等于)> (大于)< (小于) /= (不等于)= (等于)适用类型:等于和不等于适用于所有类型;其他运算适用于整数、实数、位、位矢量,以及枚举类型和数组类型;可比较位长度不相同的情况(从左向右逐位比较);关系运算的结果为boolean类型: false true注意:小于等于符号与信号赋值符号的写法相同,应注意使用位置和意义;连接运算:&适用类型bit bitvector character stringstd_logic std_logic_vector连接运算结果为同类型元素构成的数组;库和包集合除了实体、结构体外的第三种可编程结构Library 库编译后数据的集合,存放包集合定义、实体定义、构造体定义和配置定义,其功能相当于其他操作系统中的目录,经过说明后,设计中就可以使用库中的数据,实现共享;在前面图形输入的应用中,已多次采用库中的单元进行设计;库的使用:当使用库时,需要说明使用的库名称,同时需要说明库中包集合的名称及范围;每个实体都应独立进行库的说明;库的说明应该在实体之前;经过说明后,实体和结构体就可以自动调用库中的资源;库说明语句格式library 库名;use 库名.包集合名.范围(或项目名);例: library ieee;use ieee.std_logic_1164.all;VHDL中库的主要种类:IEEE库STD库ASIC库work库用户定义库IEEE库:含有IEEE的标准包集合“STD_LOGIC_1164”以及一些大公司提供的包集合;使用前必须说明;例:library ieee;use ieee.std_logic_1164.all; 使用标准逻辑量的定义和运算;use ieee.std_logic_unsigned.all; 无符号数算术运算的定义;use ieee.std_logic_arith.all; 使用符号数算术运算的定义;STD库:含有“STANDARD”包集合和“TEXTIO”包集合,使用前者时无需说明;ASIC库:由各公司提供,存放与逻辑门一一对应的实体,用于ASIC 设计的门级仿真,使用时需加以说明;例library altera;use altera.maxplus2.all;library lpm;use lpm.lpm_components.all;WORK库:WORK库为现行作业库,位于当前使用时设计文件的指定保存目录;WORK使用时通常无须说明;但在结构设计中进行元件的宏调用时需要说明;例:use work.all;用户定义库:由用户自定义生成,使用时需说明(指定库所在的路径);package 包集合用于罗列VHDL语言中使用的类型定义、信号定义、常数定义、元件定义、函数定义和过程定义等(类似于C语言中的include语句),方便不同模块的设计中公共定义的共享;数字电路设计中经常使用的包集合:ieee.std_logic_1164 逻辑量的定义ieee.std_logic_arith 数据转换,逻辑判断ieee.std_logic_unsigned 算术运算std.textio 文本数据输入/输出格式包集合在使用前必须采用use语句进行说明(在设计程序的最前面);包集合可以由用户自定义;包的结构与定义:(用户自定义的包集合)包集合标题+(包集合体)包集合标题:package 包集合名 is说明语句;(只有名称)end 包集合名;包集合体:package body包集合名 is说明语句;(完整定义)end 包集合名;例:(函数取自p.279 表4-38 )library ieee;use ieee.std_logic_1164.all;packge upac isconstant k: integer := 4;subtype cpu_bus is std_logic_vector(k-1downto 0); function conv_integer (x:std_logic_vector) return integer; end upac;packge body upac isfunction conv_integer (x: std_logic_vector) return integer is variable result: integer;beginresult := 0;for I in x'range loopresult :=result*2;case x(i) iswhen '0'|'L' => null;when '1'|'H' => result := result+1;when others => null;end case;end loop;return result;end conv_integer;end upac;用户自行编写的包集合将自动存放于WORK库中,使用时可采用下列语句调用use work.upac.all;configuration 配置在一个实体内可以编写多种不同的构造体,通过配置语句来进行选择;配置语句格式:configuration 配置名 of 实体名 isfor 选择的构造体名end for;end 配置名;此语句可以为设计增加更大的灵活性,可以对不同构造体进行比较。

第三章 VHDL语言的数据类型及运算操作符_1

进程中的信号与变量赋值语句

【例1】 】 SIGNAL in1,in2,e1, ... : STD_LOGIC ; , , , ... PROCESS(in1,in2, . . .) ( , , ) VARIABLE c1,. . . : STD_LOGIC_VECTOR(3 DOWNTO 0) ; , BEGIN IF in1 = '1' THEN ... –- 第 1 行 e1 <= "1010" ; –- 第 2 行 ... IF in2 = '0' THEN . . . –- 第 15+n 行 ... c1 := "0011" ; –- 第 30+m 行 ... END IF; END PROCESS;

1.0 0.0 65971.333333 65_971.333_3333 8#43.6#e+4 43.6E-4 十进制浮点数 十进制浮点数 十进制浮点数 与上一行等价 八进制浮点数 十进制浮点数

VHDL语言的数据类型 语言的数据类型

BIT)数据类型 3. 位(BIT)数据类型 位数据类型属于枚举型,取值只能中‘ 位数据类型属于枚举型,取值只能中‘1’可‘0’(用单 引号括起来)。在包集合STANDARD中定义的源代码是: )。在包集合STANDARD中定义的源代码是 引号括起来)。在包集合STANDARD中定义的源代码是: IS( 0 , 1 ); TYPE BIT IS(’0’,’1’); 4. 位矢量(BIT_VECTOR)数据类型 位矢量(BIT_VECTOR)数据类型 位矢量是基于BIT数据类型的数组, BIT数据类型的数组 位矢量是基于BIT数据类型的数组,使用位矢量时必须注 明位宽,例如: 明位宽,例如: BIT_VECTOR( SIGNAL A:BIT_VECTOR(7 TO 0); 5. 布尔(BOOLEAN)数据类型 布尔(BOOLEAN)数据类型 布尔数据类型属于枚举型,取值只能中‘ 可 布尔数据类型属于枚举型,取值只能中‘真’可‘假’ 在包集合STANDARD中定义的源代码是: STANDARD中定义的源代码是 。在包集合STANDARD中定义的源代码是: IS(FALSE,TRUE); TYPE BOOLEAN IS(FALSE,TRUE);

第三章VHDL语言的数据类型及运算操作符

例3-1: PROCESS(A,B,C,D) BEGIN D<=A; X<=B+D; D<=C; Y<=B; 结果:X<=B+C; END PROCESS

例3-2: PROCESS(A,B,C) VARIABLE D:STD_LOGIC_VECTOR(3DOWNTO 0) BEGIN D:=A; X:=B+D; D:=C; Y:=B; END PROCESS

3、位(BIT)数据类型

位数据类型也属于枚举型,取值只能是1 或0。位数据类型的数据对象,如变量、信 号等,可以参与逻辑运算,运算结果仍是 位的数据类型。VHDL综合器用一个二进制 位表示BIT。在程序包STANDARD中定义 的源代码是: TYPE BIT IS (‘0’,‘1’);

4、位矢量(BIT_VECTOR)数据类型

常量定义语句所允许的设计单元有实体、结构 体、程序包、块、进程和子程序。在程序包中定 义的常量可以暂不设具体数值,它可以在程序包 体中设定。 常量的可视性,即常量的使用范围取决于它被 定义的位置。在程序包中定义的常量具有最大全 局化特征,可以用在调用此程序包的所有设计实 体中;定义在设计实体中的常量,其有效范围为 这个实体定义的所有的结构体;定义在设计实体 的某一结构体中的常量,则只能用于此结构体; 定义在结构体的某一单元的常量,如一个进程中, 则这个常量只能用在这一进程中。

总结:

在运行中不变,若要改变必须要改变设计, 也就是说改变常量说明,重新编译。 常量必须在程序的实体、结构体或过程的 说明区中,对其标识符类型常量值进行指 定。 定义在实体中的常量仅在实体中使用。以 此类推。

3.1.2变量(Variable)

第七章第三部分VHDL语言的数据类型和运算操作符号

2) 位(BIT)数据类型

位数据类型也属于枚举型,取值只 能是1或0。位数据类型的数据对象,如 变量、信号等,可以参与逻辑运算,运 算结果仍是位的数据类型。VHDL综合器 用一个二进制位表示BIT。在程序包 STANDARD中定义的源代码是:

10) 错误等级(SEVERITY_LEVEL)

在VHDL仿真器中,错误等级用来指示设计系统的工作状态, 共有四种可能的状态值:NOTE(注意)、WARNING(警告)、 ERROR(出错)、FAILURE(失败)。在仿真过程中,可输出这四种 值来提示被仿真系统当前的工作情况。其定义如下:

3.2.1、 VHDL的预定义数据类型

1) 布尔(BOOLEAN)数据类型 程序包STANDARD中定义布尔数据类型的源代码如下:

TYPE BOOLEAN IS(FALES,TRUE); 布尔数据类型实际上是一个二值枚举型数据

类型,它的取值有FALSE和TRUE两种。综合器将用 一个二进制位表示BOOLEAN型变量或信号。

3、从综合后所对应的硬件电路结构来看,信 号一般将对应更多的硬件结构,但在许多情况 下,信号和变量并没有什么区别。例如在满足 一定条件的进程中,综合后它们都能引入寄存 器。这时它们都具有能够接受赋值这一重要的 共性,而VHDL综合器并不理会它们在接受赋 值时存在的延时特性。

4、虽然VHDL仿真器允许变量和信号设置初 始值,但在实际应用中,VHDL综合器并不会 把这些信息综合进去。这是因为实际的 FPGA/CPLD芯片在上电后,并不能确保其初 始状态的取向。因此,对于时序仿真来说,设 置的初始值在综合时是没有实际意义的。

(三)VHDL语言的数据类型及运算操作符090914(119)

5. 布尔量(Boolean)

一个布尔量具有两种状态,“真”或者“假”。虽然布尔量也是 二值枚举量,但它和位不同,没有数值的含义,也不能进行算术 运算。它能进行关系运算。例如,它可以在IF语句中被测试,测 试结果产生一个布尔量TRUE或者FALSE。 一个布尔量常用来表示信号的状态或者总线上的情况。如果 某个信号或者变量被定义为布尔量,那么在仿真中将自动地对其 赋值进行核查。这一类型的数据的初始值一般总为FALSE。

【例3-1-b】

PROCESS( A, B, C)

VARIABLE D:STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

D:=A; X<=B+D;

结果:X<=B+A; Y<=B+C;

D:=C;

Y<=B+D;

END PROCESS;

进程内的语句是顺序执行的, 由于D是变量,在执行 D:=A后,D=A,接着执行X<=B+D,使得在退出进程后 X=B+A 。接着执行D:=C 和 Y<=B+D ,使D=C,退出时, Y=B+C。

信号赋值语句举例: X<= y; a <= ‘1’; s1 <= s2 AFTER 10 ns;

3.1.4 信号和变量的主要区别

1) 赋值符不同 信号和变量的赋值符不同,如果一个值要赋给信号应用

代入符“<=”;而变量赋值则用赋值符“:=”。

信号和变量可以互相赋值,此时赋值符应根据左边被赋 值量的类型来确定。如果被赋值是信号应用代入符“<=”;如 果是变量,则应用赋值符“:=”。

例如: CONSTANT VCC: REAL:=5.0; CONSTANT DALY: TIME:=100 ns; CONSTANT FBUS: BIT_VECTOR:="0101";

第11讲VHDL的运算符2

在指定位的脚标时,也可以用“OTHERS”来说明: tmp_b<=(OTHERS=>en);

要注意,在集合体中“OTHERS”只能放在最后。假若b 位矢量的脚标b(2)的选择信号为“0”,其他位的选择信号 均为en。那么此时表达式可写为

tmp_b<=(2=>'0',OTHERS=>en);

第11讲 VHDL的运算符2

本讲知识点: 关系运算符 并置运算符

3、关系运算符: 操作符 功能 操作数类型

= 等于 任何数据类型 /= 不等于 任何数据类型 < 小于 integer、real、 bit、 std_logic等及其一维向量 <= 小于等于 integer、real、 bit、 std_logic等及其一维向量 > 大于 integer、real、 bit、 std_logic等及其一维向量 >= 大于等于 integer、real、 bit、 std_logic等及其一维向量

P92 例4-11 注意:操作数必须有相同的类型。

VHDL运算符的优先级

运算符

优先级

not

高

*

+(正号) -(负号)

- -

+(加号) -(减号) &amL SLA SRA ROL ROR

- -

= /= < > <= >=

and or nand nor xor xnor 低

注意:

(1)关系运算符运算的最后结果总是布尔类型 (2)关系运算符两边的数据类型必须相同,但 是位的长度不一定相同。 (3)对位矢量数据进行比较时,比较从最左边 的位开始,自左至右进行比较的。在位长不同的 情况下,只能按自左至右的比较结果作为关系运 算的结果。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

整数相除取商

-

取2的补码

ABS

取绝对值

VHDL中所使用的运算符

表1设定运算符

信号的设定

<=

变量的设定

=

表2关系运算符

等于

=

大于

>

小于

<

不等于

/=

大于等于

>=

小于等于

<=

表3数值移位运算符

ROL

循环左移(原MSB移入LSB)

ROR

循环右移(原LSB移入MSB)

SLL

逻辑左移(0移入LSB)

SRL

逻辑右移(0移入MSB)

SLA

算数左移(原LSB保留)

SRA

算数右移(原MSB保留)

表4逻辑运算符

假设A、B为输入,Z为输出

AND

与

OR

或

NOT

非

NAND

与非

NOR

或非

XOR

异或

XNOR

同或

表5算数运算符

+加

A+ B

-减A - B来自*乘A.B/除

A/B

**次方

AB

-批注

Example

:声明使用

=>对应

&串接

Z <= A&B

表6其他运算符

REM

整数相除取余数