CPLD单片机定时器音乐播放器

毕业设计(论文)-基于单片机控制的音乐播放器[管理资料]

![毕业设计(论文)-基于单片机控制的音乐播放器[管理资料]](https://img.taocdn.com/s3/m/c2ce389c58fafab068dc02c7.png)

单片机音乐播放器设计报告学生:XXX 指导教师:XXX内容摘要:单片机具有体积小、功能强、成本低、应用面广等优点,可以说,智能控制与自动控制的核心就是单片机。

根据要求设计一款音乐播放器,能实现音乐播放的简单功能,同时为了美化,添加了韵律闪烁彩灯,设计时采用Keil软件编程,用protues软件仿真,核心器件采用灵活性高且价格低廉的AT89C51芯片。

设计完成后系统可播放自编歌曲,同时发光二极管随着歌曲韵律闪烁。

关键词:单片机 AT89C51 音乐播放英文标题Abstract: SCM has small, strong function, low cost, application, advantages and intelligent control and automatic control of the core is the microcontroller. According to the requirements of a music player, design of music broadcast can realize simple function, and to beautify, added rhythm flashing lights, design is used when Keil C software programming, with protues software simulation, the core device adopts high flexibility and the price is cheap AT89C51 chip. The design is completed system can play Wrote songs, and leds with songs rhythm flicker.Keywords:SCM Temperature AT89C51 Music broadcast前言:微机原理和接口技术是一门实践性强的学科,不但要求有较高的理论水平,而且还要求有实际的动手能力,其中很多的原量、规则、现象等仅仅靠学习教科书是无法完全掌握的,必须通过实践才能比较直观和深刻的理解。

音乐播放器-单片机课程设计

设计内容与设计要求设计内容:本课题要求以单片机为核心设计一个音乐播放器,完成多曲选择播放控制、停止控制、省电模式控制等功能。

音乐播放器利用单片机的定时器产生乐谱的各种频率方波,信号经过放大后由喇叭发出声音,选取某段音乐使单片机连续播放。

设计3个按键:播放/停止、下一曲、上一曲;4位LED 显示器,用来显示所选曲目,该显示器在播放期间为了节省电源,设计为关闭状态,当一歌曲演奏结束,或选曲时显示器才显示曲目信息。

要求焊接好开发板,在开发板上进行调试。

设计要求:1)确定系统设计方案;2)进行系统的硬件设计;3)完成必要元器件选择;4)开发板焊接及测试5)系统软件设计及调试;6)系统联调及操作说明7)写说明书主要设计条件1、MCS-51单片机实验操作台1台;2、PC机及单片机调试软件,仿真软件proteus;3、开发板1块;4、制作工具1套;5、系统设计所需的元器件。

说明书格式目录第1章、概述第2章、系统总体方案设计第3章硬件设计第4章软件设计及调试第5章系统联调及操作说明第6章总结参考文献附录A系统硬件原理图附录B程序清单进度安排设计时间分为二周第一周星期一、上午:布置课题任务,课题介绍及讲课。

下午:借阅有关资料,总体方案讨论。

星期二、分班级焊接开发板星期三、确定总体方案,学习与设计相关内容。

星期四、各部分方案设计,各部分设计。

星期五、设计及上机调试。

星期六、设计并调试第二周星期一:设计及上机调试。

星期二:调试,中期检查。

星期三:调试、写说明书。

星期四--星期五上午:写说明书、完成电子版并打印成稿。

星期五下午:答辩。

参考文献参考文献1、王迎旭编.《单片机原理与应用》[M].机械工业出版社.2、楼然苗编.《51系列单片机设计实例》[M].北京航空航天大学出版社.3、黄勤编.《计算机硬件技术基础实验教程》[M].重庆大学出版社4、刘乐善编.《微型计算机接口技术及应用》[M].华中科技大学出版社.5、陈光东编.《单片微型计算机原理及接口技术》[M].华中科技大学出版社.第1章概述... ... ... ... ... ... ... ... .. .. . 61.1单片机简介... ... ... ... .. ... ... ... (6)1.2 任务简介. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7第2章系统总体方案设计 (8)2.1 音乐的产生... . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .82.2 系统方案. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .. 10第3章硬件设计 (11)3.1 89C51单片机 (12)3.2 I/O并行口直接驱动LED显示 (14)3.3 蜂鸣电路. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .153.4控键电路.. . . . . . . . . . . . . . . . . . .163.5时钟电路 . . . . . . . . . . . . . . . . .. .173.6电源电路 . . . . . . . . . . . . . . . . . . 17 第4章软件设计 (18)4.1.软件设计 (18)4.2 设计方案. . . . . . . . . . . . .. . . . . . . . . . . . . .. . . . . . .. . . . .19第5章系统调试与仿真 (20)5.1软件仿真阶段 (20)5.2系统的仿真调试阶段 (20)5.3调试问题处理 (21)第6章心得体会 (22)参考文献 (23)附录A:音乐播放器电路设计图 (24)附录B:程序清单 (25)第1章概述1.1单片机简介单片机又称单片微控制器,它不是完成某一逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

单片机音乐播放器开题报告

单片机音乐播放器开题报告单片机音乐播放器开题报告一、引言音乐是人们生活中不可或缺的一部分,而音乐播放器则是人们享受音乐的重要工具。

随着科技的不断发展,音乐播放器也从最初的磁带式、CD式,逐渐演变为数字化的MP3、MP4等形式。

然而,市面上的音乐播放器功能繁多,价格也各不相同,对于一些对音质要求不高,只想简单听歌的用户来说,这些播放器过于复杂且昂贵。

因此,我们决定设计一款简单实用、价格适中的单片机音乐播放器。

二、项目背景目前市场上的音乐播放器大多采用了复杂的操作系统,功能繁多,造成了用户在使用时的困扰。

而单片机音乐播放器则是一种基于单片机的音乐播放设备,它以简单易用、功能实用为特点,适合那些对音质要求不高,只想简单听歌的用户。

通过对市场调研和用户需求分析,我们认为单片机音乐播放器有着广阔的市场前景。

三、项目目标我们的目标是设计一款简单实用、价格适中的单片机音乐播放器,以满足用户对音乐播放的基本需求。

具体目标如下:1. 支持常见音频格式,如MP3、WAV等。

2. 提供简单的操作界面,方便用户使用。

3. 支持音量调节、歌曲切换等基本功能。

4. 具备耳机输出和扬声器输出两种音频输出方式。

5. 采用低功耗设计,延长电池使用寿命。

6. 价格适中,以满足大众用户的购买需求。

四、项目方案1. 硬件设计我们将采用一块单片机作为核心控制器,通过外部存储器存储音频文件,并通过DAC芯片将数字信号转换为模拟信号输出。

同时,我们将设计一个简单的按键控制电路,用于用户操作。

此外,为了满足不同用户的音频输出需求,我们还将设计耳机输出和扬声器输出两种音频输出方式。

2. 软件设计在软件设计方面,我们将编写一套简单的程序,用于控制单片机音乐播放器的各项功能。

该程序将包括音频文件的读取、解码、播放等功能,同时还将设计一个简单的用户界面,方便用户进行操作。

为了提高音质和减少功耗,我们还将对程序进行优化,确保音乐播放器的性能和稳定性。

五、项目进度计划1. 前期准备阶段(1周)- 进行市场调研,了解用户需求。

单片机音乐原理

单片机音乐原理

单片机音乐原理是指通过单片机控制音源发出不同的音符,以实现音乐的播放。

它主要包括音乐存储、音符输出和控制过程三个部分。

首先,音乐存储是指将音乐数据存储到单片机中。

一般来说,音乐数据是以midi 格式存储的,midi格式是一种数字音乐文件格式,其中包含了音符、音高、音长等音乐元素。

单片机通常会使用SPI接口或者SD卡接口等方式读取音乐数据,并将其存储到内部的寄存器或者外部存储器中。

其次,音符输出是指将存储的音乐数据经过处理后输出到音源中。

单片机通常会通过定时器/计数器模块来实现音符的输出。

定时器/计数器模块可以产生固定频率的时钟信号,并且可以通过设置计数值的大小来调节时钟信号的频率。

在音符输出过程中,单片机会根据存储的音乐数据设置相应的计数值,从而输出不同的频率。

最后,控制过程是指单片机控制音乐播放的过程。

单片机可以通过外部按键、编码器、蓝牙模块等方式接收用户的控制信号,根据用户的操作来控制音乐的播放。

例如,当用户按下某个按键时,单片机可以根据预设的逻辑判断是否需要切换音乐,调节音量等。

总的来说,单片机音乐原理主要包括音乐存储、音符输出和控制过程三个部分。

通过存储音乐数据,将其输出到音源中,然后通过控制过程来控制音乐的播放,

最终实现了单片机音乐的功能。

这种原理在很多电子琴、音频播放器等设备中都得到了广泛的应用。

单片机音乐播放器课程设计

单片机音乐播放器课程设计一、课程目标知识目标:1. 理解单片机的基础知识,掌握其内部结构与工作原理;2. 学会使用C语言编写单片机程序,实现音乐播放器的功能;3. 了解音乐播放器的基本组成部分,如音符产生、音调控制等;4. 掌握音乐理论知识,能将简单的乐谱转换为单片机程序。

技能目标:1. 能够运用所学知识,设计并实现一个具有基础音乐播放功能的单片机系统;2. 熟练使用编程软件进行单片机程序编写、调试与优化;3. 学会使用相关工具和仪器,进行电路搭建、测试与故障排查。

情感态度价值观目标:1. 培养学生对单片机及电子制作的兴趣,激发创新精神;2. 培养学生的团队协作能力,学会与他人共同解决问题;3. 增强学生的自信心,敢于面对挑战,勇于克服困难;4. 培养学生的责任心,关注环境保护,养成良好的操作习惯。

课程性质:本课程为实践性较强的课程,以项目为导向,结合单片机原理与应用,培养学生的动手能力和创新能力。

学生特点:本课程针对高中年级学生,学生具备一定的物理、数学基础,对电子制作有一定兴趣,但编程能力参差不齐。

教学要求:教师需结合学生特点,采用循序渐进的教学方法,注重理论与实践相结合,关注个体差异,提高学生的实践操作能力。

在教学过程中,注重引导学生思考,激发学生的学习兴趣,培养其创新精神。

通过课程学习,使学生能够独立完成一个简单的单片机音乐播放器设计。

二、教学内容1. 单片机基础知识:介绍单片机的内部结构、工作原理、性能特点,引导学生了解并掌握单片机的基本概念。

教材章节:第一章 单片机概述2. C语言编程基础:讲解C语言的基本语法、数据类型、运算符、控制结构等,为学生编写单片机程序奠定基础。

教材章节:第二章 C语言基础3. 单片机程序设计与调试:学习如何使用编程软件进行程序编写、调试与优化,掌握单片机程序的开发流程。

教材章节:第三章 单片机程序设计与调试4. 音频信号处理:介绍音频信号的基本知识,如音符、音调、节拍等,学习如何将乐谱转换为单片机程序。

单片机音乐播放器(两只老虎)

;sing a song//T0定时中断控制音符,T1定时中断控制节拍,基准定时50msTH1_DA TA EQU 03CHTL1_DA TA EQU 0B0HYINFU EQU 30HJIEPAI EQU 31HBUZZER BIT P1.0ORG 0000HAJMP STARTORG 000BHAJMP INT_T0 ;控制音符(音调)ORG 001BHAJMP INT_T1 ;控制节拍(音符持续时间)ORG 0100HSTART:MOV SP, #60HMOV TMOD, #11H //定时器T0/T1都是方式1MOV R2, #0 ;取歌曲音符和节拍的偏移量MOV A, R2MOV DPTR, #TABLE_SONGMOVC A, @A+DPTR ;取歌曲音符MOV YINFU, AMOV DPTR, #TABLE_TH0MOVC A, @A+DPTR ;取音符对应定时器T0的初始值MOV TH0, AMOV A, YINFUMOV DPTR, #TABLE_TL0MOVC A, @A+DPTRMOV TL0, AMOV A, R2MOV DPTR, #TABLE_LENGTHMOVC A, @A+DPTR ;取该音符对应的节拍MOV JIEPAI, AMOV TH1, #TH1_DA TA ;节拍基准定时50ms(12MHz晶振)MOV TL1, #TL1_DA TASETB PT1 ;设置节拍中断为高优先级中断SETB ET0SETB ET1SETB EASETB TR0SETB TR1SJMP $;--------------------------------------------------------;控制音符的定时中断,依据R2的值决定取歌曲中哪个音符;读到音符为0代表歌曲结束,则关中断,停止定时器。

否则继续;根据读到的音符查表选择对应的定时器初始值;---------------------------------------------------------INT_T0:PUSH ACCPUSH PSWCPL BUZZER //改变蜂鸣器状态MOV A, R2MOV DPTR, #TABLE_SONGMOVC A, @A+DPTRMOV YINFU, AJNZ SING //判断是否到歌曲结束CLR TR0CLR TR1CLR EASJMP EXITSING:MOV A, YINFUMOV DPTR, #TABLE_TH0MOVC A, @A+DPTRMOV TH0, AMOV A, YINFUMOV DPTR, #TABLE_TL0MOVC A, @A+DPTRMOV TL0, AEXIT:POP PSWPOP ACCRETI;-------------------------------------------------------------------------;控制节拍的定时中断,每个音符节拍时间到,调整R2指向下一音符INT_T1:PUSH ACCMOV TH1, #TH1_DA TA ;节拍基准定时50ms(12MHz晶振)MOV TL1, #TL1_DA TADJNZ JIEPAI, EXIT_T1INC R2MOV A, R2MOV DPTR, #TABLE_LENGTHMOVC A, @A+DPTRMOV JIEPAI, AEXIT_T1:POP ACCRETITABLE_TH0:DB 0FCH, 0FCH, 0FCH, 0FDH, 0FDH, 0FDH ,0FDHDB 0FEH, 0FEH, 0FEH, 0FEH, 0FEH, 0FEHDB 0FEH, 0FFHTABLE_TL0:DB 00H, 44H, 0ACH, 09H, 34H, 82H, 0C8HDB 06H, 22H, 56H, 85H, 9AH, 0C1HDB 0E3H, 03HTABLE_SONG:DB 1,2,3,1,1,2,3,1,3,4,5,5,3,4,5,5DB 5,6,5,4,3,2,5,6,5,4,3,2,1,5,1,1DB 1,5,1,1,0TABLE_LENGTH:DB 10,10,10,10,10,10,10,10,10,10,10,10,10,10,10,10DB 5,5,5,5,10,10,5,5,5,5,10,10,10,10,10,10DB 10,10,10,10,10,10END。

基于51单片机的音乐播放器设计

题目:音乐播放器课程设计(论文)任务书课程设计(论文)题目:音乐播发器基本内容:利用单片机的定时器产生各种频率的方波,信号经过放大后送到喇叭从而产生各种音调。

自行定义键盘,每按一键,可选择一首歌曲进行演奏,至少能够存储并播放十首歌曲,在LCD上显示演奏歌曲的名称并滚动显示歌词,单片机可连续播放这首歌曲,演奏可通过按键停止。

课程设计(论文)专题部分:题目:音乐播放器基本内容:通过单片机设计可以播放十首歌曲的音乐播放器,同步显示歌曲名称和歌词。

学生接受毕业设计(论文)题目日期第19 周指导教师签字:2009年7月摘要随着电子技术的发展和计算机越来越普遍的使用,单片机作为这两项技术的有机结合也得到了广泛的应用,在某些领域具有不可替代的作用。

音乐播放功能随处都会用到,如,在开发儿童智力的玩具中,等等。

目前,基于单片机实现音乐播放,其体积小、价格低、编程灵活等特点在这一领域独领风骚。

单片机的英文名称为single chip microcomputer,最早出现在20世纪70年代,国际上现在已逐渐被微控制器(Microcontroller Unit 或MCU)一词所取代。

它体积小,集成度高,运算速度快,运行可靠,功耗低,价格廉,因此在数据采集、智能化仪表、通讯设备等方面得到了广泛应用。

而8051单片机在小到中型应用场合很常见,已成为单片机领域的实际标准。

随着硬件的发展,8051单片机系列的软件工具也有了C级编译器和实时多任务操作系统RTOS,为单片机编程使用C语言提供了便利的条件;并针对单片机常用的接口芯片编制通用的驱动函数,可针对常用的功能模块,算法等编制相应的函数;C语言模块化程序结构特点,可以使程序模块大家共享,不断丰富,这样就使得单片机的的程序设计更简单可靠,实时性强,效率高。

作为测控技术与仪器的学生,掌握8051单片机硬件基础及其相关软件操作,将其应用于现代电子产品中是必要而且重要的,这次课程设计我们的题目是用单片机实验箱系统制作音乐播放器。

基于单片机的音乐播放器的设计 实验原理图

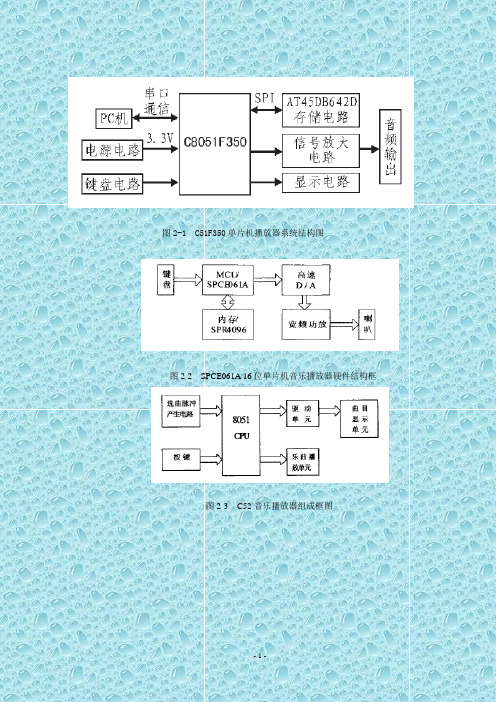

图2-1 C51F350单片机播放器系统结构图图2-2SPCE061A 16位单片机音乐播放器硬件结构框图2-3 C52音乐播放器组成框图图3-1 AT89C52引脚排列图图3-2 晶振电路图3-3 微分型复位电路432P1.01P1.12P1.23P1.34P1.45P1.56P1.67P1.78RST 9 3.0/RXD 10 3.1/TXD 11P3.2/INT012P3.3/INT113P3.4/T014P3.5/T115P3.6/WR 16P3.7/RD 17XTAL118XTAL219Vss 20P2.021P2.122P2.223P2.324P2.425P2.526P2.627P2.728PSEN 29ALE 30EA 31P0.732P0.633P0.534P0.435P0.336P0.237P0.138P0.039VC C 40AT89C52Y112M HZC630PF C730PFX 1X 2VC CR1VC CVC C图3-4 单片机最小系统图a) 八段共阴LED显示管原理图图b) 八段共阳LED显示管原理图图3-5 八段LED显示管原理图[7]图3-7 音乐播放器LED显示电路设计图3-8 LM2575集成稳压器的两种引脚图[11]图3-9 LM2575内部框图图3-10 电源电路的设计电路图[13]图3-11 内部结构图表3-2 音频功率放大器R1 R23.3V 1.0K 1.7K5V 1.0K 3.1K 12V 1.0K 8.84K 15V 1.0K 11.3K 输出电压可调Open 0图3-12 全数字功放与普通功放过载失真度比较图3-13 LM386引脚图图3-14 LM386方块图表3-3 LM386电子特性表图3-15 音频功率放大器[18]图4-1 主程序流程图[20]图4-2 显示子程序的流程图[21]图4-3 INT0中断模块流程[24]图4-4 T1中断模块程序流程图附录A:电气原理图321DC B AC310u FC130pC230pC5100nF+C2100uFY1D1IN5819123456781234567812345678A1LM386R1330uhR1R110KS1S2+C2330VS3OUTFbVinGNDONU2LM2575GNDP1.01P1.12P1.23P1.34P1.45P1.56P1.67P1.78RST93.0/RXD103.1/TXD11P3.2/INT012P3.3/INT113P3.4/T014P3.5/T115P3.6/WR16PSEN29XTAL118XTAL219Vss20P2.021P2.122P2.223P2.324P2.425P2.526P2.627P2.728P3.717ALE30EA31P0.732P0.633P0.534P0.435P0.336P0.237P0.138P0.039VCC40U1AT89C52VCC123。

单片机音乐播放器应用 实现简单的音乐播放功能

单片机音乐播放器应用实现简单的音乐播放功能单片机音乐播放器应用音乐是人们生活中不可或缺的一部分,而在现代科技的不断发展下,单片机音乐播放器应用已经成为许多人追求的目标。

本文将介绍如何实现一个简单的单片机音乐播放器功能,让您能够轻松享受音乐的魅力。

一、硬件准备在开始之前,我们需要准备一些硬件设备,以确保音乐播放器能够正常工作。

首先,我们需要一块单片机开发板,例如STC89C52,这是一款常用的单片机开发板;其次,我们需要一个音频解码模块,例如DFPlayer Mini,他可以轻松解码并播放存储卡上的音乐文件;最后,我们还需要一个音箱或者耳机,用于输出音乐。

二、软件编程1. 搭建开发环境首先,我们需要安装MIDE-51集成开发环境,它是STC89C52单片机所使用的开发工具。

安装完成后,可以通过打开MIDE-51来创建一个新的工程。

2. 编写代码首先,我们需要在代码中包含一些必要的库文件,以便使用一些功能函数。

例如,我们可以通过以下代码片段引入DFPlayer Mini音频库文件:```c#include <DFPlayer_Mini_Mp3.h>```接下来,我们可以通过定义一些常量或变量来控制音乐的播放,例如:```cconst int playButton = 2; // 播放按钮连接到单片机的2号引脚const int nextButton = 3; // 下一首按钮连接到单片机的3号引脚const int previousButton = 4; // 上一首按钮连接到单片机的4号引脚```然后,我们可以在主循环中不断检测按钮的状态,并根据按钮的状态来控制音乐的播放:```cvoid loop() {if (digitalRead(playButton) == HIGH) { // 如果播放按钮被按下DFPlayer_Mini_Mp3.play(); // 播放音乐}if (digitalRead(nextButton) == HIGH) { // 如果下一首按钮被按下 DFPlayer_Mini_Mp3.next(); // 播放下一首音乐}if (digitalRead(previousButton) == HIGH) { // 如果上一首按钮被按下DFPlayer_Mini_Mp3.previous(); // 播放上一首音乐}}```通过上述代码,我们可以实现简单的音乐播放功能。

「基于单片机的MP3播放器设计_毕业设计」

「基于单片机的MP3播放器设计_毕业设计」随着科技的发展,MP3播放器成为了大众日常生活中不可或缺的一部分。

本文将介绍一个基于单片机的MP3播放器的设计,并探讨其在毕业设计中的应用。

首先,我们需要明确设计目标。

该MP3播放器的主要功能是播放音频文件,包括MP3和其他常见格式的音频文件。

除此之外,它还应具备控制播放、暂停、快进、快退等功能。

另外,该MP3播放器还需要具备文件管理功能,能够浏览音频文件,并通过界面进行选择和播放。

接下来,我们将进行硬件设计。

MP3播放器的核心部分是单片机,我们可以选择一款功能强大的单片机,如ARM Cortex-M系列的单片机。

该单片机需要支持音频解码功能,因此可以选择一款集成了音频解码芯片的单片机,这样可以减小外围电路的复杂度。

此外,我们还需要添加音频输入和输出电路,以及LCD显示屏、按键和电源管理电路。

在软件设计方面,我们需要进行音频解码的程序开发。

我们可以选择使用现成的开源解码软件库,如mad(MPEG Audio Decoder)或LAME (LAME Ain't an MP3 Encoder)。

这些库可以实现对MP3格式的音频文件进行解码,并输出数字音频信号。

我们还需要开发一个用户界面程序,实现文件浏览和选择,并与解码软件库进行交互。

最后,我们将介绍该MP3播放器的应用于毕业设计中的可能性。

毕业设计可以从以下几个方面展开:1.性能优化:可以通过对音频解码算法的优化,提高音频文件的解码速度和音质;或者对MP3播放器的界面进行优化,提高用户体验。

2.功能扩展:可以通过添加额外的功能模块,如蓝牙模块、存储卡接口等,实现更多的功能,如无线传输、外部存储扩展等。

3.系统集成:可以将MP3播放器与其他系统进行集成,如车载音频系统、家庭音响系统等,以实现更广泛的应用。

综上所述,基于单片机的MP3播放器设计具有许多潜在的应用领域。

在毕业设计中,我们可以通过对性能优化、功能扩展和系统集成等方面的研究,使MP3播放器的设计更加完善和创新。

基于单片机音乐播放器的设计

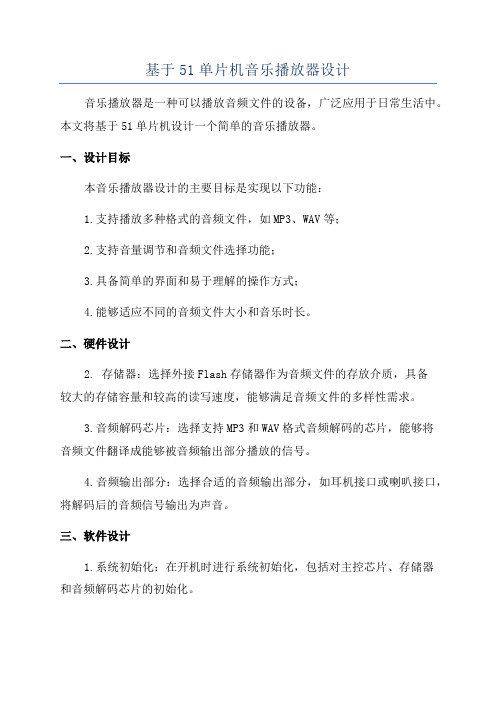

题目:基于单片机音乐播放器的设计文献综述:单片机又称单片微控制器,它不是完成某一个逻辑功能的芯片,而是把一个计算机系统集成到一个芯片上。

概括的讲,一块芯片就成了一台计算机。

MCS-51单片机是美国INTEL公司于1980年推出的产品,与MCS- 48单片机相比,它的结构更先进,功能更强,在原来的基础上增加了更多的电路单元和指令,指令数达111条,MCS-51单片机可以算是相当成功的产品,一直到现在,MCS-51系列或其兼容的单片机仍是应用的主流产品,各高校及专业学校的培训教材仍与MSC-51单片机作为代表进行理论基础学习。

基于单片机的音乐播放器可应用于mp3,MP4,扩音器等很多方面,并可作为很多系统的辅助功能,作为单片机的重要硬件资源之一,利用定时器可以产生各种固定频率的方波信号,也可以产生包括"Do"、"Re"、"Me"--等音阶在内的各种频率声音。

将各个音阶连接在一起,便可组成一支曲子或是演奏一段旋律。

基于这个思想,我设计了一款特殊的"音乐播放器",本播放器可实现播放、暂停、复位等功能。

为了体现乐曲播放过程中的动态效果,增加了1只LED,作随机闪烁以指示旋律的节奏。

由于时间及条件限制,本设计实现了一种简单的音乐播放器,其核心器件采用AT89C52单片机,本播放器具有电路简单,功能强大,易于拓展等特点。

在此基础上,可以添加按键,LED显示屏等模块,实现切换歌曲,歌曲序号的显示。

此音乐播放器实现的控制功能如下:1.程序中存有5首歌曲;2.按下某键后,能选择歌曲,并通过LED显示歌曲序号。

2.选题依据、主要研究内容、研究思路及方案:通过控制定时器的定时时间来产生不同频率的方波,驱动喇叭发出不同音阶的声音,再利用延迟来控制发音时间的长短,即可控制音调中的节拍。

把乐谱中的音符和相应的节拍变换为定常数和延迟常数,作为数据表格存放在存储器中。

单片机播放音乐

一般说来,单片机演奏音乐基本都是单音频率,它不包含相应幅度的谐波频率,也就是说不能象电子琴那样能奏出多种音色的声音。

因此单片机奏乐只需弄清楚两个概念即可,也就是“音调”和“节拍”。

音调表示一个音符唱多高的频率,节拍表示一个音符唱多长的时间。

1)音调的确定音调就是我们常说的音高。

它是由频率来确定的!我们可以查出各个音符所对应的相应的频率,那么现在就需要我们来用51来发出相应频率的声音!我们常采用的方法就是通过单片机的定时器定时中断,将单片机上对应蜂鸣器的I/O口来回取反,或者说来回清零,置位,从而让蜂鸣器发出声音,为了让单片机发出不同频率的声音,我们只需将定时器予置不同的定时值就可实现。

那么怎样确定一个频率所对应的定时器的定时值呢?以标准音高A为例:A的频率f = 440 Hz,其对应的周期为:T = 1/ f = 1/440 =2272μs那么,单片机上对应蜂鸣器的I/O口来回取反的时间应为:t = T/2 = 2272/2 = 1136μs,也就是清零、置位在一个周期内完成.这个时间t也就是单片机上定时器应有的中断触发时间。

一般情况下,单片机奏乐时,其定时器为工作方式1,它以振荡器的十二分频信号为计数脉冲。

设振荡器频率为f0,则定时器的予置初值由下式来确定:t = 12 *(T ALL– T HL)/ f0式中T ALL = 216 = 65536,T HL为定时器待确定的计数初值。

因此定时器的高低计数器的初值为:TH = T HL / 256 = ( T ALL– t* f0/12) / 256TL = T HL % 256 = ( T ALL– t* f0/12) %256将t=1136μs代入上面两式(注意:计算时应将时间和频率的单位换算一致),即可求出标准音高A在单片机晶振频率f0=12Mhz,定时器在工作方式1下的定时器高低计数器的予置初值为:TH440Hz = (65536 – 1136 * 12/12) /256 = FBHTL440Hz = (65536 – 1136 * 12/12)%256 = 90H就这样,我们通过延时,发出了我们所需要的频率以单片机12MHZ晶振为例,列出高中低音符与单片机计数T0相关的计数值如下表所示音符频率(HZ)简谱码(T值)音符频率(HZ)简谱码(T值)低1 DO 262 63628 # 4 FA# 740 64860#1 DO# 277 63731 中 5 SO 784 64898低2 RE 294 63835 # 5 SO# 831 64934#2 RE# 311 63928 中 6 LA 880 64968低 3 M 330 64021 # 6 932 64994低 4 FA 349 64103 中 7 SI 988 65030# 4 FA# 370 64185 高 1 DO 1046 65058低 5 SO 392 64260 # 1 DO# 1109 65085# 5 SO# 415 64331 高 2 RE 1175 65110低 6 LA 440 64400 # 2 RE# 1245 65134# 6 466 64463 高 3 M 1318 65157低 7 SI 494 64524 高 4 FA 1397 65178中 1 DO 523 64580 # 4 FA# 1480 65198# 1 DO# 554 64633 高 5 SO 1568 65217中 2 RE 587 64684 # 5 SO# 1661 65235# 2 RE# 622 64732 高 6 LA 1760 65252中 3 M 659 64777 # 6 1865 65268中 4 FA 698 64820 高 7 SI 1967 65283下面我们要为这个音符建立一个表格,有助于单片机通过查表的方式来获得相应的数据低音0-19之间,中音在20-39之间,高音在40-59之间TABLE: DW 0,63628,63835,64021,64103,64260,64400,64524,0,0DW 0,63731,63928,0,64185,64331,64463,0,0,0DW 0,64580,64684,64777,64820,64898,64968,65030,0,0DW 0,64633,64732,0,64860,64934,64994,0,0,0DW 0,65058,65110,65157,65178,65217,65252,65283,0,0DW 0,65085,65134,0,65198,65235,65268,0,0,0DW 02)节拍的确定在一张乐谱中,我们经常会看到这样的表达式,如1=C (4/4) 、1=G(3/4) …… 等等,这里1 =C (4/4),1=G(3/4)表示乐谱的曲调,和我们前面所谈的音调有很大的关联,4/4、3/4 就是用来表示节拍的。

基于51单片机音乐播放器设计

基于51单片机音乐播放器设计音乐播放器是一种可以播放音频文件的设备,广泛应用于日常生活中。

本文将基于51单片机设计一个简单的音乐播放器。

一、设计目标本音乐播放器设计的主要目标是实现以下功能:1.支持播放多种格式的音频文件,如MP3、WAV等;2.支持音量调节和音频文件选择功能;3.具备简单的界面和易于理解的操作方式;4.能够适应不同的音频文件大小和音乐时长。

二、硬件设计2. 存储器:选择外接Flash存储器作为音频文件的存放介质,具备较大的存储容量和较高的读写速度,能够满足音频文件的多样性需求。

3.音频解码芯片:选择支持MP3和WAV格式音频解码的芯片,能够将音频文件翻译成能够被音频输出部分播放的信号。

4.音频输出部分:选择合适的音频输出部分,如耳机接口或喇叭接口,将解码后的音频信号输出为声音。

三、软件设计1.系统初始化:在开机时进行系统初始化,包括对主控芯片、存储器和音频解码芯片的初始化。

2.文件系统管理:设计一个简单的文件系统,能够以目录结构的形式管理存储器中的音频文件。

3.音频解码:根据选择的音频文件格式,进行相应的解码操作,将解码后的音频数据传输给音频输出部分。

4.播放控制:实现音量调节和音频文件选择功能,能够暂停、播放、停止等操作。

5.用户界面:设计一个简单直观的用户界面,通过按键或显示屏等方式进行操作反馈和信息显示。

四、系统流程1.开机初始化:对主控芯片、存储器和音频解码芯片进行初始化。

2.文件系统管理:读取存储器中的文件目录,生成文件列表供用户选择。

3.用户操作:用户通过按键或其他方式进行音量调节和音频文件选择操作。

4.音频解码:根据用户选择的音频文件,进行相应的解码操作。

5.播放控制:根据用户的操作,进行音频的暂停、播放、停止等操作。

6.操作反馈:在用户界面上显示操作反馈和信息。

五、总结本文基于51单片机设计了一个简单的音乐播放器,实现了支持多种格式音频文件的播放、音量调节和文件选择功能,并提供了简单的用户界面。

MP3智能播放器定时编程方法

MP3智能播放器定时编程方法随着科技的发展,智能设备已经成为我们日常生活中不可或缺的一部分。

在这些设备中,MP3智能播放器以其方便、灵活的特点,特别受到年轻人的喜爱。

然而,对于许多用户来说,如何设置定时播放成为了使用过程中的一个难题。

今天,我们就来探讨一下MP3智能播放器定时编程方法。

一、了解你的MP3播放器你需要了解你的MP3播放器的操作系统和功能。

大部分现代的MP3播放器都运行在Android或iOS系统上,这意味着他们可以连接到互联网,并使用各种应用程序。

如果你的播放器支持蓝牙,那么你可以将它连接到电脑或其他设备上,进行文件的传输和播放。

二、设置定时播放1、在你的手机或电脑的浏览器中搜索并下载你MP3播放器对应的同步软件或应用程序。

这些软件通常可以帮助你管理你的播放器,包括设置定时任务。

2、打开下载的软件,并将你的MP3播放器连接到电脑或手机上。

一旦连接成功,你就可以在软件界面上看到你的播放器的所有文件和设置。

3、在软件中找到“定时任务”或“闹钟”之类的选项。

在这个选项中,你可以设置在特定时间自动播放音乐。

例如,你可以设置在每天早上7点自动播放你选择的音乐。

4、选择你想要定时播放的音乐文件,并设置你想要定时播放的时间。

在完成这些步骤后,你的MP3播放器就会在设定的时间自动播放你选择的音乐。

三、其他注意事项1、确保你的MP3播放器和电脑或手机已经正确连接。

如果连接失败,你可能需要检查你的设备是否开启了蓝牙或者Wi-Fi,以及他们的信号是否足够强。

2、在设置定时任务时,要确保你设定的时间是在你的播放器处于开机状态时。

如果你的播放器在设定时间前已经关机,那么定时任务将无法执行。

3、不同的MP3播放器可能有不同的操作步骤和功能。

如果你遇到问题,你可以查看你的播放器的用户手册,或者在网上搜索相关的教程和指南。

设置MP3智能播放器的定时播放并不复杂。

只要大家知道大家的播放器的操作系统和功能,以及一些基本的电脑操作,大家就可以轻松地设置定时播放。

(完整word版)单片机控制音乐播放-开题报告

南昌大学共青学院本科生毕业论文(设计)开题报告

图1

四、研究方法

方案一方案设计

采用51系列作为系统控制器,单片机算术运算功能强,软件编程灵活、自由度大,可用软件编程实现各种算法和逻辑控制。

由于其功耗低、体积较小、技术成熟和成本低等优点,在各个领域应用广泛。

而且抗干扰性能好。

采用LED数码管控制用单片机,显示用LED数码管这种方案。

虽然显示的内容有限,但是也可以显示数字和几个英文字母,在这个设计中已经足够了,并且价格比液晶字符式要低的多,为了控制设计制作的成本,在此设计中我们选用LED数码管显示。

[3] 王港元.电工电子实践指导.江西电子科学技术出版社.2007

[4] 阎石.数字电子技术基础第五版.高等教育出版社,2006.

[5] 谭浩强.C程序设计第四版.清华大学出版社.2010.

[6] 张鑫.单片机原理及应用[M].北京:电子工业出版社.2005

[7] 李玉梅.基于MCS-51系列单片机原理的设计应用[M].北京:国防工业出版社.2006

[8] 吴金戌.8051单片机实践与应用[M].清华大学出版社.2003.

[9] 戴梅芳.微型计算机技术及应用[M].清华大学出版社.1996.

[10] 徐爱卿.单片微型计算机应用和开发系统[M].北京航空航天大学出版社. 1998

填写说明

1.指导教师意见填写对本课题的深度、广度及工作量的意见和对论文结果的预测;

2.所在教研室审查意见包括对指导教师意见的认定和是否同意开题等;

3.本开题报告打印存档,但签名部分必须由指导教师或学生亲笔签名。

智能时程音乐播放器功能说明

智能时程音乐播放器功能说明※系统概述:M P3智能音乐播放系统:采用世界最先进的微电脑控制、M P3、F L A S H录音技术。

将广播自动播放、音源选播、录音下载/音频和麦克风录音存储等先进功能综合为一体。

高标准的产品定位,多功能的超前设计,成为广播设备的典范之精品,达到国内领先水平。

广泛适用于校园自动广播音乐打铃、外语广播教学听力考试系统。

※综合功能:M P3自动广播、智能分区广播、日常教学广播、消防紧急广播、背景音乐播放、外语教学及听力考试广播功能。

※系统特点:1、M P3存储:本系统采用F L A S H为存储方式,音质清晰、优美、内存容量有2G,可满足各种用户广播需求。

2、编程播放:具有自动广播功能、每天可达99次设定编程播放,对播放内容和播出时间、次数及循环设定多遍播放并任意编程控制,实现无人直守。

每一次编程时间设定可达几十首歌曲进行播放输入。

对某些需要准点播放的内容拥有优先权。

3、功放管理:在每次执行定时播放程序时会自动提前5秒钟将功放电源打开,避免功放机开机因启动及预热延时而影响正常播放。

(智能化的设计起到了节能和科学化管理功放开关)4、中文菜单显示:M P3自动广播系统采用中文式菜单液晶显示,引导式菜单进入,让操作者对各项功能信息一目了然,上下翻页及功能设定简洁方便,简单明朗易学易用。

5、程序设定:用户可根据不同的作息时间、内容进行编程设定,达到任意选择和调整作息时间,满足各广播单位对广播作息的选择需求。

6、M P3下载存录音源:用户可直接从计算机上下载或自行录制需要的乐曲到系统内,再进行编程播放。

7、音频及麦克存录音源:本系统可直接从各种媒体(V C D、C D、卡座等)线路和麦克风两种方式录音输入存储音源音乐曲目。

8、时钟显示:本系统具有日常时钟功能:本机采用专用实时时钟模块,走时准确,停电正常计时,标准时间及工作程序不会丢失、错乱。

对年、月、日及时间显示,起到了对操作使用者及时了解当前时间和下一曲将播放的时间显示功能。

定时课间音乐播放的原理

定时课间音乐播放的原理定时课间音乐播放的原理是通过设定一个精确的时间计划来自动播放音乐。

该系统通常由一个正常工作的计算机或音乐播放器控制,并配备了一套高质量的音响设备。

以下将详细介绍定时课间音乐播放的原理和相关技术。

首先,在实际应用中,定时课间音乐播放系统通常由两个主要组成部分组成:音乐控制主机和音箱系统。

音乐控制主机通常是一个嵌入式系统或计算机,通过一个软件程序来控制音箱系统的播放。

音乐控制主机通过内置的硬件时钟或计算机系统时钟来定时启动音箱系统。

使用计算机的话,系统管理员可以使用特定的软件程序来设置播放时间表,以指定每个时间段应播放的音乐曲目。

这些时间表可以根据学校的时间表进行设定,可以设置每天的上课时间和课间休息时间。

一旦设定好时间表,音乐控制主机将在指定的时间点启动音箱系统并播放相应的音乐。

音箱系统通常由多个音箱组成,这些音箱可以放置在学校的各个教室和走廊里,以确保音乐的覆盖范围和音质的质量。

这些音箱通常由主机通过电缆或无线信号连接,以便接收音乐信号。

当音乐控制主机发送音乐信号到音箱系统时,音箱系统会解码音乐信号并将其转换为声音。

在音箱中,音乐信号经过放大器放大后,通过扬声器发出。

这样,学校的各个教室和走廊就可以同时播放相同的音乐,营造出一个独特的音乐氛围。

除了基本的定时和播放功能外,定时课间音乐播放系统通常还具有一些额外的功能,以增强用户体验和管理功能。

例如,一些系统可以允许管理员通过网络远程管理和控制音乐播放。

管理员可以通过一个专门的控制界面或手机应用程序来更改播放时间表、选择不同的音乐曲目和调整音量。

另外,一些高级的定时课间音乐播放系统还可以提供多种音乐源选择,如内置音乐库、外部存储设备或在线音乐流媒体服务。

这样,学校可以根据自己的喜好和需求来选择不同的音乐来源,为学生和教职员工提供多样化的音乐选择。

总的来说,定时课间音乐播放的原理是通过一个音乐控制主机控制音箱系统,根据预设的时间表自动启动音乐播放。

cpl单片机指令

cpl单片机指令CPL单片机指令是一种经常用于单片机编程中的指令,其全称为Complex Programmable Logic Device。

CPLD有着类似于现代FPGA芯片的布局和架构,可以对电路进行灵活且高效的编程和设计,因此在数字电路设计等领域中广泛应用。

CPLD芯片是由多个可编程逻辑单元构成,这些单元可以按照需求合并,以及配置内部的定时器等设备。

下面分步骤来介绍CPL单片机指令的使用。

1. 创建工程在使用CPL单片机指令时,我们需要首先创建一个工程。

我们可以在编程工具中选择“新建工程”选项,然后输入工程名称和存储路径即可。

创建好工程后,我们可以开始创建并编辑CPL单片机指令。

2. 设计电路在使用CPL单片机指令时,我们需要先设计出需要的电路,然后再进行编程和配置。

我们可以使用LogicWorks等电路设计软件,将需要的电路设计好之后再用CPL单片机指令来对电路进行编程。

3. 添加CPL单片机指令当我们完成了所需的电路设计并导入到了编程工具中后,我们可以开始添加CPL单片机指令了。

我们可以在编程工具的指令库中选择需要的指令,然后将其添加到我们的代码中。

CPL单片机指令可以用来控制电路的运行状态,配置计时器等设备,以及实现各种功能。

4. 编写代码当我们添加完所需的CPL单片机指令后,我们就需要开始编写我们的代码了。

我们可以使用各种编程语言,如VHDL和Verilog等,来编写我们的代码。

我们需要将电路的设计和CPL单片机指令混合在一起,以便让单片机可以对电路进行控制和管理。

5. 烧录程序当我们完成了代码编写后,我们需要将程序烧录到CPL单片机芯片中,以便让芯片能够按照程序的要求来控制电路的运行。

我们可以使用烧录工具,将程序上传到单片机中。

同时,我们需要注意烧录的方式和芯片的型号等参数,以免烧录错误。

总之,CPL单片机指令是一种十分有用的工具,可以协助我们完成各种电路设计和控制任务。

我们可以通过以上几个步骤,来深入学习和使用这一指令。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

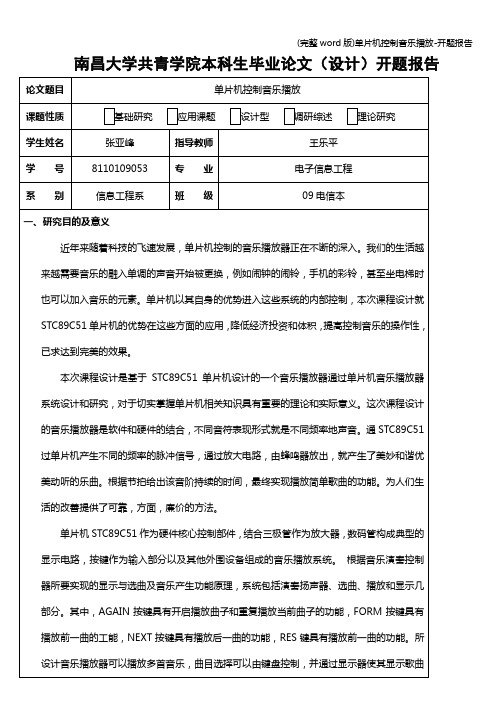

基于CPLD与51单片机的定时器与音乐播放器马大康 06007122万树 06007113覃朋 060071102009.12一、系统简介本系统利用CPLD 和51单片机联合实现了倒计时器和音乐播放器的功能。

作 为《电子系统设计》的课程设计,本系统充分利用了两块开发板上的资源,并实 现了可编程器件与单片机之间的串口异步通信,器件连接方便,并有良好的人机 交互界面。

二、系统结构框图与思路图2 CPLD 内部功能模块划分及连接经过对两块开发板板上资源的对比,我们发现,CPLD 板上的资源较为丰富, 尤其是其8个独立按键和1602液晶屏,十分适合人机交互,因此我们选择用CPLD 开发板作为主控板。

单片机板上拥有4个七段数码管,显示变化的数字十分方便, 可以构成1〜60分钟可变初值的倒计时器。

由于之前的实验中已经实现了在CPLD 中嵌入简易的UART,因此可以利用 CPLD 上的8个拨码开关设定倒计时器的初值,并通过异步串行通信传输给单片 机。

单片机上的拨码可以实现对倒计时器进行暂停、清零。

图1 系统结构框图除此之外,由于CPLD板上已有蜂鸣器,可以播放预先存入的歌曲,并通过板上的其他按键控制音斥的暂停与继续播放。

介于上述分析,设计的系统结构框图如图1所示,CPLD中功能模块的划分如图2所示。

操作流程:CPLD板上:Keyl->进入倒计时器模式,设定倒计时器初值(通过8个拨码),液晶屏上显示u D-counter Set time needed M。

Key2-〉发送倒计时器初值到单片机,单片机开始倒计时,液晶屏上显示“ D-counter D-countering nKey3->进入音乐盒模式,播放音乐《喀秋莎》。

Key4->暂停音圧播放单片机板上:在倒讣时过程中,将拨码开关1向上拨,倒计时暂停,向下拨后继续倒计时。

在倒计时过程中,按下CPLD板上的Keyl后(此时为设定初值模式),将拨码开关2向上拨,倒计时器清零,此时可对其重新置初值。

三、功能模块的实现1、异步串行发送模块想要在CPLD中嵌入异步吊行通信模块,就必须对异步吊行通信协议有深入的理解,由于系统中只用到了发送模块,这里仅对发送模块的设计做介绍。

在空闲时,发送1。

当发送使能WR为高电平且发送缓冲寄存器为高电平时, 向发送缓冲寄存器中写入待发送的数据。

当发送移位寄存器为空时,将发送缓冲寄存器中的值置入发送移位寄存器,并将TxDone变为低电平,表示发送一个字节的周期开始,此时不能向发送寄存器中置数。

发送周期开始首先发送一个低电平作为起始位,接着从数据的低位开始发送数据,发送结束后发送高电平作为结束位,并将TxDone变为高电平,表示发送一个字节结束。

整个模块的状态图如图3所示。

图3图4标准的UART设计是将系统时钟分频成16XBaudrate的频率,然后每个16 个这样的时钟周期发送一位数据。

我们这里的设计与标准设讣有些不同,我们直接把系统时钟分频成波特率时钟,然后每个周期发送一位数据,这样的效果与原先相同,但在编程上轻松了许多。

2、按键检测模块图5通过在每个时钟的上升沿检测引脚的值,经过延时再判断达到消抖的作用, 再将其转化为键值输岀。

3、液晶显示模块图6LCD_Top模块内部山时钟分频模块与LCD驱动模块构成,其中时钟分频模块负责将50M的系统时钟分频成500Hz的LCD驱动时钟。

LCD驱动模块主要负责产生控制信号并发送显示数据。

L C D驱动模块的状态流程图如下图所示。

4、蜂鸣器模块图8蜂鸣器演奏音乐模块较为简单,我们参考实验指导书中的代码,将《梁祝》的谱换成了《喀秋莎》。

5、定时器模块定时器模块在单片机中,其程序流程图如下:图10在这块单片机板上做倒讣时器有两个缺陷:第一,我们采用的是软件定时的方式,精确度不如硬件电路高;笫二,此开发板的按键和拨码没有直接接到单片机的I/O 口上,而是通过锁存器挂在总线上,这就决定了使用按键只有采取查询的方法,而不能釆用中断的方法。

因此在倒计时的过程中,每延时1秒前需要查询按键的值来实现暂停或停止的功能,指令也是需要执行时间的,这样会使延时时间超过1S,而且数码管略微有些闪烁。

不过,经过缩短延时Is程序的时间,我们将每秒钟的误差控制在了1/30秒。

四、系统调试过程本系统由三人共同合力完成,具体分工如下:马大康负责完成了串口通信模块、液晶显示模块和按键控制模块,并撰写了最终的设计文档。

万树负责完成了单片机上倒计时模块以及乐谱的输入,覃朋负责完成了蜂鸣器模块。

系统的调试是按照先单独模块测试,再组合拼接整体调试的步骤进行的,整个过程有条不紊,系统的总体设计也根据单独模块测试的情况与原先计划做岀了相应调整。

比如原先是汁划利用USB接口实现PC与CPLD板的通信,在PC上自行开发小软件以控制CPLD板上的资源。

但由于USB模块(FT245)没有在计划的时间内调试成功,我们就放弃了此方案,改用CPLD板上的按键来控制整个系统,这样并不影响系统的整体功能。

1、串口通信模块的调试山于考虑到在CPLD中实现UART并非易事,并且要实现我们系统的口标最好的方法就是利用串口通信,因此我们率先尝试了此模块。

该模块的调试时间表如下:12.9〜12. 13 深入学习了串口通信协议,编写了verilog代码,并在QuartusII 软件中仿真成功。

这里的仿真是指通过自行设计的发送模块TxUnit 向自行设计的接收模块RxUnit发送数据,接收到的数据无误。

12.21实现了CPLD板与PC机之间的通信,通过拨码设置发送数据,PC端的串口调试工具接收到数据无误。

12. 26实现了CPLD板与单片机板的通信。

在软件编写过程中,我们参考了很多资料,观摩了别人写的一些代码。

本想利用别人的代码加以改进,但未能成功。

我想原因有二:第一,从网上下载的代码可靠性值得怀疑,其本身有无经过验证还不清楚。

第二,自身阅读verilog 代码能力还需加强,不知是不是因为软件中不能写中文注释的原因,很多代码没有注释,阅读起来相当吃力。

由于接触verilog时间不长,面对长篇的代码常常抓不住重点,从头到尾都读完了,却弄不清每个状态都实现了什么功能。

在修改代码未果的情况下,我决定,与其花时间阅读那么冗长的代码,不如先花时间把吊口通信的协议(尤其是接收模块的操作)吃透,然后尝试自己编写代码,这样代码中的每一步自己都知道是什么意思,出了错解决起来也方便。

通过此次的串口模块程序的编写,我初步掌握了利用状态机编写时序的方法,摒弃了烦琐的条件判断语句(网上部分代码就是如此编写的,十分不规范),十分具有锻炼意义。

从软件调通到实现CPLD和PC机的通信没有花太长时间,于是便开始准备CPLD 和单片机间的通信。

山于两块开发板上的RS232 口均为母口,因此我在网上购买了一根公对公的串口线。

当我迫不及待地将两块板子连接起来时,什么反 应也没有。

我这时有些不知所措,因为CPLD 可以发送数据给PC, PC 也能发送数 据给单片机,波特率都是9600,为什么将两者直接连接就不行了呢?出问题的 值可能有一个地方,那就是我够买的那根公头对公头的串口线。

难道线是断的, 这商家也太不厚道了吧,应该不会。

这时在我脑海中突然浮现出串口通信最基本的那张示意图:认为TxD 与RxD 在传输线中完成 输线里没有完成 起万用表测量了公对公帘口线的两个2脚,发现这两个脚是导通的,也就是说吊口线中没有实现 信号的交义!再对着两块板子的原理图看了一下,TxD 都接的是各自的串口座2 脚,RxD 都接的是各自的串口座3脚,这样的话相当于把两个发送的TxD 管脚连 接在了一起,要实现通信是根本不可能的。

后来在网上一查,原来串口线有直连 线与交义线两种之分,(估讣直连线是单纯做延长用的),而公对公的线没有交 义线,需要定制。

不怕出问题,怕的是出了问题找不到问题的原因,既然找到了原因,就有方 法解决。

于是我来到了创新实验室,先用两根导线将RxD 与TxD 连接起来,并将 两块开发板共地。

打开电源后,按下按键,单片机成功接收到了 CFLD 发送的数据。

这证明了之前的不成功完全是因为硬件电路的问题。

为了使最后的作品方便展示,两根导线显然不够稳定。

于是我将那根公对公 的串口线从中间剪断,其中有10根线,我找到每根线对应是儿针,再将两边的 2针与3针交义连接起来。

山于CPLD 开发板上是将地与1针相连,而单片机开 发板上是将地与5针相连,这两根线需要缠在一起,因此这根线的两头并不等价, 一头固定接单片机,另一头固定接CPLDo这根自制的串口交义线完成后,经过检验无误,我们的串口通信模块算是成 功完成了。

2. 液晶模块、键盘模块的调试液晶模块的调试也并不轻松,起初和大家一样,我们花了很长时间阅读把实 验指导书中给的代码,并把其烧到了板子里进行测试,液晶屏并没有被点亮,于 是我们放弃了修改那冗长的代码,在另一份代码上进行修改。

12. 14〜12. 15学习了 1602液晶屏的控制方法,并修改了一份已有的 verilog代码,将其烧入板子后成功的在液晶屏上显示了u madakangisfromee n o12.27确定了整个程序的框架,编写了键盘模块(可以采集按键、消抖并输出键值),改进了之前编写的液晶模块,使其能够根据键值显示不同的文字。

在这一阶段其实也走了一段小小的弯路。

在我的液品模块中,需要显示的字 符是作为模块的参数的,因此最初我的想法是通过实例化时的参数传递将不同键 值对应的文字传递给液晶模块,因为verilog 中也有现成的参数传递语句,如defparamc但这种想法经实践检验既不可行也不科学:首先,如果你有5种字符串要显 示,你就必须实例化5个液晶显示模块,而这5个module 实例无法公用同样的 输岀,也就是说如果想要这样实现的话还必须在5个module 实例后加一个数据 选择器,这样确实非常的繁琐。

其次,即使实现了,也非常地耗费LEo 因此我 放弃了这样的方案。

后来我还是对module 本身做了修改,将要显示的文本存为不同的parameter, 然后在给显示数据寄存器赋值时,加一个case 语句判断,根据不同的键值选择 不同我之前一直 的交义应该是 的,但会不会传 呢?于是我拿的parameter,成功实现了通过按键改变屛幕显示的功能。

3.倒计时器的调试本来倒计时器的调试倒是一帆风顺,只是在添加暂停与停止功能时,无意中改动了一个变量的类型,将原先的int型改为了unsigned char,导致参数调用时不匹配,讣数减到0时会数码管就开始出现乱码了。

不过后来还是发现了这个问题。

4.蜂鸣器的调试采用6MHz作为基频,山于所选歌曲的最短的音符为四分音符,如果将全音符的持续时间设为Is的话,还需要一个4Hz的分频即可。