LH28F320S3-L130中文资料

和利时LM可编程控制器硬件手册

第1章从硬件体系结构、编程软件、快速应用等各个方面对LM小型PLC作了概述性介绍。

第2、3章主要针对CPU模块、扩展模块的技术规格、端子定义与接线示意图及等效电路进行 了详细阐述。

目录

第 1 章 概述 .......................................................................................................... 1

1.1 概述................................................................................................................................................... 1 1.2 硬件体系结构................................................................................................................................... 1

本手册仅供商业用户阅读、查询,在未得到北京和利时系统工程股份有限公司特别授权的 情况下,无论出于何种原因和目的,均不得用任何电子或机械方法,以任何形式复制和传递本 手册的内容。否则本公司将依法追究法律责任。

我们已核对本手册中的内容、图表与所述硬件设备相符,但误差难以避免,并不能保证完 全一致,还恳请广大用户批评指正。同时,我们会定期对手册的内容、图表进行检查、修改和 维护,恕不另行通知。

AS320电梯专用变频器使用说明书V2.09

本使用说明书对 AS320 系列电梯专用变频器的安装、使用、功能参数设定、 维护及故障处理进行了全面系统的阐述。本手册可作为采用 AS320 系列电梯专用 变频器进行电梯控制系统设计的参考资料,也可作为系统安装、调试、维护的使用 资料。

为了确保能够正确的安装、使用本变频器,请在使用前仔细阅读本使用说明 书。

重要 用户需要遵守、重点注意的部分。

V

目录

第一章 变频器使用须知 ......................................................................................................................... 1

简便、快速的电梯调试方法

变频器配线完成后,电梯调试的方便与否至关重要。为完成变频器调试,操作 人员往往要耗费大量的时间和精力来设置一大批参数和进行复杂的操作。由于本变 频器是电梯专用,所以驱动电梯调试极其简便、快速,只需以下 3 步骤。

1. 参数设定 a) 先通过操作器将所有参数恢复到出厂设置值; b) 再根据电机铭牌数据设置电机参数,以及编码器参数。 2. 运行方向调整 通过操作器就能看清编码器接线和电机运行方向的正确与否,如发现错误,可 简易地通过参数调整。 3. 舒适感调整 a) 即使不用任何参数改动,使用出厂设定值就能达到相当程度的舒适感; b) 如再作细微 PID 调节器调整,就可获得最佳舒适感。

第二章 型号与规格 ................................................................................................................................. 1

tms320f28335中文数据手册介绍

wj28产品说明书

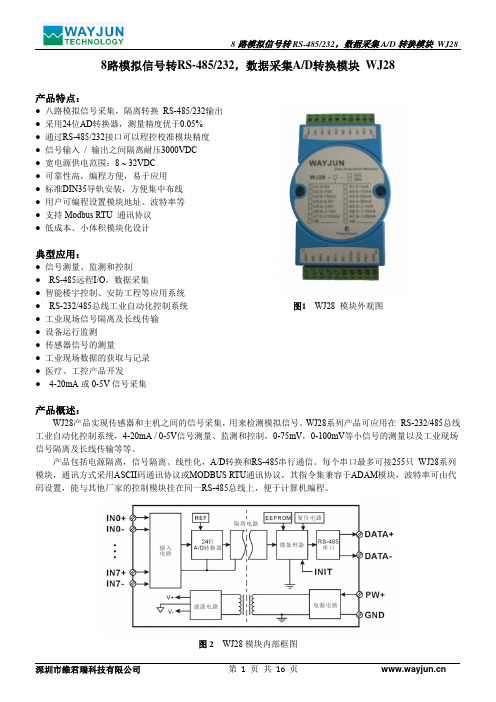

8路模拟信号转RS-485/232,数据采集A/D转换模块 WJ28产品特点:●八路模拟信号采集,隔离转换 RS-485/232输出●采用24位AD转换器,测量精度优于0.05%●通过RS-485/232接口可以程控校准模块精度●信号输入 / 输出之间隔离耐压3000VDC●宽电源供电范围:8 ~ 32VDC●可靠性高,编程方便,易于应用●标准DIN35导轨安装,方便集中布线●用户可编程设置模块地址、波特率等●支持Modbus RTU 通讯协议●低成本、小体积模块化设计典型应用:●信号测量、监测和控制●RS-485远程I/O,数据采集●智能楼宇控制、安防工程等应用系统●RS-232/485总线工业自动化控制系统图1 WJ28 模块外观图●工业现场信号隔离及长线传输●设备运行监测●传感器信号的测量●工业现场数据的获取与记录●医疗、工控产品开发●4-20mA或0-5V信号采集产品概述:WJ28产品实现传感器和主机之间的信号采集,用来检测模拟信号。

WJ28系列产品可应用在 RS-232/485总线工业自动化控制系统,4-20mA / 0-5V信号测量、监测和控制,0-75mV,0-100mV等小信号的测量以及工业现场信号隔离及长线传输等等。

产品包括电源隔离,信号隔离、线性化,A/D转换和RS-485串行通信。

每个串口最多可接255只 WJ28系列模块,通讯方式采用ASCII码通讯协议或MODBUS RTU通讯协议,其指令集兼容于ADAM模块,波特率可由代码设置,能与其他厂家的控制模块挂在同一RS-485总线上,便于计算机编程。

图2 WJ28模块内部框图WJ28系列产品是基于单片机的智能监测和控制系统,所有的用户设定的校准值,地址,波特率,数据格式,校验和状态等配置信息都储存在非易失性存储器EEPROM里。

WJ28系列产品按工业标准设计、制造,信号输入 / 输出之间隔离,可承受3000VDC隔离电压,抗干扰能力强,可靠性高。

LH系列螺杆式水冷冷水机组(R134a)

第三章 LH系列螺杆式水冷冷水机组(R134a)一、产品概述1、产品特点在水冷冷水机市场上,效率和运行成本越来越为人们所关注,格力螺杆式水冷式冷水机组(R134a)系列采用环保冷媒R134a,高效节能,运行稳定可靠,在提高性能方面持续改进,名义工况下的制冷量范围为:180~1400KW,可广泛适用于各类办公楼宇、医院、学校、商场,也可应用于生产工艺流程的降温。

1.1 高效节能◆采用满液式蒸发方式A、蒸发器中的制冷剂分布更均匀,温度场优化换热效率更高。

B、满液式蒸发器,大幅度地提高了机组的蒸发温度,提升了机组的换热效率。

通过与高性能高可靠性的专用螺杆压缩机的搭配,大大提升了机组的制冷量和能效比。

◆新型节流方式A、自动计算最佳能效比值,并快速调节实际值,按需输出,进一步优化控制逻辑。

B、电子膨胀阀更精确地调节制冷流量及蒸发器液位的变化。

C、机组的部分负荷效率始终保持最高,运行范围更宽。

◆多机并联、部分负荷效率更高A、由于大部分运行时间处于非设计工况,在选择冷水机组时应注意:它不但要满足满负荷的设计要求,并且在较低负荷时,以及冷却塔水温较低时也能高效运行,相同满负荷能效比的冷水机组,在部分负荷运行费用有时会相差10%以上。

B、格力满液式多机并联技术,可设置双机并联运行,也可设置单机独立运行,部分负荷运行时效率更高。

◆容量调节与机组负荷匹配A、可根据用户需求进行有级或无级容量调节。

B、压缩机在最小负荷位置启动,可对制冷量进行无级调节。

获取中国首批冷水机组节能认证证书满液式蒸发效果图C、无级滑阀调节强制输气,与实际负荷完全匹配。

1.2 高可靠性◆严格实验流程A、螺杆机组在线检测时,通过具有业内最先进的在线检测系统(合肥机械研究所研制的,具有条形码管理系统以及采用电脑全自动检测及判定的超大型在线检测系统)。

B、严格按照国标GB/T10870、GB/T18430等的要求执行。

◆可靠的回油系统测试图A、专门针对满液式冷水机组系统,设置低油位保护控制,完全杜绝了压缩机少油损坏的可能性。

意大利卡莱菲流量平衡阀130型说明书

意大利卡莱菲流量平衡阀130型功能静态流量平衡阀运用于水力系统,它精确地平衡系统每个支路或者每个末端的流量。

循环系统的平衡是保证系统按设计工况正确运行的前提,只有在此前提下系统才能提供最大的热舒适度、最大限度地降低能耗。

螺纹连接型的平衡阀阀体内部采用文氏流量计,使流量调节更精确、流量检测更方便。

产品范围130型 文氏流量计型流量平衡阀,螺纹连接型 口径 :DN 15 (1/2"), DN 20 (3/4"), DN 25 (1"), DN 32 (1 1/4"), DN 40 (1 1/2"), DN 50 (2")130 型 流量平衡阀,法兰连接型 口径:DN 65, DN 80, DN 100, DN 125, DN 150, DN 200, DN 250, DN 300130型 文氏流量计型平衡阀配套保温壳保温壳的构造特征材质材质: PE-X 密封发泡厚度: 15 mm 密度: -内部:30 kg/m3 -外部:80 kg/m3导热系数(ISO2581): - 0℃:0.038 W/(m•K)- 40℃: 0.045 W/(m•K)湿阻因子(DIN52615): >1,300工作温度范围: 0~100℃防火等级(DIN4102): B2级尺寸图130060 130080 130100 130120 1301501315.5213245 ADN 65DN 80DN 100DN 125DN 150B290310350400480C225235245350380130200 130250 130300115160210 DN 200DN 250DN 300600730850480525535编号重量 (kg)系统平衡的优点经过流量平衡的系统其主要优点如下:1. 系统的末端在供暖、制冷及除湿状态下正常工作,不会造成能源浪费,舒适度得到保证。

LB132 变送器说明书

目录 ............................................................................................................................................................................... - 1 一、概述 ....................................................................................................................................................................... - 2 二、LB-132 变送器结构............................................................................................................................................. - 3 三、变送器性能指标 ................................................................................................................................................... - 3 3.1、密度性能指标(仅液体) ..........................................................................................................

济南达科力华机械设备有限公司电动调节阀产品手册说明书

济南达科力华机械设备有限公司(第五版)(提示:请妥善保管,以备急需,遗失不补!)电动调节阀产品手册书中国·山东电话:0531-6869 0668济南达科力华机械设备有限公司主要从事供热节能方面的技术及产品开发;水处理等行业和领域的技术研发、设备制造和工程实施、方案设计、技术服务等工作。

包括西门子温控阀、西门子温控器西门子电动执行器等相关技术咨询、暖通及热能设备销售、安装与调试,西门子温控阀可实现无人值守,超温报警,温度补偿等人性化控制。

济南达科力华机械设备有限公司还是依托省农科院兴办的集科、工、贸于一体的科技型高新技术企业,在工厂化养殖自动化控制领域(食用菌、花卉等)、食品加工等与省农科院深度合作,在温度、湿度、气体浓度、压力等自动控制上取得良好的效果,得到广泛认可。

公司同时代理德国西门子楼宇科技产品,为暖通空调设备厂家及工程公司提供售前、售中和售后服务工作,为广大用户提供优良产品和优质服务。

公司秉承“诚信至上,以人为本,效率优先,服务社会”的办企原则,以优质的产品和高效的售后服务回报广大客户。

路漫漫其修远兮,吾将上下而求索。

孜孜耕、默默前行,是我们永远不变的敬业精神;自强不息,敢于亮剑是我们永远不变的创业精神。

电动温控阀,自力式温控阀,电动二通阀,电动三通阀电动调节阀,减温减压装置,电动减压阀,全自动软化水电动压差旁通阀,高频电子水处理,楼宇自控系统、工厂化养殖自控系统解决方案,工业生产温控、压控、气控等系统解决方案。

企业宗旨:一切以用户体验为导向,以用户价值为中心!企业文化:一步一步,脚踏实地绿色环保节能高效一、产品介绍根据现场情况的不同,选用达科力华电动阀,能够满足空调制冷、换热供暖、通风等控制系统的需要,达到调节温度、压力、湿度及流量的目的。

也广泛适用于石油、化工、冶金、纺织、印染等工业现场的自动控制。

二、产品特点达科力华电动阀采用进口执行器、控制器、传感器,阀门采用平衡式单阀座结构,能够抵消阀门内部高压降产生的推力,有效解决高压现场关断力的问题,降低了执行器的负荷,延长了机器寿命。

RC28F128J3A-150资料

3 Volt Intel ® StrataFlash ™ Memory28F128J3A, 28F640J3A, 28F320J3A (x8/x16)Preliminary DatasheetProduct FeaturesCapitalizing on Intel’s 0.25 µ generation two-bit-per-cell technology, second generation Intel ®StrataFlash ™ memory products provide 2X the bits in 1X the space, with new features for mainstream performance. Offered in 128-Mbit (16-Mbyte), 64-Mbit, and 32-Mbit densities, these devices bring reliable, two-bit-per-cell storage technology to the flash market segment.Benefits include: more density in less space, high-speed interface, lowest cost-per-bit NOR devices, support for code and data storage, and easy migration to future devices.Using the same NOR-based ETOX ™ technology as Intel ’s one-bit-per-cell products, Intel StrataFlash memory devices take advantage of over one billion units of manufacturing experience since 1987. As a result, Intel StrataFlash components are ideal for code and data applications where high density and low cost are required. Examples include networking, telecommunications, digital set top boxes, audio recording, and digital imaging.By applying FlashFile ™ memory family pinouts, Intel StrataFlash memory components allow easy design migrations from existing Word-Wide FlashFile memory (28F160S3 and 28F320S3), and first generation Intel StrataFlash memory (28F640J5 and 28F320J5) devices.Intel StrataFlash memory components deliver a new generation of forward-compatible software support. By using the Common Flash Interface (CFI) and the Scalable Command Set (SCS), customers can take advantage of density upgrades and optimized write capabilities of future Intel StrataFlash memory devices. Manufactured on Intel ® 0.25 micron ETOX ™ VI process technology, Intel StrataFlash memory provides the highest levels of quality and reliability.sHigh-Density Symmetrically-Blocked Architecture—128 128-Kbyte Erase Blocks (128 M)—64 128-Kbyte Erase Blocks (64 M)—32 128-Kbyte Erase Blocks (32 M)sHigh Performance Interface Asynchronous Page Mode Reads—110/25 ns Read Access Time (32 M)—120/25 ns Read Access Time (64 M)—150/25 ns Read Access Time (128 M)s 2.7 V –3.6 V V CC Operation s128-bit Protection Register—64-bit Unique Device Identifier—64-bit User Programmable OTP Cells sEnhanced Data Protection Features Absolute Protection with V PEN = GND —Flexible Block Locking—Block Erase/Program Lockout during Power TransitionssPackaging—56-Lead TSOP Package—64-Ball Intel ® Easy BGA PackagesCross-Compatible Command Support Intel Basic Command Set—Common Flash Interface —Scalable Command Set s32-Byte Write Buffer—6 µs per Byte Effective Programming Times12.8M Total Min. Erase Cycles (128 Mbit)6.4M Total Min. Erase Cycles (64 Mbit)3.2M Total Min. Erase Cycles (32 Mbit)—100K Minimum Erase Cycles per Block sAutomation Suspend Options —Block Erase Suspend to Read —Block Erase Suspend to Program —Program Suspend to Reads0.25 µ Intel ® StrataFlash ™ Memory TechnologyOrder Number: 290667-008April 2001Notice: This document contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.28F128J3A, 28F640J3A, 28F320J3A Contents1.0Product Overview (1)2.0Principles of Operation (6)2.1Data Protection (6)3.0Bus Operations (7)3.1Read (8)3.2Output Disable (8)3.3Standby (8)3.4Reset/Power-Down (8)3.5Read Query (9)3.6Read Identifier Codes (9)3.7Write (9)4.0Command Definitions (9)4.1Read Array Command (13)4.2Read Query Mode Command (13)4.2.1Query Structure Output (13)4.2.2Query Structure Overview (14)4.2.3Block Status Register (15)4.2.4CFI Query Identification String (15)4.2.5System Interface Information (16)4.2.6Device Geometry Definition (17)4.2.7Primary-Vendor Specific Extended Query Table (18)4.3Read Identifier Codes Command (19)4.4Read Status Register Command (20)4.5Clear Status Register Command (22)4.6Block Erase Command (22)4.7Block Erase Suspend Command (22)4.8Write to Buffer Command (23)4.9Byte/Word Program Commands (24)4.10Program Suspend Command (24)4.11Set Read Configuration Command (24)4.11.1Read Configuration (25)4.12Configuration Command (25)4.13Set Block Lock-Bit Commands (26)4.14Clear Block Lock-Bits Command (27)4.15Protection Register Program Command (27)4.15.1Reading the Protection Register (27)4.15.2Programming the Protection Register (27)4.15.3Locking the Protection Register (28)5.0Design Considerations (38)5.1Three-Line Output Control (38)5.2STS and Block Erase, Program, and Lock-Bit Configuration Polling (38)5.3Power Supply Decoupling (38)5.4Input Signal Transitions - Reducing Overshoots and Undershoots When Using28F128J3A, 28F640J3A, 28F320J3A28F128J3A, 28F640J3A, 28F320J3A Revision HistoryDate of Revision Version Description07/07/99-001Original Version08/03/99-002A0–A2 indicated on block diagram09/07/99-003Changed Minimum Block Erase time,I OL, I OH, Page Mode and ByteMode currents. Modified RP# on AC Waveform for Write Operations 12/16/99-004Changed Block Erase time and t AVWHRemoved all references to 5 V I/O operationCorrected Ordering Information, Valid Combinations entriesChanged Min program time to 211 µsAdded DU to Lead Descriptions tableChanged Chip Scale Package to Ball Grid Array PackageChanged default read mode to page modeRemoved erase queuing from Figure 10, Block Erase Flowchart03/16/00-005Added Program Max timeAdded Erase Max timeAdded Max page mode read currentMoved tables to correspond with sectionsFixed typographical errors in ordering information and DC parametertableRemoved V CCQ1 setting and changed V CCQ2/3 to V CCQ1/2Added recommended resister value for STS pinChange operation temperature rangeRemoved note that rp# could go to 14 VRemoved V OL of 0.45 VRemoved V OH of 2.4 VUpdated I CCR Typ valuesAdded Max lock-bit program and lock timesAdded note on max measurements06/26/00-006Updated cover sheet statement of 700 million units to one billion.Corrected Table 10 to show correct maximum program times.Corrected error in Max block program time in section 6.7Corrected typical erase time in section 6.72/15/01-007Updated cover page to reflect 100K minimum erase cycles.Updated cover page to reflect 110 ns 32M read speed.Removed Set Read Configuration command from Table 4.Updated Table 8 to reflect reserved bits are 1-7; not 2-7.Updated Table 16 bit 2 definition from R to PSS.Changed V PENLK Max voltage from 0.8 V to 2.0 V, Section 6.4, DCCharacteristicsUpdated 32Mbit Read Parameters R1, R2 and R3 to reflect 110ns, Sec-tion 6.5, AC Characteristics–Read-Only Operations (1,2)Updated write parameter W13 (t WHRL) from 90 ns to 500 ns, Section6.6, AC Characteristics–Write OperationsUpdated Max. Program Suspend Latency W16 (t WHRH1) from 30 to 75µs, Section 6.7, Block Erase, Program, and Lock-Bit Configuration Per-formance (1,2,3)04/13/01-008Revised Section 7.0, Ordering Information28F128J3A, 28F640J3A, 28F320J3A 1.0Product OverviewThe 0.25 µ 3 Volt Intel StrataFlash memory family contains high-density memories organized as16 Mbytes or 8 Mwords (128-Mbit), 8 Mbytes or 4 Mwords (64-Mbit), and 4 Mbytes or 2 Mwords(32-Mbit). These devices can be accessed as 8- or 16-bit words. The 128-Mbit device is organizedas one-hundred-twenty-eight 128-Kbyte (131,072 bytes) erase blocks. The 64-Mbit device isorganized as sixty-four 128-Kbyte erase blocks while the 32-Mbits device contains thirty-two128-Kbyte erase blocks. Blocks are selectively and individually lockable and unlockable in-system. A 128-bit protection register has multiple uses, including unique flash deviceidentification.The device’s optimized architecture and interface dramatically increases read performance bysupporting page-mode reads. This read mode is ideal for non-clock memory systems.A Common Flash Interface (CFI) permits software algorithms to be used for entire families ofdevices. This allows device-independent, JEDEC ID-independent, and forward- and backward-compatible software support for the specified flash device families. Flash vendors can standardizetheir existing interfaces for long-term compatibility.Scalable Command Set (SCS) allows a single, simple software driver in all host systems to workwith all SCS-compliant flash memory devices, independent of system-level packaging (e.g.,memory card, SIMM, or direct-to-board placement). Additionally, SCS provides the highestsystem/device data transfer rates and minimizes device and system-level implementation costs.A Command User Interface (CUI) serves as the interface between the system processor andinternal operation of the device. A valid command sequence written to the CUI initiates deviceautomation. An internal Write State Machine (WSM) automatically executes the algorithms andtimings necessary for block erase, program, and lock-bit configuration operations.A block erase operation erases one of the device’s 128-Kbyte blocks typically within one second—independent of other blocks. Each block can be independently erased 100,000 times. Block erasesuspend mode allows system software to suspend block erase to read or program data from anyother block. Similarly, program suspend allows system software to suspend programming (byte/word program and write-to-buffer operations) to read data or execute code from any other blockthat is not being suspended.Each device incorporates a Write Buffer of 32 bytes (16 words) to allow optimum programmingperformance. By using the Write Buffer, data is programmed in buffer increments. This feature canimprove system program performance more than 20 times over non-Write Buffer writes.Individual block locking uses block lock-bits to lock and unlock blocks. Block lock-bits gate blockerase and program operations. Lock-bit configuration operations set and clear lock-bits (Set BlockLock-Bit and Clear Block Lock-Bits commands).The status register indicates when the WSM’s block erase, program, or lock-bit configurationoperation is finished.The STS (STATUS) output gives an additional indicator of WSM activity by providing both ahardware signal of status (versus software polling) and status masking (interrupt masking forbackground block erase, for example). Status indication using STS minimizes both CPU overheadand system power consumption. When configured in level mode (default mode), it acts as a RY/BY# pin. When low, STS indicates that the WSM is performing a block erase, program, or lock-bitconfiguration. STS-high indicates that the WSM is ready for a new command, block erase is28F128J3A, 28F640J3A, 28F320J3A28F128J3A, 28F640J3A, 28F320J3A28F128J3A, 28F640J3A, 28F320J3A2.0Principles of OperationThe Intel StrataFlash memory devices include an on-chip WSM to manage block erase, program,and lock-bit configuration functions. It allows for 100% TTL-level control inputs, fixed powersupplies during block erasure, program, lock-bit configuration, and minimal processor overheadwith RAM-like interface timings.After initial device power-up or return from reset/power-down mode (see Section 3.0, “BusOperations” on page7), the device defaults to read array mode. Manipulation of external memorycontrol pins allows array read, standby, and output disable operations.Read array, status register, query, and identifier codes can be accessed through the CUI (CommandUser Interface) independent of the V PEN voltage. V PENH on V PEN enables successful blockerasure, programming, and lock-bit configuration. All functions associated with altering memorycontents—block erase, program, lock-bit configuration—are accessed via the CUI and verifiedthrough the status register.Commands are written using standard micro-processor write timings. The CUI contents serve asinput to the WSM, which controls the block erase, program, and lock-bit configuration. Theinternal algorithms are regulated by the WSM, including pulse repetition, internal verification, andmargining of data. Addresses and data are internally latched during program cycles.Interface software that initiates and polls progress of block erase, program, and lock-bitconfiguration can be stored in any block. This code is copied to and executed from system RAMduring flash memory updates. After successful completion, reads are again possible via the ReadArray command. Block erase suspend allows system software to suspend a block erase to read orprogram data from/to any other block. Program suspend allows system software to suspend aprogram to read data from any other flash memory array location.2.1Data ProtectionDepending on the application, the system designer may choose to make the V PEN switchable(available only when memory block erases, programs, or lock-bit configurations are required) orhardwired to V PENH. The device accommodates either design practice and encouragesoptimization of the processor-memory interface.When V PEN≤ V PENLK, memory contents cannot be altered. The CUI’s two-step block erase, byte/word program, and lock-bit configuration command sequences provide protection from unwantedoperations even when V PENH is applied to V PEN. All program functions are disabled when V CC isbelow the write lockout voltage V LKO or when RP# is V IL. The device’s block locking capabilityprovides additional protection from inadvertent code or data alteration by gating erase and programoperations.3.0Bus OperationsThe local CPU reads and writes flash memory in-system. All bus cycles to or from the flash memory conform to standard microprocessor bus cycles.NOTE:For single-chip applications, CE 2 and CE 1 can be strapped to GND.Figure 4. Memory MapTable 2. Chip Enable Truth TableCE 2CE 1CE 0DEVICE V IL V IL V IL Enabled V IL V IL V IH Disabled V IL V IH V IL Disabled V IL V IH V IH Disabled V IH V IL V IL Enabled V IH V IL V IH Enabled V IH V IH V IL Enabled V IHV IHV IHDisabled4.0Command DefinitionsWhen the V PEN voltage ≤ V PENLK, only read operations from the status register, query, identifiercodes, or blocks are enabled. Placing V PENH on V PEN additionally enables block erase, program,and lock-bit configuration operations.Device operations are selected by writing specific commands into the CUI. Table 4 defines thesecommands.Table 6. Example of Query Structure Output of a x16- and x8-Capable DeviceWord Addressing Byte AddressingOffset Hex Code Value Offset Hex Code ValueA15–A0 D15–D0A7–A0 D7–D00010h0051“Q”20h51“Q”0011h0052“R”21h51“Q”0012h0059“Y”22h52“R”0013h P_ID LO PrVendor23h52“R”0014h P_ID HI ID #24h59“Y”0015h P LO PrVendor25h59“Y”0016h P HI TblAdr26h P_ID LO PrVendor0017h A_ID LO AltVendor27h P_ID LO ID #0018h A_ID HI ID #28h P_ID HI ID #... ... ...... ... ...Table 8. Block Status RegisterOffset Length Description Address Value(BA+2)h(1)1Block Lock Status Register BA+2:--00 or --01BSR.0 Block Lock Status0 = Unlocked1 = LockedBA+2:(bit 0): 0 or 1BSR 1–7: Reserved for Future Use BA+2:(bit 1–7): 0 Table 9. CFI IdentificationOffset Length Description Add.HexCodeValue10h3Query-unique ASCII string “QRY”10--51“Q”11:--52“R”12:--59“Y”13h2Primary vendor command set and control interface ID code.13:--01 16-bit ID code for vendor-specified algorithms14:--00 15h2Extended Query Table primary algorithm address 15:--3116:--00Table 10. System Interface InformationOffset Length Description Add.HexCodeValue1Bh1V CC logic supply minimum program/erase voltagebits 0–3 BCD 100 mVbits 4–7 BCD volts1B:--27 2.7 V1Ch1V CC logic supply maximum program/erase voltagebits 0–3 BCD 100 mVbits 4–7 BCD volts1C:--36 3.6 V1Dh1V PP [programming] supply minimum program/erase voltagebits 0–3 BCD 100 mVbits 4–7 HEX volts1D:--000.0 V1Eh1V PP [programming] supply maximum program/erase voltagebits 0–3 BCD 100 mVbits 4–7 HEX volts1E:--000.0 V1Fh1“n” such that typical single word program time-out = 2n µs1F:--07128 µs 20h1“n” such that typical max. buffer write time-out = 2n µs 20:--07128 µs 21h1“n” such that typical block erase time-out = 2n ms21:--0A 1 s 22h1“n” such that typical full chip erase time-out = 2n ms22:--00NA23h1“n” such that maximum word program time-out = 2n timestypical23:--04 2 ms24h1“n” such that maximum buffer write time-out = 2n times typical24:--04 2 ms 25h1“n” such that maximum block erase time-out = 2n times typical25:--0416 s 26h1“n” such that maximum chip erase time-out = 2n times typical26:--00NA28h2Flash device interface: x8 async x16 async x8/x16 async28:--02x8/ x1628:00,29:00 28:01,29:00 28:02,29:0029:--002Ah2“n” such that maximum number of bytes in write buffer = 2n2A:--05322B:--002Ch1Number of erase block regions within device:1. x = 0 means no erase blocking; the device erases in “bulk”2. x specifies the number of device or partition regions with one ormore contiguous same-size erase blocks3. Symmetrically blocked partitions have one blocking region4. Partition size = (total blocks) x (individual block size)2C:--0112Dh4Erase Block Region 1 Information 2D: bits 0–15 = y, y+1 = number of identical-size erase blocks2E: bits 16–31 = z, region erase block(s) size are z x 256 bytes2F:30:Address32 Mbit64 Mbit128 Mbit 27:--16--17--18 28:--02--02--02 29:--00--00--00 2A:--05--05--05 2B:--00--00--00 2C:--01--01--01 2D:--1F--3F--7F 2E:--00--00--00 2F:--00--00--00 30:--02--02--02Table 14. Burst Read InformationOffset(1) P = 31h LengthDescription(Optional Flash Features and Commands)Add.HexCodeValue(P+13)h1Page Mode Read capabilitybits 0–7 = “n” such that 2n HEX value represents the numberof read-page bytes. See offset 28h for device word width todetermine page-mode data output width. 00h indicates noread page buffer.44:--038 byte(P+14)h1Number of synchronous mode read configuration fields thatfollow. 00h indicates no burst capability.45:--000(P+15)h Reserved for future use46:• Block Is Unlocked DQ0 = 0• Block Is Locked DQ0 = 1• Reserved for Future Use DQ1–7Table 21. Byte-Wide Protection Register AddressingByte Use A8A7A6A5A4A3A2A1LOCK Both10000000LOCK Both10000000 0Factory100000011Factory100000012Factory100000103Factory100000104Factory100000115Factory100000116Factory100001007Factory100001008User100001019User10000101A User10000110B User10000110C User10000111D User10000111E User10001000F User100010005.0Design Considerations5.1Three-Line Output ControlThe device will often be used in large memory arrays. Intel provides five control inputs (CE0, CE1,CE2, OE#, and RP#) to accommodate multiple memory connections. This control provides for:a.Lowest possible memory power dissipation.plete assurance that data bus contention will not occur.To use these control inputs efficiently, an address decoder should enable the device (see Table 2)while OE# should be connected to all memory devices and the system’s READ# control line. Thisassures that only selected memory devices have active outputs while de-selected memory devicesare in standby mode. RP# should be connected to the system POWERGOOD signal to preventunintended writes during system power transitions. POWERGOOD should also toggle duringsystem reset.5.2STS and Block Erase, Program, and Lock-Bit ConfigurationPollingSTS is an open drain output that should be connected to V CCQ by a pull-up resistor to provide ahardware method of detecting block erase, program, and lock-bit configuration completion. It isrecommended that a 2.5k resister be used between STS# and V CCQ. In default mode, it transitionslow after block erase, program, or lock-bit configuration commands and returns to High Z whenthe WSM has finished executing the internal algorithm. For alternate configurations of the STSpin, see the Configuration command.STS can be connected to an interrupt input of the system CPU or controller. It is active at all times.STS, in default mode, is also High Z when the device is in block erase suspend (with programminginactive), program suspend, or in reset/power-down mode.5.3Power Supply DecouplingFlash memory power switching characteristics require careful device decoupling. System designersare interested in three supply current issues; standby current levels, active current levels andtransient peaks produced by falling and rising edges of CE0, CE1, CE2, and OE#. Transient currentmagnitudes depend on the device outputs’ capacitive and inductive loading. Two-line control andproper decoupling capacitor selection will suppress transient voltage peaks. Since Intel StrataFlashmemory devices draw their power from three V CC pins (these devices do not include a V PP pin), itis recommended that systems without separate power and ground planes attach a 0.1 µF ceramiccapacitor between each of the device’s three V CC pins (this includes V CCQ) and ground. Thesehigh-frequency, low-inductance capacitors should be placed as close as possible to package leadson each Intel StrataFlash memory device. Each device should have a 0.1 µF ceramic capacitorconnected between its V CC and GND. These high-frequency, low inductance capacitors should beplaced as close as possible to package leads. Additionally, for every eight devices, a 4.7 µFelectrolytic capacitor should be placed between V CC and GND at the array’s power supplyconnection. The bulk capacitor will overcome voltage slumps caused by PC board traceinductance.6.0Electrical Specifications6.1Absolute Maximum RatingsParameter Maximum Rating Temperature under Bias Expanded–25 °C to +85 °CStorage Temperature–65 °C to +125 °CVoltage On Any Pin –2.0 V to +5.0 V(1)Output Short Circuit Current100 mA(2)NOTES:1.All specified voltages are with respect to GND. Minimum DC voltage is –0.5 V on input/output pins and–0.2V on V CC and V PEN pins. During transitions, this level may undershoot to –2.0 V for periods <20 ns.Maximum DC voltage on input/output pins, V CC, and V PEN is V CC +0.5 V which, during transitions, mayovershoot to V CC +2.0 V for periods <20 ns.2.Output shorted for no more than one second. No more than one output shorted at a time.NOTICE: This datasheet contains preliminary information on new products in production. The specifications aresubject to change without notice. Verify with your local Intel Sales office that you have the latest datasheet beforefinalizing a design.Warning:Stressing the device beyond the “Absolute Maximum Ratings” may cause permanent damage.These are stress ratings only. Operation beyond the “Operating Conditions” is not recommendedand extended exposure beyond the “Operating Conditions” may affect device reliability.Symbol Parameter(1)Typ Max Unit Condition C IN Input Capacitance68pF V IN = 0.0 VC OUT Output Capacitance812pF V OUT = 0.0 VFigure 15. Transient Input/Output Reference Waveform for V CCQ = 3.0 V–3.6 V or V CCQ = 2.7 V–3.6 VTest Configuration C L (pF) V CCQ = V CC = 3.0 V−3.6 V30V CCQ = V CC = 2.7 V−3.6 V30。

SAMPO HX-S131HL换气机 说明书

Simple good life, Sampo

安裝位置與準備

三.牆 壁 和 天 花 板 上 開 孔 1 .在 浴 室 靠 近 排 風 口的 牆 壁 上 開 一 個 直 徑1 2 5 m m的 圓 孔 ,將 本機 內附 之通 風罩 裝在 牆壁上, 注意依其上標示的箭頭方向朝上,保證通風罩的葉片是閉合的,通風罩和牆體之間用水泥 或海棉等填充物填充。 2 .先 將 內 附 之 抱 箍 套入 通 風 管 , 再 將 其 一 頭 套 在 通 風 罩 上, 用抱 箍固 定。 如(圖一)

額定電壓 AC110V/60Hz

消耗功率 1310W

請使用指定專用的燈泡或其他附合電壓規格類型的燈泡以免影響使用效 果甚至引發危險

13

10

11

使用方法

本 機 為 家 庭 浴 室 取 暖 專 用 機 具.有 交 換 空 氣;乾 燥 浴 室,照 明 等 功 能. 操 作 步 驟 說 明:

1.換 氣:換 氣 按 鑑 按 一 下 為 弱,再 按 一 下 為 強,第 三 下 轉 為 關,依 此 操 作 循 環. 2.暖 房:暖 房 按 鑑 按 一 下 為 涼 風,再 按 一 下 為 溫 風,按 第 三 下 為 浴 室 乾 燥,按 第 四 下 轉

圖一

填充物 排風口

通風管

抱箍 牆壁

天花板

支撐架

● 通 風 罩 開 口 位 置 請 保 持 向 上. ● 通 風 罩 的安 裝 並 非 強 制 式 的 配 件. ● 通 風 管 不 可 與 熱 水 器 或 排 油 煙 機 之 通 風 口共 用,以避 免因 而導 入骯 髒且 具危 害

的 氣 體 致 有 害 人 體 健 康.

●請勿加裝非本產品所提供的附件,以免造成損壞。 ●若電器功能不能正常運作時,必須由本公司服務部門或具有類似資格人員維修更換

LH28F320BFB-PTTL60资料

• Handle this document carefully for it contains material protected by international copyright law. Any reproduction, full or in part, of this material is prohibited without the express written permission of the company.• When using the products covered herein, please observe the conditions written herein and the precautions outlined in the following paragraphs. In no event shall the company be liable for any damages resulting from failure to strictly adhere to these conditions and precautions.(1) The products covered herein are designed and manufactured for the following application areas. When using theproducts covered herein for the equipment listed in Paragraph (2), even for the following application areas, be sure to observe the precautions given in Paragraph (2). Never use the products for the equipment listed in Paragraph(3).• Office electronics• Instrumentation and measuring equipment• Machine tools• Audiovisual equipment• Home appliance• Communication equipment other than for trunk lines(2) Those contemplating using the products covered herein for the following equipment which demands highreliability, should first contact a sales representative of the company and then accept responsibility for incorporating into the design fail-safe operation, redundancy, and other appropriate measures for ensuring reliability and safety of the equipment and the overall system.• Control and safety devices for airplanes, trains, automobiles, and other transportation equipment• Mainframe computers• Traffic control systems• Gas leak detectors and automatic cutoff devices• Rescue and security equipment• Other safety devices and safety equipment, etc.(3) Do not use the products covered herein for the following equipment which demands extremely high performancein terms of functionality, reliability, or accuracy.• Aerospace equipment• Communications equipment for trunk lines• Control equipment for the nuclear power industry• Medical equipment related to life support, etc.(4) Please direct all queries and comments regarding the interpretation of the above three Paragraphs to a salesrepresentative of the company.• Please direct all queries regarding the products covered herein to a sales representative of the company.PAGE 0.8mm pitch 48-Ball CSP Pinout (3)Pin Descriptions (4)Simultaneous Operation ModesAllowed with Four Planes (5)Memory Map (6)Identifier Codes and OTP Addressfor Read Operation (7)Identifier Codes and OTP Address forRead Operation on Partition Configuration (7)OTP Block Address Map for OTP Program (8)Bus Operation (9)Command Definitions (10)Functions of Block Lock and Block Lock-Down (12)Block Locking State Transitions uponCommand Write (12)Block Locking State Transitions uponWP# Transition (13)Status Register Definition (14)PAGE Extended Status Register Definition (15)Partition Configuration Register Definition (16)Partition Configuration (16)1 Electrical Specifications (17)1.1 Absolute Maximum Ratings (17)1.2 Operating Conditions (17)1.2.1 Capacitance (18)1.2.2 AC Input/Output Test Conditions (18)1.2.3 DC Characteristics (19)1.2.4 AC Characteristics- Read-Only Operations (21)1.2.5 AC Characteristics- Write Operations (25)1.2.6 Reset Operations (27)1.2.7 Block Erase, Full Chip Erase,(Page Buffer) Program andOTP Program Performance (28)2 Related Document Information (29)CONTENTSLH28F320BFB-PTTL6032Mbit (2Mbit×16)Page Mode Dual Work Flash MEMORY32M density with 16Bit I/O InterfaceHigh Performance Reads• 60/25ns 8-Word Page ModeConfigurative 4-Plane Dual Work• Flexible Partitioning• Read operations during Block Erase or (Page Buffer) Program• Status Register for Each PartitionLow Power Operation• 2.7V Read and Write Operations• V CCQ for Input/Output Power Supply Isolation• Automatic Power Savings Mode Reduces I CCRin Static ModeEnhanced Code + Data Storage• 5µs Typical Erase/Program SuspendsOTP (One Time Program) Block• 4-Word Factory-Programmed Area• 4-Word User-Programmable AreaHigh Performance Program with Page Buffer• 16-Word Page Buffer• 5µs/Word (Typ.) at 12V V PPOperating Temperature 0°C to +70°CCMOS Process (P-type silicon substrate) Flexible Blocking Architecture• Eight 4K-word Parameter Blocks• Sixty-three 32K-word Main Blocks• Top Parameter LocationEnhanced Data Protection Features• Individual Block Lock and Block Lock-Down with Zero-Latency• All blocks are locked at power-up or device reset.• Absolute Protection with V PP≤V PPLK• Block E rase, Full Chip E rase, (Page Buffer) Word Program Lockout during Power TransitionsAutomated Erase/Program Algorithms• 3.0V Low-Power 11µs/Word (Typ.)Programming• 12V No Glue Logic 9µs/Word (Typ.)Production Programming and 0.5s Erase (Typ.)Cross-Compatible Command Support• Basic Command Set• Common Flash Interface (CFI)Extended Cycling Capability• Minimum 100,000 Block Erase Cycles0.8mm pitch 48-Ball CSPETOX TM* Flash TechnologyNot designed or rated as radiation hardenedThe product, which is 4-Plane Page Mode Dual Work (Simultaneous Read while Erase/Program) Flash memory, is a low power, high density, low cost, nonvolatile read/write storage solution for a wide range of applications. The product can operate at V CC=2.7V-3.6V and V PP=1.65V-3.6V or 11.7V-12.3V. Its low voltage operation capability greatly extends battery life for portable applications.The product provides high performance asynchronous page mode. It allows code execution directly from Flash, thus eliminating time consuming wait states. Furthermore, its newly configurative partitioning architecture allows flexible dual work operation.The memory array block architecture utilizes Enhanced Data Protection features, and provides separate Parameter and Main Blocks that provide maximum flexibility for safe nonvolatile code and data storage.Fast program capability is provided through the use of high speed Page Buffer Program.Special OTP (One Time Program) block provides an area to store permanent code such as a unique number.* ETOX is a trademark of Intel Corporation.Table 1.Pin DescriptionsSymbol Type Name and FunctionA0-A20INPUT ADDRESS INPUTS: Inputs for addresses. 32M: A0-A20DQ0-DQ15INPUT/OUTPUT DATA INPUTS/OUTPUTS: Inputs data and commands during CUI (Command User Interface) write cycles, outputs data during memory array, status register, query code, identifier code and partition configuration register code reads. Data pins float to high-impedance (High Z) when the chip or outputs are deselected. Data is internally latched during an erase or program cycle.CE#INPUT CHIP ENABLE: Activates the device’s control logic, input buffers, decoders and sense amplifiers. CE#-high (V IH) deselects the device and reduces power consumption to standby levels.RST#INPUT RESET: When low (V IL), RST# resets internal automation and inhibits write operations which provides data protection. RST#-high (V IH) enables normal operation. After power-up or reset mode, the device is automatically set to read array mode. RST# must be low during power-up/down.OE#INPUT OUTPUT ENABLE: Gates the device’s outputs during a read cycle.WE#INPUT WRITE ENABLE: Controls writes to the CUI and array blocks. Addresses and data are latched on the rising edge of CE# or WE# (whichever goes high first).WP#INPUT WRITE PROTECT: When WP# is V IL, locked-down blocks cannot be unlocked. Erase or program operation can be executed to the blocks which are not locked and not locked-down. When WP# is V IH, lock-down is disabled.RY/BY#OPEN DRAINOUTPUTREADY/BUSY#: Indicates the status of the internal WSM (Write State Machine). Whenlow, WSM is performing an internal operation (block erase, full chip erase, (page buffer)program or OTP program). RY/BY#-High Z indicates that the WSM is ready for newcommands, block erase is suspended and (page buffer) program is inactive, (page buffer)program is suspended, or the device is in reset mode.V PP INPUT MONITORING POWER SUPPLY VOLTAGE: V PP is not used for power supply pin. With V PP≤V PPLK, block erase, full chip erase, (page buffer) program or OTP program cannot be executed and should not be attempted.Applying 12V±0.3V to V PP provides fast erasing or fast programming mode. In this mode, V PP is power supply pin. Applying 12V±0.3V to V PP during erase/program can only be done for a maximum of 1,000 cycles on each block. V PP may be connected to 12V±0.3V for a total of 80 hours maximum. Use of this pin at 12V beyond these limits may reduce block cycling capability or cause permanent damage.V CC SUPPLY DE VICE POWE R SUPPLY (2.7V-3.6V): With V CC≤V LKO, all write attempts to the flash memory are inhibited. Device operations at invalid V CC voltage (see DC Characteristics) produce spurious results and should not be attempted.V CCQ SUPPLY INPUT/OUTPUT POWE R SUPPLY (2.7V-3.6V): Power supply for all input/outputpins.GND SUPPLY GROUND: Do not float any ground pins.NOTES:1. "X" denotes the operation available.2. Configurative Partition Dual Work Restrictions:Status register reflects partition state, not WSM (Write State Machine) state - this allows a status register for each partition. Only one partition can be erased or programmed at a time - no command mands must be written to an address within the block targeted by that command.Table 2.Simultaneous Operation Modes Allowed with Four Planes (1, 2)IF ONE PARTITION IS:THEN THE MODES ALLOWED IN THE OTHER PARTITION IS:Read Array Read ID/OTP Read Status Read Query Word Program Page Buffer Program OTP Program Block Erase Full Chip Erase ProgramSuspendBlockEraseSuspend Read Array X X X X X X X X X Read ID/OTP X X X X X X X X X Read Status X X X X X X XX XX X Read Query X X X X XXXXX Word Program X X X X X Page Buffer Program XXX XXOTP Program X Block E rase XXX XFull Chip Erase X Program Suspend X X X X XBlock Erase SuspendXXXXXXXNOTES:1. The address A 20-A 16 are shown in below table for reading the manufacturer code, device code, device configuration code and OTP data.2. Top parameter device has its parameter blocks in the plane3 (The highest address).3. Block Address = The beginning location of a block address within the partition to which the Read Identifier Codes/OTP command (90H) has been written.DQ 15-DQ 2 are reserved for future implementation.4. PCRC=Partition Configuration Register Code.5. OTP-LK=OTP Block Lock configuration.6. OTP=OTP Block data.NOTES:1. The address to read the identifier codes or OTP data is dependent on the partition which is selected when writing the Read Identifier Codes/OTP command (90H).2. Refer to Table 12 for the partition configuration register.Table 3.Identifier Codes and OTP Address for Read OperationCodeAddress [A 15-A 0]Data [DQ 15-DQ 0]Notes Manufacturer Code Manufacturer Code 0000H 00B0H 1Device CodeTop Parameter Device Code 0001H00B4H 1, 2Block Lock Configuration CodeBlock is Unlocked Block Address + 2DQ 0 = 03Block is LockedDQ 0 = 13Block is not Locked-Down DQ 1 = 03Block is Locked-DownDQ 1 = 13Device Configuration Code Partition Configuration Register 0006H PCRC 1, 4OTPOTP Lock0080H OTP-LK 1, 5OTP 0081-0088HOTP1, 6Table 4.Identifier Codes and OTP Address for Read Operation on Partition Configuration (1) (32M-bit device)Partition Configuration Register (2)Address (32M-bit device)PCR.10PCR.9PCR.8[A 20-A 16]00000H 00100H or 08H 01000H or 10H 10000H or 18H 01100H or 08H or 10H 11000H or 10H or 18H 10100H or 08H or 18H 11100H or 08H or 10H or 18HNOTES:1. Refer to DC Characteristics. When V PP ≤V PPLK , memory contents can be read, but cannot be altered.2. X can be V IL or V IH for control pins and addresses, and V PPLK or V PPH1/2 for V PP . See DC Characteristics for V PPLK and V PPH1/2 voltages.3. RST# at GND±0.2V ensures the lowest power consumption.4. Command writes involving block erase, full chip erase, (page buffer) program or OTP program are reliably executed when V PP =V PPH1/2 and V CC =2.7V-3.6V.5. Refer to Table 6 for valid D IN during a write operation.6. Never hold OE# low and WE# low at the same timing.7. Refer to Appendix of LH28F320BF series for more information about query code.8. RY/BY# is V OL when the WSM (Write State Machine) is executing internal block erase, full chip erase, (page buffer) program or OTP program algorithms. It is High Z during when the WSM is not busy, inblock erase suspend mode (with program and page buffer program inactive), (page buffer) program suspend mode, or reset mode.Table 5.Bus Operation (1, 2)Mode Notes RST#CE#OE#WE#Address V PP DQ 0-15RY/BY# (8)Read Array 6V IH V IL V IL V IH X X D OUT X Output Disable V IH V IL V IH V IH X X High Z X Standby V IH V IH X X X X High ZX Reset3V IL X X X X X High Z High Z Read Identifier Codes/OTP 6V IH V IL V IL V IH See Table 3 and Table 4X See Table 3 and Table 4X Read Query 6,7V IH V IL V IL V IH See AppendixX See Appendix X Write4,5,6V IHV ILV IHV ILXXD INXNOTES:1. Bus operations are defined in Table 5.2. All addresses which are written at the first bus cycle should be the same as the addresses which are written at the second bus cycle.X=Any valid address within the device.PA=Address within the selected partition.IA=Identifier codes address (See Table 3 and Table 4).QA=Query codes address. Refer to Appendix of LH28F320BF series for details.BA=Address within the block being erased, set/cleared block lock bit or set block lock-down bit.WA=Address of memory location for the Program command or the first address for the Page Buffer Program command.OA=Address of OTP block to be read or programmed (See Figure 3).PCRC=Partition configuration register code presented on the address A 0-A 15.3. ID=Data read from identifier codes. (See Table 3 and Table 4).QD=Data read from query database. Refer to Appendix of LH28F320BF series for details.SRD=Data read from status register. See Table 10 and Table 11 for a description of the status register bits.WD=Data to be programmed at location WA. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.OD=Data within OTP block. Data is latched on the rising edge of WE# or CE# (whichever goes high first) during command write cycles.N-1=N is the number of the words to be loaded into a page buffer.4. Following the Read Identifier Codes/OTP command, read operations access manufacturer code, device code, block lock configuration code, partition configuration register code and the data within OTP block (See Table 3 and Table 4).The Read Query command is available for reading CFI (Common Flash Interface) information.5. Block erase, full chip erase or (page buffer) program cannot be executed when the selected block is locked. Unlocked block can be erased or programmed when RST# is V IH .6. Either 40H or 10H are recognized by the CUI (Command User Interface) as the program setup.7. Following the third bus cycle, input the program sequential address and write data of "N" times. Finally, input the any valid address within the target block to be programmed and the confirm command (D0H). Refer to Appendix ofTable mand Definitions (11)CommandBusCycles Req ’d Notes First Bus CycleSecond Bus Cycle Oper (1)Addr (2)Data Oper (1)Addr (2)Data (3)Read Array1Write PA FFH Read Identifier Codes/OTP ≥ 24Write PA 90H Read IA or OA ID or OD Read Query ≥ 24Write PA 98H Read QA QD Read Status Register 2Write PA 70H ReadPASRDClear Status Register 1Write PA 50H Block Erase 25Write BA 20H Write BA D0H Full Chip Erase 25,9Write X 30H Write X D0H Program25,6Write WA 40H or 10H Write WA WD Page Buffer Program ≥ 45,7Write WA E8H WriteWAN-1Block Erase and (Page Buffer) Program Suspend18,9Write PA B0H Block Erase and (Page Buffer) Program Resume 18,9Write PA D0H Set Block Lock Bit 2Write BA 60H Write BA 01H Clear Block Lock Bit 210Write BA 60H Write BA D0H Set Block Lock-down Bit 2Write BA 60H Write BA 2FH OTP Program29Write OA C0H Write OA OD Set Partition Configuration Register2WritePCRC60HWritePCRC04HLH28F320BF series for details.8. If the program operation in one partition is suspended and the erase operation in other partition is also suspended, the suspended program operation should be resumed first, and then the suspended erase operation should be resumed next. 9. Full chip erase and OTP program operations can not be suspended. The OTP Program command can not be accepted while the block erase operation is being suspended.10. Following the Clear Block Lock Bit command, block which is not locked-down is unlocked when WP# is V IL. When WP# is V IH, lock-down bit is disabled and the selected block is unlocked regardless of lock-down configuration.11. Commands other than those shown above are reserved by SHARP for future device implementations and should not be used.NOTES:1. DQ 0=1: a block is locked; DQ 0=0: a block is unlocked.DQ 1=1: a block is locked-down; DQ 1=0: a block is not locked-down.2. Erase and program are general terms, respectively, to express: block erase, full chip erase and (page buffer) program operations.3. At power-up or device reset, all blocks default to locked state and are not locked-down, that is,[001] (WP#=0) or [101] (WP#=1), regardless of the states before power-off or reset operation.4. When WP# is driven to V IL in [110] state, the state changes to [011] and the blocks are automatically locked.5. OTP (One Time Program) block has the lock function which is different from those described above.NOTES:1. "Set Lock" means Set Block Lock Bit command, "Clear Lock" means Clear Block Lock Bit command and "Set Lock-down" means Set Block Lock-Down Bit command.2. When the Set Block Lock-Down Bit command is written to the unlocked block (DQ 0=0), the corresponding block is locked-down and automatically locked at the same time.3. "No Change" means that the state remains unchanged after the command written.4. In this state transitions table, assumes that WP# is not changed and fixed V IL or V IH .Table 7.Functions of Block Lock (5) and Block Lock-DownCurrent StateErase/Program Allowed (2)State WP#DQ 1(1)DQ 0(1)State Name [000]000Unlocked Yes [001](3)001Locked No [011]011Locked-down No [100]100Unlocked Yes [101](3)101LockedNo [110](4)110Lock-down Disable Yes [111]111Lock-down DisableNoTable 8.Block Locking State Transitions upon Command Write (4)Current StateResult after Lock Command Written (Next State)State WP#DQ 1DQ 0Set Lock (1)Clear Lock (1)Set Lock-down (1)[000]000[001]No Change [011](2)[001]001No Change (3)[000][011][011]011No Change No Change No Change [100]100[101]No Change [111](2)[101]101No Change [100][111][110]110[111]No Change [111](2)[111]111No Change[110]No ChangeNOTES:1. "WP#=0→1" means that WP# is driven to V IH and "WP#=1→0" means that WP# is driven to V IL .2. State transition from the current state [011] to the next state depends on the previous state.3. When WP# is driven to V IL in [110] state, the state changes to [011] and the blocks are automatically locked.4. In this state transitions table, assumes that lock configuration commands are not written in previous, current and next state.Table 9.Block Locking State Transitions upon WP# Transition (4)Previous StateCurrent StateResult after WP# Transition (Next State)State WP#DQ 1DQ 0WP#=0→1(1)WP#=1→0(1)-[000]000[100]--[001]001[101]-[110](2)[011]011[110]-Other than [110](2)[111]--[100]100-[000]-[101]101-[001]-[110]110-[011](3)-[111]111-[011]Table 10.Status Register DefinitionR R R R R R R R 15141312111098 WSMS BESS BEFCES PBPOPS VPPS PBPSS DPS R 76543210SR.15 - SR.8 = RESERVED FOR FUTUREENHANCEMENTS (R)SR.7 = WRITE STATE MACHINE STATUS (WSMS)1 = Ready0 = BusySR.6 = BLOCK ERASE SUSPEND STATUS (BESS)1 = Block Erase Suspended0 = Block Erase in Progress/CompletedSR.5 = BLOCK ERASE AND FULL CHIP ERASESTATUS (BEFCES)1 = Error in Block Erase or Full Chip Erase0 = Successful Block Erase or Full Chip EraseSR.4 = (PAGE BUFFER) PROGRAM ANDOTP PROGRAM STATUS (PBPOPS)1 = Error in (Page Buffer) Program or OTP Program0 = Successful (Page Buffer) Program or OTP ProgramSR.3 = V PP STATUS (VPPS)1 = V PP LOW Detect, Operation Abort0 = V PP OKSR.2 = (PAGE BUFFER) PROGRAM SUSPENDSTATUS (PBPSS)1 = (Page Buffer) Program Suspended0 = (Page Buffer) Program in Progress/CompletedSR.1 = DEVICE PROTECT STATUS (DPS)1 = Erase or Program Attempted on aLocked Block, Operation Abort0 = UnlockedSR.0 = RESERVED FOR FUTURE ENHANCEMENTS (R)NOTES:Status Register indicates the status of the partition, not WSM (Write State Machine). Even if the SR.7 is "1", the WSM may be occupied by the other partition when the device is set to 2, 3 or 4 partitions configuration.Check SR.7 or RY/BY# to determine block erase, full chip erase, (page buffer) program or OTP program completion. SR.6 - SR.1 are invalid while SR.7="0".If both SR.5 and SR.4 are "1"s after a block erase, full chip erase, (page buffer) program, set/clear block lock bit, set block lock-down bit, set partition configuration register attempt, an improper command sequence was entered.SR.3 does not provide a continuous indication of V PP level. The WSM interrogates and indicates the V PP level only after Block Erase, Full Chip Erase, (Page Buffer) Program or OTP Program command sequences. SR.3 is not guaranteed to report accurate feedback when V PP≠V PPH1, V PPH2 or V PPLK. SR.1 does not provide a continuous indication of block lock bit. The WSM interrogates the block lock bit only after Block E rase, Full Chip E rase, (Page Buffer) Program or OTP Program command sequences. It informs the system, depending on the attempted operation, if the block lock bit is set. Reading the block lock configuration codes after writing the Read Identifier Codes/OTP command indicates block lock bit status.SR.15 - SR.8 and SR.0 are reserved for future use and should be masked out when polling the status register.Table 11.Extended Status Register DefinitionR R R R R R R R 15141312111098 SMS R R R R R R R 76543210XSR.15-8 = RESERVED FOR FUTUREENHANCEMENTS (R)XSR.7 = STATE MACHINE STATUS (SMS)1 = Page Buffer Program available0 = Page Buffer Program not availableXSR.6-0 = RESERVED FOR FUTURE ENHANCEMENTS (R)NOTES:After issue a Page Buffer Program command (E8H), XSR.7="1" indicates that the entered command is accepted. If XSR.7 is "0", the command is not accepted and a next Page Buffer Program command (E8H) should be issued again to check if page buffer is available or not.XSR.15-8 and XSR.6-0 are reserved for future use and should be masked out when polling the extended status register.1 Electrical Specifications 1.1 Absolute Maximum Ratings *Operating TemperatureDuring Read, Erase and Program......0°C to +70°C (1)Storage TemperatureDuring under Bias...............................-10°C to +80°C During non Bias................................-65°C to +125°C V oltage On Any Pin(except V CC and V PP )..............-0.5V to V CC +0.5V (2)V CC and V CCQ Supply V oltage..........-0.2V to +3.9V (2)V PP Supply V oltage....................-0.2V to +12.6V (2, 3, 4)Output Short Circuit Current...........................100mA (5)*WARNING: Stressing the device beyond the "AbsoluteMaximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.NOTES:1. Operating temperature is for commercial temperature product defined by this specification.2. All specified voltages are with respect to GND.Minimum DC voltage is -0.5V on input/output pins and -0.2V on V CC and V PP pins. During transitions,this level may undershoot to -2.0V for periods <20ns.Maximum DC voltage on input/output pins is V CC +0.5V which, during transitions, may overshoot to V CC +2.0V for periods <20ns.3. Maximum DC voltage on V PP may overshoot to +13.0V for periods <20ns.4. V PP erase/program voltage is normally 2.7V-3.6V.Applying 11.7V-12.3V to V PP during erase/program can be done for a maximum of 1,000 cycles on the main blocks and 1,000 cycles on the parameter blocks.V PP may be connected to 11.7V-12.3V for a total of 80hours maximum.5. Output shorted for no more than one second. No more than one output shorted at a time.1.2 Operating ConditionsNOTES:1. See DC Characteristics tables for voltage range-specific specification.2. Applying V PP =11.7V-12.3V during a erase or program can be done for a maximum of 1,000 cycles on the main blocks and 1,000 cycles on the parameter blocks. A permanent connection to V PP =11.7V-12.3V is not allowed and can cause damage to the device.ParameterSymbol Min.Typ.Max.Unit NotesOperating Temperature T A 0+25+70°C V CC Supply Voltage V CC 2.7 3.0 3.6V 1I/O Supply VoltageV CCQ 2.7 3.0 3.6V 1V PP V oltage when Used as a Logic Control V PPH1 1.65 3.0 3.6V 1V PP Supply V oltageV PPH211.71212.3V 1, 2Main Block Erase Cycling: V PP =V PPH1100,000Cycles Parameter Block Erase Cycling: V PP =V PPH1100,000Cycles Main Block Erase Cycling: V PP =V PPH2, 80 hrs.1,000Cycles Parameter Block Erase Cycling: V PP =V PPH2, 80 hrs.1,000Cycles Maximum V PP hours at V PPH280Hours1.2.3 DC CharacteristicsV CC=2.7V-3.6VSymbol Parameter Notes Min.Typ.Max.Unit Test Conditions I LI Input Load Current1-1.0+1.0µA V CC=V CC Max.,V CCQ=V CCQ Max.,V IN/V OUT=V CCQ orGND I LO Output Leakage Current1-1.0+1.0µAI CCS V CC Standby Current1,8420µA V CC=V CC Max.,CE#=RST#=V CCQ±0.2V, WP#=V CCQ or GNDI CCAS V CC Automatic Power Savings Current1,4420µA V CC=V CC Max.,CE#=GND±0.2V, WP#=V CCQ or GNDI CCD V CC Reset Power-Down Current1420µA RST#=GND±0.2VI CCR Average V CC ReadCurrentNormal Mode1,71525mA V CC=V CC Max.,CE#=V IL,OE#=V IH,f=5MHz Average V CC ReadCurrentPage Mode8 Word Read1,7510mAI CCW V CC (Page Buffer) Program Current 1,5,72060mA V PP=V PPH1 1,5,71020mA V PP=V PPH2I CCE V CC Block Erase, Full ChipErase Current1,5,71030mA V PP=V PPH11,5,7410mA V PP=V PPH2I CCWS I CCES V CC (Page Buffer) Program orBlock Erase Suspend Current1,2,710200µA CE#=V IHI PPSI PPRV PP Standby or Read Current1,6,725µA V PP≤V CCI PPW V PP (Page Buffer) Program Current 1,5,6,725µA V PP=V PPH1 1,5,6,71030mA V PP=V PPH2I PPE V PP Block Erase, Full ChipErase Current1,5,6,725µA V PP=V PPH11,5,6,7515mA V PP=V PPH2I PPWS V PP (Page Buffer) ProgramSuspend Current1,6,725µA V PP=V PPH11,6,710200µA V PP=V PPH2I PPES V PP Block Erase Suspend Current 1,6,725µA V PP=V PPH1 1,6,710200µA V PP=V PPH2。

LF230-S 弹簧返回式调节器 带应急控制功能 气漏门 产品说明书

Spring-return actuator with emergencycontrol function for adjusting dampersin technical building installations• Air damper size up to approx. 0.8 m²• Nominal torque 4 Nm• Nominal voltage AC 230 V• Control Open-close• With integrated auxiliary switchTechnical dataElectrical data Nominal voltage AC 230 VNominal voltage frequency50/60 HzNominal voltage range AC 198...264 VPower consumption in operation 5 WPower consumption in rest position 3 WPower consumption for wire sizing7 VAPower consumption for wire sizing note Imax 150 mA @ 10 msAuxiliary switch 1 x SPDT, 0...100%Switching capacity auxiliary switch 1 mA...3 (0.5 inductive) A, AC 250 VConnection supply / control Cable 1 m, 2 x 0.75 mm²Connection auxiliary switch Cable 1 m, 3 x 0.75 mm²Parallel operation Yes (note the performance data)Functional data Torque motor Min. 4 NmTorque spring return Min. 4 NmDirection of motion motor Selectable by mounting L / RDirection of motion emergency controlSelectable by mounting L / RfunctionManual override NoAngle of rotation Max. 95°Angle of rotation note Adjustable 37...100% with integratedmechanical limitationRunning time motor40...75 s / 90°Running time emergency control position<20 s / 90°<20 s @ -20...50°C / <60 s @ -30°CRunning time emergency setting positionnoteSound power level motor50 dB(A)Spindle driver Universal spindle clamp 8...16 mmPosition indication MechanicalService life Min. 60,000 emergency positionsSafety Protection class IEC/EN II Protective insulatedProtection class auxiliary switch IEC/EN II Protective insulatedDegree of protection IEC/EN IP54EMC CE according to 2004/108/ECLow voltage directive CE according to 2006/95/ECCertification IEC/EN IEC/EN 60730-1 and IEC/EN 60730-2-14Mode of operation Type 1.BRated impulse voltage supply / control 4 kVRated impulse voltage auxiliary switch 4 kVControl pollution degree3Ambient temperature-30...50°CNon-operating temperature-40...80°CAmbient humidity95% r.h., non-condensingMaintenance Maintenance-freeWeight Weight approx. 1.8 kgwww.belimo.eu LF230-S • en-gb • 2015-10-07 • subject to changes1!• The device must not be used outside the specified field of application, especially notin aircraft or in any other airborne means of transport.• Outdoor application: only possible in case that no (sea)water, snow, ice, insolationor aggressive gases interfere directly with the actuator and that is ensured that theambient conditions remain at any time within the thresholds according to the datasheet.• Caution: Power supply voltage!• Only authorised specialists may carry out installation. All applicable legal orinstitutional installation regulations must be complied during installation.• The device may only be opened at the manufacturer’s site. It does not contain anyparts that can be replaced or repaired by the user.• Cables must not be removed from the device.• To calculate the torque required, the specifications supplied by the dampermanufacturers concerning the cross-section, the design, the installation site and theventilation conditions must be observed.• The device contains electrical and electronic components and must not be disposedof as household refuse. All locally valid regulations and requirements must beobserved.Product featuresMode of operation The actuator moves the damper to the operating position at the same time astensioning the return spring. The damper is turned back to the safety position by springenergy when the supply voltage is interrupted.Simple direct mounting Simple direct mounting on the damper spindle with an universal spindle clamp,supplied with an anti-rotation device to prevent the actuator from rotating.High functional reliability The actuator is overload protected, requires no limit switches and automatically stopswhen the end stop is reached.Adjustable angle of rotation Adjustable angle of rotation with mechanical end stops.Flexible signalization With adjustable auxiliary switch (0 ... 100%)AccessoriesDescription Type Electrical accessories Auxiliary switch, 2 x SPDT S2A-FFeedback potentiometer, 200 Ohm, incl. installation accessories P200A-FFeedback potentiometer 1 kOhm, incl. installation accessories P1000A-FDescription Type Mechanical accessories Shaft extension 170 mm, for damper spindles Ø 6...20 mm AV6-20Shaft extension 250 mm, for damper spindles Ø 8...25 mm AV8-25Spindle clamp, for damper spindles Ø 16...20 mm K6-1Straight ball joint with M8, suitable for damper crank arms KH8KG10AAngled ball joint with M8, suitable for damper crank arms KH8KG8Damper crank arm, for damper spindles KH8Actuator arm, for damper spindles Ø 8...16 mm KH-LFAngle of rotation limiter, for LF with end stop ZDB-LFAdditional shaft adapter 4-kt. 8x8mm for LF ZF8-LFMounting kit for linkage operation LF..ZG-LF1Mounting kit for linkage operation LF.., suitable for damper spindles Ø 10...18 mm ZG-LF3Spring-return actuator, Open-close, AC 230 V, 4 Nm, Withintegrated auxiliary switchSafety noteswww.belimo.euLF230-S • en-gb • 2015-10-07 • subject to changes2!Notes• Caution: Power supply voltage!• Parallel connection of other actuators possible. Observe the performance data.Wiring diagrams AC 230 V, open-close0...100%S3S2S1N12LCable colours:1 = blue 2 = brown S1 = white S2 = white S3 = whiteDimensions [mm]Spindle lengthClamping rangeDimensional drawingsSpring-return actuator, Open-close, AC 230 V, 4 Nm, With integrated auxiliary switchElectrical installationwww.belimo.euLF230-S • en-gb • 2015-10-07 • subject to changes3。

FC Series 30单相电源滤波器用于频率转换器说明书

FC SeriesFC SeriesSingle Phase Power Line Filter for Frequency ConvertersMaximum leakage current each Line to Ground:B suffix no suffix@ 120 VAC 60 Hz: 3.9 mA 3.8 mA @250 VAC 50 Hz:7.0 mA 6.7 mA Hipot rating (one minute):Line to Ground:2250 VDC Line to Line:1450 VDC Rated Voltage (max):250 VAC Operating Frequency:50/60 Hz Rated Current:6to 50AOperating Ambient Temperature Range (at rated current I r ):-10°C to +40°CIn an ambient temperature (T a ) higher than +40°C the maximum operating current (I o ) is calculated asfollows: I o = I r √(85-T a)/45• Designed for frequency inverters and variable speed motor drives• Suitable for electronically noisy environments • Protects programmable logic controllers from RF noise on the AC power line • Side flanges for easy mounting• T ouch safe terminals provide easy connections and prevent inadvertent contact for safety in the most demanding applicationsOrdering Information36 FC 10 BSuffixB – Single stage Omit for dual stageInput / Output Style10 – DIN type terminal block FC SeriesCurrent Rating6, 12, 16, 25, 36 or 50ASpecificationsElectrical SchematicsUL RecognizedAvailable Part NumbersFC10FC10BNote 1:25, 36, 50A only Note 2:50A onlyFC SeriesSingle Phase Filter for Frequency Converters (continued)RFI Power Line Filters1Case StylesFC10 / FC10B(6, 12, 16A)may be on either flange.Typical Dimensions:Line/Load Terminals (4): DIN type accepts 10AWG solid / 12AWG stranded Ground Terminals (2): 8-32 screw terminals Mounting Holes (4):.203 x .156 [5.16 x 3.96]FC10 / FC10B(25, 36, 50A )Typical Dimensions:Line/Load Terminals (4): DIN type accepts 8AWG solid / 10AWG stranded Ground Terminals (2): 8-32 screw terminals Mounting Slots (4):.260 [6.6] wide6FC104.60 3.10 1.78 2.677 3.70 2.0116.878.745.2167.894.050.812FC10/10B 16FC10/10B 5.47 3.96 2.18 3.50 4.532.0139.0100.655.488.9114.8 5.0825, 36, 50FC10/10B 6.90 5.48 2.55 4.90 5.94 2.756175.3139.264.77124.5150.970.0Case Dimensions32FC SeriesSingle Phase Filter for Frequency Converters (continued)Dimensions are in inches and millimeters unless otherwise specified. Values in italicsare metric equivalents. Dimensions are shown for reference purposes only.For email, phone or live chat, please go to/help Performance DataTypical Insertion LossMinimum Insertion LossFrequency – MHzPart No..01.03.05.1.51510306FC109192637656550403512FC105172537656565603516FC104152236656570703525FC102142236757570704836, 50FC10-61427687570705012, 16FC10B16283750817663553825FC10B14253649918871644636FC10B11253750818773664950FC10B112436498175625437Common Mode / Asymmetrical (Line to Ground)Differential Mode / Symmetrical (Line to Line)Common Mode / Asymmetrical (L-G)Differential Mode / Symmetrical (L-L) Measured in closed 50 Ohm systemFrequency – MHzPart No..01.03.05.1.51510306FC1010103560757560504512FC1014143051757575704516FC1014142955757575704525FC1014141742757570705036, 50FC1014141742757570705012, 16FC10B30324664918677786525FC10B24243146928786755536FC10B27332741898882745550FC10B303248649187827967。

LH28F160S3HNS-L13资料

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网wwwLeabharlann

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

LH28Fxxx FLASH MEMORY FLASH NON-VOLATILE MEMORY FLASH E2ROM FLASH ROM READ ONLY MEMORY ETOX LH28F160S3-L 16M(2Mx8/1Mx16) Smart3 Voltage

MEMORY存储芯片MT28F320J3RG-15中文规格书

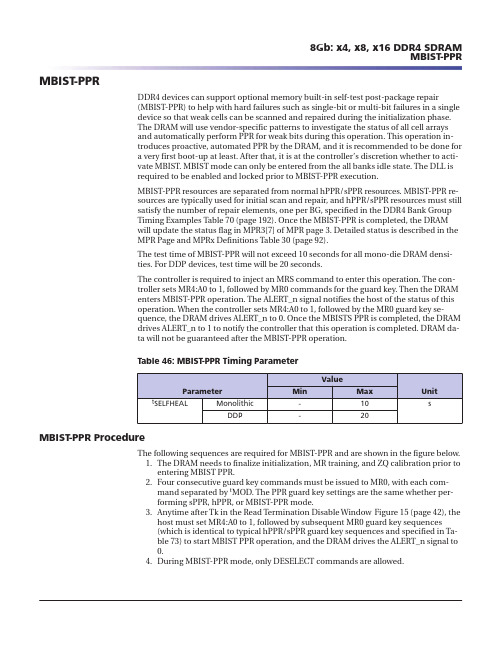

MBIST -PPRDDR4 devices can support optional memory built-in self-test post-package repair(MBIST-PPR) to help with hard failures such as single-bit or multi-bit failures in a single device so that weak cells can be scanned and repaired during the initialization phase.The DRAM will use vendor-specific patterns to investigate the status of all cell arrays and automatically perform PPR for weak bits during this operation. This operation in-troduces proactive, automated PPR by the DRAM, and it is recommended to be done for a very first boot-up at least. After that, it is at the controller’s discretion whether to acti-vate MBIST. MBIST mode can only be entered from the all banks idle state. The DLL is required to be enabled and locked prior to MBIST-PPR execution.MBIST-PPR resources are separated from normal hPPR/sPPR resources. MBIST-PPR re-sources are typically used for initial scan and repair, and hPPR/sPPR resources must still satisfy the number of repair elements, one per BG, specified in the DDR4 Bank Group Timing Examples Table 70 (page 192). Once the MBIST-PPR is completed, the DRAM will update the status flag in MPR3[7] of MPR page 3. Detailed status is described in the MPR Page and MPRx Definitions Table 30 (page 92).The test time of MBIST-PPR will not exceed 10 seconds for all mono-die DRAM densi-ties. For DDP devices, test time will be 20 seconds.The controller is required to inject an MRS command to enter this operation. The con-troller sets MR4:A0 to 1, followed by MR0 commands for the guard key. Then the DRAM enters MBIST-PPR operation. The ALERT_n signal notifies the host of the status of this operation. When the controller sets MR4:A0 to 1, followed by the MR0 guard key se-quence, the DRAM drives ALERT_n to 0. Once the MBISTS PPR is completed, the DRAM drives ALERT_n to 1 to notify the controller that this operation is completed. DRAM da-ta will not be guaranteed after the MBIST-PPR operation.Table 46: MBIST -PPR Timing ParameterMBIST -PPR ProcedureThe following sequences are required for MBIST-PPR and are shown in the figure below.1.The DRAM needs to finalize initialization, MR training, and ZQ calibration prior to entering MBIST PPR.2.Four consecutive guard key commands must be issued to MR0, with each com-mand separated by t MOD. The PPR guard key settings are the same whether per-forming sPPR, hPPR, or MBIST-PPR mode.3.Anytime after Tk in the Read Termination Disable Window Figure 15 (page 42), the host must set MR4:A0 to 1, followed by subsequent MR0 guard key sequences (which is identical to typical hPPR/sPPR guard key sequences and specified in Ta-ble 73) to start MBIST PPR operation, and the DRAM drives the ALERT_n signal to 0.4.During MBIST-PPR mode, only DESELECT commands are allowed.8Gb: x4, x8, x16 DDR4 SDRAM MBIST -PPRDLL-On/Off Switching ProceduresThe DLL-off mode is entered by setting MR1 bit A0 to 0; this will disable the DLL for subsequent operations until the A0 bit is set back to 1.DLL Switch Sequence from DLL-On to DLL-OffTo switch from DLL-on to DLL-off requires the frequency to be changed during self re-fresh, as outlined in the following procedure:1.Starting from the idle state (all banks pre-charged, all timings fulfilled, and, to dis-able the DLL, the DRAM on-die termination resistors, R TT(NOM), must be in High-Z before MRS to MR1.)2.Set MR1 bit A0 to 1 to disable the DLL.3.Wait t MOD.4.Enter self refresh mode; wait until t CKSRE/t CKSRE_PAR is satisfied.5.Change frequency, following the guidelines in the Input Clock Frequency Change section.6.Wait until a stable clock is available for at least t CKSRX at device inputs.7.Starting with the SELF REFRESH EXIT command, CKE must continuously be regis-tered HIGH until all t MOD timings from any MRS command are satisfied. In addi-tion, if any ODT features were enabled in the mode registers when self refresh mode was entered, the ODT signal must continuously be registered LOW until all t MOD timings from any MRS command are satisfied. If R TT(NOM) was disabled in the mode registers when self refresh mode was entered, the ODT signal is "Don't Care."8.Wait t XS_FAST, t XS_ABORT, or t XS, and then set mode registers with appropriate values (an update of CL, CWL, and WR may be necessary; a ZQCL command can also be issued after t XS_FAST).•t XS_FAST: ZQCL, ZQCS, and MRS commands. For MRS commands, only CL and WR/RTP registers in MR0, the CWL register in MR2, and gear-down mode in MR3 may be accessed provided the device is not in per-DRAM addressability mode. Access to other device mode registers must satisfy t XS timing.•t XS_ABORT: If MR4 [9] is enabled, then the device aborts any ongoing refresh and does not increment the refresh counter. The controller can issue a valid command after a delay of t XS_ABORT. Upon exiting from self refresh, the device requires a minimum of one extra REFRESH command before it is put back into self refresh mode. This requirement remains the same regardless of the MRS bit setting for self refresh abort.•t XS: ACT, PRE, PREA, REF , SRE, PDE, WR, WRS4, WRS8, WRA, WRAS4, WRAS8,RD, RDS4, RDS8, RDA, RDAS4, and RDAS8.9.Wait t MOD to complete.The device is ready for the next command.8Gb: x4, x8, x16 DDR4 SDRAM DLL-On/Off Switching Procedures。

LH-130红外功率计说明书

应用领域

太阳光、红外灯、红外遥控等红外源的辐射强度测量 材料对红外线的透过率、阻隔率、反射率测量 太阳膜、隔热玻璃等的隔热性能测试 光学及实验室,气象和农业生产领域

透过率和阻隔率测量

1. 开机后按 M 键切换到模式 2 2. 将功率计前端探பைடு நூலகம்窗口对准辐射源,此时 A 和 B 都显示实时功率值,“A”闪动 3. 按 OK 键定标,锁定功率 A 即总功率(此时如需重新测定总功率再按 OK 可以解锁 A),此时 “B”开始闪动将被测样品置于光源和功率计探头窗之间,由于被测物的遮挡辐射功率会被衰减, 此时 B 显示的就是透过的光功率,仪器自动计算出透过率:即透过功率占总功率的百分比

功率和温度测量:

1. 按 OK 键开机,等待开机自检结束,默认进入模式 1—功率测量模式。 2. 将功率计前端探头窗口对准辐射源,读取功率和温度数据即可。注意每次测量要保证距离位置 角度相同测得的数据才会一致,温度测量需要等其数据稳定后再读取。 3. 按 H 键可以锁定峰值,按 OK 键保存数据并解除锁定 4. 保存的数据可在模式 1 下按 R 键读取,按上、下方向键翻页,在数据查询界面:按 OK 键可 退出查询;按 H 键进入删除当前数据菜单,再按上、下方向键和 OK 键选择需要的操作;按 S 键进入删除全部数据。

优点

1.测量功率范围大 3.可测量功率峰值适合遥控器测试 5.带温度计,适合隔热性能测试

2.响应光谱范围宽 4.可测量透过率、阻隔率 6.可保存 100 组测试数据

3. 模式 2:设置显示透过率或者阻隔率,默认:透过率 4. 自动关机:是--3 分钟无操作自动关机,否--不自动关机,默认:是 5. Language: 选择语言 Chinese—中文,English—英文,默认:中文 6. 归零:当无光信号输入功率计不归零(有底数)时,使用此功能归零 7. 恢复出厂设置:将测试仪参数恢复出厂时候的设置

FC301 FC302 FC312系列变频器宣传样本

4 24V直流电源选件

电源 选件 能确保 在失 去交 流电源 时变 频器的程序保持运行。

5 RFI/EMC无线电干扰滤波器

标准内 置EN61800-3标准的C3级滤波 器 (等同前EN55011的A2级),另可 提 供内 置的 C1/C2级滤 波器( 等同 前 B/A1级)。

5 6

1 3 4

10 13 11 8 14 2 15

通讯”类 来自34个国家 的1000项产 品 中一举夺魁。

直流电抗器

内 置直 流电 抗器 ,有效 降低 电源 的谐 波 干 扰 , 符 合 IEC-1000-3-2国 际标 准。设计紧凑、无需外部选件。

模块式结构,易于维护

所 有元 器件 都可 以直接 从变 频器 前端 触 及, 简化 维护 工作, 并能 实现 并列 无 间隙 安装 。同 时模块 化设 计也 非常 方便维护人员更换损坏的器件。

智 能逻 辑控制器能监视 任何 可定 义为 “ 真( True)” 或“假 (False) ”的 参数。

该功能监视的对象不仅包括数字指令, 也包括逻辑表述,甚至可以使传感器的 输出影响运行。温度、压力、流量、时 间、负载、频率、电压以及其它参数与 运 算 符 号 “ >” 、 “ <” 、 “ +” 、 “and”和 “or”组 合成 逻辑 语句 。这 就是丹佛斯称之为“逻辑”控制器的原 因,这也是为什么用户能对控制器进行 编程,使之响应用户选择的几乎任何事 件。

AutomationDrive 经批 准符合三类 安全 应用设备。

电气连接极 为简单仅仅只有一根线。 AutomationDrive已 被 认 可 提 供三 类装 置的 安全 停车,无需 从变 频器 到安 全继 电器的反馈信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

LH28F320S3-L11/14 32M, Smart3, Flash, Flash File, CFI, ETOX, Non Volatile

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网

元器件交易网