chipsee的beaglebone的开发底板BEAGLEBONE-EXP

Microsemi IGLOO2 FPGA 评估板说明书

IGLOO2 FPGA Evaluation KitQuickstart CardKit Contents—M2GL-EVAL-KITQuantity Description1IGLOO2 FPGA 12K LE M2GL010T-1FGG484 Evaluation Board 112 V, 2 A AC power adapter1FlashPro4 JTAG programmer1USB 2.0 A-Male to Mini-B cable1Quickstart cardOverviewThe Microsemi IGLOO®2 FPGA Evaluation Kit makes it easier to develop embedded applications that involve motor control, system management, industrial automation, and high-speed serial I/O applications such as PCIe, SGMII, and user-customizable serial interfaces. The kit offers best-in-class feature integration coupled with the lowest power, proven security, and exceptional reliability. The board is also small form-factor PCIe-compliant, which allows quick prototyping and evaluation using any desktop PC or laptop with a PCIe slot.The kit enables you to:• Develop and test PCI Express Gen2 x1 lane designs• Test signal quality of the FPGA transceiver using the full-duplex SerDes SMA pairs• Measure the low power consumption of the IGLOO2 FPGA• Quickly create a working PCIe link with the included PCIe Control Plane DemoHardware Features• 12K LE IGLOO2 FPGA in the FGG484 package (M2GL010T-1FGG484)• 64 Mb SPI flash memory• 512 Mb LPDDR• PCI Express Gen2 x1 interface• Four SMA connectors for testing the full-duplex SerDes channel • RJ45 interface for 10/100/1000 Ethernet • JTAG/SPI programming interface• Headers for I2C, SPI, and GPIOs• Push-button switches and LEDs for demo purposes• Current measurement test pointsRunning the DemoThe IGLOO2 FPGA Evaluation Kit is shipped with the PCI Express Control Plane demo preloaded. Instructions on running the demo design are available in the IGLOO2 FPGA Evaluation Kit PCIe Control Plane Demo user guide. See the Documentation Resources section for more information. ProgrammingThe IGLOO2 FPGA Evaluation Kit comes with a FlashPro4 programmer. Embedded programming with the IGLOO2 FPGA Evaluation Kit is also available, and it is supported by the Libero SoC v11.4 SP1 or later.Jumper SettingsJumper Development Kit Function Pins Factory DefaultJ23Selects switch-side MUX inputsof A or B to the line side 1–2 (input A to the line side) thatis on board 125 MHz differentialclock oscillator output will berouted to line sideClosed2–3 (input B to the line side)that is external clock requiredto source through SMAconnectors to the line sideOpenJ22Selects the output enablecontrol for the line side outputs 1–2 (line-side output enabled)Closed 2–3 (line-side output disabled)OpenJ24Provides the VBUS supply toUSB when using in Host mode OpenJ8Selects between RVI headeror FP4 header for applicationdebug1–2 FP4 for SoftConsole/FlashPro Closed2–3 RVI for Keil ULINK/IARJ-Link Open2–4 for toggling JTAG_SELsignal remotely using the GPIOcapability of the FT4232 chipOpenJ3Selects either the SW2 inputor the ENABLE_FT4232 signalfrom the FT4232H chip1–2 for manual power switchingusing the SW7 switch Closed2–3 for remote power switchusing the GPIO capability of theFT4232 chipOpenJ31Selects between FTDI JTAGprogramming and FTDI slaveprogramming1–2 for FlashPro FTDI JTAGprogramming Closed2–3 for SPI slave programming OpenJ32Selects between FTDI SPI andSC_SCI header 1–2 for programming throughFTDI SPI Closed 2–3 for programming throughSC_SPI header OpenJ35Selects between FP4 headerand FTDI JTAG 1–2 for programming throughFP4 header Closed 2–3 for programming throughFTDI JTAG Open©2016–2017 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are registered trademarks of Microsemi Corporation. Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996Email:***************************Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer’s responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself Software and LicensingLibero ® SoC Design Suite offers high productivity with its comprehensive, easy-to-learn, easy-to-adopt development tools for designing with Microsemi’s low power Flash FPGAs and SoC. The suite integrates industry standard Synopsys Synplify Pro ® synthesis and Mentor Graphics ModelSim ® simulation with best-in-class constraints management and debug capabilities.Download the latest Libero SoC release/products/fpga-soc/design-resources/design-software/libero-soc#downloads Generate a Libero Silver license for your kit/products/fpga-soc/design-resources/licensingDocumentation ResourcesFor more information about the IGLOO2 FPGA Evaluation Kit, including user’s guides, tutorials, and design examples, see the documentation at /products/fpga-soc/design-resources/dev-kits/igloo2/igloo2-evaluation-kit#documentation .SupportTechnical support is available online at /soc/support and by email at **********************Microsemi sales offices, including representatives and distributors, are located worldwide. To find your local representative, go to /salescontacts。

AM335x BeagleBoneBlack Schematic 原理图,A5A版本

42 2

R7 0,1%

VRTC

10uF,10V C15 10uF,10V

3 1

VLDO1

R5 0,1% R8 0,DNI C16 DGND DGND DGND 2.2uF,6.3V

AGND

PPAD

VDD_3V3B VDD_3V3AUX SYS_5V U4 DGND 470K,1% R10 280K,1% R11 TPS65217C

DDR_VTP

C26 18pF,50V

OSC0_IN OSC0_OUT VSS_OSC0 OSC1_IN OSC1_OUT VSS_RTC DDR_A0 DDR_A1 DDR_A2 DDR_A3 DDR_A4 DDR_A5 DDR_A6 DDR_A7 DDR_A8 DDR_A9 DDR_A10 DDR_A11 DDR_A12 DDR_A13 DDR_A14 DDR_A15 DDR_BA0 DDR_BA1 DDR_BA2 DDR_D0 DDR_D1 DDR_D2 DDR_D3 DDR_D4 DDR_D5 DDR_D6 DDR_D7 DDR_D8 DDR_D9 DDR_D10 DDR_D11 DDR_D12 DDR_D13 DDR_D14 DDR_D15 DDR_CK DDR_NCK DDR_CKE DDR_CSN0 DDR_CASN DDR_RASN DDR_WEn DDR_DQM0 DDR_DQS0 DDR_DQSN0 DDR_DQM1 DDR_DQS1 DDR_DQSN1 DDR_ODT DDR_RESETN DDR_VTP VREFSSTL

B B

This schematic is *NOT SUPPORTED* and DOES NOT constitute a reference design. Only “community” support is allowed via resources at /discuss. THERE IS NO WARRANTY FOR THIS DESIGN , TO THE EXTENT PERMITTED BY APPLICABLE LAW. EXCEPT WHEN OTHERWISE STATED IN WRITING THE COPYRIGHT HOLDERS AND/OR OTHER PARTIES PROVIDE THE DESIGN “AS IS” WITHOUT WARRANTY OF ANY KIND, EITHER EXPRESSED OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE. THE ENTIRE RISK AS TO THE QUALITY AND PERFORMANCE OF THE DESIGN IS WITH YOU. SHOULD THE DESIGN PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL NECESSARY SERVICING, REPAIR OR CORRECTION.

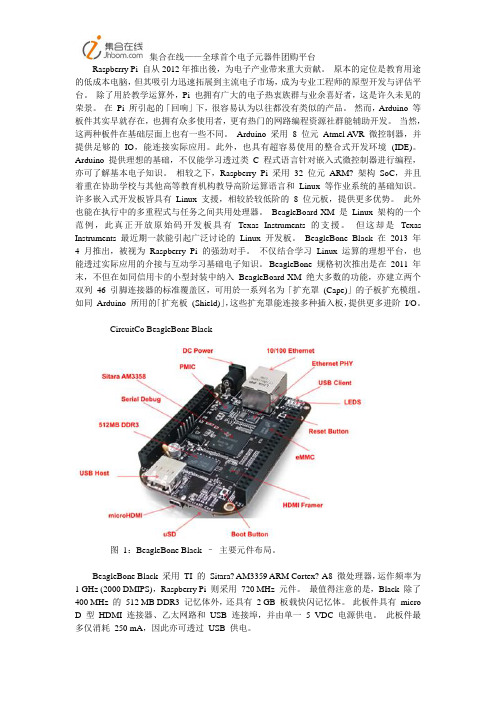

比较RaspberryPi与BeagleBone

比较RaspberryPi与BeagleBone作者:ABOpenLtd主管AndrewBack在BeagleBone推出即将一年之际,比其稍晚问世的RaspberryPi则可以说更富有魅力,让我们来看看二者的对比吧。

带注释的BeagleBone端口(来源:,CCBYSA3.0)BeagleBone不但具有相当强大的基于ARM的SoC、且具有黑客友好性和低价位,一经发布即引起轰动。

然而不久之后,却被功能相似但价格更低的树莓派RaspberryPi抢走了风头,RaspberryPi一时间占据了英国各大主流媒体,迅速发展成为家喻户晓的品牌。

由于RaspberryPi声誉鹊起,已成为其它嵌入式平台的杰出基准,所以进一步比较Pi和BeagleBone将有助于明确它们各自的优势。

接下来比较一些主要区别,如需了解综合的详细信息,请查看官方文档。

基本系统RaspberryPi和BeagleBone的SoC都使用装有时钟速度约为700MHz的ARM处理器,且二者的RAM均为256MB。

但是,BeagleBoneAM3359SoC使用ARMv7内核,而Pi则使用较早的ARMv6,因而BeagleBone具有双超标架构和NEONSIMD扩展的优势。

就执行速度而言,BeagleBone可达到1440DMIPS,Pi则为965DMIPS。

二者均具有以太网功能和USB接口,但BeagleBone的以太网MAC由SoC提供,而Pi则通过外挂在USB的芯片提供,这意味着BeagleBone集合的I/O吞吐量要比Pi更高。

其它I/O相关的考量包括BeagleBone的微型USB插口是连接到双端口USB集线器,然后再路由至SoCUSB和FTDIUSB串行转换器,可用于控制台访问和JTAG调试。

通过该端口访问的SoCUSB可配置为将SD卡作为存储设备或提供Ethernet-over-USB。

相比之下,Pi的微型USB仅用于为电脑板供电。

杰奇莱恩Digilab 2E FPGA开发板说明书

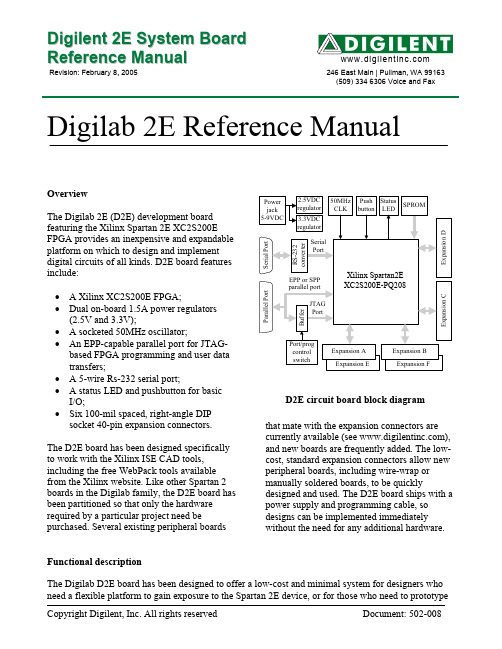

D i g i l e n t2E S y s t e m B o a r d R e f e r e n c e M a n u a lRevision: February 8, 2005 246 East Main | Pullman, WA 99163(509) 334 6306 Voice and Fax Digilab 2E Reference ManualOverviewThe Digilab 2E (D2E) development board featuring the Xilinx Spartan 2E XC2S200E FPGA provides an inexpensive and expandable platform on which to design and implement digital circuits of all kinds. D2E board features include:• A Xilinx XC2S200E FPGA;•Dual on-board 1.5A power regulators(2.5V and 3.3V);• A socketed 50MHz oscillator;•An EPP-capable parallel port for JTAG-based FPGA programming and user datatransfers;• A 5-wire Rs-232 serial port;• A status LED and pushbutton for basic I/O;•Six 100-mil spaced, right-angle DIP socket 40-pin expansion connectors.The D2E board has been designed specifically to work with the Xilinx ISE CAD tools, including the free WebPack tools available from the Xilinx website. Like other Spartan 2 boards in the Digilab family, the D2E board has been partitioned so that only the hardware required by a particular project need be purchased. Several existing peripheral boardscurrently available (see ), and new boards are frequently added. The low-cost, standard expansion connectors allow new peripheral boards, including wire-wrap or manually soldered boards, to be quickly designed and used. The D2E board ships with a power supply and programming cable, so designs can be implemented immediately without the need for any additional hardware.Functional descriptionThe Digilab D2E board has been designed to offer a low-cost and minimal system for designers who need a flexible platform to gain exposure to the Spartan 2E device, or for those who need to prototype。

Microchip Explorer 16 开发板介绍(含 MPLAB ICD 3)说明书

Microchip - DV164037 - DV164037 Development Board Kit Product Overview:Explorer 16 (with MPLAB ICD 3) Development Board Kit. Thedevelopment board provides a low-cost, modular developmentsystem for Microchip’s new line of 16-bit microcontroller families,including the PIC24, PIC24H and the 16-bit digital signal controllerfamily, dsPIC33F.As provided, the development board works as a demo board rightfrom the box, and also has the ability to extend its functionalitythrough modular expansion interfaces. The Explorer 16 boardsupports MPLAB ICD 2 for full emulation and debug capabilities,and also allows 3V controllers to interface with 5V peripheraldevices.Kit Content:The Explorer 16 Development Board Kit contains the following:∙The Explorer 16 Development Board.∙ A preprogrammed PIC24FJ128GA010 Processor Installation Module (PIM), already installed to the board∙ A preprogrammed dsPIC33FJ256GP710 PIM∙An RS-232 cable∙The Explorer 16 Development CD ROM, containing:▪ This User’s Guide▪Data Sheets for the PIC24FJ128GA family and dsPIC33FJ256GP family▪Schematics and PCB drawing files for the PIM modules▪Example programs for use with the PIC24 and dsPIC33F devices▪Files detailing general purpose expansion boards that can be used with the Explorer16 board (provided in Gerber format).Key Features:∙100-pin PIM riser, compatible with the PIM versions of all Microchip PIC24F/24H/dsPIC33F devices ∙Direct 9 VDC power input that provides +3.3V and +5V (regulated) to the entire board∙ Power indicator LED∙ RS-232 serial port and associated hardware ∙ On-board analog thermal sensor∙ USB connectivity for communications and device programming/debugging∙ Standard 6-wire In-Circuit Debugger (ICD) connector for connections to an MPLAB ICD 2 programmer/debugger module∙ Hardware selection of PIM or soldered on-board microcontroller (in future versions) ∙ 2-line by 16-character LCD∙ Provisioning on PCB for add on graphic LCD∙ Push button switches for device Reset and user-defined inputs ∙ Potentiometer for analog input ∙ Eight indicator LEDs∙ 74HCT4053 multiplexers for selectable crossover configuration on serial communication lines ∙ Serial EEPROM∙ Independent crystals for precision microcontroller clocking (8 MHz) and RTCC operation (32.768 kHz) ∙ Prototype area for developing custom applications∙ Socket and edge connector for PICtail™ Plus card compatibility ∙Six-pin interface for PICkit 2 Programmer∙ JTAG connector pad for optional boundary scan functionalityOrdering Information: Products:Part NumberManufacturerFarnell P/NNewark P/NDV164037 Microchip 1771308 25R7377Associated Products:Part NumberManufacturerDescriptionFarnell P/NNewark P/NPIC24FJ128GA010-I/PT Microchip16BIT MCU 128K FLASH 8K RAM, SMD 1146523 56K7341 PIC18F4550-I/PTMicrochip8-Bit Microcontroller IC932136508J963325LC256-I/P MicrochipEEPROM SERIAL 256KB,PDIP81331398 92C7459Similar Products:Part NumberManufacturerDescriptionSupport DeviceFarnell P/N Newark P/N DM240002 Microchip Explorer 16kit(44-PIN) PIC24F1754668 54M4471 DM240001 Microchip Explorer 16kit(100-PIN) dsPIC33F1146554 04M6008 MA320001 MicrochipPIC32MX360F512LPLUG-IN MODULEPIC32M152331673M8723AC164137-1 Microchip MRF49XAPICtail/PICtail PlusDaughter Board(433.92 MHz) MRF491736502 14R8658AC164137-2 Microchip MRF49XAPICtail/PICtail PlusDaughter Board(868/915 MHz)MRF491736503 14R8659MA240012 Microchip PIC24H 100P to 100P TQFP Plug-InModule use w/Explorer 16(DM240001 or DM240002)PIC24HNA 88K5499MA240015 Microchip PIC24F Plug-In Module use w/Explorer 16 (DM240001 or DM240002)PIC24FNA 98M1509MA330011 Microchip dsPIC33 GP 100P to 100P TQFP Plug-InModule use w/ Explorer 16 (DM240001)dsPIC33NA 56K6941Document List: Datasheets:Part NumberDescriptionSizeDM240002dsPIC® Digital Signal Controllers 2.84MBMBPIC24FJ128GA010 PIC24FJ128GA Family 3.51PIC24F16KA102 Module PIC24F16KA102 Plug-in Module Information Sheet 93KBMA240013 PIC24FJ64GA004 PIM (MA240013) Manual 132KBApplication Notes:File Name SizeAN100 How to build a Linux Wireless Sniffer 56KB100-pin Plug-In Module (PIM) Dimensions 14KBAN1247 - Communication Device Class (CDC) Host 351KBAN1192 - MRF24J40 Radio Utility Driver Program 839KB Hardware & Software:File Name SizedsPIC33F Demo Files for Explorer 16 25KB MiWi(TM) P2P for PIC18, PIC24, dsPIC, PIC32 7.81MBMiWi(TM) Protocol Stack for PIC18, PIC24, dsPIC, PIC32 4.95MBPIC24F Demo Files for Explorer 16 46KB PIC24F16KA102 Demo Files for Explorer 16 278KBPIC24H Demo Files for Explorer 16 24KBOthers Resources:File Name SizeDM240001 BOM and Schematics 866KBdsPIC33FJ128GP804 PIM Information Sheet 289KbdsPIC33FJ12GP202 PIM Information Sheet 393KBdsPIC33FJ256GP710 100-pin to 100-pin TQFP Plug-In Module (PIM) Information Sheet 672KB。

FPGA可编程逻辑器件芯片EP4CE115F29C8LN中文规格书

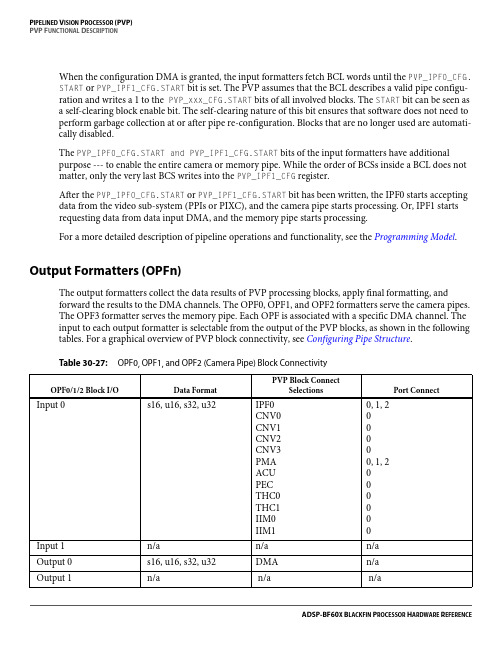

PIPELINED VISION PROCESSOR (PVP) PVP FUNCTIONAL DESCRIPTION

• If PVP_IIMn_SCALE.HSCL =7, the IIMn outputs only every 8th column.

• Supports independent scaling in both directions

The output frame size is selectable in steps of 16. The values supported are: 16 × n × 16 × m where n,m=1,2,...,8. The output size is programmed in the PVP_UDS_OHCNT and PVP_UDS_OVCNT registers.

M L

,QS, - 6$7, - 6$7, - 6$7, -

As with integral row mode, the initial values of the integral are assumed to be zero—SAT-1,J = 0 and SATI,1 = 0. In the SAT output map, each value contains the accumulated input values from the frame's origin to the actual position, as shown in the Illustration of SAT Mode figure.

Camera pipes and memory pipes can operate concurrently. The pipes have separate control mechanisms, have separate data paths, and operate with independent timing. The camera and memory pipes do share

BeagleboneBlack教程项目1闪烁板载LED

BeagleboneBlack教程项⽬1闪烁板载LED Beaglebone Black教程项⽬1闪烁板载LED项⽬1闪烁板载LED当设置完你的Beaglebone Black的时候,可能早就⾮常期待你的第⼀个项⽬了。

下⾯就来满⾜⼤家的愿望,当然,这个项⽬可不是惊天动地的⼤项⽬,但万事总是有个开始的。

这个项⽬不需要额外的电⼦器件,这可以让你的精⼒集中在编程这⽅⾯来。

这也可以确保你的Beaglebone Black板⼦所有的设置都是正确的。

闲话少叙,我们的这个项⽬是编写代码控制Beaglebone Black的板载LED。

如果你之前有过编程经验,那么可以把这个项⽬当做Beaglebone Black的“Hello World”程序。

我们将会从零开始完成整个程序,这样可以使你在Cloud9 IDE中编写BoneScript代码有⼀个初步的感觉。

下⾯的就是闪烁板载LED的代码:var b = require('bonescript');var led = "USR3";b.pinMode(led, b.OUTPUT);var state = b.LOW;b.digitalWrite(led, state);setInterval(toggle, 1000);function toggle() {if(state == b.LOW) state = b.HIGH;else state = b.LOW;b.digitalWrite(led, state)}当使⽤BoneScript编写代码的时候,我们需要将代码指向BoneScript库以访问GPIO端⼝和Beaglebone Black的其他功能。

所以,我们的第⼀⾏代码就创建⼀个变量(b)来将两个括号之间的库引⼊我们的代码:var b = require('bonescript');代码的下⼀个逻辑上的代码段是创建引⽤板载LED USR3的⼀个变量:var led = "USR3";在上⾯的例⼦中我们将这个变量称为led,它对应于板载LED的USR3。

element14 BeagleBone Black用户手册_V2.0

用户手册

版本 2.0– 2014 年 5 月 7 日

英蓓特科技有限公司

i

版权声明:

中国版 BB-Black 开发套件及其相关知识产权由深圳市英蓓特科技有限公司所有。 本文档由深圳市英蓓特科技有限公司版权所有,并保留一切权利。在未经英蓓特 公司书面许可的情况下,不得以任何方式或形式来修改、分发或复制本文档的任 何部分。 Microsoft, MS-DOS, Windows, Windows95, Windows98, Windows2000, Windows xp, Windows Embedded Compact 7 由微软公司授权使用。

element BeagleBone Black 用户手册

英蓓特科技有限公司

ii

目录

第 1 章 产品概述 .................................................................................................................. 1 1.1 产品介绍................................................................................................................. 1 1.2 包装内容................................................................................................................. 1 1.3 硬件特性................................................................................................................. 2 1.4 系统框图................................................................................................................. 4 1.5 硬件尺寸(毫米) .................................................................................................. 4 第 2 章 硬件系统介绍 .......................................................................................................... 5 2.1 CPU 简介 ................................................................................................................ 5 2.1.1 时钟信号 ...................................................................................................... 5 2.1.2 复位信号 ...................................................................................................... 5 2.1.3 通用接口 ...................................................................................................... 6 2.1.4 可编程实时单元和工业通讯子系统 .............................................................. 6 2.1.5 3D 图形引擎 ................................................................................................. 6 2.2 CPU 周边芯片 ......................................................................................................... 6 2.2.1 TPS65217 电源管理芯片.............................................................................. 6 2.2.2 KE4CN2H5A eMMC Flash 存储器 ............................................................... 7 2.2.3 MT41K256M16HA-125 DDR 存储器............................................................ 7 2.2.4 LAN8710A-EZC-TR Ethernet 芯片 .............................................................. 7 2.2.5 TDA19988 发送器 ........................................................................................ 7 2.3 接口/按钮/LED ....................................................................................................... 8 2.3.1 电源接口(P1) .......................................................................................... 8 2.3.2 JTAG 接口(P2)......................................................................................... 8 2.3.3 USB Host 接口(P3).................................................................................. 9 2.3.4 USB Device 接口(P4) .............................................................................. 9 2.3.5 LAN 接口(P5)......................................................................................... 10 2.3.6 HDMI D Type 接口(P6) .......................................................................... 10 2.3.7 调试串口(J1) ......................................................................................... 11 2.3.8 右扩展接口(P8) ..................................................................................... 11 2.3.9 左扩展接口 2(P9) .................................................................................. 13 2.3.10 按钮 ......................................................................................................... 14 2.3.11 LED 指示灯 ............................................................................................... 14

altium窗口菜单中英文对照表

- ..Altium_Designer(protel_DXP)英文菜单汉化对应表表2021-01-08 17:065964人阅读评论(0)收藏举报分类:硬件〔100〕%s - No SI model for part%s - 没有部件的SI模型%s Degrees%s 度%s mm%s 毫米%s object selected in %s document在%s个文档有%s个对象被选中%s Objects Displayed (%s Selected)%s 对象显示(%s 被选择)%s objects selected%s 对象被选择(custom)(自定义)(pixels)(像素)+12 Power Port+12 电源端口+5 Power Port+5 电源端口-5 Power Port-5 电源端口0 Hidden ment strings0 隐藏注释行0.01uF Capacitor0.01uF 电容0.1uF Capacitor0.1uF 电容1 Locked ponents1 锁定元件1 By Ascending X Then Ascending Y根据X递增量决定Y递增量1.0uF Capacitor1.0uF 电容100K Hertz Pulse100KHz 脉冲100K Hertz Sine Wave100KHz 正弦波100K Resistor100K 电阻10K Hertz Pulse10KHz 脉冲10K Hertz Sine Wave10KHz 正弦波10K Resistor10K 电阻10uF Capacitor10uF 电容1K Hertz Pulse1KHz 脉冲1K Hertz Sine Wave1KHz 正弦波1K Resistor1K 电阻1M Hertz Pulse1MHz 脉冲1M Hertz Sine Wave1MHz 正弦波2 Pads and vias with a hole size between 15and 302 焊盘和过孔的孔大小在15-30之间2.2uF Capacitor2.2uF 电容4 All testpoints4 全部测试点4 Port Serial Interface4 端口串行接口4.7K Resistor4.7K 电阻47K Resistor47K 电阻5 ponent track and arc silkscreenprimitives5 元件丝印层的根本线和弧线A KeywordA关键字Abort Simulation终止仿真About Design Explorer关于设计浏览器Absolute绝对Absolute Layer绝对层Absolute Origin绝对原点AC Small Signal Analysis Setup交流小信号分析配置Accept Changes (Create ECO)成认改变(建立ECO)Access Code验证码Accuracy精度Activates open documents激活显示文本Active Low Input激活低电平输入Active Low Output激活低电平输出Active project当前激活工程Active sheet当前激活图纸Active Signals激活的信号Add All添加全部- ..Add All Waveforms添加全部波形Add as Rule作为规那么添加Add Assembly Outputs增加装配输出Add Class添加分类Add ponent Part添加元件部件Add Document增加文本Add Document to Focused Project添加文档到当前工程Add Documentation Outputs增加文本输出Add Existing Project添加已存在的工程Add Fabrication Outputs增加生产输出Add first condition添加首要条件Add From To添加From ToAdd Internal Plane增加电层Add Layer添加层Add Library添加库Add License添加许可证Add Net添加网络Add Net Class添加网络分类Add Netlist Outputs增加网表输出Add New Cursor增加标Add New Model添加新模式Add New Project添加新工程Add One添加一个Add or Remove Libraries添加或移出库文件Add Other Outputs添加其他输出Add Plane添加电层Add Plot增加图表Add Project To Version Control将工程添加到版本控制Add Remove ponent Libraries添加移出元件库Add Remove Libraries添加/移出库文件Add Reports增加报告Add Selected添加选择的Add Selected Primitives to ponent添加所选根本元素到元件Add Sheet Entry添加图纸入口Add Signal Layer增加信号层Add Suffix加后缀Add Template to Clipboard添加模板到剪贴板Add To Current Sheet添加到当前图纸Add to Custom Colors添加到自定义颜色Add To Design添加到设计Add To Entire Project添加到整个工程Add to new Y axis增加到新Y轴Add to Project添加到工程Add To Sheet添加到图纸Add To Version Control添加到版本控制Add top level signals to waveform给波形增加顶层信号Add Variant添加变量Add Watch增加监视Add Wave增加波形Add Wave To Plot给图表增加波形Add Waveform增加波形Add waveforms to the new plot给新图表增加波形Add Y Axis增加Y 轴Add/Edit Model增加/编辑模型Add/Remove Libraries装载/移出库文件Add/Remove Library装载/移出库AddAlias添加别名Advanced (Query)高级(查询)Advanced Mode高级模式Affected Document所影响的文本- ..Affected Object所影响的对象Aggregate合计Align Bottom底部对齐Align ponents对齐元件Align ponents by Bottom Edges根据元件下缘对齐Align ponents by Horizontal Centers元件居中对齐Align ponents by Left Edges元件左边对齐Align ponents by Right Edges元件右边对齐Align ponents by Top Edges元件对齐顶部边缘Align ponents by Vertical Centers根据垂直中心对其元件Align Left左对齐Align Right右对齐Align Top顶部对齐Aligned - Bottom对齐- 底部Aligned - Center对齐- 中心Aligned - Inside Left对齐- 部左边Aligned - Inside Right对齐- 部右边Aligned - Left对齐- 左边Aligned - Right对齐- 右边Aligned - Top对齐- 顶部all全部All ponents全部元件All Draft全部草图All Final全部最终All Hidden全部隐藏All Locked全部锁定All Nets全部网络All Off全部关闭All On全部翻开All On Current Document全部当前文档All on Layer全部翻开层All open schematic documents所有翻开原理图文档All Orientations所有方向All schematic documents in the currentproject当前工程中所有原理图文档All Text Docs全部文本文件Allow Dock允许停放Allow multiple testpoints on same net允许同一网络多个测试点Allow Ports to Name Nets允许端口到网络名Allow Sheet Entries to Name Nets允许图纸入口到网络名Allow Short Circuit允许电路短路Allow Synchronization With Database允许和数据库同步Allow Synchronization With Library允许和库同步Allow testpoint under ponent元件下允许测试点Allow Vias under SMD PadsSMD焊盘下允许过孔Allowed Orientations允许方向Allowed Side and Order允许边和定制Alpha字母Alpha Numeric字母数字Alpha Numeric Suffix字母数字下标Alphabetically字母顺序Alternate 1另一选择1Alternative其他选择Always load error file总是加载错误文件Amplitude振幅Analog模拟Analog +12V (+12V)模拟+12V (+12V)Analog +5V (+5V)模拟+5V (+5V)Analog Ground (AGND)模拟地(AGND)Analog Routing 1模拟布线层1Analog Routing 2模拟布线层2- ..Analog Routing 3模拟布线层3Analog Signal In模拟信号输入Analyse分析Analyses Setup分析配置Analyses/Options分析/选项Analysis分析Analysis Errors分析错误Analyze Design分析设计Analyze Document分析文档And Gate与门And to wrap long lines增加到可交换长行Angular角形Angular Dimension角度Angular Step角幅Animation speed动画速度Annotate标注Annotation注释Anode正极ANSIANSIAny任何Aperture File (using Wizard formats)光圈文件(利用向导格式) Aperture Library光圈库Aperture List光圈列表Aperture Matching TolerancesD码表匹配公差Append Sheet Numbers to Local Nets附加图纸编号到本地网络Applicable Binary Rules适用的二元规那么Applicable Rules适用的规那么Applicable Unary Rules适用的一元规那么Apply Filter应用过滤器Apply to Active Chart Only仅适用于激活图表Apply to Entire Document适用于整个文本Arc弧线Arc (Any Angle)弧形(任何角度)Arc (Center)弧形(定中心)Arc (Edge)弧形(边限)Arc Line Width弧线宽度Arc Radius圆弧半径Architecture构造Archive project document存档工程文件Arcs弧形Arithmetic算法Around Point附近的点Arrange All Windows Horizontally水平排列所有窗口Arrange All Windows Vertically垂直排列所有窗口Arrange ponents Inside Area在区域排列元件Arrange ponents Within Room在布局空间排列元件Arrange Outside Board在底边界外排列Arrange Within Rectangle在矩形里排列Arrange Within Room在布局空间里排列Arrow Length箭头长度Arrow Line Width箭头线宽度Arrow Position箭头位置Arrow Size箭头大小Arrow Style Power Port发射型电源端口Arrow Width箭头宽度Articles and Tutorials文章和教程Assembly %s装配%sAssembly Drawings装配制图Assembly Outputs装配输出At Margin在页边距- ..At Window在窗口Attributes on Layer层上属性Auto Create posite自动创立合成Auto indent mode自动缩进模式Auto Pan Fixed Jump自动平移固定围Auto Pan Off自动平移关闭Auto Pan Options自动平移选项Auto Pan ReCenter自动平移至中心Auto Placement自动布局Auto Placer自动放置Auto Route自动布线Auto save every自动保存间隔Auto Zoom自动缩放Auto-Increment During Placement在布局时自动增加Auto-Junction自动加节点Auto-Position Sheet自动定位图纸Automatic (Based on project contents)自动〔基于工程容〕Automatically crossprobe first error自动穿插检索第一个错误Automatically Remove Loops自动去除回路Autopan Options自动位移选项Autoposition自动定位Autosave desktop自动保存桌面设置Available Libraries当前库Available Routing Strategies可用的布线策略Available Signals可用的信号Average Track Length (mil)平均铜线长度〔mil〕Avg平均Avoid Obstacle避开障碍物Back Annotate反向标注Background背景Backspace unindents回车取消缩进Backup Files备份文件Backup Options备份选项Ball Grid Arrays (BGA)BGABallistic可变速度移动Bank1组列1Bank2组列2Bar Style Power Port条型电源端口Bar to use as Main Menu栏作为主菜单使用Bar Type栏类型Bars栏Base Value低电平Baseline基线Baseline Dimension基线尺度Basic DC根本直流Batch批处理Batch Mode批命令模式Begin Group开场分组Below is a list of all the processesprovided by this server以以下表是此效劳提供的所有处理模块Beta DegBeta降级Bezier曲线BGA OptionsBGA 选项Bidirectional Signal Flow双向信号流向Bill of Materials材料清单Bill of Materials (By PartType) For Project[%]工程[%s]物料清单(元件类型)Bill of Materials For PCB%sPCB %s材料清单Bill of Materials For Project %s工程材料清单%sBitmap File位图文件Blank Project (Embedded)空白工程(嵌入式)- ..Blank Project (FPGA)空白工程(FPGA)Blank Project (Library Package)空白工程(库包) Blank Project (PCB)空白工程(PCB)Block Indent块缩进Block Name块名称Block Name : %s块名称: %sBoard板Board Area Color板区域颜色Board Dimensions板尺寸Board in 3D3D 板视图Board Information板信息Board La&yers & Colors板层和颜色Board La&yers && Colors板层和颜色Board Layers Colors板层颜色Board Layers & Colors板层和颜色Board Layers and Colors板层和颜色Board Line Color板层线颜色Board Options板选项Board Shape板形Board Specifications板技术参数Bold Waveforms实线波形BOOLEAN布尔数学体系Border (Auto-Detect)边界(自动探测)Border Color边框颜色Border On边框显示Border Width边框宽度Bottom底层Bottom Dielectric底部绝缘层Bottom Layer底层Bottom Layer Annular Ring Size底层圆环尺寸Bottom Overlay底层丝印层Bottom Paste底层焊锡层Bottom Solder底层阻焊层Bottom Solder Mask底层阻焊层BottomLayer底层BottomOverlay底层丝印层Brackets支架Break All ponent Unions从单元中别离出所有元件Break ponent from Union从单元中别离出元件Break Track断开轨迹Breakpoints断点Brightness亮度Bring To Front Of带到某对象前面Browse浏览Browse ponent Libraries浏览元件库Browse ponents浏览元件Browse Libraries浏览库Browse Library浏览库文件Bubble Help Advisor (Shift+F1)浮动帮助参谋(Shift+F1) Build posite构造合成Build Later后来再建Build PCB Project构造PCB 工程Build Project构造工程Build Query构造智能语句Build Sooner立即创立Build-Up绝缘层对Building Query from Board从板构造查询Bus总线Bus Entry总线入口Bus indices out of range总线超出围- ..Bus range syntax errors总线围语法错误Bus Width总线线宽By class通过类By document type通过文本类型C MenuC 菜单C StandardC 标准Calc. Copper Area计算.铜面积Calculated Impedance =计算阻抗=Calculated Trace Width =计算线宽=CAM DocumentCAM 文档CAM EditorCAM 编辑器Cannot Locate Document %s无法找到%s文档信息Capacitance电容Capacitor电容Capacitors电容Categories类别Cathode负极Center Dimension中心点尺度Center Horizontal水平居中Center of Object对象中心Center Vertical垂直居中Change Language更换语言Change Order改变顺序Change System Font改变系统字体Change Technology改变封装技术Channel Offset通道偏移Characteristic Impedance Driven Width特性阻抗驱动线宽Chart制图Chart name is blank图表名称为空Chart Options图表选项Check All ponents检查所有元件Check In签入Check Mode校验模式Check Out签出Check Syntax校验语法Choose a snap grid size选择捕获网格尺寸Choose Color选择颜色Choose cursor to delete选择要光标删除Choose cursor to jump to选择要跳转到的光标Choose Default Backup Folder选择缺省的备份文件夹Choose Default Document Folder选择缺省文档文件夹Choose Design Rule Type选择设计规那么类型Choose Document选择文档Choose Document Scope选择文档围Choose Document to Open选择要翻开的文档Choose Document to Place选择文档放置Choose Documents选择文档Choose Documents to Add to Project %s选择文档加到工程%sChoose Documents To pare选择比拟文档Choose documents to pare - one from theleft list and one from the right list选择比拟文档- 一个从左面列表另一个从右面列表选择Choose Project选择工程Choose Project Group to Open选择要翻开的工程组Choose Project to Open选择要翻开的工程Choose second corner选择第二角Choose the document to pare against thedesign hierarchy of %s选择与设计层次%s进展比拟的文本Choose the document to pare against thedesign hierarchy of Documents.PRJPCB选择与工程文本的层次设计进展比拟的文本Choose Top Level选择顶层- ..Choose WAS-IS File for Back-Annotation fromPCB从PCB选择WAS-IS文件作为反向注释Circle Style Power Port循环型电源端口Circuit电路Circuit Simulation电路仿真CKTCKTClamping箝位Class I分类IClass II分类IIClass Type类型Classes分类Classic Color Set典型颜色设置Clean All Nets去除全部网络Clean Single Nets去除单一网络Clear All Nets去除全部网络Clear All Test points去除全部检测点Clear All Testpoints去除全部测试点Clear Browser Marks去除浏览器标记Clear Class去除类别Clear Current Filter去除当前过滤器Clear Current Filter (Shift+C)去除当前过滤器(Shift+C)Clear Existing去除已存在Clear Filter去除过滤器Clear History去除历史Clear Memory去除存储器Clear non-numerical values去除非数字的值Clear Selected去除已选Clear Status去除状态Clear workspace pile messages onpile编译时去除工作空间编译信息Clearance间距Click Clears Selection单击去除选择Click on the finish button to plete thetask在完毕按钮上点击完成任务Client客户端Client License Usage客户端许可证用法Client Setup客户端设置Clip to Area显示框文本Clipboard Reference剪贴板属性clock时钟Close 'pile Errors'关闭‘编译错误’面板Close 'piled Object Debugger'关闭‘编译对象调试器’面板Close 'Differences'关闭‘差异’面板Close 'Files'关闭‘文件’面板Close 'Help Advisor'关闭‘帮助参谋’面板Close 'Inspector'关闭'检视器'Close 'Libraries'关闭'库'Close 'List'关闭'列表'Close 'Messages'关闭‘消息’面板Close 'navigator'关闭‘浏览器’面板Close 'Projects'关闭‘工程’面板Close All Documents关闭全部文件Close posite关闭合成Close Documents关闭文档Close Focused Project关闭当前工程Close Project关闭工程Close Project Documents关闭工程文档Collapse Row折叠行Collect Data For数据收集类型Collector集电极Color Options颜色选项Color Set颜色设置- ..Colors && Gray Scales色彩/灰度级Colours颜色Column Best Fit适应列宽mand Reference命令参考mand Status命令状态栏ment type注释类型p Drag拖动比拟parator比拟器parison Type Description比拟类型描述pile Active Document编译当前文档pile Active Project编译当前工程pile All编译全部pile All Open Projects编译全部已翻开的工程pile All Projects编译所有工程pile Current Project编译当前工程pile Document编译文档pile Errors编译错误pile FPGA Project编译FPGA 工程pile Later后来再编译pile Library编译库pile only if modified仅编译修改之后pile PCB Project编译PCB 工程pile Project编译工程pile Sooner立即编译piled编译piled Object Debugger编译对象调试器piler Options编译选项piling %s正在编译%spiling Flattened Project编译平行工程plex Data复杂数据ponent元件ponent %s元件%sponent Actions元件操作ponent Class Generator元件分类发生器ponent Classes元件分类ponent ment元件注释ponent Connections元件连接ponent Cross Reference元件互相参照ponent Cross Reference Report ForProject %s工程元件穿插参考报告%s ponent Designator%s元件标识符%sponent Grid元件网格ponent Links元件ponent Name部件名ponent Names元件名称ponent Naming元件命名ponent Nets元件网络ponent Parameter元件参数ponent Pin Designator元件引脚标识符ponent Pin Editor元件引脚编辑器ponent Pins元件引脚ponent Placement元件布局ponent Primitives元件根本元素ponent Properties元件属性ponent Report元件报告ponent Rule Check元件规那么检查ponent scope for filtering andselection过滤及选择元件的围ponent Side元件层ponent Type元件类型ponent Types元件类型ponent Wizard元件向导- ..ponent Wizard - Pin Grid Arrays (PGA)元件向导- PGAponents元件ponents Cut Wires元件切线posite Drill Guide合成钻孔向导posite Layers合并层posite Properties合成特性Condition Type / Operator类型/操作状态Condition Value条件值Conductor Width导体宽度Conductors导体Configure Drill Pairs配置钻孔层对Configure Licenses配置软件许可证Configure PLD piler配置PLD编译Configure Project Options for ActiveProject为当前工程配置工程选项Confirm Delete Parameter确认删除参数Confirm Global Edit确定全局编辑Confirm Remove %s确认删除%sConfirm remove the layer %s确认是删除层%sConfirm Selection Memory Clear选择存储器去除时确认Connect Layer连接层Connect Style连接样式Connect To连接到Connect to Net连接到网络Connect Wire Check接线检查Connect Wire Extractor接线数据Connected Copper连接铜线Connected Tracks连接铜线Connection Color连接颜色Connection Matrix连接矩阵Connector连接器Connector Type连接器类型Constant Level常数等级Constraints约束限制Contract All全部压缩Convert Part To Sheet Symbol转换元件为图纸符号Convert Selected Free Pads to Vias将所选自由焊盘转换为过孔Convert Selected Vias to Free Pads将所选过孔转换为自由焊盘Convert Special Strings转换特殊字符串Convert to DXP Plane Mode转换为DXP电层模式Coordinate坐标Coordinate Positions坐标位置Copper thickness铜厚度Copy (Ctrl+C)复制(Ctrl+C)Copy ponent复制元件Copy Footprint From/To复制封装从/到Copy on Field复制域Copy preexisting edif models whenavailable当可访问到时拷贝已经存在的EDIF模型Copy Room Formats复制布局空间格式Copy to Layers复制到层Copyright ?Altium Limited 2002 Altium 所有2002Core (%s)核心(%s)Corner角Corner 1角1Corner 2角2Corrections校正Coupling耦合Create a new Board Level Design Project创立新的板级设计工程Create a new FPGA Design Project创立新的FPGA设计工程Create a new Integrated Library Package创立新的集成库包Create backup files创立备份文件- ..Create piled SimCode output file创立编译SimCode输出文件Create ponent创立元件Create Engineering Change Order创立工程改变顺序(ECO)Create Expression创立表达式Create FFT Chart新建FFT图表Create Library创立库Create List From PCB从PCB建表Create Netlist From Connected Copper从连接的铜板创立网表Create New Chart新建图表Create New Database新建数据库Create Non-Orthoganal Room from selectedponents根据所选元件创立非正交布局空间Create Non-Orthogonal Room from ponents根据元件创立非正交布局空间Create Orthogonal Room from ponents根据元件创立正交布局空间Create Orthogonal Room from selectedponents根据所选元件创立正交布局空间Create Pairs From Layer Stack从层堆栈中创立层对Create Pairs From Used Vias从所用过孔中创立层对Create Projects from Path从指定路径创立工程Create Rectangle Room from selectedponents根据所选元件创立矩形布局空间Create Rectangular Room from ponents根据元件创立矩形布局空间Create Report建立报告Create Report File创立报告文件Create Rule创立规那么Create Sheet From Symbol从符号创立图纸Create Symbol From Sheet从图纸创立符号Create Union from ponents从元件创立单元Create Union from Selected ponents根据所选元件创立单元Create VHDL File From Symbol从符号创立VHDL 文件Create VHDL from FPGA-Part从FPGA 零件创立VHDLCreate VHDL Testbench创立VHDL 测试平台Create Violations创立违规信息Cross Probe插入探针Cross Probe to Documents文档中插入探针Cross Probe to Schematic穿插检索到原理图Crossing Window穿插窗口Crossprobe schematic穿插检索原理图Crosstalk串扰Crosstalk Analysis串扰分析Crosstalk Waveforms串扰分析CTRL+Double Click Opens SheetCTRL+双击翻开图纸Current ponent当前元件Current Document当前文档Current Font当前字体Current Layer当前层Current Origin当前原点Current Page当前页Cursor A光标ACursor B光标BCursor beyond EOFEOF的光标Cursor beyond EOLEOL的光标Cursor Grid Options指针网格选项Cursor through tabs通过Tab移动光标Cursor Type光标类型Curve Width曲线宽度Custom Aperture Library File (*.LIB)自定义光圈库文件(*.LIB)Custom Height自定义高Custom Size自定义大小Custom Step定制调试Custom Style自定义风格Custom Width自定义宽- ..Customize Resources自定义资源Customizing DefaultEditor Editor用户缺省自定义编辑器Customizing PCB Editor自定义PCB 编辑器Customizing PCBLib Editor自定义PCBLib编辑器Customizing Sch Editor自定义原理图编辑器Customizing SchLib Editor定制原理图库编辑器Customizing VHDL Editor自定义VHDL编辑器Cut (Ctrl+X)剪切(Ctrl+X)Cutout挖除局部Darken调暗Data Process接线数据处理Database Connection数据库连接Database key field数据库关键字段Database Link File数据库文件Database Link Options数据库选项Database Linking数据库Database Linking Menu数据库菜单Database Links数据库DatabaseLink数据库Datasheet数据表Datum数据Datum Dimension数据尺度DC AnalysisDC分析DC Sweep Analysis Setup直流扫描分析配置Debugging Options调试选项Decision判定Declare ponent At Cursor在指针指向元件显示说明Decrease减少Decrease Horizontal Spacing of ponents减小元件水平间距Decrease Priority降低优先级Decrease Vertical Spacing of ponents减小元件的垂直间距default默认Default Background默认背景Default Bars缺省面板Default Color Set默认颜色设置Default Designator缺省名称Default File Name缺省文件名Default Locations默认位置Default Power Object Names默认电源对象名称Default Primitives默认根本元素Default Prints默认打印Default Shortcuts默认快捷方式Default Stimulus默认鼓励Default Template Name缺省模板名Default time units默认时间单位Default Value默认值Default Vendor Family默认厂家芯片系列DefaultEditor默认编辑DefaultRowHeight默认行高Define from selected objects从所选对象定义Define the layout of the PGA footprint byselecting the proper values选择适当的值定义PGA封装引脚布局degrees度数Delete All全部删除Delete All Cursors删除全部光标Delete All Waveforms删除全部波形Delete Chart删除图表Delete Class删除分类Delete Current Cursor删除当前光标Delete Cursor删除光标- ..Delete generated files before pile编译之前删除生成的文件Delete Net删除网络Delete Net Class删除网络分类Delete Plot删除坐标图Delete Watch删除监视Delete Waveform删除波形Delta Step增量调试Demote降级Density Map密度图Deselect All取消全部选择DeSelect All On Current Document取消选择当前的全部文档Design设计Design Documents设计文本Design Explorer DXP DXP 设计浏览器Design Explorer DXP - %s设计浏览器DXP - %sDesign Explorer Error设计浏览器错误Design Explorer Information设计浏览器信息Design Explorer Preferences设计浏览器属性Design Explorer Project Manager设计浏览器工程管理器Design Explorer Version 7.1.70设计浏览器版本7.1.70 Design Explorer Version 7.2.92设计浏览器版本7.2.92 Design Explorer Warning设计浏览器告警Design Rule Check设计规那么检查Design Rule Checker设计规那么检查Design Rules设计规那么Designator标识符Designator Display标识符显示Designator Format标识符格式Designator Index Control标识符指针控制Designators标识符Destination Library目标库Device Family器件系列Dielectric constant绝缘材料常数Dielectric Properties绝缘体属性Differences差异Different不同Digital Ground (GND)数字地层(GND)Digital Objects数字对象Digital Power (VCC)数字电源层(VCC)Digital Routing 1数字布线层1Digital Routing 2数字布线层2Digital Routing 3数字布线层3Digital Routing 4数字布线层4Digital Routing 5数字布线层5Digital Routing 6数字布线层6Digital Signal In数字信号输入Digital supply VCC数字电源VCCDigital Supply VDD数字电源VDDDimension标注线Dimensions标注线Diode二极管Diodes二极管Direction From Pad出焊盘方向Directive Options提示选项Directives指令Disable不激活Disable All全部禁用Disable All Watches禁用全部监视Disable dragging取消拖动Disable Update All取消修改全部- ..Disable Update Selected取消修改选择的Disable Watch禁用监视Display Cross Sheet Connectors显示图纸间连接符Display FFT Charts显示FFT图表Display Full Hierarchy显示全部层次Display Graphical Lines显示图形线条Display Logical Designators显示逻辑标识符Display Mode显示模式Display Name显示名称Display Net Labels显示网络标志Display No Hierarchy显示没有层次图Display Options显示选项Display Physical Designators显示物理标识符Display Pins显示引脚Display Ports显示端口Display Printer Fonts显示打印字体Display Report显示报告Display shadows around menus, toolbars andpanels显示菜单, 工具栏, 面板的阴影Display Sheet显示图纸Display Sheet Entries显示图纸入口Display Sheet Symbols显示图纸符号Display Symbols显示符号Display System Information显示系统信息Distance factor距离因素Distribute Horizontally水平居中分布Distribute Vertically垂直居中分布Division Size分割尺度Do not group不分组Do you wish to delete the Parameter你希望删除这个参数Documen文本Document Editors文档编辑器Document Name文档名称Document Options文档选项Document Order文档顺序Document Parameters文本参数Document Path文档路径Document scope for filtering and selection过滤选择文档围Documentation %s文本%sDocumentation Output文本输出Documents for %s%s 文档Documents for Free Documents文档为自由文档Does nothing无任何操作Don't Annotate ponent不注释元件Don't care不关注dot点Dot Grid网格点Dotted点Double click line双击行Double Click Runs Inspector鼠标双击那么运行检视器Double Sided双面Draft Thresholds草图起点Drag拖动Drag a column header here to group by thatcolumn拖动一列标头到这列用于分组Drag Orthogonal直角拖动Drag Selection拖动选择容Drag Track End拖动轨迹末端Draw Solid画实线Draw to Custom Aperture自定义光圈绘图Drawing制图Drawing Tools制图工具- ..DRC Error MarkersDRC 错误标记DRC Report OptionsDRC报告选项DRC ViolationsDRC违规数Drill钻孔机Drill Drawing钻孔图Drill Drawing Plots钻孔绘制图Drill Drawing Symbols钻孔绘制符号Drill Drawings钻孔图Drill Guide钻孔向导Drill Guide Plots钻孔导向图Drill Pair Properties钻孔层对属性Drill Pairs钻孔配对层Drill-Pair Manager钻孔层对管理器Drill-Pair Properties钻孔对属性DrillDrawing钻孔图DrillGuide钻孔向导Dual in-line Package (DIP)DIPDuplicate Selected复制被选DXP Help AdvisorDXP 帮助指导DXP Knowledge BaseDXP 知识库DXP Learning GuidesDXP 学习指南DXP Online helpDXP 在线帮助Dynamic动态Dynamic transparency动态透明效果Earth接地Earth Power Port接地电源端口ECO GenerationECO 启动EDA ServersEDA 效劳Edge Connectors边缘连接器EDIF MacroEDIF宏EDIF MenuEDIF 菜单EDIF StandardEDIF 标准Edit Buffer编辑缓冲Edit mand编辑命令Edit ment编辑注释Edit Full Pad Layer Definition编辑完整的焊盘层Edit Keyword Properties编辑关键字属性Edit Language Syntax编辑语言语法Edit Layer编辑层Edit Library编辑库Edit Net编辑网络Edit Net Class编辑网络分类Edit Nets编辑网络Edit Number编辑编号Edit Pins编辑引脚Edit Polygonal Room Vertices编辑多边形空间的顶点Edit Rule Priorities编辑规那么优先级Edit Rule Values编辑规那么数值Edit Selected编辑被选Edit Simulation Signals编辑仿真信号Edit String编辑字符串Edit Style编辑风格Edit Values编辑值Edit Variant编辑变量Edit Wave编辑波形Editing Options编辑选项Editor Preferences参数选择编辑器EditScript编辑脚本Eight Layer (5 x Signal, 3 x Plane)八层〔5信号层,3电层〕Elaborate and generate on pile编译时详细阐述和产生- ..Electrical Grid电子网格Electrical Type电气类型Ellipse椭圆形Elliptical Arc椭圆的弧线Embedded嵌入Embedded apertures (RS274X)嵌光圈表[RS274X]Embedded Project嵌入式工程Embedded Projects嵌入式工程Emitter发射极Enable All全部启用Enable All Watches启用全部监视Enable Font Substitution允许字型替换Enable In-Place Editing启用位置编辑Enable Update All使能修改全部Enable Update Selected使能修改选择的Enable Version Control允许版本控制Enable Watch启用监视Enabled激活End Angle完毕角度End Layer完毕层Enforce layer pairs settings执行层对设置Engineering Change Order工程改变单Entity/Configuration实体/配置Equalize Net Lengths补偿网络长度Error Marker错误标记Error Reporting错误报告Errors Detected监测到错误Errors or warnings found发现错误或告警Esc取消Example Layer Stacks层堆栈举例Examples例Excel Template FilenameExcel 模板文件名Exclude IEEE Directory不包括IEEE目录Exclude System Parameters拒绝系统参数Execute Changes执行改变Expand Row扩展行Expansion扩展Expansion value from rules从规那么扩展值Expiry Date有效期限Explode拆解Explode ponent to Free Primitives将元件拆解为自由的根本元素Explode posite拆解合成Explode Coordinate to Free Primitives将坐标拆解为自由的根本元素Explode Dimension to Free Primitives将尺度标注拆解为自由的根本元素Explode Polygon to Free Primitives将多边形敷铜拆解为自由的根本元素Explore浏览Explore Differences探测差异ExplorerFramePanel管理器框架面板Exponential/Logarithmic指数/对数Export Grid Contents导出容Export Netlist From PCB从PCB 导出网表Export Selected Waveforms导出选择的波形Export to PCB导出到PCBExport Using Template导出使用模板Expression表达式Extension Width延伸宽度Fabrication %s生产%sFabrication Outputs生产输出Falling Edge Flight Time下降沿延迟时间Falling Edge Overshoot下降沿过冲- ..Falling Edge Slope下降沿斜率Falling Edge Undershoot下降沿下冲False错误Fanout扇出Fanout DirectionFanout 方向Fanout OptionsFanout 选项Fanout StyleFanout 风格faster快Fatal Error严重错误File Mask文件过滤Files Found on All Search Paths在全部路径上查找到的文件Fill Color填充颜色Fills填充Film Box胶片盒Film Size胶片尺寸Film Wizard胶片向导Filter过滤Filter browsed objects过滤浏览对象Filter For过滤Filtered Objects过滤对象Final最终Final Properties最终属性Find and Replace Text查找并替换文本Find and Set Testpoints选择和设置测试点Find ponent查找部件Find Coupled Nets发现耦合网络Find Selections查找选择容Find Similar Objects找出相似对象Find text at cursor光标位置查找文本First ponent第一个元件First Layer首层First Page首页First Transition首次转换Fit All Objects适合全部对象Fit Board适合底板Fit Document适合大小文档Fit Document (Ctrl+PgDn)适合大小文档(Ctrl+PgDn)Fit Filtered Objects适合过滤对象Fit Selected适合选择Fit Selected Objects适合选中对象Fit Sheet适合图纸Fit Specified Area适合指定区域Fit Waveforms适合波形Fixed Size Jump固定步长跳转Flat (Only ports global)平面〔只对全局端口〕Flip Selection翻转被选FLOAT浮点Focus Wave主波形Font Substitutions字型置换Footprint封装Footprint Model封装模型Footprint not found没有发现封装Footprints封装For a parallel gap of平行线间距Force Columns Into View所有列显示Force plete tenting on bottom在底部强制完全伸展Force plete tenting on top在顶部强制完全伸展Foreground前景Formal Type格式类型Format and Radix格式和基数- ..Format Axis格式化轴Format Wave格式化波形Format Y Axis格式化Y 轴Formats格式Formatting格式化Found in发现于Four Layer (2 x Signal, 2 x Plane)四层〔2信号层,2电层〕FPGA OptionsFPGA 选项FPGA PreferencesFPGA 参数选择FPGA ProjectFPGA工程FPGA ProjectsFPGA工程Free Documents自由文档Free Objects自由对象From To Display Settings飞线显示设置From Tos飞线From-To Editor飞线编辑器Full Circle圆环Full line ment全行注释Full Query完全查询Full Results全部结果Full Stack完全层叠Function Definitions函数定义Gap间隙Gear 2齿轮2Gear 3齿轮3Gear 4齿轮4Gear 5齿轮5Gear 6齿轮6Gear's Method 1st Order齿轮方法第1命令Gear's Method 2nd Order齿轮方法第2命令Gear's Method 3rd Order齿轮方法第3命令Generate Change Orders产生改变命令Generate DRC Rules产生DRC规那么Generate implicit modules for LPM, XBLOX orLogicB为LPM, XBLOX orLogicB产生隐含模块Generate Print Preview of Active Document生成激活文档的打印预览Generate Report生成报告Generate XSPICE Netlist生成XSPICE 连线表Generates pick and place files生成拾取和摆放文件Gerber FilesGerber文件Gerber SetupGerber设置Get Latest Version得到最后的版本Global (Netlabels and ports global)全局〔网络标号和全局端口〕GND Power Port接地电源端口Goto Line Number转到连线编号Graph图表Graphic图形Graphical图形Graphical Editing图形编辑Greater Equal大于等于Grid栅格Grid 1网格1Grid 2网格2Grid Color网格颜色Grid Range网格围Grid Size网格尺寸Grid Type栅格类型Grids网格Ground Plane 1 (GND)地平面层1(GND)Ground Plane 2 (GND)地平面层2(GND)。

FPGA可编程逻辑器件芯片EP4CE115F29C8L中文规格书

Mode 0 (continuous frame mode) is popular for camera pipe operation. Often, the camera pipe is enabled statically, and updates to the coefficients are only required from time to time. On demand software may enable the configuration DMA in stop mode to trigger the fetch of one single BCL. In this mode, the PVP_IPFn_TAG register is useful to match status results with a respective configuration. The new BCL only updates coefficients of processing blocks. The BCL does not alter the pipe configuration.Mode 1 (back-to-back mode) is useful in camera pipe mode when coefficients have to change every N th frame. This mode supports on-the-fly reprogramming of coefficients, but it does not support on-the-fly reprogramming of pipe configurations. The following settings must not change unless the DRAIN bit is set:•Pipe structure (PVP_xxx_CFG registers)•Fundamental operating modes (such as 1st-derivative to 2nd-derivative mode of PEC)•Input format and OPORT configuration (PVP_IPFn_CTL registers)•Horizontal size of input frame (HCNT)If any of the above settings change on-the-fly, the PVP_IPFn_PIPECTL.DRAIN bit must be set for proper operation to use Mode 2. In memory pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes of few clock cycles of overhead depending to pipeline depth. In camera pipe mode, the PVP_IPFn_PIPECTL.DRAIN bit causes the loss of an entire frame. Operation stops after the pipe has been drained and resumes with the next incoming VSYNC signal.Whenever the next PVP job stalls until the completion event of the data output DMA is flagged either as an interrupt or as a system trigger, setting the PVP_IPFn_PIPECTL.DRAIN bit is a requirement at the appli-cation level. The data output DMA work unit does not complete as long as related data sticks in the pipe. The data in the pipe does not progress until the configuration DMA and data source grant. Such deadlock situations can be avoided by using Mode 2. Once a deadlock occurs, it can be resolved by Mode 3 opera-tion.Mode 3 (drain now instruction) is more similar to a one-time instruction than an operating mode. This mode is used whenever software needs to respond to unpredictable events. For example, while the camera >01Mode 2: Auto-Completion ModeFCNT frames are requested by the IPFn, and these feed the pipe. The last datawords are automatically pushed out, and the operation automatically completes.If a new configuration is granted by DMA or by MMR writes, the configuration isapplied for the next FCNT set of frames.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.01Mode 3: Drain Now InstructionThis combination instructs the IPFn to flush all content out of the pipe.All processing blocks auto-disable. A new configuration must set all wanted STARTbits again.Table 30-47:Operating Modes by FCNT and DRAIN Selections (Continued)FCNT DRAINModeConfiguring with Daisy Chain MethodConfiguration and coefficient memory mapped registers (MMRs) of all processing blocks are double buff-ered. Whenever PVP_IPFn_FCNT is zero and the PVP_IPF0_CFG.START and PVP_IPF1_CFG.START bits =1, the values are copied from MMR registers into application buffers at the frame boundary. Due to the pipe-lined nature of the PVP, not all values are copied at the same time. Rather, the timing of value copying is closely related to how the VSYNC of the next frame progresses through the pipe. New settings apply to the first pixel of the new frame immediately after the last pixel of the old frame has been processed. The update command is daisy chained through the pipe, starting from the IPFn blocks through to the OPFn blocks. While sequencing through the daisy chain operation, hardware clears the PVP_xxx_CFG.START bits of all involved processing blocks in MMR space. Write conflicts can occur if software attempts to write the PVP_xxx_CFG registers during the daisy chain operation.The PVP_STAT register provides two status bits that report whether a daisy chain operation is ongoing in the camera pipes (PVP_STAT.CPDC ) or in the memory pipe (PVP_STAT.MPDC ). These bits are set along with the PVP_IPF0_CFG.START or PVP_IPF1_CFG.START bit and are cleared if the output formatters have been updated.In camera pipe mode, the PVP_STAT.CPDC bit is cleared only after the daisy chain progresses through the furthest of the enabled OPFn blocks. During this time, software should not write the PVP registers. If soft-ware mistakenly does write to these registers, the event is reported by the PVP_STAT.CPWRERR and PVP_STAT.MPWRERR flags. While all status bits in the PVP_STAT register are self clearing, the PVP_ILAT register latches the events until cleared by a software handshake.A PVP block which is enabled in either the camera pipe or memory pipe can be moved to the other pipe only after the drain done command is received for the former pipe. This restriction ensures that the PVP completely processes all the pixels in one pipe and disables the PVP block, before the PVP is enables the PVP block for pixel processing in the next pipe.NOTE :Camera pipes and memory pipes can be configured by MMR writes or BCL fetches. These are sepa-rate control mechanisms and are not intended to be mixed for a given pipe during ongoing opera-tion. Before switching from one method to the other, inspect the daisy chain and drain status bits in the PVP_STAT register to ensure no operation from the other method is pending.PMA5ACU7PEC2x HCNT + 11 if 2nd derivative mode with ZCRSS=0, otherwise 1xHCNT + 6IIMn6UDS varies with settingsTable 30-48:Block Latencies (Continued)PVP Block Latency [Data Clocks]P IPELINED V ISION P ROCESSOR (PVP)P ROGRAMMING M ODELto handle the three data flows, BCS, data IN, data OUT, and optionally status data OUT. If the descrip-tors are all completed by the core, multiple PVP memory pipe jobs can be chained without any further core intervention as the DMA operations run through the chained lists and handle the multiple dataflows autonomously. The following description assumes the memory pipe is inactive, (a non initialized state PVP_CTL.MPEN =0).To run a PVP memory pipe job from the PVP memory pipe job list, the PVP first loads the memorypipe configuration into the respective shadow registers of the respective PCP elements to build the PVP memory pipe. The configuration within the shadow register is activated (transferred from shadowregister to active register) using hardware triggers (staggered transfer). This configuration stream into the shadow registers is handled by DMA 45 which is controlled by a linked descriptor list. The last valid descriptor must contain a DMA_CFG.FLOW field =0 (STOP Mode) to gracefully stop the DMA 45 aftercompleting the PVP memory pipe job list and avoid loading non valid data into PVP memory pipeconfiguration register. All DMA_CFG descriptor fields within the linked list have DMA_CFG.FLOW =6 or =7 (descriptor list mode) or alternatively DMA_CFG.FLOW =4 (descriptor array mode).A 1-dimensional DMA operation is shown in the following figure. Note however, a 2-dimensionalDMA operation can also be used.Figure 30-55:Static Linked Descriptor List for Configuration Data (BCL Data)•Job List Global TriggerAfter the first initialization of the linked descriptor list the parameter registers of DMA 45 have to beinitialized, particularly the DMA_DSCPTR_NXT and DMA_CFG register. The DMA 45 is started but thenstalls until the PVP memory pipe is enabled and the PVP_IPFn_FCNT =0.To generate a unique synchronization signal that synchronizes the Data Out (DMA 42) and Data In(DMA 43) stream, all DMA_CFG descriptor fields of DMA 45 should have the bit field DMA_CFG.TRIG =1.This generates a trigger signal after a new configuration is loaded into the shadow registers.•Job List StartAfter setting up the three DMA linked lists, the memory pipe has to be activated (PVP_CTL.MPEN =1).。

Freescale Kinetis E 系列 KE06 微控制器开发板用户指南说明书

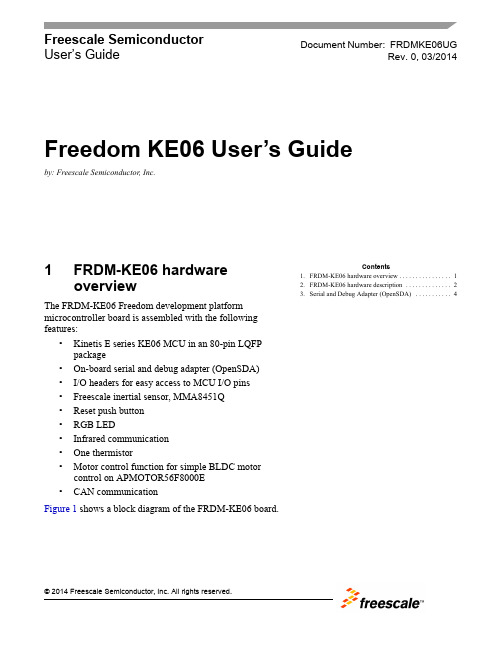

Freescale Semiconductor User’s Guide1FRDM-KE06 hardware overviewThe FRDM-KE06 Freedom development platform microcontroller board is assembled with the following features:•Kinetis E series KE06 MCU in an 80-pin LQFP package•On-board serial and debug adapter (OpenSDA)•I/O headers for easy access to MCU I/O pins •Freescale inertial sensor, MMA8451Q •Reset push button •RGB LED•Infrared communication •One thermistor•Motor control function for simple BLDC motor control on APMOTOR56F8000E •CAN communication Figure 1 shows a block diagram of the FRDM-KE06 board.Document Number:FRDMKE06UGRev. 0, 03/2014Contents1.FRDM-KE06 hardware overview . . . . . . . . . . . . . . . . 12.FRDM-KE06 hardware description . . . . . . . . . . . . . . 23.Serial and Debug Adapter (OpenSDA) . . . . . . . . . . . 4Freedom KE06 User’s Guideby: Freescale Semiconductor, Inc.FRDM-KE06 hardware descriptionFigure1. FRDM-KE06 block diagramThe FRDM-KE06 features two microcontrollers, the target MCU and a serial and debug adapter (OpenSDA) MCU. The target MCU is a Kinetis E series KE06 family device. The OpenSDA MCU is a Kinetis K series K20 family device, the K20DX128VFM5.2FRDM-KE06 hardware description2.1Power supplyThe FRDM-KE06 offers a design with multiple power supply options. It can be powered from the USB connector, the V IN pin on the I/O header, an off-board 1.71-3.6V supply from the 3.3V pin on the I/O header or 3.3V from motor control board. The USB and V IN supplies are regulated on-board using a 3.3V linear regulator to produce the main power supply. The other two sources are not regulated on-board. Note that KE06 on FRDM board can be powered by 5V or 3.3V.The following figure shows the schematic drawing for the power supply inputs and the on-board voltage regulator.FRDM-KE06 hardware descriptionFigure 2. FRDM-KE06 power supplyTable 1 provides the operational details and requirements for the power supplies.Note that the OpenSDA circuit is only operational when a USB cable is connected and supplying power to J6. However, the protection circuitry is in place to allow multiple sources to be powered at once.Table 1. Power supply requirementsSupply Source Valid RangeOpenSDA Operational?Regulated on-board?OpenSDA USB (J6)5VYes Yes V IN Pin on I/O header 4.3-9V Yes Yes 3.3V Pin on I/O header 1.71-3.6V Yes No 3.3V Pin on motor control header3.3VYesNoTable 2. Power suppliesPower Supply Name DescriptionVDD_PERIPHPeripheral power supply, including RGB LED, Key buttons, infrared, thermistor, reset circuit.J14 Pin1&2 connected, 3.3V power supply;J14 Pin2&3 connected, 5V power supply.Serial and Debug Adapter (OpenSDA)Notes:1.J9 and J10 are not populated by default on the production version. The two pins of these headers are shorted together by 0 ohm resistor R12 and R26 on the PCB. To measure the energyconsumption of either the KE06 or the OpenSDA MCU, the 0 ohm resistor between these pins must first be cut. A current probe or a shunt resistor and voltage meter can then be applied to measure the energy consumption on these rails. When the MCU current measurement is done, this 0 ohm resistor can be soldered on again.2.To better get ADC accuracy on KE06, it is recommended that a 0 ohm resistor R13 be soldered on. Ensure there is no power supply from P3V3_MOTOR and P3V3 sourced from I/O headers.3Serial and Debug Adapter (OpenSDA)OpenSDA is an open-standard serial and debug adapter. It bridges serial and debug communications between a USB host and an embedded target processor as shown in Figure 3.VDD_KE06KE06 MCU power supply.Header J9 provides a convenient means for KE06 energy consumption measurements.Header J14 for KE06 power supply selection: 3.3V or 5V.J14 Pin1&2 connected, 3.3V power supply,J14 Pin2&3 connected, 5V power supply.P3V3_SDAOpenSDA circuit power supply. Can be 3.3V only.Header J10 provides a convenient means for K20 energy consumption measurements.P5V_SDA INPUT [J6 Pin1] Input 5V Power supplied from the OpenSDA USB connector. P5-9V_VIN INPUT [J4 Pin16] Power supplied from the V IN pin of the I/O headers.P3V3_MOTOR INPUT [J2 Pin13] Input 3.3V power supplied from motor control header.P5V_USB OUTPUT[J4 Pin10] Output 5V to the I/O headers.Sourced from J6 USB (P5V_SDA) supply through a back drive protection Schottky diode.Table 2. Power suppliesSerial and Debug Adapter (OpenSDA)Figure3. OpenSDA block diagramOpenSDA is managed by a Kinetis K20 MCU built on the ARM® Cortex™-M4 core. The OpenSDA circuit includes a status LED (D4) and a reset pushbutton (SW1). The pushbutton asserts the reset signal to the KE06 target MCU. It can also be used to place the OpenSDA circuit into Bootloader mode by holding down the reset pushbutton while plugging the USB cable to USB connector J6. Once the OpenSDA enters bootloader mode, other OpenSDA applications such as debug app can be programmed. SPI and GPIO signals provide an interface to the SWD debug port of the KE06. Additionally, signal connections are available to implement a UART serial channel. The OpenSDA circuit receives power when the USB connector J6 is plugged into a USB host.3.1Debugging InterfaceSignals with SPI and GPIO capability are used to connect directly to the SWD of the KE06. These signals are also brought out to a standard 10-pin (0.05”) Cortex Debug connector (J7) as shown in Figure 4. It is possible to isolate the KE06 MCU from the OpenSDA circuit and use J7 to connect to an off-board MCU. To accomplish this, cut the 0 ohm resistor R58. This will disconnect the SWD_CLK pin to the KE06 so that it will not interfere with the communications to an off-board MCU connected to J7.When KE06 on FRDM board is 5V powered, and the OpenSDA is power off, there need to connect an external debugger to debug KE06 on board.Serial and Debug Adapter (OpenSDA)Figure4. SWD debug connector to KE063.2Virtual Serial PortA serial port connection is available between the OpenSDA MCU and UART1 pin PTC7 (TXD1) and PTC6 (RXD1) of KE06. Several of the default OpenSDA applications provided by Freescale, including the MSD Flash Programmer and the P&E Debug Application, provide a USB Communications Device Class (CDC) interface that bridges serial communications between the USB host and this serial interface on the KE06.3.3KE06 Microcontroller3.3.1Clock SourceThe Kinetis KE06 microcontrollers feature an on-chip oscillator compatible with two ranges of input crystal or resonator frequencies: 32 kHz (low frequency mode), 4-20 MHz (high frequency mode).The KE06 on the FRDM-KE06 is clocked from an 8 MHz crystal.3.3.2Serial PortThe serial port interface signals used with OpenSDA are UART1 pin PTC7 (TXD1) and PTC6 (RXD1). These signals are also connected to I/O header J1.3.3.3ResetThe PTA5/RESET signal on the KE06 is connected externally to a pushbutton SW1. The reset button can be used to force an external reset event in the target MCU. The reset button can also be used to force the OpenSDA circuit into bootloader mode when plugging the USB cable to J6. See Section3, “Serial and Debug Adapter (OpenSDA)” section for more details.Serial and Debug Adapter (OpenSDA)3.3.4DebugThe sole debug interface on all Kinetis E Series devices is a Serial Wire Debug (SWD) port. The primary controller of this interface on the FRDM-KE06 is the onboard OpenSDA circuit. However, a 2x5-pin (0.05”) Cortex Debug connector, J7, provides access to the SWD signals for the KE06 MCU. The following table shows SWD connector signals description for KE06:3.4ThermistorOne thermistor (RT1) is connected to two ADC inputs (PTF4/ADP12, PTF5/ADP13) of KE06 for evaluating the ADC module.Figure 5. Thermistor connectionTable 3. ARM JTAG/SWD mini Connector DescriptionPin FunctionConnection to KE061VTref 3.3V or 5V KE06 power supply (VDD_KE06)2SWDIO/TMS PTA4/SWD_DIO 3GNDGND4SWDCLK/TCK PTC4/SWD_CLK 5GND GND 6SWO/TDO NC 7NC NC 8TDI NC 9NC NC10RESETPTA5/RESETSerial and Debug Adapter (OpenSDA)3.5Infrared PortOne infrared Rx port and one Tx port (as shown in the following figure) are connected to ACMP0 input pin (ACMP0_IN1) and UART0 TXD0 pin of KE06 to demonstrate the capability of SCI0 modulated by a flextimer to generate infrared signals and use ACMP0 as a filter to receive the SCI data via infrared signal.Figure6. Infrared connection3.6Key buttonsTwo key buttons are connected to PTH3/4 to demonstrate KBI function of KE06, which can capture both falling edge and rising edge of key button input, as shown in the following figure.Serial and Debug Adapter (OpenSDA)Figure7. Key buttons connection3.7Three-axis accelerometerA Freescale MMA8451Q low power, three-axis accelerometer is interfaced through an I2C bus and two GPIO signals as shown in the following table. By default, the I2C address is 0x1D (SA0 pulled high).Table4. Accelerometer signal connectionsMMA8451Q KE06SCL PTA3SDA PTA2INT1 PTD4INT2 PTD3Serial and Debug Adapter (OpenSDA)Figure8. Accelerometer connection3.8RGB LEDThree PWM-capable pins are connected to a red, green, blue LED. The signal connections are shown in the table below.Table5. RGB LED Signal ConnectionsRGB LED KE06Red Cathode PTG5/FTM2CH3Green Cathode PTG6/FTM2CH4Blue Cathode PTG7/FTM2CH5Serial and Debug Adapter (OpenSDA)Figure9. GB LED connection3.9CANThe CAN phy on KE06 FRDM board is 3.3V powered.Table6. CAN signal connectionCAN Phy KE06D CAN_TXR CAN_RXSerial and Debug Adapter (OpenSDA)Figure10. CAN3.10Input/Output HeadersThe KE06 microcontroller is packaged in an 80-pin LQFP. Some pins are utilized in on-board circuitry, but many are directly connected to one of four I/O headers (J1, J2, J3, J4 and J5). J1 and J2 also function as motor control headers to provide access to a motor control board such as simple BLDC motor driving board APMOTOR56F8000E.Serial and Debug Adapter (OpenSDA)Figure11. I/O headers3.11Arduino CompatibilityThe I/O headers on the FRDM-KE06 are arranged to allow compatibility with peripheral boards (known as shields) that connect to Arduino and Arduino-compatible microcontroller boards. The pins on the headers share the same mechanical spacing and placement as the I/O headers on the Arduino Uno Revision 3 board design. See Figure11 for compatible signals.Document Number:FRDMKE06UG Rev. 003/2014Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including “typicals,” must be validated for each customer application by customer’s technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: /SalesTermsandConditions.How to Reach Us:Home Page:Web Support:/supportFreescale, the Freescale logo, and Kinetis, are trademarks of FreescaleSemiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names arethe property of their respective owners. ARM and Cortex are the registered trademarksof ARM Limited. ARMCortex-M4 is the trademark of ARM Limited.© 2014 Freescale Semiconductor, Inc.。

MICRO-STAR INTERNATIONAL MS-98H3(v1.x)工业计算机板说明书

(v1.x) Industrial Computer Boardi1Thank you for choosing the MS-98H3, an excellent industrial computerboard.With low power and low profile design, the MS-98H3 accommodates theIntel®KBL/SKL ULT Series Processor and supports up to single channelDDR4 2133 MHz SO-DIMM slot to provide the maximum of 16GBmemory capacity.In the entry-level and mid-range market segment, the MS-98H3 providesa high-performance solution for today’s front-end and general purposeworkstation, as well as in the future.1-1-12This chapter provides you with the information about hardware setupprocedures. While doing the installation, be careful in holding the com-ponents and follow the installation procedures. For some components, ifyou install in the wrong orientation, the components will not work prop-erly.Use a grounded wrist strap before handling computer components. Staticelectricity may damage the components.2-2-13This chapter provides information on the BIOS Setup program and allowsusers to configure the system for optimal use.Users may need to run the Setup program when:■An error message appears on the screen at system startup and requests users to run SETUP.■Users want to change the default settings for customized features.• Please note that BIOS update assumes technician-level experience.• As the system BIOS is under continuous update for better system performance, the illustrations in this chapter should be held forreference only.2-3-1MainUse this menu for basic system configurations, such as time, date, etc. AdvancedUse this menu to set up the items of special enhanced features.BootUse this menu to specify the priority of boot devices.SecurityUse this menu to set supervisor and user passwords.ChipsetThis menu controls the advanced features of the onboard chipsets.PowerUse this menu to specify your settings for power management.Save & ExitThis menu allows you to load the BIOS default values or factory default settings into the BIOS and exit the BIOS setup utility with or without changes.System DateThis setting allows you to set the system date. The date format is <Day>, <Month> <Date> <Year>.System Timesetting allows you to set the system time. The time format is <Hour> <Minute> <Second>.SATA Mode SelectionThis setting specifies the SATA controller mode.Full Screen Logo DisplayThis BIOS feature determines if the BIOS should hide the normal POST messages with the motherboard or system manufacturer’s full-screen logo.When it is enabled, the BIOS will display the full-screen logo during the boot-up sequence, hiding normal POST messages.When it is disabled, the BIOS will display the normal POST messages, instead of the full-screen logo.Please note that enabling this BIOS feature often adds 2-3 seconds of delay to the booting sequence. This delay ensures that the logo is displayed for a sufficient amount of time. Therefore, it is recommended that you disable this BIOS feature for a faster boot-up time.Bootup NumLock StateThis setting is to set the Num Lock status when the system is powered on. Setting to [On] will turn on the Num Lock key when the system is powered on. Setting to [Off] will allow users to use the arrow keys on the numeric keypad.Option ROM Messagesitem is used to determine the display mode when an optional ROM initialized during POST. When set to [Force BIOS], the display mode used AMI BIOS is used. Select [Keep Current] if you want to use the display mode ofIntel Virtualization TechnologyVirtualization enhanced by Intel Virtualization Technology will allow a platform to run multiple operating systems and applications in independent partitions.virtualization, one computer system can function as multipleActive Processor CoresThis setting specifies the number of active processor cores.Execute Disable BitIntel’s Execute Disable Bit functionality can prevent certain classes of maliciousSerial Port 1/ 2/ 3/ 4/ 5/ 6This setting enables/disables the specified serial port.Change SettingsThis setting is used to change the address & IRQ settings of the specified serial port.Mode SelectSelect an operation mode for the specified serial port.Watch Dog TimerYou can enable the system watch-dog timer, a hardware timer that generates a reset when the software that it monitors does not respond as expected each time the watch dog polls it.FIFO ModeThis setting controls the FIFO data transfer mode.Shared IRQ ModeThis setting provides the system with the ability to share interrupts among itsSmart Fan Configurationsetting enables/disables the Smart Fan function. Smartexcellent feature which will adjust the CPU/system fan speed automatically depending on the current CPU/system temperature, avoiding the overheating to damage your system.Legacy USB SupportSet to [Enabled] if you need to use any USB 1.1/2.0 device in the operating system that does not support or have any USB 1.1/2.0 driver installed, such as DOS and SCO Unix.GPO0 ~ GPO7These settings control the operation mode of the specified GPIO.CSM Supportsetting enables/disables the support for Compatibility Support Module, part of the Intel Platform Innovation Framework for EFI providing the capability to support legacy BIOS interfaces.VideoThis setting selects the video mode.Boot Option Prioritiessetting allows users to set the sequence of boot devices where attempts to load the disk operating system.Hard Drive BBS PrioritiesThis setting allows users to set the priority of the specified devices. First press <Enter> to enter the sub-menu. Then you may use the arrow keys ( ↑↓ ) to select the desired device, then press <+>, <-> or <PageUp>, <PageDown> key to move it up/down in the priority list.Administrator PasswordAdministrator Password controls access to the BIOS Setup utility.User PasswordPassword controls access to the system at boot and to the BIOSIntel BIOS Guard SupportEnable/Disable Intel BIOS Guard Support.Intel Trusted Execution TechnologyIntel Trusted Execution Technology provides highly scalable platform security in physical and virtual infrastructures.ME Firmware Version, ME Firmware Mode, ME Firmware SKU, System Integrity Value, ME Firmware Status 1, ME Firmware Status 2, NFC Sup-These settings show the firmware information of the Intel ME (ManagementThis setting enables/disables the ME status.Manageablility Features StatesThis setting specifies the Intel ME Manageability Features.AMT BIOS FeaturesThis setting specifies theAMT BIOS Features.AMT ConfigurationIntel Active Management Technology (AMT) is hardware-based technology forME Unconfig on RTC ClearThis setting enables/disables ME Firmware Un-configure on RTC clear state. Comms Hub SupportThis setting enables/disables Comms Hub Support.JHI SupportThis setting enables/disables JHI Support.ME FW Image Re-FlashThis setting enables/disables the ME FW image reflash.PTT Configuration (Support by request)ME Debug ConfigurationTrusted ComputingSecurity Device SupportThis setting enables/disables BIOS support for security device. When set to [Disable], the OS will not show security device. TCG EFI protocol and INT1A interface will not be available.Console RedirectionConsole Redirection operates in host systems that do not have a monitor and attached. This setting enables/disables the operation redirection. When set to [Enabled], BIOS redirects and sends all contents that should be displayed on the screen to the serial COM port for display on the terminal screen. Besides, all data received from the serial port is interpreted as keystrokes from a local keyboard.Console Redirection Settings (COM1)Terminal TypeTo operate the system’s console redirection, you need a terminal supporting ANSI terminal protocol and a RS-232 null modem cable connected between the host system and terminal(s). This setting specifies the type of terminal device for console redirection.Bits per second, Data Bits, Parity, Stop BitsThis setting specifies the transfer rate (bits per second, data bits, parity, stop bits) of Console Redirection.Flow ControlRedirection COM PortSelect a COM port to display redicrection of Legacy OS and Legacy OPROM ResolutionIn Legacy OS, the Number of Rows and Columns supported redirection. Out-of-Band Mgmt PortWindows Emergency Management Service (EMS)remote management of a Windows Server OS through a serial port. Terminal TypeVT-UTF8 is the preferred terminal type for out-of-band management. The choice is VT100+ and then VT100. Read ConsoleDVMT Pre-AllocatedThis setting defines the DVMT pre-allocated memory. Pre-allocated memory is the small amount of system memory made available at boot time by the system BIOS for video. Pre-allocated memory is also known as locked memory. This is because it is "locked" for video use only and as such, is invisible and unable to be used by the operating system.DVMT Total Gfx MemThis setting specifies the memory size for DVMT.Primary IGFX Boot DisplayUse the field to select the type of device you want to use as the displays of the system.LVDSThis setting enables/disables LVDS.LCD Panel TypeThis setting specifies the LCD panel type.LCD Backlight ControlThis setting controls the LVDS backlight.Restore AC Power Losssetting specifies whether your system will reboot after a power failure interrupt occurs. Available settings are:[Power Off]Leaves the computer in the power off state.[Power On]Leaves the computer in the power on state.[Last State]Restores the system to the previous statusbefore power failure or interrupt occurred.Deep Sleep Modesetting enables/disables the Deep S5 power saving mode. S5 is almost same as G3 Mechanical Off, except that the PSU still supplies power,a minimum, to the power button to allow return to S0. A full reboot is required. No previous content is retained. Other components may remain powered so the computer can “wake” on input from the keyboard, clock, modem, LAN, or USB device.Save Changes and ResetSave changes to CMOS and reset the system.Discard Changes and ExitAbandon all changes and exit the Setup Utility.Discard ChangesAbandon all changes.Load Optimized DefaultsUse this menu to load the default values set by the motherboard manufacturer specifically for optimal performance of the motherboard.Save as User DefaultsSave changes as the user’s default profile.Restore User DefaultsRestore the user’s default profile.Launch EFI Shell from filesystem deviceThis setting helps to launch the EFI Shell application from one of the available file system devices.。

USAMADE INPCI-GPIB高性能IEEE-488.2接口和驱动软件说明书