Minimizing Concurrent Test Time in SoC’s by Balancing Resource Usage ABSTRACT

state variables 英文 定义

In the realm of computer science and programming, state variables serve as fundamental building blocks for modeling systems and processes that evolve over time. They embody the essence of dynamic behavior in software applications, enabling developers to capture and manipulate various aspects of an object or system's condition at any given moment. This essay delves into the concept of state variables from multiple perspectives, providing a detailed definition, discussing their roles and significance, examining their implementation across various programming paradigms, exploring their impact on program design, and addressing the challenges they introduce.**Definition of State Variables**At its core, a state variable is a named data item within a program or computational system that maintains a value that may change over the course of program execution. It represents a specific aspect of the system's state, which is the overall configuration or condition that determines its behavior and response to external stimuli. The following key characteristics define state variables:1. **Persistence:** State variables retain their values throughout the lifetime of an object or a program's execution, unless explicitly modified. These variables hold onto information that persists beyond a single function call or statement execution.2. **Mutability:** State variables are inherently mutable, meaning their values can be altered by program instructions. This property allows programs to model evolving conditions or track changes in a system over time.3. **Contextual Dependency:** The value of a state variable is dependent on the context in which it is accessed, typically determined by the object or scope to which it belongs. This context sensitivity ensures encapsulation and prevents unintended interference with other parts of the program.4. **Time-variant Nature:** State variables reflect the temporal dynamics of a system, capturing how its properties or attributes change in response to internal operations or external inputs. They allow programs to model systemswith non-static behaviors and enable the simulation of real-world scenarios with varying conditions.**Roles and Significance of State Variables**State variables play several critical roles in software development, contributing to the expressiveness, versatility, and realism of programs:1. **Modeling Dynamic Systems:** State variables are instrumental in simulating real-world systems with changing states, such as financial transactions, game characters, network connections, or user interfaces. By representing the relevant attributes of these systems as state variables, programmers can accurately model complex behaviors and interactions over time.2. **Enabling Data Persistence:** In many applications, maintaining user preferences, application settings, or transaction histories is crucial. State variables facilitate this persistence by storing and updating relevant data as the program runs, ensuring that users' interactions and system events leave a lasting impact.3. **Supporting Object-Oriented Programming:** In object-oriented languages, state variables (often referred to as instance variables) form an integral part of an object's encapsulated data. They provide the internal representation of an object's characteristics, allowing objects to maintain their unique identity and behavior while interacting with other objects or the environment.4. **Facilitating Concurrency and Parallelism:** State variables underpin the synchronization and coordination mechanisms in concurrent and parallel systems. They help manage shared resources, enforce mutual exclusion, and ensure data consistency among concurrently executing threads or processes.**Implementation Across Programming Paradigms**State variables find expression in various programming paradigms, each with its own idiomatic approach to managing and manipulating them:1. **Object-Oriented Programming (OOP):** In OOP languages like Java, C++, or Python, state variables are typically declared as instance variables withina class. They are accessed through methods (getters and setters), ensuring encapsulation and promoting a clear separation of concerns between an object's internal state and its external interface.2. **Functional Programming (FP):** Although FP emphasizes immutability and statelessness, state management is still necessary in practical applications. FP languages like Haskell, Scala, or Clojure often employ monads (e.g., State monad) or algebraic effects to model stateful computations in a pure, referentially transparent manner. These constructs encapsulate state changes within higher-order functions, preserving the purity of the underlying functional model.3. **Imperative Programming:** In imperative languages like C or JavaScript, state variables are directly manipulated through assignment statements. Control structures (e.g., loops and conditionals) often rely on modifying state variables to drive program flow and decision-making.4. **Reactive Programming:** Reactive frameworks like React or Vue.js utilize state variables (e.g., component state) to manage UI updates in response to user interactions or data changes. These frameworks provide mechanisms (e.g., setState() in React) to handle state transitions and trigger efficient UI re-rendering.**Impact on Program Design**The use of state variables significantly influences program design, both positively and negatively:1. **Modularity and Encapsulation:** Well-designed state variables promote modularity by encapsulating relevant information within components, objects, or modules. This encapsulation enhances code organization, simplifies maintenance, and facilitates reuse.2. **Complexity Management:** While state variables enable rich behavioral modeling, excessive or poorly managed state can lead to complexity spirals. Convoluted state dependencies, hidden side effects, and inconsistent state updates can make programs difficult to understand, test, and debug.3. **Testing and Debugging:** State variables introduce a temporal dimension to program behavior, necessitating thorough testing across different states and input scenarios. Techniques like unit testing, property-based testing, and state-machine testing help validate state-related logic. Debugging tools often provide features to inspect and modify state variables at runtime, aiding in diagnosing issues.4. **Concurrency and Scalability:** Properly managing shared state is crucial for concurrent and distributed systems. Techniques like lock-based synchronization, atomic operations, or software transactional memory help ensure data consistency and prevent race conditions. Alternatively, architectures like event-driven or actor-based systems minimize shared state and promote message-passing for improved scalability.**Challenges and Considerations**Despite their utility, state variables pose several challenges that programmers must address:1. **State Explosion:** As programs grow in size and complexity, the number of possible state combinations can increase exponentially, leading to a phenomenon known as state explosion. Techniques like state-space reduction, model checking, or static analysis can help manage this complexity.2. **Temporal Coupling:** State variables can introduce temporal coupling, where the correct behavior of a piece of code depends on the order or timing of state changes elsewhere in the program. Minimizing temporal coupling through decoupled designs, immutable data structures, or functional reactive programming can improve code maintainability and resilience.3. **Caching and Performance Optimization:** Managing state efficiently is crucial for performance-critical applications. Techniques like memoization, lazy evaluation, or cache invalidation strategies can optimize state access and updates without compromising correctness.4. **Debugging and Reproducibility:** Stateful programs can be challenging to debug due to their non-deterministic nature. Logging, deterministic replaysystems, or snapshot-based debugging techniques can help reproduce and diagnose issues related to state management.In conclusion, state variables are an indispensable concept in software engineering, enabling programmers to model dynamic systems, maintain data persistence, and implement complex behaviors. Their proper utilization and management are vital for creating robust, scalable, and maintainable software systems. While they introduce challenges such as state explosion, temporal coupling, and debugging complexities, a deep understanding of state variables and their implications on program design can help developers harness their power effectively, ultimately driving innovation and progress in the field of computer science.。

腾讯NDA限制-腾讯NDA限制-Jacinto6Eco SoC电源解决方案-DRA72 TDA2

TPS22965 + TPS51200

8

New PDN Concept

0.40 = $3.25

(3 AVS @ 1‐2.5A, Dual 1.8/3.3V IO, DDR3L)

18 + 4 + 4.6 + 4.6 + 4 + 9 = 44

$4.42 128 $2.53 74

$7.32 190 $4.64 119

5. “PDN’s AVS Capability” is the achievable power if all AVS power rails are increased to 90% of capacity while other power rails remain at typical Use Case modelled values.

(3 AVS @ 1‐3.5A, Dual 1.8/3.3V IO, DDR3L) (similar to EVM PDN #0)

49 + 9 + 4 = 62

#8.2 – LP87524 + LP5912 + TLV713 + LP5907 +

9.92

1.26 + 0.19 + 0.07 + 0.10 + 0.10 +

2. PDN Support component (Rs, Cs & Ls) pricing from Mouser Distribution website using single 4k – 10k/reel qty costs as of May 2016. Both PDN Support & PDN Total Costs have been provided for relative comparison only, individual customer volume pricing may vary.

Oracle 应用测试套件 - Oracle E-Business Suite 功能测试加速器说明书

ORACLE APPLICATION TESTING SUITE - TESTING ACCELERATORS FOR ORACLE E-BUSINESS SUITEFEATURES• Automates complex Oracle E-Business Suite transactionsfor both functional testing andload testing• Supports automation of bothWeb and Oracle Formsapplication interfaces andprotocols• Provides custom test cases tovalidate application content• Enables parameterization oftest scripts for data-driventesting• Simulates loads of hundredsto tens of thousands ofconcurrent users whileminimizing hardwarerequirements• Gathers critical infrastructureperformance metrics toidentify bottlenecks underload• Provides an intuitive Web-based console to configureand run load tests and sharereal-time results withdistributed users• EBS Test Starter Kit withsample test scripts providedfor EBS R12 and 11iOracle Application Testing Suite’s Testing Accelerators for Oracle E-Business Suite provide a comprehensive solution for ensuring the quality and performance of Oracle E-Business Suite applications. The Functional Testing Accelerator for Oracle E-Business Suite extends Oracle Functional Testing to enable automated functional and regression testing of Oracle E-Business Suite applications. The Load Testing Accelerator for Oracle E-Business Suite extends Oracle Load Testing to enable load and performance testing of Oracle E-Business Suite applications. The Testing Accelerators for Oracle E-Business Suite are components of Oracle Application Testing Suite, the centerpiece of the Oracle Enterprise Manager solution for comprehensive testing of packaged, Web and service-oriented architecture–based applications. Ensuring Oracle E-Business Suite Application Quality Ensuring the quality of your Oracle E-Business Suite (EBS) applications is critical to your business. But testing EBS applications prior to deployment and keeping up with the pace application updates while maintaining application quality can be a challenge. Oracle Application Testing Suite (ATS) provides a comprehensive quality management solution for Oracle E-Business Suite. Oracle Functional Testing and the Functional Testing Accelerator for Oracle E-Business Suite provides an automated functional and regression testing solution to validate application functionality prior to deployment and reduce the need for manual testing. Oracle Load Testing and the Load Testing Accelerator for Oracle E-Business Suite provide a powerful load testing solution to test and tune application performance under real production workloads and identify bottlenecks. Oracle Test Manager provides an integrated solution for managing the test process including documenting test cases, test requirements and issues identified during testing in a central repository and managing test execution. Together, these products provide a comprehensive solution for ensuring EBS application quality. Functional Testing Accelerator for Oracle E-Business Suite The Functional Testing Accelerator for Oracle E-Business Suite extends Oracle Functional Testing to provide a powerful and easy-to-use solution to automate functional and regression testing of Oracle’s E-Business Suite applications. OracleFunctional Testing allows users to create test scripts that automate complex business transactions within their EBS applications, including both Web and Oracle Forms based application interfaces. Oracle Functional Testing’s OpenScript integrated scripting platform combines an intuitive graphical scripting interface to quickly create complex test scripts and a powerful Java IDE that provides users with the flexibility to extend scripts programmatically. Users can automate business transactions by simply creating a new script and recording as they step through an EBS transaction in a browser. OpenScript captures all actions performed within Web or Forms based applications interfaces which can then be played back to automatically reproduce the recorded transaction. Users can then add test cases to validate specific Web or Forms application content and parameterize their script inputs to perform data-driven testing. Additional transactions can then be recorded to create a comprehensive automated regression test suite.Figure1. Oracle Functional Testing automates Oracle E-Business Suite functional and regression testingLoad Testing Accelerator for Oracle E-Business SuiteThe Load Testing Accelerator for Oracle E-Business Suite extends Oracle Load Testing to enable automated load and performance testing of Oracle E-Business Suite applications. With Oracle Load Testing you can simulate thousands of virtual users accessing the Oracle E-Business Suite application simultaneously to measure the effect of user load on application performance.Users create their EBS load test scripts in Oracle Functional Testing’s OpenScript integrated scripting platform. OpenScript automates both Web and Forms application protocols to generate highly scalable load test scripts for Oracle EBS. The scripts are automatically correlated to handle dynamic session parameters. These scripts can then be configured to run in Oracle Load Testing against any number of virtual users.Oracle Load Testing provides a Web-based console that allows you to configure and run one or multiple scripts across thousands of virtual users to assess performance. Users can specify a number of run time parameters such as the amount of think time each user spends per page and the browser or connection speed to emulate. During the load test, Oracle Load Testing measures end-user response times as well as the performance of the underlying application infrastructure to help identify and resolve application performance bottlenecks.Comprehensive Testing for Oracle E-Business SuiteOracle Application Testing Suite provides a comprehensive testing solution for Oracle E-Business Suite. With Oracle Functional Testing and the Functional Testing Accelerator for Oracle E-Business Suite, users can effectively introduce automation into their functional test process to ensure the quality of their Oracle E-Business Suite applications and reduce testing time. With Oracle Load Testing and the Load Testing Accelerator for Oracle E-Business Suite, users can leverage a powerful solution for ensuring Oracle E-Business Suite application performance. The Oracle E-Business Suite testing accelerator includes a Test Starter Kit with pre-build test automation scripts for Oracle E-Business Suite applications. The Test Starter Kit covers a broad range of applications and user flows for both functional and performance testing based on the VISION demo database.And with Oracle Test Manager users can effectively document and manage their test process from a central location and report on application readiness.Oracle Application Testing Suite provides a powerful integrated scripting platform for automated functional & regression testing and load testing. Oracle Functional Testing’s OpenScript integrated scripting interface provides a unique combination of ease-of-use and flexibility through its intuitive graphical scripting interface and powerful Java IDE for extending scripts at the code-level. Oracle Functional Testing also provides custom capabilities for testing SOA and Oracle packaged applications through its integrated testing accelerators. Oracle Load Testing provides a fully Web-based user interface for configuring and running load tests and an integrated ServerStats module for monitoring application infrastructure during a load test to identify bottlenecks. Oracle Load Testing also enables multi-user collaboration by allowing testers to view and share real-time results during load test execution through their browser. With Oracle Application Testing Suite users can leverage a comprehensive, integrated solution for automated functional and regression testing, load testing and test process management.Contact UsFor more information about Oracle Application Testing Suite Oracle E-Business Suite Accelerators and Oracle Enterprise Manager please visit or call+1.800.ORACLE1 to speak to an Oracle representative.Copyright © 2011, Oracle and/or its affiliates. All rights reserved.This document is provided for information purposes only and the contents hereof are subject to change without notice. This document is not warranted to be error-free, nor subject to any other warranties or conditions, whether expressed orally or implied in law, including implied warranties and conditions of merchantability or fitness for a particular purpose. We specifically disclaim any liability with respect to this document and no contractual obligations are formed either directly or indirectly by this document. This document may not be reproduced or transmitted in any form or by any means, electronic or mechanical, for any purpose, without our prior written permission.Oracle and Java are registered trademarks of Oracle and/or its affiliates. Other names may be trademarks of their respective owners.AMD, Opteron, the AMD logo, and the AMD Opteron logo are trademarks or registered trademarks of Advanced Micro Devices. Intel and Intel Xeon are trademarks or registered trademarks of Intel Corporation. All SPARC trademarks are used under license and are trademarks or registered trademarks of SPARC International, Inc. UNIX is a registered trademark licensed through X/Open Company, Ltd. 0110。

swirlymms

swirlymmsSwirlyMMS: A High-Performance Solution for Multimedia Messaging ServiceIntroductionMultimedia Messaging Service (MMS) has become an integral part of our daily communication, allowing us to send multimedia content such as images, videos, and audio files directly to other users' mobile phones. With the increasing demand for richer and more engaging media content, MMS platforms are faced with the challenge of delivering these files quickly and efficiently. This document introduces SwirlyMMS, a high-performance solution designed to enhance and optimize the delivery of multimedia content via MMS.1. Overview of MMSMMS refers to the technology that enables users to exchange multimedia files over a mobile network. Compared to traditional Short Message Service (SMS) which only supports text, MMS allows the transmission of various media types,including images, videos, audio, and even slideshows. This enhanced messaging capability has revolutionized the way we communicate and share information on mobile devices.2. The Need for High-Performance MMS SolutionsAs the popularity of multimedia content continues to grow, there is a need for MMS platforms to handle higher volumes of data and deliver them with minimal delay. Users expect their multimedia messages to be delivered promptly and reliably, regardless of the size or complexity of the media files.3. Introducing SwirlyMMSSwirlyMMS is a cutting-edge solution designed to meet the demands of high-performance multimedia messaging. Leveraging advanced technologies and optimization techniques, SwirlyMMS aims to provide a seamless and efficient user experience for both senders and receivers of multimedia messages.4. Key Features4.1. Enhanced Performance: SwirlyMMS utilizes optimized transmission protocols and algorithms to ensure swift and reliable delivery of multimedia content. By minimizing the transfer time, users can enjoy a seamless experience when sending and receiving media files.4.2. Scalability: SwirlyMMS is built to handle high volumes of data and concurrent connections, making it suitable for large-scale deployments. The solution can easily adapt to the ever-increasing demand for multimedia messaging services.4.3. Media Compression: To optimize bandwidth usage and reduce transfer times, SwirlyMMS employs advanced compression techniques. This allows for the efficient transmission of multimedia files without compromising the quality of the content.4.4. Cross-Platform Compatibility: SwirlyMMS is designed to work seamlessly across different mobile operating systems and devices. Whether it's Android, iOS, or Windows, SwirlyMMS ensures a consistent and reliable experience for all users.4.5. Secure and Reliable: SwirlyMMS prioritizes the security and privacy of multimedia messages. The solutionincorporates robust encryption algorithms and authentication mechanisms to protect the confidentiality and integrity of the transmitted content.5. Benefits of SwirlyMMS5.1. Improved User Experience: SwirlyMMS enhances the speed and reliability of multimedia messaging, ensuring a seamless user experience. Users can easily send and receive multimedia content without interruptions or delays.5.2. Cost-Efficiency: SwirlyMMS optimizes bandwidth usage by compressing media files, resulting in reduced data consumption and lower costs for both users and service providers.5.3. Increased Productivity: With SwirlyMMS, businesses can efficiently exchange important documents, images, and videos, improving productivity and collaboration among team members.5.4. Integration Capability: SwirlyMMS offers APIs and SDKs that allow developers to integrate the solution into existingapplications and platforms, enabling seamless integration and expanding its functionalities.6. ConclusionSwirlyMMS is a high-performance solution that revolutionizes the way we send and receive multimedia messages. By providing enhanced speed, reliability, and security, SwirlyMMS ensures a seamless user experience and opens up new possibilities for businesses and individuals alike. With its advanced features and compatibility across platforms, SwirlyMMS is the ideal solution for optimizing multimedia messaging service.。

Eliminating stack overflow by abstract interpretation

In Proceedings of the3rd International Conference on Embedded Software,Philadelphia,PA,pages306–322,October13–15,2003.c Springer-Verlag. Eliminating stack overflow by abstract interpretationJohn Regehr Alastair Reid Kirk WebbSchool of Computing,University of UtahAbstract.An important correctness criterion for software running on embeddedmicrocontrollers is stack safety:a guarantee that the call stack does not over-flow.We address two aspects of the problem of creating stack-safe embeddedsoftware that also makes efficient use of memory:statically bounding worst-casestack depth,and automatically reducing stack memory requirements.Ourfirstcontribution is a method for statically guaranteeing stack safety by performingwhole-program analysis,using an approach based on context-sensitive abstractinterpretation of machine code.Abstract interpretation permits our analysis toaccurately model when interrupts are enabled and disabled,which is essentialfor accurately bounding the stack depth of typical embedded systems.We haveimplemented a stack analysis tool that targets Atmel A VR microcontrollers,andtested it on embedded applications compiled from up to30,000lines of C.Weexperimentally validate the accuracy of the tool,which runs in a few secondson the largest programs that we tested.The second contribution of this paper isa novel framework for automatically reducing stack memory requirements.Weshow that goal-directed global function inlining can be used to reduce the stackmemory requirements of component-based embedded software,on average,to40%of the requirement of a system compiled without inlining,and to68%of therequirement of a system compiled with aggressive whole-program inlining that isnot directed towards reducing stack usage.1IntroductionInexpensive microcontrollers are used in a wide variety of embedded applications such as vehicle control,consumer electronics,medical automation,and sensor networks. Static analysis of the behavior of software running on these processors is important for two main reasons:–Embedded systems are often used in safety critical applications and can be hard to upgrade once deployed.Since undetected bugs can be very costly,it is useful to attempt tofind software defects early.–Severe constraints on cost,size,and power make it undesirable to overprovision resources as a hedge against unforeseen demand.Rather,worst-case resource re-quirements should be determined statically and accurately,even for resources like memory that are convenient to allocate in a dynamic style.0 KB4 KB Without stack boundingWith static stack bounding Fig.1.Typical RAM layout for an embedded program with and without stack bounding.Without a bound,developers must rely on guesswork to determine the amount of storage to allocate to the stack.In this paper we describe the results of an experiment in applying static analysis techniques to binary programs in order to bound and reduce their stack memory re-quirements.We check embedded programs for stack safety :the property that they will not run out of stack memory at run time.Stack safety,which is not guaranteed by tra-ditional type-safe languages like Java,is particularly important for embedded software because stack overflows can easily crash a system.The transparent dynamic stack ex-pansion that is performed by general-purpose operating systems is infeasible on small embedded systems due to lack of virtual memory hardware and limited availability of physical memory.For example,8-bit microcontrollers typically have between a few tens of bytes and a few tens of kilobytes of RAM.Bounds on stack depth can also be usefully incorporated into executable programs,for example to assign appropriate stack sizes to threads or to provide a heap allocator with as much storage as possible without compromising stack safety.The alternative to static stack depth analysis that is currently used in industry is to ensure that memory allocated to the stack exceeds the largest stack size ever observed during testing by some safety margin.A large safety margin would provide good in-surance against stack overflow,but for embedded processors used in products such as sensor network nodes and consumer electronics,the degree of overprovisioning must be kept small in order to minimize per-unit product cost.Figure 1illustrates the rela-tionship between the testing-and analysis-based approaches to allocating memory for the stack.Testing-based approaches to software validation are inherently unreliable,and test-ing embedded software for maximum stack depth is particularly unreliable because its behavior is timing dependent:the worst observed stack depth depends on what code is executing when an interrupt is triggered and on whether further interrupts trigger before the first returns.For example,consider a hypothetical embedded system where the maximum stack depth occurs when the following events occur at almost the same time:1)the main program summarizes data once a second spending 100microseconds2at maximum stack depth;2)a timer interruptfires100times a second spending100mi-croseconds at maximum stack depth;and3)a packet arrives on a network interface up to10times a second;the handler spends100microseconds at maximum stack depth.If these events occur independently of each other,then the worst case will occur roughly once every10years.This means that the worst case will probably not be discovered during testing,but will probably occur in the real world where there may be many in-stances of the embedded system.In practice,the events are not all independent and the timing of some events can be controlled by the test environment.However,we would expect a real system to spend less time at the worst-case stack depth and to involve more events.Another drawback of the testing-based approach to determining stack depth is that it treats the system as a black box,providing developers with little or no feedback about how to best optimize memory usage.Static stack analysis,on the other hand,identifies the critical path through the system and also the maximum stack consumption of each function;this usually exposes obvious candidates for optimization.Using our method for statically bounding stack depth as a starting point,we have developed a novel way to automatically reduce the stack memory requirement of an em-bedded system.The optimization proceeds by evaluating the effect of a large number of potential program transformations in a feedback loop,applying only transformations that reduce the worst-case depth of the stack.Static analysis makes this kind of opti-mization feasible by rapidly providing accurate information about a program.Testing-based approaches to learning about system behavior,on the other hand,are slower and typically only explore a fraction of the possible state space.Our work is preceded by a stack depth analysis by Brylow et al.[3]that also per-forms whole-program analysis of executable programs for embedded systems.How-ever,while they focused on relatively small programs written by hand in assembly lan-guage,we focus on programs that are up to30times larger,and that are compiled from C to a RISC architecture.The added difficulties in analyzing larger,compiled programs necessitated a more powerful approach based on context-sensitive abstract interpreta-tion of machine code;we motivate and describe this approach in Section2.Section3 discusses the problems in experimentally validating the abstract interpretation and stack depth analysis,and presents evidence that the analysis provides accurate results.In Sec-tion4we describe the use of a stack bounding tool to support automatically reducing the stack memory consumption of an embedded system.Finally,we compare our research to previous efforts in Section5and conclude in Section6.2Bounding Stack DepthEmbedded system designers typically try to statically allocate resources needed by the system.This makes systems more predictable and reliable by providing a priori bounds on resource consumption.However,an almost universal exception to this rule is that memory is dynamically allocated on the call stack.Stacks provide a useful model of storage,with constant-time allocation and deallocation and without fragmentation.Fur-thermore,the notion of a stack is designed into microcontrollers at a fundamental level. For example,hardware support for interrupts typically pushes the machine state onto3the stack before calling a user-defined interrupt handler,and pops the machine state upon termination of the handler.For developers of embedded systems,it is important not only to know that the stack depth is bounded,but also to have a tight bound—one that is not much greater than the true worst-case stack depth.This section describes the whole-program analysis that we use to obtain tight bounds on stack depth.Our prototype stack analysis tool targets programs for the Atmel A VR,a popular family of microcontrollers.We chose to analyze binary program images,rather than source code,for a number of reasons:–There is no need to predict compiler behavior.Many compiler decisions,such as those regarding function inlining and register allocation,have a strong effect on stack depth.–Inlined assembly language is common in embedded systems,and a safe analysis must account for its effects.–The source code for libraries and real-time operating systems are commonly not available for analysis.–Since the analysis is independent of the compiler,developers are free to change compilers or compiler versions.In addition,the analysis is not fragile with respect to non-standard language extensions that embedded compilers commonly use to provide developers withfine-grained control over processor-specific features.–Adding a post-compilation analysis step to the development process presents de-velopers with a clean usage model.2.1Analysis Overview and MotivationThefirst challenge in bounding stack depth is to measure the contributions to the stack of each interrupt handler and of the main program.Since indirect function calls and recursion are uncommon in embedded systems[4],a callgraph for each entry point into the program can be constructed using standard analysis techniques.Given a callgraph it is usually straightforward to compute its stack requirement.The second,more difficult,challenge in embedded systems is accurately estimating interactions between interrupt handlers and the main program to compute a maximum stack depth for the whole system.If interrupts are disabled while running interrupt handlers,one can safely estimate the stack bound of a system containing interrupt handlers using this formula:stack bound depth(main)depth(interrupt)However,interrupt handlers are often run with interrupts enabled to ensure that other interrupt handlers are able to meet real-time deadlines.If a system permits at most one concurrent instance of each interrupt handler,the worst-case stack depth of a system can be computed using this formula:stack bound depth(main)depth(interrupt)4Fig.2.This fragment of assembly language for Atmel A VR microcontrollers motivates our approach to program analysis and illustrates a common idiom in embedded soft-ware:disable interrupts,execute a critical section,and then reenable interrupts only if they had previously been enabledUnfortunately,as we show in Section3,this simple formula often provides unneces-sarily pessimistic answers when used to analyze real systems where only some parts of some interrupt handlers run with interrupts enabled.To obtain a safe,tight stack bound for realistic embedded systems,we developed a two-part analysis.Thefirst must generate an accurate estimate of the state of the proces-sor’s interrupt mask at each point in the program,and also the effect of each instruction on the stack depth.The second part of the analysis—unlike thefirst—accounts for potential preemptions between interrupts handlers and can accurately bound the global stack requirement for a system.Figure2presents a fragment of machine code that motivates our approach to pro-gram analysis.Analogous code can be found in almost any embedded system:its pur-pose is to disable interrupts,execute a critical section that must run atomically with respect to interrupt handlers,and then reenable interrupts only if they had previously been enabled.There are a number of challenges in analyzing such code.First,effects of arithmetic and logical operations must be modeled with enough ac-curacy to track data movement through general-purpose and special-purpose registers. In addition,partially unknown data must be modeled.For example,analysis of the code fragment must succeed even when only a single bit of the CPU status register—the master interrupt control bit—is initially known.Second,dead edges in the control-flow graph must be detected and avoided.For ex-ample,when the example code fragment is called in a context where interrupts are dis-abled,it is important that the analysis conclude that the sei instruction is not executed since this would pollute the estimate of the processor state at subsequent addresses.Finally,to prevent procedural aliasing from degrading the estimate of the machine state,a context sensitive analysis must be used.For example,in some systems the code501 (a)Lattice for each bit in the machine stateand1000101111xor110101(b)Logical operations on abstract bits and combining machine states at merge pointsFig.3.Modeling machine states and operations in the abstract interpretationin Figure2is called with interrupts disabled by some parts of the system and is called with interrupts enabled by other parts of the system.With a context-insensitive ap-proach,the analysis concludes that since the initial state of the interruptflag can vary,thefinal state of the interruptflag can also vary and so analysis of both callers of the function would proceed with the interruptflag unknown.This can lead to large over-estimates in stack bounds since unknown values are propagated to any code that could execute after the call.With a context-sensitive analysis the two calls are analyzed sepa-rately,resulting in an accurate estimate of the interrupt state.The next section describes the abstract interpretation we have developed to meet these challenges.2.2Abstracting the Processor StateThe purpose of our abstract interpretation is to generate a safe,precise estimate of the state of the processor at each point in the program;this is a requirement forfindinga tight bound on stack depth.Designing the abstract interpretation boils down to twomain design decisions.First,how much of the machine state should the analysis model?For programs thatwe have analyzed,it is sufficient to model the program counter,general-purpose regis-ters,and several I/O registers.Atmel A VR chips contain32general-purpose registers and64I/O registers;each register stores eight bits.From the I/O space we model theregisters that contain interrupt masks and the processor status register.We do not model main memory or most I/O registers,such as those that implement timers,analog-to-digital conversion,and serial communication.Second,what is the abstract model for each element of machine state?We chose to model the machine at the bit level to capture the effect of bitwise operations on theinterrupt mask and condition code register—we had initially attempted to model themachine at word granularity and this turned out to lose too much information through conservative approximation.Each bit of machine state is modeled using the lattice de-picted in Figure3(a).The lattice contains the values0and1as well as a bottom element, ,that corresponds to a bit that cannot be proven to have value0or1at a particular program point.Figure3(b)shows abstractions of some common logical operators.Abstractions of operators should always return a result that is as accurate as possible.For example,6when all bits of the input to an instruction have the value0or1,the execution of the instruction should have the same result that it would have on a real processor.In this respect our abstract interpreter implements most of the functionality of a standard CPU simulator.For example,when executing the and instruction with as one argument and as the other argument,the result register will con-tain the value.Arithmetic operators are treated similarly,but re-quire more care because bits in the result typically depend on multiple bits in the input. Furthermore,the abstract interpretation must take into account the effect of instructions on processor condition codes,since subsequent branching decisions are made using these values.The example in Figure2illustrates two special cases that must be accounted for in the abstract interpretation.First,the add-with-carry instruction adc,when both of its arguments are the same register,acts as rotate-left-through-carry.In other words,it shifts each bit in its input one position to the left,with the leftmost bit going into the CPU’s carryflag and the previous carryflag going into the rightmost bit.Second,the exclusive-or instruction eor,when both of its arguments are the same register,acts like a clear instruction—after its execution the register is known to contain all zero bits regardless of its previous contents.2.3Managing Abstract Processor StatesAn important decision in designing the analysis was when to create a copy of the ab-stract machine state at a particular program point,as opposed to merging two abstract states.The merge operator,shown in Figure3(b),is lossy since a conservative approx-imation must always be made.We have chosen to implement a context-sensitive anal-ysis,which means that we fork the machine state each time a function call is made, and at no other points in the program.This has several consequences.First,and most important,it means that the abstract interpretation is not forced to make a conservative approximation when a function is called from different points in the program where the processor is in different states.In particular,when a function is called both with inter-rupts enabled and disabled,the analysis is not forced to conclude that the status of the interrupt bit is unknown inside the function and upon return from it.Second,it means that we cannot show termination of a loop implemented within a function.This is not a problem at present since loops are irrelevant to the stack depth analysis as long as there is no net change in stack depth across the loop.However,it will become a problem if we decide to push our analysis forward to bound heap allocation or execution time.Third, it means that we can,in principle,detect termination of recursion.However,our current implementation rarely does so in practice because most recursion is bounded by values that are stored on the stack—which our analysis does not model.Finally,forking the state at function calls means that the state space of the stack analyzer might become large.This has not been a problem in practice;the largest programs that we have ana-lyzed cause the analyzer to allocate about140MB.If memory requirements become a problem for the analysis,a relatively simple solution would be to merge program states that are identical or that are similar enough that a conservative merging will result in minimal loss of precision.72.4Abstract Interpretation and Stack Analysis AlgorithmsThe program analysis begins by initializing a worklist with all entry points into the program;entry points are found by examining the vector of interrupt handlers that is stored at the bottom of a program image,which includes the address of a startup routine that eventually jumps to main().For each item in the worklist,the analyzer abstractly interprets a single instruction.If the interpretation changes the state of the processor at that program point,items are added to the worklist corresponding to each live control flow edge leaving the instruction.Termination is assured because the state space for a program isfinite and because we never revisit states more than once.The abstract interpretation detects control-flow edges that are dead in a particular context,and also control-flow edges that are dead in all contexts.In many systems we have analyzed,the abstract interpretationfinds up to a dozen branches that are provably not taken.This illustrates the increased precision of our analysis relative to the dataflow analysis that an optimizing compiler has previously performed on the embedded pro-gram as part of a dead code elimination pass.In the second phase,the analysis considers there to be a controlflow edge from every instruction in the program to thefirst instruction of every interrupt handler that cannot be proven to be disabled at that program point.An interrupt is disabled if either the master interrupt bit is zero or the enable bit for the particular interrupt is zero.Once these edges are known,the worst-case stack depth for a program can be found using the method developed by Brylow et al.[3]:perform a depth-first search over controlflow edges,explicit and implicit,keeping track of the effect of each instruction on the stack depth,and also keeping track of the largest stack depth seen so far.A complication that we have encountered in many real programs is that interrupt handlers commonly run with all interrupts enabled,admitting the possibility that a new instance of an interrupt handler will be signaled before the previous instance terminates. From an analysis viewpoint reentrant interrupt handlers are a serious problem:systems containing them cannot be proven to be stack-safe without also reasoning about time. In effect,the stack bounding problem becomes predicated on the results of a real-time analysis that is well beyond the current capabilities of our tool.In real systems that we have looked at reentrant interrupt handlers are so common that we have provided a facility for working around the problem by permitting a de-veloper to manually assert that a particular interrupt handler can preempt itself only up to a certain number of times.Programmers appear to commonly rely on ad hoc real-time reasoning,e.g.,“this interrupt only arrives10times per second and so it cannot possibly interrupt itself.”In practice,most instances of this kind of reasoning should be considered to be designflaws—few interrupt handlers are written in a reentrant fashion so it is usually better to design systems where concurrent instances of a single handler are not permitted.Furthermore,stack depth requirements and the potential for race conditions will be kept to a minimum if there are no cycles in the interrupt preemp-tion graph,and if preemption of interrupt handlers is only permitted when necessary to meet a real-time deadline.82.5Other ChallengesIn this section we address other challenges faced by the stack analysis tool:loads into the stack pointer,self-modifying code,indirect branches,indirect stores,and recursive function calls.These features can complicate or defeat static analysis.However,em-bedded developers tend to make very limited use of them,and in our experience static analysis of real programs is still possible and,moreover,effective.We support code that increments or decrements the stack pointer by constants,for example to allocate or deallocate function-scoped data structures.Code that adds non-constants to the stack pointer(e.g.,to allocate variable sized arrays on the stack)would require some extra work to bound the amount of space added to the stack.We also do not support code that changes the stack pointer to new values in a more general way,as is done in the context switch routine of a preemptive operating system.The A VR has a Harvard architecture,making it possible to prove the absence of self-modifying code simply by ensuring that a program cannot reach a“store program memory”instruction.However,by reduction to the halting problem,self-modifying code cannot be reliably detected in the general case.Fortunately,use of self-modifying code is rare and discouraged—it is notoriously difficult to understand and also pre-cludes reducing the cost of an embedded system by putting the program into ROM.Our analysis must build a conservative approximation of the program’s controlflow graph.Indirect branches cause problems for program analysis because it can be diffi-cult to tightly bound the set of potential branch targets.Our approach to dealing with indirect branches is based on the observation that they are usually used in a structured way,and the structure can be exploited to learn the set of targets.For example,when analyzing TinyOS[6]programs,the argument to the function TOSit contained only14recursive loops.Our approach to dealing with recursion,therefore, is blunt:we require that developers explicitly specify a maximum iteration count for each recursive loop in a system.The analysis returns an unbounded stack depth if the developers neglect to specify a limit for a particular loop.It would be straightforward to port our stack analyzer to other processors:the anal-ysis algorithms,such as the whole-program analysis for worst-case stack depth,operate on an abstract representation of the program that is not processor dependent.However, the analysis would return pessimistic results for register-poor architectures such as the Motorola68HC11,since code for those processors makes significant use of the stack, and stack values are not currently modeled by our tool.In particular,we would proba-bly not obtain precise results for code equivalent to the code in Figure2that we used to motivate our approach.To handle register-poor architectures we are developing an approach to modeling the stack that is based on a simple type system for registers that are used as pointers into stack frames.2.6Using the Stack ToolWe have a prototype tool that implements our stack depth analysis.In its simplest mode of usage,the stack tool returns a single number:an upper bound on the stack depth for a system.For example:$./stacktool-w flybywire.elftotal stack requirement from global analysis=55To make the tool more useful we provide a number of extra features,including switching between context-sensitive and context-insensitive program analysis,creating a graphical callgraph for a system,listing branches that can be proven to be dead in all contexts,finding the shortest path through a program that reaches the maximum stack depth,and printing a disassembled version of the embedded program with annotations indicating interrupt status and worst-case stack depth at each instruction.These are all useful in helping developers understand and manually reduce stack memory consump-tion in their programs.There are other obvious ways to use the stack tool that we have not yet implemented. For example,using stack bounds to compute the maximum size of the heap for a sys-tem so that it stops just short of compromising stack safety,or computing a minimum safe stack size for individual threads in a multi-threaded embedded system.Ideally,the analysis would become part of the build process and values from the analysis would be used directly in the code being generated.3Validating the AnalysisWe used several approaches to increase our confidence in the validity of our analysis techniques and their implementations.103.1Validating the Abstract InterpretationTo test the abstract interpretation,we modified a simulator for A VR processors to dump the state of the machine after executing each instruction.Then,we created a separate program to ensure that this concrete state was“within”the conservative approximation of the machine state produced by abstract interpretation at that address,and that the simulator did not execute any instructions that had been marked as dead code by the static analysis.During early development of the analysis this was helpful infinding bugs and in providing a much more thorough check on the abstract interpretation than manual inspection of analysis results—our next-best validation technique.We have tested the current version of the stack analysis tool by executing at least100,000instructions of about a dozen programs,including several that were written specifically to stress-test the analysis,and did notfind any discrepancies.3.2Validating Stack BoundsThere are two important metrics for validating the bounds returned by the stack tool. Thefirst is qualitative:Does the tool ever return an unsafe result?Testing the stack tool against actual execution of about a dozen embedded applications has not turned up any examples where it has returned a bound that is less than an observed stack depth.This justifies some confidence that our algorithms are sound.Our second metric is quantitative:Is the tool capable of returning results that are close to the true worst-case stack depth for a system?The maximum observed stack depth,the worst-case stack depth estimate from the stack tool,and the(non-computable) true worst-case stack depth are related in this way:worst observed true worst estimated worstOne might hope that the precision of the analysis could be validated straightfor-wardly by instrumenting some embedded systems to make them report their worst ob-served stack depth and comparing these values to the bounds on stack depth.For several reasons,this approach produces maximum observed stack depths that are significantly smaller than the estimated worst case and,we believe,the true worst case.First,the timing issues that we discussed in Section1come into play,making it very hard to ob-serve interrupt handlers preempting each other even when it is clearly possible that they may do so.Second,even within the main function and individual interrupt handlers,it can be very difficult to force an embedded system to execute the code path that pro-duces the worst-case stack depth.Embedded systems often present a narrower external interface than do traditional applications,and it is correspondingly harder to force them to execute certain code paths using test inputs.While the difficulty of thorough test-ing is frustrating,it does support our thesis that static program analysis is particularly important in this domain.The71embedded applications that we used to test our analysis come from three families.Thefirst is Autopilot,a simple cyclic-executive style control program for an autonomous helicopter[10].The second is a collection of application programs that are distributed with TinyOS version0.6.1,a small operating system for networked sensor11。

Thermo Scientific MK.4 ESD和Latch-Up测试系统中文名说明书

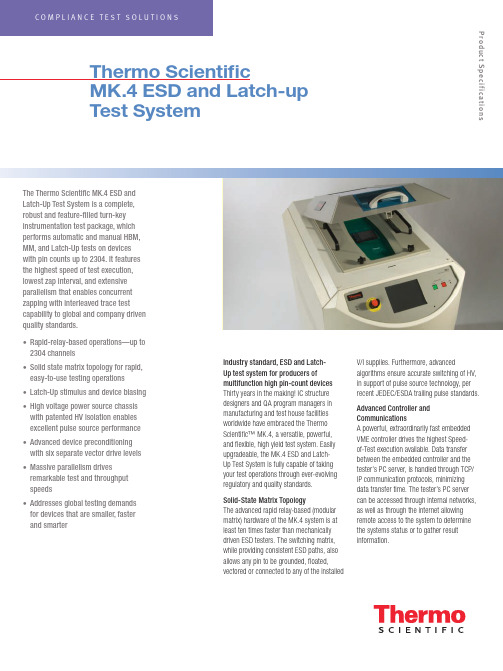

The Thermo Scientific MK.4 ESD and Latch-Up Test System is a complete,robust and feature-filled turn-key instrumentation test package, which performs automatic and manual HBM, MM, and Latch-Up tests on devices with pin counts up to 2304. It features the highest speed of test execution, lowest zap interval, and extensive parallelism that enables concurrent zapping with interleaved trace test capability to global and company driven quality standards.• Rapid-relay-based operations—up to 2304 channels• Solid state matrix topology for rapid, easy-to-use testing operations • Latch-Up stimulus and device biasing • High voltage power source chassis with patented HV isolation enables excellent pulse source performance • Advanced device preconditioning with six separate vector drive levels • Massive parallelism drives remarkable test and throughput speeds• Addresses global testing demands for devices that are smaller, faster and smarterThermo ScientificMK.4 ESD and Latch-up Test SystemIndustry standard, ESD and Latch-Up test system for producers ofmultifunction high pin-count devices Thirty years in the making! IC structure designers and QA program managers in manufacturing and test house facilities worldwide have embraced the Thermo Scientific™ MK.4, a versatile, powerful, and flexible, high yield test system. Easily upgradeable, the MK.4 ESD and Latch-Up Test System is fully capable of taking your test operations through ever-evolving regulatory and quality standards.Solid-State Matrix TopologyThe advanced rapid relay-based (modular matrix) hardware of the MK.4 system is at least ten times faster than mechanically driven ESD testers. The switching matrix, while providing consistent ESD paths, also allows any pin to be grounded, floated,vectored or connected to any of the installedV/I supplies. Furthermore, advancedalgorithms ensure accurate switching of HV, in support of pulse source technology, per recent JEDEC/ESDA trailing pulse standards.Advanced Controller and CommunicationsA powerful, extraordinarily fast embedded VME controller drives the highest Speed- of-Test execution available. Data transfer between the embedded controller and the tester’s PC server, is handled through TCP/IP communication protocols, minimizing data transfer time. The tester’s PC server can be accessed through internal networks, as well as through the internet allowing remote access to the system to determine the systems status or to gather result information.Product SpecificationsLatch-Up Stimulus and Device Biasing The MK.4 can be equipped with up to eight 100 V four-quadrant Voltage and Current (V/I) power supplies. Each V/I supply has a wide dynamic range enabling it to force and measure very low voltage at high current levels from 100 mV/10 A to 100 V/1 A. The system’s power supply matrix can deliver up to a total of 18A of current, which is distributed between the installed supplies. These supplies are able to provide a fast and versatile means of making DC parametric and leakage measurements as well as providing latch-up pulses, while offering total control and protection of the DUT.Advanced Device PreconditioningThe MK.4 system provides the most advanced device preconditioning capability available. The DUT can be vectored with complex vector patterns, providing excellent control over the device. Each pin can be driven using one of the 6 different vector supplies. The patterns can be up to 256k deep, running at clock speeds of up to 10 MHz. Device conditioning is easily verified, using the read back compare capability available on every pin.Thermo Scientific MK.4 Scimitar™Software Makes Programming Easy, while Providing Unsurpassed Programming FlexibilityThe MK.4 Windows®-based Scimitar operating software empowers users with the flexibility to easily set-up tests based on industry standards or company driven requirements.Device test plans can be created by importing existing text based device files, on the testers PC server or off-line from a satellite PC containing the application. The software also provides the capabilities to import test plans and device files from previous Thermo Scientific test systems.Test vectors from your functional testers can also be imported into the application. And of course, the vector application allows manual creation and debug of vector files.Device test plans and results are stored in an XML data base, providing unsurpassed results handling, sorting and data mining capabilities.Parallelism Drives Remarkable Test Throughput SpeedsThe MK.4 software enables ESD testing of up to twelve devices at one time using the multisite pulse source design.Embedded VME power supplies eliminate any communication delays that would be seen by using stand alone supplies. The embedded parametric (curve tracing) supply also provides fast, accurate curve tracing data to help you analyze your devices performance.The systems curve tracer can also be used as a failure analysis tool by allowing the comparison of stored, known good results, versus results from a new test sample or samples.Ready for Today’s Component Reliability Demands and Anticipating Those to Come ESD and Latch-Up testing of electronic and electrical goods can be very expensive aspects of the design and manufacturing process. This is especially true as market demands for products that are smaller, faster and smarter become the standard rather than the exception. The Thermo Scientific MK.4 leverages the technology and know- how gained over three decades of test system experience, as well as our in-depth participation and contributions to global regulatory bodies governing these changes, enabling today’s products to meet both global and industry-driven quality standards.The real key to our customers’ success is in anticipating what’s next. And to ensure that our customers possess the ability to evolve quickly to meet all change factors with efficiency and cost effectiveness.As such, the strategically-designed, field upgradeable architecture of the MK.4 system ensures a substantial return on investment over a very considerable test system lifecycle, as well as better short- and long-term qualityand ESD and Latch-Up test economies.Custom fixtures include universal package adaptors to enable the industry’s lowest cost-in-service high pin count device fixturing yetdevised. (2304-pin, Universal 1-mm pitch BGA package adaptor shown.)100W V/I Performance Thermo Scientific MK.4: eight-V/I configuration. Powerful V/Is can deliver a total of 800 W to the DUT, enabling complex testing of all advanced high power processors on your product roadmap.Solid state matrix topology for rapid, easy-to-use testing operations. Design ensures waveform integrity and reproducibility.General SpecificationsHuman Body Model (HBM) per ESDA/JEDEC JS-001-2014, MIL-STD 883E, and AEC Q100-002 25 V to 8 kV in steps of 1 V Test to multiple industry standards in one integrated system; no changing or alignment of pulse sources.Wizard-like prompts on multi-step user actions MachineModel (MM) per ESDA STM5.2, JEDEC/JESD22-A115, andAEC Q100-003, 25 V to 1.5 kV in steps of 1 VIntegrated pulse sources allow fast multi-site test execution.Latch-up testing per JEDEC/JESD 78 test pin and AECQ100-004Includes preconditioning, state read-back and full control of each.Rapid Relay-based operations at least 10 times faster thanrobotic-driven testersSuper fast test speeds.Test devices up to 2304 pins Systems available configured as 1152, 1728 or 2304 pins.Waveform network: Two, 12 site HBM (100 pF/1500Ω)and MM (200 pF/0Ω) pulse sources address up to 12devices simultaneouslyPatented design ensures waveform compliance for generations to come.Multiple device selection When multiple devices are present; graphical display indicates the devices selectedfor test; progress indicator displays the current device under test (DUT), along withtest status information.Unsurpassed software architecture Flexible programming, easy to use automated test setups, TCP/IP communication. Enables use of device set-up information Increased efficiency and accuracy from other test equipment, as well as deviceinformation import.Event trigger output Manages setup analysis with customized scope trigger capabilities.High voltage power supply chassis Modular chassis with patented HV isolation enables excellent pulse sourceperformance.Power supply sequencing Provides additional flexibility to meet more demanding test needs of integratedsystem-on-chip (SOC) flexibility.Manages ancillary test equipment through Plug-n feature allows the user to control external devices, such as scopes or heatstreams or other devices the Scimitar Plug-ins feature as required for automatedtesting.Pin drivers for use during Latch-Up testing Vector input/export capability from standard tester platforms and parametricmeasurements.256k vectors per pin with read-back Full real-time bandwidth behind each of the matrix pins.Six independent vector voltage levels Test complex I/O and Multi-Core products with ease.Up to 10MHz vector rate (programmable) Quickly and accurately set the device into the desired state for testing from an internalclock.Comprehensive engineering vector debug. Debug difficult part vectoring setups with flexibility.Up to eight separate V/I supplies (1 stimulus and 7 bias supplies) capability through the V/I matrix High accuracy DUT power, curve tracing, and Latch-up stimulus available; design also provides high current.Low resolution/high accuracy parametric measurements, using an embedded Keithley PSU With the optional Keithley PSU feature (replaces one V/I, nA measurements are achievable, allowing supply bus resistance measurement analysis to be performed.Multiple self-test diagnostic routines Ensures system integrity throughout the entire relay matrix, right up to the test socket Test reports: pre-stress, pre-fail (ESD) and post-fail data,as well as full curve trace and specific data pointmeasurementsData can be exported for statistical evaluation & presentation.Individual pin parametrics Allows the user to define V/I levels, compliance ranges, and curve trace parametersfor each pin individually.Enhanced data set features Report all data gathered for off-line reduction and analysis; core test data is readilyavailable; all data is stored in an easy-to-manipulate standard XML file structure. Interlocked safety cover Ensures no user access during test. All potentially lethal voltages are automaticallyterminated when cover is opened. Safety cover window can be easily modified toaccept 3rd party thermal heads.Dimensions60 cm (23.5 in) W x 99 cm (39 in) D x 127 cm (50 in) H© 2016 Thermo Fisher Scientific Inc. All rights reserved. Windows is a registered trademark of Microsoft Corporation in the United States and/or other countries. All other trademarks are the property of Thermo Fisher Scientific and its subsidiaries. Results may vary under different operating conditions. Specifications, terms and pricing are subject to change. Not all products are available in all countries. Please consult your local sales representative for details.Africa-Other +27 11 570 1840 Australia +61 2 8844 9500 Austria +43 1 333 50 34 0 Belgium +32 53 73 42 41 Canada +1 800 530 8447 China +86 10 8419 3588 Denmark +45 70 23 62 60 Europe-Other +43 1 333 50 34 0Finland /Norway/Sweden+46 8 556 468 00France +33 1 60 92 48 00Germany +49 6103 408 1014India +91 22 6742 9434Italy +39 02 950 591Japan +81 45 453 9100Latin America +1 608 276 5659Middle East +43 1 333 50 34 0Netherlands +31 76 579 55 55South Africa +27 11 570 1840Spain +34 914 845 965Switzerland +41 61 716 77 00UK +44 1442 233555USA +1 800 532 4752Thermo Fisher Scientific,San Jose, CA USA is ISO Certified. CTS.05102016Product SpecificationsScimitar Software FeaturesSummary Panel with easy navigation among device componentsWizard-like prompts on multi-step user actionsControl of external devices through the use of Scimitar’s user programmable Plug-in capabilities, in addition to the Event Trigger Outputs, which provide TTL control signals for external devices, such as power supplies or for triggering oscilloscopesFlexible parametric tests that are defined and placed at an arbitrary position within the executable test plan.Comprehensive results viewer that provides:• ESD and Static Latch-up data viewing capabilities• Curves viewer with zooming capabilities and the ability to add user comments• Data filtering on the following criteria – failed pins, failed results, final stress levels• A complete set or subset of results using user defined parameters• Sorting in ascending or descending order by various column criteriaTree-like logical view of the tests and test plans.Flexible data storage that provides the ability for the end-user to query the dataSeamless support of existing ZapMaster, MK.2, MK.4, and Paragon test plansCurve tracing with curve-to-curve and relative spot-to-spot comparisonOff-line curve analyzing, including third-party generated waveformsCanned JESD78A test (static latch-up only) that can be defined automaticallyPause/Resume test capabilitiesIntermediate results viewingAutomated waveform capture capability and analysis using the embedded EvaluWave software feature。

ENCOUNTERTRUE-TIMEATPG

Encounter True-Time ATPGPart of the Encounter Test family, Encounter True-Time ATPG offers robust automated test patterngeneration (ATPG) engines, proven to generate the highest quality tests for all standard design-for-test (DFT) methods, styles, and flows. It supports not only industry-standard stuck-at and transition fault models, but also raises the bar on fault detection by providing defect-based, user-definable modeling capability with its patented pattern fault technology.Pattern fault technology is what enables the Encounter “gate-exhaustive” coverage(GEC) methodology, proven to be two-to-four times more efficient at detecting gate intrinsic faults than any other static methodologies available on the market (e.g. SSF, N-Detect).For delay test, True-Time ATPGincludes a dynamic timing engine and uses either circuit timing information or constraints to automaticallygenerate transition-based fault tests and faster-than-at-speed tests for identifying very deep sub-micron design-process feature defects (e.g. certain small delay defects).Figure 1: Encounter True-Time ATPG provides a timing-based ATPG engine driven by SDF or SDC informationOn-product clock generation (OPCG) produces and applies patterns to effectively capture this class of faults while minimizing false failures. Use of SDF or SDC information ensures the creation of a highly accurate timing-based pattern set.True-Time ATPG optimizes test coverage through a combination of topological random resistant fault analysis (RRFA) and deterministic fault analysis (DFA)with automated test point insertion—far superior to traditional test coverage algorithms. RRFA is used for early optimi-zation of test coverage, pattern density, and runtime performance. DFA is applied downstream for more detailed circuit-level fault analysis when the highest quality goals must be met.To reduce scan test time while maintaining the highest test coverage, True-Time technology provides intelligent ATPG with on-chip compression (XOR- or MISR-based). It is also power-aware and uses patented technologies to significantly reduce and manage power consumption during manufacturing test.True-Time ATPG also offers a customizable environment to suityour project development needs.The GUI provides highly interactive capabilities for coverage analysis and debug; it includes a powerful sequence analyzer that boosts productivity. Encounter True-Time ATPG is available in two offerings: Basic and Advanced.Benefits• Ensures high quality of shipped silicon with production-proven 2-4x reduction in test escapes• Provides superior partial scan coverage with proprietary pattern fault modeling and sequential ATPG algorithms• Optimizes test coverage with RRFA and DFA test point insertion methodology • Boosts productivity by integrating with Encounter RTL Compiler• Delivers superior runtime throughput with high-performance model build and fault simulation engines as well as distributed ATPG • Lowers cost of test with patterncompaction and compressiontechniques that maintain fullscan coverage• Balances tester costs with diagnosticsmethodologies by offering flexiblecompression architectures with fullX masking capabilities (includingOPMISR+ and XOR-based solutions)• Supports low pin-count testingvia JTAG control of MBIST andhigh-compression ratio technology• Supports reduced pin-count testing forI/O test• Interfaces with Encounter Power Systemfor accurate power calculation andpattern IR drop analysis• Reduces circuit and switching activityduring manufacturing test to managepower consumption• Reduces false failures due tovoltage drop• Provides a GUI with powerfulinteractive analysis capabilitiesincluding a schematic viewer andsequence analyzerEncounter TestPart of the Encounter digital design andimplementation platform, the EncounterTest product family delivers an advancedsilicon verification and yield learningsystem. Encounter Test comprises threeproduct technologies:• Encounter DFT Architect: ensuresease of use, productivity, and predict-ability in generating ATPG-readynetlists containing DFT structures, fromthe most basic to the most complex;available as an add-on option toEncounter RTL Compiler• Encounter True-Time ATPG: ensuresthe fewest test escapes and the highestquality shipped silicon at the lowestdevelopment and production costs• Encounter Diagnostics: delivers themost accurate volume and precisiondiagnostics capabilities to accelerateyield ramp and optimize device andfault modelingEncounter Test also offers a flexible APIusing the PERL language to retrieve designdata from its pervasive database. Thisunique capability allows you to customizeSoC Test Infrastructure• Maximize productivity• Maximize predictabilityTest Pattern Generation• Maximize product quality• Minimize test costsDiagnostic• Maximize yeld and ramp• Maximize silicon bring-upEncounter DFT Architect• Full-chip test infrastructure• Scan compression(XOR and MISR), BIST,IEEE1500, 1149.1/6• ATPG-aware insertionverification• Power-aware DFT and ATPGEncounter True-Time ATPG• Stuck-at, at-speed, andfaster-than-at-speed testing• Design timing drivestest timing• High-quality ATPGEncounter Diagnostics• Volume mode finds criticalyield limiters• Precision mode locatesroot cause• Unsurpassed silicon bring-upprecisionSiliconFigure 2: Encounter Test offers a complete RTL-to-silicon verification flow and methodologies that enable the highest quality IC devices at the lowest costreporting, trace connections in the design, and obtain information that might be helpful for debugging design issues or diagnostics.FeaturesTrue-Time ATPG BasicTrue-Time ATPG Basic contains thestuck-at ATPG engine, which supports:• High correlation test coverage, easeof use, and productivity through integration with the Encounter RTL Compiler synthesis environment• Full scan, partial scan, and sequential ATPG for edge-triggered andLSSD designs• Stuck-at, IDDQ, and I/O parametric fault models• Core-based testing, test data migration, and test reuse• Special support for custom designs such as data pipelines, scan control pipelines, and safe-scan• Test pattern volume optimization using RRFA-based test point insertion• Test coverage optimization usingDFA-based test point insertion• Pre-defined (default) and user-defined defect-based fault modeling andgate-exhaustive coverage based on pattern fault technology• Powerful GUI with interactive analysis capabilitiesPattern fault capability enables defect-based testing with a patented technology for accurately modeling the behavior of nanometer defects, such as bridges and opens for ATPG and diagnostics, and for specifying the complete test of a circuit. The ATPG engine, in turn, uses this definition wherever the circuit is instan-tiated within a design. By default, pattern faults are used to increase coverage of XOR, LATCH, FLOP, TSD, and MUX primi-tives. They can also be used to model unique library cells and transition and delay-type defects.True-Time ATPG AdvancedTrue-Time ATPG Advanced offers thesame capabilities as the Basic configu-ration, plus delay test ATPG functionality.It uses post-layout timing data from theSDF file to calculate the path delay of allpaths in the design, including distributiontrees of test clocks and controls. Usingthis information, you can decide on thebest cycle time(s) to test for in a givenclock domain.True-Time ATPG Advanced is capableof generating tests at multiple testfrequencies to detect potential early yieldfailures and certain small delay defects.You can specify your own cycle time orlet True-Time ATPG calculate one basedon path lengths. It avoids generating testsalong paths that exceed tester cycle timeand/or mask transitions along paths thatexceed tester cycle time. True-Time ATPGgenerates small delay defect patternsbased on longest path analysis to ensurepattern efficiency.A unique feature of the Advancedoffering is its ability to generate faster-than-at-speed tests to detect small delaydefects that would otherwise fail duringsystem test or result in early field failures.True-Time ATPG Advanced also usestester-specific constraint informationduring test pattern generation. Thecombination of actual post-layout timingand tester constraint information withTrue-Time ATPG Advanced algorithmsensures that the test patterns will work“first pass” on the tester.The test coverage optimizationmethodology is expanded beyond RRFAand DFA-based test point insertion(TPI) technology. The combinationof both topological and circuit-levelfault analysis with automated TPIprovides the most advanced capabilityfor ensuring the highest possible testcoverage while controlling the numberof inserted test points. DFA-based TPIBridge TestingFigure 3: Pattern faults model any type ofbridge behavior; net pair lists automaticallycreate bridging fault models; ATPG anddiagnostics use the models to detect andisolate bridgesFigure 4: Power-aware ATPG for scan and capture modes prevents voltage-drop–induced failures in test modeCadence is transforming the global electronics industry through a vision called EDA360.With an application-driven approach to design, our software, hardware, IP, and services helpcustomers realize silicon, SoCs, and complete systems efficiently and profitably. © 2012 Cadence Design Systems, Inc. All rights reserved. Cadence, the Cadence logo, Conformal, Encounter, and VoltageStorm are registered trademarks of Cadence Design Systems, Inc. All other s are properties of their respective holders.has links to Encounter Conformal ® Equivalence Checker to ensure the most efficient, logically equivalent netlist modifications with maximum controllability and observability.The ATPG engine works with multiple compression architectures to generate tests that cut costs by reducing scan test time and data volume. Actual compression ratios are driven by the compression architecture as well asdesign characteristics (e.g. available pins, block-level structures). Users can achieve compression ratios exceeding 100x.Flexible compression options allow you to select a multiple input signature register (MISR) architecture with the highest compression ratio, or an exclusive-or (XOR)–based architecture that enables a highly efficientcombinational compression ratio and a one-pass diagnostics methodology. Both architectures support a broadcast type or XOR-based decompressor.On-product MISR plus (OPMISR+) uses a MISR-based output compression, which eliminates the need to check the response at each cycle. XOR-based compression uses an XOR-tree–based output compression to enable a one-pass flow through diagnostics.Additionally, intelligent ATPG algorithms minimize full-scan correlation issues and reduce power consumption, deliv-ering demonstrated results of >99.5 stuck-at test coverage with >100x test time reduction. Optional X-state masking capability is available on a per-chain/ per-cycle basis. Masking is usuallyrequired when using delay test because delay ATPG may generate unknown states in the circuit.Using the Common Power Format (CPF), True-Time ATPG Advanced automatically generates test modes to enable individual power domains to be tested independently or in small groups. This, along with automaticrecognition and testing of power-specific structures (level shifters, isolation logic, state retention registers) ensures the highest quality for low-power devices.Power-aware ATPG uses industry-leading techniques to manage and significantly reduce power consumption due to scan and capture cycles during manufacturing test. The benefit is reduced risk of false failures due to voltage drop and fewer reliability issues due to excessive power consumption. True-Time ATPG Advanced uses algorithms that limit switching during scan testing to further reduce power consumption.Encounter Test offers a flexible API using the PERL language to retrievedesign data from its pervasive database. This unique capability allows users to customize reporting, trace connections in the design, and obtain information that might be helpful for debugging design issues or diagnostics.Platforms• Sun Solaris (64-bit)• HP-UX (64-bit)• Linux (32-bit, 64-bit)• IBM AIX (64-bit)Cadence Services and Support• Cadence application engineers can answer your technical questions by telephone, email, or Internet—they can also provide technical assistance and custom training • Cadence certified instructors teach more than 70 courses and bring their real-world experience into the classroom • More than 25 Internet Learning Series (iLS) online courses allow you the flexibility of training at your own computer via the Internet • Cadence Online Support gives you24x7 online access to a knowledgebase of the latest solutions, technicaldocumentation, software downloads, and more。

单机下最小化最大延迟问题的滚动调度方法研究