RTL8671B+RTL8271B应用参考原理图

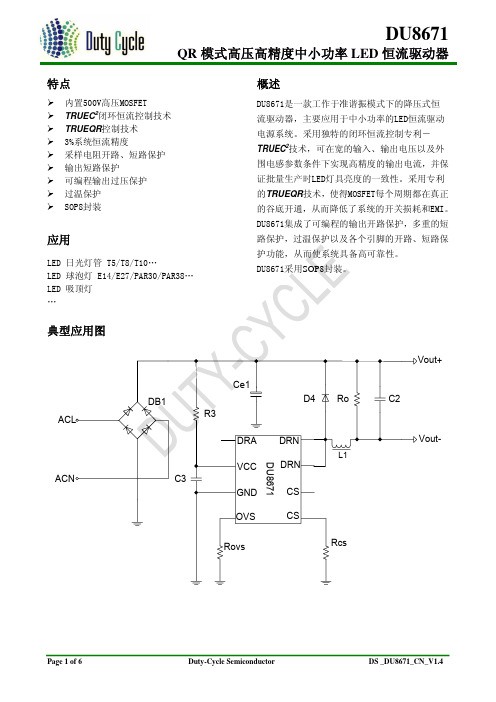

DU8671

电气参数

(无特别说明外,VCC=15V, Ta=25oC)

符号

参数

测试条件

最小值 典型值 最大值 单位

电源供电部分

VCCCLAMP VCC 钳位电压

VCCON 芯片开启工作电压

VCCOFF 芯片关断电压

VCCOVP VCC 过压保护电压

ISS

启动电流

IOP

工作电流

电流采样

IVCC<10mA VCC 上升 VCC 下降 IVCC>10mA

-0.3~500

V

OVS

1 输出开路电压设置端

-0.3~6

V

CS

7,8 电流采样端

-0.3~6

V

IVCC DRA

3 VCC 最大钳位电流 4 内置低压MOSFET漏极

10

mA

-0.3~40

V

θJA

--- 热阻(结温-环境)

Tj

--- 最大工作结温

150 -40~150

℃/W ℃

Tstg

--- 存储温度范围

DU8671

QR 模式高压高精度中小功率 LED 恒流驱动器

特点

¾ 内置500V高压MOSFET ¾ TRUEC2闭环恒流控制技术 ¾ TRUEQR控制技术 ¾ 3%系统恒流精度 ¾ 采样电阻开路、短路保护 ¾ 输出短路保护 ห้องสมุดไป่ตู้ 可编程输出过压保护 ¾ 过温保护 ¾ SOP8封装

应用

LED 日光灯管 T5/T8/T10… LED 球泡灯 E14/E27/PAR30/PAR38… LED 吸顶灯 …

输出电流比较基准 最大关断时间 最小关断时间 最大开通时间

396

400

404

以太网接口PCB设计经验分享

以太网口PCB布线经验分享目前大部分32位处理器都支持以太网口。

从硬件的角度看,以太网接口电路主要由MAC控制器和物理层接口(Physical Layer,PHY)两大部分构成,目前常见的以太网接口芯片,如LXT971、RTL8019、RTL8201、RTL8039、CS8900、DM9008等,其内部结构也主要包含这两部分。

一般32位处理器内部实际上已包含了以太网MAC控制,但并未提供物理层接口,因此,需外接一片物理层芯片以提供以太网的接入通道。

常用的单口10M/100Mbps高速以太网物理层接口器件主要有RTL8201、LXT971等,均提供MII接口和传统7线制网络接口,可方便的与CPU接口。

以太网物理层接口器件主要功能一般包括:物理编码子层、物理媒体附件、双绞线物理媒体子层、10BASE-TX编码/解码器和双绞线媒体访问单元等。

下面以RTL8201为例,详细描述以太网接口的有关布局布线问题。

一、布局1、RJ452、3、元件周围4、RTL8201和变压器之间的距离也应该尽可能的短。

为了实际操作的方便,这一点经常被放弃。

但是,保持Tx±, Rx±信号走线的对称性是非常重要的,而且RTL8201和变压器之间的距离需要保持在一个合理的范围内,最大约10~12cm。

5、Tx+ and Tx- (Rx+ and Rx-) 信号走线长度差应当保持在2cm之内。

二、布线1、走线的长度不应当超过该信号的最高次谐波(大约10th)波长的1/20。

例如: 25M的时钟走线不应该超过30cm,125M信号走线不应该超过12cm (Tx±, Rx±)。

2、电源信号的走线(退耦电容走线,电源线,地线)应该保持短而宽。

退耦电容上的过孔直径最好稍大一点。

3、每一个电容都应当有一个独立的过孔到地。

4、退耦电容应当放在靠近IC的正端(电源),走线要短。

每一个RTL8201 模拟电源端都需要退耦电容(pin 32, 36, 48).每一个RTL8201 数字电源最好也配一个退耦电容。

小信号解码集成块LA76810ALA76818A引脚功能和应用电路图纸

小信号解码集成块LA76810ALA76818A引脚功能和应用电路图纸LA76810A引脚功能 LA76818A引脚功能引脚功能工作电压/V 对地电阻(R×1KΩ)正测/Ω反测/Ω1 音频输出 2.0 3.9K 3.8K2 调频输出 1.9 7.0K 8.5K3 图象中频【AGC】滤波 2.1 7.4K 9.0K4 RF 【AGC】输出 3.5 6.8K 16K5 图象中频输入 2.6 7.2K 8.2K6 图象中频输入 2.6 7.2K 8.2K7 地 0 0 08 中频dianyuan电源 4.6 0.5K 0.5K9 滤波 1.5 7.4K 9.5K10 AFT输出 2.2 7.0K 8.8K11 总线【存储器数据】线 4.4 4.3K 5.5K12 总线时钟线 4.3 4.3K 5.5K13 自动亮度限制 3.9 5.6K 4.5K14 R输入 0.5 7.2K 8.6K15 G输入 0.5 7.2K 8.6K16 B输入 0.5 7.2K 8.6K17 消隐输入 0 3.4K 3.4K18 RGBdianyuan电源 7.2 0.7K 0.7K19 R输出 2.0 5.5K 7.8K20 G输出 1.9 5.6K 7.8K21 B输出 2.0 5.5K 7.8K22 同步分离输出 0.2 5.8K 8.0K23 场输出 2.2 2.0K 2.0K24 场锯齿波滤波 1.2 7.4K 8.6K25 行dianyuan电源 4.9 0.7K 0.7K26 行AFC滤波 2.4 7.4K 9.1K27 行输出 0.5 2.2K 2.1K28 行逆程脉冲输入 0.8 7.2K 8.2K29 VCO基准 1.4 4.9K 4.8K30 4MHz时钟输出 0.1 5.4K 9.1K31 dianyuan电源 4.7 0.5K 0.5K32 滤波 7.5 4.8K ∞K33 地 0 0 034 SECAM B-Y输入 1.6 7.5K 8.2K35 SECAM R-Y输入 1.6 7.5K 8.4K36 C-AFC滤波 3.5 7.8K 8.8K37 FSC输出 2.1 7.0K 8.2K38 4.43MHz晶振 2.5 7.6K 8.8K39 色度APC滤波 2.7 7.5K 8.4K40 视频输出 2.2 7.5K 9.0K41 地 0 0 042 外接视频输入 2.3 7.6K 9.0K43 V/C/Ddianyuan电源 4.7 0.5K 0.5K44 视频输入 2.4 7.5K 9.1K45 黑延伸滤波 1.6 7.5K 8.2K46 视频输出 1.9 1.8K 1.7K47 图象中频APC滤波0.9 7.5K 9.0K48 视频检波 3.9 1.1K 1.0K49 视频检波 3.9 1.1K 1.1K50 VDO滤波 2.2 7.2K 9.0K51 外接音频输入 1.6 7.5K 8.8K52 伴音中频输出 1.6 7.2K 9.0K53 伴音中频APC滤波1.9 7.4K 9.0K54 伴音中频输入 2.8 7.6K 9.1KLA76810相信大家都不陌生,但在组装机上却的故障表现却千奇百怪;笔者将一些实践维修结论公布于此,供大家探讨。

博安通WIFI模块常用使用方法

第二步: 扫描当前局域网的热点,使用命令: ATWS

打印截图如下:

第三步: 设置 WIFI 的模式为 STA 模式,使用命令: ATPW=1

打印截图如下:

第四步: 设置 WIFI STA 模式的参数,使用命令: ATPN=<ssid>,<pwd>,<key_id>(,<bssid>)

文件版本 01 (2016-03-01)

文件版本 01 (2016-03-01)

版权所有

博安通专有和保密信息 中山市博安通通信技术有限公司

RTL8710 专业型 IOT WIFI SOC

RTL8710

一,WIFI 连接功能设置 1.1,STA 模式的设置

第一步: 设置打印信息,使用命令: ATSE=2

打印截图如下: (0: NO DEBUG,1:OUTPUT REMOTE UART, 2:LOCALE UART, DEFAULT MODE 1)

打印截图如下:

注意: 使用 ATW?查看当前 wifi 的状态信息确定是否设置成功: 打印截图如下:

文件版本 01 (2016-03-01)

版权所有

博安通专有和保密信息 中山市博安通通信技术有限公司

RTL8710 专业型 IOT WIFI SOC

第二步: 设置 WIFI 的模式为 AP 模式:使用命令: ATPW=2 打印截图如下:

文件版本 01 (2016-03-01)

版权所有

博安通专有和保密信息 中山市博安通通信技术有限公司

RTL8710 专业型 IOT WIFI SOC

RTL8710

第三步: 设置 WIFI STA 模式的参数,使用命令: ATPA=<ssid>,<pwd>,<chl>,<hidden>

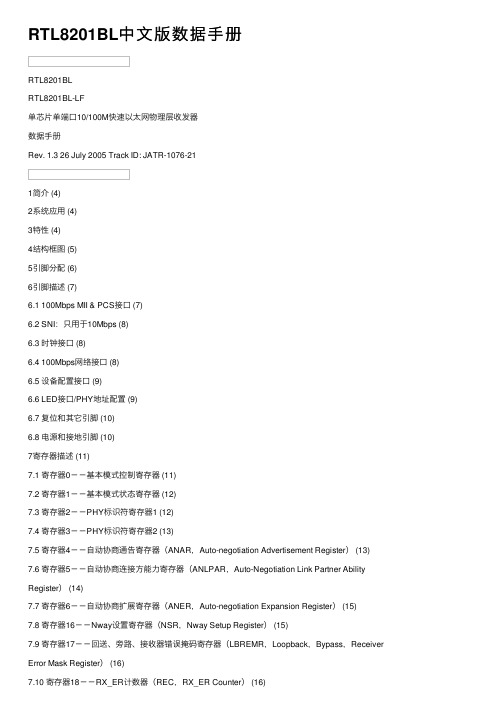

RTL8201BL中文版数据手册

RTL8201BL中⽂版数据⼿册RTL8201BLRTL8201BL-LF单芯⽚单端⼝10/100M快速以太⽹物理层收发器数据⼿册Rev. 1.3 26 July 2005 Track ID: JATR-1076-211简介 (4)2系统应⽤ (4)3特性 (4)4结构框图 (5)5引脚分配 (6)6引脚描述 (7)6.1 100Mbps MII & PCS接⼝ (7)6.2 SNI:只⽤于10Mbps (8)6.3 时钟接⼝ (8)6.4 100Mbps⽹络接⼝ (8)6.5 设备配置接⼝ (9)6.6 LED接⼝/PHY地址配置 (9)6.7 复位和其它引脚 (10)6.8 电源和接地引脚 (10)7寄存器描述 (11)7.1 寄存器0--基本模式控制寄存器 (11)7.2 寄存器1--基本模式状态寄存器 (12)7.3 寄存器2--PHY标识符寄存器1 (12)7.4 寄存器3--PHY标识符寄存器2 (13)7.5 寄存器4--⾃动协商通告寄存器(ANAR,Auto-negotiation Advertisement Register) (13) 7.6 寄存器5--⾃动协商连接⽅能⼒寄存器(ANLPAR,Auto-Negotiation Link Partner Ability Register) (14)7.7 寄存器6--⾃动协商扩展寄存器(ANER,Auto-negotiation Expansion Register) (15)7.8 寄存器16--Nway设置寄存器(NSR,Nway Setup Register) (15)7.9 寄存器17--回送、旁路、接收器错误掩码寄存器(LBREMR,Loopback,Bypass,Receiver Error Mask Register) (16)7.10 寄存器18--RX_ER计数器(REC,RX_ER Counter) (16)7.11 寄存器19--10Mbps⽹络接⼝配置寄存器 (17)7.12 寄存器20--PHY1_1寄存器 (17)7.13 寄存器21--PHY1_2寄存器 (17)7.14 寄存器22--PHY 2寄存器 (17)7.15 寄存器23--Twister_1寄存器 (17)7.16 寄存器24--Twister_2寄存器 (18)7.17 寄存器25--测试寄存器 (18)8功能描述 (18)8.1MII和管理接⼝ (19)8.1.1数据传递 (19)8.1.2串⾏管理 (19)8.2 ⾃动协商和平⾏检测 (20)8.3 流控⽀持 (21)8.4 硬件配置和⾃动协商 (21)8.5 LED和PHY地址配置 (22)8.6 串⾏⽹络接⼝ (22)8.7 掉电、掉线、省电和隔离模式 (22)8.8 媒介接⼝ (23)8.8.1100Base-TX (23)8.8.2100Base-FX光纤操作⽅式 (23)8.8.310Base-Tx/Rx (24)8.9 转发器模式 (24)8.10 复位和传输偏压(RTSET,Reset and Transmit Bias) (24) 8.11 3.3V电源⽀持和电压转化电路 (24)8.12 远端故障指⽰ (25)9电⽓特性 (25)9.1 D.C.特性 (25)9.1.1绝对最⼤额定值 (25)9.1.2操作条件 (25)9.1.3功耗 (26)9.1.4供电电压:Vcc (26)9.2 A.C.特性 (27)9.2.1MII发送时序 (27)9.2.2MII接收时序 (28)9.2.3SNI发送时序 (29)9.2.4SNI接收时序 (29)9.2.5MDC/MDIO时序 (29)9.2.6⽆冲突发送 (30)9.2.7⽆冲突接收 (31)9.3 晶振和变压器规格 (31)9.3.1晶振规格 (31)9.3.2变压器规格 (31)10机械尺⼨ (32)11订购信息 (33)1简介RTL8201BL是⼀个单端⼝的物理层收发器,它只有⼀个MII/SNI(媒体独⽴接⼝/串⾏⽹络接⼝)接⼝。

Datasheet_RTL8671B_v04_preliminary

RTL8671B/ RTL8671BH Integrated ADSL2+ Router ControllerDatasheetRev. 0.46 May, 2008Track ID: xxxx-nnnn-nn©2003 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.DISCLAIMERRealtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.TRADEMARKSRealtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners. CONFIDENTIALITYThis document is confidential and should not be provided to a third-party without the permission of Realtek Semiconductor Corporation.USING THIS DOCUMENTThis document is intended for the software engineer’s reference and provides detailed programming information.Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process.REVISION HISTORYRevision Release Date Summary0.0 2008/01/18 First release.0.1 2008/01/23 n Correcting pin 113 as ‘OVDD’n Block diagram added0.2 2008/01/30 n Correcting pin 12 as ‘VSS’0.3 2008/01/31 n Correcting polarity of ‘U1ID’0.4 2008/05/06 n‘U1ID’ should be input only, not I/On RTL8671BH addedTable of Contents1.GENERAL DESCRIPTION (1)2.FEATURES (2)3.SYSTEM APPLICATIONS (2)4.BLOCK DIAGRAM (3)5.PIN ASSIGNMENTS (4)6.PIN DESCRIPTIONS (5)7.SYSTEM OVERVIEW (10)8.ELECTRICAL REQUIREMENTS (11)8.1.DC C HARACTERISTICS (11)8.1.1.Absolute Maximum Rating (11)8.1.2.Recommended Operation Conditions (11)8.1.3.Power Consumption (11)8.1.4.Reference Crystal (12)8.1.5.ADSL Interface Clock Input (12)8.2.AC C HARACTERISTICS (12)8.2.1.FLASH – Parallel (12)8.2.2.FLASH – Serial (13)8.2.3.SDRAM (13)8.2.3.1SDRAM Input Timing (13)8.2.3.2SDRAM Output Timing (14)8.2.3.3SDRAM Access Control Timing (15)8.2.4.AFE (16)8.2.4.1Master clock (16)8.2.4.2Transmission Interface (16)8.2.4.3Reception Interface (16)8.2.5.JTAG (16)8.2.6.Reset (18)8.2.7.V REF Timing (18)8.2.8.Power-on sequence (19)9.MECHANICAL DIMENSIONS (20)10.ORDERING INFORMATION (22)List of TablesT ABLE 1P IN D ESCRIPTIONS OF RTL8671B/RTL8671BH(128-PIN LQFP) (5)T ABLE 2A BSOLUTE M AXIMUM R ATING (11)T ABLE 3R ECOMMENDED O PERATION C ONDITIONS (11)T ABLE 4P OWER C ONSUMPTION (11)T ABLE 5R EFERENCE C RYSTAL (12)T ABLE 6ADSL I NTERFACE C LOCK I NPUT (12)T ABLE 7P ARALLEL FLASH T IMING (12)T ABLE 8SDRAM I NPUT T IMING (13)T ABLE 9SDRAM O UTPUT T IMING (14)T ABLE 10SDRAM A CCESS C ONTROL T IMING (15)T ABLE 11AFE M ASTER C LOCK (16)T ABLE 12AFE TX I NTERFACE (16)T ABLE 13AFE RX I NTERFACE (16)T ABLE 14JTAG I NTERFACE T IMING (16)T ABLE 15R ESET T IMING (18)T ABLE 16V REF T IMING (18)T ABLE 17D IMENSION OF LQFP-128 (21)List of FiguresF IGURE 1A PPLICATION D IAGRAM I (2)F IGURE 2A PPLICATION D IAGRAM II (2)F IGURE 3B LOCK D IAGRAM (3)F IGURE 4P IN-OUT D IAGRAM (4)F IGURE 5F LASH A CCESS T IMING (13)F IGURE 6SDRAM I NPUT T IMING (14)F IGURE 7SDRAM O UTPUT T IMING (14)F IGURE 8SDRAM A CCESS C ONTROL T IMING (15)F IGURE 9B OUNDARY-S CAN G ENERAL T IMING (17)F IGURE 10B OUNDARY-S CAN R ESET T IMING (17)F IGURE 11R ESET T IMING (18)F IGURE 12D RAWING OF LQFP-128 (20)1. General DescriptionThe Realtek RTL8671B/ RTL8671BH are integrated SoC featuring a RISC, an ADSL2+ Discrete Multi-tone (DMT) data-pump, a hardware-based ATM Segmentation and Reassembly (SAR), two 10/100Mbps IEEE 802.3 compliant MACs with an embedded Ethernet transceiver, and a USB PHY port. Mated with the Realtek RTL8271B (ADSL2+ Analog Front End), RTL8671B/ RTL8671BH provide a low cost integrated solution for ADSL2+ CPE modems, routers, or gateways.RTL8671B/ RTL8671BH encompass high-performance DSP technologies, optimized mix-signal designs, and an efficient architecture to provide a seamless WAN to LAN router controller. The embedded RISC network processor supports the MIPS I instruction set along with DSP extensions and achieves a 340MHz clock rate in a six-stage pipeline to support layer 2, 3, and other upper layer applications.The DMT engine supports the upstream data rate from 32kbp to above 3Mbps and the downstream data rate from 32kbps to above 24Mbps throughput, and complies with:n ANSI T1.413 Issue 2n ITU-T G.992.1 (G..dmt) Annexes A and Bn G.992.2 (G..lite) Annexes A and Bn G.992.3 ADSL2 (G.dmt.bis) Annexes A, B, I, J, L, and Mn G.992.4 ADSL2 (G.lite.bis)n G.992.5 ADSL2+The Ethernet interface offers high-speed transmission over CAT-5 UTP cable or CAT-3 UTP (10Mbps only) cable. Ethernet functions such as Crossover Detection & Auto-Correction and polarity correction are implemented to provide robust transmission and reception capability at high speeds.2. Featuresn Two-chip ADSL2+ CPE solution:RTL8671B/ RTL8671BH (ADSL2+/Network Processor SoC) + RTL8271B (ADSL2+Analog Front End).n Field proven DMT data-pump complies with ANSI T1.413 Issue 2, ITU-T G992.1,G.992.2 , G.992.3, G.992.4, G.992.5supporting Annexes A, B, I, J, L, and M.Supports S=1/3 coding.n High performance embedded RISC with MMU, TLB and DSP instruction extension. n Embedded hardware-based ATM SAR: up to 8 distinct VCs—ATM AAL5 adaptation, F4/F5 OAM cell, HEC, CRC, IP/TCP/UDP checksum offloading, and error packetfiltering— and QoS supported for CBR,UBR, rt-VBR, and nrt-VBR.n Embedded 10/100 Base-TX Ethernet MAC and transceiver supporting CrossoverDetection & Auto-Correction and polaritycorrection, IP/TCP/UDP checksum offload supported as well. n One on-chip USB PHY port supporting the host/device moden Support serial SPI interface for device controln Network device management via HTTP, SNMP, and CLI (UART).n IP layer processing, DHCP, NAT, and typical higher layer applications supported n16-bit-wide, 166MHz SDRAM support up to 256Mbn8/16-bit-wide parallel/SPI Flash support up to 128Mbn 3.3V signaling, 1.2V core voltage; a embedded linear regulator controller toreduce an external LDOn Two 32-bit timers and a watchdog timern Embedded “Dying-Gasp” detection circuit n EJTAG interfacen Package of 128-pin LQFP available3. System ApplicationsFigure 2 Application Diagram II4. Block Diagram5. Pin AssignmentsFigure 4 Pin-out DiagramV M MD13V C T D D 3V D D 1T X O T X O V S R X I R X I V D D 1V D D 1C K I V S V D D 1V D D 3R S R V D (N C R S R V D (N C V S V S U 1D U 1D U 1I U 1V B U V D D 3D G N G P A 5/S V C S I V D A F T X D A F T X D A F T X D A F T X D A F R X D A F R X D D 14M D 15W E #O V D D R A S #C A S #M C S 3#D G N D M C S 2#I V D D M A 0M A 1M A 2M A 3O V D D M A 4M A 5M A 6M A 7I V D D M A 8M A 9M A 10M A 11M A 12O V D D M A 13M A 14M A 15M A 16M A 17M A 18MD12IVDD MD11MD10OVDD MD9MD8MD7MD6SDCLK MD5IVDD MD4DGND MD3OVDD ENUSBOTGMD2MD1MD0CK25MOUTCKSEL VDD12XI XO VSS NC VDD33IBREF VSS VREFGPB7/JTDO GPB6/JTMS GPB5/JTDI GPB4/JTRST#GPB3/JTCKGPB2/URTS#/SVDO GPB1/UTXD/SVDI GPB0/URXD/SVCS#IVDDGPA7/UCTS#/SVCK6. Pin DescriptionsTable 1 Pin Descriptions of RTL8671B/ RTL8671BH (128-pin LQFP) Symbol 128 Pin# Type Description100/10 Physical LayerRXIP RXIN 78I Ethernet physical layer differentialRX pinsTXOP TXON 45O Ethernet physical layer differentialTX pinsIBREF 126 I Pull-down externally with 2.5k Ohmfor PHY referenceEthernet PHY LEDNICLED[3:0] 55, 57, 59, 61 O LED driving signals for theembedded Ethernet PHY;Pins MA[22:21] sharing withNICLED[1:0]Clock & ResetXI 121 I 25MHz crystal clock input.XO 122 O 25MHz crystal clock output. CKSEL 119 I Reference clock selection; tied to1.2 to select XO (25MHz), VSS toselect CKIN (35.328MHz) PWRRST# 41 I System reset.SPI Control InterfaceSVCS# 45 O SPI chip select pin (shared withGPB0 and URXD)SVDI 46 I SPI data in (shared with GPB1 andUTXD)SVDO 47 O SPI data out (shared with GPB2and URTS#)SVCK 48 O SPI reference clock (shared withGPA7 and UCTS#)USB InterfaceU1DP, U1DM 20, 19 I/O Differential data I/O of USB PHY 1To RTL8671BH: either host/devicemode supported; configured byU1IDTo RTL8671B: device modesupported onlyU1ID (NC) 21 I To RTL8671BH: Pull-low/high toselect PHY 1 as host/deviceTo RTL8671B: NCU1VBUS 22 I USB VBUS detect pin; used forPHY 1 configured in device mode USBLED1 54 O USB LED driver output ENUSBOTG 114 O Enable USB OTG blockAFE InterfaceAFPWDN 40 O Power down control to AFE AFRXD[3:0] 34, 33, 32, 31 I Data input from AFEAFTXD[3:0] 30, 29, 28, 27 O Data output to AFEPins AFTXD[3:2] strap into registervalues as OCCLK_SEL[1:0], whichdefines the CPU speed. ForRTL8671B/ RTL8671BH, theAFTXD[3:2] should be strictlypulled as ‘10’.[1]AFCLWD 35 I Word clock input from AFECKIN 11 I Master clock from AFEAFCTRL 37 O Control data output to AFEVREF 128 I Dying Gasp voltage detect inputMemory BusMD[15:0] 95, 96, 97, 98, 100, 101, 103, 104,105, 106, 108, 110, 112, 115, 116, 117 I/O Data for SDRAM, parallel Flash, and ROMMA[22:0] 59, 61, 62, 64, 65, 66, 67, 68, 69, 70,72, 73, 74, 75, 76, 78, 79, 80, 81, 83,84, 85, 86 O Address for SDRAM and Flash.Pins MA[10:8] strap into registervalues as OCCLK_SEL[4:2], whichdefines the CPU speed. ForRTL8671B/ RTL8671BH, theMA[10:8] should be strictly pulledas ‘001’.[1]SDCLK 107 O SDRAM clockMCS2# 88 O Bank 0 chip select SDRAM chipselect.MCS3# 90 O Bank 1 chip select SDRAM chipselectOE#/RAS# 92 O Raw address strobe for SDRAMinterface; output enable for FLASHinterfaceCAS# 91 O Column address strobeWE# 94 O Write enable for SDRAM/ FLASHinterfaceDQM[3:0] 66, 65, 68, 67 O DQM[3:0] for SDRAM; shared withAA17, AA18, AA15, AA16MCS0# 63 O ROM Bank 0 chip select for FLASHmemorySFCS# 63 O Chip select of SPI FLASH interfaceif enabled (AFPWDN pull-up onpower-on reset)SFDI 35 I Serial data in of SPI FLASHinterface if enabled; shared withAFCLWDSFDO 62 O Serial data out of SPI FLASHinterface if enabled; shared withMA20SFCK 64 O Reference clock of SPI FLASHinterface if enabled; shared withMA19GPIOGPIOA[7:5] 43, 42, 25 I/O GPIO port AGPIOB[7:0] 52, 51, 50, 49, 48, 47, 46, 45 I/O GPIO port BUARTUCTS# 43 I Clear to send; shared with GPA7and SV_CKURXD 45 I RX data; shared with GPB0 andSV_CS#UTXD 46 O TX data; shared with GPB1 andSV_DIURTS# 47 O Request to send; shared withGPB2 and SV_DOJTAG (shared with GPIOB7-3)JTCK 48 I JTAG test clock; shared with GPB3 JTMS 51 I JTAG test mode select; shared withGPB6JTDO 52 O JTAG test data output; shared withGPB7JTDI 50 I JTAG test data in; shared withGPB5JTRST# 49 I JTAG test reset; shared with GPB4POWER & GNDVDD12 3, 9, 10, 13, 120 P Analog 1.2V supplyVDD33 2, 14, 23, 125 P Analog 3.3V supplyVSS 6, 12, 17, 18, 123, 127 P Analog groundDGND 24, 58, 89, 111 P Digital groundOVDD 39, 60, 71, 82, 93, 102, 113 P 3.3V digital I/O supplyIVDD 26, 36, 44, 56, 77, 87, 99, 109 P 1.2V digital kernel supplyMiscCK25MOUT 118 O Clock output of 25MHz for possibleperipheral useVCTRL 1 O Output of the embedded regulatorcontroller to generate 1.2V VDD forthe kernel supply of the chip.Connecting to an external PNP-BJTbase if used (BJT collector outputto IVDD); leaving no connection ifnot used.DTEST 124 - No used; leaving no connection TESTMODE 38 I Test only; leaving no connectionPulled-down internally for normaloperationRSRVD(NC) 15, 16, 53 - No used; leaving no connection Notes1. MA[10:9] and AFTXD[3:2] strap into the register at the power-on reset to configure the CPU speed. The value ‘00110’ configures theCPU running at 340MHz. This is a strict setting for RTL8671B/ RTL8671BH. That is, AFTXD3 and MA8 should be pulled up via a 4.7k Ohm resistor, and AFTXD2 and MA[10:9] should be pulled low via a 4.7k Ohm resistor.7. System Overview TBD8. Electrical Requirements8.1. DC Characteristics8.1.1. Absolute Maximum RatingTable 2 Absolute Maximum RatingParameters Symbol Min Max Unit I/O supply voltage V DDIO TBD TBD V Core supply voltage V DDC TBD TBD V Storage temperature T STG TBDESD protection VESD TBD V8.1.2.Recommended Operation ConditionsTable 3 Recommended Operation ConditionsParameters Symbol Condition Min Typ Max Unit OperatingtemperatureT A Ambient TBD TBD TBD °CDigital supply for I/OringV DDR TBD 3.3 TBD VCore power supplyvoltageV DDC TBD 1.2 TBD V Input high voltage V IH TBD V Input low voltage V IL TBD V Input current V IN TBD TBD µA8.1.3. Power ConsumptionTable 4 Power ConsumptionParametes Symbol Condition Estimated Power UnitDigital supply for I/O ring (3.3V)*V DDR ADSL (ADSL2+interleaved mode),and Ethernet areactiveTBD mACore power supply voltage (1.2V) V DDC ADSL (ADSL2+interleaved mode),and Ethernet activeTBD mAPhy power supply voltage (1.2V) V DDPhy ADSL (ADSL2+interleaved mode),and Ethernet areactiveTBD mA8.1.4. Reference CrystalTable 5 Reference CrystalParameters Symbol Min Typ Max Unit Center frequency f cf25 MHz Shunt capacitance C o pF Load capacitance C L pF Crystal equivalent serial resistor C ESRΩAging ppm/yr Frequency tolerance +/-50 ppm8.1.5. ADSL Interface Clock InputTable 6 ADSL Interface Clock InputParameters Symbol Min Typ Max Unit Clock frequency f clock35.328 MHz Pulse duration high t w(HI)14.15 ns8.2. AC Characteristics8.2.1. FLASH – ParallelTable 7 Parallel FLASH TimingSymbol Parameter Min. Typ. Max. Units NotesT CS The timing interval betweenF_CS0#(or F_CS1#) and WE# Controlled by Reg.0xB9000004(MTCR0)nsT WP The timing interval for WE# topulled low (RAS# for readoperation). Controlled by Reg. 0xB9000004(MTCR0)nsFigure 5 Flash Access Timing8.2.2. FLASH – SerialTBD8.2.3. SDRAM8.2.3.1 SDRAM Input TimingTable 8 SDRAM Input TimingSymbol Parameter Min. Typ. Max. Units Notes T SETUP Input setup prior to rising edgeof clock. Inputs included in thistiming are D[31: 0] (during aread operation)TBD nsT HOLD Input hold-time after the risingedge of clock. Inputs include inthis timing are D[31: 0] (duringa read operation)TBD TBD nsFigure 6 SDRAM Input Timing8.2.3.2 SDRAM Output TimingTable 9 SDRAM Output TimingFigure 7 SDRAM Output Timing8.2.3.3SDRAM Access Control TimingTable 10 SDRAM Access Control TimingSymbolParameter Min.Typ.Max.Units Notes T REFRESH Auto-refresh timing µs T RCDThe time interval between RAS# active and CAS# activeTBD nsT RP The time interval between pre-charge and the next activeTBD nsT RAS The time interval between active and pre-chargeTBD nsT RC The time interval between active and the next activeTBD nsT RFC The time interval between auto-refresh and activeTBD nsT CAS_LATENCY The data output delay after The CAS# activeTBD nsFigure 8 SDRAM Access Control Timing8.2.4. AFE8.2.4.1 Master clockTable 11 AFE Master ClockSymbol Parameter Min. Typ. Max. Units NotesF Clock frequency 35.328 MHzT h Clock duty cycle 50 %8.2.4.2 Transmission InterfaceTable 12 AFE TX InterfaceSymbol Parameter Min. Typ. Max. Units Notes Tva r Setup time before falling edge of clock. 12 18 ns AFElatch dataat fallingedge ofclock8.2.4.3 Reception InterfaceTable 13 AFE RX InterfaceSymbol Parameter Min. Typ. Max. Units Notes3 nsT s Data setup-time prior to falling edge ofclockT h Data hold-time after falling edge of clock 3 ns8.2.5. JTAGTable 14 JTAG Interface TimingSymbol Parameter Min. Typ. Max. Units Notes T BSCL JTAG clock low time nsT BSCH JTAG clock high time nsT BSIS TDI, TMS setup time to rising edge ofnsTCKT BSIH TDI, TMS hold time from rising edge ofns TCKT BSOH TDO hold time after falling edge of TCK ns T BSOD TDO output from falling edge of TCK ns T BSR JTAG reset period nsns T BSRS TMS setup time to rising edge of JTAGresetns T BSRH TMS hold time from rising edge of JTAGresetTCKTMS, TDITDOFigure 9 Boundary-Scan General TimingFigure 10 Boundary-Scan Reset Timing8.2.6. ResetTable 15 Reset TimingTPOWERON_RESET TPUSH_RESET8.2.7. V REF TimingTable 16 V REF TimingSymbol Parameter Min. Typ. Max. Units Notes T delay Delay time from dying gaspTBD us 1 detect to ADSL dying gaspindication bit clearms T RP Required residual power sustaintimeNote1: 250*8*[(B+1)*M+R]*Tp*SEQ*D/(Lp*M)8.2.8. Power-on sequence TBD9. Mechanical DimensionsFigure 12 Drawing of LQFP-128Table 17 Dimension of LQFP-12810. Ordering Information TBD。

手机各部件的运作原理周兴才-文档资料

• FLASH按工作电压可分为:5V 3.3V 1.8V 0.9V等几种。 按其数据总线宽度可以分为8位数据总线宽度,16位数 据总线宽度两种;按其总线和数据总线分离,低16位地 址总线和数据总线合并,地址总线和数据总线合并三种; 按其扇区分布可分为TOP BOTTOM两种;其封装形 式具体有TSOP40 TSOP48 FBGA48 UBGA56 FBGA72 BGA80 BGA69 等等。根据其封装形 式字库可分为二大类,第一是比教长见。第二类是BGA封 装形式的,这种字库用在近期生产的各种手机上,如摩托 罗拉V998,诺基亚3210以及爱立信T28等手机。按其脚 管的多少,手机的字库又可以分为以下两大类:一类为40 脚的字库(如型号28F004,28F008);另一类为48脚 的字库(如型号28F800,28F160 F160等)。

手机的组成部分

• 1 CPU(中央处理器):这是手机单片机系统核心 • 2 储存器:包括两个部分,一个ROM,它是来存储 程序;二是RAM,它是来储存数据。ROM和RAM 两钟储存器是有所不同的。 • 3 输入/输出(I/O)接口:这一接口电路分为两种: 一是并行输入/输出接口;二是串行输入/输出接口。 这两种接口电路结构不同,对信息的传输方式也不同 • 4 定时器/计数器:单片机的许多应用中,往往需要进 行精确的定时并产生方波信号,这要由定时器/计数 器电路完成 • 时钟系统:手机中常见是26MHz和好32.768kHz.

手机部件的各个工作原理

• CPU是根据指令来工作的。一连串的指令集组成了一个完整的 (CPU)工作程序,程序的运行与计算机往往还需要相关的数 据参数,比如:射频控制参数,包括频率和成器参数`接受参数 `发射参数`功率控制参数等;逻辑控制,包括显示参数`语言参 数`串号`电池门限参数`放大器增益参数;而软件就是控制程序 和工作数据参数的总和。 • CPU是手机的核心部分,各部分功能如下

PHILIPS(LCD) 升压板解读

AI-0067(ADAPTOR)电路原理讲解1 芯片介绍PHILIPS产的Lenovo AK5S50/55系列机种电源部分使用飞兆半导体公司(Fairchild Semiconductor)推出的新型FAN7601器件,这是具有可设定开关频率的电流模式PWM控制器,FAN7601的内在功能特性,如可外部调整的软启动(20mS)和高压启动开关等,进一步降低了功耗。

此外,过压保护(19V 输入/2.5V反馈)、过热关断,以及欠压锁定UVLO(12V / 8V)功能都提高了系统的可靠性。

除了提供长期可靠性外, FAN7601的电路板布局简洁,确保其应用灵活方便。

图1图2我们可以从图2看出个功能引脚的定义。

PHILIPS系列机种电源部份和AOC不同的地方就是其使用了不同的PWM控制芯片,FAN7601是一款更符合节能标准的新型PWM控制器,在待机的状态下,功耗可以做到小于1W。

2 电路流程(如无说明,以输入电压~220V分析)启动220V的工频交流电经过三芯插头送到ADAPTOR电路板上,经过F001 一个2安培的保险后,我们可以看见有一个NTC1的器件。

这是一个负温度系数的热敏电阻。

它的作用是限制浪涌电流,起到保护的一个作用。

因为隔离式开关电源在加电会产生极高的浪涌电流,浪涌电流主要是由滤泼电容充电引起的,在开关管开始导通的瞬间,电容对交流呈现出很低的阻抗,一般情况下,只是电容的ESR 值,如果不采取任何保护,浪涌电流可接近几百安培。

NF002和后面的NF001都是感量较大的磁芯线圈,它们一起构成EMI滤泼器,防止产生电磁干扰,同时也限制外部的电磁干扰进入到电源里面。

R001 R002和R003一起构成EMI滤泼器的泄放会路。

CX001和CY001 CY002在本电路里面的作用是一起构成X校正和Y校正,其实就是我们了解的共膜和差膜抑制回路,主要也是消除来自电网的干扰。

在这里有一个器件V AR1,在这里是一个过压保护的器件,也叫压敏电阻。

T61电路图

: DDR2-B

55. GBE MAGNETICS

10. CRESTLINE(4/7)

: PEG/DMI

56. RJ11/RJ45 CONNECTOR

11. CRESTLINE(5/7)

: GRAPHICS

57. MINI PCI SLOT

12. CRESTLINE(6/7)

: VCC

58. EEPROM/FLASH/SHARED

VER.0.07

06/19/2006

APPLIED DAV3_FVT 038,039

VER.0.08

06/20/2006

APPLIED DAV3_FVT 040,039,020,003

VER.0.09

06/21/2006

APPLIED DAV3_FVT 039,038,036,006,041

7

VER.0.10

VER.0.01

06/05/2006

APPLIED MLB_SDV 001

VER.0.02

06/07/2006

APPLIED DAV3_FVT 005,006,009

VER.0.03

06/05/2006

APPLIED DAV3_SDV 084,085

VER.0.03

06/05/2006

APPLIED DAV3_FVT 013

CR-1 : @DESIGN.D3SDV(SCH_1):PAGE

A

B

C

D

E

F

G

H

J

K

L

M

N

P

Q

DATE

EC NO.

PART NO.

9

MLB-1 NV EXT SVT LOGIC SCHEMATICS

高保真品牌无线耳机电子线路原理图(发射与接收整套线路图全在其中)

EEWP IO16_(SYNC_LED) IO17_(SPDIF_OUT) IO33 IO26 IO27 PWM_R-CH_P PWM_R-CH_N VCC3IO GND3IO GNDK VCC_1_8V

VSS VSS ANT2 ANT1 VDDPA XC1 AVSS VDD

51 50 49 48 47 46 45 44 43 42 41

PGND

PDF 文件使用 "pdfFactory Pro" 试用版本创建

5 4

3

2

1

5

4

3

2

1

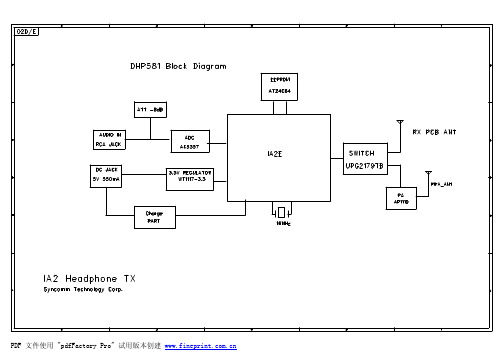

BLOCK DIAGRAM OF DHP782

D

KEY S1~S3 ANT 2.4G PIFA

D

EEPROM U1:AT24C64

C

U2 IA2E 2.4G Wireless Audio Module lCRYATAL Y1:16MHz

A

J4 + 1

BATT 1.2V/700mAh*2

TP12 TP C6 NC Q2 2N3904 PGND SW1 POWER ON/OFF

R17 1K

A

--

2

Charge port

TP15

"H" : Power ON "L" : Power OFF

PGND

POWER_CONTROL_OUT

LED2 RED

高保真品牌无线耳机电子线路原理图发射与接收整套线路图全在其中

PDF 文件使用 "pdfFactory Pro" 试用版本创建

PDF 文件使用 "pdfFactory Pro" 试用版本创建

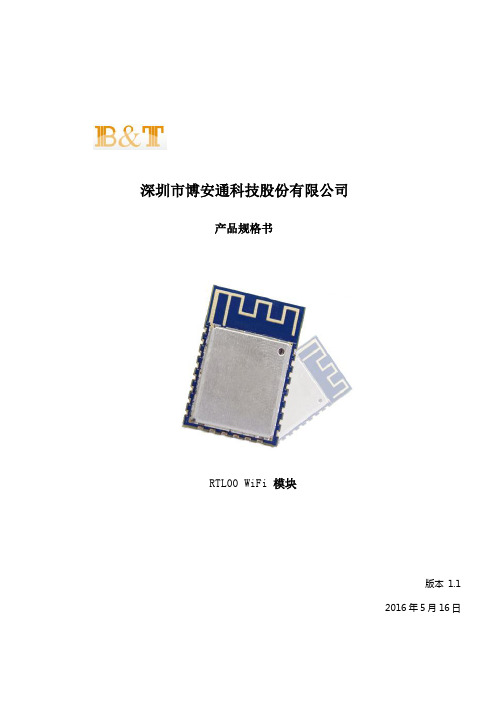

IOT WIFI RTL8710规格书

深圳市博安通科技股份有限公司产品规格书RTL00 WiFi 模块版本1.12016年5月16日免责申明和版权公告本文中的信息,包括供参考的URL 地址,如有变更,恕不另行通知。

文档“按现状”提供,不负任何担保责任,包括对适销性、适用于特定用途或非侵权性的任何担保,和任何提案、规格或样品在他处提到的任何担保。

本文档不负任何责任,包括使用本文档内信息产生的侵犯任何专利权行为的责任。

本文档在此未以禁止反言或其他方式授予任何知识产权使用许可,不管是明示许可还是暗示许可。

Wi-Fi 联盟成员标志归Wi-Fi 联盟所有。

文中提到的所有商标名称、商标和注册商标均属其各自所有者的财产,特此声明。

1目录1.产品概述 (3)1.1特点 (4)1.2主要参数 (5)2.接口定义 (6)3.外型与尺寸 (8)4.功能描述 (9)4.1.MCU (9)4.2.存储描述 (9)4.2.1.内置SRAM与ROM (9)4.2.2.SPI Flash (9)4.3.晶振 (9)4.4.最大额定值 (10)4.5.建议工作环境 (10)4.6.数字端口特征 (10)5.RF参数 (11)6.功耗 (11)7.倾斜升温 (13)8.模块安装注意事项 (13)9.参考电路图 (15)21.产品概述瑞昱智能互联平台瑞昱8710拥有高性能无线SOC,给移动平台设计师带来福⾳,它以最低成本提供最大实用性,为WiFi 功能嵌入其他系统提供无限可能。

图1 瑞昱8710结构图瑞昱8710是一个完整且自成体系的WiFi网络解决方案,能够独立运行,也可以作为从机搭载于其他主机MCU 运行。

瑞昱8710在搭载应用并作为设备中唯一的应用处理器时,能够直接从外接闪存中启动。

内置的高速缓冲存储器有利于提高系统性能,并减少内存需求。

另外⼀种情况是,瑞昱8710负责无线上网接入承担WiFi 适配器的任务时,可以将其添加到任何基于微控制器的设计中,连接简单易行,只需通过SPI /SDIO 接口或I2C/UART 口即可。

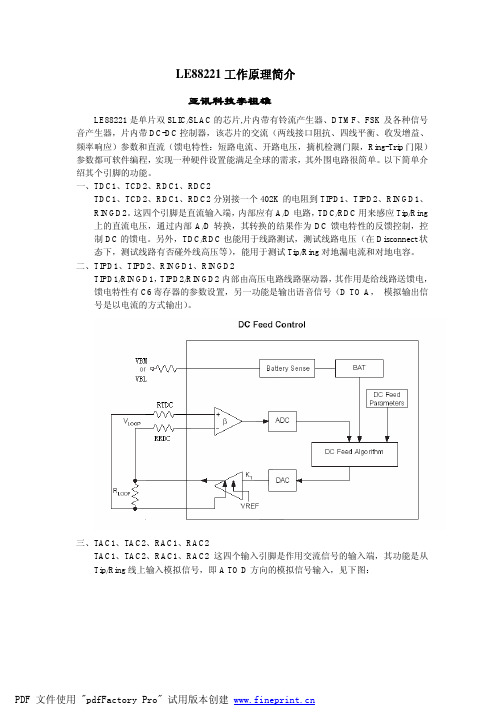

LE88221工作原理简介亚讯科技李祖雄

LE88221工作原理简介亚讯科技李祖雄LE88221是单片双SLIC/SLAC的芯片,片内带有铃流产生器、DTMF、FSK及各种信号音产生器,片内带DC-DC控制器,该芯片的交流(两线接口阻抗、四线平衡、收发增益、频率响应)参数和直流(馈电特性:短路电流、开路电压,摘机检测门限,Ring-Trip门限)参数都可软件编程,实现一种硬件设置能满足全球的需求,其外围电路很简单。

以下简单介绍其个引脚的功能。

一、TDC1、TCD2、RDC1、RDC2TDC1、TCD2、RDC1、RDC2分别接一个402K的电阻到TIPD1、TIPD2、RINGD1、RINGD2。

这四个引脚是直流输入端,内部应有A/D电路,TDC/RDC用来感应Tip/Ring 上的直流电压,通过内部A/D转换,其转换的结果作为DC馈电特性的反馈控制,控制DC的馈电。

另外,TDC/RDC也能用于线路测试,测试线路电压(在Disconnect状态下,测试线路有否碰外线高压等),能用于测试Tip/Ring对地漏电流和对地电容。

二、TIPD1、TIPD2、RINGD1、RINGD2TIPD1/RINGD1,TIPD2/RINGD2内部由高压电路线路驱动器,其作用是给线路送馈电,馈电特性有C6寄存器的参数设置,另一功能是输出语音信号(D TO A,模拟输出信号是以电流的方式输出)。

三、TAC1、TAC2、RAC1、RAC2TAC1、TAC2、RAC1、RAC2这四个输入引脚是作用交流信号的输入端,其功能是从Tip/Ring线上输入模拟信号,即A TO D方向的模拟信号输入,见下图:TAC1/RAC1、TAC2/RAC2内部是差分输入电压放大器,CTAC、CRAC是隔直流电容,RTAC、RTAC是放大其的输入电阻,其大小会影响到放大器的放大量,应用电路中推荐值是RTAC=RRAC=3.01K,CTAC=CRAC=68NF。

四、RTV1、RSN1、RTV2、RSN2RSN、RTV引脚内部是一个电压/电流放大器,也就是四线到四线的放大器(G44放大器),电阻RT是V TO I的反馈电阻/转换电阻,其大小会影响V TO I的放大量,应用电路的推荐值是RT=47.5K。

TI、ARM芯片工作原理与改天线开关、飞利普射频供电电路

TI、ARM芯片工作原理与改天线开关、飞利普射频供电电路关于电源:TI芯片3012,3011的问题如A8的电源,这个电源你在没有上CPU和字库的时候,如果电源接B+正常的电源没有坏情况下,按开机键会有很小的电流,其各个输出电压都有!如2V、2.8。

A8图纸在很明确!所以大家注意一下有的机器只要是这个电源的,你要仔细看,除了电源坏和B+正常的情况一定会有输出的没有电流的原因是电流太小,再一个是CPU741529A这个CPU要想正常工作!必须电源各个电压都得送到,时实时钟电路正常!让32.768正常振荡这时CPU会输出一个电压信号(可以照A8图纸看看)去控制一个5脚稳压管的3脚(因机器不同,控制的器件也不一样)这个管一脚供电,2脚接地,3脚接控制,4脚空可接滤波电容5脚输出,这样5脚会输出3V电压,这个电源供射频同进也供13M,如果13M工作了,经放大送到CPU,这样CPU得到了13 M信号!CPU再供给电源一个13M,复位也有了,软件也正常自检开机!(3012电源741529CPU在很多机器中被使用,如A8、猫958、波导S2000等等)关于电源:TI3014,这个电源如果电源接B+正常的电源没有坏的情况下,按住开机键,95%电源都不会有输出除了各别电路可以的(如摩机E365有时候可以输出各个电压),所以没有输出就不要总修电源了,看看32.768,(这个电源有一个脚强加2.0V电压也可以输出,我忘记哪个脚,好像维持,)电源开机键正常电源是3V也有2V不一样但是都可以说是正常的!要保证电源正常工作,必须保证32.768正常!CPU为741979这个型号的(如东信730,750,VK320, 520,等等很多)只要是3014、741979组成的电路就得让32.768工作,(电源:管脚D1是实时时钟的供电到CPUD14脚,这样时实时钟才能工作!在没有开机的时候D1输出2.0V,这样可以保持32.768正常工作)电源管脚D1会有2V多点的电压供到CPUCPU的D13/D14脚。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

R97

R96

R4

R5

3

5 6 SW2 4MS1R2021M7WQES-M B2 800Z3AR3D5M 3 2 1 C3 NC/0.1uF /K/25V/Y5V/C0402 R11 0 /J/R1206 2 1 3

+ EC2

R6

4

8 7 6 5

0.1uF /M/25V/Y5V/C0402

MC34063AD/SO8

D

Project Name

Rev

ADSL2+ Modem with 1-Port Ethernet

Title BLOCK DIAGRAM Tool: Date:

1 2 3 4

4.0

OrCAD 9.2

Author:

5

Liang Shen Sheet

Leader: 1 of 8

Monday, October 11, 2010

64 63 62 61 60 59 58 57 56 55 54 53 52 51 50 49 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

AFCTRLDATA R28

MEMORY OFF-PAGE

For SPI Flash

AFCLWD AA20 AA19 SDI SDO SCK

B

VCTL VDD33 VDD12 TXOP TXON VSS RXIP RXIN VDD12 VDD12 CKIN VSS VDD12 VDD33 RSRVD(NC) RSRVD(NC) DGND DGND U1_DM U1_DP U1_ID U1_VBUS VDD33 DGND GPA5 / SV_CS# IVDD AFTXD0 AFTXD1 AFTXD2 AFTXD3 AFRXD0 AFRXD1

B

R19 R21 R22 R23 R24 R25 R26 R27

33 /J/R0402 AFE_TX0 33 /J/R0402 AFE_TX1 33 /J/R0402 AFE_TX2 33 /J/R0402 AFE_TX3 33 /J/R0402 AFE_RX0 33 /J/R0402 AFE_RX1 33 /J/R0402 AFE_RX2 33 /J/R0402 AFE_RX3 CTRLIN_AFE 33 /J/R0402

MD13 MD12 IVDD MD11 MD10 OVDD MD9 MD8 MD7 MD6 SDCLK MD5 IVDD MD4 DGND MD3 OVDD ENUSBOTG MD2 MD1 MD0 CK25MOUT NC VDD12 NC NC VSS NC VDD33 IBREF VSS VREF

DGND

DGND DGND 3K /F/R0402

C C

R16

3.3 = 1.25 X (1 + 4.99/3)

1000pF /K/16V/X7R/C0402

0.1uF /M/25V/Y5V/C0402

EC18 1000uF /M/25V/DIP

EC4 1000uF /M/25V/DIP

EC5 1000uF /M/25V/DIP

Power of 3.3V

VDD33

0.1uF /K/10V/X7R/C0402

+

+

+

470uF /M/16V/DIP/LESR

4.99K /F/R0402

8 7 6 5

DRI IPK VCC FB

SWC SWE TC GND

1 2 3 4

220pF /J/50V/NPO/C0402

U2

+

DGND

MC34063AD/SO8 DGND C7

N17052756

R108 0 /J/R0603 NC

DRI IPK VCC FB

SWC SWE TC GND

1 2 3 4

220pF /J/50V/NPO/C0402

U1

DGND

+ DGND DGND EC3

1000uF /M/25V/DIP

C4

R9 3K /F/R0402

-

1

DGND

C5

DGND DGND

VDD33 R33 2.49K /F/R0402 VREF

97 98 99 100 101 102 103 104 105 106 107 108 109 110 111 112 113 114 115 116 117 118 119 120 121 122 123 124 125 126 127 128

MD14 MD15 WE# OVDD RAS CAS MCS3# DGND MCS2# IVDD MA0 MA1 MA2 MA3 OVDD MA4 MA5 MA6 MA7 IVDD MA8 MA9 MA10 MA11 MA12 OVDD MA13 MA14 MA15 MA16 MA17 MA18

DGND

B

CONTROL FROM SOC

C

C

REVISION HISTORY (Detail refer to Change note) REVISION 3.1 4.0

D

RELEASE DATE 2010.09.13 2010.10.11

SUMMARY Initial release Refer to change note

1

2

3

4

5

Realtek ADSL2+ Modem Evaluation Circuit

A

POWER DISTRIBUTIቤተ መጻሕፍቲ ባይዱN (1P COMBO for RTL8671B-VE)

VIN SW MODE 34063 5V FOR AFE

A

RTL8671B 1 Port Combo SoC AFE SDRAM RTL8671B RTL8271B -VE -VR

1000pF /K/16V/X7R/C0402

470uF /M/16V/DIP/LESR

3

R3 0 /J/R1206

+

A

ML2

MH1

MH2

MH3

MH4

VinDC

R17 NC/0 /J/R1206

VDD5

Mount R17 and R10 to support DC 5V power in

D D

Project Name

DGND R12 1K /F/R0402

DGND

5 = 1.25 X (1 + 3/1)

DGND

DGND

B B

VinDC

R13 510 /J/R0603 1 220 /J/R0603 R105 390K /J/R0402 2 3 Q3 2SB1188/32V/2A/SOT89 L2 1 /J/R0402 1 /J/R0402 1 /J/R0402 1 /J/R0402 1N5819/40V/1A/DIP 1 /J/R0402 R14 2 220uH/2A

Q1 2SB1188/32V/2A/SOT89 NC L1 R8 390K /J/R0402 1N5819/40V/1A/DIP 2 220uH/2A

Power of 5V

VDD5 0.1uF /M/25V/Y5V/C0402

R107 NC/0 /J/R0603 0 /J/R0603

4

R109

+

NC/4.7uF /M/50V/DIP

Rev

ADSL2+ Modem with 1-Port Ethernet

Title POWER & RESET Tool: Date:

1 2 3 4

4.0

OrCAD 9.2

Author:

Liang Shen Sheet

5

Leader: 2 of 8

Monday, October 11, 2010

1

6 6 6 6 4

A

XC61FC/SOT23 DGND

RESET#

3

VCC

OUT GND

1 2

SDRAM_CLK C16 NC/10pF /J/50V/NPO/C0402

R20

33 /J/R0402

DGND

DD13 DD12 VDD10 DD11 DD10 VDD33 DD9 DD8 DD7 DD6 SDCLK DD5 VDD10 DD4 DGND DD3 VDD33 ENUSBOTG DD2 DD1 DD0 VDD10 DGND

SDI SDO SCK

USB OFF-SHEET

ENUSBOTG USB_VBUS USB_DP1 USB_DM1 USB_ID ENUSBOTG USB_VBUS USB_DP1 USB_DM1 USB_ID 4 8 8 8 4

POWER&RESET OFF-PAGE

RESET# RST#_Factory RESET# RST#_Factory 4,5,6 4

RTL8671B-VE

MA19 / SF_CK / SV_CK MCS0# MA20 NICLED0 OVDD NICLED1 DGND NICLED2 IVDD NICLED3 USBLED1 RSRVD(NC) GPB7 / JTAG_TDO GPB6 / JTAG_TMS GPB5 / JTAG_TDI GPB4 / JTAG_RST# GPB3 / JTAG_CLK GPB2 / URTS# / SV_DO GPB1 / UTXD / SV_DI GPB0 / URXD / SV_CS# IVDD GPA7 / UCTS# / SV_CK GPA6 PWRRST# AFPDOWN OVDD TESTMODE AFCTRL IVDD AFCLWD / SF_DI AFRXD3 AFRXD2