某6万多Pin通讯板设计案例

sop小外形封装的实用例子

sop小外形封装的实用例子SOP(Small Outline Package)是一种小外形封装的集成电路封装形式,广泛应用于各类电子产品中。

它具有体积小、重量轻、散热性好等优点,适用于对尺寸要求较高的应用场景。

下面将列举10个以SOP小外形封装的实用例子。

1. 闪存芯片:SOP封装的闪存芯片在移动设备、数码相机、存储卡等产品中得到广泛应用。

闪存芯片具有高速读写、大容量存储等特点,适合于需要快速存储和读取大量数据的场合。

2. 无线通信模块:SOP封装的无线通信模块常用于智能手机、平板电脑、物联网设备等产品中。

无线通信模块可以实现蓝牙、Wi-Fi、GPS等功能,使设备能够与其他设备进行无线通信和数据传输。

3. 触摸屏控制器:SOP封装的触摸屏控制器广泛应用于智能手机、平板电脑等产品中。

触摸屏控制器可以实现对触摸屏的控制和操作,使用户能够通过触摸屏进行交互。

4. LED驱动芯片:SOP封装的LED驱动芯片常用于LED显示屏、背光模块等产品中。

LED驱动芯片可以控制LED的亮度、颜色等参数,实现对LED的精确控制。

5. 电源管理芯片:SOP封装的电源管理芯片广泛应用于各类电子产品中。

电源管理芯片可以实现对电源的监控和管理,提供稳定的电压和电流输出,保护电子设备的安全运行。

6. 传感器芯片:SOP封装的传感器芯片常用于智能家居、工业自动化等领域。

传感器芯片可以感知周围环境的温度、湿度、光照等参数,并将其转化为电信号进行处理和分析。

7. 音频解码芯片:SOP封装的音频解码芯片广泛应用于音频播放器、音响设备等产品中。

音频解码芯片可以对音频信号进行解码和处理,实现音频的播放和调节。

8. 马达驱动芯片:SOP封装的马达驱动芯片常用于电动工具、机器人等产品中。

马达驱动芯片可以控制马达的转速和转向,实现对设备的精确控制。

9. 扩展接口芯片:SOP封装的扩展接口芯片广泛应用于各类电子产品中。

扩展接口芯片可以提供额外的接口和功能,实现设备的扩展和升级。

立维腾UTP CAT6方案模板(09版本)

立维腾综合布线系统解决方案书目录第一章前言 (4)第二章立维腾公司简介 (5)第三章布线系统标准及规范 (7)第四章综合布线系统概述 (8)4.1工作区子系统 (8)4.2水平布线子系统 (9)4.3主干布线子系统 (9)4.4管理子系统 (9)4.5设备间子系统 (9)4.6建筑群主干布线子系统 (9)第五章 LCS–完美的综合布线系统解决方案 (10)5.1立维腾综合布线系统综述 (10)5.1.1立维腾综合布线系统符合所有相关的国际、国内标准 (10)5.1.2卓越的产品性能 (10)5.1.3布线系统生产厂商 (10)5.1.4系统的质量保证 (10)5.1.5最全面的解决方案 (10)5.1.6立维腾综合布线系统的产品特点 (10)5.2立维腾六类综合布线系统 (12)5.3立维腾光纤布线系统 (13)5.4立维腾布线系统质量保证体系 (14)第六章XXXXX项目设计方案 (16)6.1用户需求分析及系统设计概述 (16)6.2解决方案设计说明及产品选型 (16)6.2.1工作区子系统 (16)6.2.2水平布线子系统 (19)6.2.3楼层配线间子系统 (20)6.2.4垂直主干子系统 (23)6.2.5主配线间系统 (24)6.2.6建筑群主干系统 (25)第七章系统安装及施工 (26)7.1系统集成商的责任 (26)7.1.1系统集成商负责提供 (26)7.1.2系统集成商需要提供以下安装必须的设备和工具 (26)7.1.3系统集成商提供以下文件 (26)7.2系统安装规范及工艺要求 (26)7.2.1链路与设备必须具有保护措施以防止干扰 (26)7.2.2综合布线电缆与强电电缆的最小间距应遵循的规定 (26)7.2.3其它需要特别注意的事项 (27)7.2.4系统安装的工艺要求 (28)7.3施工组织计划 (28)7.3.1 工程组织 (28)7.3.2工程实施 (28)7.3.3质量管理及措施 (29)7.3.4安全文明施工措施 (29)第八章系统测试、验收及质量保证 (30)8.1现场测试收检 (30)8.2铜缆信息点的测试及性能保证 (30)8.3光纤信息点的测试及性能保证 (31)第九章人员培训及售后服务 (32)9.1培训 (32)9.2售后服务 (33)第一章前言本设计书向用户推荐的是一套完整的综合布线系统(GCS,Generic Cabling System)。

手机堆叠设计(PCBA)

手机堆叠设计关于手机设计,论坛中有不少的知识,但在手机设计初期的PCBA的堆叠方面却很少有人提及,其实堆叠的质量直接影响一款手机的生产量。

希望有这方面经验的前辈提供相关的知识让我们这些后辈也提高一下手机堆叠设计(也称系统设计)是手机研发过程中非常重要的一环.系统设计的好坏直接影响后续的结构设计,甚至其它可靠性等方面的问题.一个好的结构工程师,系统设计水平一定要过关.对ID/BB/RF/LAYOUT这几个部门的意见整合起来,是不件不容易的事情.结构工程师需要了解这方面的知识,综合起来,满足各部门所需,完成产品定义的要求.这方方面面完成,是一项全面而细致的工作.也体现兄弟们细心的一面.本贴置顶,大家可以就系统设计过程中与ID/BB/RF/LAYOUT部门沟通以及注意事项,设计经验方方面面发现自己的观点和感想.我会根据实际情况加分处理!加分范围:1~3分.應該是硬件做的事,很多小公司都給ME做,所以做出來的東西肯定不會是什麽好東西不同意楼上的说法,如果交给硬件做堆叠,出来的PCBA做结构,很难作出好产品.我是MD出身,最近专做pcba堆叠.不是小公司,230多人的方案研发公司.堆叠PCBA是一个非常综合的工作,MD,LAYOUT,RF,ID要多方位权衡,最终妥协达成一致,任何一方面太强,必然伤害其他性能.都不能算一个好的PCBA设计.其中要考虑的问题大概有一下几点:1.满足产品规划,适合做ID2.充分考虑射频天线空间3.考虑ESD/EMI4.考虑电源供电合理5.考虑屏蔽框简单6.考虑叠加厚度7.考虑各个连接简单可靠8.考虑各个定位孔,测试孔,螺丝孔,扣位避让,邮票孔等等9.预留扩展性......时间关系没有很系统的去总结,碰到具体问题必须要具体分析.我也反对3楼的说法,PCBA里有很多跟结构有关的件,SPEAKER、MIC、RECEIVER、BATTERY、ANTENNA、KEYPAD_FPC、SIDEKEY、HINGE、FPC、CONNECTOR、LCD、等等太多了,这些都是直接跟结构相关的器件,需要考虑到方方面面的问题,MD不去堆谁堆呀,当然选件以及摆放位置多听听其它人的意见是很不错的。

不同的走线层,一样的STUB

N年的宝贵经验告诉我们,遇到过孔stub时,最好办法就是器件在表层走线靠下层,器件在底层走线就靠上层,这样能把stub降到最低。

但是,有没有这样一种情况,你们觉得无论走哪一层都觉得不能把stub降得很低的情况呢?恩,还真有这么一种操作,而且其实我们还见得不少。

在比较理想的器件布局下,我们喜欢把高速信号的收发芯片都放在同一面,要么都是表层,要么都是底层。

原因很简单,这样的话我们从表层的pin打孔到内层走线时,只要我们走到了靠下的层(以器件放表层说明,如果是放底层则相反哈),这样两个过孔就都会是比较短的过孔stub,有利于提高信号传输质量。

而且不要老是动不动就提要背钻这事嘛,能保证质量的同时又可以简单快捷的省成本和加工流程这种好事,相信谁都不会拒绝吧?但是,有的高速信号却不能做到两个器件都放在正面,看起来好像显得我们不重视这些高速走线似的。

大家是不是觉得只要我们想优先保证它们的传输的话,就肯定轻松的做到先把它们都放在表层是吧?有的东西连臣妾都不能保证啊,更何况PCB 工程师呢?例如,其中一个器件是双面都有高速走线的pin 。

其实这样的器件是有的,而且应用很广泛,其中一种就是我们今天的主人公,PCIE 金手指。

在我们很多PCIE 子卡设计中,都会遇到它。

它的封装就是双面的焊盘结构。

这样的PCIE 信号我们最近接触非常多,主要就是应用在现在很火的人工智能领域上。

像上图高亮的TX 链路(怎么分的TX 还是RX ?看看电容呗)是在底层,而我们的主芯片放在表层,那我们的内线走线好像走到哪一层就是不能达到放同一面时的效果,无论是放在靠上层还是靠下层,都会有其中一个过孔有很长的stub 。

这时能够想象PCB 工程师的心情就好像下图的情况一样矛盾。

在说完了前面的铺垫之后,再说说本文想描述的案例。

该信号走的是PCIE3.0的协议(8Gbps ),板厚是2.0mm。

在第一版中,客户为了省成本,问我们能不能不背钻处理,然后我们高速先生也不是动不动就叫客户背钻的,因为经过验证之后,认为把走线走到靠下层时,长过孔的stub 大概在60mil 左右,对于8Gbps的信号仍在可以接受的范围。

5G通信基站大功率射频开关设计

0 引 言

大功率射频开关体积小且成本低,被广泛应用 于射频毫米波通信系统,以控制信号的导通和断开。 随着 5G 技术在全球范围内受到关注,将 5G 技术推 广到射频通信领域是目前的研究热点 [1]。毫米波通 信和波束成形等都是 5G 通信中的关键技术,而天线 是这些技术应用中的关键器件,射频开关则是天线的 重要电子元器件之一,可以快速控制信号通断。有开 关存在的天线能使得可重构的多波段相控阵实现几微 秒的动态重构,可以用于对工作频率差别要求较大的 情况。传统的 PIN 开关无法满足工作过程中驱动电压 的控制要求,因此本文设计一种 5G 通信基站大功率 射频开关来弥补传统开关性能不足的问题。

关键词:5G 通信基站;大功率射频开关;电路结构;电极设计

Design of High Power Radio Frequency Switch for Base Station in 5G Communication

ZHU Yan (China Information Consulting & Design Institute Co., Ltd., Nanjing ,高 博,等 . 一种用于 5G 移动通

信基站的大功率射频开关 [J]. 半导体技术,2020,45 (2):128-132. [2] 刘文学,陈诗军,葛 建,等 . 基于 GNSS 邻域相似 性的 5G 基站纳秒级时间同步技术研究 [J]. 通信学报, 2020,41(1):180-190. [3] 王 伟,宋家友 . 一种大功率高隔离度射频 SPDT 开 关的设计 [J]. 科学与信息化,2018(26):26-27. [4] 方峪民 . 无线通信基站雷害防护原理与工程设计要点 研究 [J]. 通讯世界,2018(3):39-40. [5] 武海涛,秦 磊,刘 佳 . 通信基站电源系统探讨: 浅析通信基站电源设备安全运行防护原理与解决办

ProeCreo手机主板堆叠设计案例解析(经典)

ProeCreo手机主板堆叠设计案例解析(经典)(一) ID 部分1. 概述:1.1.本手机结构状态如下:类别名称属性屏摄像头类屏 3.2WQVGA ,假纯平,兼容触摸板;摄像头前摄像头,FPC 式焊接,30w;后摄像头,BTB,30w,兼容 200W电声器件类扬声器2030 规格,引线式, 1 个受话器1506 规格,弹片式, 1 个麦克风4015 规格, FPC 式, 1 个马达圆柱弹片式 H=4.4 ,1 个连接器类SIM 卡座双 SIM 卡TF 卡座单 T 卡USB 接口10PIN耳机座 3.5mm 耳机, 10pin usb 电池连接器刀式电池连接器NOKIA 充电接口兼容天线类主天线支架弹片接触方式蓝牙天线陶瓷式FM 天线外接耳机式其他类键盘 3 键,支持自定义侧键兼容 3 个 FPC 侧键(音量侧键、拍照侧键) ,顶部兼容机械式开关机键手电筒,闪光灯贴片 led 灯;焊线式闪光灯电池电池容量 1500mAh1.2 备注:7835是一款双卡双待单 T 卡 PDA 手机;3.2' WQVGA,假纯平,兼容触摸板;2030喇叭一个;弹片式1506受话器;4015FPC 式 MIC;圆柱弹片式马达;前置30万,后置30万 (兼容200W)双摄像头;兼容手电筒及闪光灯;内置天线;全新 UI 设计。

1.3 图示:A:3D 图示B.CAD 档六视图,需标注结构器件名称。

2 .键盘定义:3 键。

FPC 式键盘,支持客户自定义。

兼容3 个侧键和一个顶部开关机键。

注意事项:a. 电铸或金属键上使用图标 (导航键\OK 键等),请在开模前仔细核对定义,避免造成模具报废与长时间修改;b. 键盘或机壳上必须加上导盲点;c. 软件必须与具体的按键丝印相匹配,否则 CTA 会有问题;3 .显示区域:LCD AA 区域如下图所示,其中建议面壳的开口尺寸比 TP _AA 区域大单边大 0.3mm 以上 (无触摸屏时面壳开口尺寸建议比 LCD AA 区大 0.50mm 以上), LCM 支撑泡棉内孔比壳体开口单边大 0.3MM,以从窗口侧面看不到泡棉为宜.因为各供应商的 LCD AA 和 TPAA 区也有一定的差别,客户作结构时需要参考采购的屏的图纸,以免不必要的麻烦。

AP6XXX模块设计Layout指导及AP6212 使用文档

AP6XXX Layout 注意事项:模块摆放如下图:请注意圆圈部分的走线(1). PIN2天线走50欧姆阻抗设计,走线越短越好,两边GND到RF走线距离要等距,30mil距离打地孔,如果需要支持5G模块,必须第三层作为天线参考地(天线底下第二层掏空),不能走直角锐角,要走弧线,走线和模块必须在同一层,走线宽度和焊盘同宽,且天线走线远离电源和时钟走线,走线不能有分支,避免能量辐射,RF座子底下要挖空,走线如下图(2). PIN9 VBAT,须先经过4.7uF滤波电容再到PIN9(建议再同时加多一颗0.1uF滤波电容),走线宽度与PIN9同宽即可,如果要打孔穿层,至少要两个过孔,保证电流能过600mA,PIN10是时钟输入线,尽量不要靠近PIN9,避免对VBAT产生纹波的干扰,需隔地处理。

(3). 晶体与模块同层,晶体及走线底部建议完整地,邻层不要放电源孔和走电源线或者走信号线,如下图三走法不推荐,晶体的两个地脚与匹配电容两个地需要单点下主地,与同层的主地隔离,注意如下黄色标识,推荐图一,图二走线:图一,图二,图三(4). SDIO_D0-D3&CMD走线尽量要平行等长,走线长度相差控制在30mil以内, 并且相邻层要远离其他电源和时钟走线,同时,这些走线需要加30K上拉电阻。

如果是SDIO3.0, 因是高速走线,这些走线需要做50ohm阻抗(5).PIN17 SDIO_CLK是高频走线,建议串一个22R或者0R电阻,再接一个电容NC到地,CLK走线全程需要包地处理,不能与信号线平行走线,邻层需远离电源/其他信号线(6).PIN21和PIN23是芯片内部Buck电路,外接一颗4.7uH的功率电感,是一颗噪声源,从PIN21脚出来的走线以及进到PIN23脚走线都需要包地及多打一些过孔处理,要先经过滤波电容再到PIN 23,且这两段走线宽度和模块PIN脚宽度一样即可,功率电感两个PAD中间需要挖空处理(7). PIN24 32.768k是系统参考时钟,全程走线远离电源/时钟走线及信号线,需全程包地处理,邻层也需要包地跟随,注意PIN24和PIN23脚之间用地隔一下(8)PIN25-28#为蓝牙PCM接口,要与CPU或者CODEC反接,即IN >OUT(9). 如果是用带GPS的模块,时钟是从PIN30输入,TCXO底部所有层必须掏空(9). 如果是用GPS,无源天线,需要接LNA,内部尽量打地孔,射频走线及LNA均和模块走在同一层,避免天线打孔,同时避开电源和时钟线(10). GPS信号是非常脆弱的信号,天线走线摆放要远离其他高频及电源走线,并要远离DDR及摄像头的走线,GPS天线座子地下要掏空(10). 如果是带NFC,天线匹配网络为:推荐接法,所用的阻容值均和下面用的值要一样:L1/L2 用0603封装即可,330nH的电感,注意物料的Q值,RSM1/RSM2用0603即可天线摆放,须严格按下实物图拜访,尤其L5/L6不能平行,可垂直,避免电磁感应相互干扰,两条走线直线拉出去即可下面这种是非常错误的走法:(8). 模块下面,即Top 层需要留一个完整地,不能走线切割,尽量不要有电源过孔,因为模块本身底面有高频走线,需要PCB的TOP层有完整地做参考,模块的PIN脚的出线如果要打孔,需在模块PAD或者以外打孔(9). 如果涉及到改版,请发板前再发给我们检查AP6212特点如下:1. AP6212 内部芯片的工艺要比AP6210高,体现在RF性能,功耗,吞吐量,蓝牙和WIFI共存上都有一定的优势2. AP6212的蓝牙是支持到BT4.2,而AP6210只支持到BT4.0AP6212和AP6210软硬件设计部份差异说明:(1)AP6212采用的是26M无源晶体从PIN10,11输入,而AP6210是26M无源晶体经过一个反相器之后从PIN30脚输入,如下图,如果用AP6212 A框要去掉,即不需要再接反相器,并接上接上R47=R48=0R,;(2)AP6212硬件上PIN29脚悬空,而AP6210是接上拉;(ps.如果26M时钟没有做兼容从PIN10,11进去,接AP6212的时候,可以尝试把时钟从PIN10脚输入,PIN29同时上拉)(3)AP6212要更新bcmhd新驱动1.201.34.x/1.201.59.x或者更新的版本,目前已经更新给主控原厂,请从主控原厂获取最新驱动版本,另外固件包firmware &Nvram也需要从主控原厂更新,验证的办法是:打开WIFI,抓出Kernel的log,检查打印信息,如果打印如下信息,说明AP6212已经正常工作:<4>[ 155.620641] Dongle Host Driver, version 1.201.59.2 (r491657)<4>[ 156.115862] Final fw_path=/system/etc/firmware/fw_bcm43438a0.bin<4>[ 156.115908] Final nv_path=/system/etc/firmware/nvram_ap6212.txt<4>[ 156.115956] Final conf_path=/system/etc/firmware/config.txt<4>[ 156.217659] NVRAM version: AP6212_NVRAM_V1.0_20140603<4>[ 156.218698] dhdsdio_write_vars: Download, Upload and compare of NVRAM succ以下是AP6212吞吐量测试,分别为只开WIFI,和同时打开WIFI跟蓝牙的性能测试只开WIFI,吞吐量:50Mbps打开BT,吞吐量: 30Mbps1.WIFI onlyRX:[ 3] 0.0- 1.0 sec 5.75 MBytes 48.2 Mbits/sec[ 3] 1.0- 2.0 sec 6.50 MBytes 54.5 Mbits/sec[ 3] 2.0- 3.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 3.0- 4.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 4.0- 5.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 5.0- 6.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 6.0- 7.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 7.0- 8.0 sec 6.50 MBytes 54.5 Mbits/sec[ 3] 8.0- 9.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 9.0-10.0 sec 6.38 MBytes 53.5 Mbits/sec[ 3] 0.0- 1.0 sec 5.54 MBytes 46.5 Mbits/sec [ 3] 1.0- 2.0 sec 5.94 MBytes 49.8 Mbits/sec [ 3] 2.0- 3.0 sec 5.95 MBytes 49.9 Mbits/sec [ 3] 3.0- 4.0 sec 5.95 MBytes 49.9 Mbits/sec [ 3] 4.0- 5.0 sec 5.99 MBytes 50.3 Mbits/sec [ 3] 5.0- 6.0 sec 5.88 MBytes 49.3 Mbits/sec [ 3] 6.0- 7.0 sec 5.95 MBytes 49.9 Mbits/sec [ 3] 7.0- 8.0 sec 5.99 MBytes 50.3 Mbits/sec [ 3] 8.0- 9.0 sec 5.79 MBytes 48.6 Mbits/sec [ 3] 9.0-10.0 sec 5.55 MBytes 46.5 Mbits/sec [ 3] 10.0-11.0 sec 6.02 MBytes 50.5 Mbits/sec [ 3] 11.0-12.0 sec 5.91 MBytes 49.5 Mbits/sec2.打开蓝牙,连接蓝牙音响RX:[ 3] 3.0- 4.0 sec 4.88 MBytes 40.9 Mbits/sec [ 3] 6.0- 7.0 sec 4.62 MBytes 38.8 Mbits/sec [ 3] 7.0- 8.0 sec 3.12 MBytes 26.2 Mbits/sec [ 3] 8.0- 9.0 sec 4.75 MBytes 39.8 Mbits/sec [ 3] 9.0-10.0 sec 5.12 MBytes 43.0 Mbits/sec [ 3] 10.0-11.0 sec 3.75 MBytes 31.5 Mbits/sec [ 3] 12.0-13.0 sec 3.88 MBytes 32.5 Mbits/sec [ 3] 17.0-18.0 sec 4.75 MBytes 39.8 Mbits/sec [ 3] 20.0-21.0 sec 4.25 MBytes 35.7 Mbits/sec [ 3] 22.0-23.0 sec 4.12 MBytes 34.6 Mbits/sec [ 3] 24.0-25.0 sec 4.12 MBytes 34.6 Mbits/sec [ 3] 27.0-28.0 sec 4.50 MBytes 37.7 Mbits/sec [ 3] 31.0-32.0 sec 3.62 MBytes 30.4 Mbits/sec [ 3] 34.0-35.0 sec 5.38 MBytes 45.1 Mbits/sec TX:[ 3] 0.0- 1.0 sec 4.78 MBytes 40.1 Mbits/sec [ 3] 1.0- 2.0 sec 5.48 MBytes 46.0 Mbits/sec [ 3] 2.0- 3.0 sec 5.52 MBytes 46.3 Mbits/sec [ 3] 3.0- 4.0 sec 5.31 MBytes 44.6 Mbits/sec [ 3] 8.0- 9.0 sec 5.45 MBytes 45.7 Mbits/sec [ 3] 9.0-10.0 sec 5.68 MBytes 47.6 Mbits/sec [ 3] 10.0-11.0 sec 5.47 MBytes 45.9 Mbits/sec [ 3] 11.0-12.0 sec 5.48 MBytes 46.0 Mbits/sec [ 3] 12.0-13.0 sec 4.96 MBytes 41.6 Mbits/sec [ 3] 13.0-14.0 sec 5.19 MBytes 43.5 Mbits/sec [ 3] 14.0-15.0 sec 4.68 MBytes 39.3 Mbits/sec [ 3] 15.0-16.0 sec 5.27 MBytes 44.2 Mbits/sec [ 3] 16.0-17.0 sec 5.21 MBytes 43.7 Mbits/sec [ 3] 17.0-18.0 sec 5.41 MBytes 45.4 Mbits/sec [ 3] 18.0-19.0 sec 5.48 MBytes 46.0 Mbits/sec。

Chap5-基于ARM的硬件系统设计

5

RS-232 串行接口

2

嵌入式

3

开发板

5

第32页,共100页。

32

2410的UART

S3C2410A 的UART (Universal Asynchronous Receiver and Transmitter) 提供了三个独立的异 步串行I/O口,每一个都可以工作在中断模式或 DMA模式,即UART可以产生中断或DMA请求以 在CPU和UART之前传送数据,使用系统时钟, UART最高可以支持230.4K bps 的位传输率。

第28页,共100页。

28

建立通用的I/O接口函数

应用

I/O操作

Create()

Open()

Read()

Write() Close() Loctl()

Destroy()

设备驱动程序

Driver_Create() Driver_Open() Driver_Read() Driver_Write() Driver_Close() Driver_Loctl() Driver_Destroy()

0X0000

I/O设备1

0X0000

主要优点:内存地址空间与I/O接口地址空间分开,互不影响,译码电路较 简单,并设有专门的I/O指令,所以编程序易于区分,且执行时间短,快 速性好。

缺点:只用I/O指令访问I/O端口,功能有限且要采用专用I/O周期和专用I/O控制 线,使微处理器复杂化。

第25页,共100页。

37

第38页,共100页。

38

UART的操作

串口初始化

将寄存器ULCONn、UCONn置零 设置寄存器ULCONn、UCONn、

UBRDIV 延时

PCB板pin-lam制作工艺培训教程

方正集团IT 产业集信息技术之大成,提供IT 服务、软件、硬件和数据运营在内的综合解决方案。

Founder Group's IT sector is a leader in informationtechnology, providing comprehensive solutions,including IT services, software, hardware,and data operation.珠海方正高密电子有限公司Zhuhai Founder Hi-Density Electronic Co.,ltd Pin-lam制作流程培训编写人:loron时间:2011.06.14 一、相关设备、物料介绍二、工程设计要点介绍三、Pin-lam制作流程四、Pin-lam 规范要求与制程能力目录1.1 压板工具--------Lamination Plate ( or Caul Plate)1.2 压板工具--------钢板(Stainless Steel Separator)Bushing衬套Pin 销钉1.3 压板工具------销钉和衬套(Pin and Bushing )PIN 钉长度规格:6.35*4.76* 38mm 、44mm 、51mm1.4 压板工具的组合 1.5冲槽孔冲钉PIN 孔冲头规格:CP2000冲头:5.762*8.112 ;PE3000冲头:7.11*4.762;PP2000冲头:5.762*8.112 ;1.6 牛皮纸打孔机1.7 PE-3000 PE冲孔机PE 冲孔机冲头PE 冲孔机冲座1.8 PP-2000 PP冲孔机1.9 CP-2000 PP冲孔机1.10 Pin-lam 叠板台面盖板底盘2.1.1 PIN Lam 平面图2.1 PIN Lam 设计效果与尺寸要求常规拼版15.5常规拼版15.5YA+YB 备注(inch)5.5~6.5mm2L3L4L2.2.1 流程及标注:1)内层AOI (大站)—PE 冲孔(小站):标注“此板为PIN LAM 板,需冲出四个槽孔”;2)压合(大站)—熔合(小站):流程更改为“压合(大站)—组合(小站)”备注“PIN LAM 板,使用PIN 钉叠板”。

基于PIN管的大功率射频开关研制

通 讯系统 中, 常需要在 两个不同的设备 间切换 , 经 使两

* 收稿 日期 :0 1年 9月 4 E, 回 日期 :0 1 l 21 t修 2 1 年 O月 1 6日

作 者 简 介 : 帅 , , 士 研究 生 , 究 方 向 : 频 收 发 开 关 。 尹 男 硕 研 射

12 2

图 4 导 通 时 损 耗 和驻 波 比仿 真 图 形

Im5 I Im6 l

向电阻 R , 经长度 a 4后 , / 在分 支点 , 输入阻抗 变为 / 其 R 。对 于通道 2 不考 虑 D , 2反偏 结 电容 , 在 / R 旁路作 用下, 其功率损失 为 / / +Z ) 折算 为衰减 分 贝数 ( R o,

尹

帅: 基于 PN管 的大功率射频开关研制 I

( . p ) 15 F 1 L 、 3为调 谐 电感 。 O 5 F 一 . p 。L 、 2L

第4 O卷

条微 波通 道交 替工作 , 以通 过单 刀双掷 开关 来实 现 。 可 比如天线收发开关 , 发射 机和接收机公用一个 天线 , 由于雷 达 的工作多为脉 冲体制 , 发射 和接收可在时 间上分割 , 由收 发 开关来进行控制 。

阻 ; ,零偏 或 者 反 偏 状 态 下 的 电 容 ; : 大 允 许 的 反 偏 C: VR 最

2 P N 二 极 管 的 基 本 原 理 I

2 1 P N 管 的 结 构 . I

直流电压 . . r载流子平均寿命 ;/ 前向偏置电流 I:

R, -

“ 【 J f

厂—1 —T—] _ _

50 0 MHz差损小于 0 7 B, , . d 隔离度大于 7 d 驻波 比小一地 1 5 功率容量 1 0 开关速度小于 2 0B, ., 0 W, O s的一分 四射频开关 。

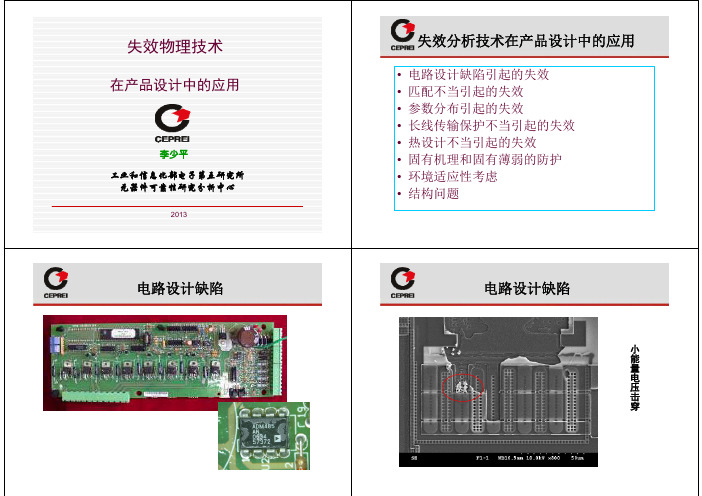

3失效分析经典案例-设计缺陷案例

由现象可以看到:

¾ 与低亮无关 ¾ 与基极电流大小有关 ¾ 与高亮的启动有关

——高亮的启动状态

¾ 与高亮工作后的结果有关 (与高亮的时间间隔长短有关)

——温度 ¾ 每个灯均工作在大电流状态

——电流流向,电流增大的道理

电路设计缺陷

电瓶+

103/250V 47μF/25V

2200μF/35V

R1

R2 220Ω

220Ω

SCR2

D4 M7

C1

R4* 2.7K

BT151-500R

SCR1

D1 M7

R5 51K

Q1 MMBT5401

BATT1 12V/7Ah

交流入~

BT151-500R

ACG

SCR3

Z1

MCR100-8

16V

Z2 13V

R6

1K R11

C2

D7 10A

1K/1210

设计缺陷

端口长线保护

XCS30XL分析启发

工程应用失 效与浪涌试 验失效表征 相同

工程失效属 于浪涌电压 --脉冲大 电压击穿失 效

Pin102 重点防护

失效端口 Pin102

相同

Pin102相关外 围电路易引入 高压?

电路设计缺陷

开关部件(VDMOS)热失效: 9缓慢开启,开时极大功耗; 9开快后,还出现振荡又热烧毁。

VA/VB(输入)连接到航空插座 也属于”长线传输”

VA输入端(Pn11)

VA/VB输入端连 接到航空插座

C极 B极

烧毁点

Pin7输出驱动管形貌

CAN总线数据传输端口电压击穿

烧毁点

VME接口板设计

VIACKOUT = 1; // 不能乱传中断应答

VDTACK := 0; // 不能随便应答

if (!RST) then SV0

else if (!CS_VME) then SV1 // VME 普通读写

else if (!VIACK & !VIACKIN) then SV4

else if (!CS_VME) then SV3 // 本周期没完没了

else SV0

with {VDTACK := 0; }

// SV4..SV7 为中断应答周期

State SV4:

VIACKOUT = H; // 情况不明,先别往下传

VDTACK := L;

if (!RST # VIACK # VIACKIN) then SV0

if (!RST) then SV0;

else if (!BUSYL) then SV2 // 双口正忙

else SV3

with { VDTACK := 1;}

State SV3:

VIACKOUT = 1; // 不传中断应答

VDTACK := 1; // 准备好了

if (!RST) then SV0

..

//==========================================

// VME 总线周期控制之状态机 (包括中断应答)

//==========================================

State_Diagram [Qv2,Qv1,Qv0];

IntVec.clk = VCLK;

VIRQ3.clk = VCLK;

一种S波段PIN开关的设计

图5

开关实际测试的损耗和隔离度结果

参考文献

[1]甘本祓.吴万春.现代徽波滤波器的结构与设计.北京:科学出版社,1972.

[2]Inder Bald.Padumh Bhartia.徽波固态电路设计(第二版).北京:电子工业出版社,2006.

258

L.

C C

C

&

Cf

图2

PIN二极管的等效电路

图3

PIN二极管的简化等效电路图

(a)反向偏置;(b)正向偏置。

4梳状滤波器PIN开关的设计

由于PIN管具有转换的特性,并且在反向偏压下具有确定的电容值。因此,如果用PIN管的C代替

图l中的集中电容C5就又可能形成微波PIN开关。三对PIN二极管的梳状滤波器开关的结构示意图如 图4。

perfect pedormsnce.

Keywords:PIN switch,Isolation,loss

1

引言

微波半导体开关在相控阵雷达、电子对抗、微波通信、卫星通信以及微波测量等方面有着广泛的应用。

半导体开关与电子机械开关相比,具有开关速度快的特点;与铁氧体相比,具有频带宽、体积小、重量轻的优

点。又由于PIN开关稳定性好、可控功率大、损耗小、所以在许多半导体控制电路中多数采用PIN管。虽然 近年来MMIC开关发展迅猛,但由于它的功率承受能力与PIN管开关相比尚存在一定的差距,所以未能取代 PIN管开关。 本文将介绍一种由梳状滤波器和PIN管结合而形成的SPST开关,由于此种开关中的PIN管的结电容 被纳入滤波器的谐振元中,PIN管的寄生参数获得了合理的利用,从而大大提高了开关的性能。因此它具有 较宽的带宽、损耗小、隔离度高、结构紧凑、体积小、重量轻的特点。

本文将介绍一种由梳状滤波器和pin管结合而形成的spst开关由于此种开关中的pin管的结电容被纳入滤波器的谐振元中pin管的寄生参数获得了合理的利用从而大大提高了开关的性能

《射频通信电路设计》习题及解答

解: GSM 是 Global System for Mobile Communications 的缩写,意为全球移动通信

系统。 CDMA 英文全称是 Code Division Multiple Address,意为码分多址。 Code division multiple access (CDMA) is a channel access method used by

GP

10 lg

Pout PIN

PIN

199mw

6. 在阻抗为 Z0=75的 CATV 系统中,如果测量得到电压为 20dBV,则对应的功率 P

为多少?如果在阻抗为 Z0=50的系统中,测量得到相同的电压,则对应的功率 P

又为多少?

解答:

V (dBuv) 90 10 lg Z0 P(dBm) P(dBm) V (dBuv) 90 10 lg Z0 当 Z0 =75 时, P(dBm) =-88.7 dBm

1.7 一个 L=10nF 的电容器,引脚的分布电容为 C=1pF。请问当频率 f 为多少时,电感器开

始呈现容抗。

解:

思路同上,当频率 f 小于 1.59 GHz 时,电感器呈现感抗。

1.8 1)试证明(1.2)式。2)如果导体横截面为矩形,边长分别为 a 和 b,请给出射频电

阻 RRF 与直流电阻 RDC 的关系。

习题 1:

1.1 本书使用的射频概念所指的频率范围是多少? 解:

本书采用的射频范围是 30MHz~4GHz 1.2 列举一些工作在射频范围内的电子系统,根据表 1-1 判断其工作波段,并估算相应射频

信号的波长。

解: 广播工作在甚高频(VHF)其波长在 10~1m 等

10个cadence allegro经典案例

一、斯卡鲁帕尔马尼的“春之韵”系列斯卡鲁帕尔马尼是一位在艺术领域备受瞩目的艺术家,他的“春之韵”系列作品中,使用了Cadence Allegro软件进行了精准的电路设计,实现了艺术与科技的完美结合。

通过Cadence Allegro的卓越性能和稳定性,斯卡鲁帕尔马尼成功地实现了作品中的电路元件的精确布局和优化,让作品在内部结构上更加完美。

这一系列作品的成功,不仅展现了艺术家对科技的巧妙运用,也向人们展示了Cadence Allegro在电路设计中的优秀表现。

二、华为5G基站天线设计作为全球领先的通信技术企业,华为公司在5G领域的发展备受瞩目。

在5G基站天线设计中,Cadence Allegro发挥了关键作用。

通过Cadence Allegro的高度灵活性和智能设计工具,华为公司工程师们实现了天线的快速设计、仿真和验证,大大加快了产品上市时间,提高了5G基站的性能和可靠性。

华为的成功案例再次证明了Cadence Allegro在电路设计领域的卓越性能和广泛应用价值。

三、尼康相机电路设计尼康是全球知名的相机制造商,其产品质量和性能一直备受推崇。

在尼康相机的电路设计中,Cadence Allegro为设计师们提供了强大的支持和工具,帮助他们实现了电路的高度集成和优化,从而使得尼康相机在成像质量、稳定性和实用性上获得了极大的提升。

尼康相机的成功案例充分显示了Cadence Allegro在消费电子产品领域的重要作用,也证明了Cadence Allegro在实际应用中的稳定性和可靠性。

四、特斯拉电动汽车电池管理系统设计特斯拉作为电动汽车领域的领先者,其产品一直以高性能和创新著称。

在特斯拉电动汽车的电池管理系统设计中,Cadence Allegro发挥了关键作用。

通过Cadence Allegro提供的强大电路设计和仿真工具,特斯拉工程师们成功地实现了电池管理系统的高效设计和验证,保证了汽车电池的安全性和性能稳定性。

板级can通讯实现方式

板级can通讯实现方式

板级CAN通讯实现方式主要有以下几种:

1.硬件实现方式:通过CAN控制器和支持CAN通信的微控制器来实现。

这些控制器具有CAN总线驱动能力,能实现多个节点之间的通信。

2.软件实现方式:通过在微控制器上运行CAN通信协议栈来实现。

这种方法不需要额外的硬件设备,但需要占用一定的处理器资源。

3.硬件和软件结合实现方式:这种方式综合了硬件实现和软件实现的优势,既能保证通信性能,又能降低资源占用。

4.基于FPGA的实现方式:通过编写FPGA程序来实现CAN通信,具有较高的灵活性和可定制性,但需要一定的硬件设计和编程能力。

5.基于嵌入式系统的实现方式:在嵌入式系统中集成CAN通信模块,通过操作系统或实时操作系统实现CAN通信协议栈,实现多个节点之间的通信。

6.使用现成CAN总线模块实现:购买成熟的CAN总线模块,通过接口协议与微控制器连接,实现板级CAN通信。

这种方式简单易用,但成本较高。

在实际应用中,可以根据具体需求和条件选择合适的板级CAN通讯实现方式。

微波pin二极管开关驱动器设计[汇集]

![微波pin二极管开关驱动器设计[汇集]](https://img.taocdn.com/s3/m/29a1051b6d85ec3a87c24028915f804d2b1687f6.png)

微波PIN二极管开关驱动器设计

随着现代通讯技术的发展和系统小型化的趋势,在许多通讯领域,发射信号要求输出功率大,因此要求与其相连的如开关切换、跳频滤波等电路,动态范围大、交调指标高。

许多情况下使用PIN二级管作为开关元件,它对驱动器的要求是当开关打开时要有足够大的驱动电流输出,当开关关闭时无电流输出,同时要有足够的反向电压,反向电压越高,交调指标就越好,动态范围就越大。

因而对于大信号来说,系统中的驱动电路尤为关键。

1.微波PIN二极管开关中使用的二极管必须由电流来驱动,而现在通常控制信号都由数字电路输出,多是给一个电平,不具备电流驱动能力。

所以每个开关或微波控制电路产品,在电路和控制信号间必须安装一个驱动电路,即要做的事。

现在该类驱动器有单片集成电路卖,比如,中电24所,骊山微电子公司(771所),北京华虹,国外也有专门的产品。

为何要自己做:

通常标准产品都是标准电源产品,比如+-5V;+5-12v,驱动电流偏小,一般电流不超过35毫安,不能满足其他及特殊的需要。

比如控制大功率电路产品,需要高反压,大电流等,如+5-28V,电流50毫安。

降低成本,通常单片售价每路约70元,自制每路约10元,每年需求约20万只。

2什么是驱动器:简单说就是将一个低频控制信号,向TTL,ECL

电平(0V;+5V,无电流提供能力),通过加电(正负电源)变化成正和负电源输出带电流驱动的电平。

要考虑:驱动器内部偏置电阻设置、负载电阻设置、响应时间、元器件选择、电源等。

3单路驱动电路附后

TTL

PIN负载。

印制板设计制造和组装术语和定义

印制板设计制造和组装术语和定义印制板(Printed Circuit Board,简称PCB)是电子设备中最基本的组成部分之一,它是由绝缘材料上绘制导电图案并通过化学和电镀等工艺制成的电路,被应用于电力、通讯、医疗、工业控制等领域。

印制板的设计、制造和组装涉及许多术语和定义,下面将介绍一些常见的术语及其定义。

1.印制板设计术语:- 原理图(Schematic):电路设计师根据系统需求,使用符号和线条的形式绘制电路图。

- PCB布局(PCB Layout):根据原理图,将各个电子元件在PCB板上的位置进行规划和布置,确保电路的特性和性能得到最佳表现。

- 焊盘(Pad):印制板上的金属圆形区域,用于连接电子元件引脚和印制板。

- 引脚(Pin):电子元件上用于与其他元件或印制板连接的金属接触区域。

- 丝印(Silkscreen):印制板上的文字和图案,用于标识元件位置、数值和方向等信息。

- 板厚(Thickness):印制板的厚度,通常以毫米(mm)为单位。

- 设计规则(Design Rule):印制板设计中的一组规定,用于确定布局、走线、钻孔等的限制条件。

2.印制板制造术语:- 基材(Substrate):印制板的基础材料,通常采用玻璃纤维增强的环氧树脂材料。

- 接线层(Copper Layer):印制板上的导电层,用于连接电子元件引脚和形成电路。

- 容量(Capacity):指印制板上导线层的电容值,影响信号传输的速度和质量。

- 层数(Layer):印制板上导线层的数量,多层印制板能够实现更复杂的电路设计。

- 阻抗控制(Impedance Control):指印制板上信号传输线的阻抗的控制,以确保信号质量和匹配。

- 焊接(Soldering):将电子元件与印制板通过焊接工艺进行连接,通常采用锡焊工艺。

3.印制板组装术语:- 表面贴装技术(Surface Mount Technology,简称SMT):一种将电子元件直接焊接在印制板表面的组装技术。

variopin connector符合的标准

variopin connector符合的标准全文共四篇示例,供读者参考第一篇示例:Variopin连接器是一种常用的电子元件,用以连接不同的电子设备和电路板。

它具有多个引脚,通常为20个或更多,适用于各种复杂电子系统的连接。

Variopin连接器也被称为多引脚连接器,因为它可以同时连接多个信号或电源线。

Variopin连接器符合的标准是指符合国际标准或行业标准的连接器,以确保其质量和性能符合各种应用领域的要求。

下面是一些主要的标准,Variopin连接器需要符合的:1. UL认证:UL是美国Underwriters Laboratories的缩写,是全球最具权威的独立测试和认证机构之一。

获得UL认证说明连接器符合美国和加拿大的安全标准,并且经过了严格的测试和审核。

2. RoHS指令:RoHS指令是欧盟颁布的限制使用有害物质的法规,旨在减少废弃电子产品对环境的影响。

Variopin连接器需要符合RoHS指令,确保其中不含有铅、汞、镉等有害物质。

3. ISO 9001:ISO 9001是国际标准化组织颁布的质量管理体系标准,确保生产过程和产品符合一定的质量要求。

Variopin连接器需要符合ISO 9001标准,以确保其品质稳定、可靠。

4. IPC标准:IPC是国际电子工业协会的缩写,设立了一系列关于电子元件和设备制造的标准。

Variopin连接器需要符合IPC标准,以保证其设计、制造和测试的一致性和可靠性。

除了以上提到的标准外,Variopin连接器还需要符合一系列电气性能、机械性能和环境适应性方面的标准。

这些标准包括但不限于电气接触阻抗、引线尺寸、耐热性、潮湿性能等方面,以确保其在各种环境条件下都能正常工作。

总的来说,Variopin连接器需要符合的标准涵盖了其安全性、质量稳定性和可靠性等方面,以确保其能够广泛应用于各种电子设备和系统中。

只有符合这些标准,Variopin连接器才能成为电子领域中不可或缺的元件,为数字化时代的进步贡献力量。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

某6万多Pin通讯板设计案例

【案例背景】:此板共6万多pin,板子布局空间紧张,客户交期比较急,要求在2个月内完成设计、仿真及制板,而且客户原理图还没有最终确定就已经开始进行

设计,相当于是一边评审原理图,一边修改方案进行设计,同时还进行仿

真;板上小电压大电流的电源种类多,且接口类型繁多,速率都相当高。

【接口类型】:SFP+、Interlaken、QPI、PCIE3、DDR4和DDR3信号等

【标准】:SFF8431,QPI3.0,PCIE3.0,JESD79-4,JESD79-3E等

【信号速率】: 1.PCIE3.0 -8Gbps;

2.PCIE2.0- 5Gbps;

3.QPI- 8Gbps;

4.DDR4- 2133Mbps

5.DMI- 5Gbps;

6.Interlaken- 12.5Gbps/10.3125Gbps;

7.DDR3- 1600Mbps;

8. serdes-10.3125Gbps

【设计描述】该项目布局比较密,电源和高速信号种类比较多,信号最高速率12.5G,这就要求走线层面规划要到位,还要确保信号质量,经过仿真确认,最终采用介电常数比较小的TU872SLK-sp,同时高速信号进行背钻设计;电源通道需要整体规划,大电流电源保证了足够的通流平面,最终满足了客户的设计。

(1)DDR4部分的设计:

(2)主要芯片DDR3设计

(3)主要芯片的设计

(4)电源层。