GS88236AB-250I中文资料

GS881Z32BGD-150IV中文资料

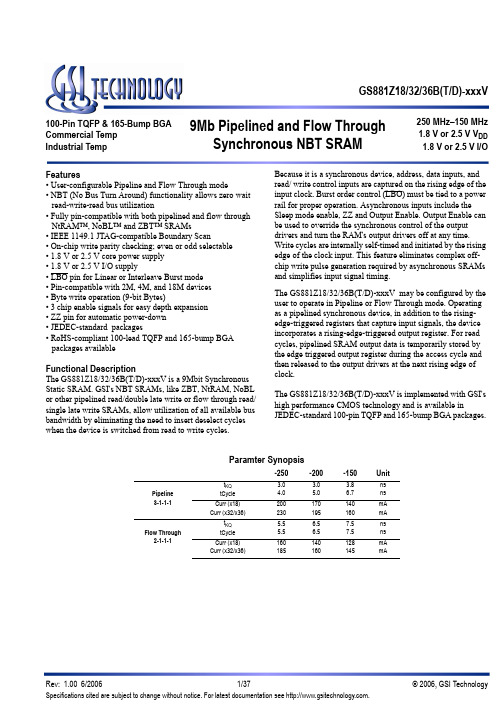

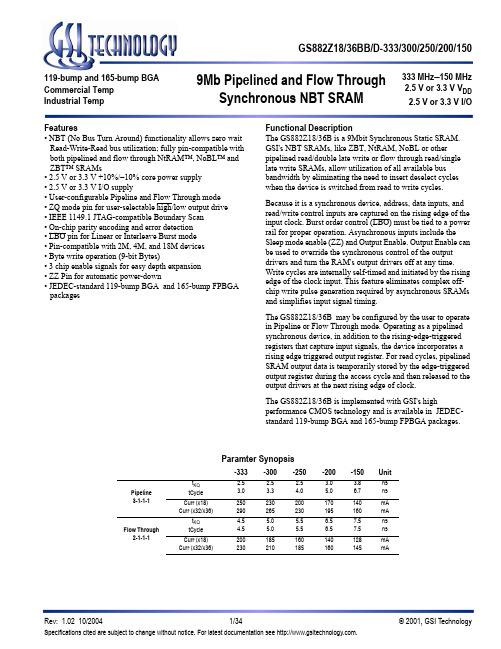

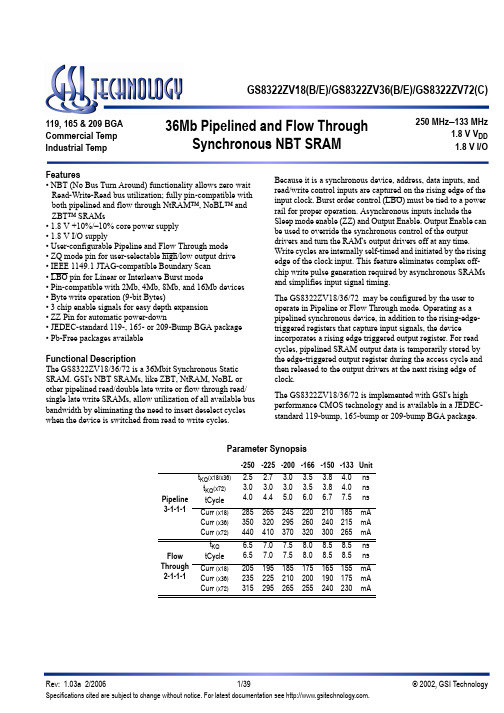

GS881Z18/32/36B(T/D)-xxxV9Mb Pipelined and Flow ThroughSynchronous NBT SRAM250 MHz–150 MHz 1.8 V or 2.5 V V DD 1.8 V or 2.5 V I/O100-Pin TQFP & 165-Bump BGA Commercial Temp Industrial Temp Features• User-configurable Pipeline and Flow Through mode• NBT (No Bus Turn Around) functionality allows zero wait read-write-read bus utilization• Fully pin-compatible with both pipelined and flow through NtRAM™, NoBL™ and ZBT™ SRAMs• IEEE 1149.1 JTAG-compatible Boundary Scan• On-chip write parity checking; even or odd selectable • 1.8 V or 2.5 V core power supply • 1.8 V or 2.5 V I/O supply• LBO pin for Linear or Interleave Burst mode • Pin-compatible with 2M, 4M, and 18M devices • Byte write operation (9-bit Bytes)• 3 chip enable signals for easy depth expansion • ZZ pin for automatic power-down • JEDEC-standard packages• RoHS-compliant 100-lead TQFP and 165-bump BGA packages availableFunctional DescriptionThe GS881Z18/32/36B(T/D)-xxxV is a 9Mbit Synchronous Static SRAM. GSI's NBT SRAMs, like ZBT, NtRAM, NoBL or other pipelined read/double late write or flow through read/single late write SRAMs, allow utilization of all available bus bandwidth by eliminating the need to insert deselect cycles when the device is switched from read to write cycles.Because it is a synchronous device, address, data inputs, and read/ write control inputs are captured on the rising edge of the input clock. Burst order control (LBO) must be tied to a power rail for proper operation. Asynchronous inputs include the Sleep mode enable, ZZ and Output Enable. Output Enable can be used to override the synchronous control of the output drivers and turn the RAM's output drivers off at any time. Write cycles are internally self-timed and initiated by the rising edge of the clock input. This feature eliminates complex off-chip write pulse generation required by asynchronous SRAMs and simplifies input signal timing.The GS881Z18/32/36B(T/D)-xxxV may be configured by the user to operate in Pipeline or Flow Through mode. Operating as a pipelined synchronous device, in addition to the rising-edge-triggered registers that capture input signals, the device incorporates a rising-edge-triggered output register. For read cycles, pipelined SRAM output data is temporarily stored by the edge triggered output register during the access cycle and then released to the output drivers at the next rising edge of clock.The GS881Z18/32/36B(T/D)-xxxV is implemented with GSI's high performance CMOS technology and is available inJEDEC-standard 100-pin TQFP and 165-bump BGA packages.Paramter Synopsis-250-200-150UnitPipeline 3-1-1-1KQ tCycle 4.0 5.0 6.7ns Curr (x18)Curr (x32/x36)200230170195140160mA mA Flow Through 2-1-1-1t KQ tCycle 5.55.5 6.56.57.57.5ns ns Curr (x18)Curr (x32/x36)160185140160128145mA mA807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B FT V DD NC V SS DQ B DQ B6V DD V SS DQ B DQ B DQP BV SS V DDQ V DDQ V SS DQ A DQ A V SS V DDQ DQ A DQ A V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A A 1A A E 1E 2 N C N C B BB AE 3C K W C K E VD DV S SG A D V N C A A AA 512K x 18Top View DQP A A NC NC NC NC NC NC NC NCNC NC NC NC NC NC NCNC NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z18BT-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C V SS V DDQ DQ C DQ C FT V DD NC V SS DQ D DQ D2V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A AA A E 1E 2 B DB CB BB AE 3C K W C K E VD DV S SG A D V N C A A AA 256K x 32Top View DQB NC DQ B DQ B DQ B DQ A DQ A DQ A DQ A NCDQ C DQ C DQ C DQ D DQ D DQ D NCDQ C NC 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z32BT-xxxV 100-Pin TQFP Pinout (Package T)807978777675747372717069686766656463626160595857565554535251123456789101112131415161718192021222324252627282930V DDQ V SS DQ C DQ C V SS V DDQ DQ C DQ C FT V DD NC V SS DQ D DQ D2V DDQ V SS DQ D DQ D DQ D V SS V DDQ V DDQ V SS DQ B DQ B V SS V DDQ DQ B DQ B V SS NC V DD ZZ DQ A DQ A V DDQ V SS DQ A DQ A V SS V DDQ L B O A A A A A 1A 0T M S T D I V S SV D DT D O T C K A A A A A AA A E 1E 2 B DB CB BB AE 3C K W C K E VD DV S SG A D V N C A A AA 256K x 36Top View DQB DQP B DQ B DQ B DQ B DQ A DQ A DQ A DQ A DQP ADQ C DQ C DQ C DQ D DQ D DQ D DQP DDQ C DQP C 100999897969594939291908988878685848382813132333435363738394041424344454647484950GS881Z18/32/36B(T/D)-xxxVGS881Z36BT-xxxV 100-Pin TQFP Pinout (Package T)100-Pin TQFP Pin DescriptionsSymbolTypeDescriptionA 0, A 1In Burst Address Inputs; Preload the burst counterA In Address Inputs CK In Clock Input SignalB A In Byte Write signal for data inputs DQ A1–DQ A9; active low B B In Byte Write signal for data inputs DQ B1–DQ B9; active low BC In Byte Write signal for data inputs DQ C1–DQ C9; active low BD In Byte Write signal for data inputs DQ D1–DQ D9; active lowW In Write Enable; active low E 1In Chip Enable; active lowE 2In Chip Enable—Active High. For self decoded depth expansion E 3In Chip Enable—Active Low. For self decoded depth expansionG In Output Enable; active lowADV In Advance/Load; Burst address counter control pinCKE In Clock Input Buffer Enable; active lowNC —No ConnectDQ A I/O Byte A Data Input and Output pins DQ B I/O Byte B Data Input and Output pins DQ C I/O Byte C Data Input and Output pins DQ D I/O Byte D Data Input and Output pins ZZ In Power down control; active high FT In Pipeline/Flow Through Mode Control; active lowLBO InLinear Burst Order; active low.TMS Scan Test Mode Select TDI Scan Test Data In TDO Scan Test Data Out TCK Scan Test Clock V DD In Core power supplyV SS In GroundV DDQInOutput driver power supplyGS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x18 Commom I/O—Top View 1234567891011A NC A E1BB NC E3CKE ADV A17A A A B NC A E2NC BA CK W G NC A NC B C NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQA C D NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA D E NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA E F NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA F G NC DQB V DDQ V DD V SS V SS V SS V DD V DDQ NC DQA G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC J K DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC K L DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC L M DQB NC V DDQ V DD V SS V SS V SS V DD V DDQ DQA NC M N DQB NC V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x32 Common I/O—Top View 1234567891011A NC A E1BC BB E3CKE ADV A17A NC A B NC A E2BD BA CK W G NC A NC B C NC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC NC C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N NC NC V DDQ V SS NC NC NC V SS V DDQ NC NC N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36B(T/D)-xxxV165 Bump BGA—x36 Common I/O—Top View 1234567891011A NC A E1BC BB E3CKE ADV A A NC A B NC A E2BD BA CK W G NC A NC B C DQPC NC V DDQ V SS V SS V SS V SS V SS V DDQ NC DQPB C D DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB D E DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB E F DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB F G DQC DQC V DDQ V DD V SS V SS V SS V DD V DDQ DQB DQB G H FT MCH NC V DD V SS V SS V SS V DD NC NC ZZ H J DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA J K DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA K L DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA L M DQD DQD V DDQ V DD V SS V SS V SS V DD V DDQ DQA DQA M N DQPD NC V DDQ V SS NC NC NC V SS V DDQ NC DQPA N P NC NC A A TDI A1TDO A A A NC P RLBONCAATMSA0TCKAAAAR11 x 15 Bump BGA—13 mm x 15 mm Body—1.0 mm Bump Pitch(Package D)GS881Z18/32/36D-xxxV165-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsA I Address Inputs DQ A DQB DQC DQD I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active high CKE I Clock Enable; active low W I Write Enable; active low E 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active highZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock MCH —Must Connect High DNU —Do Not Use V DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS881Z18/32/36B(T/D)-xxxVK18S A 1S A 0Bu r s t C o u n t e rL B OA D VM e m o r y A r r a yGC KC K ED QF TN CN CD Q a –D Q nKS A 1’S A 0’D QM a t c hW r i t e A d d r e s sR e g i s t e r 2W r i t e A d d r e s sR e g i s t e r 1W r i t e D a t aR e g i s t e r 2W r i t e D a t aR e g i s t e r 1KKKKKKS e n s e A m p sW r i t e D r i v e r sR e a d , W r i t e a n dD a t a C o h e r e n c yC o n t r o l L o g i cD QKP a r i t y C h e c kF TA 0–A nE 3E 2E 1WB DB CB BB AGS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxV NBT SRAM Functional Block DiagramGS881Z18/32/36B(T/D)-xxxVFunctional DetailsClockingDeassertion of the Clock Enable (CKE) input blocks the Clock input from reaching the RAM's internal circuits. It may be used to suspend RAM operations. Failure to observe Clock Enable set-up or hold requirements will result in erratic operation.Pipeline Mode Read and Write OperationsAll inputs (with the exception of Output Enable, Linear Burst Order and Sleep) are synchronized to rising clock edges. Single cycle read and write operations must be initiated with the Advance/Load pin (ADV) held low, in order to load the new address. Device activation is accomplished by asserting all three of the Chip Enable inputs (E 1, E 2 and E 3). Deassertion of any one of the Enable inputs will deactivate the device. Function W B A B B B C B D Read H X X X X Write Byte “a”L L H H H Write Byte “b”L H L H H Write Byte “c”L H H L H Write Byte “d”L H H H L Write all Bytes L L L L L Write Abort/NOPLHHHHRead operation is initiated when the following conditions are satisfied at the rising edge of clock: CKE is asserted low, all three chip enables (E 1, E 2, and E 3) are active, the write enable input signals W is deasserted high, and ADV is asserted low. The address presented to the address inputs is latched in to address register and presented to the memory core and control logic. The control logic determines that a read access is in progress and allows the requested data to propagate to the input of the output register. At the next rising edge of clock the read data is allowed to propagate through the output register and onto the output pins.Write operation occurs when the RAM is selected, CKE is active and the write input is sampled low at the rising edge of clock. The Byte Write Enable inputs (B A , B B , B C & B D ) determine which bytes will be written. All or none may be activated. A write cycle with no Byte Write inputs active is a no-op cycle. The pipelined NBT SRAM provides double late write functionality, matching the write command versus data pipeline length (2 cycles) to the read command versus data pipeline length (2 cycles). At the first rising edge of clock, Enable, Write, Byte Write(s), and Address are registered. The Data In associated with that address is required at the third rising edge of clock.Flow Through Mode Read and Write OperationsOperation of the RAM in Flow Through mode is very similar to operations in Pipeline mode. Activation of a read cycle and the use of the Burst Address Counter is identical. In Flow Through mode the device may begin driving out new data immediately after new address are clocked into the RAM, rather than holding new data until the following (second) clock edge. Therefore, in Flow Through mode the read pipeline is one cycle shorter than in Pipeline mode.Write operations are initiated in the same way, but differ in that the write pipeline is one cycle shorter as well, preserving the ability to turn the bus from reads to writes without inserting any dead cycles. While the pipelined NBT RAMs implement a double late write protocol, in Flow Through mode a single late write protocol mode is observed. Therefore, in Flow Through mode, address and control are registered on the first rising edge of clock and data in is required at the data input pins at the second rising edge of clock.Synchronous Truth TableOperationType Address CK CKE ADV W Bx E 1E 2E 3G ZZDQNotesRead Cycle, Begin Burst R External L-H L L H X L H L L L Q Read Cycle, Continue Burst B Next L-H L H X X X X X L L Q 1,10NOP/Read, Begin Burst R External L-H L L H X L H L H L High-Z 2Dummy Read, Continue Burst B Next L-H L H X X X X X H L High-Z 1,2,10Write Cycle, Begin Burst W External L-H L L L L L H L X L D 3Write Cycle, Continue Burst B Next L-H L H X L X X X X L D1,3,10Write Abort, Continue Burst B Next L-H L H X H X X X X L High-Z 1,2,3,10Deselect Cycle, Power Down D None L-H L L X X H X X X L High-Z Deselect Cycle, Power Down D None L-H L L X X X X H X L High-Z Deselect Cycle, Power Down D None L-H L L X X X L X X L High-Z Deselect Cycle D None L-H L L L H L H L X L High-Z 1Deselect Cycle, Continue DNone L-H L H X X X X X X L High-Z 1Sleep ModeNone X X X X X X X X X H High-Z Clock Edge Ignore, StallCurrentL-HHXXXXXXXL-4Notes:1.Continue Burst cycles, whether read or write, use the same control inputs. A Deselect continue cycle can only be entered into if a Dese-lect cycle is executed first.2.Dummy Read and Write abort can be considered NOPs because the SRAM performs no operation. A Write abort occurs when the Wpin is sampled low but no Byte Write pins are active so no write operation is performed.3.G can be wired low to minimize the number of control signals provided to the SRAM. Output drivers will automatically turn off duringwrite cycles.4.If CKE High occurs during a pipelined read cycle, the DQ bus will remain active (Low Z). If CKE High occurs during a write cycle, the buswill remain in High Z.5. X = Don’t Care; H = Logic High; L = Logic Low; Bx = High = All Byte Write signals are high; Bx = Low = One or more Byte/Writesignals are Low6.All inputs, except G and ZZ must meet setup and hold times of rising clock edge.7.Wait states can be inserted by setting CKE high.8.This device contains circuitry that ensures all outputs are in High Z during power-up.9. A 2-bit burst counter is incorporated.10.The address counter is incriminated for all Burst continue cycles.GS881Z18/32/36B(T/D)-xxxVGS881Z18/32/36B(T/D)-xxxVDeselectNew ReadNew WriteBurst ReadBurst WriteWRBRBWDDBBWRD BWRDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input commandcodes as indicated in the Synchronous Truth Table.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipelined and Flow Through Read/Write Control State DiagramWRPipelined and Flow Through Read Write Control State DiagramGS881Z18/32/36B(T/D)-xxxVIntermediateIntermediateIntermediateIntermediateIntermediateIntermediateHigh Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)TransitionƒInput Command CodeKeyTransitionIntermediate State (N+1)Notes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateIntermediate ƒn n+1n+2n+3ƒƒƒCurrent State and Next State Definition for Pipeline Mode Data I/O State DiagramNext StateStatePipeline Mode Data I/O State DiagramGS881Z18/32/36B(T/D)-xxxVFlow Through Mode Data I/O State Diagram High Z (Data In)Data Out (Q Valid)High Z B W B R B DRW RWDDCurrent State (n)Next State (n+1)TransitionƒInput Command CodeKeyNotes:1. The Hold command (CKE Low) is notshown because it prevents any state change.2. W, R, B, and D represent input command codes as indicated in the Truth Tables.Clock (CK)CommandCurrent StateNext Stateƒnn+1n+2n+3ƒƒƒCurrent State and Next State Definition for: Pipeline and Flow through Read Write Control State DiagramGS881Z18/32/36B(T/D)-xxxVBurst CyclesAlthough NBT RAMs are designed to sustain 100% bus bandwidth by eliminating turnaround cycle when there is transition from read to write, multiple back-to-back reads or writes may also be performed. NBT SRAMs provide an on-chip burst address generator that can be utilized, if desired, to further simplify burst read or write implementations. The ADV control pin, when driven high, commands the SRAM to advance the internal address counter and use the counter generated address to read or write the SRAM. The starting address for the first cycle in a burst cycle series is loaded into the SRAM by driving the ADV pin low, into Load mode.Burst OrderThe burst address counter wraps around to its initial state after four addresses (the loaded address and three more) have beenaccessed. The burst sequence is determined by the state of the Linear Burst Order pin (LBO). When this pin is low, a linear burst sequence is selected. When the RAM is installed with the LBO pin tied high, Interleaved burst sequence is selected. See the tables below for details.Mode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down ControlZZL or NC Active HStandby, I DD = I SBNote:There is a pull-up device on the FT pin and a pull-down device on the ZZ pin, so this input pin can be unconnected and the chip will operate in the default states as specified in the above table.Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS881Z18/32/36B(T/D)-xxxVSleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by it’s internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after ZZ recovery time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a high state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode Timing DiagramtZZRtZZHtZZStKLtKHtKCCKZZDesigning for CompatibilityThe GSI NBT SRAMs offer users a configurable selection between Flow Through mode and Pipelinemode via the FT signal found on Pin 14. Not all vendors offer this option, however most mark Pin 14 as V DD or V DDQ on pipelined parts and V SS on flow through parts. GSI NBT SRAMs are fully compatible with these sockets.Pin 66, a No Connect (NC) on GSI’s GS8160Z18/36 NBT SRAM, the Parity Error open drain output on GSI’s GS881Z18/36B NBT SRAM, is often marked as a power pin on other vendor’s NBT compatible SRAMs. Specifically, it is marked V DD or V DDQ on pipelined parts and V SS on flow through parts. Users of GSI NBT devices who are not actually using the ByteSafe™ parity feature may want to design the board site for the RAM with Pin 66 tied high through a 1k ohm resistor in Pipeline modeapplications or tied low in Flow Through mode applications in order to keep the option to use non-configurable devices open.Absolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage on V DDQ Pins –0.5 to V DDV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCGS881Z18/32/36B(T/D)-xxxVNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage Ranges (1.8 V/2.5 V Version)ParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD1 1.7 1.82.0V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 1.8 V V DDQ I/O Supply Voltage V DDQ1 1.7 1.8V DD V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.5V DDVNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS881Z18/32/36B(T/D)-xxxVV DDQ2 & V DDQ1 Range Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low VoltageV IL–0.3—0.3*V DDV1Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceFigure 1Input high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS881Z18/32/36B(T/D)-xxxVDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA FT, ZZ Input Current I IN V DD ≥ V IN ≥ 0 V –100 uA 100 uA Output Leakage CurrentI OLOutput Disable, V OUT = 0 to V DD–1 uA1 uADC Output Characteristics (1.8 V/2.5 V Version)ParameterSymbolTest ConditionsMinMax1.8 V Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V —2.5 V Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V1.7 V —1.8 V Output Low Voltage V OL1I OL = 4 mA —0.4 V2.5 V Output Low VoltageV OL2I OL = 8 mA—0.4 VGS881Z18/32/36B(T/D)-xxxVOperating CurrentsParameterTest ConditionsModeSymbol-250-200-150Unit0to 70°C–40 to 85°C0to 70°C –40to 85°C 0 to 70°C –40to 85°COperating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x32/x36)PipelineI DD I DDQ 200302203017025190251402016020mA Flow Through I DD I DDQ 160251802514020160201301515015mA (x18)PipelineI DD I DDQ 185152051515515175151301015010mA Flow ThroughI DD I DDQ 1451516515130101501012081408mA Standby Current ZZ ≥ V DD – 0.2 V —Pipeline I SB 405040504050mA Flow Through I SB 405040504050mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—PipelineI DD 859075806065mA Flow Through I DD606550555055mA1.I DD and I DDQ apply to any combination of V DD1, V DD2, V DDQ1, and V DDQ2 operation.2.All parameters listed are worst case scenario.。

GS864218B-200V资料

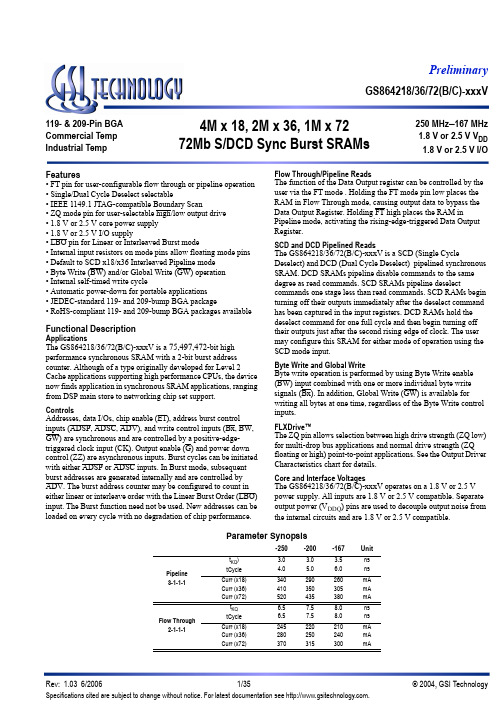

PreliminaryGS864218/36/72(B/C)-xxxV4M x 18, 2M x 36, 1M x 7272Mb S/DCD Sync Burst SRAMs250 MHz –167 MHz 1.8 V or 2.5 V V DD 1.8 V or 2.5 V I/O119- & 209-Pin BGA Commercial Temp Industrial Temp Features• FT pin for user-configurable flow through or pipeline operation • Single/Dual Cycle Deselect selectable• IEEE 1149.1 JTAG-compatible Boundary Scan• ZQ mode pin for user-selectable high/low output drive • 1.8 V or 2.5 V core power supply • 1.8 V or 2.5 V I/O supply• LBO pin for Linear or Interleaved Burst mode• Internal input resistors on mode pins allow floating mode pins • Default to SCD x18/x36 Interleaved Pipeline mode • Byte Write (BW) and/or Global Write (GW) operation • Internal self-timed write cycle• Automatic power-down for portable applications • JEDEC-standard 119- and 209-bump BGA package• RoHS-compliant 119- and 209-bump BGA packages availableFunctional DescriptionApplicationsThe GS864218/36/72(B/C)-xxxV is a 75,497,472-bit high performance synchronous SRAM with a 2-bit burst address counter. Although of a type originally developed for Level 2Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support.ControlsAddresses, data I/Os, chip enable (E1), address burst control inputs (ADSP, ADSC, ADV), and write control inputs (Bx, BW, GW) are synchronous and are controlled by a positive-edge-triggered clock input (CK). Output enable (G) and power down control (ZZ) are asynchronous inputs. Burst cycles can be initiated with either ADSP or ADSC inputs. In Burst mode, subsequent burst addresses are generated internally and are controlled by ADV. The burst address counter may be configured to count in either linear or interleave order with the Linear Burst Order (LBO) input. The Burst function need not be used. New addresses can be loaded on every cycle with no degradation of chip performance.Flow Through/Pipeline ReadsThe function of the Data Output register can be controlled by the user via the FT mode . Holding the FT mode pin low places the RAM in Flow Through mode, causing output data to bypass the Data Output Register. Holding FT high places the RAM inPipeline mode, activating the rising-edge-triggered Data Output Register.SCD and DCD Pipelined ReadsThe GS864218/36/72(B/C)-xxxV is a SCD (Single CycleDeselect) and DCD (Dual Cycle Deselect) pipelined synchronous SRAM. DCD SRAMs pipeline disable commands to the same degree as read commands. SCD SRAMs pipeline deselectcommands one stage less than read commands. SCD RAMs begin turning off their outputs immediately after the deselect command has been captured in the input registers. DCD RAMs hold the deselect command for one full cycle and then begin turning off their outputs just after the second rising edge of clock. The user may configure this SRAM for either mode of operation using the SCD mode input.Byte Write and Global WriteByte write operation is performed by using Byte Write enable (BW) input combined with one or more individual byte write signals (Bx). In addition, Global Write (GW) is available for writing all bytes at one time, regardless of the Byte Write control inputs.FLXDrive™The ZQ pin allows selection between high drive strength (ZQ low) for multi-drop bus applications and normal drive strength (ZQ floating or high) point-to-point applications. See the Output Driver Characteristics chart for details.Core and Interface VoltagesThe GS864218/36/72(B/C)-xxxV operates on a 1.8 V or 2.5 V power supply. All inputs are 1.8 V or 2.5 V compatible. Separate output power (V DDQ ) pins are used to decouple output noise from the internal circuits and are 1.8 V or 2.5 V compatible.Parameter Synopsis-250-200-167UnitPipeline 3-1-1-1KQ tCycle 4.0 5.0 6.0ns Curr (x18)Curr (x36)Curr (x72)340410520290350435260305380mA mA mA Flow Through 2-1-1-1t KQ tCycle 6.56.57.57.58.08.0ns ns Curr (x18)Curr (x36)Curr (x72)245280370220250315210240300mA mA mAGS864218/36/72(B/C)-xxxV209-Bump BGA—x72 Common I/O—Top View (Package C)1234567891011A DQ G DQ G A E2ADSP ADSC ADV E3A DQB DQ B AB DQ G DQ G BC BG NC BW A BB BF DQ B DQ B BC DQ G DQ G BH BD NC E1NC BE BA DQ B DQ B CD DQ G DQ G V SS NC NC G GW NC V SS DQ B DQ B DE DQP G DQP C V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQPF DQP B EF DQ C DQ C V SS V SS V SS ZQ V SS V SS V SS DQ F DQ F FG DQ C DQ C V DDQ V DDQ V DD MCH V DD V DDQ V DDQ DQ F DQ F GH DQ C DQ C V SS V SS V SS MCL V SS V SS V SS DQ F DQ F H J DQ C DQ C V DDQ V DDQ V DD MCL V DD V DDQ V DDQ DQ F DQ F J K NC NC CK NC V SS MCL V SS NC NC NC NC K L DQ H DQ H V DDQ V DDQ V DD FT V DD V DDQ V DDQ DQ A DQ A L M DQ H DQ H V SS V SS V SS MCL V SS V SS V SS DQ A DQ A M N DQ H DQ H V DDQ V DDQ V DD SCD V DD V DDQ V DDQ DQ A DQ A N P DQ H DQ H V SS V SS V SS ZZ V SS V SS V SS DQ A DQ A P R DQP D DQP H V DDQ V DDQ V DD V DD V DD V DDQ V DDQ DQP A DQP E R T DQ D DQ D V SS NC NC LBO NC NC V SS DQ E DQ E T U DQ D DQ D A A A A A A A DQ E DQ E U V DQ D DQ D A A A A1A A A DQ E DQ E V W DQ D DQ D TMS TDI A A0A TDO TCK DQ E DQ E W11 x 19 Bump BGA—14 x 22 mm2 Body—1 mm Bump PitchGS864218/36/72(B/C)-xxxVGS864272C-xxxV 209-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset Inputs.An IAddress InputsDQ A DQ B DQ C DQ D DQ E DQ F DQ G DQ H I/O Data Input and Output pinsB A , B B I Byte Write Enable for DQ A , DQ B I/Os; active low BC ,BD I Byte Write Enable for DQ C , DQ D I/Os; active low BE , BF , BG ,B HI Byte Write Enable for DQ E , DQ F , DQ G , DQ H I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highGW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low E 3I Chip Enable; active low E 2I Chip Enable; active high G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep Mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowSCD I Single Cycle Deselect/Dual Cycle Deselect Mode ControlMCH IMust Connect High MCL Must Connect Low BW I Byte Enable; active lowZQ I FLXDrive Output Impedance Control(Low = Low Impedance [High Drive], High = High Impedance [Low Drive])TMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCKIScan Test ClockGS864218/36/72(B/C)-xxxVV DD I Core power supply V SS I I/O and Core Ground V DDQIOutput driver power supplyGS864272C-xxxV 209-Bump BGA Pin Description (Continued)SymbolTypeDescriptionGS864218/36/72(B/C)-xxxV119-Bump BGA—x36 Common I/O—Top View 1234567A V DDQ A A ADSP A A V DDQ A B NC A A ADSC A A NC B C NC A A V DD A A NC C D DQ DQP V SS ZQ V SS DQP B DQ B D E DQ DQ V SS E1V SS DQ B DQ B E F V DDQ DQ V SS G V SS DQ B V DDQ F G DQ DQ BC ADV BB DQ B DQ B G H DQ DQ V SS GW V SS DQ B DQ B H J V DDQ V DD NC V DD NC V DD V DDQ J K DQ D DQ D V SS CK V SS DQ A DQ A K L DQ D DQ D BD SCD BA DQ A DQ A L M V DDQ DQ D V SS BW V SS DQ A V DDQ M N DQ D DQ D V SS A1V SS DQ A DQ A N P DQ D DQP D V SS A0V SS DQP A DQ A P R NC A LBO V DD FT A NC R T NC A A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump Pitch(Package B)C C C C C C2C C CGS864218/36/72(B/C)-xxxV119-Bump BGA—x18 Common I/O—Top View 1234567A V DDQ A A ADSP A A V DDQ A B NC A A ADSC A A NC B C NC A A V DD A A NC C D DQ B NC V SS ZQ V SS DQP A NC D E NC DQ B V SS E1V SS NC DQ A E F V DDQ NC V SS G V SS DQ A V DDQ F G NC DQ B BB ADV NC NC DQ A G H DQ B NC V SS GW V SS DQ A NC H J V DDQ V DD NC V DD NC V DD V DDQ J K NC DQ B V SS CK V SS NC DQ A K L DQ B NC NC SCD BA DQ A NC L M V DDQ DQ B V SS BW V SS NC V DDQ M N DQ B NC V SS A1V SS DQ A NC N P NC DQP B V SS A0V SS NC DQ A P R NC A LBO V DD FT A NC R T A A A A A A ZZ T UV DDQTMSTDITCKTDONCV DDQU7 x 17 Bump BGA—14 x 22 mm 2 Body—1.27 mm Bump Pitch(Package B)GS864218/36/72(B/C)-xxxVGS864218/36B-xxxV 119-Bump BGA Pin DescriptionSymbolTypeDescriptionA 0, A 1I Address field LSBs and Address Counter Preset InputsAn I Address Inputs DQ A DQ B DQ C DQ D I/O Data Input and Output pinsB A , B B , BC , B DI Byte Write Enable for DQ A , DQ B , DQ C , DQ D I/Os; active lowNC —No ConnectCK I Clock Input Signal; active highBW I Byte Write—Writes all enabled bytes; active low GW I Global Write Enable—Writes all bytes; active lowE 1I Chip Enable; active low G I Output Enable; active lowADV I Burst address counter advance enable; active low ADSP, ADSCI Address Strobe (Processor, Cache Controller); active lowZZ I Sleep mode control; active high FT I Flow Through or Pipeline mode; active low LBO I Linear Burst Order mode; active lowZQ I FLXDrive Output Impedance Control (Low = Low Impedance [High Drive], High = High Impedance [LowDrive])SCD I Single Cycle Deselect/Dual Cyle Deselect Mode ControlTMS I Scan Test Mode Select TDI I Scan Test Data In TDO O Scan Test Data Out TCK I Scan Test Clock V DD I Core power supply V SS I I/O and Core Ground V SS I I/O and Core Ground V DDQIOutput driver power supplyGS864218/36/72(B/C)-xxxVA1A0A0A1D0D1Q1Q0Counter LoadD QDQRegisterRegisterDQRegisterDQRegisterDQRegisterD QRegisterD QRegisterD QRegisterDQR e g i s t e rDQRegisterA0–AnLBO ADV CK ADSC ADSP GW BW E 1GZZPower Down ControlMemory Array36364AQDE 2E 3DQx1–DQx9Note: Only x36 version shown for simplicity.B AB BB CB DFT GS864218/36/72-xxxV Block DiagramMode Pin FunctionsMode NamePin NameStateFunctionBurst Order Control LBO L Linear Burst H Interleaved Burst Output Register Control FT L Flow Through H or NC Pipeline Power Down Control ZZ L or NC Active H Standby, I DD = I SB Single/Dual Cycle Deselect Control SCD L Dual Cycle Deselect H or NC Single Cycle Deselect FLXDrive Output Impedance ControlZQL High Drive (Low Impedance)H or NCLow Drive (High Impedance)GS864218/36/72(B/C)-xxxVNote:There are pull-up devices on the ZQ, SCD, and FT pins and a pull-down device on the ZZ pin, so those input pins can be unconnected and the chip will operate in the default states as specified in the above tables.Note:The burst counter wraps to initial state on the 5th clock.Note:The burst counter wraps to initial state on the 5th clock.Linear Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 011011003rd address 101100014th address11000110Interleaved Burst SequenceA[1:0]A[1:0]A[1:0]A[1:0]1st address 000110112nd address 010011103rd address 101100014th address11100100Burst Counter SequencesBPR 1999.05.18GS864218/36/72(B/C)-xxxVByte Write Truth TableFunctionGWBWB AB BB CB DNotesRead H H X X X X 1Read H L H H H H 1Write byte a H L L H H H 2, 3Write byte b H L H L H H 2, 3Write byte c H L H H L H 2, 3, 4Write byte d H L H H H L 2, 3, 4Write all bytes H L L L L L 2, 3, 4Write all bytesLXXXXX1.All byte outputs are active in read cycles regardless of the state of Byte Write Enable inputs.2.Byte Write Enable inputs B A , B B , B C , and/or B D may be used in any combination with BW to write single or multiple bytes.3.All byte I/Os remain High-Z during all write operations regardless of the state of Byte Write Enable inputs.4.Bytes “C ” and “D ” are only available on the x36 version.Synchronous Truth TableOperationAddress UsedState Diagram Key 5E 1E 2ADSP ADSCADVW 3DQ 4Deselect Cycle, Power Down None X H X X L X X High-Z Deselect Cycle, Power Down None X L F L X X X High-Z Deselect Cycle, Power Down None X L F H L X X High-Z Read Cycle, Begin Burst External R L T L X X X Q Read Cycle, Begin Burst External R L T H L X F Q Write Cycle, Begin Burst External W L T H L X T D Read Cycle, Continue Burst Next CR X X H H L F Q Read Cycle, Continue Burst Next CR H X X H L F Q Write Cycle, Continue Burst Next CW X X H H L T D Write Cycle, Continue Burst Next CWH X X H L T D Read Cycle, Suspend Burst Current X X H H H F Q Read Cycle, Suspend Burst Current H X X H H F Q Write Cycle, Suspend BurstCurrentXXHHHTDWrite Cycle, Suspend Burst Current H X X H H T D 1.X = Don’t Care, H = High, L = Low2. E = T (True) if E 2 = 1 and E 3 = 0; E = F (False) if E 2 = 0 or E 3 = 13.W = T (True) and F (False) is defined in the Byte Write Truth Table preceding.4.G is an asynchronous input. G can be driven high at any time to disable active output drivers. G low can only enable active drivers (shownas “Q” in the Truth Table above).5.All input combinations shown above are tested and supported. Input combinations shown in gray boxes need not be used to accomplishbasic synchronous or synchronous burst operations and may be avoided for simplicity.6.Tying ADSP high and ADSC low allows simple non-burst synchronous operations. See BOLD items above.7.Tying ADSP high and ADV low while using ADSC to load new addresses allows simple burst operations. See ITALIC items above.GS864218/36/72(B/C)-xxxVFirst WriteFirst ReadBurst WriteBurst ReadDeselect R WCRCWXXWRRWRXXX S i m p l e S y n c h r o n o u s O p e r a t i o nS i m p l e B u r s t S y n c h r o n o u s O p e r a t i o nCR RCWCRCRNotes:1.The diagram shows only supported (tested) synchronous state transitions. The diagram presumes G is tied low.2.The upper portion of the diagram assumes active use of only the Enable (E1) and Write (B A , B B , B C , B D , BW, and GW) control inputs, andthat ADSP is tied high and ADSC is tied low.3.The upper and lower portions of the diagram together assume active use of only the Enable, Write, and ADSC control inputs andassumes ADSP is tied high and ADV is tied low.GS864218/36/72(B/C)-xxxVSimplified State DiagramFirst WriteFirst ReadBurst WriteBurst ReadDeselectR WCRCWXXWRRWRXXX CRR CW CRCRW CWW CWNotes:1.The diagram shows supported (tested) synchronous state transitions plus supported transitions that depend upon the use of G.e of “Dummy Reads” (Read Cycles with G High) may be used to make the transition from read cycles to write cycles without passingthrough a Deselect cycle. Dummy Read cycles increment the address counter just like normal read cycles.3.Transitions shown in grey tone assume G has been pulsed high long enough to turn the RAM’s drivers off and for incoming data to meetData Input Set Up Time.GS864218/36/72(B/C)-xxxVSimplified State Diagram with GAbsolute Maximum Ratings(All voltages reference to V SS )SymbolDescriptionValueUnitV DD Voltage on V DD Pins –0.5 to 4.6V V DDQ Voltage on V DDQ Pins –0.5 to V DDV V I/O Voltage on I/O Pins –0.5 to V DDQ +0.5 (≤ 4.6 V max.)V V IN Voltage on Other Input Pins –0.5 to V DD +0.5 (≤ 4.6 V max.)V I IN Input Current on Any Pin +/–20mA I OUT Output Current on Any I/O Pin +/–20mA P D Package Power Dissipation 1.5WT STG Storage Temperature –55 to 125o C T BIASTemperature Under Bias–55 to 125oCGS864218/36/72(B/C)-xxxVNote:Permanent damage to the device may occur if the Absolute Maximum Ratings are exceeded. Operation should be restricted to Recommended Operating Conditions. Exposure to conditions exceeding the Absolute Maximum Ratings, for an extended period of time, may affect reliability of this component. Power Supply Voltage Ranges (1.8 V/2.5 V Version)ParameterSymbolMin.Typ.Max.UnitNotes1.8 V Supply Voltage V DD1 1.7 1.82.0V 2.5 V Supply Voltage V DD2 2.3 2.5 2.7V 1.8 V V DDQ I/O Supply Voltage V DDQ1 1.7 1.8V DD V 2.5 V V DDQ I/O Supply VoltageV DDQ22.32.5V DDVNotes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.GS864218/36/72(B/C)-xxxVV DDQ2 & V DDQ1 Range Logic LevelsParameterSymbolMin.Typ.Max.UnitNotesV DD Input High Voltage V IH 0.6*V DD —V DD + 0.3V 1V DD Input Low VoltageV IL–0.3—0.3*V DDV1Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.Recommended Operating TemperaturesParameterSymbolMin.Typ.Max.UnitNotesAmbient Temperature (Commercial Range Versions)T A 02570°C 2Ambient Temperature (Industrial Range Versions)T A–402585°C2Notes:1.The part numbers of Industrial Temperature Range versions end the character “I”. Unless otherwise noted, all performance specifica-tions quoted are evaluated for worst case in the temperature range marked on the device.2.Input Under/overshoot voltage must be –2 V > Vi < V DDn +2 V not to exceed 4.6 V maximum, with a pulse width not to exceed 20% tKC.20% tKCV SS – 2.0 V50%V SS V IHUndershoot Measurement and TimingOvershoot Measurement and Timing20% tKCV DD + 2.0 V50%V DDV ILCapacitanceo C, f = 1 MH Z , V DD ParameterSymbolTest conditionsTyp.Max.UnitInput Capacitance C IN V IN = 0 V 45pF Input/Output Capacitance C I/OV OUT = 0 V67pFNote:These parameters are sample tested.(T A = 25= 2.5 V)AC Test ConditionsParameterConditionsDQV DDQ/250Ω30pF *Output Load 1* Distributed Test Jig CapacitanceFigure 1Input high level V DD – 0.2 V Input low level 0.2 V Input slew rate 1 V/ns Input reference level V DD /2Output reference levelV DDQ /2Output loadFig. 11.Include scope and jig capacitance.2.Test conditions as specified with output loading as shown in Fig. 1unless otherwise noted.3.Device is deselected as defined by the Truth Table. GS864218/36/72(B/C)-xxxVDC Electrical CharacteristicsParameterSymbolTest ConditionsMinMaxInput Leakage Current (except mode pins)I IL V IN = 0 to V DD –1 uA 1 uA FT, SCD, ZQ, ZZ Input Current I IN V DD ≥ V IN ≥ 0 V –100 uA 100 uA Output Leakage CurrentI OLOutput Disable, V OUT = 0 to V DD–1 uA1 uADC Output Characteristics (1.8 V/2.5 V Version)ParameterSymbolTest ConditionsMinMax1.8 V Output High Voltage V OH1I OH = –4 mA, V DDQ = 1.6 V V DDQ – 0.4 V —2.5 V Output High Voltage V OH2I OH = –8 mA, V DDQ = 2.375 V1.7 V —1.8 V Output Low Voltage V OL1I OL = 4 mA —0.4 V2.5 V Output Low VoltageV OL2I OL = 8 mA—0.4 VGS864218/36/72(B/C)-xxxVOperating CurrentsParameterTest ConditionsModeSymbol-250-200-167Unit0to 70°C –40 to 85°C 0to 70°C –40to 85°C 0 to 70°C –40to 85°C Operating CurrentDevice Selected; All other inputs ≥V IH o r ≤ V IL Output open(x72)PipelineI DD I DDQ 460604806038550405503404036040mA Flow Through I DD I DDQ 330403404028530295302703028030mA (x32/x36)Pipeline I DD I DDQ 360503805031040330402703529035mA Flow Through I DD I DDQ 255252752523020250202202024020mA (x18)PipelineI DD I DDQ 315253352527020290202402026020mA Flow Through I DD I DDQ 230152501520515225151951521515mA Standby Current ZZ ≥ V DD – 0.2 V —PipelineI SB 100120100120100120mA Flow Through I SB 100120100120100120mA Deselect CurrentDevice Deselected; All other inputs ≥ V IH or ≤ V IL—PipelineI DD 140155130146125140mA Flow ThroughI DD125140120135120135mA1.I DD and I DDQ apply to any combination of V DD and V DDQ operation.2.All parameters listed are worst case scenario.AC Electrical CharacteristicsParameter Symbol -250-200-167Unit Min Max Min Max Min Max PipelineClock Cycle Time tKC 4.0— 5.0— 6.0—ns Clock to Output ValidtKQ — 3.0— 3.0— 3.5ns Clock to Output Invalid tKQX 1.5— 1.5— 1.5—ns Clock to Output in Low-ZtLZ 1 1.5— 1.5— 1.5—ns Setup time tS 1.5— 1.5— 1.5—ns Hold time tH 0.2—0.4—0.5—ns Flow ThroughClock Cycle Time tKC 6.5—7.5—8.0—ns Clock to Output ValidtKQ — 6.5—7.5—8.0ns Clock to Output Invalid tKQX 3.0— 3.0— 3.0—ns Clock to Output in Low-ZtLZ 1 3.0— 3.0— 3.0—ns Setup time tS 1.5— 1.5— 1.5—ns Hold time tH 0.5—0.5—0.5—ns Clock HIGH Time tKH 1.3— 1.3— 1.3—ns Clock LOW Time tKL 1.7— 1.7— 1.7—ns Clock to Output in High-Z (x18/x36)tHZ 1 1.5 2.5 1.5 3.0 1.5 3.0ns Clock to Output in High-Z (x72)tHZ 1 1.5 3.0 1.5 3.0 1.5 3.0ns G to Output Valid (x18/x36)tOE — 2.5— 3.0— 3.5ns G to Output Valid(x72)tOE — 3.0— 3.0— 3.5ns G to output in Low-Z tOLZ 10—0—0—ns G to output in High-Z(x18/36)tOHZ 1— 2.5— 3.0— 3.0ns G to output in High-Z(x72)tOHZ 1— 3.0— 3.0— 3.0ns ZZ setup time tZZS 25—5—5—ns ZZ hold time tZZH 21—1—1—ns ZZ recoverytZZR20—20—20—nsGS864218/36/72(B/C)-xxxVNotes:1.These parameters are sampled and are not 100% tested.2.ZZ is an asynchronous signal. However, in order to be recognized on any given clock cycle, ZZ must meet the specified setup and holdtimes as specified above.GS864218/36/72(B/C)-xxxVPipeline Mode Timing (SCD)Begin Read A Cont Cont Deselect Write B Read C Read C+1Read C+2Read C+3ContDeselecttHZtKQX tKQtLZtHtStOHZtOEtHtStHtStHtStHtStHtStStHtStHtStHtSBurst ReadtKCtKL tKH Single Write Single ReadQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCDeselected with E1E1 masks ADSPE2 and E3 only sampled with ADSP and ADSCADSC initiated readCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS864218/36/72(B/C)-xxxVFlow Through Mode Timing (SCD)Begin Read A ContCont Write B Read C Read C+1Read C+2Read C+3Read C Cont DeselecttHZtKQXtKQ tLZtH tStOHZtOEtHtS tHtS tHtStHtS tHtS tHtStHtS tHtS tH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSCADSC initiated readDeselected with E1Fixed HighCK ADSPADSCADVA0–AnGWBWBa–BdE1E2E3GDQa–DQdGS864218/36/72(B/C)-xxxVPipeline Mode Timing (DCD)Begin Read A Cont Deselect Deselect Write BRead C Read C+1Read C+2Read C+3Cont Deselect DeselecttHZtKQXtKQtLZtHtStOHZtOEtHtStHtStHtStH tStHtStStHtStHtStHtStKCtKL tKHQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)ABCHi-ZDeselected with E1E2 and E3 only sampled with ADSCADSC initiated readCK ADSPADSCADVAo–AnGWBWBa–BdE1E2E3GDQa–DQdGS864218/36/72(B/C)-xxxVFlow Through Mode Timing (DCD)Begin Read A ContDeselect Write B Read C Read C+1Read C+2Read C+3Read C DeselecttHZtKQX tLZtH tStOHZtOE tKQtHtS tHtS tHtStH tStHtS tHtStHtS tHtS tH tStH tS tHtS tKCtKL tKHABCQ(A)D(B)Q(C)Q(C+1)Q(C+2)Q(C+3)Q(C)E2 and E3 only sampled with ADSP and ADSCE1 masks ADSPADSC initiated readDeselected with E1E1 masks ADSPFixed HighCK ADSPADSCADVAo–AnGWBWBa–BdE1E2E3GDQa–DQdGS864218/36/72(B/C)-xxxVSleep ModeDuring normal operation, ZZ must be pulled low, either by the user or by its internal pull down resistor. When ZZ is pulled high, the SRAM will enter a Power Sleep mode after 2 cycles. At this time, internal state of the SRAM is preserved. When ZZ returns to low, the SRAM operates normally after ZZ recovery time.Sleep mode is a low current, power-down mode in which the device is deselected and current is reduced to I SB 2. The duration of Sleep mode is dictated by the length of time the ZZ is in a High state. After entering Sleep mode, all inputs except ZZ become disabled and all outputs go to High-Z The ZZ pin is an asynchronous, active high input that causes the device to enter Sleep mode. When the ZZ pin is driven high, I SB 2 is guaranteed after the time tZZI is met. Because ZZ is an asynchronous input, pending operations or operations in progress may not be properly completed if ZZ is asserted. Therefore, Sleep mode must not be initiated until valid pending operations are completed. Similarly, when exiting Sleep mode during tZZR, only a Deselect or Read commands may be applied while the SRAM is recovering from Sleep mode.Sleep Mode TimingtZZRtZZHtZZSHoldSetup tKLtKHtKCCKADSP ADSCZZApplication TipsSingle and Dual Cycle DeselectSCD devices (like this one) force the use of “dummy read cycles” (read cycles that are launched normally, but that are ended with the output drivers inactive) in a fully synchronous environment. Dummy read cycles waste performance, but their use usually assures there will be no bus contention in transitions from reads to writes or between banks of RAMs. DCD SRAMs do not waste bandwidth on dummy cycles and are logically simpler to manage in a multiple bank application (wait states need not be inserted at bank address boundary crossings), but greater care must be exercised to avoid excessive bus contention.JTAG Port OperationOverviewThe JTAG Port on this RAM operates in a manner that is compliant with IEEE Standard 1149.1-1990, a serial boundary scan interface standard (commonly referred to as JTAG). The JTAG Port input interface levels scale with V DD . The JTAG output drivers are powered by V DDQ .Disabling the JTAG PortIt is possible to use this device without utilizing the JTAG port. The port is reset at power-up and will remain inactive unless clocked. TCK, TDI, and TMS are designed with internal pull-up circuits.To assure normal operation of the RAM with the JTAG Port unused, TCK, TDI, and TMS may be left floating or tied to either V DD or V SS . TDO should be left unconnected.JTAG Pin DescriptionsPinPin NameI/ODescriptionTCK Test Clock In Clocks all TAP events. All inputs are captured on the rising edge of TCK and all outputs propagate from the falling edge of TCK.TMSTest Mode SelectInThe TMS input is sampled on the rising edge of TCK. This is the command input for the TAP controller state machine. An undriven TMS input will produce the same result as a logic one input level.TDI Test Data In InThe TDI input is sampled on the rising edge of TCK. This is the input side of the serial registers placed between TDI and TDO. The register placed between TDI and TDO is determined by the state of the TAP Controller state machine and the instruction that is currently loaded in the TAP Instruction Register (refer to the TAP Controller State Diagram). An undriven TDI pin will produce the same result as a logic one input level.TDO Test Data OutOut Output that is active depending on the state of the TAP state machine. Output changes inresponse to the falling edge of TCK. This is the output side of the serial registers placed betweenTDI and TDO.This device does not have a TRST (TAP Reset) pin. TRST is optional in IEEE 1149.1. The Test-Logic-Reset state is entered while TMS is held high for five rising edges of TCK. The TAP Controller is also reset automaticly at power-up.GS864218/36/72(B/C)-xxxVJTAG Port RegistersOverviewThe various JTAG registers, refered to as Test Access Port orTAP Registers, are selected (one at a time) via the sequences of 1s and 0s applied to TMS as TCK is strobed. Each of the TAP Registers is a serial shift register that captures serial input data on the rising edge of TCK and pushes serial data out on the next falling edge of TCK. When a register is selected, it is placed between the TDI and TDO pins.Instruction RegisterThe Instruction Register holds the instructions that are executed by the TAP controller when it is moved into the Run, Test/Idle, or the various data register states. Instructions are 3 bits long. The Instruction Register can be loaded when it is placed between the TDI and TDO pins. The Instruction Register is automatically preloaded with the IDCODE instruction at power-up or whenever the controller is placed in Test-Logic-Reset state.Bypass RegisterThe Bypass Register is a single bit register that can be placed between TDI and TDO. It allows serial test data to be passed through the RAM’s JTAG Port to another device in the scan chain with as little delay as possible.Boundary Scan RegisterThe Boundary Scan Register is a collection of flip flops that can be preset by the logic level found on the RAM’s input or I/O pins. The flip flops are then daisy chained together so the levels found can be shifted serially out of the JTAG Port’s TDO pin. The Boundary Scan Register also includes a number of place holder flip flops (always set to a logic 1). The relationship between the device pins and the bits in the Boundary Scan Register is described in the Scan Order Table following. The Boundary Scan Register, under the control of the TAP Controller, is loaded with the contents of the RAMs I/O ring when the controller is inCapture-DR state and then is placed between the TDI and TDO pins when the controller is moved to Shift-DR state. SAMPLE-Z, SAMPLE/PRELOAD and EXTEST instructions can be used to activate the Boundary Scan Register.。

SL2.2S规格书,usb HUB大全,替换FE1.1S,GL850,GL852,PL2586

USB2.0 HUB控制器集成电路USB 2.0 HIGH SPEED 4-PORT HUB CONTROLLERSL2.2s数据手册Data Sheet内容目录第一章管脚分配 (3)1.1 SL2.2S管脚图 (3)1.2 SL2.2S管脚定义 (3)第二章 功能叙述 (5)2.1综述 (5)2.2指示灯 (5)2.2.1单灯方案 (5)2.2.2多灯方案 (6)2.2.3 LED指示定义 (6)2.3过流保护 (6)2.4充电支持 (6)2.5I2C接口 (7)2.6EEPROM设置 (7)第三章电气特性 (8)3.1极限工作条件 (8)3.2工作范围 (8)3.3直流电特性 (8)3.4HS/FS/LS电气特性 (8)3.5ESD特性 (8)附录一封装 (9)表格目录表格1: 端口LED定义 (6)表格 2 : ACTIVE LED定义 (6)表格3:EEPROM数据结构定义 (7)表格4: 最大额定值 (8)表格5: 工作范围 (8)表格6: 直流电特性 (8)插图目录图1:SSOP28 管脚图 (3)图2:单灯方案配置 (5)图3: 5灯方案配置 ............................................................................... (6)图 4:附录 封装图 ................................................................................... .9第一章管脚分配1.1SL2.2s管脚图图1:SSOP28 管脚图1.2SL2.2s管脚定义管脚名称28Die IO类型定义Pin#VSS 1 P 芯片地XOUT 2 O晶振PAD XIN 3 IDM4 4 B下行口4的USB信号DP4 5 BDM3 6 B下行口3的USB信号DP3 7 BDM2 8 B下行口2的USB信号DP2 9 BDM1 10 B下行口1的USB信号DP1 11 BVDD18 12 P 模拟1.8vVDD33 13 P 模拟3.3v - 14 NCUDM 15 B上行口的USB信号UDP 16 BRESET_N 17 I,Pu 芯片外部复位输入- 18 NCPSELF 19 I,Pu 高为自供电,低为总线供电VDD5 20 P 5v输入VDD33 21 P 3.3v输出DRV 22 B,Pu 点灯驱动信号LED1 23 B,Pu 点灯驱动信号LED2 24 B,Pu 点灯驱动信号PWRN 25 B,Pu 下行口电源输出控制,低有效OVCRN/SDA 26 B,PuI2C SDA数据线,内部上拉;芯片初始化完成后作为过流保护输入脚,低有效SCL 27 B,Pu I2C SCL时钟输出VDD18 28 P 数字1.8v注释:O,输出;I 输入;B 双向;P 电源/接地;Pu 上拉;Pd 下拉;NC 悬空;第二章 功能叙述2.1综述SL2.2s 是一颗高集成度,高性能,低功耗的USB2.0集线器主控芯片;该芯片采用STT 技术,单电源供电方式,芯片供电电压为5v , 内部集成5V 转3.3V,只需在外部电源添加滤波电容;芯片自带复位电路,低功耗技术让他更加出众。

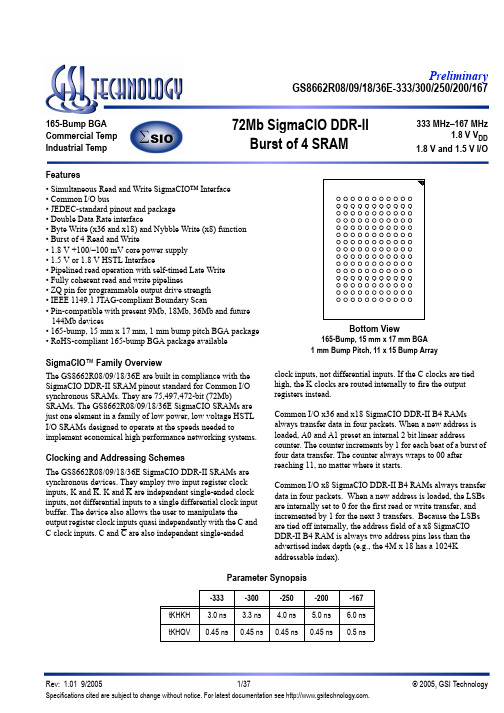

GS8662R18E-200资料