MPC17511AEPR2;中文规格书,Datasheet资料

PI2001-EVAL1;中文规格书,Datasheet资料

IntroductionThe PI2001-EVAL1 allows the user to test the basic principle and operational characteristics of an Active ORing function in a redundant power architecture, while also experiencing the benefits and value of the PI2001 solution versus conventional Active ORing solutions. The PI2001-EVAL1 evaluation board is configured to receive two independent power source inputs,per a typical redundant power architecture, through two Active ORing channels that are combined to form aredundant power output. Each channel contains a PI2001controller and an N-channel power MOSFET. The MOSFET foot print can take an SO-8 or Power SO-8 MOSFET package.Each channel is capable of up to 20 A, for high current Active ORing, above 20 A, the two channels provided on the evaluation board can be paralleled in a master /slave configuration and OR’d with a second evaluation board.The PI2001-EVAL1 evaluation board is designed withoptimized PCB layout and component placement to represent a realistic high density final design for an embedded Active ORing solution for ≤7 Vbus applications requiring up to 20 A.This evaluation board is intended as an easy and simple way to test the electrical and thermal performance of the PI2001Active ORing controller.Both dynamic and steady state testing of the PI2001 can be completed on the PI2001-EVAL1 evaluation board, in addition to using the key features of the product. Dynamic testing can be completed under a variety of system level fault conditions to check for response time to faults.This document provides basic instructions for initial start-up and configuration of the evaluation board. Further information on the functionality of the PI2001 can be found in the PI2001 product data sheet.PI2001-EVAL1Cool-ORing ™ SeriesPI2001-EVAL1 Active ORingEvaluation Board User Guide®PI2001-EVAL1 Evaluation Board featuring the Cool-ORing PI2001 Universal Active ORing controller.Cool-ORing™ SeriesThe PI2001-EVAL1 Evaluation Board is intended to acquaint the user with the benefits and features of the Cool-ORing TM PI2001Universal Active ORing controller. It is not designed to be installed in end-use equipment.Please read this document before setting up the PI2001-EVAL1Evaluation Board and refer to the PI2001 product data sheet for device specifications, functional description and characteristics.During operation, the power devices and surrounding structures can be operated safely at high temperatures.•Remove power and use caution when connecting and disconnecting test probes and interface lines to avoid inadvertent short circuits and contact with hot surfaces.•When testing electronic products always use approved safety glasses. Follow good laboratory practice and procedures.The Cool-ORing PI2001 with an external industry standard N-channel MOSFET provides a complete Active ORing solution designed for use in redundant power systemarchitectures. The PI2001 controller with N-channel MOSFET enables extremely low power loss with fast dynamic response to fault conditions, critical for high availability systems. A master /slave feature allows the paralleling of PI2001solutions for high current Active ORing requirements. The PI2001 can also drive multiple paralleled MOSFETs.The PI2001 controller with a low Rds(on) N-channel MOSFET provides very high efficiency and low power loss during steady state operation. The PI2001 controller provides an active low fault flag output to the system during excessive forward current, light load, reverse current, over-voltage,under-voltage, and over-temperature fault conditions. A temperature sensing function indicates a fault if themaximum junction temperature exceeds 160°C. The under-voltage and over-voltage thresholds are programmable via an external resistor divider.Figure 1 shows a photo of the PI2001-EVAL1 evaluation board, with two PI2001 controllers and two N-channelMOSFETs used to form the two Active ORing channels. The board is built with two identical Active ORing circuits with options and features that enable the user to fully explore thecapabilities of the PI2001 universal Active ORing controller.Figure 1 –PI2001-EVAL1 Evaluation Board (1.8" x 1.8")Terminals RatingVin1, Vin28V / 24 AVaux1, Vaux2, (R2 = R4 = 10 Ω)-0.3 V to 17.3 V / 40 mA SL1, SL2-0.3 V to 8.0 V / 10 mA FT1, FT2-0.3 V to 17.3 V / 10 mATerminal DescriptionVin1Power Source Input #1or bus input designed to accommodate up to 20 A continuous current.Vaux1Auxiliary Input Voltage #1to supply PI2001 VC power. Vaux1 should be equal to Vin1 plus 5 V or higher. See details in Auxiliary Power Supply (Vaux) section of the PI2001 data sheet.Rtn1Vaux1 Return Connection: Connected to Ground planeGnd Vin & Vout Return Connection:Three Gnd connections are available and are connected to a common point, the Ground plane. Input supplies Vin1 & Vin2 and the output load at Vout should all be connected to their respective local Gnd connection.SL1PI2001 (U1) Slave Input-Output Pin: For monitoring U1 slave pin. When U1 is configured as the Master, this pin functions as an output that drives slaved PI2001 devices. When U1 is configured in Slave mode, SL1 serves as an input.SL2PI2001 (U2) Slave Input-Output Pin: For monitoring U2 slave pin. When U2 is configured as the Master, this pin functions as an output that drives slaved PI2001 devices. When U2 is configured in Slave mode, SL2 serves as an input.Vin2Power Source Input #2or bus input designed to accommodate up to 20 A continuous current.Vaux2Auxiliary Input Voltage #2to supply PI2001 VC power. Vaux2 should be equal to Vin2 plus 5 V or higher. See details in Auxiliary Power Supply (Vaux) section of the PI2001 data sheet.Rtn2Vaux2 Return Connection: Connected to Ground plane FT1PI2001 (U1) Fault Pin: Monitors U1 fault conditions FT2PI2001 (U2) Fault Pin: Monitors U2 fault conditionsVoutOutput: Q1 and Q2 MOSFET Drain pins connection, connect to the load high side.Table 1 –PI2001-EVAL1 Evaluation Board terminals descriptionCool-ORing TM PI2001 Product DescriptionJumper DescriptionJ1, J3BK Jumpers: Connect jumper across M for master mode and across S for slave mode. Remove jumper to adjust reverse fault blanking time using Rbk. Rbk is R7 for U1 and R14 for U2 shown in the schematic, Figure 2.J2Slave Jumper: Remove the jumper unless one of the PI2001 is configured in slave mode.Table 2 –PI2001-EVAL1 Evaluation Board jumpers descriptionFigure 2 –PI2001-EVAL1 Evaluation Board schematic.Item QTY Reference Designator Value Description Footprint Manufacturer 12C1, C2 1 µF Capacitor, MLCC X5R, 06031 µF,16 V21C322 µF Capacitor, MLCC X7R,121022 µF, 25 V34C4, C5, C6, C7Not installed120642D1, D2LED, Super Red THIN 0603Lite-On, Inc.,58FT1, FT2, Rtn1, Rtn2, Turret Test point TURRET-1528Keystone SL1, SL2, Vaux1, Vaux2Electronics67Gnd1, Gnd2, Gnd3, Gnd4,Turret Test point TURRET-1502Keystone Vin1, Vin2, Vout1, Vout2Electronics 72J1, J3Header Pins 0.1" pitch 2 x 3mm81J2Header Pins 0.1" pitch 2 x 2mm92Q1, Q2FDS8812NZSO-8Fairchild 30 V, 20 A, N-MOSFET102R1, R88.45 KΩResistor,8.45 KΩ,1%0603112R2, R913.3 KΩResistor,13.3 KΩ,1%0603122R3, R1010 ΩResistor,10 Ω,5%0603132R4, R11 4.99 KΩResistor, 4.99 KΩ,5%0603144R5, R6, R12, R13 2.00 KΩResistor, 2.00 KΩ,1%0603152R7, R14Not Installed0603162U1, U2PI2001Picor Universal Active ORing Controller3mmx3mm; 10-TDFN PICOR Table 3 –PI2001-EVAL1 Evaluation Board bill of materialsInitial Test Set UpTo test the PI2001-EVAL1 evaluation board it is necessary to configure the jumpers (J1, J2 and J3) first based on the required board configuration.Failure to configure the jumpers prior to the testing may result in improper circuit behaviorBaseline Test Procedure (Refer to Figure 3)1.0 Recommended Equipment1.1Two DC power supplies - 0-10 V; 25 A.1.2DC power supply 12 V; 100 mA.1.3DC electronic load - 50 A minimum.1.4Digital Multimeter 1.5Oscilloscope.1.6Appropriately sized interconnect cables.1.7Safety glasses.1.8PI2001 Product Data sheet.Figure 3 –Layout configuration for a typical redundant power application, using PI2001 with both solutions configured in Master Mode.Reference Designator Value Functional Description C1, C2 1 µF VC Bypass Capacitor C322 µF Output (Load) CapacitorC4, C5, C6, C7Not installedSnubber to reduce voltage ringing when the device turns off D1, D2LED To indicate a fault exist when it is onJ1, J3Jumper To select between Master and Slave Modes J2Jumper Connection between SL1 and SL2Q1, Q2N-MOSFET ORing Main SwitchR1, R88.45 K ΩUV Voltage Divider Resistor ( R2UV in Figure 4) R2, R913.3 K ΩOV Voltage Divider Resistor ( R2OV in Figure 4) R3, R1010 ΩVC Bias resistor R4, R11 4.99 K ΩLED Current LimiterR5, R6 2.00 K ΩUV Voltage Divider Resistor ( R1UV in Figure 4) R7, R14Not Installed BK Delay Timer Programmable Resistor U1, U2PI2001Universal Active ORing ControllerTable 4 –Component functional descriptionBefore initial power-up follow these steps to configure the evaluation board for specific end application requirements: 2.0 Undervoltage (UV) and Overvoltage (OV) resistors set up:2.1UV and OV programmable resistors are configuredfor a 3.3 V Vin (BUS voltage) application in atwo-resistor voltage divider configuration as shown inFigure 4. UV is set to 2.6 V and OV is set for 3.8 V,R1OV and R1UV are 2.00KΩ1%. If PI2121-EVAL1 isrequired to be used in a different Vin voltage . .application please follow the following steps tochange the resistor values.2.1.1It is important to consider the maximum currentthat will flow in the resistor divider andmaximum error due to UV and OV input .current.R1UV=V(UV TH)I RUV2.1.2Set R1UV and R1OV value based on systemallowable minimum current and 1% error;I RUV ≥ 100 µAR2UV=R1UV (V(UV)–1)V(UV TH)Where:V(UV TH) : UV threshold voltageV(UV) : UV voltage set (0.5 V typ)I RUV: R1UV currentR2OV=R1OV (V(OV)–1)V(OV TH)Where:V(OV TH) : OV threshold voltageV(OV) : OV voltage set (0.5 V typ)I ROV: R1OV currentFigure 4 –UV & OV two-resistor divider configuration2.1.3Example for 2.0 V Vin (BUS voltage), to set UV and OV for ±10% Vin set UV at 1.8 V and OV at 2.2 V.R2UV= R1UV (V(UV)–1) = 2.00 KΩ*( 1.8 V–1)= 5.20 KΩ(or 5.23 KΩ% standard value)V(UV TH)0.5 VR2OV= R1OV (V(OV)–1) = 2.00 KΩ*( 2.2 V–1)= 6.80 KΩ(or 6.81 KΩ% standard value)V(OV TH)0.5 V3.0Blanking timer setup:3.1The blanking timer provides noise filtering fortypical switching power conversion that mightcause premature reverse current detection bymasking the reverse fault condition. The shortestblanking time is 50 ns when the BK pin isconnected to ground. Connecting an externalresistor (R BK, reference designators R7 for U1 andR14 for U2) between the BK pin and ground willincrease the blanking time as shown in Figure 5.Where:R BK≤ 200 KΩNote:When BK is connected to VC for slave mode .operation,then the blanking time will be 270 ns typically.4.0Auxiliary Power Supply (Vaux):4.1The PI2001 Controller has a separate input (VC) thatprovides power to the control circuitry and the gatedriver. An internal voltage regulator (VC) clamps theVC voltage to 15.5 V typically.4.2Connect independent power source to Vaux inputs ofPI2001-EVAL1 Evaluation Board to supply power tothe VC input. The Vaux voltage should be 5V higherthan Vin (redundant power source output voltage) tofully enhance the MOSFET. If the MOSFET is replacedwith different MOSFET, make sure that Vaux= Vin +0.5 V + required voltage to be enhance the MOSFET.4.310 Ωbias resistors (Rbias, reference designators R3and R10) are installed on the PI2001-EVAL1 betweeneach Vaux input and VC pin of one of the PI2001controller. 4.4If Vaux is higher than the Clamp voltage, 15.5 Vtypical, the Rbias value has to be changed using thefollowing equations:4.4.1Select the value of Rbias using the followingequation:Rbias =Vaux min–VC clampMAXIC max4.4.2Calculate Rbias maximum power dissipation:Pd Rbias= (Vaux max–VC clampMIN)2RbiasWhere:Vaux min: Vaux minimum voltageVaux max: Vaux maximum voltageVC ClampMAX:Maximum controllerclamp voltage, 16.0 VVC ClampMIN:Minimum controllerclamp voltage, 14.0 VIC max: Controller maximum bias current,use 4.2 mA4.4.3For example, if the minimum Vaux = 22 Vand the maximum Vaux = 28 VRbias = Vaux min–VC clampMAX =22 V–16 V = 1.429 KΩIC max 4.2 mA,use 1.43 KΩ1% resistorPd Rbias= (Vaux max–VC clampMIN)2= (28 V–14.0 V)2=137 mWRbias 1.43 KΩNote:Minimize the resistor value for low Vaux voltagelevels to avoid a voltage drop that may reduce the VCvoltage lower than required to drive the gate of theinternal MOSFET. Figure 5 –BK Resistor selection versus Blanking Time5.0Hook Up of the Evaluation Board5.1OV and UV resistors values are configured for a 3.3 Vinput voltage. If you are using the evaluation board ina different input voltage level you have to adjust theresistor values by replacing R1, R2, R8 and R9, orremove R2, R5, R9 and R12 to disable UV and OV.Please refer to the UV/OV section for details to set R1,R2, R8 and R9 proper values.5.2Verify that the jumpers J1 and J3 are installed formaster mode [across M] and no Jumper on J2.5.3Connect the positive terminal of PS1 power supplyto Vin1. Connect the ground terminal of PS1 to itslocal Gnd. Set the power supply to 3.3 V.Keep PS1 output disabled (OFF).5.4Connect the positive terminal of PS2 power supplyto Vin2. Connect the ground terminal of PS2 to itslocal Gnd. Set the power supply to 3.3 V. Keep PS2output disabled (OFF).5.5Connect the positive terminal of PS3 power supplyto Vaux1 and Vaux2. Connect the ground terminalof this power supply to Rtn1 and Rtn2. Set thepower supply to 12 V. Keep PS3 output disabled(OFF).5.6Connect the electronic load to the output betweenVout and Gnd. Set the load current to 10 A.5.7Enable (turn ON) PS1 power supply output.5.8Turn on the electronic load.5.9Verify that the electronic load input voltagereading is one diode voltage drop below 3.3 V.5.10Enable (turn ON) PS3 power supply output.5.11Verify that the electronic load voltage readingincreases to a few millivolts below 3.3 V. This verifiesthat the MOSFET is in conduction mode.5.12D1 should be off. This verifies that there is nofault condition.5.13Reduce PS1 output voltage to 2 V,5.14D1 should turn on, this verifies that the circuit is inan under-voltage fault condition.5.15Increase PS1 output to 3.3 V, D1 should turn off, thenincrease PS1 output to 4 V, D1 should turn onindicating an over-voltage fault condition5.16Verify that Vin2 is at 0V. This verifies that thePI2001 (U2) FET (Q2) is off.5.17D2 should be on. This is due to a reverse voltagefault condition caused by the bus voltage beinghigh with respect to the input voltage (Vin2).5.18Enable (turn ON) PS2 output.5.19Verify that both PS1 and PS2 are sharing loadcurrent evenly by looking at the supply current.5.20Disable (turn OFF) PS1, PS2 and PS3 outputs.5.21Enable (turn ON) PS2 output then Enable PS3 output.5.22Verify that the electronic load voltage reading isfew millivolts below 3.3 V. This verifies that the PI2001(U2) MOSFET (Q2) is in conduction mode.5.23D2 should be off. This verifies that there is nofault condition.5.24Reduce PS2 output voltage to 2 V,5.25D2 should turn on, this verifies that the circuit is inan under-voltage fault condition.5.26Increase PS2 output to 3.3 V, D2 should turn off, thenincrease PS2 output to 4 V, D2 should turn onindicating an over voltage fault condition.5.27Verify that Vin1 is at 0V. This verifies that thePI2001 (U1) FET (Q1) is off.5.28D1 should be on. This is due to a reverse voltagefault condition caused by the bus voltage beinghigh with respect to the input voltage (Vin1).6.0Slave Mode: Slave Mode can be demonstrated in two setups; either by using one PI2001-EVAL1 evaluation board as a single ORing function with both PI2001 effectively in parallel or two PI2001-EVAL1 evaluation boards to demonstrate a true redundant 40A system. The following test steps use a single PI2001-EVAL1 in a slave mode application. Note:In this experiment U1 is configured in master mode andU2 is configured in slave mode.6.1BK pin (J1) of the master device will be connected toground [across M] while the slaved device BK pin (J3)is connected to VCC [across S]. Place a jumper across J2to connect slave pins together.6.2Connect the positive terminal of PS1 power supplyto Vin1. Connect the ground terminal of this powersupply to Gnd. Set the power supply to 3.3 V. KeepPS1 output disabled (OFF).6.3Connect the positive terminal of PS2 power supplyto Vin2. Connect the ground terminal of this powersupply to Gnd. Set the power supply to 3.3 V. KeepPS2 output disabled (OFF).6.4Connect the positive terminal of PS3 power supplyto Vaux1 and Vaux2. Connect the ground terminalof this power supply to Rtn1 and Rtn2. Set thepower supply to 12 V. Keep PS3 output disabled (OFF).6.5Connect the electronic load between Vout andGnd. Set the load current to 10 A.6.6Enable (Turn ON) PS2, and PS3 outputs, and keepPS1 output disabled (OFF).6.7Turn on the electronic load.6.8Verify that electronic load voltage drops to a diodedrop below PS2. This verifies that the Q2 is off due tothe Master (U1) not being on.6.9Enable (turn on) PS1 output:6.10Verify that the electronic load input voltage reading isa few millivolts below 3.3 V and PS1 and PS2 aresharing the load current evenly. This verifies that both MOSFET's, Q1 and Q2, are in conduction mode.7.0Input short circuit test7.1To emulate a real application, the BUS supplies for thistest should have a solid output source such as DC-DC converter that supplies high current and can be connected very close to the evaluation board to reduce stray parasitic inductance. Or use theprospective supply sources of the end application where the PI2001 will be used. 7.2Stray parasitic inductance in the circuit can contributeto significant voltage transient conditions, particularly when the MOSFET is turned-off after a reverse current fault has been detected. When a short is applied at the output of the input power sources and the .evaluation board input (Vin), a large reverse current is sourced from the evaluation board output through the ORing MOSFET. The reverse current in the MOSFET may reach over 60 A in some conditions before the MOSFET is turned off. Such high current conditionswill store high energy even in a small parasitic element, and can be represented as ½ Li2. A 1 nH parasitic inductance with 60 A reverse current will generate 1.8 µJ. When the MOSFET is turned off, the stored energy will be released and will produce a high negative voltage at the MOSFET source and high positive voltage at the MOSFET drain. This event will create a high voltage difference across the drain and source of the MOSFET.7.3Apply a short at one of the inputs (Vin1 or Vin2) whenthe evaluation board is configured with bothcontrollers (U1 and U2) in master mode. The short can be applied electronically using a MOSFET connected between Vin and Gnd or simply by connecting Vin to Gnd. Then measure the response time between when the short is applied and the MOSFET is disconnected (or turned off). An example for PI2001 response time to an input short circuit is shown in Figure 6.Figure 6 –Plot of PI2001 response time to reverse current detectionFigure 7a–PI2001-EVAL1 layout top layer. Scale 2.0:1 Figure 7b–PI2001-EVAL1 layout mid layer 2. Scale 2.0:1Figure 7c–PI2001-EVAL1 layout mid layer 1. Scale 2.0:1 Figure 7d–PI2001-EVAL1 layout Bottom layer. Scale 2.0:1Mechancial Drawing分销商库存信息: VICORPI2001-EVAL1。

MPC-2121系列12英寸面板计算机操作指南说明书

P/N: 1802021210011 *1802021210011*MPC-2121 SeriesQuick Installation GuideVersion 1.1, January 2021Technical Support Contact Information/support2021 Moxa Inc. All rights reserved.OverviewThe MPC-2121 12-inch panel computers with E3800 Series processors deliver a reliable and durable platform of wide versatility for use in industrial environments. All interfaces come with IP66-rated M12 connectors to provide anti-vibration and waterproof connections. With a software selectable RS-232/422/485 serial port and two Ethernet ports, the MPC-2121 panel computers support a wide variety of serial interfaces as well as high-speed IT communications, all with native network redundancy.Package ChecklistBefore installing the MPC-2121, verify that the package contains the following items:• 1 MPC-2121 panel computer• 1 2-pin terminal block for DC power input• 6 panel mounting screws• 1 M12 phone jack power cable• 1 M12 Type A USB cable•Quick installation guide (printed)•Warranty cardNOTE: Please notify your sales representative if any of the above items are missing or damaged.Hardware InstallationFront ViewLeft Side ViewBottom ViewRight Side ViewAmbient Light SensorThe MPC-2121 comes with an ambient light sensor located on the upper part of the front panel.The ambient light sensor helps automatically adjust the brightness of the panel with the ambient light condition. This function is disabled by default and has to be enabled before it can be used. For details, refer to the MPC-2121 Hardware User’s Manual.The MPC-2121 can also be mounted using the front panel. Use the four screws on the front panel to attach the front panel of the computer to a wall. Refer to the following figures for the location of the screws.Refer to the figure on the right for thespecifications of the mounting screws.A panel-mounting kit consisting of 6 mounting units is provided in the MPC-2121 package. Refer to the following illustrations for the dimensions and the cabinet space required to panel mount the MPC-2121.To install the panel-mounting kit on the MPC-2121, follow these steps: 1.Place the mounting units in the holes provided on the rear panel andpush the units to the left as shown in the illustration below:2. Use a torque of 4Kgf-cm to fasten the mounting screws and securethe panel-mounting kit units onto a wall.Display-control ButtonsThe MPC-2121 is provided with two display-control buttons on the right panel.The display-control buttons can be used as described in the following table:Symbol and NameUsageFunctionPower Press• Power on• Enter Sleep or Hibernation mode•Wake upNOTE: You can change the function ofthe Power button in the OS settings menu.Press andhold for 4 secondsPower offBrightness + Press Manually increase the brightness of the panelBrightness -PressManually decrease the brightness of the panelConnector DescriptionDC Power InputThe MPC-2121 can be supplied power through a DC power input using an M12 connector. The DC pin assignments are as shown in the following figure:Pin Definition 1 V+ 2 – 3 V- 4 – 5 –Serial PortsThe MPC-2121 offers one software-selectable RS-232/422/485 serial portwith an M12 connector. The pin assignments for the ports are shown in the table below:Pin RS-232 RS-422RS-4851 RI – –2 RXD TX+ –3 DTR RX-D- 4 DSR – – 5 CTS – – 6 DCD TX- – 7 TXD RX+ D+ 8 RTS – – 9 GND GND GND 10 GND GND GND 11 GND GND GND 12–––Ethernet PortsThe pin assignments for the two Ethernet 10/100 Mbps ports with M12 connectors are shown in the following table:Pin Definition1 TD+2 RD+3 TD- 4RD-USB PortsA USB 2.0 port with an M12 connector is available on the rear panel. Use this port to connect a mass-storage drive or other peripheral.Pin Definition1 D-2 VCC3 –4 D+ 5GNDAudio PortThe MPC-2121 comes with an audio output port with an M12 connector. Refer to the following figure for the pin definitions.Pin Definition 1 Detect 2 Line out _L 3 Line out _R4 GND5 Speaker out-6 Speaker out+7 GND 8GNDDIO PortThe MPC-2121 is provided with a DIO port, which is an 8-pin M12connector that includes 4 DIs and 2 DOs. For wiring instructions, refer to the following diagrams and the pin assignment table.PinDefinition1 COM2 DI_03 DI_14 DI_25 DI_36 DO_07 GND 8DO_1Installing a CFast Card or an SD CardMPC-2121 provides two storage options—CFast card and SD card. The storage slots are located on the left panel. You can install the OS in the CFast card and save your data in the SD card. For a list of compatible CFast models, check the MPC-2121 component compatibility report available on Moxa’s website.To install the storage devices, do the following:1.Remove the two screws on the storage-socket cover.The top slot is for the CFast card while the lower slot is for the SD card, as indicated by the following illustration:2.Insert a CFast or SD card into the respective slot using the push-pushmechanism.CFast CardSD Card3. Reattach the cover and secure it with screws.Real-time ClockThe real-time clock (RTC) is powered by a lithium battery. We strongly recommend that you do not replace the lithium battery without help from a qualified Moxa support engineer. If you need to change the battery, contact the Moxa RMA service team. The contact details are available at: https:///en/support/repair-and-warranty/product-repair -service.Grounding the MPC-2121Proper grounding and wire routing help to limit the effects of noise from electromagnetic interference (EMI). Run the ground connection from the ground screw to the grounding surface prior to connecting the power source.Powering On/Off the MPC-2121Connect an M12 Connector to Power Jack Converter to theMPC-2121’s M12 connector and connect a 40 W power adapter to the converter. Supply power through the power adapter. After you have connected a power source, the system power turns on automatically. It takes about 10 to 30 seconds for the system to boot up. You can change the power-on behavior of your computer by changing the BIOS settings. To power off the MPC-2121, we recommend using the "shut down" function provided by the OS installed on the MPC. If you use the Power button, you may enter one of the following states depending on the power management settings in the OS: standby, hibernation, or system shutdown mode. If you encounter problems, you can press and hold the Power button for 4 seconds to force a hard shutdown of the system.- 11 -。

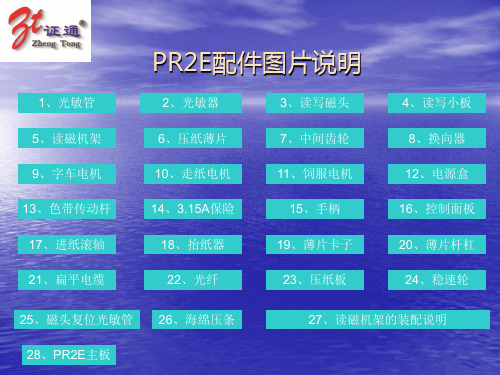

存折打印机PR2E配件图片说明

2

3

铁架

P2RE主板说明

扁平电缆线插座

电源插座

光敏器 走纸电机插座

字车电机插座

饲服电机插座 控制面板

PR2E主板说明

1488、1489串口通讯芯片

字库

FLASH

内存

3个出针保险

主CPU 饲服电机芯片

从CPU

饲服,走纸电机共用保险

PR2E主板说明

出针控制模块

字车电机保险 字车电机控制芯片3个 走纸电机控制芯片

黑长条铁架铁片往上掰字车电机插座扁平电缆线插座走纸电机插座饲服电机插座光敏器电源插座控制面板p2re主板说明3个出针保险字库flash内存主cpu从cpu饲服走纸电机共用保险饲服电机芯片14881489串口通讯芯片pr2e主板说明走纸电机控制芯片字车电机控制芯片3个字车电机保险出针控制模块pr2e主板说明深圳证通客服总部编制深圳证通客服总部编制云云2008年3月20日2008年3月20日

挡纸器杠杆 作用:将挡纸铁片抬起,而挡纸铁片作用是将纸张对齐。 它的左边塑料损坏将使纸张无法吸入

薄片卡子: 作用:带动薄片杆杠的抬起和放下。 容易老化,而与薄片杆杠间固定不紧,需更换。

薄片杠杆 作用:退纸时,打印头移动到最右边,碰到薄片杠杆,将压纸薄片抬起。 如果挂在它上边的小弹簧脱落,退纸时卡纸

弹簧钩

扁平电缆 作用:连接打印头和主板的信号线 损坏的话,出现缺针,或做光电参数时死机

不要插变形

压纸板 作用:接住吸入的纸张 常见故障是压轴弹簧脱落,造成卡纸和进纸倾斜,重装弹簧即可

压轴弹簧 容易脏,清

此处损坏可用A、B胶 将其与读磁电机固定

控制面板 作用:提示打印机当前状态用,当打印机异常时,,指示灯将闪烁。 联机时LOCAL灯亮,南天的设置#PNS4007为CLS,湘计的换控制面板

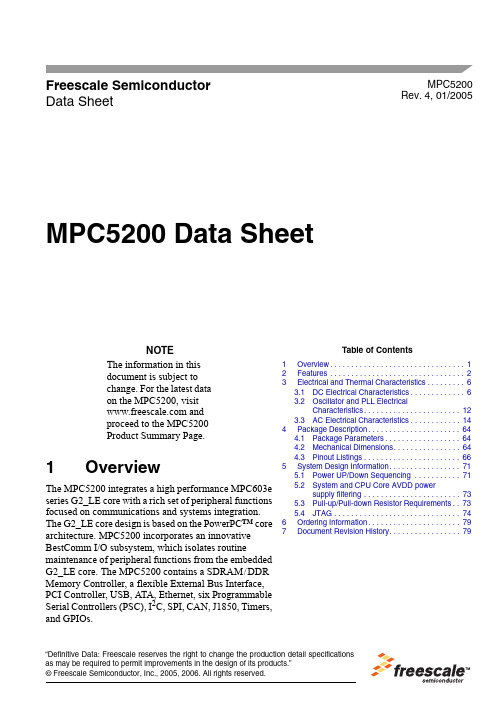

MPC5200资料

Freescale Semiconductor Data SheetMPC5200Rev. 4, 01/2005 Table of ContentsNOTEThe information in thisdocument is subject tochange. For the latest dataon the MPC5200, visit andproceed to the MPC5200Product Summary Page.1OverviewThe MPC5200 integrates a high performance MPC603e series G2_LE core with a rich set of peripheral functions focused on communications and systems integration. The G2_LE core design is based on the PowerPC TM core architecture. MPC5200 incorporates an innovative BestComm I/O subsystem, which isolates routine maintenance of peripheral functions from the embedded G2_LE core. The MPC5200 contains a SDRAM/DDR Memory Controller, a flexible External Bus Interface, PCI Controller, USB, ATA, Ethernet, six Programmable Serial Controllers (PSC), I2C, SPI, CAN, J1850, Timers, and GPIOs.1Overview. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 2Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 3Electrical and Thermal Characteristics. . . . . . . . . 63.1DC Electrical Characteristics. . . . . . . . . . . . . 63.2Oscillator and PLL ElectricalCharacteristics. . . . . . . . . . . . . . . . . . . . . . . 123.3AC Electrical Characteristics. . . . . . . . . . . . 14 4Package Description. . . . . . . . . . . . . . . . . . . . . . 644.1Package Parameters. . . . . . . . . . . . . . . . . . 644.2Mechanical Dimensions. . . . . . . . . . . . . . . . 644.3Pinout Listings. . . . . . . . . . . . . . . . . . . . . . . 66 5System Design Information. . . . . . . . . . . . . . . . . 715.1Power UP/Down Sequencing . . . . . . . . . . . 715.2System and CPU Core AVDD powersupply filtering . . . . . . . . . . . . . . . . . . . . . . . 735.3Pull-up/Pull-down Resistor Requirements. . 735.4JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 74 6Ordering Information. . . . . . . . . . . . . . . . . . . . . . 79 7Document Revision History. . . . . . . . . . . . . . . . . 79MPC5200 Data SheetFeatures2FeaturesKey features are shown below.•MPC603e series G2_LE core—Superscalar architecture—760 MIPS at 400 MHz (-40 to +85 o C)—16 k Instruction cache, 16 k Data cache—Double precision FPU—Instruction and Data MMU—Standard and Critical interrupt capability•SDRAM / DDR Memory Interface—up to 132-MHz operation—SDRAM and DDR SDRAM support—256-MByte addressing range per CS, two CS available—32-bit data bus—Built-in initialization and refresh•Flexible multi-function External Bus Interface—Supports interfacing to ROM/Flash/SRAM memories or other memory mapped devices —8 programmable Chip Selects—Non multiplexed data access using 8/16/32 bit databus with up to 26-bit address—Short or Long Burst capable—Multiplexed data access using 8/16/32 bit databus with up to 25-bit address •Peripheral Component Interconnect (PCI) Controller—Version 2.2 PCI compatibility—PCI initiator and target operation—32-bit PCI Address/Data bus—33- and 66-MHz operation—PCI arbitration function•ATA Controller—Version 4 ATA compatible external interface—IDE Disk Drive connectivity •BestComm DMA subsystem—Intelligent virtual DMA Controller—Dedicated DMA channels to control peripheral reception and transmission—Local memory (SRAM 16 kBytes)• 6 Programmable Serial Controllers (PSC), configurable for the following:—UART or RS232 interfaceFeatures—CODEC interface for Soft Modem, Master/Slave CODEC Mode, I2S and AC97—Full duplex SPI mode—IrDA mode from 2400 bps to 4 Mbps•Fast Ethernet Controller (FEC)—Supports 100Mbps IEEE 802.3 MII, 10 Mbps IEEE 802.3 MII, 10 Mbps 7-wire interface •Universal Serial Bus Controller (USB)—USB Revision 1.1 Host—Open Host Controller Interface (OHCI)—Integrated USB Hub, with two ports.•Two Inter-Integrated Circuit Interfaces (I2C)•Serial Peripheral Interface (SPI)•Dual CAN 2.0 A/B Controller (MSCAN)—Freescale Scalable Controller Area Network (F SCAN) architecture—Implementation of version 2.0A/B CAN protocol—Standard and extended data frames•J1850 Byte Data Link Controller (BDLC)—J1850 Class B data communication network interface compatible and ISO compatible for low speed (<125 kbps) serial data communications in automotive applications.—Supports 4X mode, 41.6 kbps—In-frame response (IFR) types 0, 1, 2, and 3 supported•Systems level features—Interrupt Controller supports four external interrupt request lines and 47 internal interrupt sources—GPIO/Timer functions–Up to 56 total GPIO pins (depending on functional multiplexing selections) that support a variety of interrupt/WakeUp capabilities.–Eight GPIO pins with timer capability supporting input capture, output compare, and pulse width modulation (PWM) functions—Real-time Clock with one-second resolution—Systems Protection (watch dog timer, bus monitor)—Individual control of functional block clock sources—Power management: Nap, Doze, Sleep, Deep Sleep modes—Support of WakeUp from low power modes by different sources (GPIO, RTC, CAN)Features•Test/Debug features—JTAG (IEEE 1149.1 test access port)—Common On-chip Processor (COP) debug port •On-board PLL and clock generationFigure1 shows a simplified MPC5200 block diagram.FeaturesFigure 1. Simplified Block Diagram—MPC5200603G 2_L E C o r eS D R A M / D D R J T A G / C O P I n t e r f a c eR e s e t / C l o c k MSCAN R e a l -T i m e C l o c kS y s t e m F u n c t i o n sI n t e r r u p t C o n t r o l l e rG P I O /T i m e r sP C I B u s C o n t r o l l e rL o c a l P l u s C o n t r o l l e r A T A H o s t C o n t r o l l e rS y s t e m s I n t e r f a c e U n i t (S I U )S D R A M / D D RC o m m B u sL o c a l BestComm DMASRAM 16KB u sJ1850USB SPII 2C EthernetPSC M e m o r y C o n t r o l l e rG e n e r a t i o n2x2x2x6xElectrical and Thermal Characteristics3Electrical and Thermal Characteristics3.1DC Electrical Characteristics3.1.1Absolute Maximum RatingsThe tables in this section describe the MPC5200 DC Electrical characteristics. Table 1 gives the absolute maximum ratings.3.1.2Recommended Operating ConditionsTable 2 gives the recommended operating conditions.Table 1. Absolute Maximum Ratings 1NOTES:1Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage.CharacteristicSymbol Min Max Unit SpecID Supply voltage - G2_LE core and peripheral logic VDD_CORE –0.3 1.8V D1.1Supply voltage - I/O buffers VDD_IO,VDD_MEM_IO –0.3 3.6V D1.2Supply voltage - System APLL SYS_PLL_AVDD –0.3 2.1V D1.3Supply voltage - G2_LE APLL CORE_PLL_AVDD–0.3 2.1V D1.4Input voltage (VDD_IO)Vin –0.3VDD_IO + 0.3V D1.5Input voltage (VDD_MEM_IO)Vin –0.3VDD_MEM_IO+ 0.3V D1.6Input voltage overshoot Vinos – 1.0V D1.7Input voltage undershoot Vinus – 1.0VD1.8Storage temperature rangeTstg–55150oCD1.9Table 2. Recommended Operating ConditionsCharacteristicSymbol Min 1Max (1)Unit SpecID Supply voltage - G2_LE core and peripheral logicVDD_CORE 1.42 1.58V D2.1Supply voltage - standard I/O buffers VDD_IO 3.0 3.6V D2.2Supply voltage - memory I/O buffers (SDR)VDD_MEM_IO SDR 3.0 3.6V D2.3Supply voltage - memory I/O buffers (DDR)VDD_MEM_IO DDR 2.42 2.63V D2.4Supply voltage - System APLL SYS_PLL_AVDD 1.42 1.58V D2.5Supply voltage - G2_LE APLL CORE_PLL_AVDD1.42 1.58V D2.6Input voltage - standard I/O buffers Vin 0VDD_IO V D2.7Input voltage - memory I/O buffers (SDR)Vin SDRVDD_MEM_IO SDRVD2.8Electrical and Thermal Characteristics3.1.3DC Electrical SpecificationsTable 3 gives the DC Electrical characteristics for the MPC5200 at recommended operating conditions (see Table 2).Input voltage - memory I/O buffers (DDR)Vin DDR 0VDD_MEM_IO DDRVD2.9Ambient operating temperature range 2T A -40+85o C D2.10Extended ambient operating temperature range 3T Aext -40+105oCD2.11Die junction operating temperature range Tj -40+115o C D2.12Extended die junction operating temperature rangeTjext-40+125o CD2.13NOTES:1These are recommended and tested operating conditions. Proper device operation outside these conditions is not guaranteed.2Maximum G2_LE core operating frequency is 400 MHz 3Maximum G2_LE core operating frequency is 264 MHzTable 3. DC Electrical SpecificationsCharacteristicConditionSymbol Min Max Unit SpecID Input high voltage Input type = TTLVDD_IO/VDD_MEM_IO SDRV IH 2.0—V D3.1Input high voltage Input type = TTL VDD_MEM_IO DDR V IH 1.7—V D3.2Input high voltage Input type = PCIVDD_IO V IH 2.0—V D3.3Input high voltage Input type = SCHMITTVDD_IOV IH 2.0—V D3.4Input high voltage SYS_XTAL_IN CV IH 2.0—V D3.5Input high voltage RTC_XTAL_IN CV IH 2.0—V D3.6Input low voltage Input type = TTLVDD_IO/VDD_MEM_IO SDRV IL —0.8V D3.7Input low voltage Input type = TTL VDD_MEM_IO DDR V IL —0.7V D3.8Input low voltage Input type = PCIVDD_IO V IL —0.8V D3.9Input low voltage Input type = SCHMITTVDD_IOV IL —0.8V D3.10Input low voltage SYS_XTAL_IN CV IL —0.8V D3.11Input low voltageRTC_XTAL_INCV IL—0.8VD3.12Table 2. Recommended Operating Conditions (continued)CharacteristicSymbol Min 1Max (1)Unit SpecIDElectrical and Thermal CharacteristicsInput leakage currentVin = 0 orVDD_IO/VDD_IO_MEM SDR(depending on input type 1)I IN—+10µAD3.13Input leakage current SYS_XTAL_IN Vin = 0 or VDD_IO I IN —+10µA D3.14Input leakage current RTC_XTAL_IN Vin = 0 or VDD_IOI IN —+10µA D3.15Input current, pullup resistorPULLUP VDD_IO Vin = 0I INpu40109µAD3.16Input current, pullup resistor - memory I/O buffersPULLUP_MEM VDD_IO_MEM SDRVin = 0I INpu41111µA D3.17Input current, pulldown resistorPULLDOWN VDD_IO Vin = VDD_IOI INpd36106µA D3.18Output high voltage IOH is driver dependent 2VDD_IO, VDD_IO_MEM SDR V OH 2.4—V D3.19Output high voltage IOH is driver dependent 2VDD_IO_MEM DDR V OHDDR 1.7—V D3.20Output low voltage IOL is driver dependent 2VDD_IO, VDD_IO_MEM SDR V OL —0.4V D3.21Output low voltageIOL is driver dependent 2VDD_IO_MEM DDRV OLDDR —0.4V D3.22DC Injection Current Per Pin 3I CS-1.0 1.0mA D3.23CapacitanceVin = 0V , f = 1 MHzC in—15pFD3.24NOTES:1Leakage current is measured with output drivers disabled and pull-up/pull-downs inactive.2See Table 4 for the typical drive capability of a specific signal pin based on the type of output driver associated with that pin as listed in Table 52.3All injection current is transferred to VDD_IO/VDD_IO_MEM. An external load is required to dissipate this current to maintain the power supply within the specified voltage range.Total injection current for all digital input-only and all digital input/output pins must not exceed 10 mA. Exceeding this limit can cause disruption of normal operation.Table 4. Drive Capability of MPC5200 Output PinsDriver Type Supply Voltage I OH I OL Unit SpecID DRV4VDD_IO = 3.3V 44mA D3.25DRV8VDD_IO = 3.3V88mAD3.26Table 3. DC Electrical Specifications (continued)CharacteristicConditionSymbol Min Max Unit SpecIDElectrical and Thermal Characteristics3.1.4Electrostatic DischargeCAUTIONThis device contains circuitry that protects against damage due tohigh-static voltage or electrical fields. However, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages. Operational reliability is enhanced if unused inputs are tied to an appropriate logic voltage level (i.e., either GND or V CC ). Table 7 gives package thermal characteristics for this device.3.1.5Power DissipationPower dissipation of the MPC5200 is caused by 3 different components: the dissipation of the internal or core digital logic (supplied by VDD_CORE), the dissipation of the analog circuitry (supplied by SYS_PLL_A VDD and CORE_PLL_A VDD) and the dissipation of the IO logic (supplied byVDD_IO_MEM and VDD_IO). Table 6 details typical measured core and analog power dissipation figures for a range of operating modes. However, the dissipation due to the switching of the IO pins can not be given in general, but must be calculated by the user for each application case using the following formulaDRV8_OD VDD_IO = 3.3V -8mA D3.27DRV16_MEM VDD_IO_MEM = 3.3V 1616mA D3.28DRV16_MEM VDD_IO_MEM = 2.5V 1616mA D3.29PCIVDD_IO = 3.3V1616mAD3.30Table 5. ESD and Latch-Up Protection CharacteristicsSym RatingMin Max Unit SpecID V HBM Human Body Model (HBM)—JEDEC JESD22-A114-B 2000—V D4.1V MMMachine Model (MM)—JEDEC JESD22-A115200—V D4.2V CDM Charge Device Model (CDM)—JEDEC JESD22-C101500—V D4.3I LATLatch-up Current at T A =85o C positive negative+100-100—mAD4.4I LATLatch-up Current at T A =27o C positive negative+200-200—mAD4.5Table 4. Drive Capability of MPC5200 Output Pins (continued)Driver Type Supply Voltage I OH I OL Unit SpecID P IO P IOint N M∑+C VDD _IO 2f×××=Electrical and Thermal Characteristicswhere N is the number of output pins switching in a group M, C is the capacitance per pin, VDD_IO is the IO voltage swing, f is the switching frequency and PIOint is the power consumed by the unloaded IO stage. The total power consumption of the MPC5200 processor must not exceed the value, which would cause the maximum junction temperature to be exceeded.Table 6. Power DissipationCore Power Supply (VDD_CORE)SpecIDModeSYS_XTAL/XLB/PCI/IPG/CORE (MHz)Unit Notes33/66/33/33/26433/132/66/132/396TypTyp Operational 727.51080mW 1,2NOTES:1Typical core power is measured at VDD_CORE = 1.5 V , Tj = 25 C 2Operational power is measured while running an entirely cache-resident program with floating-point multiplication instructions in parallel with a continuous PCI transaction via BestComm.D5.1Doze —600mW 1,33Doze power is measured with the G2_LE core in Doze mode, the system oscillator, System PLL and Core PLL are active, all other system modules are inactive D5.2Nap —225mW 1,44Nap power is measured with the G2_LE core in Nap mode, the stem oscillator, System PLL and Core PLL are active, all other system modules are inactive D5.3Sleep —225mW 1,55Sleep power is measured with the G2_LE core in Sleep mode, the stem oscillator, System PLL and Core PLL are active, all other system modules are inactiveD5.4Deep-Sleep52.552.5mW1,66Deep-Sleep power is measured with the G2_LE core in Sleep mode, the stem oscillator, System PLL, Core PLL and all other system modules are inactive D5.5PLL Power Supplies (SYS_PLL_AVDD, CORE_PLL_AVDD)Mode Typ Unit NotesT ypical2mW77Typical PLL power is measured at SYS_PLL_AVDD = CORE_PLL_AVDD = 1.5 V , Tj = 25 CD5.6Unloaded I/O Power Supplies (VDD_IO, VDD_MEM_IO 8)8IO power figures given in the table represent the worst case scenario. For the mem_io rail connected to 2.5V the IO power is expected to be lower and bounded by the worst case with VDD_MEM_IO connected to 3.3V .Mode Typ Unit NotesT ypical33mW99Unloaded typical I/O power is measured in Deep-Sleep mode at VDD_IO = VDD_MEM_IOSDR = 3.3 V , Tj = 25 CD5.7P total P core P analog P IO ++=Electrical and Thermal Characteristics3.1.6Thermal Characteristics3.1.7Heat DissipationAn estimation of the chip-junction temperature, T J , can be obtained from the following equation:T J =T A +(R θJA × P D )Eqn.1where:T A =ambient temperature for the package (°C)R θJA =junction to ambient thermal resistance (°C/W)P D =power dissipation in package (W)The junction to ambient thermal resistance is an industry standard value, which provides a quick and easy estimation of thermal performance. Unfortunately, there are two values in common usage: the value determined on a single layer board, and the value obtained on a board with two planes. For packages such as the PBGA, these values can be different by a factor of two. Which value is correct depends on the power dissipated by other components on the board. The value obtained on a single layer board is appropriate for the tightly packed printed circuit board. The value obtained on the board with the internal planes is usually appropriate if the board has low power dissipation and the components are well separated.Table 7. Thermal Resistance DataRatingValueUnit NotesSpecID Junction to Ambient Natural Convection Single layer board (1s)R θJA 30°C/W 1,2NOTES:1Junction temperature is a function of die size, on-chip power dissipation, package thermal resistance, mounting site (board) temperature, ambient temperature, air flow, power dissipation of other components on the board, and board thermal resistance.2Per SEMI G38-87 and JEDEC JESD51-2 with the single layer board horizontal.D6.1Junction to Ambient Natural ConvectionFour layer board (2s2p)R θJMA 22°C/W 1,33Per JEDEC JESD51-6 with the board horizontal.D6.2Junction to Ambient (@200 ft/min)Single layer board (1s)R θJMA 24°C/W 1,3D6.3Junction to Ambient (@200 ft/min)Four layer board (2s2p)R θJMA 19°C/W 1,3D6.4Junction to Board R θJB 14°C/W 44Thermal resistance between the die and the printed circuit board per JEDEC JESD51-8. Board temperature is measured on the top surface of the board near the package.D6.5Junction to Case R θJC8°C/W 55Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).D6.6Junction to Package T opNatural ConvectionΨJT2°C/W66Thermal characterization parameter indicating the temperature difference between package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.D6.7Electrical and Thermal CharacteristicsHistorically, the thermal resistance has frequently been expressed as the sum of a junction to case thermal resistance and a case to ambient thermal resistance:RθJA=RθJC+RθCA Eqn.2 where:RθJA=junction to ambient thermal resistance (°C/W)RθJC=junction to case thermal resistance (°C/W)RθCA=case to ambient thermal resistance (°C/W)RθJC is device related and cannot be influenced by the user. The user controls the thermal environment to change the case to ambient thermal resistance, RθCA. For instance, the user can change the air flow around the device, add a heat sink, change the mounting arrangement on printed circuit board, or change the thermal dissipation on the printed circuit board surrounding the device. This description is most useful for ceramic packages with heat sinks where some 90% of the heat flow is through the case to the heat sink to ambient. For most packages, a better model is required.A more accurate thermal model can be constructed from the junction to board thermal resistance and the junction to case thermal resistance1-3. The junction to case covers the situation where a heat sink will be used or where a substantial amount of heat is dissipated from the top of the package. The junction to board thermal resistance describes the thermal performance when most of the heat is conducted to the printed circuit board. This model can be used for either hand estimations or for a computational fluid dynamics (CFD) thermal model.To determine the junction temperature of the device in the application after prototypes are available, the Thermal Characterization Parameter (ΨJT) can be used to determine the junction temperature with a measurement of the temperature at the top center of the package case using the following equation:T J=T T+(ΨJT× P D)Eqn.3 where:T T=thermocouple temperature on top of package (°C)ΨJT=thermal characterization parameter (°C/W)P D=power dissipation in package (W)The thermal characterization parameter is measured per JESD51-2 specification using a 40-gauge type T thermocouple epoxied to the top center of the package case. The thermocouple should be positioned, so that the thermocouple junction rests on the package. A small amount of epoxy is placed over the thermocouple junction and over approximately one mm of wire extending from the junction. The thermocouple wire is placed flat against the package case to avoid measurement errors caused by cooling effects of the thermocouple wire.3.2Oscillator and PLL Electrical CharacteristicsThe MPC5200 System requires a system-level clock input SYS_XTAL. This clock input may be driven directly from an external oscillator or with a crystal using the internal oscillator.Electrical and Thermal CharacteristicsThere is a separate oscillator for the independent Real-Time Clock (RTC) system. The MPC5200 clock generation uses two phase locked loop (PLL) blocks. •The system PLL (SYS_PLL) takes an external reference frequency and generates the internal system clock. The system clock frequency is determined by the external reference frequency and the settings of the SYS_PLL configuration.•The G2_LE core PLL (CORE_PLL) generates a master clock for all of the CPU circuitry. The G2_LE core clock frequency is determined by the system clock frequency and the settings of the CORE_PLL configuration.3.2.1System Oscillator Electrical Characteristics3.2.2RTC Oscillator Electrical Characteristics3.2.3System PLL Electrical CharacteristicsTable 8. System Oscillator Electrical CharacteristicsCharacteristicSymbol NotesMin Typical Max Unit SpecID SYS_XT AL frequency f sys_xtal 15.633.335.0MHz O1.1Oscillator start-up timet up_osc——100µsO1.2Table 9. RTC Oscillator Electrical CharacteristicsCharacteristicSymbol NotesMin Typical Max Unit SpecID RTC_XTAL frequencyf rtc_xtal—32.768—kHzO2.1Table 10. System PLL SpecificationsCharacteristicSymbol NotesMin Typical Max Unit SpecID SYS_XT AL frequency f sys_xtal 1NOTES:1The SYS_XTAL frequency and PLL Configuration bits must be chosen such that the resulting system frequency, CPU (core) frequency, and PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.15.633.335.0MHz O3.1SYS_XT AL cycle time T sys_xtal (1)66.630.028.5ns O3.2SYS_XT AL clock input jitter t jitter 22This represents total input jitter - short term and long term combined - and is guaranteed by design. T wo different types of jitter can exist on the input to core_sysclk, systemic and true random jitter. True random jitter is rejected, but the PLL. Systemic jitter will be passed into and through the PLL to the internal clock circuitry, directly reducing the operating frequency.——150ps O3.3System VCO frequency f VCOsys (1)250533800MHz O3.4System PLL relock timet lock33Relock time is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for the PLL lock after a stable Vdd and core_sysclk are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep modes.——100µsO3.5Electrical and Thermal Characteristics3.2.4G2_LE Core PLL Electrical CharacteristicsThe internal clocking of the G2_LE core is generated from and synchronized to the system clock by means of a voltage-controlled core PLL.3.3AC Electrical CharacteristicsHyperlinks to the indicated timing specification sections are provided below.AC Test Timing Conditions:Unless otherwise noted, all test conditions are as follows:Table 11. G2_LE PLL SpecificationsCharacteristicSymbol NotesMin Typical Max Unit SpecID G2_LE frequency f core 1NOTES:1The XLB_CLK frequency and G2_LE PLL Configuration bits must be chosen such that the resulting systemfrequencies, CPU (core) frequency, and G2_LE PLL (VCO) frequency do not exceed their respective maximum or minimum operating frequencies.50—550MHz O4.1G2_LE cycle time t core (1) 2.85—40.0ns O4.2G2_LE VCO frequency f VCOcore (1)400—1200MHz O4.3G2_LE input clock frequency f XLB_CLK 25—367MHz O4.4G2_LE input clock cycle time t XLB_CLK 2.73—50.0ns O4.5G2_LE input clock jitter t jitter 22This represents total input jitter - short term and long term combined - and is guaranteed by design. T wo different types of jitter can exist on the input to core_sysclk, systemic and true random jitter. True random jitter is rejected, but the PLL. Systemic jitter will be passed into and through the PLL to the internal clock circuitry, directly reducing the operating frequency.——150ps O4.6G2_LE PLL relock timet lock33Relock time is guaranteed by design and characterization. PLL-relock time is the maximum amount of time required for the PLL lock after a stable Vdd and core_sysclk are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep modes.——100µsO4.7•AC Operating Frequency Data •USB •Clock AC Specifications •SPI •Resets•MSCAN •External Interrupts •I 2C •SDRAM •J1850•PCI•PSC•Local Plus Bus •GPIOs and Timers•ATA •IEEE 1149.1 (JTAG) AC Specifications•EthernetElectrical and Thermal Characteristics•TA = -40 to 85 o C •Tj = -40 to 115 o C•VDD_CORE = 1.42 to 1.58 V VDD_IO = 3.0 to 3.6 V •Input conditions:All Inputs: tr, tf <= 1 ns •Output Loading:All Outputs: 50 pF3.3.1AC Operating Frequency DataTable 12 provides the operating frequency information for the MPC5200.3.3.2Clock AC SpecificationsFigure 2. Timing Diagram—SYS_XTAL_INTable 12. Clock FrequenciesMinMax Units SpecID 1G2_LE Processor Core —400MHz A1.12SDRAM Clock —133MHz A1.23XL Bus Clock —133MHz A1.34IP Bus Clock—133MHz A1.45PCI / Local Plus Bus Clock —66MHz A1.56PLL Input Range15.635MHzA1.6t FALLt RISEt CYCLE SYSCLKt DUTY t DUTY CV IHCV ILV MV MV MElectrical and Thermal Characteristics3.3.3ResetsThe MPC5200 has three reset pins: •PORRESET - Power on Reset •HRESET - Hard Reset •SRESET - Software ResetThese signals are asynchronous I/O signals and can be asserted at any time. The input side uses a Schmitt trigger and requires the same input characteristics as other MPC5200 inputs, as specified in the DC Electrical Specifications section. Table 14 specifies the pulse widths of the Reset inputs.Notes:1.its minimum pulse width equals the minimum given for HRESET related to the same reference clock.2.The t VDD_stable describes the time which is needed to get all power supplies stable.3.For t lock, refer to the Oscillator/PLL section of this specification for further details.4.For t up_osc, refer to the Oscillator/PLL section of this specification for further details.5.Following the deassertion of PORRESET , HRESET and SRESET remain low for 4096 reference clock cycles.6.clock cycles.NOTEAs long as VDD is not stable the HRESET output is not stable.Table 13. SYS_XTAL_IN TimingSym DescriptionMin Max Units SpecID t CYCLE SYS_XT AL_IN cycle time.1NOTES:1CAUTION —The SYS_XT AL_IN frequency and system PLL_CFG[0-6] settings must be chosen such that theresulting system frequencies do not exceed their respective maximum or minimum operating frequencies. See the MPC5200 User Manual [1].28.664.1ns A2.1t RISE SYS_XT AL_IN rise time.— 5.0ns A2.2t FALL SYS_XT AL_IN fall time.— 5.0ns A2.3t DUTY SYS_XT AL_IN duty cycle (measured at V M ).2 2SYS_XTAL_IN duty cycle is measured at V M .40.060.0%A2.4CV IH SYS_XT AL_IN input voltage high 2.0—V A2.5CV ILSYS_XT AL_IN input voltage low—0.8VA2.6Table 14. Reset Pulse WidthName Description Min Pulse Width Max Pulse WidthReference Clock SpecID PORRESET Power On Reset t VDD_stable +t up_osc +t lock—SYS_XT AL_IN A3.1HRESET Hardware Reset 4 clock cycles —SYS_XT AL_IN A3.2SRESETSoftware Reset4 clock cycles—SYS_XT AL_INA3.3。

摩克斯 MPC-2101 系列 10 吋工業無風扇面板電腦说明书

MPC-2101系列10吋工業無風扇面板電腦特色與優點•10吋面板電腦•Intel Atom®處理器E38451.91GHz•日照下可判讀的1000nit LCD•-40至70°C寬溫度設計,無風扇或加熱器•EN50155:2017相容認證簡介採用Intel Atom®處理器E3800系列的MPC-210110吋面板電腦,為工業環境提供可靠耐用的多功能平台。

所有介面均配備IP66防護等級M12連接器,藉以提供防震和防水的穩定連線。

MPC-2101面板電腦配備兩個可選式軟體的RS-232/422/485串列連接埠和兩個乙太網路LAN連接埠,支援多種串列介面以及高速IT通訊,這些都提供本機網路備援。

MPC-2101系列面板電腦的設計可耐受-40至70°C的寬溫度範圍,並採用無風扇、流線型外殼,專為高效散熱而設計,成為適用於易震動、嚴苛、炎熱的戶外環境中,最可靠的工業平台。

MPC-2101也配備1000-nit LCD面板,採用日照下可判讀的投射電容式多點觸控螢幕,達到絕佳使用者體驗。

外觀規格ComputerCPU Intel Atom®Processor E3845(2M Cache,1.91GHz)Graphics Controller Intel®HD GraphicsSystem Memory Pre-installed4(8GB Max.)GB DDR3LSystem Memory Slot SODIMM DDR3/DDR3L slot x1Pre-installed OS MPC-2101-E4-LB-CT-T-W7E/MPC-2101-E4-CT-T-W7E:Windows Embedded Standard7(WS7P)64-bit pre-installedMPC-2101-E4-LB-CT-T-LX/MPC-2101-E4-CT-T-LX:Linux9pre-installedStorage Slot CFast slot x1SD slots x1,SD3.0(SDHC/SDXC)socketStorage Pre-installed MPC-2101-E4-LB-CT-T-W7E/MPC-2101-E4-CT-T-W7E:32GB CFast CardMPC-2101-E4-LB-CT-T-LX/MPC-2101-E4-CT-T-LX:32GB CFast CardExpansion Slots Mini PCIeSupported OS Windows10Pro64-bitWindows10Embedded IoT Ent2019LTSC64-bitWindows10Embedded IoT Ent2016LTSBWindows7Pro for Embedded SystemsWindows Embedded Standard7(WS7P)64-bitLinux Debian9Computer InterfaceDigital Output DOs x2(M12A-code)Digital Input DIs x4(M12A-code)Serial Ports RS-232/422/485ports x1(M12A-code12P)USB2.0USB2.0hosts x1(M12A-code5P)Ethernet Ports Auto-sensing10/100Mbps ports(M12D-coded4P)x2LED IndicatorsSystem Power x1DisplayPanel Size10.4-inch viewable imagePixel Pitch(RGB)0.240(H)x0.240(V)mmContrast Ratio1000:1Active Display Area210.4(H)x157.8(V)mmAspect Ratio4:3Viewing Angles176°/176°Max.No.of Colors16.2M(8-bit/color)Response Time5ms(gray to gray)Pixels1024x768Light Intensity(Brightness)500/1000cd/m2Touch FunctionTouch Support Points4pointsTouch Type Capacitive Touch(PCAP)Glove Support YesSerial InterfaceBaudrate50bps to115.2kbpsData Bits5,6,7,8Flow Control RTS/CTS,XON/XOFFParity None,Even,Odd,Space,MarkStop Bits1,1.5,2Serial SignalsRS-232TxD,RxD,RTS,CTS,DTR,DSR,DCD,GND RS-422Tx+,Tx-,Rx+,Rx-,GNDRS-485-2w Data+,Data-,GNDRS-485-4w Tx+,Tx-,Rx+,Rx-,GNDPower ParametersInput Voltage24to110VDCPhysical CharacteristicsDimensions256.9x214.4x58.9mm(10.11x8.44x2.32in) Housing MetalIP Rating IP66Weight2,080g(4.59lb)Environmental LimitsAmbient Relative Humidity5to95%(non-condensing)Operating Temperature-40to70°C(-40to158°F)Storage Temperature(package included)-40to70°C(-40to158°F)Standards and CertificationsEMI CISPR32,FCC Part15B Class AEMS IEC61000-4-2ESD:Contact:6kV;Air:8kVIEC61000-4-3RS:80MHz to1GHz:20V/mIEC61000-4-4EFT:Power:2kV;Signal:2kVIEC61000-4-5Surge:Power:2kV;Signal:1kVIEC61000-4-6CS:10VIEC61000-4-8PFMFMechanical Protection Rating IEC60529,IP codeSafety IEC62368-1,IEC60950-1,UL62368-1Shock EN50155standardEMC EN55032/35Vibration EN50155standardDeclarationGreen Product RoHS,CRoHS,WEEEWarrantyWarranty Period System:3yearsLCD:1yearDetails See /tw/warrantyPackage ContentsDevice1x MPC-2101Series computer Documentation1x quick installation guide1x warranty cardInstallation Kit1x M12-Phone jack power cable1x M12-Type A USB cable1x terminal block,2-pin(for remote power input)6x screw,for panel-mounting尺寸訂購資訊2.0MPC-2101-E4-LB-CT-T-W7E 10"(4:3)500nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°CMPC-2101-E4-CT-T-W7E 10"(4:3)1,000nitsE3845Quadcore4GBW7E(64-bit)2(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°CMPC-2101-E4-LB-CT-T-LX 10"(4:3)500nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°CMPC-2101-E4-CT-T-LX 10"(4:3)1,000nitsE3845Quadcore4GB Debian92(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°CMPC-2101-E4-LB-CT-T 10"(4:3)500nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°CMPC-2101-E4-CT-T 10"(4:3)1,000nitsE3845Quadcore4GB–2(M12)1(M12)1(M12)4/2(M1-2)24to110VDCIP66-40to70°C©Moxa Inc.版權所有.2021年3月10日更新。

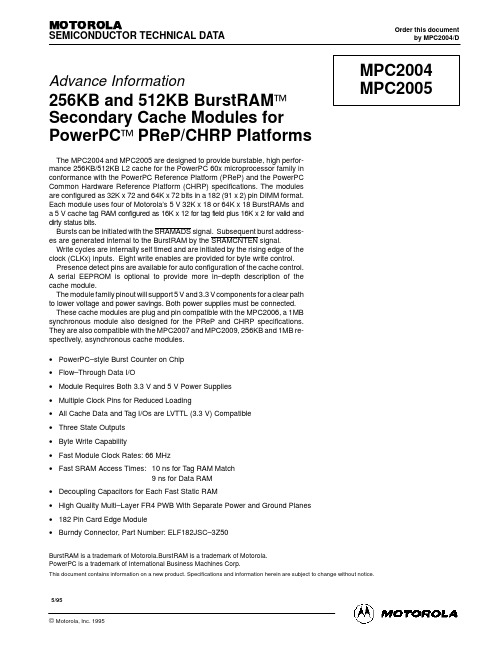

MPC2005中文资料

MPC2004•MPC20056–1Advance Information256KB and 512KB BurstRAM ™Secondary Cache Modules for PowerPC ™ PReP/CHRP PlatformsThe MPC2004 and MPC2005 are designed to provide burstable, high perfor-mance 256KB/512KB L2 cache for the PowerPC 60x microprocessor family in conformance with the PowerPC Reference Platform (PReP) and the PowerPC Common Hardware Reference Platform (CHRP) specifications. The modules are configured as 32K x 72 and 64K x 72 bits in a 182 (91 x 2) pin DIMM format.Each module uses four of Motorola’s 5 V 32K x 18 or 64K x 18 BurstRAMs and a 5 V cache tag RAM configured as 16K x 12 for tag field plus 16K x 2 for valid and dirty status bits.es are generated internal to the BurstRAM by the SRAMCNTEN signal.Write cycles are internally self timed and are initiated by the rising edge of the clock (CLKx) inputs. Eight write enables are provided for byte write control.Presence detect pins are available for auto configuration of the cache control.A serial EEPROM is optional to provide more in–depth description of the cache module.The module family pinout will support 5 V and 3.3 V components for a clear path to lower voltage and power savings. Both power supplies must be connected.These cache modules are plug and pin compatible with the MPC2006, a 1MB synchronous module also designed for the PReP and CHRP specifications.They are also compatible with the MPC2007 and MPC2009, 256KB and 1MB re-spectively, asynchronous cache modules.•PowerPC–style Burst Counter on Chip •Flow–Through Data I/O•Module Requires Both 3.3 V and 5 V Power Supplies •Multiple Clock Pins for Reduced Loading•All Cache Data and T ag I/Os are LVTTL (3.3 V) Compatible •Three State Outputs •Byte Write Capability•Fast Module Clock Rates: 66 MHz•Fast SRAM Access Times: 10 ns for Tag RAM Match9 ns for Data RAM •Decoupling Capacitors for Each Fast Static RAM•High Quality Multi–Layer FR4 PWB With Separate Power and Ground Planes •182 Pin Card Edge Module•Burndy Connector, Part Number: ELF182JSC–3Z50BurstRAM is a trademark of Motorola.BurstRAM is a trademark of Motorola.PowerPC is a trademark of International Business Machines Corp.This document contains information on a new product. Specifications and information herein are subject to change without notice.Order this documentby MPC2004/DMOTOROLASEMICONDUCTOR TECHNICAL DATAMPC2004MPC2005associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and。

乐创自动化技术 MPC6515 激光雕刻与切割 控制器 说明书

6.1 编程下载............................................................................................19

2 概 述............................................................................2

2.1 MPC6515 简介 ....................................................................................2 2.2 控制器组成..........................................................................................2

5.5.1 切边框....................................................................................................... 11 5.5.2 点射设置................................................................................................... 11 5.5.3 点动设置................................................................................................... 12 5.5.4 语言选择................................................................................................... 13 5.6 加工操作............................................................................................13 5.7 U盘下载 .............................................................................................15 5.8 错误报警界面....................................................................................15 5.8.1 简介........................................................................................................... 15 5.8.2 软件限位停止 ........................................................................................... 16 5.8.3 硬限位停止............................................................................................... 16 5.8.4 存储空间不足报警 ................................................................................... 16 5.8.5 配置与固件不匹配 ................................................................................... 17 5.8.6 函数库与固件不匹配错误 ....................................................................... 17 5.8.7 硬件与固件不匹配报警 ........................................................................... 18

南天pr2技术参数

南天pr2技术参数Nantian PR-2E主要技术性能指标存储器特性8Mb FLASH闪速存储器内含西文字库和监控程序,支持“智能升级”功能128KByte RAM动态数据区256Byte EEPROM存储打印机配置参数和光电管设置参数16Mb掩膜EPROM GBK汉字库打印头特性打印头24针,菱形排列针直径0.25mm最大打印速度350字符/秒(10CPI)PTC过热温度保护纸边检测传感器打印精度成行度:<0.10mm(同向); <0.20mm(异向)成列度:<0.14mm(同向); <0.28mm(异向)打印头寿命> 4亿次/针打印特性打印方式点阵击打式,双向预测逻辑选距打印速度(最大值)高速草稿仿信函信函质量汉字(汉字/秒) 175 135 65 43ASCII(字符/秒) 350 260 130 86BIM(位映像图形方式)1220dps(点/秒)图形(位映象方式)点阵密度(点/英寸)水平方向Olivetti 8针:72(或96),240,120,80,6024针:360,240,180,120,60IBM 60,120,240OKI 90,180LQ 90,180垂直方向Olivetti:180IBM:180OKI:180LQ:180打印字间距Olivetti ASCII字符5、10,12,13,15,16.6,17.1字符/英寸汉字:2.5,5,6,7.5,8.3,8.5汉字/英寸IBM ASCII字符10,12,15,17.1,20字符/英寸汉字:5,6,7.5,8.5,10汉字/英寸OKI ASCII字符10,12,13.8,16.6字符/英寸,汉字:13.8汉字/英寸LQ ASCII字符10,12,15字符/英寸,汉字:13.8汉字/英寸打印行间距Olivetti1/5、1/6,1/8,n/72,n/216,n/240 英寸IBM1/6,1/8,n/72,n/216 英寸OKI 1/6,1/8,n/120 英寸LQ1/6,1/8,n/180打印行长(字符/行)80、90、94打印属性正常、倍宽、倍高、三倍宽、三倍高、字符放大(西文最大:4 X 8、中文最大:4 X 4)、黑体、网底、斜体、中空、上标、下标、旋转、反白、上划线、下划线打印特征走纸进纸方式手动进纸纠偏方式光学传感器自动纠偏、自动对边最大进纸宽度245mm进纸器厚度2mm进纸速度大于26 厘米/秒对齐时间小于0.3秒打印厚度最大2mm进纸出错率纸张类型塞纸歪斜A4(80g/ m2)< 1/6000 1/6000(<1.5mm)多层拷贝(1+4)< 1/3000 1/3000(<1.5mm)存折本< 1/2000 1/500(<2mm)打印吞吐率(ECMA打印测试文本)打印质量打印吞吐率(页/小时)HSD(高速草稿)375DRAFT(草稿)280NLQ(仿信函)140LQ(信函)95仿真方式OLIVETTI PR2E、PR-2、PR-54、PR-50、PR-40、Nantian PR-50系列、Nantian PR-2系列、IBM PPDS、IBM PROPRINTER II、IBMPROPRINTER X24、OKI5330SC、OKI 5530SC、EPSON LQ1600K字体西文HSD、DRAFT、NLQ1、NLQ2、LQ、Native、Roman、Sans Serif、Italic、OCRA、OCRB汉字GBK宋体字符集ASCII 256个字符,96个半角字符GBK ISO—10646中、日、韩(C. J. K.)汉字,符合GB13000、GBK标准,共有24X24点阵的20902个汉字、1420个符号和101个扩充汉字IBM5550 1324个图形字符,6763个汉字用户造字223个ASCII字符,94个汉字国际字符组30组条形码标准UPC-A、UPC-E、EAN-8(JAN)、EAN-13(JAN)、Code 39、Code 128、Codabar(Monarch)、2/5 Interleaved、2/5Industrial可处理文本单页纸、连续纸、多页复写纸、存折本、票据、凭证纸张处理方式任意位置自动进纸、自动纠偏、自动对边、自动调整打印厚度文本打印规格单层或多层复写打印纸幅面宽允许值65mm - 245mm长允许值(OLIVETTI仿真)70mm - 450mm,最大推荐值:297mm(IBM、OKI、LQ仿真):大于70mm最大打印区域(10CPI):238mm垂直装订存折本存折本打开宽度:110mm - 241.3mm存折本长度:85mm - 220mm水平装订存折本存折本宽度110mm - 241.3mm存折本打开长度165mm - 220mm纸张厚度单层0.07mm - 0.28mm( 30 g/m2 —160g/m2)存折本存折本打开的最大厚度:1.8mm存折本页间最大厚度差:1.2mm存折本封面厚度:0.2—0.5 mm多层复写1+5页(原件40 g/m2 - 60 g/m2,复写纸20 g/m2 - 34 g/m2)多层复写最大纸重380 g/m2字符打印位置文本和存折本左右边界值LH/RH(字符边缘-页面边缘距离):3.1mm±0.3mm文本和存折页顶标准(从字符底线测量)PR-2仿真= 4.23mmPR-50/40+、PR-54仿真= 7.4mmIBM PPII仿真= 4.23 mm文本页尾的最小值(从字符底线测)PR-2/PR-54+/PR-40+ = 3.1mmIBMPPII仿真= 10mm存折页尾的最小值(从字符底线测量)5mm 从装订线以上最末行字符基线到水平装订线的最小距离5mm 从装订线以下第一行字符基线到水平装订线的最小距离8mm 字符中心距垂直装订存折本的垂直装订线最小距离 5.08mm磁记录规范硬件水平磁条读写器选件,具有存折本和信用卡水平磁条读写功能磁条标准IBM 3604、IBM4746、DIN/ISO、ISO 7811、ISO 8484、ANSI、HITACHIBP仿真字符集标准标准1、标准2、标准3、标准4磁记录密度75BPI、105BPI、210BPI信用卡符合ISO7810标准的ID1卡,磁条长度为84毫米磁道位置第二、三磁道出错率< 1/10000传感检测开盖检测、前进纸槽纸张检测、纸对齐检测、纸宽检测、纸边检测、打印头复位位置检测通信接口标准接口总线接口(在主板上)可连接选件接口或其他设备串口1(在主板上)类型RS 232C串口相关标准V.24 RS232 C接口连接器9针D型接口波特率9600、4800、2400、1200校验奇校验、偶校验、无校验数据位8、7停止位1、2接收缓冲8Kbyte选件接口第二串口选件(串口2):具有与串口1相同的特性并口选件(Parallel)类型Centronics相关标准IEEE 1284-1994操作模式SPP,nibble,byte接口连接器Centronics,36孔接收缓冲8KbyteDIN选件接口(伺服接口,在主板上)类型DIN类型6芯接口功能连接密码键盘、拖拉走纸器等USB选件接口(同时具有串口2和USB接口)类型终端类型相关标准USB rev1.1传输率200KBps色带规格特性长度22米颜色黑色寿命500 万字符电气参数电源类型开关电源电压(类型1)交流200—240V(±10%)电压(类型2)交流100—130V(±10%)频率50 Hz或60 Hz±0.5%功耗12 W (静态)-70W(动态)-170 W(最大)可靠性平均无故障时间(MTBF) ≥10,000小时安全认证标准CE、IMQ、CUL-US无线电干扰标准55022B、FCC A物理参数尺寸384mm×280mm×204mm重量9 kg (无磁条选件)Nantian PR9产品技术规格10 kg (带磁条选件)储存环境储存温度-10 ℃- 60 ℃相对湿度10% - 90%工作环境工作温度5 ℃- 3 5 ℃相对湿度15% - 85%(无霜)噪声小于54 Db应用软件Resource Kit集成环境应用软件功能:在线完成PR2E的版本“智能升级”;在线读取PR2E配置参数,并进行在线参数更改;可通过下载新的西文字符集进行字符集管理;管理宏定义命令和LOGO,通过在PR2E的64Kbyte FLASHEPROM中下载或删除宏定义命令或LOGO来管理用户标志或实现永久性用户造字功能,最多可以下载255个宏、LOGO或用户造字;Drivers驱动程序:IBM ProPrinter X24:并口连接,PR2E并口仿真设置为“南天—IBM”,IBM配置菜单下的仿真方式为“X24”,“AGM图形模式”设置为“是”,该驱动程序随WINDOWS提供;Olivetti驱动程序:串口连接,PR2仿真,垂直步距为1/216”,基于OLIVETTI协议设计,集成了工业标准应用可能涉及的所有特性。

PR2 plus、PR2E、PR2打印机说明

PR2 plus、PR2E、PR2打印机说明书,打印参数设置,边界调整说明一、控制面板按键和Set-up菜单参数打印操作说明PR2 plus、PR2E、PR2打印机的控制面板都由5个LED指示灯、3个按键组成,其3个按键的名称(STATION1、LOCAL、STATION2)、功能相同,在脱机状态下的使用功能、方法类似。

二、Set-up菜单参数打印操作1. 关闭电源。

2. 按住操作面板上的STATION2 键,再打开电源。

3. 按住操作面板上的STATION2 键,直到打印机机械动作停止。

4. 插入一张至少是A4大小(210mm×297mm)的纸到进纸器槽中。

这时打印机将自动地把纸对齐送入到正确的打印位置。

接着,将打印出一张测试页(打印机参数配置表)。

如果一张A4纸打印不完,再插入一张A4纸。

5.关闭打印机即可停止打印操作。

参数配置表的开头除打印南天的标记、打印机的型号及版本等信息外,还打印出当前打印机的设置内容。

设置内容可以进行更改,如果样张上的配置与实际使用的情况不符,可按照“Set-up 菜单参数设置方法”的叙述重新进行设置三、Set-up菜单参数设置方法进行Set-up菜单参数设置须按以下操作进行:1.关机。

2.同时按下STATION1和STATION2键,然后开机,直到打印机初始化动作完成。

3.在进纸槽中插入一张A4规格的纸。

这时,打印机打印出一行提示信息:按STATION1认可当前参数按STATION2选择下一参数按LOCAL开始设定参数4.按下LOCAL键,机器进入设置状态。

同时打印出如下一行:MENU:配置模式5.如果这时按下STATION1键,将意味着认可当前参数“配置模式”项,并对“配置模式”下的“配置参数设置”逐一进行选择。

6.如果这时按下STATION2键,将意味着不选择当前参数“配置模式”项,这时打印机将打印出:IBM配置同理:如果接下来按下STATION1键,将意味着认可当前参数选项(“IBM配置”),并对其下的“配置参数设置”逐一进行选择。

TEA1751中文

TEA1751GreenChipⅢ SMPS开关电源控制芯片Rev. 01 — 10 July 2008产品数据手册1.概述:GreenChip Ⅲ是第三代绿色开关电源(SMPS)控制芯片。

TEA1751(L)T(TEA1751T和TEA1751LT)将功率因数校正(PFC)控制器和反激式(FLYBACK)开关电源控制器集成在一起。

它的集成度高,外接元件少,因而使电源设计的成本低而效率高。

其特殊内置的绿色功能使其在任何功率等级时的效率都很高。

在大功率时它保持在谷底转换的准谐振状态,在低功率时反激控制器减少工作频率同时功率因数控制器关闭使整个变换器其保持在高效率。

在低功耗条件下反激控制器减少工作频率同时并限制峰值电流被为最大值的25%。

这就确保了在低功率时也高效,使其有良好的待机性能和减小了变压器的噪声。

TEA1751(L)T为多片模式(MCM),内部含有2片。

TEA1750专有的高压BCD800工艺使其可以直接从整流后的主高压供电线路高效绿色的起动。

片内第二个低压工艺则实现精确的高速保护和控制功能。

TEA1751(L)T外接元件很少 ,可以很容易的设计出250W以下高效可靠的电源。

2.特点2.1 与众不同的特点集成功率因数校正PFC和反激式开关电源控制器。

世界电压输入范围(70-276VAC)。

双升压PFC和准确的最大输出电压。

集成度高,外接元件少,性价比好。

2.2 绿色特性片上启动电流源。

2.3 PFC部分的绿色特性采用谷电压/零电压转换,使开关损耗最小。

频率限制以减小开关损耗。

在反激输出端负载很低时PFC功能关闭。

2.4 反激部分的绿色特性采用电压谷转换使开关损耗最少。

低功率输出时最小峰值电流固定同时频率减小以保持稳定的高效率。

2.5 保护特性系统出现故障时安全重启动。

对PFC控制器和FLYBACK反激转换都进行去磁均值检测实现连续模式保护。

欠压保护(UVP)(过载时折返保护)。

PFC控制及反激控制均可实现精确的过压保护(OVP)(反激控制过压保护可调节)。

517操作说明书

05pmii选择复印纸23预设缩小放大24缩放24分页25更改份数26用单面纸复印身份证两面用户工具用户工具菜单系统设置29用户工具菜单复印机设置31访问用户工具32更改默认设置32退出用户工具33可以通过用户工具更改的设置34系统设置34复印机功能37用户代码39注册新的用户代码39更改用户代码40删除用户代码40显示每个用户代码的计数器41打印每个用户代码的计数器41清除计数器故障排除如果本机不能正常工作43复印件不清晰44无法正常复印45内存空间用尽时45b装入纸张46装入纸张46方向固定的纸张或双面纸张47d添加碳粉48处理碳粉48碳粉存放48用过的碳粉48取出碳粉49加碳粉50kirc3azhopebookpageiiwednesdaymarch20103

PandaC4cpyZH_Cover1.fm Page 1 Sunday, April 25, 2010 8:43 AM

PR2E系列打印机驱动安装使用说明书1五篇范文[修改版]

![PR2E系列打印机驱动安装使用说明书1五篇范文[修改版]](https://img.taocdn.com/s3/m/4da144057c1cfad6185fa738.png)

第一篇:PR2E系列打印机驱动安装使用说明书1安装使用说明书一,首先检查打印机:。

把打印机取出来打开机器上的盖子。

检查色带是否装好(色带是黑色的长盒子,横卡在上面固定好的。

有时在路上可能会震动松掉)二,然后连接打印机:连接好打印机后面两条线(一条黑色的电源线一条蓝色的连接电脑的数据线)连接好后再前面左下角电源开关。

开起来。

放一A4纸进去。

正常的他会吸住一点点在门口的等待打印的状态。

一切正常后三,打印机驱动安装:不需要光盘。

仿真EPSON LQ1600驱动。

按照以下步骤在电脑上操作XP系统安装驱动步骤打印机驱动安装步骤如下:第一步:点开电脑屏左下角开始——设置——打印机和传真——添加打印机!第二步:点下一步选连接到计算机的本地打印机把自动检测并安装即插即用打印机前面的√去掉,点下一步第三步:、端口选择USB001如果有USB002就选择USB002(要点开右边的向下的箭头会显示端口出来),点下一步第四步:左边出现厂商选择EPSON,右边打印机选择LQ1600K 再点下一步。

然后一直下一步。

一直到完成。

就安装起来了。

如果出现什么提示就在网上联系我们WIN7 系统打印机驱动添加步骤:点开电脑左下角开始菜单设备与打印机现点。

添加打印机选择本地添加打印机端口改成USB001 下一步。

选择厂商和型号这一步后先不要选择要点。

Window Upate 更新驱动(需要几分钟请耐心等待)等更新出驱动后。

左边选择EPSON 右边选择LQ1600K然后再一直。

下一步。

到完成安装就可以了打印机上面的按健功能:上面三个按健:station1(菜单) lock(退纸/暂停) station2(选择)第二篇:条码打印机安装方法(USB端口驱动安装)条码打印机是一种使用非常使用的热转印机,对于大多数人来说,如何安装该机器还是很陌生,下面深圳市互信恒科技将逐一介绍如果安装和使用该机器,以下已示意图来说明如何安装该机器。

安装驱动之前确认打印机已经接好电源,USB线已经跟电脑连接号,标签纸和碳带安装正常,电脑的USB端口使用正常,当前操作系统为XP系统。

南天打印机PR2,PR2E,PR9,PRB,PR3_故障查询手册

PR2为24针打印机是意大利(Italy)好利获得(Olivetti)公司研发生产的机器,是PR50的换代产品.。

它单针直径0.25mm,菱形排列,单针寿命大于4亿次。

打印头里的打印针为单层排列(线圈为5欧姆,目前无法修复位,坏了,就大了,呵呵)。

合盖打印噪音低于小于53分贝,可靠使用时间大于1万小时。

机器有串/并口。

两种联机方式!此机最大优点“随意放纸,自动纠偏;自动对边;自动调节打印头与纸张距离”(这个打印机的打印平台是用2个强力弹簧支撑着,在外界压力下,可以上下活动。

其中打印头上的检测轮,就是起这个作用的。

纸厚时,打印头压力大平台降的幅度大,纸薄则平台的降幅小。

打印头不动,打印平台可以降。

这样,就实现了自动调节纸张距离)。

国内昆明南天公司最早引进生产线(我看到有97年机器,估计生产线要早啊)打印机控制面板为“Nantian”由于“随意放纸,自动纠偏;自动对边;自动调节打印头与纸张距离”省了银行柜员很多事。

这款机器最初南天“Nantian”独家卖,一台PR2—/K12能卖12800.00。

而且供不应求。

据南天一位业务员说,那时候傻子都能买,人家银行款都打帐上了,就等着发机器了。

(估计当时的国产化器件比较少的事,所以贵。

最典型的列子是字车电机,也叫水平电机,97年的旧电机到现在,很少有坏的。

而2000,2001年的字车电机坏的就比较多)后来国内陆续出来了几种PR2 从机器控制面板区分为:湘计(HCC)长江(长江)东南(Olivetti)中航(Olivetti)很多人分不清楚东南(Olivetti)和中航(Olivetti)那么打个自检,看看。

我手里有一台中航(Olivetti)的PR2 在打印自检时。

第一行有“OLIVETTI CATIC PR2中文打印机1.1版本”字样(估计老版本)。

要是机器无法开机,打开机器外壳,看下主板就知道了,中航(Olivetti)比较特殊,是把字库和监控片做为一体,可插拔的(他的监控片坏了,无发替代,你得去找中航)而东南的为一个监控片,一个字库片,都为可插拔的和其他厂家一样。

RPI-121;中文规格书,Datasheet资料

RELATIVE COLLECTOR CURRENT : IC (%)

d

100

100 P D PC 80 60 40 20 0

120 100 80 60 40 20 0 −40 −20 0 20 40 60 80 100

COLLECTOR CURRENT : IC (mA)

/

0.6

0.8

1.0

1.2

1.4

1.6

1.8

10

20

30

40

50

1

10

0

25

50

75

100

DISTANCE : d (mm)

AMBIENT TEMPERATURE : Ta (˚C)

FORWARD VOLTAGE : VF (V)

FORWARD CURRENT : IF (mA)

COLLECTOR CURRENT : IC (mA)

External dimensions (Unit : mm)

Input(LED)

Forward current Reverse voltage Power dissipation Collector-emitter voltage Emitter-collector voltage Collector current Collector power dissipation Operating temperature Storage temperature

中文规格书datasheet资料datasheetdatasheet网站l298ndatasheeticdatasheetpl2303datasheetds18b20datasheetdatasheetcomrt5350datasheetlm324datasheet

17550中文资料