0809LD60中文资料

MC9S08JM60中文手册USB部分

第17章通用串行总线设备控制器 (S08USBV1)17.1 介绍这一章描述了通用串行总线设备控制器 (S08USBV1) 模块,它基于通用串行总线规格版本2.0。

该USB 总线设计目的是替代已经存在的用于PC 机外围设备的RS-232, PS/2, 和 IEEE 1284 总线。

这种S08USBV1 模块提供单片全速(12 Mbps)USB 设备应用的解决方案,而且集成了必需的带有串行接口引擎(SIE )的收发器,3.3-V 调节器, 端点RAM 和其他控制逻辑。

17.1.1 时钟要求S08USBV1需要两个时钟源,一个是24 MHz 总线时钟和一个48 MHz 基准时钟。

它的48 MHz 时钟是直接来自MCGOUT 。

为了获得48 MHz 的时钟速率, MCG 必需被恰当地配置成PLL 使能的外部(PEE) 模式,外接一晶振。

对于USB 操作,例如MCG 配置使用PEE 模式包括: • 2 MHz 晶振 – RDIV = 000 , VDIV = 0110 • 4 MHz 晶振 – RDIV = 001 , VDIV = 011017.1.2 在USB 挂起模式的电流消耗在USB 挂起模式,USB 设备的电流消耗被限制在500 μA 。

当USB 设备进入挂起模式,为了符合USB 挂起模式的电流消耗要求,固件通常进入停止3模式。

注意:允许LVD 将增加在停止模式3下的电流消耗。

因此,为了能满足USB 挂起模式的要求,在进入停止模式3前要禁止LVD 。

F RE E-TE C H飞锐泰克17.1.3 内部3.3V 稳压器如果使用一个外部3.3-V 调节器作为输入给V USB33 (仅仅当USBVREN = 0), 供应电压,V DD , 必须不能低于输入给V USB33引脚的电压。

如果使用内部3.3-V 调节器 (USBVREN = 1), 确保不要把外部供应电压连接到V USB33 引脚。

【免费下载】AD0809中文资料和单片机电路及程序

ADDA

0

1

0

1

0

1

0

1

选中通道

IN0

IN1

IN2

IN3

IN4

IN5

IN6

IN7

的上升沿将逐次逼近寄存器 SAR 复位,在该上升沿之后的 2μs 加 8 个时钟周期内(不定), EOC 信号将变低电平,以指示转换操作正在进行中,直到转换完成后 EOC 再变高电平。 微处理器收到变为高电平的 EOC 信号后,便立即送出 OE 信号,打开三态门,读取转换结 果。

对全部高中资料试卷电气设备,在安装过程中以及安装结束后进行高中资料试卷调整试验;通电检查所有设备高中资料电试力卷保相护互装作置用调与试相技互术关,系电,力根通保据过护生管高产线中工敷资艺设料高技试中术卷资,配料不置试仅技卷可术要以是求解指,决机对吊组电顶在气层进设配行备置继进不电行规保空范护载高与中带资负料荷试下卷高问总中题体资,配料而置试且时卷可,调保需控障要试各在验类最;管大对路限设习度备题内进到来行位确调。保整在机使管组其路高在敷中正设资常过料工程试况中卷下,安与要全过加,度强并工看且作护尽下关可都于能可管地以路缩正高小常中故工资障作料高;试中对卷资于连料继接试电管卷保口破护处坏进理范行高围整中,核资或对料者定试对值卷某,弯些审扁异核度常与固高校定中对盒资图位料纸置试,.卷保编工护写况层复进防杂行腐设自跨备动接与处地装理线置,弯高尤曲中其半资要径料避标试免高卷错等调误,试高要方中求案资技,料术编试交写5、卷底重电保。要气护管设设装线备备置敷4高、调动设中电试作技资气高,术料课中并3中试、件资且包卷管中料拒含试路调试绝线验敷试卷动槽方设技作、案技术,管以术来架及避等系免多统不项启必方动要式方高,案中为;资解对料决整试高套卷中启突语动然文过停电程机气中。课高因件中此中资,管料电壁试力薄卷高、电中接气资口设料不备试严进卷等行保问调护题试装,工置合作调理并试利且技用进术管行,线过要敷关求设运电技行力术高保。中护线资装缆料置敷试做设卷到原技准则术确:指灵在导活分。。线对对盒于于处调差,试动当过保不程护同中装电高置压中高回资中路料资交试料叉卷试时技卷,术调应问试采题技用,术金作是属为指隔调发板试电进人机行员一隔,变开需压处要器理在组;事在同前发一掌生线握内槽图部内 纸故,资障强料时电、,回设需路备要须制进同造行时厂外切家部断出电习具源题高高电中中源资资,料料线试试缆卷卷敷试切设验除完报从毕告而,与采要相用进关高行技中检术资查资料和料试检,卷测并主处且要理了保。解护现装场置设。备高中资料试卷布置情况与有关高中资料试卷电气系统接线等情况,然后根据规范与规程规定,制定设备调试高中资料试卷方案。

ad0809-19用户手册

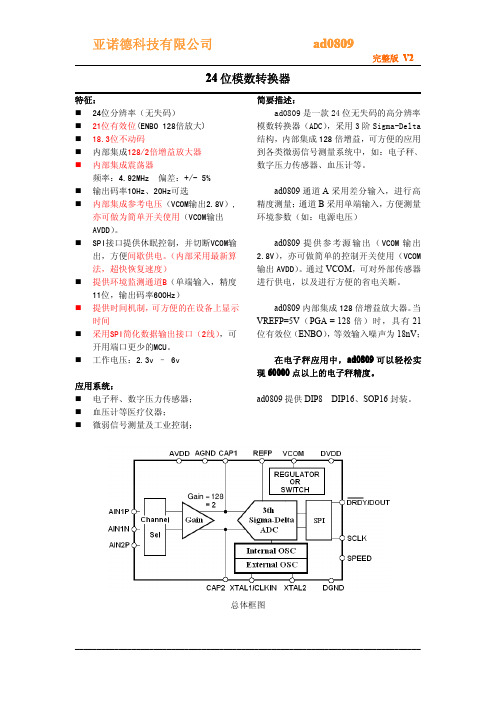

ad0809

完整版 V2

单位 V V V V V ℃ ℃

电器参数:

测试条件: AVDD = DVDD = VREFP = +5V;温度范围:-25 – 80 摄氏度;采用外置晶振:4.9152MHz 参数 条件 最小值 输入信号 差分电压输入 (VINP – VINN) 共模输入范围 输出数据频率 输入信号带宽 VREFP 1.5 ADC 性能 分辨率 等效输入噪声 积分非线性 (INL) 输入失调 输入失调温漂 PGA = 2 PGA = 128 PGA = 128 24 18n 0.0002 0.0005 3 +/-10 0.001 0.001 5 bit V % of FS % of FS % of FS AGND + 1.5 10、80 2.5、20 AVDD AVDD + 0.3 AVDD - 1.5 V Hz Hz V PGA = 128 +/- 0.5 VREFP /128 V 取值范围 典型值 最大值 单位

封装 DIP16 SOP16 DIP16 SOP16

功能 内部参考原电路做为简单开关使用( VCOM 输出 AVDD) 。 内部参考原电路工作(VCOM 输出 2.8V)

功能模块描述:

0000000h 输入为负

000000h FFFFFFh – 800000h

∆Σ ADC

ad0809 的 核 心 部 分 为 采 用 3 阶 Sigma-Delta 调制器结构的模数转换器,其 内部集成可编程增益(PGA = 2,128) 该调制器对输入模拟差分信号的采样 频率为 76.8KHz,远高于模拟信号的最大带 宽, 因而简化了应用时输入通道的前置防混 叠滤波器。

完整版 V2

19.6 18.6

W39V080FAQ中文资料

W39V080FA Data Sheet1M × 8 CMOS FLASH MEMORYWITH FWH INTERFACE Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.PIN CONFIGURATIONS (4)4.BLOCK DIAGRAM (4)5.PIN DESCRIPTION (4)6.FUNCTIONAL DESCRIPTION (5)6.1Interface Mode Selection and Description (5)6.2Read (Write) Mode (5)6.3Reset Operation (5)6.4Accelerated Program Operation (5)6.5Boot Block Operation and Hardware Protection at Initial- #TBL & #WP (5)6.6Sector Erase Command (6)6.7Program Operation (6)6.8Dual BIOS (6)6.9Hardware Data Protection (6)6.10Write Operation Status (7)6.10.1DQ7: #Data Polling (7)6.10.2RY/#BY: Ready/#Busy (7)6.10.3DQ6: Toggle Bit (7)6.10.4DQ5: Exceeded Timing Limits (8)6.11Identification Input pin ID[3:0] (8)6.12Register (8)6.12.1General Purpose Inputs Register (8)6.12.2Block Locking Registers (8)6.12.3Product Identification Registers (10)6.13Table of Operating Modes (11)6.13.1Operating Mode Selection - Programmer Mode (11)6.13.2Operating Mode Selection - FWH Mode (11)6.14Fwh Cycle Definition (12)6.15Embedded Programming Algorithm (13)6.16Embedded Erase Algorithm (14)6.17Embedded #Data Polling Algorithm (15)6.18Embedded Toggle Bit Algorithm (16)6.19Software Product Identification and Boot Block Lockout Detection Acquisition Flow..177.DC CHARACTERISTICS (18)7.1Absolute Maximum Ratings (18)7.2Programmer interface Mode DC Operating Characteristics (18)7.3FWH interface Mode DC Operating Characteristics (19)7.4Power-up Timing (19)7.5Capacitance (19)Publication Release Date: Dec. 13, 2005W39V080FA8.PROGRAMMER INTERFACE MODE AC CHARACTERISTICS (20)8.1AC Test Conditions (20)8.2AC Test Load and Waveform (20)8.3Read Cycle Timing Parameters (21)8.4Write Cycle Timing Parameters (21)8.5Data Polling and Toggle Bit Timing Parameters (21)9.TIMING WAVEFORMS FOR PROGRAMMER INTERFACE MODE (22)9.1Read Cycle Timing Diagram (22)9.2Write Cycle Timing Diagram (22)9.3Program Cycle Timing Diagram (23)9.4#DATA Polling Timing Diagram (23)9.5Toggle Bit Timing Diagram (24)9.6Sector Erase Timing Diagram (24)10.FWH INTERFACE MODE AC CHARACTERISTICS (25)10.1AC Test Conditions (25)10.2Read/Write Cycle Timing Parameters (25)10.3Reset Timing Parameters (25)11.TIMING WAVEFORMS FOR FWH INTERFACE MODE (26)11.1Read Cycle Timing Diagram (26)11.2Write Cycle Timing Diagram (26)11.3Program Cycle Timing Diagram (27)11.4#DATA Polling Timing Diagram (28)11.5Toggle Bit Timing Diagram (29)11.6Sector Erase Timing Diagram (30)11.7FGPI Register/Product ID Readout Timing Diagram (31)11.8Reset Timing Diagram (31)12.ORDERING INFORMATION (32)13.HOW TO READ THE TOP MARKING (32)14.PACKAGE DIMENSIONS (33)14.132L PLCC (33)14.232L STSOP (8X14mm) (33)14.340L TSOP (10 mm x 20 mm) (34)15.VERSION HISTORY (35)W39V080FAPublication Release Date: Dec. 13, 20051. GENERAL DESCRIPTIONThe W39V080FA is an 8-megabit, 3.3-volt only CMOS flash memory organized as 1M × 8 bits. For flexible erase capability, the 8Mbits of data are divided into 16 uniform sectors of 64 Kbytes. The device can be programmed and erased in-system with a standard 3.3V power supply. A 12-volt VPP is required for accelerated program. The unique cell architecture of the W39V080FA results in fast program/erase operations with extremely low current consumption. This device can operate at two modes, Programmer bus interface mode and FWH bus interface mode. As in the Programmer interface mode, it acts like the traditional flash but with a multiplexed address inputs. But in the FWH interface mode, this device complies with the Intel FWH specification. The device can also be programmed and erased using standard EPROM programmers.2. FEATURES•Single 3.3-volt operations: − 3.3-volt Read − 3.3-volt Erase − 3.3-volt Program• Fast program operation: − VPP = 12V− Byte-by-Byte programming: 9 μS (typ.) • Fast erase operation:− Sector erase 0.9 Sec. (typ.) • Fast read access time: Tkq 11 nS • Endurance: 30K cycles (typ.) • Twenty-year data retention • 16 Even sectors with 64K bytes • Any individual sector can be erased • Dual BIOS function− Full-chip partition with 8M-bit or dual-block partition with 4M-bit •Hardware protection:− #TBL supports 64-Kbyte Boot Block hardware protection− #WP supports the whole chip except Boot Block hardware protection• Hardware Features•Ready/#Busy output (RY/#BY)− Detect program or erase cycle completion • Hardware reset pin (#RESET)− Reset the internal state machine to the readmode• VPP input pin− Acceleration (ACC) function acceleratesprogram timing• Low power consumption− Read Active current: 15 mA (typ. for FWH mode)• Automatic program and erase timing with internal V PP generation• End of program or erase detection − Toggle bit − Data polling• Latched address and data • TTL compatible I/O• Available packages: 32L PLCC, 32L STSOP,40L TSOP(10 x 20 mm), 32L PLCC Lead free, 32L STSOP Lead free and 40L TSOP (10 x 20 mm) Lead freeW39V080FA3. PIN CONFIGURATIONS4. BLOCK DIAGRAM5. PIN DESCRIPTIONINTERFACE SYM.PGM FWH PIN NAMEIC**Interface Mode Selection#RESET * * Reset#INIT * Initialize#TBL * Top Boot Block Lock #WP * Write Protect CLK * CLK InputFGPI[4:0]*General Purpose InputsID[3:0] *Identification Inputs Pull Down with Internal Resistors FWH[3:0] * Address/Data InputsFWH4 * FWH Cycle InitialD/#F *Dual Bios/Full ChipPull Down with Internal Resistors U/#L *Upper 4M/Lower 4MPull Down with Internal Resistors R/#C * Row/Column Select A[10:0] * Address Inputs DQ[7:0]* Data Inputs/Outputs#OE * Output Enable #WE * Write Enable RY/#BY* Ready/ BusyVDD * * Power Supply VSS * * Ground VPP * * Accelerate Program Power Supply RSV * * Reserved PinsNC**No ConnectionW39V080FA6. FUNCTIONAL DESCRIPTION6.1 Interface Mode Selection and DescriptionThis device can operate in two interface modes, one is Programmer interface mode, and the other is FWH interface mode. The IC pin of the device provides the control between these two interface modes. These interface modes need to be configured before power up or return from #RESET. When IC pin is set to high state, the device will be in the Programmer mode; while the IC pin is set to low state (or leaved no connection), it will be in the FWH mode. In Programmer mode, this device just behaves like traditional flash parts with 8 data lines. But the row and column address inputs are multiplexed. The row address are mapped to the higher internal address A[19:11]. And the column address are mapped to the lower internal address A[10:0]. For FWH mode, It complies with the FWH Interface Specification. Through the FWH[3:0] and FWH4 to communicate with the system chipset .6.2 Read (Write) ModeIn Programmer interface mode, the read (write) operation of the W39V080FA is controlled by #OE (#WE). The #OE (#WE) is held low for the host to obtain (write) data from (to) the outputs (inputs). #OE is the output control and is used to gate data from the output pins. The data bus is in high impedance state when #OE is high. As for in the FWH interface mode, the read or write is determined by the "bit 0 & bit 1 of START CYCLE ". Refer to the FWH cycle definition and timing waveforms for further details.6.3 Reset OperationThe #RESET input pin can be used in some application. When #RESET pin is at high state, the device is in normal operation mode. When #RESET pin is at low state, it will halt the device and all outputs will be at high impedance state. As the high state re-asserted to the #RESET pin, the device will return to read or standby mode, it depends on the control signals.6.4 Accelerated Program OperationThe device provides accelerated program operations through the ACC function. This function is primarily intended to allow a faster manufacturing throughput in the factory.6.5 Boot Block Operation and Hardware Protection at Initial- #TBL & #WPThere is a hardware method to protect the top boot block and other sectors. Before power on programmer, tie the #TBL pin to low state and then the top boot block will not be programmed/erased. If #WP pin is tied to low state before power on, the other sectors will not be programmed/erased.In order to detect whether the boot block feature is set on or not, users can perform software command sequence: enter the product identification mode (see Command Codes for Identification/Boot Block Lockout Detection for specific code), and then read from address FFFF2(hex). You can check the DQ2/DQ3 at the address FFFF2 to see whether the #TBL/#WP pin is in low or high state. If the DQ2 is “0”, it means the #TBL pin is tied to high state. In such condition, whether boot block can be programmed/erased or not will depend on software setting. On the other hand, if the DQ2 is “1”, it means the #TBL pin is tied to low state, then boot block is locked no matter how the software is set. Like the DQ2, the DQ3 inversely mirrors the #WP state. If the DQ3 is “0”, it means the #WP pin is in high state, then all the sectors except the boot block can be programmed/erased. On the other hand, if the DQ3 is “1”, then all the sectors except the boot block are programmed/erased inhibited.To return to normal operation, perform a three-byte command sequence (or an alternate single-byte command) to exit the identification mode. For the specific code, see Command Codes for Identification/Boot Block Lockout Detection.Publication Release Date: Dec. 13, 2005W39V080FA6.6 Sector Erase CommandSector erase is a six bus cycles operation. There are two "unlock" write cycles, followed by writing the "set-up" command. Two more "unlock" write cycles then follows by the Sector erase command. The Sector address (any address location within the desired Sector) is latched on the rising edge of R/#C in programmer mode, while the command (30H) is latched on the rising edge of #WE.Sector erase does not require the user to program the device prior to erase. When erasing a Sector, the remaining unselected sectors are not affected. The system is not required to provide any controls or timings during these operations.The automatic Sector erase begins after the erase command is completed, right from the rising edge of the #WE pulse for the last Sector erase command pulse and terminates when the data on DQ7, Data Polling, is "1" at which time the device returns to the read mode. Data Polling must be performed at an address within any of the sectors being erased.Refer to the Erase Command flow Chart using typical command strings and bus operations.6.7 Program OperationThe W39V080FA is programmed on a byte-by-byte basis. Program operation can only change logical data "1" to logical data "0." The erase operation, which changed entire data in main memory and/or boot block from "0" to "1", is needed before programming.The program operation is initiated by a 4-byte command cycle (see Command Codes for Byte Programming). The device will internally enter the program operation immediately after the byte-program command is entered. The internal program timer will automatically time-out (9μS typ.-T BP) once it is completed and then return to normal read mode. Data polling and/or Toggle Bits can be used to detect end of program cycle.6.8 Dual BIOSThe W39V080FA provides a solution for Dual-BIOS application. In FWH mode, when D/#F is low, the device functions as a full-chip partition of 8M-bit which address ranges from FFFFFh to 00000h with A[19:0]. If D/#F is driven high, the device functions as a dual-block partition that each block consists of 4M-bit. For dual-block partition, there is only one 4M-bit block, either upper or lower, can be accessed. The U/#L pin selects either upper or lower 4M-bit block and its address ranges from 7FFFFh to 00000h with A[19:0]. When U/#L is low, the lower 4M-bit block will be selected; while, U/#L is high, the upper 4M-bit block will be selected.6.9 Hardware Data ProtectionThe integrity of the data stored in the W39V080FA is also hardware protected in the following ways:(1) Noise/Glitch Protection: A #WE pulse of less than 15 nS in duration will not initiate a write cycle.(2) V DD Power Up/Down Detection: The programming and read operation are inhibited when V DD isless than 2.0V typical.(3) Write Inhibit Mode: Forcing #OE low or #WE high will inhibit the write operation. This preventsinadvertent writes during power-up or power-down periods.W39V080FA6.10 Write Operation StatusThe device provides several bits to determine the status of a program or erase operation: DQ5, DQ6, and DQ7. Each of DQ7 and DQ6 provides a method for determining whether a program or erase operation is complete or in progress. The device also offers a hardware-based output signal, RY/#BY in programmer mode, to determine whether an Embedded Program or Erase operation is in progress or has been completed.6.10.1 DQ7: #Data PollingThe #Data Polling bit, DQ7, indicates whether an Embedded Program or Erase algorithm is in progress or completed. Data Polling is valid after the rising edge of the final #WE pulse in the command sequence.During the Embedded Program algorithm, the device outputs on DQ7 and the complement of the data programmed to DQ7. Once the Embedded Program algorithm has completed, the device outputs the data programmed to DQ7. The system must provide the program address to read valid status information on DQ7. If a program address falls within a protected sector, #Data Polling on DQ7 is active for about 1μS, and then the device returns to the read mode.During the Embedded Erase algorithm, #Data Polling produces “0” on DQ7. Once the Embedded Erase algorithm has completed, #Data Polling produces “1” on DQ7. An address within any of the sectors selected for erasure must be provided to read valid status information on DQ7.After an erase command sequence is written, if all sectors selected for erasing are protected, #Data Polling on DQ7 is active for about 100μS, and then the device returns to the read mode. If not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selected sectors that are protected. However, if the system reads DQ7 at an address within a protected sector, the status may not be valid.Just before the completion of an Embedded Program or Erase operation, DQ7 may change asynchronously with DQ0-DQ6 while Output Enable (#OE) is set to low. That is, the device may change from providing status information to valid data on DQ7. Depending on when it samples the DQ7 output, the system may read the status or valid data. Even if the device has completed the program or erase operation and DQ7 has valid data, the data outputs on DQ0-DQ6 may be still invalid. Valid data on DQ7-DQ0 will appear on successive read cycles.6.10.2 RY/#BY: Ready/#BusyThe RY/#BY is a dedicated, open-drain output pin which indicates whether an Embedded Algorithm is in progress or complete. The RY/#BY status is valid after the rising edge of the final #WE pulse in the command sequence. Since RY/#BY is an open-drain output, several RY/#BY pins can be tied together in parallel with a pull-up resistor to V DD.When the output is low (Busy), the device is actively erasing or programming. When the output is high (Ready), the device is in the read mode or standby mode.6.10.3 DQ6: Toggle BitToggle Bit on DQ6 indicates whether an Embedded Program or Erase algorithm is in progress or complete. Toggle Bit I may be read at any address, and is valid after the rising edge of the final #WE pulse in the command sequence (before the program or erase operation), and during the sector erase time-out.During an Embedded Program or Erase algorithm operation, successive read cycles to any address cause DQ6 to toggle. The system may use either #OE to control the read cycles. Once the operation has completed, DQ6 stops toggling.Publication Release Date: Dec. 13, 2005W39V080FAAfter an erase command sequence is written, if all sectors selected for erasing are protected, DQ6toggles for about 100μS, and then returns to reading array data. If not all selected sectors are protected, the Embedded Erase algorithm erases the unprotected sectors, and ignores the selectedsectors which are protected.The system can use DQ6 to determine whether a sector is actively erasing. If the device is activelyerasing (i.e., the Embedded Erase algorithm is in progress), DQ6 toggles. If a program address fallswithin a protected sector, DQ6 toggles for about 1 μs after the program command sequence is written,and then returns to reading array data.6.10.4 DQ5: Exceeded Timing LimitsDQ5 indicates whether the program or erase time has exceeded a specified internal pulse count limit.DQ5 produces “1” under these conditions which indicates that the program or erase cycle was not successfully completed.The device may output “1” on DQ5 if the system tries to program “1” to a location that was previously programmed to “0.” Only the erase operation can change “0” back to “1.” Under this condition, thedevice stops the operation, and while the timing limit has been exceeded, DQ5 produces “1.”Under both these conditions, the system must hardware reset to return to the read mode.6.11 Identification Input pin ID[3:0]These pins are part of mechanism that allows multiple parts to be used on the same bus. The bootdevice should be 0000b. And all the subsequent parts should use the up-count strapping.6.12 RegisterThere are three kinds of registers on this device, the General Purpose Input Registers, the Block LockControl Registers and Product Identification Registers. Users can access these registers through respective address in the 4Gbytes memory map. There are detail descriptions in the sections below.6.12.1 General Purpose Inputs RegisterThis register reads the FGPI[4:0] pins on the W39V080FA.This is a pass-through register which canread via memory address FFBC0100(hex). Since it is pass-through register, there is no default value.GPI Register TableBIT FUNCTION7 − 5 Reserved4 Read FGPI4 pin status3 Read FGPI3 pin status2 Read FGPI2 pin status1 Read FGPI1 pin status0 Read FGPI0 pin status6.12.2 Block Locking RegistersThis part provides 16 even 64Kbytes blocks, and each block can be locked by register control. Thesecontrol registers can be set or clear through memory address. Below is the detail description.W39V080FAPublication Release Date: Dec. 13, 2005Block Locking Registers type and access memory map TableREGISTERSREGISTERSTYPECONTROL BLOCKDEVICE PHYSICALADDRESS4GBYTES SYSTEM MEMORY ADDRESSBLR15 R/W 15 0FFFFFh – 0F0000h FFBF0002h BLR14 R/W 14 0EFFFFh – 0E0000h FFBE0002h BLR13 R/W 13 0DFFFFh – 0D0000h FFBD0002h BLR12 R/W 12 0CFFFFh – 0C0000h FFBC0002h BLR11 R/W 11 0BFFFFh – 0B0000h FFBB0002h BLR10 R/W 10 0AFFFFh – 0A0000h FFBA0002h BLR9 R/W 9 09FFFFh – 090000h FFB90002h BLR8 R/W 8 08FFFFh – 080000h FFB80002h BLR7 R/W 7 07FFFFh – 070000h FFB70002h BLR6 R/W 6 06FFFFh – 060000h FFB60002h BLR5 R/W 5 05FFFFh – 050000h FFB50002h BLR4 R/W 4 04FFFFh – 040000h FFB40002h BLR3 R/W 3 03FFFFh – 030000h FFB30002h BLR2 R/W 2 02FFFFh – 020000h FFB20002h BLR1 R/W 1 01FFFFh – 010000h FFB10002h BLR0R/W00FFFFh – 000000hFFB00002hBlock Locking Register Bits Function TableBIT FUNCTION7 – 3 Reserved2 Read Lock1: Prohibit to read in the block where set0: Normal read operation in the block where clear. This is default state.1 Lock Down1: Prohibit further to set or clear the Read Lock or Write Lock bits. This Lock Down Bit can only be set not clear. Only the device is reset or re-powered, the Lock Down Bit is cleared.0: Normal operation for Read Lock or Write Lock. This is the default state. 0 Write Lock1: Prohibited to write in the block where set. This is default state. 0: Normal programming/erase operation in the block where clear.W39V080FARegister Based Block Locking Value Definitions TableBIT [7:3] BIT 2 BIT 1 BIT 0 RESULTAccess.Full00000 0 0 000000 0 0 1 Write Lock. Default State.00000 0 1 0 Locked Open (Full Access, Lock Down).00000 0 1 1 Write Locked, Locked Down.Locked.Read00000 1 0 000000 1 0 1 Read & Write Locked.00000 1 1 0 Read Locked, Locked Down.00000 1 1 1 Read & Write Locked, Locked Down.Read LockAny attempt to read the data of read locked block will result in “00H.” The default state of any block is unlocked upon power up. User can clear or set the write lock bit anytime as long as the lock down bit is not set.Write LockThis is the default state of blocks upon power up. Before any program or erase to the specified block, user should clear the write lock bit first. User can clear or set the write lock bit anytime as long as the lock down bit is not set. The write lock function is in conjunction with the hardware protect pins, #WP & TBL. When hardware protect pins are enabled, it will override the register block locking functions and write lock the blocks no matter how the status of the register bits. Reading the register bit will not reflect the status of the #WP or #TBL pins.Lock DownThe default state of lock down bit for any block is unlocked. This bit can be set only once; any further attempt to set or clear is ignored. Only the reset from #RESET or #INIT can clear the lock down bit. Once the lock down bit is set for a block, then the write lock bit & read lock bit of that block will not be set or cleared, and keep its current state.6.12.3 Product Identification RegistersThere is an alternative software method to read out the Product Identification in both the Programmer interface mode and the FWH interface mode. Thus, the programming equipment can automatically matches the device with its proper erase and programming algorithms.In the full-chip(8Mb) FWH interface mode, a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC, 0001(hex) can output the device code, D3(hex).For Dual-BIOS(4Mbx2) FWH mode , a read from FFBC, 0000(hex) can output the manufacturer code, DA(hex). A read from FFBC,0001(hex) can output the device code 93(hex).In the software access mode, a JEDEC 3-byte command sequence can be used to access the product ID for programmer interface mode. A read from address 0000(hex) outputs the manufacturer code, DA(hex). A read from address 0001(hex) outputs the device code, D3(hex).” The product ID operation can be terminated by a three-byte command sequence or an alternate one-byte command sequence (see Command Definition table for detail).W39V080FAPublication Release Date: Dec. 13, 20056.13 Table of Operating Modes6.13.1 Operating Mode Selection - Programmer ModeMODE PINS#OE#WE#RESETADDRESSDQ.Read V IL V IH V IH AIN Dout Write V IH V ILV IHAIN DinStandby X X V IL X High ZWrite Inhibit V IL X V IH X High Z/DOUT X V IH V IH X High Z/DOUTOutput DisableV IH X V IH X High Z6.13.2 Operating Mode Selection - FWH ModeOperation modes in FWH interface mode are determined by "START Cycle" when it is selected. When it is not selected, its outputs (FWH[3:0]) will be disable. Please reference to the "FWH Cycle Definition".Table of Command DefinitionCOMMAND NO. OF 1ST CYCLE 2ND CYCLE 3RD CYCLE 4TH CYCLE 5TH CYCLE 6TH CYCLE DESCRIPTION Cycles (1)Addr. Data Addr. DataAddr. DataAddr. DataAddr. DataAddr. DataRead 1 A IN D OUTSector Erase 6 5555 AA 2AAA 555555 805555 AA 2AAA 55SA (5)30Byte Program 4 5555 AA 2AAA 555555 A0A IN D INProduct ID Entry 3 5555 AA 2AAA 555555 90 Product ID Exit (4)35555 AA2AAA 555555 F0Product ID Exit (4) 1 XXXX F0 Notes: 1. The cycle means the write command cycle not the FWH clock cycle. 2. The Column Address / Row Address are mapped to the Low / High order Internal Address. i.e. Column Address A[10:0] are mapped to the internal A[10:0], Row Address A[7:0] are mapped to the internal A[19:11] 3. Address Format: A14−A0 (Hex); Data Format: DQ7-DQ0 (Hex) 4. Either one of the two Product ID Exit commands can be used. 5. SA: Sector AddressSA = FXXXXh for Unique Sector15 (Boot Sector) SA = 7XXXXh for Unique Sector7 SA = EXXXXh for Unique Sector14 SA = 6XXXXh for Unique Sector6 SA = DXXXXh for Unique Sector13 SA = 5XXXXh for Unique Sector5 SA = CXXXXh for Unique Sector12 SA = 4XXXXh for Unique Sector4 SA = BXXXXh for Unique Sector11 SA = 3XXXXh for Unique Sector3 SA = AXXXXh for Unique Sector10 SA = 2XXXXh for Unique Sector2 SA = 9XXXXh for Unique Sector9 SA = 1XXXXh for Unique Sector1 SA = 8XXXXh for Unique Sector8SA = 0XXXXh for Unique Sector0W39V080FA6.14 Fwh Cycle DefinitionFIELDNO. OF CLOCKSDESCRIPTIONSTART 1"1101b" indicates FWH Memory Read cycle; while "1110b" indicates FWHMemory Write cycle. 0000b" appears on FWH bus to indicate the initial IDSEL 1 This one clock field indicates which FWH component is being selected. MSIZE 1 Memory Size. There is always show “0000b” for single byte access. TAR2Turned Around TimeADDR 7Address Phase for Memory Cycle. FWH supports the 28 bits address protocol. The addresses transfer most significant nibble first and leastsignificant nibble last. (i.e. Address[27:24] on FWH[3:0] first, and Address[3:0] on FWH[3:0] last.) SYNC N Synchronous to add wait state. "0000b" means Ready, "0101b" means ShortWait, "0110b" means Long Wait, "1001b" for DMA only, "1010b" meanserror, and other values are reserved. DATA 2 Data Phase for Memory Cycle. The data transfer least significant nibble firstand most significant nibble last. (i.e. DQ[3:0] on FWH[3:0] first, then DQ[7:4]on FWH[3:0] last.)W39V080FA 6.15 Embedded Programming AlgorithmPublication Release Date: Dec. 13, 2005W39V080FA 6.16 Embedded Erase AlgorithmW39V080FA 6.17 Embedded #Data Polling AlgorithmPublication Release Date: Dec. 13, 2005W39V080FA 6.18 Embedded Toggle Bit AlgorithmW39V080FAPublication Release Date: Dec. 13, 20056.19 Software Product Identification and Boot Block Lockout Detection AcquisitionFlowNotes for software product identification/boot block lockout detection:(1) Data Format: DQ7−DQ0 (Hex); Address Format: A14−A0 (Hex)(2) A1−A19 = V IL ; manufacture code is read for A0 = V IL ; device code is read for A0 = V IH .(3) The device does not remain in identification and boot block lockout detection mode if power down. (4) The DQ[3:2] to indicate the sectors protect status as below:DQ2 DQ30 64Kbytes Boot Block Unlocked by #TBL hardware trappingWhole Chip Unlocked by #WP hardware trapping Except Boot Block164Kbytes Boot Block Locked by #TBL hardware trappingWhole Chip Locked by #WP hardware trapping Except Boot Block(5) The device returns to standard operation mode.(6) Optional 1-write cycle (write F0 (hex.) at XXXX address) can be used to exit the product identification/boot block lockoutdetection.W39V080FA7. DC CHARACTERISTICS7.1 Absolute Maximum RatingsPARAMETER RATINGUNIT Power Supply Voltage to V SS Potential -0.5 to +4.0 VOperating Temperature 0 to +70 °CStorage Temperature -65 to +150 °CD.C. Voltage on Any Pin to Ground Potential -0.5 to V DD +0.5 VV PP Voltage -0.5 to +13 VTransient Voltage (<20 nS) on Any Pin to Ground Potential -1.0 to V DD +0.5 VNote: Exposure to conditions beyond those listed under Absolute Maximum Ratings May adversely affect the life and reliabilityof the device.7.2 Programmer interface Mode DC Operating Characteristics(V DD = 3.3V ± 0.3V, V SS= 0V, T A = 0 to 70° C)LIMITSPARAMETER SYM. TESTCONDITIONSMIN.TYP. MAX.UNITPower Supply Current (read)I CC1In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3 MHz- 15 20 mAPower Supply Current (erase/ write)I CC2In Read or Write mode, all DQs openAddress inputs = 3.0V/0V, at f = 3 MHz- 35 45mAInput Leakage Current I LI V IN = V SS to V DD --90μAOutput Leakage Current I LO V OUT = V SS to V DD --90μAInput Low Voltage V IL - -0.5-0.8V Input High Voltage V IH - 2.0-V DD +0.5VOutput Low Voltage V OL I OL = 2.1 mA - - 0.45 VOutput High Voltage V OH I OH = -0.1mA 2.4- - V。

TL080中文资料

元器件交易网IMPORTANT NOTICETexas Instruments (TI) reserves the right to make changes to its products or to discontinue any semiconductorproduct or service without notice, and advises its customers to obtain the latest version of relevant informationto verify, before placing orders, that the information being relied on is current.TI warrants performance of its semiconductor products and related software to the specifications applicable atthe time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques areutilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of eachdevice is not necessarily performed, except those mandated by government requirements.Certain applications using semiconductor products may involve potential risks of death, personal injury, orsevere property or environmental damage (“Critical Applications”).TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTEDTO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHERCRITICAL APPLICATIONS.Inclusion of TI products in such applications is understood to be fully at the risk of the customer. Use of TIproducts in such applications requires the written approval of an appropriate TI officer. Questions concerningpotential risk applications should be directed to TI through a local SC sales office.In order to minimize risks associated with the customer’s applications, adequate design and operatingsafeguards should be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance, customer product design, software performance, orinfringement of patents or services described herein. Nor does TI warrant or represent that any license, eitherexpress or implied, is granted under any patent right, copyright, mask work right, or other intellectual propertyright of TI covering or relating to any combination, machine, or process in which such semiconductor productsor services might be or are used.Copyright © 1995, Texas Instruments Incorporated。

ld中文手册完全版%28带目录%29

ld中文使用手册完全版(译)-1、概述 (4)2、命令行选项 (5)2.1、连接器提供大量的命令行选项 (5)2.2、连接脚本 (5)2.3、对于名称是单个字符的选项 (5)2.4、对于名称是多个字符的选项,选项前可以有一个或两个破折号; (5)2.5、多字符选项的参数 (5)2.5、如果连接器通过,被编译器驱动来间接引用(比如GCC), (6)2.5.1、被GNU连接器接受的常用命令行开关的一个列表 (6)`-aKEYWORD' (6)`-AARCHITECTURE'`--architecture=ARCHITECTURE' (6)`-b INPUT-formAT'`--format=INPUT-formAT' (6)`-cMRI-COMMANDFILE' (6)`-d'`-dc'`-dp' (6)`-e ENTRY'`--entry=ENTRY' (6)`-E'`--export-dynamic' (6)`-EB'连接big-endian对象. 会影响缺省输出格式 (7)`-EL'连接little-endian对象. 会影响缺省输出格式 (7)`-g'忽略. 为了跟其它工具兼容而提供 (7)`-i'执行一个增量连接(跟'-r'等同) (7)`-init NAME' (7)`-lARCHIVE'`--library=ARCHIVE' (7)`-M'`--print-map'打印一个连接位图到标准输出 (7)`-n'`--nmagic', (7)`-N'`--omagic' (7)`--no-omagic' (7)`-o OUTPUT'`--output=OUTPUT' (7)`-O LEVEL' (7)`-q'`--emit-relocs' (7)`-r'`--relocateable' (7)`-R FILENAME'`--just-symbols=FILENAME' (8)`-s'`--strip-all',忽略输出文件中所有的符号信息 (8)`-S'`--strip-debug'忽略输出文件中所有的调试符号信息(但不是所有符号). (8)`-t'`--trace',打印ld处理的所有输入文件的名字 (8)`-T SCRIPTFILE'`--script=SCRIPTFILE' (8)`-u SYMBOL'`--undefined=SYMBOL' (8)`-Ur' (8)`--unique[=SECTION]' (8)`-v'`--version' `-V' (8)`-x'`--discard-all'删除所有的本地符号. (8)`-X'`--discard-locals' (8)`-y SYMBOL'`--trace-symbol=SYMBOL' (8)`-z KEYWORD' (8)`-( ARCHIVES -)'`--start-group ARCHIVES --end-group' (9)`--accept-unknown-input-arch' (9)`-assert KEYWORD'这个选项被忽略,只是用来跟SunOS保持兼容 (9)`-Bdynamic'`-dy'`-call_shared'连接动态链接库 (9)`-Bgroup' (9)'--no-undefined' (9)`-Bstatic'`-dn' `-non_shared' `-static' (9)`-Bsymbolic' (9)`--check-sections'`--no-check-sections' (10)`--cref' (10)`--no-define-common' (10)`--defsym SYMBOL=EXPRESSION' (10)`--demangle[=style]' `--no-demangle' (10)`--dynamic-linker FILE' (10)`--embedded-relocs' (10)`--fatal-warnings'把所有的警告视为错误 (10)`--force-exe-suffix'确保输出文件有一个.exe后缀 (10)`--no-gc-sections'`--gc-sections' (11)`--help'在标准输出上打印一个命令行选项概要,然后退出. (11)`--target-help' (11)`-Map MAPFILE' (11)`--no-keep-memory' (11)`--no-undefined'`-z defs' (11)`--allow-multiple-definition'`-z muldefs' (11)`--allow-shlib-undefined' `--no-allow-shlib-undefined' (11)`--no-undefined-version' (11)`--no-warn-mismatch' (11)`--no-whole-archive' (11)`--noinhibit-exec' (11)`-nostdlib' (12)`--oformat OUTPUT-formAT' (12)`-qmagic'这个选项被忽略,只是为了跟Linux保持兼容 (12)`-Qy'这个选项被忽略,只是为了跟SVR4保持兼容. (12)`--relax' (12)`--retain-symbols-file FILENAME' (12)'--retain-symbols-file' (12)`-rpath DIR' (12)`-rpath-link DIR' (12)`-shared'`-Bshareable' (13)`--sort-common' (13)`--split-by-file [SIZE]' (13)`--split-by-reloc [COUNT]' (13)`--traditional-format' (13)'--trafitinal-format'开关告诉ld 不要把相同的入口合并起来 (13)`--section-start SECTIONNAME=ORG' (13)`-Tbss ORG'`-Tdata ORG' `-Ttext ORG' (14)`--dll-verbose'`--verbose' (14)`--version-script=VERSION-SCRIPTFILE' (14)`--warn-common' (14)`--warn-constructors' (14)`--warn-multiple-gp' (15)`--warn-once' (15)`--warn-section-align' (15)`--whole-archive' (15)`--wrap SYMBOL' (15)`--enable-new-dtags'`--disable-new-dtags' (15)i386 PE平台的特定选项 (15)`--add-stdcall-alias' (16)`--base-file FILE' (16)`--enable-stdcall-fixup'`--disable-stdcall-fixup' (16)`--export-all-symbols' (16)3、环境变量 (16)`GNUTARGET' (16)`LDEMULATION' (16)4、连接脚本 (17)4.1、基本的连接脚本的概念 (17)4.1.1、三种节 (17)4.1.2、每一个loadable或allocatable的输出节有两个地址 (17)4.1.3、每一个目标文件还有一个关于符号的列表, 被称为'符号表' (17)4.2、连接脚本的格式 (18)4.3、简单的连接脚本示例 (18)4.4、简单的连接脚本命令 (19)4.4.1、设置入口点. (19)4.4.2、处理文件的命令. (19)`INCLUDE FILENAME' (19)`INPUT(FILE, FILE, ...)'`INPUT(FILE FILE ...)' (19)`GROUP(FILE, FILE, ...)'`GROUP(FILE FILE ...)' (19)`OUTPUT(FILENAME)' (19)`SEARCH_DIR(PATH)' (19)`STARTUP(FILENAME)' (20)4.5、处理目标文件格式的命令 (20)`OUTPUT_formAT(BFDNAME)'`OUTPUT_formAT(DEFAULT, BIG, LITTLE)' (20)`TARGET(BFDNAME)' (20)4.6、其它的连接脚本命令 (20)`EXTERN(SYMBOL SYMBOL ...)'. (20)`FORCE_COMMON_ALLOCATION' (20)`INHIBIT_COMMON_ALLOCATION' (20)`NOC ROSSREFS(SEC TION SEC TION ...)' . (20)`OUTPUT_ARC H(BFDARCH)' (21)4.6、为符号赋值 (21)4.7、SEC TIONS命令 (22)4.7.1、输出节描述 (22)4.7.2、输出节名 (23)4.7.3、输出节描述 (23)4.7.4、输入节描述 (23)4.7.4.1、输入节通配符 (24)4.7.4.2、输入节中的普通符号. (25)4.7.4.3、输入节和垃圾收集 (25)4.7.5、输出节数据 (26)4.7.5.1、输出节关键字 (27)4.7.5.2、输出节的丢弃。

微机原理0832,0809

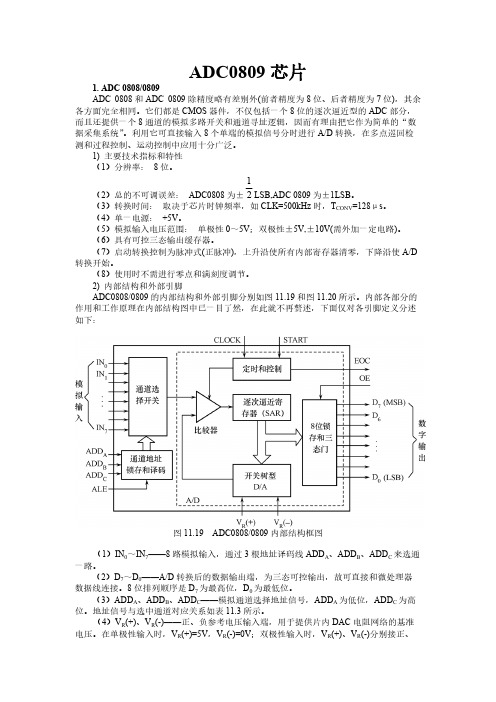

一、ADC0809的内部结构及引脚功能

START IN7 8路 模拟 开关 IN0

3 C B A

CLK EOC 三 态 输 出 锁 存 器 D7 D6 D5 D4 D3 D2 D1 D0 OE

ALE

地址锁 存与 译码 VR(+) VR(-)

ADC0809

8位 A/D 转换 器

IN3 IN4 IN5 IN6 IN7 START EOC D3 OE CLK VCC VR(+) GND D1

14

3、直通工作方式 当DAC0832芯片的片选信号、写信号、 及传送控制信号的引脚全部接地,允许输 入锁存信号ILE引脚接+5V时,DAC0832 芯片就处于直通工作方式,数字量一旦输 入,就直接进入DAC寄存器,进行D/A转 换。

15

完成da转换输出153直通工作方式当dac0832芯片的片选信号写信号及传送控制信号的引脚全部接地允许输入锁存信号ile引脚接5v时dac0832芯片就处于直通工作方式数字量一旦输入就直接进入dac寄存器进行da转

9.2.2 ADC0809芯片及其与单片机的接口

主要性能为: 分辨率为8位; 精度:ADC0809小于±1LSB(ADC0808小于 ±1/2LSB); 单+5V供电,模拟输入电压范围为0~+5V; 具有锁存控制的8路输入模拟开关; 可锁存三态输出,输出与TTL电平兼容; 功耗为15mW; 不必进行零点和满度调整; 转换速度取决于芯片外接的时钟频率。时钟频 率范围:10~1280KHz。典型值为时钟频率 640KHz,转换时间约为100μS。

3

二、ADC0809与单片机的接口 1、查询方式

ALE G D7 : : D0 OE Q7 : : Q0 + + 1

adc0809中文资料手册下载pdf

1.主要特性1)8路8位A/D转换器,即分辨率8位。

2)具有转换起停控制端。

3)转换时间为100μs4)单个+5V电源供电5)模拟输入电压范围0~+5V,不需零点和满刻度校准。

6)工作温度范围为-40~+85摄氏度7)低功耗,约15mW。

2.内部结构ADC0809是CMOS单片型逐次逼近式A/D转换器,内部结构如图13.22所示,它由8路模拟开关、地址锁存与译码器、比较器、8位开关树型D/A转换器、逐次逼近3.外部特性(引脚功能)ADC0809芯片有28条引脚,采用双列直插式封装,如图13.23所示。

下面说明各引脚功能。

IN0~IN7:8路模拟量输入端。

2-1~2-8:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路ALE:地址锁存允许信号,输入,高电平有效。

START:A/D转换启动信号,输入,高电平有效。

EOC:A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):基准电压。

Vcc:电源,单一+5V。

GND:地。

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。

此地址经译码选通8路模拟输入之一到比较器。

START上升沿将逐次逼近寄存器复位。

下降沿启动A/D转换,之后EOC输出信号变低,指示转换正在进行。

直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。

当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。

ADC0809-芯片介绍

3 中断采样方式

中断采样方式:CPU启动A/D转换后, 可以继续执行主程序。当A/D结束时, 发出转换结束信号EOC,该信号经反 相器接单片机的P3.2引脚,向CPU发 出中断请求。

ADC0809时序

03

ADC0809 管脚功能

ADC0809 管脚功能

IN0~IN7:8路模拟量输入端 D0~D7:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路。

ALE:地址锁存允许信号,输入高电平有效。

START: A/D转换启动脉冲输入端,输入一个正脉冲(至少100ns宽)使其 启动(脉冲上升沿使0809复位,下降沿启动A/D转换)。

ADC0809 工作工程

首先: A,B,C输入3位地址,ALE上升沿将地址存入 地址锁存器中。 其次: START上升沿将寄存器复位。下降沿启动AD 转换,之后EOC变低,指示转换正在进行。 再次: AD转换完成,EOC变为高电平,结果存入 锁存器,此信号可作中断申请。 最后: OE输入高电平时,输出三态门打开,转换 结果的数字量输出到数据总线上。

Vcc、GND:电源电压Vcc接+5V,GND为数字地。

04

ADC0809 接口设计

ADC0809 接口设计

硬件接口设计

A/D转换器与单片机接口一般有两种方法: 第一种方法是通过并行I/O接口与单片机

连接,需占用两个并行接口(其中一个接A/D 转换器数据线,另一个接口用来产生A/D转换 器工作控制信号)。

3

输出部分

ADC0809-N资料datasheet (1)

ADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013 ADC0808/ADC08098-BitμP Compatible A/D Converters with8-Channel MultiplexerCheck for Samples:ADC0808-N,ADC0809-NFEATURES DESCRIPTIONThe ADC0808,ADC0809data acquisition component •Easy Interface to All Microprocessorsis a monolithic CMOS device with an8-bit analog-to-•Operates Ratiometrically or with5V DC or digital converter,8-channel multiplexer and Analog Span Adjusted Voltage Reference microprocessor compatible control logic.The8-bit •No Zero or Full-Scale Adjust Required A/D converter uses successive approximation as theconversion technique.The converter features a high •8-Channel Multiplexer with Address Logicimpedance chopper stabilized comparator,a256R •0V to V CC Input Range voltage divider with analog switch tree and a•Outputs meet TTL Voltage Level Specifications successive approximation register.The8-channelmultiplexer can directly access any of8-single-ended •ADC0808Equivalent to MM74C949analog signals.•ADC0809Equivalent to MM74C949-1The device eliminates the need for external zero and KEY SPECIFICATIONSfull-scale adjustments.Easy interfacing tomicroprocessors is provided by the latched and •Resolution:8Bits decoded multiplexer address inputs and latched TTL•Total Unadjusted Error:±½LSB and±1LSB TRI-STATE outputs.•Single Supply:5VDC The design of the ADC0808,ADC0809has been •Low Power:15mW optimized by incorporating the most desirable aspectsof several A/D conversion techniques.The ADC0808,•Conversion Time:100μsADC0809offers high speed,high accuracy,minimaltemperature dependence,excellent long-termaccuracy and repeatability,and consumes minimalpower.These features make this device ideally suitedto applications from process and machine control toconsumer and automotive applications.For16-channel multiplexer with common output(sample/holdport)see ADC0816data sheet.(See AN-247(Literature Number SNOA595)for more information.)Block DiagramConnection DiagramsPlease be aware that an important notice concerning availability,standard warranty,and use in critical applications ofTexas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.All trademarks are the property of their respective owners.PRODUCTION DATA information is current as of publication date.Copyright©1999–2013,Texas Instruments Incorporated Products conform to specifications per the terms of the TexasADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED Figure1.PDIP Package Figure2.PLCCPackageSee Package N0028ESee Package FN0028AThese devices have limited built-in ESD protection.The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.Absolute Maximum Ratings(1)(2)(3)Supply Voltage(V CC)(4) 6.5V Voltage at Any Pin Except Control Inputs−0.3V to(V CC+0.3V) Voltage at Control Inputs−0.3V to+15V (START,OE,CLOCK,ALE,ADD A,ADD B,ADD C)Storage Temperature Range−65°C to+150°C Package Dissipation at T A=25°C875mW Lead Temp.(Soldering,10seconds)PDIP Package(plastic)260°CPLCC Package Vapor Phase(60seconds)215°CInfrared(15seconds)220°C ESD Susceptibility(5)400V (1)Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do notapply when operating the device beyond its specified operating conditions.(2)All voltages are measured with respect to GND,unless otherwise specified.(3)If Military/Aerospace specified devices are required,please contact the TI Sales Office/Distributors for availability and specifications.(4)A Zener diode exists,internally,from V CC to GND and has a typical breakdown voltage of7V DC.(5)Human body model,100pF discharged through a1.5kΩresistor.Operating Conditions(1)(2)Temperature Range T MIN≤T A≤T MAX−40°C≤T A≤+85°C Range of V CC 4.5V DC to6.0V DC (1)Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do notapply when operating the device beyond its specified operating conditions.(2)All voltages are measured with respect to GND,unless otherwise specified.Electrical Characteristics–Converter SpecificationsConverter Specifications:V CC=5V DC=V REF+,V REF(−)=GND,T MIN≤T A≤T MAX and f CLK=640kHz unless otherwise stated.Symbol Parameter Conditions Min Typ Max Units ADC080825°C±½LSBTotal Unadjusted Error(1)Tto T MAX±¾LSBMIN(1)Total unadjusted error includes offset,full-scale,linearity,and multiplexer errors.See Figure5.None of these A/Ds requires a zero orfull-scale adjust.However,if an all zero code is desired for an analog input other than0.0V,or if a narrow full-scale span exists(for example:0.5V to4.5V full-scale)the reference voltages can be adjusted to achieve this.See Figure15.2Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013Electrical Characteristics–Converter Specifications(continued)Converter Specifications:V CC=5V DC=V REF+,V REF(−)=GND,T MIN≤T A≤T MAX and f CLK=640kHz unless otherwise stated.Symbol Parameter Conditions Min Typ Max Units ADC08090°C to70°C±1LSBTotal Unadjusted Error(1)Tto T MAX±1¼LSBMINInput Resistance From Ref(+)to Ref(−) 1.0 2.5kΩAnalog Input Voltage Range See(2)V(+)or V(−)GND−0.1V CC+0.1V DCV REF(+)Voltage,Top of Ladder Measured at Ref(+)V CC V CC+0.1VVoltage,Center of Ladder(V CC/2)−0.1V CC/2(V CC/2)+0.1VV REF(−)Voltage,Bottom of Ladder Measured at Ref(−)−0.10VI IN Comparator Input Current f c=640kHz,(3)−2±0.52μA(2)Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages one diode drop below ground orone diode drop greater than the V CC n supply.The spec allows100mV forward bias of either diode.This means that as long as the analog V IN does not exceed the supply voltage by more than100mV,the output code will be correct.To achieve an absolute0V DC to 5V DC input voltage range will therefore require a minimum supply voltage of4.900V DC over temperature variations,initial tolerance and loading.(3)Comparator input current is a bias current into or out of the chopper stabilized comparator.The bias current varies directly with clockfrequency and has little temperature dependence(Figure8).See ANALOG COMPARATOR INPUTSElectrical Characteristics–Digital Levels and DC SpecificationsDigital Levels and DC Specifications:ADC0808CCN,ADC0808CCV,ADC0809CCN and ADC0809CCV,4.75≤V CC≤5.25V,−40°C≤T A≤+85°C unless otherwise notedSymbol Parameter Conditions Min Typ Max Units ANALOG MULTIPLEXERV CC=5V,V IN=5V,I OFF(+)OFF Channel Leakage Current T A=25°C10200nAT MIN to T MAX 1.0μAV CC=5V,V IN=0,I OFF(−)OFF Channel Leakage Current T A=25°C−200−10nAT MIN to T MAX−1.0μA CONTROL INPUTSV IN(1)Logical“1”Input Voltage(V CC−1.5)VV IN(0)Logical“0”Input Voltage 1.5VLogical“1”Input Current(The ControlI IN(1)V IN=15V 1.0μAInputs)Logical“0”Input Current(The ControlI IN(0)V IN=0−1.0μAInputs)I CC Supply Current f CLK=640kHz0.3 3.0mA DATA OUTPUTS AND EOC(INTERRUPT)V CC=4.75VV OUT(1)Logical“1”Output Voltage I OUT=−360µA 2.4VI OUT=−10µA 4.5VV OUT(0)Logical“0”Output Voltage I O=1.6mA0.45VV OUT(0)Logical“0”Output Voltage EOC I O=1.2mA0.45VV O=5V3μAI OUT TRI-STATE Output CurrentV O=0−3μA Electrical Characteristics–Timing SpecificationsTiming Specifications V CC=V REF(+)=5V,V REF(−)=GND,t r=t f=20ns and T A=25°C unless otherwise noted.Symbol Parameter Conditions MIn Typ Max Unitst STCLK Start Time Delay from Clock(Figure7)300900ns Copyright©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback3ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED Electrical Characteristics–Timing Specifications(continued)Timing Specifications V CC=V REF(+)=5V,V REF(−)=GND,t r=t f=20ns and T A=25°C unless otherwise noted.Symbol Parameter Conditions MIn Typ Max Unitst WS Minimum Start Pulse Width(Figure7)100200nst WALE Minimum ALE Pulse Width(Figure7)100200nst s Minimum Address Set-Up Time(Figure7)2550nst H Minimum Address Hold Time(Figure7)2550nst D Analog MUX Delay Time From ALE R S=0Ω(Figure7)1 2.5μst H1,t H0OE Control to Q Logic State C L=50pF,R L=10k(Figure10)125250nst1H,t0H OE Control to Hi-Z C L=10pF,R L=10k(Figure10)125250nst c Conversion Time f c=640kHz,(Figure7)(1)90100116μsf c Clock Frequency106401280kHzClockt EOC EOC Delay Time(Figure7)08+2μSPeriodsC IN Input Capacitance At Control Inputs1015pFC OUT TRI-STATE Output Capacitance At TRI-STATE Outputs1015pF(1)The outputs of the data register are updated one clock cycle before the rising edge of EOC.4Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013Functional DescriptionMULTIPLEXERThe device contains an8-channel single-ended analog signal multiplexer.A particular input channel is selected by using the address decoder.Table1shows the input states for the address lines to select any channel.The address is latched into the decoder on the low-to-high transition of the address latch enable signal.Table1.Analog Channel SelectionADDRESS LINESELECTED ANALOGCHANNEL C B AIN0L L LIN1L L HIN2L H LIN3L H HIN4H L LIN5H L HIN6H H LIN7H H HCONVERTER CHARACTERISTICSThe ConverterThe heart of this single chip data acquisition system is its8-bit analog-to-digital converter.The converter is designed to give fast,accurate,and repeatable conversions over a wide range of temperatures.The converter is partitioned into3major sections:the256R ladder network,the successive approximation register,and the comparator.The converter's digital outputs are positive true.The256R ladder network approach(Figure3)was chosen over the conventional R/2R ladder because of its inherent monotonicity,which ensures no missing digital codes.Monotonicity is particularly important in closed loop feedback control systems.A non-monotonic relationship can cause oscillations that will be catastrophic for the system.Additionally,the256R network does not cause load variations on the reference voltage.The bottom resistor and the top resistor of the ladder network in Figure3are not the same value as the remainder of the network.The difference in these resistors causes the output characteristic to be symmetrical with the zero and full-scale points of the transfer curve.The first output transition occurs when the analog signal has reached+½LSB and succeeding output transitions occur every1LSB later up to full-scale.The successive approximation register(SAR)performs8iterations to approximate the input voltage.For any SAR type converter,n-iterations are required for an n-bit converter.Figure4shows a typical example of a3-bit converter.In the ADC0808,ADC0809,the approximation technique is extended to8bits using the256R network.The A/D converter's successive approximation register(SAR)is reset on the positive edge of the start conversion start pulse.The conversion is begun on the falling edge of the start conversion pulse.A conversion in process will be interrupted by receipt of a new start conversion pulse.Continuous conversion may be accomplished by tying the end-of-conversion(EOC)output to the SC input.If used in this mode,an external start conversion pulse should be applied after power up.End-of-conversion will go low between0and8clock pulses after the rising edge of start conversion.The most important section of the A/D converter is the comparator.It is this section which is responsible for the ultimate accuracy of the entire converter.It is also the comparator drift which has the greatest influence on the repeatability of the device.A chopper-stabilized comparator provides the most effective method of satisfying all the converter requirements.The chopper-stabilized comparator converts the DC input signal into an AC signal.This signal is then fed through a high gain AC amplifier and has the DC level restored.This technique limits the drift component of the amplifier since the drift is a DC component which is not passed by the AC amplifier.This makes the entire A/D converter extremely insensitive to temperature,long term drift and input offset errors.Copyright©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback5ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED Figure6shows a typical error curve for the ADC0808.Figure3.Resistor Ladder and Switch TreeFigure4.3-Bit A/D Transfer Curve Figure5.3-Bit A/D Absolute Accuracy CurveFigure6.Typical Error Curve6Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013 Timing DiagramFigure7.Copyright©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback7ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED Typical Performance CharacteristicsComparator I INvsV IN(V CC=V REF=5V)Figure8.Multiplexer R ONvsV IN(V CC=V REF=5V)Figure9.8Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-NSNAS535H –OCTOBER 1999–REVISED MARCH 2013TRI-STATE Test Circuits and Timing Diagramst 1H ,t H1t 0H ,t H0t 1H ,C L =10pF t 0H ,C L =10pFt H1,C L =50pFt H0,C L =50pFFigure 10.TRI-STATE Test Circuits and Timing DiagramsCopyright ©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback 9ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED APPLICATIONS INFORMATIONOPERATIONRATIOMETRIC CONVERSIONThe ADC0808,ADC0809is designed as a complete Data Acquisition System(DAS)for ratiometric conversion systems.In ratiometric systems,the physical variable being measured is expressed as a percentage of full-scale which is not necessarily related to an absolute standard.The voltage input to the ADC0808is expressed by the equation•V IN=Input voltage into the ADC0808•V fs=Full-scale voltage•V Z=Zero voltage•D X=Data point being measured•D MAX=Maximum data limit•D MIN=Minimum data limit(1) A good example of a ratiometric transducer is a potentiometer used as a position sensor.The position of the wiper is directly proportional to the output voltage which is a ratio of the full-scale voltage across it.Since the data is represented as a proportion of full-scale,reference requirements are greatly reduced,eliminating a large source of error and cost for many applications.A major advantage of the ADC0808,ADC0809is that the input voltage range is equal to the supply range so the transducers can be connected directly across the supply and their outputs connected directly into the multiplexer inputs,(Figure11).Ratiometric transducers such as potentiometers,strain gauges,thermistor bridges,pressure transducers,etc., are suitable for measuring proportional relationships;however,many types of measurements must be referred to an absolute standard such as voltage or current.This means a system reference must be used which relates the full-scale voltage to the standard volt.For example,if V CC=V REF=5.12V,then the full-scale range is divided into 256standard steps.The smallest standard step is1LSB which is then20mV.RESISTOR LADDER LIMITATIONSThe voltages from the resistor ladder are compared to the selected into8times in a conversion.These voltages are coupled to the comparator via an analog switch tree which is referenced to the supply.The voltages at the top,center and bottom of the ladder must be controlled to maintain proper operation.The top of the ladder,Ref(+),should not be more positive than the supply,and the bottom of the ladder,Ref(−), should not be more negative than ground.The center of the ladder voltage must also be near the center of the supply because the analog switch tree changes from N-channel switches to P-channel switches.These limitations are automatically satisfied in ratiometric systems and can be easily met in ground referenced systems. Figure12shows a ground referenced system with a separate supply and reference.In this system,the supply must be trimmed to match the reference voltage.For instance,if a5.12V is used,the supply should be adjusted to the same voltage within0.1V.Figure11.Ratiometric Conversion System10Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013 The ADC0808needs less than a milliamp of supply current so developing the supply from the reference is readily accomplished.In Figure13a ground referenced system is shown which generates the supply from the reference.The buffer shown can be an op amp of sufficient drive to supply the milliamp of supply current and the desired bus drive,or if a capacitive bus is driven by the outputs a large capacitor will supply the transient supply current as seen in Figure14.The LM301is overcompensated to insure stability when loaded by the10μF output capacitor.The top and bottom ladder voltages cannot exceed V CC and ground,respectively,but they can be symmetrically less than V CC and greater than ground.The center of the ladder voltage should always be near the center of the supply.The sensitivity of the converter can be increased,(i.e.,size of the LSB steps decreased)by using a symmetrical reference system.In Figure15,a2.5V reference is symmetrically centered about V CC/2since the same current flows in identical resistors.This system with a2.5V reference allows the LSB bit to be half the size of a5V reference system.Figure12.Ground ReferencedConversion System Using Trimmed SupplyFigure13.Ground Referenced Conversion System withReference Generating V CC SupplyCopyright©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback11ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED Figure14.Typical Reference and Supply CircuitR A=R B*Ratiometric transducersFigure15.Symmetrically Centered ReferenceCONVERTER EQUATIONSThe transition between adjacent codes N and N+1is given by:(2) The center of an output code N is given by:(3) The output code N for an arbitrary input are the integers within the range:Where:•V IN=Voltage at comparator input•V REF(+)=Voltage at Ref(+)•V REF(−)=Voltage at Ref(−)•V TUE=Total unadjusted error voltage(typically•V REF(+)÷512)(4) 12Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedADC0808-N,ADC0809-N SNAS535H–OCTOBER1999–REVISED MARCH2013ANALOG COMPARATOR INPUTSThe dynamic comparator input current is caused by the periodic switching of on-chip stray capacitances.These are connected alternately to the output of the resistor ladder/switch tree network and to the comparator input as part of the operation of the chopper stabilized comparator.The average value of the comparator input current varies directly with clock frequency and with V IN as shown in Figure8.If no filter capacitors are used at the analog inputs and the signal source impedances are low,the comparator input current should not introduce converter errors,as the transient created by the capacitance discharge will die out before the comparator output is strobed.If input filter capacitors are desired for noise reduction and signal conditioning they will tend to average out the dynamic comparator input current.It will then take on the characteristics of a DC bias current whose effect can be predicted conventionally.Typical Application*Address latches needed for8085and SC/MP interfacing the ADC0808to a microprocessorTable2.Microprocessor Interface TablePROCESSOR READ WRITE INTERRUPT(COMMENT)8080MEMR MEMW INTR(Thru RST Circuit)8085RD WR INTR(Thru RST Circuit)Z-80RD WR INT(Thru RST Circuit,Mode0)SC/MP NRDS NWDS SA(Thru Sense A)6800VMA•φ2•R/W VMA•φ•R/W IRQA or IRQB(Thru PIA)Copyright©1999–2013,Texas Instruments Incorporated Submit Documentation Feedback13ADC0808-N,ADC0809-NSNAS535H–OCTOBER1999–REVISED REVISION HISTORYChanges from Revision G(March2013)to Revision H Page •Changed layout of National Data Sheet to TI format (13)14Submit Documentation Feedback Copyright©1999–2013,Texas Instruments IncorporatedPACKAGING INFORMATION(1) The marketing status values are defined as follows:ACTIVE: Product device recommended for new designs.LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.PREVIEW: Device has been announced but is not in production. Samples may or may not be available.OBSOLETE: TI has discontinued the production of the device.(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check /productcontent for the latest availability information and additional product content details.TBD: The Pb-Free/Green conversion plan has not been defined.Pb-Free (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.Addendum-Page 1Pb-Free (RoHS Exempt): This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)(3) MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.(4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.(5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.(6) Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.Addendum-Page 2IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,enhancements,improvements and other changes to its semiconductor products and services per JESD46,latest issue,and to discontinue any product or service per JESD48,latest issue.Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All semiconductor products(also referred to herein as“components”)are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its components to the specifications applicable at the time of sale,in accordance with the warranty in TI’s terms and conditions of sale of semiconductor products.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by applicable law,testing of all parameters of each component is not necessarily performed.TI assumes no liability for applications assistance or the design of Buyers’products.Buyers are responsible for their products and applications using TI components.To minimize the risks associated with Buyers’products and applications,Buyers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any patent right,copyright,mask work right,or other intellectual property right relating to any combination,machine,or process in which TI components or services are rmation published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Buyer acknowledges and agrees that it is solely responsible for compliance with all legal,regulatory and safety-related requirements concerning its products,and any use of TI components in its applications,notwithstanding any applications-related information or support that may be provided by TI.Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures,monitor failures and their consequences,lessen the likelihood of failures that might cause harm and take appropriate remedial actions.Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.In some cases,TI components may be promoted specifically to facilitate safety-related applications.With such components,TI’s goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements.Nonetheless,such components are subject to these terms.No TI components are authorized for use in FDA Class III(or similar life-critical medical equipment)unless authorized officers of the parties have executed a special agreement specifically governing such use.Only those TI components which TI has specifically designated as military grade or“enhanced plastic”are designed and intended for use in military/aerospace applications or environments.Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk,and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.TI has specifically designated certain components as meeting ISO/TS16949requirements,mainly for automotive use.In any case of use of non-designated products,TI will not be responsible for any failure to meet ISO/TS16949.Products ApplicationsAudio /audio Automotive and Transportation /automotiveAmplifiers Communications and Telecom /communicationsData Converters Computers and Peripherals /computersDLP®Products Consumer Electronics /consumer-appsDSP Energy and Lighting /energyClocks and Timers /clocks Industrial /industrialInterface Medical /medicalLogic Security /securityPower Mgmt Space,Avionics and Defense /space-avionics-defense Microcontrollers Video and Imaging /videoRFID OMAP Applications Processors /omap TI E2E Community Wireless Connectivity /wirelessconnectivityMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2013,Texas Instruments Incorporated。

adc0808中文资料[整理版]

![adc0808中文资料[整理版]](https://img.taocdn.com/s3/m/02ae1a6e84254b35effd345a.png)

adc0808中文资料[整理版]11.2.4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,并在转换结束RD后利用读数信号选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC 芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU配套使用的芯片,MPU的I/O写脉冲都能满足ADC芯片对启动脉冲的要求。

对电平启动转换的ADC芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D触发器或可编程并行I/O接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

80960RD资料