大容量Falsh型AT91系列ARM核微控制器

AT91SAM7S64学习资料

ARM入门笔记(1)前言如果您是一个单片机爱好者,当见到一款功能强大、性价比高的处理器时,一定会有一股很想掌握它、运用它的冲动,起码我是这样。

5年前第一次接触单片机(标准的51系列),就被它强大的功能所吸引,而痴迷于它,一直到今天。

在这期间的不同时期,各种增强型51,PIC、AVR,DSP和ARM等不同程度的吸引和诱惑着我。

有的已经玩过了,有的则没有,但很想玩的这股冲动一直存在心里,特别是对ARM。

记得2002年我就知道了ARM这个东东,眼睁睁地看着它一天天的火热,但由于对其开发工具及开发过程的不了解等原因一直只处于认识的阶段,尽管也曾玩过ZLG的2104开发板!可能是ZLG团队做的太出色的原因吧(详细的教材与源码,还有非常方便的工程模板),没过多久、没费多少劲就把里面的实验做完了,然后由于自已性格上的缺陷把它给扔在了一边,导致不到一个月就把大部分的东东还给了周老师。

直到前段时间,让我有机会真真正正的玩起了ARM!像最初玩8051那样的尽兴(出现问题时,吃不下饭、睡不着觉的那种痛苦和解决问题后的那种畅快)。

这篇文档就是记录了我在前段时间学习、调试目前最低价的ARM核处理器——AT91SAM7Sxx 时出现的问题与解决方法。

它尽量完整地记录了我从开始不懂ARM,到最终完成AT91SAM7S64各种外围实验的各个环节及整个过程,包括我在开始一个实验前的一些想法,实验目的,以及各个实验中,我以单片机的思维去思考时遇到的各种问题,和这些问题的解决方法。

现将自己的一点经验以及体会拿出来与大家共同分享,一来是希望能够为那些在ARM门口徘徊迷茫的人提供一些借鉴,使他们顺利越过这道门槛;二来是希望能够抛砖引玉,以结识更多有共同爱好的朋友。

由于我也是新手上路,文章中难免疏漏与错误,希望大家不吝指正,如果在调试AT91SAM7Sxx时有什么问题,欢迎大家共同讨论。

第一章开发工具与调试环境一.目标板所用实验板是参考ATMEL公司官方网站上发布的《AT91SAM7S-EK Evaluation Board User Guide》设计的,相当于AT91SAM7Sxx评估测试板,主要用于各种外围实验,结构框图如图1-1所示。

常见的单片机品牌与型号介绍

常见的单片机品牌与型号介绍单片机(Microcontroller Unit,简称MCU)作为嵌入式系统的核心部件,广泛应用于各种电子设备中。

随着科技的不断发展,市场上涌现了众多单片机品牌和型号。

本文将为大家介绍常见的单片机品牌与型号,供读者参考选择。

一、Atmel(爱特梅尔)Atmel是全球领先的单片机厂商之一,其产品在市场上占据了显著的份额。

Atmel的单片机以高性能、低功耗、易用性和可靠性著称。

以下是Atmel单片机的几个典型型号:1. ATmega328P:这是一款广泛应用于Arduino开发板中的单片机,具有32KB的Flash存储器和2KB的SRAM,适合中小规模的嵌入式应用。

2. ATtiny85:这是一款微型单片机,具有8KB的Flash存储器和512字节的SRAM,尺寸小巧,适合于资源受限的应用场景。

3. ATSAM4S16C:这是一款高性能的ARM Cortex-M4核心单片机,具有256KB的Flash存储器和64KB的SRAM,适用于复杂的嵌入式系统设计。

二、STMicroelectronics(意法半导体)STMicroelectronics是全球领先的半导体解决方案供应商之一,其STMicroelectronics单片机也备受认可。

STMicroelectronics的单片机以性能稳定、丰富的外设接口以及低功耗特性而著称。

以下是几款常见的型号:1. STM32F103C8T6:这是STMicroelectronics的一款32位ARM Cortex-M3核心单片机,具有64KB的Flash存储器和20KB的SRAM,适合于中等规模的嵌入式应用。

2. STM8S003F3P6:这是STMicroelectronics的一款8位单片机,具有8KB的Flash存储器和1KB的SRAM,适合于资源受限的应用场景。

3. STM32F407VET6:这是STMicroelectronics的一款高性能32位ARM Cortex-M4核心单片机,具有512KB的Flash存储器和192KB的SRAM,适用于要求较高计算能力的嵌入式系统设计。

AT91SAM9G15 9G25 9G35 9X25 9X35 ARM 嵌入式评估板用户手册 V1.

MBS-SAM9G15/9G25 /9G35/9X25/9X35 User ManualRelease:V1.0 Date:2012.04.17Embest Info&Tech Co.,LTD.Revision historyRev Date Description by1.0 20120417 Initial version huangyin Note:This user guide introduces the ARM embedded evaluation board produced by Embest , based on A TMEL ARM926 -EJ-S-based processors as listed below:A T91SAM9G15A T91SAM9G25A T91SAM9G35A T91SAM9X25A T91SAM9X35The user guide pertains to the following kit references:MBS-SAM9G15MBS-SAM9G25MBS-SAM9G35MBS-SAM9X25MBS-SAM9X35The user guide gives design information on the kit and is made up of 4 sections:Section 1 includes a photo of the board, deliverables and applicable documents.Section 2 describes the hardware resource of the board.Section 3 describes the updating software list of the board.Section 4 provides the ways to contact us.This document copyright belongs to embest technology Co., LTD. © 2012In the passage , 9X5 serial general means 9G15,9G25,9G35,9X25,9X35.Section 1_Scope1.1 IntroductionThe MBS-SAM9X5 Series development board, which consists of two parts of the MBC-SAM9X5 core board and MBM-SAM9X5_9M10 main board, is the Embest launched based on the development board the A TMEL A T91SAM9X5. The core board is the smallest-sized 9X5 core board to help you as much as possible to reduce the product space, you can take advantage of the core board to complete product development easily and improve time to hit the market. Using industrial-grade connectors can achieve seamless connection with the custom main board, greatly improving the stability of the product.MBS-SAM9X5 SBC clocked up to 400MHz, the development board that supportsLinux-2.6.39 operating system debugging, angstrom, and the android-2.3.5_r1 file system test. With 256MB NandFlash, 128MB of DDR II, 4MB serial dataflash, 64KBserial eeprom, and a rich feature set expansion: high-speed USB 2.0 (480MHz), audio input, audio output, 10/100Mbps network, the JTAG debug interface, DBGU serial Micro SD card slot, SD/MMC card interface, CMOS camera interface, support for video data acquisition.1.2 Scope1.3 DeliverablesNO Items Qty Description Inspection1 MBS-SAM9X5 board 1 MBC + MBM SC2 Power Adapter (5V, 1.25A rating) 1 5V, 1.25A SC3 Micro USB Cable 1 Micro USB SC4 10/100 Ethernet Cable 1 Cross-over cable SC5 DB9-IDC10 Cable 1 Serial cable SC7 TFT LCD Panel 1 LCD with touch(4'', 7'')SCSection 2_Hardware2.1 Available resource for 9x5projects 9G15 9G25 9G35 9X25 9X35MPUs AT91SAM9G15/9G25/9G35/9X25/9X35(ARM926EJ-Score frequency400MHz) learn more <<memory 128MB SDRAMFlash256MB nandflash; 4MB serial dataflash;EEPROM64KB serial eeprom;256B 1-wire eeprom *2 (MBC+MBM)USBUSB HOST 2 2 2 2 2USB OTG 1 1 1 1 1 AudioAudio in 1 1 1 1 1Audio out 1 1 1 1 1 NET ETH 0 1 1 2 1 Camera Camera 0 1 0 0 0 UartUART interface 1 1 1 1 1USART interface 1 2 1 2 1 JTAG JTAG 1 1 1 1 1 RS485 RS485 2 2 2 2 2 CAN CAN 0 0 0 2 2 SD cardMicroSD 1 1 1 1 1SDCard 1 1 1 1 1 telephone telephone 1 1 1 1 1 LCD 4.3,7.0inch LCD 1 0 1 0 1button User button*2;Q touch button*41 1 1 1 1RTC Back up battery 1 1 1 1 1 Extended 30*2pin interface 1 1 1 1 1power 5V supply 1 1 1 1 1 2.2 Core Board2.2.1 ScopeFigure 2-1 core board frontFigure 2-2 core board back2.2.2 Structure2.2.3 Core board resourcesProcessor SAM9X5(SAM9G15/9G25/9G35/9X25/9X35)12MHz32.768MHz128MB DDR2 memory256MB nandflash memory with chip selection control switch4MB SPI Serial dataflash with chip selection control switch64KB EEPROM256B 1-wire EEPROMOn-board power regulationTwo user LEDsOptional PHYSDIOIMM200 card edge interface2.3 Function blocks for MBC-SAM9G15Here we make description about function blocks of the board with some parts of the schematic. For the whole schematic please refer to MBC-SAM9X5_REVB(embest).pdf and MBM_SAM9X5_9M10_RevA(embest).pdf (direct:)2.3.1 processorSAM9G15---ARM926EJ-S™ ARM® Thumb® Processor running at up to 400 MHz, System running at up to 133 MHz For more information about processor ATSAM9G15, please refer to SAM9G15 Complete.pdf or SAM9G15 Summary.pdf ()2.3.2 clock circuitryCrystal for internal clock, 12MHzCrystal for RTC clock, 32.768KHzCrystal for Ethernet clock RMII,50MHz2.3.4 Power supplies2.3.5 MemoryThe device serial processor features a DDR/SDR memory interface and an External Bus Interface to enable interfacing to a wide range of external memories and to almost any kind of parallel peripheral.The EBI is connected to two kinds of memory device:128MB DDR SDRAM256MB nandflash2.3.6 Dataflash(SPI controller)The serial processor provides two high-speed serial peripheral interface (SPI) controllers. One port is used to interface with the on-board serial Dataflash (4MB serial dateflash).2.3.7 EEPROM(TWI controller)The serial processor has a full speed(400KHz) master/slave TWI Serial Controller. The controller is mostly compatible with industry standard I2C and SMBus Interfaces. This port is used to interface with the on-board serial EEPROM,ISI, Qtouch device and audio codec interface.2.3.8 1-wire EEPROMThe board uses a 1-wire device as “firmware label”to store the information such as chip type, manufacturer’s name, production date etc.2.3.9 Optional PHYSome of the core boards (SAM9G15 not included) provide a location for a 10/100 Ethernet MAC/PHY interface. For more information about the Ethernet controller device, refer to the Dacvicom DM9161 controller manufacturer’s datasheet.2.3.10 SODIMM200 interface2.4 Main BoardThe main board is compatible with both the the 9m10 core board and 9x5 series core board.2.4.1 resourcesONE WIRE EPPROM(1024-bit);1 JTAG DEBUG interface;1 Camera interface(9m10 & 9G25);2 24-bit LCD interfaces(with touch);1 DBGU serial interface(3 wires);2 communication serial interfaces(5-wire & 3-wire);2 10/100Mb Ethernet interfaces;Note: 9m10 1; 9G15, 9G25, 9X35, 9G35 1; 9X25 22 RS485 interfaces;2 CANinterfaces;1 SmartDAA interface;2 USB 2.0 Host interfaces;Note: 9m10 1 (USB_A); 9x5 2 (USB_B & USB_C);1 USB high speed USB2.0 OTG interface;Note: 9m10(USB_B) and 9X5(USB_A) OTG interface;4 buttons (QTOUCH);2 buttons (reset, wakeup);1 Micro SD interface;1 SD card interface;3 LEDs;1 audio input and output interface;1 backup battery holder;User interface (50 GPIOs).2.4.2 Electrical CharacteristicsPower: 5V, 2A;Operating Temperature: 0~70C;Power Consumption: to be confirmed2.4.3 Mechanical and Physical CharacteristicsSize: 181x125mm;Board layer: 4;Board thickness: 6mm;Interface type: DIMM 200 Pins2.5 Function blocks for MBM-SAM9G152.5.1 Power supply2.5.2 AUDIOThe board includes a WM8731 CODEC for digital sound input and output. This interface includes audio jacks for line audio input and headphone line output.The SAM9 processor is configured in IIS slave mode to interface with the WM8731 Codec.2.5.3 Ethernet 0 interfaceEthernet 0 is available for the core board which has a optional PHY.2.5.4 Ethernet1Etherne1 is only available for SAM9X25, The PHY on Ethernet 1 is enabled by the SELCONFIG signal from a pull-down resistor on the core board.2.5.5 SD/MMC CardThe board has two high-speed Multi Media Card Interface. The first interface is used as a 4-bit interface (MCI0), connected to a MicroSD card slot. The second interface is used as a 4-bit Interface (MCI1), connected to an SD/MMCcard slot.2.5.6 1-wire EEPROM2.5.7 USB moduleThe board contains two USB HOST interfaces and an USB OTG interface.2.5.8 DBGUThe DBGU is connected to the DB-9 male socket through an RS-232 Transceiver (TXD and RXD only).2.5.9 USARTsThe USART0 and USART3 are used as serial communication ports. Both USARTs are buffered with an RS-232 Transceiver and connected to the DB-9 male socket. USART0 just own TXD and RXD signal, and USART3 equips addition handshake CTS/RTS control.The USART3 is only supported by SAM9G25 and SAM9X25 processors.USART0USART32.5.10 CANTwo boards(MBS-SAM9X35 and MBS-SAM9X25), feature two controller area network (CAN) ports with transceiver.2.5.11 RS485Two RS485 interfaces.2.5.12 JTAGSoftware debug is accessed by a standard 20-pin JTAG connection.2.5.13 Qtouch2.5.13 LCD interface 4.3 inch LCD interface7.0 inch LCD interface2.5.14 ISI Interface2.5.15 Telephone interfaceThe board features a smart DAA(DATA Access Arrangement) chip to drive an analog telephone line.2.5.16 Key2.5.17 RTC Power2.5.18 user interface2.6 Jumpers2.6.1 SW1 settingsNO. Setting 1 Nandflash enable 2 Dataflash enable2.6.2 SW2 settingsIt ’s used for matching Audio Lord the clock signal of the 9x5 core board NO. Settings 1 Do not care 2 Close 3 Open 4Close2.6.3 JP jumpersNO. settingsdefault JP1close :force powerclose JP2,JP3,JP4,JP5,JP6.JP7, close :enable RS485 terminal resistance open JP8,JP10close :enable CAN terminal resistance openJP9 close :DBGU available open : CAN availableNote: if you download image to the board throughUSB, you must close the jumperclose JP11close: enable camera interface (for 9G25)openJP12 Open: disable external flashClose: enable external flash closeJP14,JP15 1-2:RS485 for 9M10 core 2-3:RS485 for 9x5 coreSection 3_Software (updating)3.1 MDK resourcesARM9 productsprojects9G15 9G25 9G35 9x25 9x35 adc √√√√√can × × × √√dma √√√√√eeprom √√√√√Emac(eth1) × × × √×getting-started √√√√√Hsmci_multimedia_card √√√√√Hsmci_sdcard √√√√√Hsmci_sdio √√√√√LCD_4.3 √× √× √LCD_7.0 √× √× √LCD_10.2 √× √× √periph_protect √√√√√pmc_clock_switching √√√√√pwm √√√√√qtouch √√√√√Rs485_loopback √√√√√Rs485_twoport √√√√√Smc_nandflash √√√√√Spi_serialflash √√√√√Ssc_dma_audio √√√√√sysc √√√√√tc_capture_waveform √√√√√Touchscreen_4.3 √× √× √Touchscreen_7.0 √× √× √twi √√√√√Usart_serial_COM0 √√√√√Usart_serial_COM3 × √× √× Usart_hw_handshaking_COM3 × √× √× usb_audio_looprec √√√√√usb_cdc_serial √√√√√usb_core √√√√√usb_hid_keyboard √√√√√usb_hid_mouse √√√√√usb_hid_msd √√√√√usb_hid_transfer √√√√√usb_iad_cdc_cdc √√√√√usb_iad_cdc_hid √√√√√usb_iad_cdc_msd √√√√√usb_masstorage √√√√√3.2 Linux resourcesnote :(1) “√”--included, “×”-- not included; (2) Free and open CategoriesDrivers 9G159G259G359X259X359x5BootloaderAT91BootstrapLead Uboottested, free&openUboot1. NandFlash erasing ,reading and writing2.support network download images3. Support the establishment, save the environmentvariable4. Support the memory contents display, contrast,and modification5. Support bootm 、bootargs settingstested, free&openkernelnetETH0× √ √ √ √ tested, free&open ETH1 × × × √ × tested, free&open serialUSART0√ √ √ √ √ tested, free&open USART3 × √ × √ × tested, free&open DBGU √ √ √ √ √ tested, free&open CANCAN0× × × √ √ untested, providecodes CAN1 × × × √ √ untested, providecodes USBUSB_HOST*2 √ √ √ √ √ tested, free&open USB_OTG √ √ √ √ √ tested, free&open SMD 驱动√ √ √ √ √ provide hardware interface only SDcardMicroSD√ √ √ √ √ tested, free&open SDCard√ √ √ √ √ tested, free&open camera (ISI) × √ × × × untested, providecodes LCD+touch √ × √ × √ tested, free&open Zigbee√ √ √ √ √ provide hardware interface only SPI√√√√√reuse, unregistered equipmentTWI √√√√√tested, free&openQtouch √√√√√tested, free&openDMA √√√√√tested, free&openGPIO √√√√√tested, free&openAngstrom √√√√√provide file system File systemAndroid √× √× √provide file systemSection 4_Purchase and serviceIf you are interested in the board ,you may connect:Sales and marketing: **********************For Technical Support: ************************URL: /en/。

AT91SAM7S32_CN

硬件篇目录:0,AT91SAM7S32芯片介绍1,AT91SAM7S供电(系统电源,1.8V,PLL);2,时钟设置,PLL设置,32K时钟;3,RESET电路;4,DBGU/ISP/BOOT;5,JTAG电路;6,ADC电路;7,IIC/TWI;8,SPI;9,USART10,PWM11,AIC;12,PMC;13,RTT;14,USB UART第0章 AT91SAM7S32芯片介绍AT91SAM7S系列ARM控制器是ATMEL在2004年推出的内置FLASH,内置RAM的小ARM7器件,非常适用于成本敏感型应用,可以以8bit MCU的价格,提供32bit MCU的性能。

AT91SAM7S32具备32K的FLASH,8K的RAM,极高的性价比适合其在低成本,大产量的消费类产品中应用。

AT91SAM7S32主要有如下优点:>ARM7TDMI内核,标准的JTAG接口是片内调试电路(ICE);与LPC2000系列ARM不同,AT91SAM系列ARM7采用的是ARM7TDMI,而LPC2000系列是ARM7TDMI-S,-S内核是的JTAG 调试速度不能太高,最高只能达到1/6系统时钟,实际测试情况是最高上到4.8M;而AT91SAM7S的JTAG时钟可以和系统时钟一样高,实际测试情况是可以轻松上到12M JTAG时钟>32K Flash,共256页,每页128字节。

AT91SAM7S系列的FLASH 页(page)大小和LPC2000的FLASH的扇区(sector)大小也不一样。

LPC2000的各个扇区大小不一样,编号为0-7的Sector的大小是4KB,编号为7-21的Sector的大小是32KB,编号为22-26的Sector 的大小是4KB。

在对FLASH编程的时候,LPC2000会稍微快一点,但是在应用的时候,由于ATMEL的page比较小,使用起来就比较方便。

>FLASH有10,000次写寿命,具备FLASH安全锁定位,可以防止非法读取,和A VR一样,可以通过整片擦除来取消该锁定位,也可以用AT91SAM7S的ERASE引脚来擦除FLASH内容和锁定位。

AT91SAM7S 系列 ARM 微控制器 快速入门

ATARM快速入门-基于AT91SAM7S系列ARM微控制器作者:Team Mcuzone网址:版本:Rev1.0a日期:2006-11版本信息:Rev1.0a: 2006-11成稿,原始版本版权信息:本资料部分资料取材于网络,若侵犯到某些个人或者公司的版权或其他利益,请主动和我们联系,我们将注明、更改、删除相关内容。

联系方法:QQ:8204136手机:139********MSN:hdapple_2000@目录介绍篇:1,ARM简介;2,AT91简介;3,ARM开发环境KEIL,IAR,ADS,RV,WINARM简介;4,ARM开发工具WIGGLER,MULTI-ICE,XLINK,ULINK简介;5,SAM7S32学习板介绍;6,LED范例演示;7,ARM/Thumb汇编指令集;硬件篇:1,AT91SAM7S供电(系统电源,1.8V,PLL);2,时钟设置,PLL设置,32K时钟;3,RESET电路(RESET电路);4,DBGU/ISP/BOOT;5,JTAG电路;6,ADC电路;7,IIC/TWI;8,SPI;9,USART10,PWM11,AIC;12,PMC;13,RTT;14,USB UART15,原理图介绍,分析,JTAG调试,DBGU下载演示软件篇:00,汇编指令分析;01,启动代码分析,头文件分析;1,GPIO(LED/KEY);2,UART;3,IIC/TWI(24C02);4,ADC(温度,光照度);5,Timer;6,RTT;7,PWM(LED);8,Uc/OS II;进阶篇:1,7S64的USB应用(S64-DEK);2,7X256的USB应用(7X256 LITE/EK);3,7X256的CAN应用(7X256 EK);4,7X256的NET应用(7X256 LITE/EK);附录:1,IAR下wiggler,MULTI-ICE的使用;2,SAM-BA中文用户手册;3,MULTI-ICE用户手册;4,XLINK用户手册;在开始阅读本书前,建议浏览一下ARM公司推荐的关于ARM的中文出版物,然后找几本比较适合自己的入门书籍来做一下预习工作,当然,也可以将本站整理的资料做为您的ARM入门必读书籍。

AT91RM9200简明手册

NRST是一个无上拉电阻的施密特触发器。NRST信号被包含到边界扫描中。

6.4 PIO 控制器A,B,C,D端口

所有的I/O口线,PA0-PA31、PB0-PB29、PC0-PC31、PD0-PD31、内部都集成了一个可编程的上拉电阻 (15K)。通过PIO控制器可以对每一个I/O的上拉电阻进行单独控制。

6

中嵌科技有限公司 表 3-1. 外设信号说明

7

中嵌科技有限公司 表 3-1. 外设信号说明

8

中嵌科技有限公司 表 3-1. 外设信号说明

4. 封装和引脚输出

7.2 调试与测试

· 集成了嵌入式内部电路仿真器 · 调试单元

- 两引脚的UART - 调试信道 - 芯片 ID 寄存器 · 嵌入式追踪宏单元:ETM9™ Rev2a - 中级实现 - 半速时钟模式 - 四对地址比较器 - 两个数据比较器 - 八个存储器映射解码器输入 - 两个计数器 - 一个序列发生器 - 一个18个字节的FIFO · 所有数字引脚的 IEEE 1149.1 JTAG 边界扫描

TDO为三态输出引脚。引脚JTAGSEL拉高时选择JTAG边界扫描功能。 NTRST引脚被用来初始化内置ICE™ TAP控制器。

6.2 测试引脚

TST1、TST0引脚用来定义器件的测试模式。这些引脚都没有集成下拉电阻所以用户必须确保这些引脚都 为低,以提供正常工作的条件(若为高将导致不可预知的结果)。与这些引脚相关的其它值保留作厂商测试 用。

4.1 208 引脚 PQFP 封装轮廓 图4-1给出208引脚PQFP封装定位。详细的机械说明见生产数据手册的AT91RM9200机械特性部分。 图 4-1. 208引脚PQFP封装(俯视图)

单片机家族

1. ATMEL单片机目前,国内广泛应用的芯片是80C51系列,其中ATMEL公司生产的具有Flash ROM的增强型51系列单片机目前在市场上仍然十分流行,其中AT89S系列十分活跃。

AVR单片机: AVR单片机是ATMEL在90年代推出的精简指令集RISC的单片机 ,跟PIC类似。

使用哈佛结构。

是增强型RISC内载Flash的单片机,芯片上的Flash存储器附在用户的产品中,可随时编程,再编程,使用户的产品设计容易,更新换代方便.AVR单片机采用增强的RISC 结构,使其具有高速处理能力,在一个时钟周期内可执行复杂的指令,每MHz可实现1MIPS的处理能力.AVR单片机工作电压为2.7~6.0V,可以实现耗电最优化。

AVR的单片机广泛应用于计算机外部设备,工业实时控制,仪器仪表,通讯设备,家用电器,宇航设备等各个领域。

AT91M系列是基于ARM7TDMI 嵌入式处理器的ATMEL 16/32 微处理器系列中的一个新成员该处理器用高密度的16 位指令集实现了高效的32位RISC结构且功耗很低。

2. Philips单片机飞利浦半导体作为全球著名的半导体产品供应商,在单片机( MCU )领域具有强大的影响力,产品范围广泛并且在技术创新上极为活跃。

尤其近几年在ARM(32位)和增强型51单片机方面,有大量的新产品问世。

飞利浦51系列单片机与MCS-51指令系统完全兼容。

代理商:广州周立功单片机发展有限公司:/home.asp2. MicroChip单片机MicroChip单片机的主要产品是PIC 16C系列和17C系列8位单片机,CPU采用RISC结构,分别仅有33,35,58条指令,采用Harvard双总线结构,运行速度快,低工作电压,低功耗,较大的输入输出直接驱动能力,价格低,一次性编程,小体积。

适用于用量大,档次低,价格敏感的产品.在办公自动化设备,消费电子产品,电讯通信,智能仪器仪表,汽车电子,金融电子,工业控制不同领域都有广泛的应用,PIC系列单片机在世界单片机市场份额排名中逐年提高.发展非常迅速。

AT91SAM7S64分析

芯片基本功能模块分析• 集成了ARM7TDMI® ARM® Thumb® 处理器–高性能的32 位RISC架构–高密度的16 位指令集–性能/功耗(MIPS/Watt) 的领先者–嵌入式ICE电路仿真,支持调试通讯分析:可以由FOUNDRY厂家license ARM7来解决,属于普通的ARM7内核• 64K 字节的片内高速Flash存储器,共512 页,每页128 字节–在最坏的条件下可以30 MHz 的速度进行单时钟周期访问,预取(Prefetch) 缓冲器可以实现Thumb指令的优化,使处理器以最快的速度执行指令–页编程时间为4 ms,包括页自动擦除,全片擦除时间为10 ms– 10,000 次的写寿命,10 年数据保持能力,扇区锁定功能,Flash 安全锁定位–适合量产的快速Flash编程接口分析:高速Flash也是由工艺厂家提供解决,但要分析性能与参数是否满足要求非易失性掉电检测控制掉电检测(BOD) 由两个通用的NVM (GPNVM)位控制。

因此即使没有了电源,掉电检测仍然可以保持用户的定义。

两个GPNVM 位的清除和设置分别通过EFC 用户接口的“清除通用NVM 位”命令和“设置通用NVM 位”命令来实现。

GPNVM 位0用于控制掉电检测的使能。

设置GPNVM0 将使能BOD,清除它即禁止BOD。

拉高ERASE 将清除GPNVM0,从而禁止BOD。

GPNVM 位1控制掉电检测信号是否可以用于系统复位。

置位GPNVM1使能这个功能,清零GPNVM1 则禁止掉电检测信号复位整个芯片。

拉高ERASE 将禁止掉电检测复位。

8个NVM位用于标定掉电检测器及电压调节器。

• 16K 字节的片内高速SRAM,可以在最高时钟速度下进行单时钟周期访问操作分析:由厂家提供解决,但控制器需要前端设计解决• 存储器控制器(MC)–嵌入式Flash控制器,异常中断(Abort)状态及未对齐(Misalignment) 检测分析:还需要分析这个MC详细的功能包括哪些?• 复位控制器(RSTC)–上电复位和经过工厂标定的掉电检测–提供复位源信息以及给外部电路使用的复位信号分析:需要详细分析功能,尤其掉电检测机制• 时钟发生器(CKGR)–低供耗RC 振荡器,3 到20MHz 的片上振荡器和一个PLL分析:RC振荡器应该由厂家解决,PLL应该可以免费得到• 电源管理控制器(PMC)–可以通过软件进行电源优化,包括慢速时钟模式( 低至500 Hz)和空闲(Idle)模式–三个可编程的外部时钟信号分析:类似SOC时钟模块,提供一些可编程控制,时钟切换,需要前端设计实现• 先进的中断控制器(AIC)–可以单独屏蔽的、具有8 个优先级的向量式中断源–两个外部中断源和一个快速中断源,可以防止虚假(spurious)中断分析:需要分析功能,要看看网上是否由可用的免费模块• 调试单元(DBGU)– 2线UART,支持调试通讯通道中断;可通过程序来禁止通过ICE进行访问分析:仅仅是uart?• 周期性间隔定时器(PIT)– 20位可编程的计数器,加上12 位的间隔计数器分析:类似timer,但12bit的间隔计数器要分析• 11 个外设数据控制器(PDC) 通道外设数据控制器(PDC) 在诸如UART、USART、SSC、SPI、MCI 等片上外设与片内或片外存储器间传输数据。

ATMEL芯片AT91SAM9G45

ATMEL 芯片AT91SAM9G45

介绍一款新的ATMEL 芯片AT91SAM9G45

推荐SAM9G45 开发板主频高达400MHz,可支持WinCE 和Linux 操

作系统的开发板调试,带有256MB NandFlash,2MB NorFlash,512KB EEPROM,4MB DataFlash,以及2 个64MB 的DDR2 SDRAM,并带有丰富的功能扩展:高速USB2.0(480MHz),音频输入,音频输出,10/100Mbps 网络,JTAG 调试接口,DBGU 串口,Micro SD 卡接口,SD/MMC 卡接口

AT91SAM9G45 芯片使用ARM926EJ-S 内核,它带有MMU 功能,有

一个64KB 的内部SRAM 和一个64KB 的内部ROM,并带有两个外部总线

接口,总共可支持4 块DDR2/LPDDR,SDRAM/LPSDR,静态存储器,CF

闪存或带ECC 校验的SLC NAND Flash。

AT91SAM9G45 芯片把用户接口的功能性和高速数据连接相结合,包

括LCD 控制器,电阻触摸屏,相机接口,音频,10/100M 以太网,高速

USB 和SDIO 等等。

随着处理器运行在400MHz 和多个速率超过100Mbps 的外设,AT91SAM9G45 使用高性能和带宽网络或本地存储媒体来提供良好的

用户体验。

AT91SAM9G45 支持最新的DDR2 和NAND 闪存接口来存储程序和数据。

一个与37 个DMA 通道相关的133M 的内部多层总线接口,以及一个双

外部总线接口,和一个能够用来配置紧密耦合内存(TCM)的64K 字节的分布。

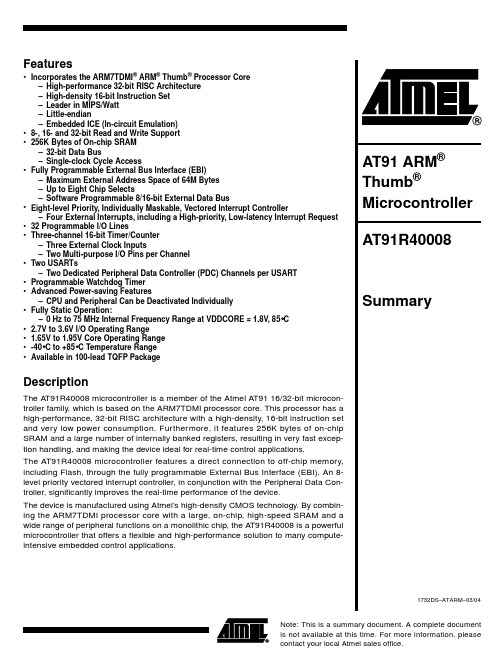

AT91R40008中文资料

1732DS–ATARM–03/04Features•Incorporates the ARM7TDMI ® ARM ® Thumb ® Processor Core–High-performance 32-bit RISC Architecture –High-density 16-bit Instruction Set –Leader in MIPS/Watt –Little-endian–Embedded ICE (In-circuit Emulation)•8-, 16- and 32-bit Read and Write Support •256K Bytes of On-chip SRAM –32-bit Data Bus–Single-clock Cycle Access•Fully Programmable External Bus Interface (EBI)–Maximum External Address Space of 64M Bytes –Up to Eight Chip Selects–Software Programmable 8/16-bit External Data Bus•Eight-level Priority, Individually Maskable, Vectored Interrupt Controller–Four External Interrupts, including a High-priority, Low-latency Interrupt Request •32 Programmable I/O Lines•Three-channel 16-bit Timer/Counter –Three External Clock Inputs–Two Multi-purpose I/O Pins per Channel •Two USARTs–Two Dedicated Peripheral Data Controller (PDC) Channels per USART •Programmable Watchdog Timer •Advanced Power-saving Features–CPU and Peripheral Can be Deactivated Individually •Fully Static Operation:–0 Hz to 75 MHz Internal Frequency Range at VDDCORE = 1.8V , 85°C • 2.7V to 3.6V I/O Operating Range• 1.65V to 1.95V Core Operating Range •-40°C to +85°C Temperature Range •Available in 100-lead TQFP PackageDescriptionThe AT91R40008 microcontroller is a member of the Atmel AT91 16/32-bit microcon-troller family, which is based on the ARM7TDMI processor core. This processor has a high-performance, 32-bit RISC architecture with a high-density, 16-bit instruction set and very low power consumption. Furthermore, it features 256K bytes of on-chip SRAM and a large number of internally banked registers, resulting in very fast excep-tion handling, and making the device ideal for real-time control applications.The AT91R40008 microcontroller features a direct connection to off-chip memory,including Flash, through the fully programmable External Bus Interface (EBI). An 8-level priority vectored interrupt controller, in conjunction with the Peripheral Data Con-troller, significantly improves the real-time performance of the device.The device is manufactured using Atmel’s high-density CMOS technology. By combin-ing the ARM7TDMI processor core with a large, on-chip, high-speed SRAM and a wide range of peripheral functions on a monolithic chip, the A T91R40008 is a powerful microcontroller that offers a flexible and high-performance solution to many compute-intensive embedded control applications.AT91 ARM ® Thumb ®Microcontroller AT91R40008SummaryNote: This is a summary document. A complete document is not available at this time. For more information, please contact your local Atmel sales office.2AT91R40008 - Summary1732DS–ATARM–03/04Pin ConfigurationFigure 1. AT91R40008 in 100-lead TQFP PackageP 21/T X D 1/N T R IP 20/S C K 1P 19P 18P 17P 16P 15/R X D 0P 14/T X D 0P 13/S C K 0P 12/F I QG N DP 11/I R Q 2P 10/I R Q 1V D D C O R EP 9/I R Q 0P 8/T I O B 2P 7/T I O A 2P 6/T C L K 2P 5/T I O B 1P 4/T I O A 1P 3/T C L K 1G N DG N DP 2/T I O B 0P1/TIOA0P0/TCLK0D15D14D13D12VDDIO D11D10D9D8D7D6D5GND D4D3D2D1D0P31/A23/CS4P30/A22/CS5VDDIO VDDCORE P29/A21/CS6P22/RXD1NWR1/NUBGND NRST NWDOVF VDDIO MCKI P23P24/BMS P25/MCKOGND GND TMS TDO TCK NRD/NOE NWR0/NWE VDDCOREVDDIO NWAIT NCS0NCS1P26/NCS2P27/NCS3A 0/N L BA 1A 2A 3A 4A 5A 6A 7A 8A 9A 10A 11A 12A 13A 14G N DG N DA 15A 16A 17A 18A 19P 28/A 20/C S 7G N D125234567891011121314151617181920212223242650272829303132333435363738394041424344454647484975517473727170696867666564636261605958575655545352100769998979695949392919089888786858483828180797877TDI V D D I OV D D I O3AT91R40008 - Summary1732DS–ATARM–03/04Pin DescriptionTable 1. AT91R40008 Pin DescriptionModuleName Function Type Active Level Comments EBIA0 - A23Address Bus Output –All valid after resetD0 - D15Data Bus I/O – NCS0 - NCS3Chip Select Output Low CS4 - CS7Chip SelectOutput High A23 - A20 after reset NWR0Lower Byte 0 Write Signal Output Low Used in Byte Write option NWR1Upper Byte 1 Write Signal Output Low Used in Byte Write option NRD Read Signal Output Low Used in Byte Write option NWE Write Enable Output Low Used in Byte Select option NOE Output Enable Output Low Used in Byte Select option NUB Upper Byte Select Output Low Used in Byte Select option NLB Lower Byte Select Output Low Used in Byte Select option NWAIT Wait Input Input Low BMSBoot Mode Select Input –Sampled during reset AICFIQ Fast Interrupt Request Input –PIO-controlled after reset IRQ0 - IRQ2External Interrupt Request Input –PIO-controlled after reset TCTCLK0 - TCLK2Timer External Clock Input –PIO-controlled after reset TIOA0 - TIOA2Multipurpose Timer I/O pin A I/O –PIO-controlled after reset TIOB0 - TIOB2Multipurpose Timer I/O pin B I/O –PIO-controlled after reset USARTSCK0 - SCK1External Serial Clock I/O –PIO-controlled after reset TXD0 - TXD1Transmit Data Output Output –PIO-controlled after reset RXD0 - RXD1Receive Data Input Input –PIO-controlled after reset PIO P0 - P31Parallel IO line I/O –WD NWDOVF Watchdog Overflow Output Low Open-drain ClockMCKI Master Clock Input Input –Schmidt trigger MCKO Master Clock Output Output –ResetNRST Hardware Reset Input Input Low Schmidt trigger NTRI Tri-state Mode Select Input Low Sampled during resetICETMSTest Mode Select Input –Schmidt trigger, internal pull-up TDI Test Data Input Input –Schmidt trigger, internal pull-up TDO Test Data Output Output –TCK Test Clock Input –Schmidt trigger, internal pull-up PowerVDDIOI/O Power Power – 3V nominal supply VDDCORE Core Power Power – 1.8V nominal supply GNDGroundGround–4AT91R40008 - Summary1732DS–ATARM–03/04Block DiagramFigure 2. AT91R40008ARM7TDMI CoreEmbeddedICEReset E B I : E x t e r n a l B u s I n t e r f a c eASB ControllerClockAIC: Advanced Interrupt ControllerAMBA BridgeEBI User InterfaceTC: Timer Counter TC0TC1TC2USART0USART12 PDC Channels2 PDC ChannelsPIO: Parallel I/O ControllerPS: Power SavingChip IDWD: WatchdogTimerAPBASBP I OP I ONRSTD0-D15A1-A19A0/NLB NRD/NOE NWR0/NWE NWR1/NUB NWAIT NCS0NCS1P26/NCS2P27/NCS3P28/A20/CS7P29/A21/CS6P30/A22/CS5P31/A23/CS4P0/TCLK0P3/TCLK1P6/TCLK2P1/TIOA0P2/TIOB0P4/TIOA1P5/TIOB1P7/TIOA2P8/TIOB2NWDOVFTMS TDO TDI TCKMCKIP25/MCKOP12/FIQ P9/IRQ0P10/IRQ1P11/IRQ2P13/SCK0P14/TXD0P15/RXD0P20/SCK1P21/TXD1/NTRIP22/RXD1P16P17P18P19P23P24/BMS256K Bytes RAM5AT91R40008 - Summary1732DS–ATARM–03/04Architectural OverviewThe AT91R40008 microcontroller integrates an ARM7TDMI with embedded ICE inter-face, memories and peripherals. The architecture consists of two main buses: the Advanced System Bus (ASB) and the Advanced Peripheral Bus (APB). Designed for maximum performance and controlled by the memory controller, the ASB interfaces the ARM7TDMI processor with the on-chip 32-bit memories, the External Bus Interface (EBI) and the AMBA ™ Bridge. The AMBA Bridge drives the APB, which is designed for accesses to on-chip peripherals and optimized for low power consumption.The AT91R40008 microcontroller implements the ICE port of the ARM7TDMI processor on dedicated pins, offering a complete, low-cost and easy-to-use debug solution for tar-get debugging.MemoriesThe AT91R40008 microcontroller embeds 256K bytes of internal SRAM. The internal memory is directly connected to the 32-bit data bus and is single-cycle accessible. The AT91R40008 microcontroller features an External Bus Interface (EBI), which enables connection of external memories and application-specific peripherals. The EBI supports 8- or 16-bit devices and can use two 8-bit devices to emulate a single 16-bit device. The EBI implements the early read protocol, enabling faster memory accesses than standard memory interfaces.PeripheralsThe AT91R40008 microcontrollers integrate several peripherals, that are classified as system or user peripherals. All on-chip peripherals are 32-bit accessible by the AMBA Bridge, and can be programmed with a minimum number of instructions. The peripheral register set consists of control, mode, data, status and enable/disable/status registers.An on-chip Peripheral Data Controller (PDC) transfers data between the on-chip USARTs and on- and off-chip memories address space without processor intervention.Most importantly, the PDC removes the processor interrupt handling overhead, making it possible to transfer up to 64K contiguous bytes without reprogramming the start address, thus increasing the performance of the microcontroller and reducing the power consumption.System PeripheralsThe External Bus Interface (EBI) controls the external memory or peripheral devices via an 8- or 16-bit data bus and is programmed through the Advanced Peripheral Bus (APB). Each chip select line has its own programming register.The Power-saving (PS) module implements the Idle mode (ARM7TDMI core clock stopped until the next interrupt) and enables the user to adapt the power consumption of the microcontroller to application requirements (independent peripheral clock control).The Advanced Interrupt Controller (AIC) controls the internal interrupt sources from the internal peripherals and the four external interrupt lines (including the FIQ) to provide an interrupt and/or fast interrupt request to the ARM7TDMI. It integrates an 8-level priority controller and, using the Auto-vectoring feature, reduces the interrupt latency time.The Parallel Input/Output Controller (PIO) controls up to 32 I/O lines. It enables the user to select specific pins for on-chip peripheral input/output functions and general-purpose input/output signal pins. The PIO controller can be programmed to detect an interrupt on a signal change from each line.The Watchdog (WD) can be used to prevent system lock-up if the software becomes trapped in a deadlock.The Special Function (SF) module integrates the Chip ID, the Reset Status and the Pro-tect registers.6AT91R40008 - Summary1732DS–ATARM–03/04User PeripheralsTwo independently configurable USARTs enable communication at a high baud rate in synchronous or asynchronous mode. The format includes start, stop and parity bits and up to 8 data bits. Each USART also features a Time-out and a Time-guard register,facilitating the use of the two dedicated Peripheral Data Controller (PDC) channels.The 3-channel, 16-bit Timer/Counter (TC) is highly programmable and supports capture or waveform modes. Each TC channel can be programmed to measure or generate dif-ferent kinds of waves, and can detect and control two input/output signals. The TC also has three external clock signals.7AT91R40008 - Summary1732DS–ATARM–03/04Associated DocumentationThe A T91R40008 is part of the A T91X40 series of microcontrollers, a member of the Atmel AT91 16/32-bit microcontroller family, which is based on the ARM7TDMI processor core. The table below contains details of associated documentation for further reference.Table 2. Associated DocumentationProductInformationDocument TitleA T91R40008Internal architecture of processor ARM/Thumb instruction sets Embedded in-circuit-emulator ARM7TDMI (Thumb) DatasheetExternal memory interface mapping Peripheral operations Peripheral user interfacesA T91x40 Series DatasheetDC characteristics Power consumptionThermal and reliability considerations AC characteristics A T91R40008 Electrical CharacteristicsProduct overview Ordering information Packaging information Soldering profileA T91R40008 Summary Datasheet (this document)8AT91R40008 - Summary1732DS–ATARM–03/04Product OverviewPower SupplyThe AT91R40008 microcontroller has two types of power supply pins: •VDDCORE pins, which power the chip core (i.e., the ARM7TDMI, embedded memory and the peripherals).•VDDIO pins, which power the I/O lines.An independent I/O supply allows a flexible adaptation to external component signal levels.Input/Output ConsiderationsAfter the reset, the peripheral I/Os are initialized as inputs to provide the user with maxi-mum flexibility. It is recommended that in any application phase, the inputs to the AT91R40008 microcontroller be held at valid logic levels to minimize the power consumption.Master ClockThe AT91R40008 microcontroller has a fully static design and works on the Master Clock (MCK) provided on the MCKI pin from an external source.The Master Clock is also provided as an output of the device on the pin MCKO, which is multiplexed through a general-purpose I/O line. While NRST is active, MCKO remains low. After the reset, the MCKO is valid and outputs an image of the MCK signal. The PIO controller must be programmed to use this pin as standard I/O line.ResetReset restores the default states of the user interface registers (defined in the user inter-face of each peripheral) and forces the ARM7TDMI to perform the next instruction fetch from address zero. Except for the program counter, the ARM7TDMI registers do not have defined reset states.NRST PinNRST is active low-level input. It is asserted asynchronously, but exit from reset is syn-chronized internally to the MCK. The signal presented on MCKI must be active within the specification for a minimum of 10 clock cycles up to the rising edge of NRST to ensure correct operation.The first processor fetch occurs 80 clock cycles after the rising edge of NRST.Watchdog ResetThe Watchdog can be programmed to generate an internal reset. In this case, the reset has the same effect as the NRST pin assertion, but the pins BMS and NTRI are not sampled. Boot Mode and Tri-state Mode are not updated. If the NRST pin is asserted and the Watchdog triggers the internal reset, the NRST pin has priority.Emulation FunctionsTri-state ModeThe AT91R40008 microcontroller provides a tri-state mode, which is used for debug purposes. This enables the connection of an emulator probe to an application board without having to desolder the device from the target board. In tri-state mode, all the out-put pin drivers of the AT91R40008 microcontroller are disabled.To enter tri-state mode, the NTRI pin must be held low during the last 10 clock cycles before the rising edge of NRST. For normal operation, the NTRI pin must be held high during reset by a resistor of up to 400 k Ω.NTRI is multiplexed with I/O line P21 and USART1 serial data transmit line TXD1.Standard RS-232 drivers generally contain internal 400 k Ω pull-up resistors. If TXD1 is connected to a device not including this pull-up, the user must make sure that a high level is tied on NTRI while NRST is asserted.9AT91R40008 - Summary1732DS–ATARM–03/04JTAG/ICE DebugARM standard embedded in-circuit emulation is supported via the JTAG/ICE port. The pins TDI, TDO, TCK and TMS are dedicated to this debug function and can be con-nected to a host computer via the external ICE interface.In ICE Debug mode, the ARM7TDMI core responds with a non-JTAG chip ID that identi-fies the microcontroller. This is not fully IEEE1149.1 compliant.Memory ControllerThe ARM7TDMI processor address space is 4G bytes. The memory controller decodes the internal 32-bit address bus and defines three address spaces:•Internal memories in the four lowest megabytes•Middle space reserved for the external devices (memory or peripherals) controlled by the EBI•Internal peripherals in the four highest megabytesIn any of these address spaces, the ARM7TDMI operates in Little-endian mode only.Internal MemoriesThe AT91R40008 microcontroller integrates 256K bytes of internal SRAM. All internal memories are 32 bits wide and single-clock cycle accessible. Byte (8-bit), half-word (16-bit) or word (32-bit) accesses are supported and are executed within one cycle. Fetching Thumb or ARM instructions is supported and internal memory can store twice as many Thumb instructions as ARM ones.The SRAM is mapped at address 0x0 (after the Remap command), allowing ARM7TDMI exception vectors between 0x0 and 0x20 to be modified by the software. Placing the SRAM on-chip and using the 32-bit data bus bandwidth maximizes the microcontroller performance and minimizes the system power consumption. The 32-bit bus increases the effectiveness of the use of the ARM instruction set and the ability of processing data that is wider than 16-bit, thus making optimal use of the ARM7TDMI advanced performance.Being able to dynamically update application software in the 256-Kbyte SRAM adds an extra dimension to the AT91R40008.Boot Mode SelectThe ARM reset vector is at address 0x0. After the NRST line is released, the ARM7TDMI executes the instruction stored at this address. This means that this address must be mapped in nonvolatile memory after the reset.The input level on the BMS pin during the last 10 clock cycles before the rising edge of the NRST selects the type of boot memory (see Table 3).The BMS pin is multiplexed with the I/O line P24, which can be programmed after reset like any standard PIO line.Table 3. Boot Mode SelectBMS Boot Memory1External 8-bit memory on NCS00External 16-bit memory on NCS010AT91R40008 - Summary1732DS–ATARM–03/04Remap CommandThe ARM vectors (Reset, Abort, Data Abort, Pre-fetch Abort, Undefined Instruction,Interrupt, Fast Interrupt) are mapped from address 0x0 to address 0x20. In order to allow these vectors to be redefined dynamically by the software, the AT91R40008microcontroller uses a Remap command that enables switching between the boot mem-ory and the internal primary SRAM bank addresses. The Remap command is accessible through the EBI User Interface by writing one in RCB of EBI_RCR (Remap Control Register). Performing a Remap command is mandatory if access to the other external devices (connected to chip-selects 1 to 7) is required. The Remap operation can only be changed back by an internal reset or an NRST assertion.Abort ControlThe abort signal providing a Data Abort or a Pre-fetch Abort exception to the ARM7TDMI is asserted when accessing an undefined address in the EBI address space.No abort is generated when reading the internal memory or by accessing the internal peripherals, whether or not the address is defined.External Bus InterfaceThe External Bus Interface handles the accesses between addresses 0x0040 0000 and 0xFFC0 0000. It generates the signals that control access to the external devices, and can be configured from eight 1M byte banks up to four 16M bytes banks. It supports byte-, half-word- and word-aligned accesses.For each of these banks, the user can program:•Number of wait states•Number of data float times (wait time after the access is finished to prevent any bus contention in case the device is too long in releasing the bus)•Data bus width (8-bit or 16-bit)The user can program the EBI to control one 16-bit device (Byte Select Access mode)with a 16-bit wide data bus or two 8-bit devices in parallel that emulate a 16-bit memory (Byte Write Access mode).The External Bus Interface also features the Early Read Protocol, configurable for all the devices, which significantly reduces access time requirements on an external device in the case of single-clock cycle access.11AT91R40008 - Summary1732DS–ATARM–03/04PeripheralsThe AT91R40008 microcontroller peripherals are connected to the 32-bit wide Advanced Peripheral Bus. Peripheral registers are only word accessible – byte and half-word accesses are not supported. If a byte or a half-word access is attempted, the mem-ory controller automatically masks the lowest address bits and generates a word access.Each peripheral has a 16-Kbyte address space allocated (the AIC only has a 4-Kbyte address space).Peripheral RegistersThe following registers are common to all peripherals:•Control Register – write-only register that triggers a command when a one is written to the corresponding position at the appropriate address. Writing a zero has no effect.•Mode Register – read/write register that defines the configuration of the peripheral. Usually has a value of 0x0 after a reset.•Data Registers – read and/or write registers that enable the exchange of data between the processor and the peripheral.•Status Register – read-only register that returns the status of the peripheral.•Enable/Disable/Status Registers are shadow command registers. Writing a one in the Enable Register sets the corresponding bit in the Status Register. Writing a one in the Disable Register resets the corresponding bit and the result can be read in the Status Register. Writing a bit to zero has no effect. This register access method maximizes the efficiency of bit manipulation and enables modification of a register with a single non-interruptible instruction, replacing the costly read-modify-write operation.Unused bits in the peripheral registers are shown as “–” and must be written at 0 for upward compatibility. These bits read 0.Peripheral Interrupt ControlThe Interrupt Control of each peripheral is controlled from the Status Register using the interrupt mask. The Status Register bits are ANDed to their corresponding interrupt mask bits and the result is then ORed to generate the Interrupt Source signal to the Advanced Interrupt Controller.The interrupt mask is read in the Interrupt Mask Register and is modified with the Inter-rupt Enable Register and the Interrupt Disable Register. The enable/disable/status (or mask) makes it possible to enable or disable peripheral interrupt sources with a non-interruptible single instruction. This eliminates the need for interrupt masking at the AIC or Core level in real-time and multi-tasking systems.Peripheral Data ControllerThe AT91R40008 microcontroller has a 4-channel PDC dedicated to the two on-chip USARTs. One PDC channel is dedicated to the receiver and one to the transmitter of each USART.The user interface of a PDC channel is integrated in the memory space of each USART.It contains a 32-bit Address Pointer Register (RPR or TPR) in addition to a 16-bit Trans-fer Counter Register (RCR or TCR). When the programmed number of transfers are performed, a status bit indicating the end of transfer is set in the USART Status Register and an interrupt can be generated.12AT91R40008 - Summary1732DS–ATARM–03/04System PeripheralsPS: Power-savingThe Power-saving feature optimizes power consumption, enabling the software to stop the ARM7TDMI clock (Idle mode), restarting it when the module receives an interrupt (or reset). It also enables on-chip peripheral clocks to be enabled and disabled individually,matching power consumption and application need.AIC: Advanced Interrupt ControllerThe Advanced Interrupt Controller has an 8-level priority, individually maskable, vec-tored interrupt controller, and drives the NIRQ and NFIQ pins of the ARM7TDMI from:•The external fast interrupt line (FIQ)•The three external interrupt request lines (IRQ0 - IRQ2)•The interrupt signals from the on-chip peripheralsThe AIC is extensively programmable offering maximum flexibility, and its vectoring fea-tures reduce the real-time overhead in handling interrupts.The AIC also features a spurious vector, which reduces spurious interrupt handling to a minimum, and a protect mode that facilitates the debug capabilities.PIO: Parallel I/O ControllerThe AT91R40008 microcontroller has 32 programmable I/O lines. Six pins are dedi-cated as general-purpose I/O pins. Other I/O lines are multiplexed with an external signal of a peripheral to optimize the use of available package pins. The PIO controller enables generation of an interrupt on input change on any of the PIO pins.WD: WatchdogThe Watchdog is built around a 16-bit counter and is used to prevent system lock-up if the software becomes trapped in a deadlock. It can generate an internal reset or inter-rupt, or assert an active level on the dedicated pin NWDOVF. All programming registers are password-protected to prevent unintentional programming.SF: Special FunctionThe AT91R40008 microcontroller provides registers that implement the following special functions:•Chip identification •RESET status •Protectmode13AT91R40008 - Summary1732DS–ATARM–03/04User PeripheralsUSART: Universal Synchronous/Asynchronous Receiver TransmitterThe AT91R40008 microcontroller provides two identical, full-duplex, universal synchro-nous/asynchronous receiver/transmitters.Each USART has its own baud rate generator and two dedicated Peripheral Data Con-troller channels. The data format includes a start bit, up to 8 data bits, an optional programmable parity bit and up to 2 stop bits.The USART also features a Receiver Time-out Register, facilitating variable length frame support when it is working with the PDC, and a Time-guard Register, used when interfacing with slow remote equipment.TC: Timer/CounterThe AT91R40008 microcontroller features a Timer/Counter block that includes three identical 16-bit Timer/Counter channels. It is possible to independently program each channel to perform a wide range of functions, including frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.The Timer/Counter can be used in Capture or Waveform mode, and all three counter channels can be started simultaneously and chained together.14AT91R40008 - Summary1732DS–ATARM–03/04Ordering InformationTable 4. Ordering InformationOrdering Code Package Operation Range A T91R40008-66AITQFP 100Industrial (-40°C to 85°C)15AT91R40008 - Summary1732DS–ATARM–03/04Packaging InformationFigure 3. 100-lead Thin Quad Flat Pack Package OutlinePIN 1aaabbbc c 1dddθ2θ3SL1R1R20.25θcccθ116AT91R40008 - Summary1732DS–ATARM–03/04Table 5. Common Dimensions (mm)SymbolMin NomMax c 0.090.2c10.090.16L 0.450.60.75L1 1.00 REFR20.080.2R10.08S 0.2q0° 3.5°7°θ10°θ211°12°13°θ311°12°13°A 1.6A10.050.15A21.351.41.45Tolerances of Form and Positionaaa 0.2bbb0.2Table 6. Lead Count Dimensions (mm)Pin Count D/E BSC D1/E1 BSC bb1 e BSC ccc ddd Min Nom Max Min Nom Max 10016.014.00.170.220.270.170.20.230.500.100.06Table 7. Device and 100-lead TQFP Package Maximum Weight710mgTable 8. 100-lead TQFP Package CharacteristicsMoisture Sensitivity Level317AT91R40008 - Summary1732DS–ATARM–03/04Soldering ProfileTable 9 gives the recommended soldering profile from J-STD-20. Small packages may be subject to higher temperatures if they are reflowed in boards with larger components. In this case, small packages may have to withstand tempera-tures of up to 235°C, not 220°C (IR reflow).Recommended package reflow conditions depend on package thickness and volume.See Table 10.When certain small thin packages are used on boards without larger packages, these small packages may be classified at 220°C instead of 235°C.Notes:1.The packages are qualified by Atmel by using IR reflow conditions, not convection orVPR.2.By default, the package level 1 is qualified at 220°C (unless 235°C is stipulated).3.The body temperature is the most important parameter but other profile parameterssuch as total exposure time to hot temperature or heating rate may also influence component reliability.A maximum of three reflow passes is allowed per component.Table 9. Soldering ProfileConvection or IR/ConvectionVPR Average Ramp-up Rate (183° C to Peak)3°C/sec. max.10°C/sec.Preheat Temperature 125°C ±25°C 120 sec. max Temperature Maintained Above 183°C 60 sec. to 150 sec.Time within 5°C of Actual Peak Temperature 10 sec. to 20 sec.60 sec.Peak T emperature Range 220 +5/-0°C or 235 +5/-0°C 215 to 219°C or 235 +5/-0°C Ramp-down Rate6°C/sec.10°C/sec.Time 25°C to Peak Temperature6 min. maxTable 10. Recommended Package Reflow Conditions (1, 2, 3)Parameter Temperature Convection 235 +5/-0°C VPR235 +5/-0°C IR/Convection235 +5/-0°C。

SAM3S微控制器系列应用说明书

SAM3S Microcontroller Series Array Schematic Check List1.IntroductionThis Application Note is a schematic review check list for systems embedding Atmel’s SAM3S series of ARM® Cortex™-M3, Thumb®2-based microcontrollers.It gives requirements concerning the different pin connections that must be consid-ered before starting any new board design and describes the minimum hardware resources required to quickly develop an application with the SAM3S Series. It does not consider PCB layout constraints.It also gives advice regarding low-power design constraints to minimize power consumption.This Application Note is not intended to be exhaustive. Its objective is to cover as many configurations of use as possible.The Check List table has a column reserved for reviewing designers to verify that theline item has been checked.211061A–ATARM–28-Jul-10Application Note2.Associated DocumentationBefore going further into this Application Note, it is strongly recommended to check the latest documents for the SAM3S Series Microcontrollers on Atmel’s Web site.Table 2-1 gives the associated documentation needed to support full understanding of this appli-cation note.Table 2-1.Associated DocumentationInformationDocument TitleUser ManualElectrical/Mechanical CharacteristicsOrdering InformationErrata SAM3S Series Product DatasheetInternal architecture of processorThumb2 instruction sets Embedded in-circuit-emulatorThis part is integrated and formated according to the core integration in the SAM3S series. This information is fully detailed in the SAM3S Series ProductDatasheet.Cortex-M3 Technical Reference Manual (available from ARM Ltd.)Evaluation Kit User GuideSAM3S-EK Evaluation Board User Guide311061A–ATARM–28-Jul-10Application Note3.Schematic Check List;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator, ADC, DAC and Analogcomparator power supply.VDDIO1.62V to 3.6VDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)Powers the peripheral I/Os, USB transceiver, Backuppart, 32kHz crystal oscillator and oscillator pads .Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.Decoupling/Filtering capacitors must be added toguarantee stability.411061A–ATARM–28-Jul-10Application NoteNote: RestrictionsWith Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable.With Main Supply ≥ 2.0V and < 3V, USB is not usable.With Main Supply ≥ 3V, all peripherals are usable.VDDCOREMust be connected directly to VDDOUTpin.1.62V to 1.95VDecoupling capacitor (100 nF)(1)(2)Power the Core, the embedded memories and theperipherals power supply.VDDPLL 1.62V to 1.95VDecoupling capacitor (100 nF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description511061A–ATARM–28-Jul-10Application Note;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator, ADC, DAC and Analogcomparator power supply.VDDIO1.62V to 3.6VConnected to Main Supply Decoupling/Filtering capacitors(100 nF and 2.2 µF)(1)(2)Powers the peripheral I/Os.Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.Decoupling/Filtering capacitors must be added toguarantee stability.611061A–ATARM–28-Jul-10Application NoteNote: RestrictionsWith Main Supply < 2.0 V, USB and ADC/DAC and Analog comparator are not usable.With Main Supply ≥ 2.0V and < 3V, USB is not usable.With Main Supply ≥ 3V, all peripherals are usable.VDDCORE 1.62V to 1.95VConnected to VDDCORE Supply Decoupling capacitor (100 nF and2.2µF)(1)(2)Core, embedded memories and peripherals power supplyVDDPLL1.62V to 1.95VConnected to VDDCORE Supply Decoupling capacitor (100 nF and2.2µF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description711061A–ATARM–28-Jul-10Application Note;Signal Name Recommended Pin Connection DescriptionVDDIN1.8V to 3.6VDecoupling/Filtering capacitor (10μF or higher ceramic capacitor)(1)(2)Powers the voltage regulator.VDDIO1.62V to 3.6VDecoupling/Filtering capacitors(100 nF and 2.2 µF)(1)(2)Powers the peripheral I/Os.Decoupling/Filtering capacitors must be added to improvestartup stability and reduce source voltage drop.Warning: At power-up VDDIO needs to reach 0.6Vbefore VDDIN reaches 1.0VVDDOUTDecoupling/Filtering capacitors(100 nF and 2.2µF)(1)(2)1.8V Output of the main voltage regulator.811061A–ATARM–28-Jul-10Application NoteNote: The two diodes provide a "switchover circuit" (for illustration purpose) between the backup battery and the main sup-ply when the system is put in backup mode.VDDCORE1.62V to 1.95VConnected to VDDOUT Supply Decoupling capacitor (100 nF)(1)(2)Core, embedded memories and peripherals power supplyVDDPLL1.62V to 1.95VConnected to VDDOUT Supply Decoupling capacitor (100 nF)(1)(2)Powers PLLA, PLLB, the Farst RC and the 3-20 MHzoscillator.GNDGroundGround pins GND are common to VDDIO, VDDPLL andVDDCORE;Signal Name Recommended Pin Connection Description911061A–ATARM–28-Jul-10Application Note1011061A–ATARM–28-Jul-10Application Note1111061A–ATARM–28-Jul-10Application NoteSerial Wire and JTAG (3)TCK/SWCLK/PB7Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TMS/SWDIO/PB6Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TDI/PB4Application dependantIf debug mode is not required this pin canbe use as GPIOReset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabled TDO/TRACESWO/PB5Application dependantIf debug mode is not required this pin canbe use as GPIO Reset State:- SWJ-DP Mode - Internal pull-up disabled - Schmitt Trigger enabledJTAGSEL Application dependant.Must be tied to V VDDIO to enter JTAGBoundary Scan.In harsh environments, It is strongly recommended to tie this pin to GND.Permanent Internal pull-down resistor (15 kOhm).Flash MemoryERASE/PB12Application dependant.If hardware erase is not required this pincan be use as GPIOInternal pull-down resistor (100kOhm).Must be tied to V VDDIO to erase the General Purpose NVM bits (GPNVMx), the whole Flash content and the securitybit.Reset state: Erase Input, with a 100 kOhm Internal pulldown and Schmitt trigger enabled Minimum debouncing time is 220 ms.Reset/TestNRSTApplication dependant.Can be connected to a push button forhardware reset.By default, the NRST pin is configured as an inputPermanent internal pull-up resistor to V VDDIO (15 kOhm).TST TST pin can be left unconnected innormal modeTo enter in FFPI mode TST pin must be tiedto V VDDIO.In harsh environments, It is strongly recommended to tie this pin to GND.Permanent internal pull-down resistor (15 kOhm).;Signal NameRecommended Pin ConnectionDescription1211061A–ATARM–28-Jul-10Application NotePIOPAx - PBx-PCxApplication Dependant (Pulled-up on V VDDIO )At reset, all PIOs are in IO or System IO mode with Schmitttrigger inputs and internal pull-up enabled.To reduce power consumption, if not used, the concerned PIO can be configured as an output and driven at ‘0’ withinternal pull-up disabled.Parallel Capture ModePIODC0-PIODC7Application Dependant V VDDIO Parallel Mode capture Data PIODCCLK Application Dependant V VDDIO Parallel Mode capture Clock PIODCEN1-2Application Dependant V VDDIOParallel Mode capture mode enableAnalog ReferenceADVREF2.0V to V DDIO (*)Decoupling capacitor(s).(*)2.0V is used for 10-bit ADC resolution only. In other case the minimum ADVREFvalue is 2.4V.ADVREF is a pure analog input.ADVREF is the voltage reference for the ADC,DAC andAnalog comparator.To reduce power consumption, if analog features are notused, connect ADVREF to GND.12-bit ADCAD0-AD140 to ADVREF.ADC Channels ADTRGV DDIO .ADC External Trigger input10-bit ADC (4)AD0-AD140 to ADVREF.ADC Channels ADTRGV DDIO .ADC External Trigger input12-bit DACDAC0-DAC11/6* ADVREF to 5/6* ADVREFDACTRGV DDIO .DAC External Trigger inputUSB Device (UDP)DDP/PB10Application dependent (3)If USB device support is not required thispin can be use as GPIO Reset State:- USB Mode - Internal Pull-down DDM/PB11Application dependent (3)If USB device support is not required thispin can be use as GPIOIReset State:- USB Mode - Internal Pull-down ;Signal Name Recommended Pin ConnectionDescription1311061A–ATARM–28-Jul-10Application NoteNotes: 1.These values are given only as a typical example.2.Decoupling capacitors must be connected as close as possible to the microcontroller and on each concerned pin.B Device Typical connection: copy of Figure 37-2 of the Datasheet4.Note that the ADC voltages in 10-bit mode resolution (ADC 12-bit in low resolution) can descend to 2.0V. Only one ADC isavailable on the SAM3S series.Static Memory Controller (SMC)D0-D15Application dependent.Data Bus (D0 to D15)Note: Data bus lines are multiplexed with the PIOB controller. Their I/O line reset state isinput with pull-up enabled .A0-A23Application dependent.Address Bus (A0 to A23)Note: Data bus lines are multiplexed withthe PIOB & PIOC controllers. Their I/O line reset state isinput with pull-up enabled .NWAITApplication dependent.NWAIT pin is an active low input.Note: NWAIT is multiplexed with PC18.;Signal NameRecommended Pin ConnectionDescription1411061A–ATARM–28-Jul-10Application Note4.SAM3S Boot Program Hardware ConstraintsSee AT91SAM Boot Program section of the SAM3S Series Datasheet for more details on the boot program.4.1SAM-BA BootThe SAM-BA ® Boot Assistant supports serial communication via the UART or USB device port:•UART0 Hardware Requirements: none.•USB Device Hardware Requirements:External Crystal or External Clock (1) with frequency of:11,289 MHz 12,000 MHz 16,000 MHz 18,432 MHzNote:1.Must be 2500 ppm and 1.8V Square Wave SignalTable 4-1.Pins driven during SAM-BA Boot Program executionPeripheral Pin PIO Line UART0URXD PA9UART0UTXDPA101511061A–ATARM–28-Jul-10Application Note5.Revision HistoryTable 5-1.Revision HistoryDoc. Rev Date Comments ChangeRequest Ref.11061A28-Jul-10First issueHeadquarters InternationalAtmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USATel: 1(408) 441-0311 Fax: 1(408) 487-2600Atmel AsiaUnit 1-5 & 16, 19/FBEA Tower, Millennium City 5418 Kwun Tong RoadKwun Tong, KowloonHong KongTel: (852) 2245-6100Fax: (852) 2722-1369Atmel EuropeLe Krebs8, Rue Jean-Pierre TimbaudBP 30978054 Saint-Quentin-en-Yvelines CedexFranceTel: (33) 1-30-60-70-00Fax: (33) 1-30-60-71-11Atmel Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Product ContactWeb Site/AT91SAMTechnical SupportAT91SAM SupportAtmel techincal supportSales Contacts/contacts/Literature Requests/literatureDisclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.© 2010 Atmel Corporation. All rights reserved. Atmel®, Atmel logo, SAM-BA® and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. ARM®, the ARMPowered® Logo, Thumb®, Cortex™ and others are the registered trade-marks or trademarks of ARM Ltd. Other terms and product names may be trademarks of others.11061A–ATARM–28-Jul-10。

AT91SAM7X256中文版

ADTRG AD0 AD1 AD2 AD3 AD4 AD5 AD6 AD7

ADVREF

JTAG

DDM DDP

PWM0 PWM1 PWM2 PWM3 TF TK TD RD RK RF TCLK0 TCLK1 TCLK2 TIOA0 TIOB0 TIOA1 TIOB1 TIOA2 TIOB2 TWD TWCK CANRX CANTX

4

欢迎访问本公司网站 /

– 支持嵌入式 ICE 内电路仿真以及调试通讯接口 • 片内高速 Flash

– 256K 字节 (AT91SAM7X256) ,共 1024 页,每页 256 字节 – 128K 字节 (AT91SAM7X128) ,共 512 页,每页 256 字节

– 最差情况下仍保持 30 MHz 的单时钟周期存取速度 – 预读取缓冲器使 Thumb 指令最优化运行以达到最高速度 – 每页编程时间为 6 ms,包括页自动擦除, 全片擦除时间为 15 ms – 10,000 次擦写次数, 10 年数据保存能力, 扇区锁定能力,设置 Flash 安全位 – 对量大的数据内容提供快速 Flash 编程接口

– 只支持主模式,支持所有的两线 Atmel EEPROM

• 一个 8 通道 10 位模数转化器,其中四个通道与数字 I/O 接口复用 • SAM-BA™ Boot 助手

– 默认 Boot 编程方式 – 与 SAM-BA 图形用户界面的接口

• IEEE 1149.1 JTAG 边界扫描支持所有数字引脚 • 容许 5V 输入/输出,包括四个高电流驱动 I/O 线,每个高达 16 mA • 电源提供

Atmel发售ARMSC100支持的安全微控制器.

上市与定价

Atmel

AtmelCorporation日前宣布推出AT91SC192192CT-USB,这是一款基于FLASH、由ARMSC100提供支持的安全微控制器。AT91SC产品是一系列低功率、高性能的32位RISC安全微控制器,具有ROM或FLASH程序存储器、EEPROM数据存储器和功能强大的密码加速器。这些产品锁定那些需要较高计算能力、高速通信接口和无缝连接到巨大的存储器的应用。

AT91SC192192CT-USB基于ARMSC100CPU,拥有192Kbytes的FLASH程序存储器、192Kbytes的高性能EEPROM(擦/写快、耐用性高)以及24Kbytes的RAM。该产品还包括一个5端口全速USB2.0接口、一个可以在嵌入式系统环境中进行通信或与NORFlash相连接的SPI接口以及可以与NANDFlash相连接的专用硬件。该设备尤其适用于建立安全的高端电子令牌(e-Token)和用于嵌入式系统。在嵌入式系统中,它能够充当安全模块,预防硬件伪造,存储安全数据,提供认证服务,进行数字版权管理等。

AT91SC192192CT-USB样品现在已经以LQFP64封装形式推出。每购买10,000件产品的起步单价为8.84美元。

Almel AT91SAM7S64 AT91 ARM Thumb 微处理器 说明书

特点Array•集成了ARM7TDMI® ARM® Thumb®处理器–高性能的32位RISC架构–高密度的16位指令集–性能/功耗(MIPS/Watt)的领先者–嵌入式ICE电路仿真,支持调试通讯•64K字节的片内高速Flash存储器,共512页,每页128字节–在最坏的条件下可以30 MHz的速度进行单时钟周期访问,预取(Prefetch)缓冲器可以实现Thumb指令的优化,使处理器以最快的速度执行指令–页编程时间为4 ms,包括页自动擦除,全片擦除时间为10 ms–10,000次的写寿命,10年数据保持能力,扇区锁定功能,Flash安全锁定位–适合量产的快速Flash编程接口•16K字节的片内高速SRAM,可以在最高时钟速度下进行单时钟周期访问操作•存储器控制器(MC)–嵌入式Flash控制器,异常中断(Abort)状态及未对齐(Misalignment)检测•复位控制器 (RSTC)–上电复位和经过工厂标定的掉电检测–提供复位源信息以及给外部电路使用的复位信号•时钟发生器(CKGR)– 低耗RC 振荡器,3 到20MHz 的片上振荡器和一个PLL•电源管理控制器(PMC)–可以通过软件进行电源优化,包括慢速时钟模式(低至500 Hz)和空闲(Idle)模式–三个可编程的外部时钟信号•先进的中断控制器(AIC)–可以单独屏蔽的、具有8个优先级的向量式中断源–两个外部中断源和一个快速中断源,可以防止虚假(spurious)中断•调试单元(DBGU)–2线UART,支持调试通讯通道中断;可通过程序来禁止通过ICE进行访问•周期性间隔定时器(PIT)–20位可编程的计数器,加上12位的间隔计数器•时间窗看门狗(WDT)–12位受预设值(key)保护的可编程计数器–为系统提供复位或中断信号–当处理器处于调试状态或空闲模式时可以停止计数器•实时定时器(RTT)–32位自由运行的具有报警功能的计数器–时钟来源于片内RC振荡器•一个并行输入/输出控制器(PIOA)–32个可编程的复用I/O,每个I/O最多可以支持两个外设功能–输入电平改变时,每个I/O都可以产生中断–可以独立编程为开漏输出、使能上拉电阻以及同步输出•11个外设数据控制器(PDC)通道•一个USB 2.0全速(12 Mbps)设备端口–片上收发器,328字节可编程的FIFO•一个同步串行控制器(SSC)–每个接收器和发送器都具有独立的时钟和帧同步信号–支持I²S,支持时分多址–支持32位数据传输的高速连续数据流功能•两个通用的同步/异步收发器(USART)–独立的波特率发生器,IrDA红外调制/解调–支持ISO7816 T0/T1智能卡,硬件握手信号,支持RS485–USART1支持全功能的调制解调器信号•主/从串行外设接口(SPI)–8到16位可编程的数据长度,4个片选线•一个3通道的16位定时器/计数器(TC)–3个外部时钟输入端,每个通道有两个多功能I/O引脚–倍速PWM发生功能,捕捉/波形模式,递增/递减计数2AT91SAM7S64 Preliminary6070A–ATARM–07-Jun-05•一个4通道的16位PWM 控制器(PWMC)•一个两线接口(TWI)–只支持主机模式,支持所有的Atmel 两线EEPROM•一个8通道的10位模数转换器,其中4个通道与数字I/O 复用•IEEE 1149.1 JTAG 边界扫描支持所有的数字引脚•5V 兼容的I/O ,包括4个高达16 mA 的大电流驱动I/O •电源–片上1.8V 电压调节器,可以为内核及外部元件提供高达100 mA 的电流–为I/O 口线提供电源的3.3V VDDIO ,以及独立的为Flash 供电的3.3V VDDFLASH –内核电源为1.8V VDDCORE ,并具有掉电检测(BoD )功能•全静态操作:极限条件下(1.65V ,85°C )高达55 MHz •封装为64脚的LQFP描述AT91SAM7S64是Atmel 32位ARM RISC 处理器小引脚数Flash 微处理器家族的一员。

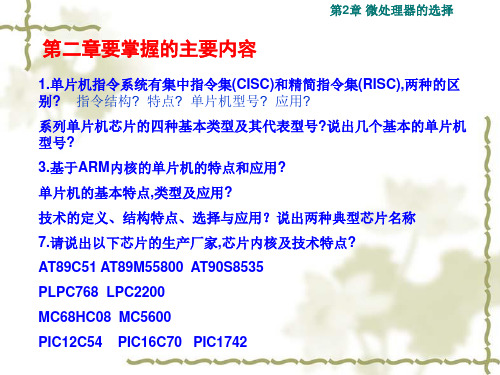

智能仪器第2章微处理器的选择

主要生产厂家? 代表性芯片?

第2章 微处理器的选择

AT89系列的主 要特点

第2章 微处理器的选择

1. 基本型单片机(Atmel公司的AT89系列)

3.精简增强型单片机(Philips公司的P87LPC900系列)

特点是无三总线构架,内部增加了许多功能部件,如 LCD段驱动器、模拟比较器、12C通信端口和看门狗定时 器等,其内部 Flash同时可作E2PROM使用,且内含RTC 日历时钟功能等。

P89LPC900系列基于6倍速的80C51兼容内核,内嵌 Flash程序存储器,可实现在应用编程(ClAP)/在系统编程 (ISP)和快速的2 ms页编程/擦除周期;包括512字节片内 E2PROM和768字节SRAM数据存储器;包括了16位捕获/ 比较/PWM、3 Mb/s的SPI和400 Kb/s的FC总线、增强型 DART、看门狗定时器和用户可选择的电源管理功能;带 有精度为±2.5%的内部振荡器。

第2章 微处理器的选择

3.高档型单片机(Silicon Lab公司的C8051F000系列)

Silicon Lab公司的C8051F系列单片机具有与 MCS 51单片机内核指令集完全兼容的微控制器。

C8051F系列单片机采用具有专利的CIP-51内 核,而Silicon Lab专利与MCS-5l单片机指令系统完 全兼容,运行速度高达25MIPS,除具有标准8051 的数字外设部件之外,片内还集成数据采集和控制 系统中常用的模拟部件和其他数字外设及功能部件。

MIPS (计算机) - 即Million Instructions Per Second(每秒百万条指令)

单片机常用芯片资料

单片机常用芯片资料单片机作为一种常见的嵌入式系统的核心组成部分,广泛应用于各个领域。

而在单片机的设计与开发过程中,选择合适的芯片是至关重要的。

本文将介绍一些常用的单片机芯片资料,以供读者参考。

I. 8051系列芯片8051系列是一种经典的单片机芯片,广泛应用于各种嵌入式系统中。

以下是一些常见的8051系列芯片资料供读者参考:1. AT89S51AT89S51是一种低功耗、高性能的8位CMOS单片机,由Atmel公司生产。

它具有4KB的Flash程序存储器、128字节的RAM和32个I/O引脚,适用于各种应用场景。

2. AT89C52AT89C52也是一种经典的8051系列芯片,同样由Atmel公司生产。

它具有8KB的Flash程序存储器、256字节的RAM和32个I/O引脚,可广泛应用于嵌入式系统中。

II. AVR系列芯片AVR系列芯片是由Atmel公司开发的一种低功耗、高性能的8位RISC微控制器。

以下是一些常见的AVR系列芯片资料供读者参考:1. ATmega328PATmega328P是一种广泛应用于Arduino开发板的AVR系列芯片,具有32KB的Flash程序存储器、2KB的SRAM和23个I/O引脚。

它支持多种通信接口(如SPI、I2C等),适用于各种创意项目。

2. ATtiny85ATtiny85是一种小型的AVR系列芯片,具有8KB的Flash程序存储器、512字节的RAM和6个I/O引脚。

它体积小巧,适合于空间受限的应用场景,如可穿戴设备等。

III. PIC系列芯片PIC系列芯片是由Microchip公司开发的一种低功耗、高性能的8位微控制器。

以下是一些常见的PIC系列芯片资料供读者参考:1. PIC16F877APIC16F877A是一种常用的PIC系列芯片,具有14KB的Flash程序存储器、368字节的RAM和33个I/O引脚。

它适用于各种嵌入式应用,如家用电器、工业控制系统等。

AT91SAM9X25中文介绍

AT91SAM9X25中文介绍概述SAM9X25是一个高性能的基于ARM926嵌入式微处理器单元,运行在400 MHz,并设有多个网络/连接外围设备,优化的工业应用,如楼宇自动化,网关和医疗。

两个2.0A / B兼容控制器区域网络(CAN)接口,2个IEEE标准802.3兼容10/100Mbps的以太网MAC SAM9X25功能。

通信接口包括一个专门的科胜讯的SmartDAA线路驱动器,的HS USB设备和主机,FS USB主机,两个HS SD卡/ SDIO / MMC接口,个USART,SPI接口,I2S,TWIS位和10位ADC的软调制解调器支持。

以最小的处理器开销,以确保不间断的数据传输中,SAM9X25加上2 x 8个中央DMA通道和专用的DMA的高速连接外围设备提供了一个10层总线矩阵。

外部总线接口采用8银行DDR2/LPDDR,SDRAM / LPSDRAM,静态存储器,和具体的电路集成了ECC MLC/ SLC NAND闪存的控制器。

SAM9X25是的217球BGA封装,球间距为0.8mm。

性能•内核- ARM926EJ-S™ARM®Thumb®的处理器,运行速度高达400 MHz@1.0V + / - 10%- 16 KB的数据Cache,16 KB的指令高速缓存,存储器管理单元•存储器- 一个64字节的内部ROM嵌入引导程序:NAND Flash的启动,SD卡的DataFlash®或串行数据闪存。

可编程顺序。

- 一个32字节的内部SRAM,单周期存取系统的运行速度- 高带宽,多端口的DDR2控制器- 32位外部总线接口支持8银行DDR2/LPDDR,SDR / LPSDR的,静态的存储器- MLC / SLC NAND控制器,24位可编程的多比特错误纠正代码(PMECC)•系统运行速度高达133 MHz- 上电复位单元,复位控制器,关闭控制器,周期间隔定时器,看门狗定时器和实时时钟- 引导模式选择选项,映射命令- 内部低功耗32 kHz的RC和快速工作频率为12MHz RC振荡器- 可选择的32768 Hz的低功耗振荡器和12 MHz振荡器- 优化的PLL为系统和一个PLL频率为480 MHz的USB高速- 12个32位AHB总线矩阵,大带宽传输层- 双外设桥专用的可编程时钟以获得最佳性能- 两个双端口8通道DMA控制器- 高级中断控制器和调试单元- 两个可编程的外部时钟信号•低功耗模式- 关闭控制器,4个32-bit电池备份寄存器- 时钟发生器和电源管理控制器- 非常慢的时钟工作模式,软件可编程功率优化功能•外设- LCD控制器与叠加,alpha混合,旋转,缩放和颜色转换- USB设备高速,高速USB主机和USB主机全速专用片上收发器- 1个10/100 Mbps以太网MAC控制器- 两个高速存储卡主机- 两个CAN控制器- 两个主/从串行外设接口- 两个三通道32位定时器/计数器- 一个同步串行控制器- 一个4通道16位PWM控制器- 三双线接口- 三个USART,两个UART- 一个12通道的10位触摸屏模拟到数字转换器- 软调制解调器•I / O- 4个32位并行输入/输出控制器- 105可编程I / O线复用三个外设的I / O- 输入电平变化中断能力对每个I / O线,可选的施密特触发器输入- 独立的可编程开漏,上拉和下拉电阻,同步输出•封装- 217球BGA封装,间距0.8毫米开发板深圳市米尔科技有限公司是ATMEL的官方合作伙伴,也是ARM公司中国区的开发工具合作代理商,自主研发基于AT91SAM9X25芯片的MYD-SAM9X25开发板、MYS-SAM9X25单板机和MYC-SAM9X25核心板包含丰富的软硬件资源,其中软件资源包有KEIL MDK-ARM例程,Linux系统和Android系统,硬件资源包含几乎所有的芯片接口,是工业控制和嵌入式学习的良好选择。

AT91SAM7S256翻译

AT91SAM7S256中文资料(有些图没放进去,可参考英文版资料) 功能特点•内部集成ARM7TDMI ARM Thumb 处理器–高性能32位RISC 架构–高密度16位指令集– MIPS/Watt (每秒百万条指令/瓦) 指标处于领先水平–支持嵌入式ICE 内电路仿真以及调试通讯接口• 片内高速Flash有256K 字节(AT91SAM7X256) ,共1024 页,每页256 字节–最差情况下仍保持30 MHz 的单时钟周期存取速度–预读取缓冲器使Thumb 指令最优化运行以达到最高速度–每页编程时间为6 ms,包括页自动擦除, 全片擦除时间为15 ms– 10,000 次擦写次数, 10 年数据保存能力, 扇区锁定能力,设置Flash 安全位–对量大的数据内容提供快速Flash 编程接口• 片内高速SRAM为64K 字节, 最高速度下单时钟周期存取• 内存控制器(MC)–嵌入式Flash 控制器, 中止状态和未对齐检测• 复位控制器(RSTC)–基于上电复位单元和经过工厂标定的低功耗掉电检测–提供外部信号整形和复位源状态• 时钟发生器(CKGR)–低功耗RC 振荡器, 3 到20 MHz 片上振荡器和一个PLL• 电源管理控制器(PMC)–具有电源优化功能,包括慢速时钟模式(低于500 Hz) 和空闲模式–三个可编程外部时钟信号• 先进中断控制器(AIC)–可分别单独屏蔽的、具有八个优先级的向量中断源–两个外部中断源(AT91SAM7S256/128/64/321)和一个快速中断源(AT91SAM7S32), 带有伪中断保护• 调试单元(DBGU)–两线UART ,支持调试通讯接口中断,可编程禁止ICE 访问• 周期性间隔定时器(PIT)– 20 位可编程计数器以及12 位间隔计数器• 时间窗看门狗定时器(WDT)– 12 位受预设值保护的可编程计数器–向系统提供复位或中断信号–当处理器处于调试模式或空闲状态时可以停止计数器• 实时定时器(RTT)–具有警告功能的32 位自由运行计时器–以内部RC 振荡器为时钟源• 一个并行输入/输出控制器(PIOA)– 32个可编程的复用I/O,每个I/O 最多可以支持两个外设功能–每个I/O 口的电平变化都可以产生中断–可以独自编程为开漏、上拉电阻和同步输出• 11个外围数据DMA 控制器(PDC) 通道• 一个USB 2.0 全速(每秒12 Mbits ) 设备接口(除了AT91SAM7S32)–具有片上收发器, 大小为1352 字节的可配置集成FIFO• 一个同步串行控制器(SSC)–每个接受器和发送器都有独立的时钟和帧同步信号–支持I²S 模拟接口, 支持分时复用–支持32 位数据传输的高速连续数据流功能• 两个通用同步/异步收发器(USART)–独立的波特率发生器, 可以IrDA 红外调制/解调–支持ISO7816 T0/T1 智能卡, 硬件握手信号以及RS485–曼彻斯特编码器/解码器– USART1 口支持全Modem 线• 一个主/从串行外设接口(SPI)– 8 位到16 位可编程数据长度, 四个外围设备片选线• 一个3 通道16 位定时器/计数器(TC)–三个外部时钟输入, 每个通道有两个通用I/O 引脚–双路PWM 发生器, 捕捉/波形模式,递增/递减计数功能• 一个4 通道的16 位PWM 控制器(PWMC)• 一个两线接口(TWI)–只支持主模式,支持所有的两线Atmel EEPROM• 一个8 通道10 位模数转化器,其中四个通道与数字I/O 接口复用• SAM-BA™ Boot 助手–默认Boot 编程方式–与SAM-BA 图形用户界面的接口• IEEE 1149.1 JTAG 边界扫描支持所有数字引脚• 容许5V 输入/输出,包括四个高电流驱动I/O 线,每个高达16 mA• 电源提供–片上1.8V 稳压器,可以为内核及外部组件提供高达100 mA 的电流– 3.3V VDDIO 提供I/O 线电源,独立的3.3V VDDFLASH 提供Flash 电源–具有掉电检测的1.8V VDDCORE 提供内核电源• 全静态操作:在1.65V 和85°C 的极限条件下仍能保持55 MHz•采用64引脚LQFP绿色包装1. 概述Atmel的AT91SAM7S是一系列基于32位ARM RISC处理器的低引脚数Flash微控制器。

AT91SAM9261片上系统介绍

AT91SAM9261片上系统介绍一.AT91SAM9261 SOC简介A T91SAM9261是atmel公司生产的以ARM926EJ-S ARM Thumb处理器为核心的完全片上系统(SOC),它扩展了DSP指令集和Jazelle Java加速器。

主时钟频率190MHz时性能高达210MIPS。

A T91SAM926是一个为带LCD显示应用而优化了的主机处理器。

它的集成LCD控制器支持BW而且达到16M色彩,主动和被动LCD显示。

16K字节的片上SRAM可配置为帧缓冲,能将LCD刷新对整体处理器性能上的影响降低到最小。

外部总线接口包括支持同步DRAM(SDRAM)和支持静态存储器的控制器,并有特殊接口电路以支持CompactFLASH 和NandFLASH。

A T91SAM9261集成了一个支持映射的基于ROM的Bootloader,例如从外部DataFlash 映射到外部SDRAM。

由软件控制的功率管理控制器(PMC)通过有选择的启用和关闭处理器、各种外设以及对工作频率的调节使得系统功率损耗保持最低。

A T91SAM9261还集成了宽范围的调试特性。

包括JTAG-ICE,一个专用的UART调试通道(DBUG)和嵌入式实时追踪。

这使所有应用和开发,特别是严格要求实时性的应用得以实现。

下面是A T91SAM9261的功能框图:二.处理器ARM926EJ-S介绍ARM926EJ-S是通用微处理器ARM9家族中的一员,属于V5TEJ版ARM架构,针对的是多任务应用,全存储器管理、高性能、小核心尺寸和低功耗都是它的特点。

ARM926EJ-S处理器支持32位ARM和16位THUMB指令集,使得用户能在高性能和高代码密度上取得平衡。

它支持8为JA V A指令集并且包括Java字节代码有效执行的功能部件,提供和JIT(Just In Time编译器)形似的Java性能,这些性能为下一代Java无线应用和嵌入式的设备提供了有效支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Fl 存 储 器 还 增 加 了 开 发 者 使 用 的 灵 活 性 。 除 此 ah S 以 外 , 大 量 的 内 部 分 组 寄 存 器 加 速 了 对 异 常 的 处 理 过 程 , 从 而 使 其 更 适 合 于 实 时 控 制 的 应 用 。 8级 基

AR / h mb微 控 制 器 和 1个 AT 9 V 1 0 A/6 4 M Tu 4 B 6 4 1 A l 1 M bt ls 6 i Fa h存 储 器 集 成 的 1 1b l B 2 . al GA 封 装 器 件 。 除 了 Fl s a h存 储 器 使 能 信 号 以 外 的 所 有 地 址 、 数 据 和 控制信 号都是内部 互连的 。 AT 1 4 0 8体 系 结 构 包 括 2条 主 要 总 线 :先 进 9 R 00 的 系 统 总 线 AS 和 先 进 的 外 围 总 线 AP 。AS 被 设 B B B

维普资讯

j

≯ ≤

≮

≯

0誓 叁

新 器 件 新 技 术

大 容量 F s 1 A g 系列 A H核微 控制器 a h型 T X R

■ 北 京 理 工 大 学 徐 英 慧

■ A m l公 司 北 京 办 事 处 te

马 忠丰 每

个 内部 存储 器是 单 周期 访 问 的 , 它 直接 与 3 2位 数 据

总 线 相 连 。这 样 通 过 使 用 微 控 制 器 的 ARM 指 令 集

在 6 6 MHz 可 以 提 供 6 I S的 最 高 性 能 , 同时 下 0M P 降 低 了 系 统 功 耗 。AT9 F 4 6 以拥 有 1 外 部 总 1 R 01 2 个 线接 口 E BI 特 性 , 它 用 于 连 接 外 部 存 储 器 和 专 用 为 外 围 设 备 。 EB1 持 8或 l 支 6位 器 件 并 且 可 以 使 用 2

于 向量 的 优 先级 中断 控制 器 和 外 围数 据 控 制 器 PDC 大 大增 强 了实 时 器 件 的 性 能 。 此 器 件适 用 于 开 发工 业 自动化 系统 、MP 3、销 售 终端 、GP S接收 机 以及

无 线 网 络 产 品 等 对 功 耗 敏 感 且 要 求 具 有 实 时 性 的 产 品 。A 9 F 4 1 2微 控 制 器 的 特 点 是 在 一 个 1 1b l T 1R 06 2 .al

36V 的 I 工 作 范 围 和 1 5 19 的 内 核 工 作 范 围 、 . / O . ~ .5V 6

一

列微 控 制器 中 的一 员 , 具有 ARM 7 DMI 、大容 T 核

量 F a h存 储 器 以 及 片 内 S ls RAM 和 外 围 。 这 种 微 控 制器 的 特 点是 高性 能 一 密度 一 3 2位 RI C 体 系 结 构 、 高 S 1 6位 指 令 集 、低 功 耗 以 及 实 时 性 , 扩 充 的

AT F 0l 2将 ARM 7 DMI 理 器 的 I 91 R4 6 T 处 CE端 口

BG A封 装 中集 成了 2 6 KB的 片内 S AM 和 1 i 5 R 6 Mbt

的 Fl s a h存 储 器 。 它 为 许 多 计 算 密 集 的 嵌 入 式 控 制 应 用 领 域 提 供 了 功 能 强 大 、 使 用 灵 活 且 性 价 比 高 的 解 决 方 案 , 同 时 还 可 以帮 助 用 户 减 小 P CB 尺 寸 和 系 统 成 本 。F a h存 储 器 可 以通 过 J AG/CE接 口或 者 ls T I 厂 家 编 写 的 F a h Up o d r 件 进 行 编 程 , 从 而 使 ls l a e 软 AT 1 R 0 6 9 F 4 1 2适 合 于在 系 统 可 编 程 应 用 。

接 到 一 些 专 用 的 引 脚 上 , 从 而 为 目标 调 试 提供 了完 整 、低 价 且 易 用 的 调 试 解 决 方 案 。

2 1 存 储 器 .

AT9 F 0 6 1 R4 1 2嵌 入 了 2 6 KB 的 内部 S 5 RAM 。这

Hale Waihona Puke 1 功 能 框 图 及 产 品 特 点

计 为最 佳性能 , 由存储 控制 器控 制 。ARM7 DMI T 通

过 AS 与 片 内 3 B 2位 存 储 器 、 外 部 总 线 接 口 E 和 BI AM B 桥 进 行 接 口 。 A B 桥 驱 动 AP A M A B, AP 被 设 B 计 用于访 问片内外 围并且进行 了低功耗优化 。

叶 勇建

关键 词

A 9 F 4 1 2 A 9 R 0 0 S A F s 微 控 制 器 T 1 R 0 6 T 1 4 0 8 RM l h a

引 言

AT 1 R 0 6 9 F 4 12是 美 国 At l 司生 产 的 AT 1 me 公 9 系

定 时 器 、先进 的 省 电特 性 、完 全静 态 的操 作 、2 7 .~

4~ 5 0 8 ℃的 运 行 温 度 范 围 以及 1 1 a 0r T× 1 l 2 . l1 l b l n l 0r T nl × 12mm G 封 装 ( 的 直 径 为 08mm ) . B A 球 . 。

2 体 系 结 构

AT91 R4 6 F 01 2是 由 At l 司 的 AT91 0 0 me 公 R4 0 8

AT 1 R 0 6 9 F 4 1 2的 功 能 框 图 如 图 1 示 。 所 AT 1 R 0 6 9 F 4 1 2的 主 要 特 点 是 : M 7 DMI 理 AR T 处 器 核 、2 6K 的 片 内 S AM 和 12 字 的 1 位 Fah 5 B R 0 4K 6 l s 存 储 器 、 完 全 可 编 程 的 外 部 总 线 接 口 E 、 具 有 8个 BI