基于ALTERA的FPGA_CPLD下载电路设计

基于ALTERACPLD的单稳态脉冲展宽电路(1)

文章编号:1009-671X (2001)12-0007-03基于AL TERA CPLD 的单稳态脉冲展宽电路汲清波,冯 驰(哈尔滨工程大学电子工程系,黑龙江哈尔滨150001)摘 要:主要介绍了CPLD 设计单稳态窄脉冲展宽电路的详细过程和这种单稳态窄脉冲展宽电路的特点,给出了相应的时序仿真波形和计数器的VHDL 语言设计。

①关 键 词:CPLD 器件;单稳态脉冲信号;VHDL 中图分类号:TN431.2 文献标识码:ADesign of Monostable Pulse Width Circuit with CPLDJ I Qing-bo ,FEN G Chi(Dept.of Electrical Eng.,Harbin Engineering University ,Harbin 150001,China )Abstract :The paper introduced a process of designing monostable pulse width cicuit with CPLD and the characteristic of the circuit.Emulation oscillogram and counter design with V HDL were given.K ey w ords :CPLD device ;monostable pulse signal ;V HDL0 引 言在数字电路设计中,经常遇到由窄脉冲触发而输出一定宽度脉冲信号这样的问题。

此时,往往采用单稳态集成电路定宽的方法来实现。

但是单稳态触发器需要外接电阻、电容才可实现其功能,显然不利于集成,并且,单稳态集成电路中的宽度定时元件电阻、电容是受温度、湿度等因素影响,不适合在精度要求较高的场合应用。

所以,当输出的宽脉冲信号的精度和温度的稳定性要求较高时,就不适合用单稳态集成电路定宽方式,可采用脉冲计数的方法,此方法的定宽精度只与脉冲频率f 有关,最大误差<1/f ,可根据精度要求选择计数脉冲的频率。

基于FPGA╲╲CPLD最小系统PCB的制作

基于FPGA\CPLD最小系统PCB的制作电子信息科学与技术专业:何胜军指导教师:郭杰荣摘要:基于FPGA\CPLD最小系统PCB的制作是通过PROTEL软件来实现的。

本文讲述的是利用在1999年,PROTEL公司推出的新一代电子线路设计系统——PROTEL99软件来绘制完整的最小系统电路原理图,并进行电气规则检测、生成网络报表以及对PCB进行布局、布线、工艺流程,制作出最小系统EDA的双面PCB。

EDA最小系统具有系统控制、功能实现以及结果显示的功能。

本文是以ALTERA公司MAX7128S系列的EPM7128SLC84-15CPLD芯片为中心,利用外围的AT89C51单片机、按键开关、ROM、数码显示管来完成一个完整的EDA最小系统。

关键词:FPGA\CPLD,PROTEL99,双面PCB,最小系统Designing of the Minimum System PCB Basedon FPGA \CPLDElectronic and Information Science and TechnologyCandidate:He Sheng-JunAdvisor:Guo Jie-rongAbstract: A minimum system PCB which is based on FPGA\CPLD can be realized by using PROTELL99. This article tells us how to draw a complete circuit of a minimum system through using a new generation circuit design system-PROTEL99 which is released by PROTEL company in 1999, and makes out the double-side PCB by running the electrical check, generating netlist and placing, routing PCB and designing the technology process. EDA minimum system has functions including system control function realizing and result showing. This article is centered around on ALTERA company’s chip EPN7128S2C84-15CPLD of the series of MAX7128S, and completes EDA minimum system with the use of AT89C51 single-chip microcomputer, keyboard switch and digit display.Keywords:FPGA\CPLD, PROTEL99, Double-side PCB, Minimum system引言在电子竞赛设计中,可编程逻辑器件作为系统的控制核心已广泛应用。

ALTERA CPLD器件的配置与下载

ALTERA CPLD器件的配置与下载一、配置方式ALTERA CPLD器件的配置方式主要分为两大类:主动配置方式和被动方式。

主动配置方式由CPLD器件引导配置操作过程,它控制着外部存储器和初始化过程;而被动配置方式由外部计算机或控制器控制配置过程。

根据数据线的多少又可以将CPLD器件配置方式分为并行配置和串行配置两类。

经过不同组合就得到四种配置方式:主动串行配置(AS)、被动串行(PS)、被动并行同步(PPS)、被动并行异步(PPA)。

我们没有必要对每一种配置方式都进行讲述,而是详细地来讲讲我们实验室中经常使用的方式:被动串行配置方式(PS)。

以FLEX10K器件为例,我们首先对PS方式中使用到的引脚有个了解,它的主要配置引脚如下:MSEL1、MSEL0:输入;接地。

nSTATUS:双向漏极开路;命令状态下器件的状态输出。

加电后,FLEX10K立即驱动该引脚到低电位,然后在100ms内释放掉它,nSTATUS必须经过1.0k电阻上拉到Vcc,如果配置中发生错误,FLEX10K将其拉低。

nCONFIG:输入;配置控制输入。

低电位使FLEX10K器件复位,在由低到高的跳变过程中启动配置。

CONF_DONE:双向漏极开路;状态输出。

在配置期间,FLEX10K将其驱动为低。

所有配置数据无误差接收后,FLEX10K将其置为三态,由于有上拉电阻,所以将变为高电平,表示配置成功。

状态输入。

输入高电位引导器件执行初始化过程并进入用户状态。

CONF_DONE 必须经过1.0k电阻上拉到Vcc,而且可以将外电路驱动为低以延时FLEX10K初始化过程。

DCLK:输入;为外部数据源提供时钟。

nCE:输入;FLEX10K器件使能输入,nCE为低时使能配置过程,而且为单片配置时,nCE必须始终为低。

nCEO:输出(专用于多片器件);FLEX10K配置完成后,输出为低。

在多片级联配置时,驱动下一片的nCE端。

DATA0:输入;数据输入,在DATA0引脚上的一位配置数据。

Altera FPGACPLD设计(高级篇)(第2版)目录

《Altera FPGA/CPLD设计(高级篇)(第2版)》:Altera公司推荐FPGA/CPLD 培训教材。

目录第1章可编程逻辑设计指导原则1.1 可编程逻辑基本设计原则1.1.1 面积和速度的平衡与互换原则1.1.2 硬件原则1.1.3 系统原则1.1.4 同步设计原则1.2 可编程逻辑常用设计思想与技巧1.2.1 乒乓操作1.2.2 串并转换1.2.3 流水线操作1.2.4 异步时钟域数据同步1.3 altera推荐的coding style1.3.1 coding style的含义1.3.2 结构层次化编码(hierarchical coding)1.3.3 模块划分的技巧(design partitioning)1.3.4 组合逻辑的注意事项1.3.5 时钟设计的注意事项1.3.6 全局异步复位资源1.3.7 判断比较语句case和if...else的优先级1.3.8 使用pipelining技术优化时序1.3.9 模块复用与resource sharing1.3.10 逻辑复制1.3.11 香农扩展运算1.3.12 信号敏感表1.3.13 状态机设计的一般原则1.3.14 altera megafunction资源的使用1.3.15 三态信号的设计1.3.16 加法树的设计1.4 小结1.5 问题与思考第2章altera器件高级特性与应用2.1 时钟管理2.1.1 时序问题2.1.2 锁相环应用2.2 片内存储器2.2.1 ram的普通用法2.2.2 ram用做移位寄存器2.2.3 ram实现固定系数乘法2.3 数字信号处理2.3.1 dsp块资源2.3.2 工具支持2.3.3 典型应用2.4 片外高速存储器2.4.1 存储器简介2.4.2 zbt sram接口设计2.4.3 ddr sdram接口设计2.4.4 qdr sram接口设计2.4.5 ddr3、qdr ii+和rldram ii+2.4.6 软件支持和应用实例2.5 高速差分接口和dpa2.5.1 高速差分接口的需求2.5.2 器件的专用资源2.5.3 动态相位调整电路(dpa)2.5.4 软件支持和应用实例2.6 高速串行收发器2.7 小结2.8 问题与思考第3章logiclock设计方法3.1 logiclock设计方法简介3.1.1 logiclock设计方法的目标3.1.2 logiclock设计流程3.1.3 logiclock设计方法支持的器件族3.2 logiclock区域3.2.1 region的类型与常用属性值3.2.2 region的创建方法3.2.3 region的层次结构3.2.4 指定region的逻辑内容3.3 logiclock的约束注意事项3.3.1 约束优先级3.3.2 规划logiclock区域3.3.3 向logiclock区域中布置器件特性3.3.4 虚拟引脚(virtual pins)3.4 反标注布线信息3.4.1 导出反标注布线信息3.4.2 导入反标注布线信息3.5 logiclock设计方法支持的tcl scripts 3.6 quartus ii基于模块化的设计流程3.7 小结3.8 问题与思考第4章时序约束与时序分析4.1 时序约束与时序分析基础4.1.1 周期与最高频率4.1.2 利用quartus ii工具分析设计4.1.3 时钟建立时间4.1.4 时钟保持时间4.1.5 时钟输出延时4.1.6 引脚到引脚的延迟4.1.7 slack4.1.8 时钟偏斜4.1.9 quartus ii时序分析工具和优化向导4.2 设置时序约束的常用方法4.2.1 指定全局时序约束4.2.2 指定个别时钟约束4.3 高级时序分析4.3.1 时钟偏斜4.3.2 多时钟域4.3.3 多周期约束4.3.4 伪路径4.3.5 修正保持时间违例4.3.6 异步时钟域时序分析4.4 最小化时序分析4.5 使用tcl工具进行高级时序分析4.6 timequest简介4.7 小结4.8 问题与思考第5章设计优化5.1 解读设计5.1.1 内部时钟域5.1.2 多周期路径和伪路径5.1.3 i/o接口的时序要求5.1.4 平衡资源的使用5.2 设计优化的基本流程和首次编译5.2.1 设计优化基本流程5.2.2 首次编译的约束和设置5.2.3 查看编译报告5.3 资源利用优化5.3.1 设计代码优化5.3.2 资源重新分配5.3.3 解决互连资源紧张的问题5.3.4 逻辑综合面积优化5.3.5 网表面积优化5.3.6 寄存器打包5.3.7 quartus ii中的资源优化顾问5.4 i/o时序优化5.4.1 执行时序驱动的编译5.4.2 使用ioe中的触发器5.4.3 可编程输入/输出延时5.4.4 使用锁相环对时钟移相5.4.5 其他i/o时序优化方法5.5 最高时钟频率优化5.5.1 设计代码优化5.5.2 逻辑综合速度优化5.5.3 布局布线器设置5.5.4 网表优化和物理综合5.5.5 使用logiclock对局部进行优化5.5.6 位置约束、手动布局和反标注5.5.7 quartus ii中的时序优化顾问5.6 使用dse工具优化设计5.6.1 为什么需要dse5.6.2 什么是dse,如何使用5.7 如何减少编译时间5.8 设计优化实例5.9 小结5.10 问题与思考第6章altera其他高级工具6.1 命令行与tcl脚本6.1.1 命令行脚本6.1.2 tcl脚本6.1.3 使用命令行和tcl脚本6.2 hardcopy流程6.2.1 结构化asic6.2.2 hardcopy器件6.2.3 hardcopy设计流程6.3 基于nios ii处理器的嵌入式系统设计6.3.1 nios ii处理器系统6.3.2 avalon交换结构6.3.3 使用sopc builder构建系统硬件6.3.4 nios ii ide集成开发环境6.3.5 nios ii系统典型应用6.4 dsp builder工具6.4.1 dsp builder设计流程6.4.2 与sopc builder一起构建系统6.5 小结6.6 问题与思考第7章fpga系统级设计技术7.1 信号完整性及常用i/o电平标准7.1.1 信号完整性7.1.2 单端标准7.1.3 差分标准7.1.4 伪差分标准7.1.5 片上终端电阻7.2 电源完整性设计7.2.1 电源完整性7.2.2 同步翻转噪声7.2.3 非理想回路7.2.4 低阻抗电源分配系统7.3 功耗分析和热设计7.3.1 功耗的挑战7.3.2 fpga的功耗7.3.3 热设计7.4 serdes与高速系统设计7.4.1 serdes的基本概念7.4.2 altera stratix ivgx中serdes的基本结构7.4.3 典型高速系统应用框图举例7.4.4 高速pcb设计注意事项7.5 小结7.6 问题与思考。

列举altera公司的cpld和fpga产品。

Altera公司是一家知名的半导体公司,致力于生产和销售可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)等产品。

下面将列举Altera公司旗下的CPLD和FPGA产品,帮助大家更好地了解这家公司的产品线。

一、CPLD产品线1. MAX 7000系列MAX 7000系列是Altera公司推出的一款CPLD产品,具有低功耗、高性能和可编程性强的特点。

该系列产品广泛应用于通信、工业控制、汽车电子等领域,为客户提供了稳定可靠的解决方案。

2. MAX 9000系列MAX 9000系列是Altera公司的另一款CPLD产品,采用了先进的CMOS工艺和可编程逻辑单元,具有高密度、可靠性高的特点。

该系列产品在航空航天、国防安全、医疗设备等领域有着广泛的应用。

二、FPGA产品线1. Stratix系列Stratix系列是Altera公司旗下最为知名的FPGA产品之一,拥有高速、高密度、低功耗等特点,适用于需要大规模数据处理和高性能计算的应用场景。

该系列产品常用于人工智能、云计算、数据中心等领域。

2. Cyclone系列Cyclone系列是Altera公司针对中小规模应用市场推出的FPGA产品,具有低成本、低功耗、高性能等特点。

该系列产品在嵌入式系统、工业自动化、网络通信等领域有着广泛的应用。

3. Arria系列Arria系列是Altera公司旗下的高性能FPGA产品,具有高速、低功耗、灵活性强等特点,适用于需要高性能和灵活性的应用场景。

该系列产品在无线通信、高性能计算、高清视频等领域有着广泛的应用。

通过以上列举,我们可以看到Altera公司在CPLD和FPGA领域拥有丰富的产品线,为不同领域的客户提供了多样化的解决方案。

期待Altera在未来能够持续推出更多高性能、低功耗的PLD和FPGA产品,满足客户不断增长的需求。

Altera公司作为半导体行业的领军企业,一直以来致力于为全球各行业提供高性能、低功耗的可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)产品。

ALTERA CPLD实验系统用户手册

CPLD 实验系统用户手册单片机爱好者网站荣誉出品Altera CPLD 实验系统是针对CPLD初、中级学习者设计,帮助用户降低学习成本和加快用户快速进入可编程逻辑器件设计开发领域,提供一个帮助用户快速开始可编程逻辑器件学习之旅的硬件平台。

可以作为数字电路的试验平台,做几乎所有的数字电路试验,不需一根导线和数字电路IC.第一章系统安装Altera CPLD 实验系统由CPLD 实验主板、Altera CPLD子板、Altera CPLD下载线、直流电源等组成首先进行软件的安装:实验系统的软件平台是Altera Quartus II 专用设计软件,完成程序的编辑、编译,以及软件模拟运行。

Altera 的EPM7128由于只可以重复烧写100次,不适合实验,实验板采用一颗atmel ATF1508-PLCC84,ATF15XX 系列CPLD芯片提供了替代ALTERA公司 EPM7000 和 EPM3000系列芯片的引脚完全一致,结构完全包容的器件。

ATF15XX系列芯片可实现ALTERA 公司芯片的完全替换!!!!不存在任何性能和设计上的不同;可重复编程10000次,可放心做实验。

安装atmel ISP编程软件,运行配套光盘中的安装程序,按程序的提示,一步步安装即可。

安装atmel 的pof2ed 编程软件,将Quartus II生成的POF文件转换成atmel ISP编程软件使用的jed文件,用于烧写ATF1508芯片下一步进行硬件安装:1、将5V直流电源的输出插头插入实验板的电源插座—J7;2、将Altera CPLD下载线的并口电缆插入计算机的并行口,将Altera CPLD下载线的10芯电缆插座插入的实验板的CPLD JTAG下载插座---J8;3、将5V直流电源插入交流220V插座,实验板的电源指示LED会亮,说明实验板已进入工作状态,硬件安装完成。

至此实验系统安装完毕,可以实验。

第二 章 实验板的具体功能介绍电源本板需外接5V电源(插头内正外负),用本机随带的5V /1A专用开关电源为电路板供电。

EDA选择题

1.在EDA工具中,能完成在目标系统器件上布局布线软件称为(C )A.仿真器B.综合器C.适配器D.下载器2.在执行MAX+PLUSⅡ的(D)命令,可以精确分析设计电路输入与输出波形间的延时量。

A .Create default symbol B. SimulatorAnalyzer3.VHDL常用的库是(A)A. IEEEC. WORKD. PACKAGE4.下面既是并行语句又是串行语句的是(C)A.变量赋值B.信号赋值语句…ELSE语句5.在VHDL中,用语句(D)表示clock的下降沿。

A. clock’EVENT’EVENT AND clock=’1’C. clock=’0’D. clock’EVENT AND clock=’0’1. IP核在EDA技术和开发中具有十分重要的地位;提供用VHDL等硬件描述语言描述的功能块,但不涉及实现该功能块的具体电路的IP核为__A__。

A .软IP B.固IP C.硬IP D.都不是2.综合是EDA设计流程的关键步骤,在下面对综合的描述中,__D__是错误的。

A.综合就是把抽象设计层次中的一种表示转化成另一种表示的过程;B.综合就是将电路的高级语言转化成低级的,可与FPGA / CPLD的基本结构相映射的网表文件;C.为实现系统的速度、面积、性能的要求,需要对综合加以约束,称为综合约束;D.综合可理解为,将软件描述与给定的硬件结构用电路网表文件表示的映射过程,并且这种映射关系是唯一的(即综合结果是唯一的)。

3.大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是__C__。

是基于乘积项结构的可编程逻辑器件;是全称为复杂可编程逻辑器件;C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置;D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。

4.进程中的变量赋值语句,其变量更新是_A__。

使用Altera器件实现电路设计

使用Altera器件实现电路设计

数码显示电路点阵二极管液晶显示器指示灯

分频将高频信号分频为低频信号

分频电路管脚分配

重新编译

58个管脚原理图

FPGA USB链接端口USB下载器端口连接

联合测试行动小组

关闭电源配置信息丢失

USB驱动已经装好301教室无驱动

装驱动步骤

查看PPT

自动安装手动安装驱动的位置(C盘altera 80 driver )选择硬件标签页

安装完毕

编程部分:

单击硬件按钮可以进行编程进度条program

注意分频

报告格式要求

选题目的

实现方案原理框图HDL设计流程图

设计目标

设计过程包括关键模块及仿真结果

实现结果

编程调试

遇到问题及解决方案。

信号发生器的FPGA实现(毕业设计)

目录摘要 (I)ABSTRACT (II)第1章绪论 (1)1.1信号发生器的研究意义与内容 (1)1。

2信号发生器的发展现状和前景展望 (1)1。

3信号发生器的总体设计思路 (3)第2章设计简介 (4)2。

1FPGA简介 (4)2.2VHDL硬件描述语言介绍 (7)2.3Q UARTUS II软件介绍 (9)2。

4RLT级仿真 (11)第3章系统硬件电路设计 (12)3。

1信号发生器的系统组成 (12)3。

2设计原理 (13)3.3输入部分 (15)3.3D/A数模转换部分 (18)第4章系统的软件设计 (20)4。

1系统软件流程图 (20)4。

2系统各模块 (21)4。

2.1 三角波产生模块 (22)4。

2.2 递减斜坡产生模块 (25)4。

2。

3递增斜坡产生模块 (28)4。

2.4 方波产生模块 (31)4。

2.5 阶梯波产生模块 (33)4。

2.6 正弦波产生模块 (36)4.2。

7 自定义波形产生模块 (43)4.2.8 波形选择器产生模块 (47)4。

2。

9 频率调节器产生模块 (50)4。

2.10 主控制器产生模块 (53)4.3引脚锁定 (58)第5章信号发生器的仿真 (61)5。

1递增斜坡的仿真结果及分析 (61)5。

2递减斜坡的仿真结果及分析 (61)5。

3三角波的仿真结果及分析 (62)5。

4正弦波的仿真结果及分析 (63)5.5方波的仿真结果及分析 (64)5.6阶梯波的仿真结果及分析 (65)5.6自定义波形的仿真结果及分析 (65)结束语 (66)参考文献 (67)致谢...................................................... 错误!未定义书签。

信号发生器的FPGA实现摘要:信号发生器在各种实验和测试中是必不可少的器件,同时在生产和科技领域中有着广泛的运用,例如在通信、控制、雷达、教学、军事等领域。

本次设计的内容是信号发生器的FPGA实现,要求用EAD技术设计一个信号发生器,此信号发生器的实现是利用EDA的硬件描述语言VHDL产生各个模块,然后在Altera公司提供的FPGA/CPLD开发集成环境的Quartus II软件上实现波形的编译、仿真、下载到Cyclone 芯片上.信号发生器由波形产生模块、频率调节模块和波形选择模块组成,波形产生模块可以产生三角波、正弦波、方波、阶梯波、递增斜坡、递减斜坡、自定义波形等,通过波形选择模块和频率调节模块可以选择自己所需要的波形和调节一定的频率。

《EDA技术》复习题-电子版答案

一、填空题1、目前国际上较大的PLD器件制造公司有Altera 和Xilinx 公司。

2、当前最流行并成为IEEE标准的硬件描述语言包括VHDL 和V erilog HDL 。

3、高密度可编程逻辑器件HDPLD包括EPLD 、CPLD 和FPGA 。

4、PLD从集成密度上可分为LDPLD 和HDPLD两类,其中HDPLD包括__EPLD_ ____、__ CPLD_____和___FPGA _____三种。

5、EDA设计流程包括设计准备、设计输入、设计处理和器件编程四个步骤。

6、图形文件的扩展名是_.bdf__;QuartusII所建工程的扩展名是_.qpf_;自建元件图形符号文件的扩展名_.bsf__;Verilog HDL所编程序的扩展名为__.v__ 。

7、图形文件的扩展名是 .bdf ;矢量波形文件的扩展名是.vwf ;自建元件图形符号文件的扩展名 .bsf 。

8、可编程逻辑器件的优化过程主要是对__速度__和___资源___的处理过程即时间优化和面积优化。

9、EDA设计输入主要包括__图形输入__、__ 文本输入和__ 波形__输入。

10、设计处理的最后一步是产生可供器件编程使用的数据文件,对CPLD来说是产生熔丝图文件即JEDEC文件,对于FPGA来说是产生位流数据文件Bitstream 。

11、EDA设计输入主要包括图形输入、文本输入和波形输入。

12、设计优化主要包括面积优化和速度优化。

13、Verilog HDL语言的扩展名为 .v 。

14、EDA的中文名称是电子设计自动化。

15、EDA仿真分为功能仿真又称前仿真、系统级仿真或行为仿真,用于验证系统的功能;时序仿真又称后仿真、电路级仿真,用于验证系统的时序特性、系统性能。

16、一般把EDA技术的发展分为_ __CAD____、__ CAE_____和___EDA____三个阶段。

17、阻塞型赋值符号为= ,非阻塞型赋值符号为<= 。

CPLD、FPGA下载线资料

一、本USB-Blaster下载线基本特性:1、稳定支持SignalTap II 嵌入式逻辑分析仪功能。

2、支持ALTERA 公司全系列器件。

CPLD:MAX3000、MAX7000、MAX9000 和MAXII 等;FPGA:Stratix、StratixII、StratxIII、Cyclone、CycloneII、CycloneIII、ACEX1K、APEX20K和FLEX10K等;主动串行配置器件:EPCS1、EPCS4、EPCS16、EPCS64等;增强配置器件:EPC1、EPC4 等。

3、支持三种下载模式:AS、PS和JTAG;4、支持与Nios II 嵌入式软核处理器的通信和在系统调试,Rev.C最新版固件!绝对不会出现以下提示:5、速度快:比常用的并口下载线ByteBlasterII快10倍;6、完全兼容ALTERA USB Blaster ,使用方法、功能和性能都和ALTERA原厂下载线一致。

7、USB-Blaster (ALTERA CPLD/FPGA 下载线) 支持1.5-5V编程电压。

二、引脚定义:采用Altera标准,定义如下:三、系统配置1、支持WindowsXP,Windows Vista, Windows7系统,USB接口;2、Quartus II 版本4.0以上;四、装箱清单1、USB-Blaster 编程器 1台2、高档USB电缆 1条3、10芯JTAG数据线 1条Lattice CPLD/FPGA/JTAG/ISP下载线DB25线对孔需要购买配件请勾选按照Lattice下载线标准电路制作,兼容JTAG/ISP模式,兼容Lattice公司的模拟器件、数字器件,下载线长度约80cm,直接使用ispVM即可下载。

引脚定义如下:Xilinx CPLD/FPGA/JTAG下载线商品货号:0228销售状态:热销中销售价格:40.00元我的价格:浏览人气:已有730人关注快递运费:12.00 元DB25线对孔需要购买配件请勾选兼容FPGA/JTAG模式。

EDA实验指导书FPGA_CPLD(第3版)

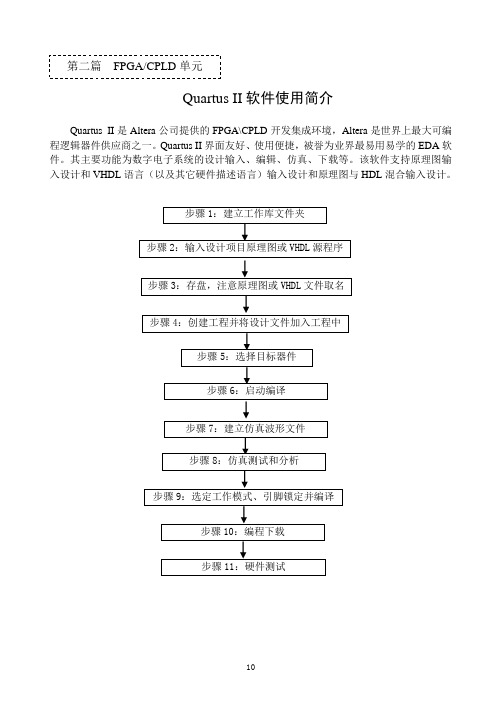

Quartus II软件使用简介Quartus II是Altera公司提供的FPGA\CPLD开发集成环境,Altera是世界上最大可编程逻辑器件供应商之一。

Quartus II界面友好、使用便捷,被誉为业界最易用易学的EDA软件。

其主要功能为数字电子系统的设计输入、编辑、仿真、下载等。

该软件支持原理图输入设计和VHDL语言(以及其它硬件描述语言)输入设计和原理图与HDL混合输入设计。

实验十用原理图输入法设计全加器一、实验目的1、熟悉利用Quartus II的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个4位全加器的设计把握利用EDA软件进行电子线路设计的详细流程。

2、学会对实验板上的FPGA/CPLD进行编程下载,硬件验证自己的设计项目。

二、原理说明一个4位全加器可以由4个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

而一个1位全加器可以按照EDA技术实用教程5.4节介绍的方法来完成。

三、实验步骤1位全加器由两个半加器及或门连接而成,如图10-1所示,ain为被加数、bin为加数,cin为进位输入,sum为和,cout为进位输出。

从图10-1看出,设计全加器应从设计半加器入手。

图10-11. 为本项工程设计建立文件夹任何一项设计都是一项工程(Project),与工程相关的文件有多个,应存放于同一个文件夹,故应首先为每个项目建立相应的文件夹。

设本项目的文件夹路径及名字为D:\adder。

注意文件夹名不能用汉字。

2. 输入设计项目原理图要设计的半加器为h_adder,如图10-2所示,a为被加数、b为加数,so为和,co为进位输出。

图10-2(1)建立新文件。

打开Quartus II,选菜单File→New,在弹出的对话框中选择“Device Design Files”页的原理图文件输入项Block Diagram/Schematic File(原理图编辑文件),扩展名为“.bdf”,按OK后将打开原理图编辑界面。

基于fpga和cpld的程序设计流程

基于fpga和cpld的程序设计流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor.I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!基于FPGA和CPLD的程序设计流程详解在现代电子设计领域,FPGA(Field-Programmable Gate Array)和CPLD(Complex Programmable Logic Device)因其高度可配置性和快速原型设计能力而备受青睐。

alteraFPGA的设计流程

推荐文章

sunburst-design/papers/ Verilog Coding Styles For Improved Simulation Efficiency State Machine Coding Styles for Synthesis Synthesis and Scripting Techniques for Designing MultiAsynchronous Clock Designs Synchronous Resets? Asynchronous Resets? I am so confused!

提供语言、图形等设计方法,十分灵活 通过仿真工具来验证设计的正确性

可以反复地擦除、编程,方便设计的修改和升级 灵活地定义管脚功能,减轻设计工作量,缩短系统开发时间

布局布线容易,设计过程相当于只有ASIC设计的前端

研发费用低

不需要投片费用

5

FPGA的应用前景

• 通信、控制、数据计算等领域得到了广泛的应用

• 减少电子系统的开发风险和开发成本 • 缩短上市时间(time to market) • 通过在系统编程、远程在线重构等技术降低维护升级成本

• 系统的原型实现+ASIC的原型验证

ASIC常用FPGA进行原型机验证

6

CPLD与FPGA的区别

内部结构 程序存储 资源类型 集成度 使用场合 速度 其他资源 保密性

,每一个描述都要考虑硬件的实现能力,是不是可 以综合的等等,目前HDL语言标准中仍然有不能被综 合的语法,这些要尤其注意。

19

功能仿真

• 对逻辑功能进行验证: • 不考虑时序问题,认为门都是理想门,没有延时; • 详细一些的可以认为门延时都是一样,而忽略互连 线的延时。

基于Altera Cyclone系列FPGA器件实现开发板的方案设计

基于Altera Cyclone系列FPGA器件实现开发板的方案设计1 引言现场可编程门阵列(FPGA,Field Programmable Gate Array)的出现是超大规模集成电路(VISI)技术和计算机辅助设计(CAD)技术发展的结果。

FPGA器件集成度高、体积小,具有通过用户编程实现专门应用的的功能。

它允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的效果。

利用FPGA可以大大缩短系统的研制周期,减少资金投入。

更吸引人的是采用FPGA器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便的对设计进行在线修改。

FPGA 器件成为研制开发的理想器件,特别适于产品的样机开发和小批量生产,因此人们也把FPGA称为可编程的ASIC。

可以断定FPGA在结构、密度、功能、速度和灵活性方面将得到进一步的发展。

随着工艺和结构的改进,FPGA的集成度将进一步提高,性能将进一步完善,成本将逐渐下降,在现代电子系统设计中将起到越来越重要的作用。

2 硬件电路设计及原理2.1 硬件电路整体结构本设计的开发板电路包括6个部分:下载电路、下载接口、FPGA、电源电路、和扩展接口。

其电路结构框图如下:2.1.1主芯片EPlC3T144C8Altera Cyclone系列FPGA是A1tera公司2003年9月份推出的,基于1.5v,O.13μm 工艺,Cyclone是一个性价比很高的FPGA系列。

其中EPlC3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本设计选用Altera公司的Cyclone系列芯片,芯片型号为EPlC3T144C8,因为该芯片是Altera公司推出的低价格、高容量的FPGA,其以较低的价格、优良的特性及丰富的片上资源在实际应用中被广泛的采用,这些都是其他同类产品无法相比的。

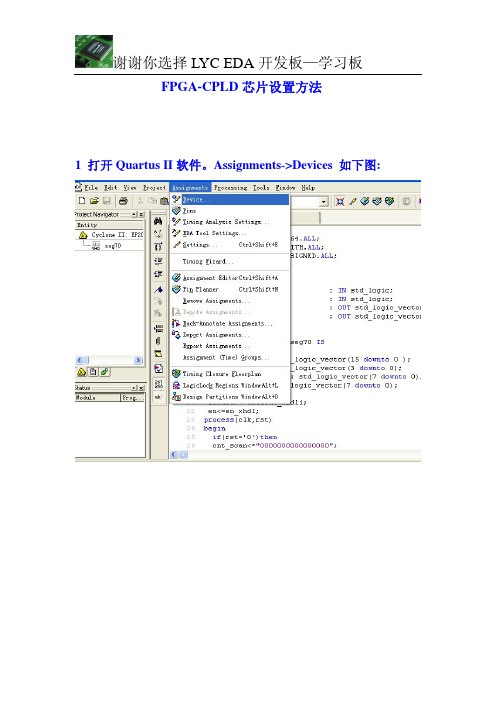

FPGA-CPLD芯片设置方法

FPGA-CPLD芯片设置方法

1 打开Quartus II软件。

Assignments->Devices 如下图:

2 出现下面的对话框,在Family选择器件(是那个家簇的),EPM240 属于MAX II家簇;如我们这里选择的是Cyclone II :

3 如下图: 选择芯片的封装.

4 选择芯片的管脚数目。

如下图:

5 选择速度等级,如下图:

6 如下图,高亮显示的就是你要找的器件。

点击确定按键,

重新编译一次工程。

7 如下图,I/O口的分配:

8 出现如下对话框,分配好你管脚。

8 出现以下对话框,将Compression 打钩,并且点击OK

9 出现以下对话框,选择.SOF ,在点击Generate.

10 当出现如下对话框,点击确定,并且重新把整个工程文件编译一次。

11 在下载模式选择AS下载,如下图,在点击Start:

12 如下图,表示下载成功。

恭喜你!!。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第21卷 第1期

吉 林 化 工 学 院 学 报Vol.21No.1 2004年3月

JOURNAL OF J IL IN INSTITU TE OF CHEMICAL TECHNOLOGY

Mar. 2004

收稿日期:2004-02-07

作者简介:翟玉文(1965-),男,吉林市人,吉林化工学院教授,硕士,主要从事自动化仪表及计算机应用方面的研究.

文章编号:100722853(2004)0120082202

基于AL TERA 的FP GA/CPLD 下载电路设计

翟玉文1,董 萍2,杨 潇1,艾学忠1

(1.吉林化工学院自动化系,吉林吉林132022;2.中国石油集团工程设计有限责任公司东北分公司,吉林吉林132002)

摘要:介绍了AL TERA CPLD/FPG A 可编程逻辑器件在系统配置方法,给出了AL TERA MAX 和

FL EX 系列器件的下载电路.

关 键 词:复杂可编程逻辑器件;现场可编程门阵列;在系统配置;下载电路中图分类号:TN 47 文献标识码:A

可编程逻辑器件PLD 是允许用户编程(配置)实现所需逻辑功能的器件.目前大规模可编程逻辑器件已日趋广泛地应用于复杂数字系统的设计中,并以其具有在系统重构ISR 的特点,给设计的修改和系统升级带来极大方便.AL TERA 公司是世界最著名的可编程逻辑器件生产厂家之一,它的EDA 开发工具MAX +PL US II 及其MAX7000S 和FL EL10K 系列器件得到了广泛应用.本文介绍采用J TA G 接口标准模式的MAX 和FL EX 系列器件下载电路设计.

1 MAX ,FL EX 系列器件下载电路

(1)MAX 系列器件是AL TERA 公司的基于EEPROM 工艺的复杂可编程逻辑器件CPLD ,包

括MAX9000、MAX7000A 、MAX7000B 、MAX7000S 、MAX7000、MAX5000、MAX3000A 和Classic 等系列.联合测试活动组织J TA G 开发了IEEE1149.1边界扫描测试BST 技术规范,用J TA G 接口作为下载接口,可以省去专用的编程接口,减少系统的引出线[1,2].图1以MAX7000S 为例给出了MAX 系列可编程逻辑器件的下载电路.J TA G 接口电路中使用了四根信号线:TDI ─—测试数据输入、TDO ─—测试数据输出、TMS ─—测试模式选择、TC K ─—测试时钟信号,对MAX 系列器件而言,TC K 、TMS 、TDI 是输入信号,TDO 是输出信号.利用MAX +PL US II 应用软件,在完成设计项目的编译后,生成的

CPLD 下载文件以pof 为扩展名,经仿真正确后,就可通过下载电路对相应的器件进行ISP 在系统编

程(下载).MAX 系列器件下载后具有非易失性.

图1 MAX 系列器件下载电路

(2)FL EX 系列器件是AL TERA 公司的基于

SRAM 工艺的现场可编程门阵列FPG A (Field Pro 2grammable G ate Array )型可编程逻辑器件,包括FL EX10K 、FL EX10KE 、FL EX8000和FL EX6000等系列.图2以FL EX10K10为例给出了FL EX 系列可编程逻辑器件的下载电路.J TA G 接口电路

中同样使用TC K 、TMS 、TDI 和TDO 四根信号线.基于SRAM 工艺的FP G A 器件由于配置数据存放于SRAM 中,系统掉电后将失去原有的逻辑功能,再次上电时需重新加载配置数据,所以这种下载电路的在系统配置方式适用于系统开发设计阶段.

2 J TA G 下载接口与计算机并口的

转换电路

J TA G 下载接口与计算机并口之间的转换连接如图3所示.电路采用J TA G 接口标准,通过并

图2 FL EX 系列器件下载电路

口下载电缆ByteBlaster (MV )采用J TA G 模式进行在系统编程(下载).25针D 型插座与计算机并口相连,10针插座(J TA G 接口)连接到用户下载板上,25针插座与10针插座之间是由74L S244组成的变换电路,用来提高信号驱动能力,将计算机并口送出的信息经缓冲后传送到下载板,同时将器件配置过程中送出的信息送给计算机,以使计算机与被配置的AL TERA 可编程器件之间进行信息交换.该转换电路可制作放置于25针D 型插座盒内

.

图3 J TA G 下载接口与计算机并口的转换连接

3 FP GA 非易失在系统配置方法

基于EEPROM 结构的CPLD 器件具有非易

失性,配置后其内容长期驻留在芯片内,可直接应用于实际系统中.但由于CPLD 芯片的规模较小(可用门数小于2万门),在复杂的大型数字系统中,基于SRAM 工艺的FP G A 器件具有更广泛的应用前景.对于已经设计完的FP G A 应用系统,如果每次掉电都通过计算机下载配置将很不方便,系统上电后能自动加载配置对FP G A 的应用是必须的.实现自动配置主要有主动串行配置(AS )和被动配置(PS 、PPA 或PPS )方式.AL 2TERA 的串行ROM 型EPC 器件是AS 方式的专用配置器件,包括O TP (一次可编程,如EPC1)和

多次可编程(如EPC2)两种.单片机可用于被动配置方式中对FP G A 进行配置.

参考文献:

[1] 赵曙光,郭万有,杨颂华.可编程逻辑器件原理、开

发与应用[J ].西安:西安电子科技大学出版社,

2000.

[2] 潘松,黄继业.EDA 技术实用教程[J ].北京:科学

出版社,2002.

[3] 何伟,唐仁圣,张玲.FPG A/CPLD 可编程逻辑器件

的在系统配置方法[J ].重庆大学学报,2003,(5):

125-128.

[4] 杨刚,杨霏.用单片机配置CPLD 器件[J ].电子设

计应用,2002,(11):49-51

Design of the dow nload circuit based on AL TERA FPGA/CPLD

ZHA I Yu 2wen 1,DON G Ping 2,YAN G Xiao 1,A I Xue 2zhong 1

(1.Dept.of Automation ,Jilin Institute of Chemical Technology ,Jilin City 132022,China ;2.Northeast Branch Company of China Petroleum Engineering Design Co.L TD ,Jilin City 132002,China )

Abstract :The method of the In 2System Reconfiguration based on AL TERA CPLD/FP G A is introduced.The download circuit for AL TERA MAX and FL EX is given.K ey w ords :CPLD ;FP G A ;ISR ;download circuit

3

8 第1期翟玉文,等:基于AL TERA 的FPGA/CPLD 下载电路设计 。