Altera FPGA的选型及开发

Altera Cyclone IV GX系列FPGA开发方案

Altera Cyclone IV GX 系列FPGA 开发方案

Altera 公司的Cyclone IV 系列FPGA 包括两个系列:Cyclone IV E 和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元, 高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps 高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业.本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA 开发套件主要特性,框图,电路图和材料清单.

Altera 新的Cyclone®IV 系列FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA 市场的领导地位,并且目前提供集成收发器功能的

型号。

Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:

■Cyclone IV E 最低的功耗,通过最低的成本实现较高的功能性。

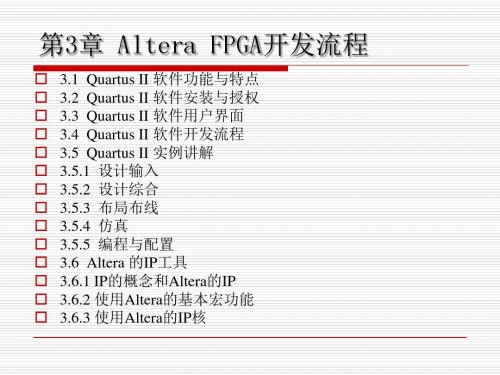

第3章_Altera_FPGA开发流程

火龙果整理

【Import Assignments】导入分配文件。 【Timing Closure Foorplan】启动时序收敛平面 布局规划器。 【LogicLock Region】查看、创建和编辑 LogicLock 区域约束以及导入导出 LogicLock 区 域约束文件。 『Processing』菜单包含对当前工程执行各种设 计流程,如综合、布局布线、时序分析等。 『Tools』 菜单中包含 Quartus II 集成的工具, 如 MegaWizard Plug-Inmanager、 Chip Editor、 RTL Viewer、Programmer等工具。

火龙果整理

3.1 Quartus II 软件功能与特点

QuartusII是Altera公司继MAX+PLUS II后的新一代 PLD 开发软件,适合大规模 FPGA 的开发,它包含 FPGA设计流程中所有工具和第三方软件接口。通过 使用该工具用户可开发和管理自己的设计。 Quartus II提供完整的多平台设计环境,能够直接 满足特定需要,为SOPC提供全面的设计环境。 QuartusII 软件包含有 FPGA 和 CPLD 所有的设计阶段 的解决方案。

创建工程

5. 用户指定目标器件,根据开发板的所使用的 器件来选择,实际开发中,通过查看核心板的 参考手册来获取所使用的器件具体型号,可以 使用窗口右边的Filters来加快器件的选择,选 择完毕点击Next。

火龙果整理

创建工程

火龙果整理

6. 指定在Quartus II 之外的用于,设计输入、综合、仿 真、时序分析的第三方EDA工具,Quartus II对第三 方工具的支持比较完善。这里我们不做选择,直接点 击Next。

Altera Cyclone IV GX系列的特性及FPGA开发套件的设计方案介绍

Altera Cyclone IV GX系列的特性及FPGA开发套件的设计方案介绍Altera 公司的Cyclone IV 系列FPGA包括两个系列:Cyclone IV E和Cyclone IV GX,具有低成本、低功耗的FPGA 架构,6 K 到150 K 的逻辑单元,高达6.3 Mb 的嵌入式存储器,小于1.5 W 的总功耗;Cyclone IV GX 器件提供高达八个3.125 Gbps高速收发器,用于大批量,成本敏感的应用如无线、有线、广播、工业,用户以及通信等行业。

本文介绍了Cyclone IV 器件系列主要特性,收发器通道框图以及Cyclone IV GX FPGA开发套件主要特性,框图,电路图和材料清单。

Altera 新的Cyclone®IV 系列FPGA 器件巩固了Cyclone 系列在低成本、低功耗FPGA 市场的领导地位,并且目前提供集成收发器功能的型号。

Cyclone IV 器件旨在用于大批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型号:■Cyclone IV E- 最低的功耗,通过最低的成本实现较高的功能性■Cyclone IV GX- 最低的功耗,集成了3.125 Gbps 收发器的最低成本的FPGA Cyclone IV 器件集成了一个可选择的低成本收发器,在未影响性能的情况下,节省了功耗及成本。

针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型应用,Cyclone IV 器件无疑是最理想的选择。

Cyclone IV 器件系列主要特性:■低成本、低功耗的FPGA 架构:■6 K 到150 K 的逻辑单元■高达6.3 Mb 的嵌入式存储器■高达360 个18 ×18 乘法器,实现DSP 处理密集型应用■协议桥接应用,实现小于1.5 W 的总功耗■Cyclone IV GX 器件提供高达八个高速收发器以支持:■高达3.125 Gbps 的数据速率■8B/10B 编码器/ 解码器。

Altera公司FPGA的配置

•

针对FPGA器件不同的内部结构,Altera公司

提供了不同的器件配置方式。Altera FPGA的配

置可通过编程器、JATG接口在线编程及Altera在

线配置等方式进行。

•

Altera器件编程下载电缆的有:

ByteBlaster并行下载电缆,ByteBlasterMV并行

MAX9000(包括MAX9000A)、MAX7000S和MAX7000A

进行编程。ByteBlaster为FPGA提供了一种快速而

廉价的配置方法,设计人员的设计可以直接通过

ByteBlaster下载电缆下载到芯片中去。

(1)下载模式

ByteBlaster并行下载电缆提供两种下载模式: • ①Passive serial mode(PS,被动串行模式)

1. PS(被动串行)模式

•

在PS(被动串行)模式下,MasterBlaster

下载电缆和ByteBlasterMV下载电缆可以对单个

与多个APEXⅡ、APEX20K、Mercury、ACEX1K、

FLEX10K或 FLEX6000系列器件进行配置。在PS模

式,配置数据从数据源通过MasterBlaster下载

电缆和ByteBlasterMV下载电缆串行地传送到器

件,配置数据由数据源提供的时钟同步。

(1)PS模式单个器件的配置电路设计

•

PS模式可以完成对单个APEXⅡ、 NhomakorabeaPEX20K、

Mercury、ACEX1K、FLEX10K或 FLEX6000系列器件

的配置,配置电路如图6.2所示。

•

图中:除 APEX20KE、APEX20KC系列器件外,

altera_fpga的设计流程

布局布线 - Map Primitives to Specific Locations inside Target Technology with Reference to Area & Performance Constraints

RTL代码

调用模块的 黑盒子接口

设置综合目标 和约束条件

逻辑综合器

EDIF网表 (netlist)

HDL网表 (netlist)

20

布局布线

• 将综合生成的网表,在FPGA内部进行布局布线的设计, 并最终生成用于下载的二进制配置文件;

逻辑综合器

EDIF网表 (netlist)

调用模块 的

综合模型

设置布局 布线约束

ModelSim 用户界面

main主窗口:

structure结构窗口

process处理窗口

:

Signal&variable信号 和变量窗口

dataflow数据流窗口

source源窗口

Wave&list 波形和列表窗口

29

ModelSim的用途

1. RTL 仿真(功能仿真) ❖ 验证设计HDL的基本逻辑功能,属于最基本的验证 ❖ 仿真速度最快

1 建立库

UI) 从主菜单里面: Design -> Create a New Library

Cmd) 从main, 记录窗口:

ModelSim> vlib <库名>

33

用ModelSim作功能仿真(4)

2 映射库到物理目录

UI) 从主菜单: Design -> Browse Libraries Design -> Create a New Library

基于Altera Cyclone系列FPGA器件实现开发板的方案设计

基于Altera Cyclone系列FPGA器件实现开发板的方案设计1 引言现场可编程门阵列(FPGA,Field Programmable Gate Array)的出现是超大规模集成电路(VISI)技术和计算机辅助设计(CAD)技术发展的结果。

FPGA器件集成度高、体积小,具有通过用户编程实现专门应用的的功能。

它允许电路设计者利用基于计算机的开发平台,经过设计输入、仿真、测试和校验,直到达到预期的效果。

利用FPGA可以大大缩短系统的研制周期,减少资金投入。

更吸引人的是采用FPGA器件可以将原来的电路板级产品集成为芯片级产品,从而降低了功耗,提高了可靠性,同时还可以很方便的对设计进行在线修改。

FPGA 器件成为研制开发的理想器件,特别适于产品的样机开发和小批量生产,因此人们也把FPGA称为可编程的ASIC。

可以断定FPGA在结构、密度、功能、速度和灵活性方面将得到进一步的发展。

随着工艺和结构的改进,FPGA的集成度将进一步提高,性能将进一步完善,成本将逐渐下降,在现代电子系统设计中将起到越来越重要的作用。

2 硬件电路设计及原理2.1 硬件电路整体结构本设计的开发板电路包括6个部分:下载电路、下载接口、FPGA、电源电路、和扩展接口。

其电路结构框图如下:2.1.1主芯片EPlC3T144C8Altera Cyclone系列FPGA是A1tera公司2003年9月份推出的,基于1.5v,O.13μm 工艺,Cyclone是一个性价比很高的FPGA系列。

其中EPlC3T144是Cyclone系列中的一员,共有2910逻辑单元,59904RAM bits,1个PLLs,最多有104个用户I/O,可以说这款FPGA的资源非常丰富,足够满足大型设计的需要。

本设计选用Altera公司的Cyclone系列芯片,芯片型号为EPlC3T144C8,因为该芯片是Altera公司推出的低价格、高容量的FPGA,其以较低的价格、优良的特性及丰富的片上资源在实际应用中被广泛的采用,这些都是其他同类产品无法相比的。

FPGA选型手册

Version 13.1Altera 产品目录 • 2013 • 1Altera 提供最全面的可编程逻辑器件系列产品—FPGA 、SoC和CPLD结合软件工具,知识产权(IP)、嵌入式处理器、客户支持和技术培训。

Altera 产品的领导地位、卓越的价值以及优质的服务给您带来显著的优势。

将带给您奇思妙想,帮助您更快更好的实现性价比更高的设计。

FPGAAltera FPGA 帮助您获得最佳的灵活性进行创新、差异化,并在市场上保持领先地位。

我们提供三类FPGA ,从业界最高密度和高性能到最具成本效益,以满足市场要求。

概述SoCSoC 将两个分立的器件合并成一个,从而降低了系统功耗和成本,减小电路板面积,同时提高了性能。

SoC 使用宽带互联链路,在FPGA 架构中集成了基于ARM 的硬核处理器系统(HPS),包括双核ARM®处理器、外设和存储器控制器。

电源采用Enpirion 电源管理产品启动您的FPGA 。

该系列集成产品提供业界领先的小外形封装、低噪声性能和高效率的组合,从而更快地完成设计。

CPLD对于胶合逻辑以及任何控制功能,我们的非易失MAX 系列提供市场上成本最低的CPLD—单芯片解决方案,非常适合接口桥接、电平转换、I/O 扩展和模拟I/O 管理。

高效能设计软件、嵌入式处理、知识产权(IP )、开发套件和培训和Altera 一起,您将获得全面的设计环境以及多种设计工具—所有的工作顺理成章,迅速完成设计。

您可以参加我们的培训课程,快速开始您的设计工作。

选择Altera ,了解我们怎样帮助您提高效能,让您从根本上与众不同。

最高带宽,最高密度的FPGA 集成收发器种类在片上设计整个系统均衡成本、功耗和性能的FPGA 集成收发器和处理器种类综合设计保护最低系统成本和功耗的FPGA 集成收发器和处理器种类最快的面市时间2 Altera 产品目录 • 2013 •2 1 所有数据在印刷时是正确的,可能会随时更改,恕不另行通知。

Altera FPGA开发说明(QuartusII 7.2 & ModelSim 6.5)

Altera FPGA开发说明(QuartusII 7.2 & ModelSim 6.5)By ccx于2010-11-22一、说明1、本例程中的代码是用Verilog编写的,但本文并不探讨Verilog本身。

推荐王金明的一本书作为入门书籍,既讲到了Verilog,也讲到了QuartusII 的使用,还探讨了Modelsim的使用(很难得地讲到了Test Bench的编写)。

2、QuartusII 7.2软件的文本编辑器不支持中文输入,Modelsim 6.5的编辑窗口也不尽如人意。

使用Notepad++(目前只支持Windows平台,方便易用)也可使用Gvim(陆博推荐,因为linux系统中也有对应的编辑工具)3、本例中的程序功能说明一个4位二进制计数器,显示到FPGA开发板(DE2-70)的4个LED上。

4、本例的验证平台为Altera公司的DE2-70开发板二、使用QuartusII 7.2和ModelSim 6.5进行Altera FPGA开发2.1、FPGA开发流程图2.2、建立QuartusII项目这里不讨论原理图输入法,也不讨论多个模块如何组织在1个顶层模块之下。

在建立项目之前,我已经编写好counter.v文件,并把它放在E:\counter目录下。

打开QuartusII软件,File→New Project Wizard…,可开始建立项目的流程。

2.2.1、向导介绍建立项目时要做的工作2.2.1、填写目录、项目名、top-level entity名注意:top-level entity需要正确填写,因为本例中只有一个模块counter,而且其为top-level entity,所以填写如下。

2.2.2、为项目添加文件2.2.3、选定器件Cyclone II系列,器件编号为EP2C70F896C6(可以网上搜索该器件号的意思)。

2.2.4、EDA工具设置默认即可,但可以留意Simulation一项,因为之后用ModelSim 6.5做时序仿真与它有关。

Altera CPLDFPGA轻松入门与开发实例第4章 (4)

2 时序分析

(5)数据要求信号---保持时间:使新信号 到达目的寄存器D输入的最早的时间

2 时序分析

(6)Slack:用于衡量设计满足或者不满足 时序约束的程度,为了使电路能够正常工 作,Slack的计算结必须是正的。

建立Slack = 建立需要的时间 — 数据到达时间 保持Slack = 数据到达时间 — 保持需要的时间

2 时序分析

(1)启动沿(Launch)和锁存沿(Latch)

2 时序分析

(2)数据到达时间:时钟启动沿使数据从 源寄存器到达目的寄存器D输入引脚的时 间

2 时序分析

(3)时钟到达时间:时钟到达寄存器时钟 引脚的时间

2 时序分析

(4)数据要求信号---建立时间:使信号由 源寄存器发送必须到达目的寄存器D输入 的时间,以便正确采样。

2 PLD设计流程

PLD的开发流程一般包括设计定义、 设计输入、功能仿真、综合优化、综合后 仿真、实现、布线后仿真、板级仿真以及 芯片编程与调试等主要步骤 。

2 布局布线

4.4 仿真及时序分析 4.4.1 仿真 4.4.2 时序分析

Page 17

机பைடு நூலகம்工业出版社

2015-1-6

1 仿真

新的Quartus II软件不再提供自带的仿真器( Simulator),因此要使用EDA 仿真工具对设计进 行功能与时序仿真。 使用 NativeLink 功能,可以让Quartus II 软件编译设计,生成相应的输出文件,然后使用 EDA 仿真工具自动进行仿真。当然也可以在编译 之前或编译之后,在Quartus II 软件中手动运行 EDA 仿真工具进行功能仿真或时序仿真。功能仿 真可以在设计流程中的任何阶段进行。时序仿真 则必须在编译之后才能进行。

列举altera公司的cpld和fpga产品。

Altera公司是一家知名的半导体公司,致力于生产和销售可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)等产品。

下面将列举Altera公司旗下的CPLD和FPGA产品,帮助大家更好地了解这家公司的产品线。

一、CPLD产品线1. MAX 7000系列MAX 7000系列是Altera公司推出的一款CPLD产品,具有低功耗、高性能和可编程性强的特点。

该系列产品广泛应用于通信、工业控制、汽车电子等领域,为客户提供了稳定可靠的解决方案。

2. MAX 9000系列MAX 9000系列是Altera公司的另一款CPLD产品,采用了先进的CMOS工艺和可编程逻辑单元,具有高密度、可靠性高的特点。

该系列产品在航空航天、国防安全、医疗设备等领域有着广泛的应用。

二、FPGA产品线1. Stratix系列Stratix系列是Altera公司旗下最为知名的FPGA产品之一,拥有高速、高密度、低功耗等特点,适用于需要大规模数据处理和高性能计算的应用场景。

该系列产品常用于人工智能、云计算、数据中心等领域。

2. Cyclone系列Cyclone系列是Altera公司针对中小规模应用市场推出的FPGA产品,具有低成本、低功耗、高性能等特点。

该系列产品在嵌入式系统、工业自动化、网络通信等领域有着广泛的应用。

3. Arria系列Arria系列是Altera公司旗下的高性能FPGA产品,具有高速、低功耗、灵活性强等特点,适用于需要高性能和灵活性的应用场景。

该系列产品在无线通信、高性能计算、高清视频等领域有着广泛的应用。

通过以上列举,我们可以看到Altera公司在CPLD和FPGA领域拥有丰富的产品线,为不同领域的客户提供了多样化的解决方案。

期待Altera在未来能够持续推出更多高性能、低功耗的PLD和FPGA产品,满足客户不断增长的需求。

Altera公司作为半导体行业的领军企业,一直以来致力于为全球各行业提供高性能、低功耗的可编程逻辑器件(PLD)和现场可编程门阵列(FPGA)产品。

用CPU配置Altera公司的FPGA

用CPU配置Altera公司的FPGA一. 概述目前很多产品都广泛用了FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的EPROM对FPGA进行配置。

专用的EPROM价格不便宜,且大部分都是一次性OTP方式编程。

一旦更改FPGA设计,代价不小。

为了进一步降低产品的成本和升级成本,可以考虑利用板上现有CPU子系统中空闲的ROM空间存放FPGA的配置数据,并由CPU模拟专用EPROM对FPGA进行配置。

本文将以PowerPC860和EP1K30为例,讲解如何利用CPU来配置FPGA。

CPU配置FPGA的优点与Configuration EPROM方式相比本设计有如下优点:1.降低硬件成本——省去了FPGA专用EPROM的成本,而几乎不增加其他成本。

以A LTERA的10K系列为例,板上至少要配一片以上的EPC1,每片EPC1的价格要几十元,容量1M位。

提供1Mb的存储空间,对于大部分单板来说(如860系统的单板),是不需要增加硬件的。

即使增加1Mb存储空间,通用存储器也会比FPGA专用EPROM便宜。

2.可多次编程——FPGA专用EPROM几乎都是OTP,一旦更换FPGA版本,旧版本的并不便宜的EPROM只能丢弃。

如果使用本设计对FPGA配置,选用可擦除的通用存储器保存FPGA的编程数据,更换FPGA版本,无须付出任何硬件代价。

这也是降低硬件成本的一个方面。

3.实现真正"现场可编程"--FPGA的特点就是"现场可编程",只有使用CPU对FPGA 编程才能体现这一特点。

如果设计周全的话,单板上的FPGA可以做到在线升级。

4.减少生产工序--省去了对"FPGA专用EPROM"烧结的工序,对提高生产率,降低生产成本等均有好处。

对于双面再流焊的单板,更可省去手工补焊DIP器件的工序。

当然,与Configuration EPROM方式相比也有一些需要注意的的地方:1.需要CPU提供5根I/O线--一般来说,这并不困难。

Altera-FPGA详解(doc 23页)

Altera中文资料FPGA在软件无线电中的应用介绍软件无线电(SDR)是具有可重配置硬件平台的无线设备,可以跨多种通信标准。

它们因为更低的成本、更大的灵活性和更高的性能,迅速称为军事、公共安全和商用无线领域的事实标准。

SDR成为商用流行的主要原因之一是它能够对多种波形进行基带处理和数字中频(IF)处理。

IF处理将数字信号处理的领域从基带扩展到RF。

支持基带和中频处理的能力增加了系统灵活性,同时减小了制造成本。

基带处理无线标准不断地发展,通过先进的基带处理技术如自适应调制编码、空时编码(STC)、波束赋形和多入多出(MIMO)天线技术,支持更高的数据速率。

基带信号处理器件需要巨大的处理带宽,以支持这些技术中大计算量的算法。

例如,美国军事联合战术无线系统(JTRS)定义了军事无线中20多种不同的无线波形。

一些更复杂的波形所需的计算能力在标准处理器上是每秒数百万条指令(MIPS),或者如果在FPGA 实现是数千个逻辑单元。

协处理器特性SDR基带处理通常需要处理器和FPGA。

在这类应用中,处理器处理系统控制和配置功能,而FPGA实现大计算量的信号处理数据通道和控制,让系统延迟最小。

当需要从一种标准切换至另一种标准时,处理器能够动态地在软件的主要部分间切换,而FPGA能够根据需要完全重新配置,实现特定标准的数据通道。

FPGA可以作为协处理器同DSP和通用处理相连,这样具有更高的系统性能和更低的系统成本。

自由地选择在哪实现基带处理算法为实现SDR算法提供了另一种方式的灵活性。

基带部件也需要足够灵活让所需的SDR功能支持在同一种标准增强版本之间的移植,并能够支持完全不同的标准。

可编程逻辑结合软核处理器和IP,具有了提供在现场远程升级的能力。

图1 是一个框图,其中FPGA能够通过IP功能如Turbo编码器、Reed-Solomon编码器、符号交织器、符号映射器和IFFT,很容易地重配置支持WCDMA/HSPDA或802.16a标准的基带发送功能。

AlteraFPGA开发流程

资源管理窗

五、编译状态显示窗 编译状态显示窗主要在编译过程中显示各个过程的进度。 包括语法检查,综合进度,布局布线时间 等。 六、工程工作区 工程工作区主要在设计过程中显示各种设置窗口、编辑 串口和显示窗口等,也是用户使用 Quartus II 软件的主要交互区。 七、信息显示窗 信息显示窗主要显示当前软件的工作状态或工程进行的 操作,其最主要功能还是显示编译过程中产 生的各项信息,这些信息包括普通信息、警告、错误等。 在编译过程中遇到错误时,可以通过错误 信息锁定错误发生点,方便用户查找和修改设计。

创建工程

创建工程

创建工程

3. 进行项目名称的设定、工作名和顶层实体名要求相同,工程目录可以随意 设置,但必须是英文的目录,工程名和顶层实体 名也要求是英文名字,我们的工程名和顶层实体 名为clock,选择Next。

创建工程

创建工程

4.可以为工程添加先期已经输入的设计文件,指定用 户自定义的元件库的路径,这里我们没有事先输入好 的文件,也没有自定义的元件库,点击Next进入下一 步。

创建工程

创建工程

5. 用户指定目标器件,根据开发板的所使用的 器件来选择,实际开发中,通过查看核心板的 参考手册来获取所使用的器件具体型号,可以 使用窗口右边的Filters来加快器件的选择,选 择完毕点击Next。

三、工具栏 工具栏中包含常用命令的快捷图标。鼠标移动到图 标时,鼠标下方会出现此图标对应的含义,每种图 标在菜单栏也能找到相应命令菜单。用户可根据个 人需要放置一些常用功能快捷图标,提高设计效率。 四、资源管理窗 资源管理窗用于显示当前工程中所有相关的资源文 件。在编译后,结构层次标签栏里会显示整个工程 设计的结构,并且还列出了每个文件占用的资源情 况。 文件标签栏里显示了所有源文件的目录和名称。设 计单元标签栏里将显示所有设计单元,包括它们的 类型。

Altera电路设计考虑部分

FPGA开发板需要考虑事项:1.FPGA选型:EP2C20F256C8N2.FPGA电路设计:●供电电路设计:满足FPGA以及外设供电●复位电路、晶振电路设计●下载调试接口电路设计:USB BLASTER选择USB-Blaster下载电缆的四大理由:/FPGA/Altera/201104/32038.html●存储电路设计:EPROM (配置模式)●外设接口电路设计:串口485/网口/IIC/KEY//LED/IO扩展口(排阵)考虑跑操作系统的扩展需求SDRAM SRAM需求以及使用。

FPGA在红外测试仪器中负载以及扩容:1. 5个AD的读写控制——可以直接挂在外部总线上也可以是GPIO;2. 5个继电器的控制;3.电磁铁控制以及检测;4.暗电流挡板控制;5.外设:串口/以太网/USB BLASTER下载;逻辑消耗:1.数据处理2.NoisII3.外设接口4.控制逻辑器件型号指南:/guantouren/blog/11-11/235033_3335a.htmlFPGA系统中DRAM,SRAM,SDRAM,FLASH 区别一般来说这几种存储器是一个nios系统都具有的,sram的好处是接口简单,速度快容易操作,用资源也比较少;sdram的最大好处是容量大,当然速度也比较快,但是接口复杂些,也耗逻辑资源多些;flash是非易失性存储器,速度慢。

SRAM、SDRAM都用于程序工作时保存临时数据和程序,因为在系统调电后,保存在其中的数据都会丢失。

FLASH用于系统中保存长期的数据,如:配置信息,程序等。

由于SRAM接口电路简单,在小系统中常用,SDRAM的接口相对复杂,需要相应的控制器支持,但由于容量大、价格便宜、访问速度快,所以常用在对内存容量和处理速度要求高的应用场合,在这种场合中,相应的处理器(CPU)都自带有SDRAM控制器。

DRAM是动态存储器(Dynamic RAM)的缩写SDRAM是英文SynchronousDRAM的缩写,译成中文就是同步动态存储器的意思。

ALTERA主流芯片选型指

ALTERA主流芯片选型指主流PLD产品:MAXII:新一代PLD器件,0.18um falsh工艺,2004年底推出,采用FPGA结构,配置芯片集成在内部,和普通PLD一样上电即可工作。

容量比上一代大大增加,内部集成一片8Kbits串行EEPROM,增加很多功能。

MAXII 采用2.5v或者3.3v内核电压,MAXII G系列采用1.8v内核电压。

MAX II 器件家族Feature EPM240/G EPM570/G EPM1270/G EPM2210/G逻辑单元 (LE) 240 570 1,270 2,210等效宏单元(Macrocell)192 440 980 1,700最大用户IO 80 160 212 272内置Flash大小(bit) 8K 8K 8K 8K管脚到管脚延时(ns) 3.6-4.5 3.6-5.5 3.6-6.0 3.6-6.52.主流FPGA产品Altera的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone,CycloneII;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix,StratixII 等,用户可以根据自己实际应用要求进行选择。

在性能可以满足的情况下,优先选择低成本器件。

Cyclone(飓风):Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列 ,是目前主流产品,其配置芯片也改用全新的产品。

CycloneII:Cyclone的下一代产品,2005年开始推出,90nm工艺,1.2v内核供电,属于低成本FPGA,性能和Cyclone相当,提供了硬件乘法器单元∙Stratix:altera大规模高端FPGA,2002年中期推出,0.13um工艺,1.5v内核供电。

集成硬件乘加器,芯片内部结构比Altera以前的产品有很大变化。

Altera(Intel)FPGA全系列芯片选型手册

逻辑元 LAB/C 总 RAM I/O 件/单元 LB 数 位数 数 数 392 72 291 291 288 392 72 288 321 321 288 291 288 6272 276480 576 2910 2910 12288 59904 59904

291 321 6 423936 6272 276480 576 12288

4608 119808 4608 119808

Cyclone® IV E ACEX-1K® Cyclone® Cyclone® Cyclone® III Cyclone® Cyclone® II Cyclone® Cyclone®

100-TQFP 256-LBGA

100-TQFP EP1C3T100I7N (14x14) EP3C5F256C8N EP4CE6F17C7N

下载 下载 下载

查询 查询 查询 查询 查询 查询

256-FBGA (17x17) 256-FBGA 256-LBGA (17x17) 144-TQFP 144-LQFP (20x20) 208-PQFP 208-BFQFP (28x28) 208-BFQFP

下载

查询 查询 查询 查询 查询 查询 查询 查询 查询

144-TQFP EP1K30TC144-3N 下载 (20x20) 144-TQFP EP1C6T144C8N 下载 (20x20) 100-TQFP EP1C3T100I7 (14x14) 256-UBGA (14x14) 144-TQFP (20x20) 144-TQFP (20x20) 324-FBGA (19x19) 144-TQFP (20x20) EP3C5U256C8N EP1C3T144C6N EP2C8T144C8N EP1C4F324C8N EP1C6T144C8 下载 下载 下载 下载 下载 下载

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA系统设计与应用

华清远见

内容大纲

Altera的FPGA体系结构简介 Altera的FPGA选型策略 嵌入式逻辑分析工具SignalTAPII的使用 基于CPLD的FPGA配置方法

v v v v

华清远见

FPGA技术的发展历史和动向

电子器件:存储器、处理器和逻辑器件 v 存储器器件保存随机信息(电子数据表或数据库的 内容); v 处理器执行软件指令,以便完成各种任务(运行数 据处理程序或视频游戏); v 逻辑器件可以提供特殊功能(器件之间的通信和系 统必须执行的其它所有功能)。

降低了成本、提高 了可靠性、缩小了物理尺寸

华清远见

逻辑器件分类

逻辑器件分成两类: v 固定的或定制的

固定的或定制的逻辑器件通常称为专用芯片 (ASIC)。

ASIC是为了满足特定的用途而设计的芯 片,例如MP3解码芯片等。

其优点是通过固化的逻 辑功能和大规模的工业化生产,降低了芯片的成 本,同时提高了产品的可靠性。

v 可编程的或可变的

华清远见

FPGA技术概念

v CPLD (Complex Programmable Logic Device) v FPGA (Field Programmable Gate Array) v 硬核:ARM、MIPS、POWERPC v 软核:Nios/NiosII v SOC: 片上系统 v SOPC:可编程片上系统 v IP核:知识产权

华清远见

可编程逻辑器件的优点

v 集成度高 v 缩短研制时间 v 体积小 v 性能高 v 可靠性高 v 保密性好 v 设计灵活(可编程、可再编程、系统内可再编程) v 通用性好 v JTAG板级和芯片级的测试

华清远见

FPGA的实现工艺分类

v 基于SRAM的FPGA,如Altera,Xilinx等

优点:灵活; 缺点:易受干扰;

v 反融丝结构FPGA,如Actel,Quicklogic等

优点:稳定; 缺点:灵活性差

v Flash结构FPGA,如Actel,Lattice等

优点:灵活,稳定; 缺点:厂家影响力小

华清远见

两大FPGA厂商的代表产品

华清远见

FPGA技术的发展动向

v 基于FPGA的嵌入式系统(SoPC)技术正在成熟(Altera

公司的NIOSII解决方案)

华清远见

v FPGA芯片向高性能、高密度、低压和低功耗的方向

发展

v 基于IP库的设计方法

华清远见

v FPGA的动态可重构技术

动态可重构的FPGA主要适用于以下的两个系统设 计: ①最新通信系统:FPGA的动态重构特性可以适应不同 体制和不同标准的通讯要求,满足软件无线电技术 的发展和第三代(3G)和第四代(4G)移动通信系 统的需要。

②重构计算机:FPGA具有并行处理能力和动态配置能 力,促使了全新概念的可自动改变硬件来适应正在 运行的程序计算机的产生。

华清远见

FPGA的典型应用(一)

接口逻辑控制器 --提供前所未有的灵活性

v ISA,PCI,PCI Express,PS/2,USB等接口控制器 v SDRAM,DDR SDRAM, QDR SRAM, NAND Flash,

NOR Flash等接口控制器 v 电平转换,LVDS,TTL,COMS,SSTL等

华清远见

设计实例一:立体三维图像分配器

v 立体三维图像分配器的存储器接口设计

基本功能:将输入的立体视频(1024×768,24bit@60Hz)分成两路(奇数帧 一路,偶数帧一路),每路的帧频仍然是60Hz。

1。

存储器类型:SDRAM或者DDR SDRAM 一帧图像大小:1024×768×24bit/3,大约2M Bytes。

采用乒乓结构,需 要2帧图像,至少要4M Bytes的存储器。

2。

存储器位宽:96位 输入:每帧2MB,每秒60帧,约120MB; 输出:每路约120MB,两路240MB; 累计的数据吞吐率为360MB。

如果采用8Bit位SDRAM,SDRAM时钟至少要达 到360MHz!(不可能) 增加位宽到96位, SDRAM时钟可以降低到30MHz!

华清远见

华清远见

实物图片

华清远见

FPGA的典型应用(二)

高速数字信号处理(DSP) --提供前所未有的计算能力

v v v

无线通信领域,如软件无线电(SDR) 视频图像处理领域,如高清数字电视(HDTV) 军事和航空航天领域,如雷达声纳

华清远见

设计实例二:视频图像处理系统

v 高速图像压缩系统

设计需求: 1920×1080,30帧/秒图像,采用H.264 Intra模式编码,实 时传输。

计算量: 传统DSP: 1GHz C6416 ,需要4颗; FPGA: 单颗, Altera EP2S180

华清远见

华清远见

FPGA的其他应用

其他应用领域 v 汽车, 如 网关控制器/车用PC ,远程信息处理系统 v 军事,如安全通信 ,雷达和声纳,电子战 v 测试和测量,如通信测试和监测 ,半导体自动测试设 备 ,通用仪表 v 消费产品,如显示器/投影仪 ,数字电视和机顶盒 ,家庭 网络 v 医疗,如软件无线电 ,电疗 ,生命科学 v 通信设备,如蜂窝基础设施 ,宽带无线通信,软件无线 电(SDR)

华清远见

基于FPGA的嵌入式系统实例

v 主要的嵌入式解决方案

Altera公司 NIOSII / ARM9方案 Xilinx公司 MicroBlaze/Power PC方案 Actel公司 ARM7方案

华清远见

工程项目中FPGA芯片选择策略和原则

v 尽量选择成熟的产品系列 v 尽量选择兼容性好的封装 v 尽量选择一个公司的产品

华清远见

FPGA实验板实物图

华清远见

FPGA最小系统概念以及构成

v FPGA最小系统概念

能独立工作的最基本电路 v 硬件系统的构成 基本组成: 主芯片,调试接口,存储器,电源,时钟,复位

华清远见

FPGA主芯片电路设计

v 管脚兼容性设计方法 v 器件的选择 成本包括硬件成本和软件开发成本以及 升级维护的成本 工艺并不是越先进越好 v 芯片管脚指定原则 1. 依据PCB布局指定 2. 专用IO的处理,比如时钟,配置管脚等 v 锁相环管脚的处理

华清远见

Altera PLL电源管脚滤波电路

华清远见

JTAG 下载与调试接口

华清远见

AS下载与调试接口

华清远见

高速SDRAM存储器接口电路设计

华清远见

异步SRAM存储器接口电路设计

华清远见

FLASH存储器接口电路设计

华清远见

电源,时钟和复位电路设计

华清远见

复位电路

华清远见

时钟电路

华清远见

FPGA最小系统的调试方法和技巧

v 调试流程

1. 短路/断路测试 2. 电源电压测试 3. 下载模式测试(JTAG/AS) 4. 其他接口依次测试

华清远见

SignalTapII嵌入式逻辑分析仪

对FPGA内部信号进行探查和评估 v 嵌入SignalTapII逻辑分析仪的方法 1. 建立一个SignalTapII文件(.stp) 2. 使用MegaWizardPlug In Manager 建立并配置stp文件 v SignalTapII逻辑分析仪器件编程

v v

启动逻辑分析仪并显示捕获的数据

华清远见

Signal TAPII波形实例

华清远见

让我们一起讨论!

成功之路

谢谢!

。