MC2856中文资料

MC33064中文资料

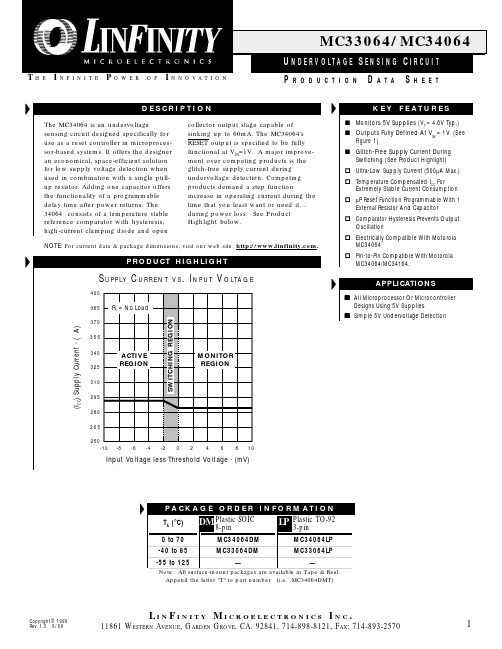

(ICC) Supply Current - ( A)

ACTIVE REGION

MONITOR REGION

-8

-6

-4

-2

0

2

4

6

8

10

Input Voltage less Threshold Voltage - (mV)

PA C K A G E O R D E R I N F O R M A T I O N TA (°C) 0 to 70 -40 to 85 -55 to 125

NOTE: For current data & package dimensions, visit our web site: .

PRODUCT HIGHLIGHT

S U P P LY C U R R E N T

400 385 370 355 340 325 310 295 280 265 250 -10

N.C. N.C. N.C. N.C.

DM PACKAGE (Top View)

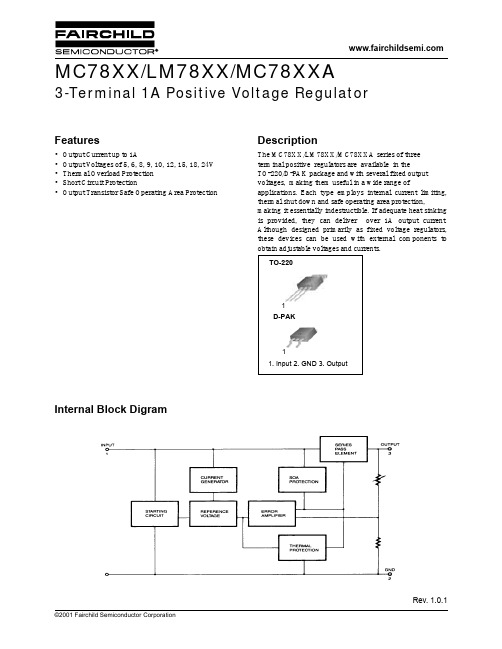

3. GROUND 2. VIN 1. RESET

THERMAL DATA

DM PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA LP PACKAGE: THERMAL RESISTANCE-JUNCTION TO AMBIENT, θJA 156°C/W 165°C/W LP PACKAGE (Top View)

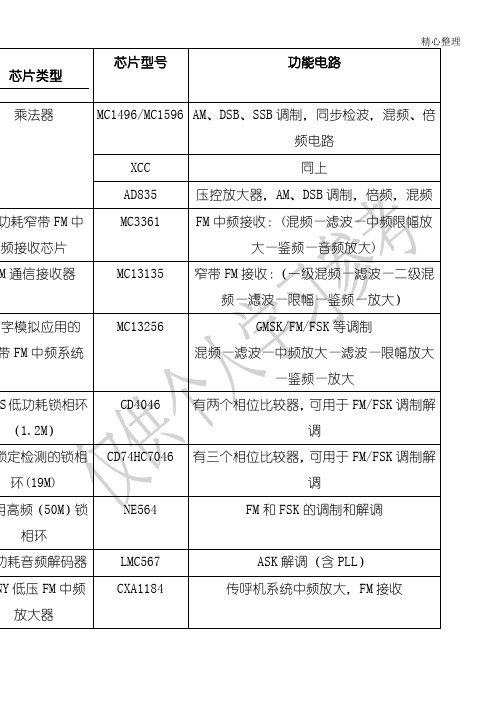

MC1496技术参数中文版(2021年整理精品文档)

MC1496技术参数中文版编辑整理:尊敬的读者朋友们:这里是精品文档编辑中心,本文档内容是由我和我的同事精心编辑整理后发布的,发布之前我们对文中内容进行仔细校对,但是难免会有疏漏的地方,但是任然希望(MC1496技术参数中文版)的内容能够给您的工作和学习带来便利。

同时也真诚的希望收到您的建议和反馈,这将是我们进步的源泉,前进的动力。

本文可编辑可修改,如果觉得对您有帮助请收藏以便随时查阅,最后祝您生活愉快业绩进步,以下为MC1496技术参数中文版的全部内容。

MC1496/MC1496B平衡式调制解调器这类器件用于输出电压是输入电压(信号)和转换电压(载波)乘积场合。

典型应用包括抑制载波调幅,同步检波,FM检波,鉴相器。

更多的应用信息请参照ON半导体公司AN531的应用手册。

特性:1.极佳的载波抑制性能− 65 dB typ @ 0。

5 MHz−50 dB typ @ 10 MHz2.增益和信号处理可调3。

平衡输入和输出4.高共模抑制比典型值为—85dB5.器件内部含有8个三极管6.多种封装形式极限参数(如无特别说明,测试温度为25。

C)评价符号值单位外加电压(v6-v8,v10—v1,v12—v8,v8-v4,v8—v1,v10—v4,v6-v10,v2-v5,v3—v5)V30V不同的输出信号V8-v10V4—V1+5。

0 ±(5+I5Re)V最大偏压I510mA 热敏电阻双列直插式封装R100°C/W工作环境温度范围MC1496MC1496B T A0 to +70 −40to +125°C存储温度范围T stg−65 to +150°C超过极限参数可能会造成器件永久性的损坏。

电气特性(测试条件:(VCC = 12 Vdc, VEE = −8.0 Vdc, I5 = 1.0 mAdc, RL = 3.9 k ,Re = 1。

0 k , TA = Tlow to Thigh),如无特别说明,所有的输入输出均为单极性。

ET80960JA3V252中文资料

80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit MicroprocessorDatasheetProduct Featuress Code Compatible with all 80960Jx ProcessorssHigh-Performance Embedded Architecture —One Instruction/Clock Execution —Core Clock Rate is:1x the Bus Clock for 80960JA/JF/JS 2x the Bus Clock for 80960JD/JC 3x the Bus Clock for 80960JT —Load/Store Programming Model —Sixteen 32-Bit Global Registers—Sixteen 32-Bit Local Registers (8 sets)—Nine Addressing Modes—User/Supervisor Protection Model sTwo-Way Set Associative Instruction Cache—80960JA - 2Kbyte —80960JF/JD - 4Kbyte —80960JS/JC/JT - 16Kbyte —Programmable Cache-Locking MechanismsDirect Mapped Data Cache —80960JA - 1Kbyte —80960JF/JD - 2Kbyte —80960JS/JC/JT - 4Kbyte —Write Through Operation sOn-Chip Stack Frame Cache—Seven Register Sets May Be Saved —Automatic Allocation on Call/Return —0-7 Frames Reserved for High-Priority InterruptssOn-Chip Data RAM—1Kbyte Critical Variable Storage —Single-Cycle Access s3.3V Supply Voltage —5V Tolerant Inputs—TTL Compatible Outputs sHigh Bandwidth Burst Bus—32-Bit Multiplexed Address/Data—Programmable Memory Configuration —Selectable 8-, 16-, 32-Bit Bus Widths —Supports Unaligned Accesses—Big or Little Endian Byte Ordering sHigh-Speed Interrupt Controller —31 Programmable Priorities —Eight Maskable Pins plus NMI#—Up to 240 Vectors in Expanded Mode sTwo On-Chip Timers—Independent 32-Bit Counting —Clock Prescaling by 1, 2, 4 or 8—Internal Interrupt Sources s Halt Mode for Low Powers IEEE 1149.1 (JTAG) Boundary Scan Compatibility sPackages—132-Lead Pin Grid Array (PGA)—132-Lead Plastic Quad Flat Pack (PQFP)—196-Ball Mini Plastic Ball Grid Array (MPBGA)Order Number: 273159-006August 2004INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining applications.Intel may make changes to specifications and product descriptions at any time, without notice.Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.The 80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling1-800-548-4725 or by visiting Intel’s website at .AlertVIEW, AnyPoint, AppChoice, BoardWatch, BunnyPeople, CablePort, Celeron, Chips, CT Connect, CT Media, Dialogic, DM3, EtherExpress, ETOX, FlashFile, i386, i486, i960, iCOMP, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Create & Share, Intel GigaBlade, Intel InBusiness, Intel Inside, Intel Inside logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel Play, Intel Play logo, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel TeamStation, Intel Xeon, Intel XScale, IPLink, Itanium, LANDesk, LanRover, MCS, MMX, MMX logo, Optimizer logo, OverDrive, Paragon, PC Dads, PC Parents, PDCharm, Pentium, Pentium II Xeon, Pentium III Xeon, Performance at Your Command, RemoteExpress, Shiva, SmartDie, Solutions960, Sound Mark, StorageExpress, The Computer Inside., The Journey Inside, TokenExpress, Trillium, VoiceBrick, Vtune, and Xircom are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.*Other names and brands may be claimed as the property of others.Copyright © Intel Corporation, 2002, 2004Contents Contents1.0Introduction (7)2.080960Jx Overview (9)2.180960 Processor Core (10)2.2Burst Bus (11)2.3Timer Unit (11)2.4Priority Interrupt Controller (11)2.5Instruction Set Summary (12)2.6Faults and Debugging (12)2.7Low Power Operation (12)2.8Test Features (12)2.9Memory-Mapped Control Registers (13)2.10Data Types and Memory Addressing Modes (13)3.0Packaging Information (15)3.1Available Processors and Packages (15)3.2Pin Descriptions (16)3.2.1Functional Pin Definitions (16)3.2.280960Jx 132-Lead PGA Pinout (23)3.2.380960Jx 132-Lead PQFP Pinout (27)3.2.480960Jx 196-Ball MPBGA Pinout (30)4.0Electrical Specifications (35)4.1Absolute Maximum Ratings (35)4.2Operating Conditions (35)4.3Connection Recommendations (36)4.4VCC5 Pin Requirements (VDIFF) (36)4.5VCCPLL Pin Requirements (37)4.6 D.C. Specifications (38)4.7 A.C. Specifications (42)4.7.1 A.C. Test Conditions and Derating Curves (45)4.7.1.1Output Delay or Hold vs. Load Capacitance (46)4.7.1.2T LX vs. AD Bus Load Capacitance (47)4.7.1.3ICC Active vs. Frequency (49)4.7.2 A.C. Timing Waveforms (53)5.0Device Identification (59)5.180960JS/JC/JT Device Identification Register (60)5.280960JD Device Identification Register (61)5.380960JA/JF Device Identification Register (62)6.0Thermal Specifications (63)6.1Thermal Management Accessories (68)6.1.1Heatsinks (68)7.0Bus Functional Waveforms (69)7.1Basic Bus States (79)7.2Boundary-Scan Register (80)ContentsFigures180960Jx Microprocessor Package Options (7)280960Jx Block Diagram (10)3132-Lead Pin Grid Array Top View-Pins Facing Down (23)4132-Lead Pin Grid Array Bottom View-Pins Facing Up (24)5132-Lead PQFP - Top View (27)6196-Ball Mini Plastic Ball Grid Array Top View-Balls Facing Down (30)7196-Ball Mini Plastic Ball Grid Array Bottom View-Balls Facing Up (31)8VCC5 Current-Limiting Resistor (36)9VCCPLL Lowpass Filter (37)10 A.C. Test Load (45)11Output Delay or Hold vs. Load Capacitance–80960JS/JC/JT (3.3 V Signals) (46)12Output Delay or Hold vs. Load Capacitance–80960JS/JC/JT (5V Signals) (46)13Output Delay or Hold vs. Load Capacitance–80960JA/JF/JD (47)14T LX vs. AD Bus Load Capacitance–80960JS/JC/JT (3.3V Signals) (47)15T LX vs. AD Bus Load Capacitance–80960JS/JC/JT (5V Signals) (48)16T LX vs. AD Bus Load Capacitance–80960JA/JF/JD (48)17I CC Active (Power Supply) vs. Frequency–80960JA/JF (49)1880960JA/JF I CC Active (Thermal) vs. Frequency (49)1980960JD I CC Active (Power Supply) vs. Frequency (50)2080960JD I CC Active (Thermal) vs. Frequency (50)2180960JC I CC Active (Power Supply) vs. Frequency (51)2280960JC I CC Active (Thermal) vs. Frequency (51)2380960JS I CC Active (Power Supply) vs. Frequency (52)2480960JS I CC Active (Thermal) vs. Frequency (52)25CLKIN Waveform (53)26T OV1 Output Delay Waveform (53)27T OF Output Float Waveform (54)28T IS1 and T IH1 Input Setup and Hold Waveform (54)29T IS2 and T IH2 Input Setup and Hold Waveform (54)30T IS3 and T IH3 Input Setup and Hold Waveform (55)31T IS4 and T IH4 Input Setup and Hold Waveform (55)32T LX, T LXL and T LXA Relative Timings Waveform (56)33DT/R# and DEN# Timings Waveform (56)34TCK Waveform (57)35T BSIS1 and T BSIH1 Input Setup and Hold Waveforms (57)36T BSOV1 and T BSOF1 Output Delay and Output Float Waveform (57)37T BSOV2 and T BSOF2 Output Delay and Output Float Waveform (58)38T BSIS2 and T BSIH2 Input Setup and Hold Waveform (58)3980960JS/JC/JT Device Identification Register Fields (60)4080960JD Device Identification Register Fields (61)4180960JA/JF Device Identification Register Fields (62)42Non-Burst Read and Write Transactions Without Wait States, 32-Bit Bus (69)43Burst Read and Write Transactions Without Wait States, 32-Bit Bus (70)44Burst Write Transactions With 2,1,1,1 Wait States, 32-Bit Bus (71)45Burst Read and Write Transactions Without Wait States, 8-Bit Bus (72)46Burst Read and Write Transactions With 1, 0 Wait Statesand Extra Tr State on Read, 16-Bit Bus (73)47Double Word Read Bus Request, Misaligned One Byte FromQuad Word Boundary, 32-Bit Bus, Little Endian (74)Contents 48HOLD/HOLDA Waveform For Bus Arbitration (75)49Cold Reset Waveform (76)50Warm Reset Waveform (77)51Entering the ONCE State (78)52Bus States with Arbitration (80)53Summary of Aligned and Unaligned Accesses (32-Bit Bus) (84)54Summary of Aligned and Unaligned Accesses (32-Bit Bus) (Continued) (85)Tables180960Jx 3.3-V Microprocessor Family (7)280960Jx Instruction Set (14)380960Jx Processors Available in 132-Pin PGA Package (15)480960Jx Processors Available in 132-Pin PQFP Package (15)580960Jx Processors Available in Extended Temperature (16)680960Jx Processors Available in 196-Ball MPBGA Package (16)7Pin Description Nomenclature (17)8Pin Description—External Bus Signals (18)9Pin Description—Processor Control Signals, Test Signals, and Power (21)10Pin Description—Interrupt Unit Signals (22)11132-Lead PGA Pinout—In Signal Order (25)12132-Lead PGA Pinout—In Pin Order (26)13132-Lead PQFP Pinout—In Signal Order (28)14132-Lead PQFP Pinout—In Pin Order (29)15196-Ball MPBGA Pinout—In Signal Order (32)16196-Ball MPBGA Pinout—In Pin Order (33)17Absolute Maximum Ratings (35)1880960Jx Operating Conditions (35)19VDIFF Parameters (37)2080960Jx D.C. Characteristics (38)2180960Jx I CC Characteristics (39)2280960Jx A.C. Characteristics (42)23Note Definitions for Table 22, 80960Jx AC Characteristics (45)2480960Jx Device Type and Stepping Reference (59)2580960JS/JC/JT Device ID Register Field Definitions (60)2680960JS/JC/JT Device ID Model Types (60)2780960JD Device ID Field Definitions (61)2880960JD Device ID Model Types (61)2980960JA/JF Device ID Field Definitions (62)3080960JA/JF Device ID Model Types (62)31Thermal Resistance for q CA and q JC Reference Table (63)32Maximum Ambient Temperature Reference Table (63)33132-Lead PGA Package Thermal Characteristics (64)3480960JA/JF/JD 196-Ball MPBGA Package Thermal Characteristics (64)3580960JS/JC/JT 196-Ball MPBGA Package Thermal Characteristics (65)36132-Lead PQFP Package Thermal Characteristics (65)37Maximum T A at Various Airflows in °C (80960JT) (66)38Maximum T A at Various Airflows in °C (80960JC) (66)39Maximum T A at Various Airflows in °C (80960JD) (67)40Maximum T A at Various Airflows in °C (80960JS) (67)41Maximum T A at Various Airflows in °C (80960JA/JF) (68)Contents42Boundary-Scan Register—Bit Order (81)43Natural Boundaries for Load and Store Accesses (81)44Summary of Byte Load and Store Accesses (82)45Summary of Short Word Load and Store Accesses (82)46Summary of n-Word Load and Store Accesses (n = 1, 2, 3, 4) (83)Revision HistoryDate Revision DescriptionSeptember 2002005Removed reference to A80960JF-16 from Table 3 on page15. Removed reference to NG80960JC-40, NG80960JC-33, NG80960JS-16,and NG80960JF-16 from Table 4 on page15.Removed reference to GD80960JC-40, GD80960JC-33, and 80960JS-16 in Table 6 on page16.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16, and 80960JF-16 in Table 18 on page35.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16, and 80960JF-16 from Table 21 on page39.Removed reference to 80960JC-40, 80960JC-33, 80960JS-16 and 80960JF-16 from Table 22 on page42.September 1999004Added new extended temp device offerings. See Table 5 on page16. Removed PGA package availability from JS/JC/JT processors. Changed AC timing parameter T OV1 (min) for extended temp devices only.See Table 22 on page42.June 1999003Merged the 80960JS/JC datasheet information into this datasheet (previously named 80960JA/JF/JD/JT 3.3V Embedded 32-Bit Microprocessor datasheet).Updated I CC values for the 80960JS/JC/JT processors. Increased TIH1 specification for the 80960JS/JC/JT processors. Updated MPBGA thermal specifications.December 1998002Corrected orientation of MPBGA package diagrams (Figure 6 on page30 and Figure 7 on page31).Added Figure 11 on page46,Figure 12 on page46,Figure 14 on page47, and Figure 15 on page48 to distinguish 80960JT 3.3-V and 5-V signal derating curves from the 80960JA/JF/JD derating curves.March 1998001This datasheet supersedes revisions to the following 80960Jx datasheets: #273109 (JT), #272971-002 (JD), and #276146-001 (JA/JF). In addition to combining the documents into one, the following content was changed: Figure 1 on page7: Added MPBGA package to diagram.Section 3.2.4, “80960Jx 196-Ball MPBGA Pinout” on page30: Added new Figures 6 and 7, Tables 10, 11 and 13.Figure 16 on page48: Added with the note that follows the figure.August 2004006To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x".80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor1.0IntroductionThis document contains information for the 80960Jx microprocessors, including electrical characteristics and package pinout information. Detailed functional descriptions, other than parametric performance, are published in the i960® Jx Microprocessor Developer’s Manual(272483) and may be viewed online at /design/i960/Techinfo/80960JX/.Throughout this datasheet, references to ‘80960Jx’ indicate features that apply to the 3.3-V Jx processors only:Figure 1. 80960Jx Microprocessor Package Optionsi960®iM©19xxx80960JXXXXXXXXX SS132-Pin PQFPTable 1. 80960Jx 3.3-V Microprocessor FamilyProcessor Voltage Instruction Cache Data Cache Core Clock80960JA 3.3 V (5 V Tolerant) 2 Kbyte 1 Kbyte 1x 80960JF 3.3 V (5 V Tolerant) 4 Kbyte 2 Kbyte 1x 80960JD 3.3 V (5 V Tolerant) 4 Kbyte 2 Kbyte 2x 80960JS 3.3 V (5 V Tolerant)16 Kbyte 4 Kbyte 1x 80960JC 3.3 V (5 V Tolerant)16 Kbyte 4 Kbyte 2x 80960JT3.3 V (5 V Tolerant)16 Kbyte4 Kbyte3xNOTE: To address the fact that many of the package prefix variables have changed, all package prefix variables in this document are now indicated with an "x".This page intentionally left blank.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor 2.080960Jx OverviewThe 80960Jx processor offers high performance to cost-sensitive 32-bit embedded applications.The 80960Jx is object code compatible with the 80960 core architecture and is capable of sustainedexecution at the rate of one instruction per clock. This processor’s features include generousinstruction cache, data cache, and data RAM. It also boasts a fast interrupt mechanism anddual-programmable timer units.The 80960Jx processor’s clock multiplication operates the processor core at two or three times thebus clock rate to improve execution performance without increasing the complexity of boarddesigns.Memory subsystems for cost-sensitive embedded applications often impose substantial wait statepenalties. The 80960Jx integrates considerable storage resources on-chip to decouple CPUexecution from the external bus.The 80960Jx rapidly allocates and de-allocates local register sets during context switches. Theprocessor must flush a register set to the stack only when it saves more than seven sets to its localregister cache.A 32-bit multiplexed burst bus provides a high-speed interface to system memory and I/O. A fullcomplement of control signals simplifies the connection of the 80960Jx to external components.The user programs physical and logical memory attributes through memory-mapped controlregisters (MMRs), an extension not found on the i960® Kx, Sx or Cx processors. Physical andlogical configuration registers enable the processor to operate with all combinations of bus widthand data object alignment. The processor supports a homogeneous byte ordering model.This processor integrates two important peripherals: a timer unit and an interrupt controller. Theseand other hardware resources are programmed through memory-mapped control registers, anextension to the familiar i960 processor architecture.The timer unit (TU) offers two independent 32-bit timers for use as real-time system clocks andgeneral-purpose system timing. These operate in either single-shot or auto-reload mode and maygenerate interrupts.The interrupt controller unit (ICU) provides a flexible, low-latency means for requesting interrupts.The ICU provides full programmability of up to 240 interrupt sources into 31 priority levels. TheICU takes advantage of a cached priority table and optional routine caching to minimize interruptlatency. Clock doubling on the 80960JD/JC processors reduces interrupt latency by 40% comparedto the 80960JA/JF, and clock tripling on the 80960JT reduces interrupt latency by 20% comparedto the 80960JD/JC. Local registers may be dedicated to high-priority interrupts to further reducelatency. Acting independently from the core, the ICU compares the priorities of posted interruptswith the current process priority, off-loading this task from the core. The ICU also supports theintegrated timer interrupts.The 80960Jx features a Halt mode designed to support applications where low power consumptionis critical. The halt instruction shuts down instruction execution, resulting in a power savings of upto 90 percent.The 80960Jx’s testability features, including ONCE (On-Circuit Emulation) mode and BoundaryScan (JTAG), provide a powerful environment for design debug and fault diagnosis.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit MicroprocessorThe Solutions960® program features a wide variety of development tools which support the i960 processor family. Many of these tools are developed by partner companies; some are developed by Intel, such as profile-driven optimizing compilers. For more information on these products, contact your local Intel representative.2.180960 Processor CoreThe 80960Jx family is a scalar implementation of the 80960 core architecture. Intel designed this processor core as a very high performance device that is also cost-effective. Factors that contribute to the core ’s performance include:•Core operates at the bus speed with the 80960JA/JF/JS•Core operates at two or three times the bus speed with the 80960JD/JC and 80960JT,respectively•Single-clock execution of most instructions •Independent Multiply/Divide Unit•Efficient instruction pipeline minimizes pipeline break latency•Register and resource scoreboarding allow overlapped instruction execution •128-bit register bus speeds local register caching •Two-way set associative, integrated instruction cache •Direct-mapped, integrated data cache•1-Kbyte integrated data RAM delivers zero wait state program dataFigure 2. 80960Jx Block DiagramProgrammable Interrupt Controller Control Address/Instruction SequencerPhysical Region Configuration Interrupt Port1K Data RAMMemory Interface Execution Multiply UnitDivide UnitMemory-Mapped Register InterfaceData BusGlobal / Local Register FileSRC2DESTSRC1addressControleffective ConstantsGenerationUnitAddress 32-bit Address 32-bit DataBus Request Queuesand Two 32-BitTimers8-SetLocal Register CacheS R C 1S R C 2D E S TPLL, Clocks,Power MgmtBoundary Scan ControllerTAP 5CLKINS R C 1S R C 2D E S TS R C 1D E S T93232-bit buses address / data21Instruction Cache 80960JA - 2K 80960JF/JD - 4K80960JS/JC/JT - 16KDirect Mapped Data Cache 80960JA - 1K 80960JF/JD - 2K 80960JS/JC/JT -1283 Independent 32-Bit SRC1, SRC2, and DEST BusesBus Control Unit80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor2.2Burst BusA 32-bit high-performance Bus Controller Unit (BCU) interfaces the 80960Jx to external memoryand peripherals. The BCU fetches instructions and transfers data at the rate of up to four 32-bitwords per six clock cycles. The external address/data bus is multiplexed.Users may configure the 80960Jx’s bus controller to match an application’s fundamental memoryorganization. Physical bus width is register-programmed for up to eight regions. Byte ordering anddata caching are programmed through a group of logical memory templates and a defaults register.The BCU’s features include:•Multiplexed external bus to minimize pin count•32-, 16-, and 8-bit bus widths to simplify I/O interfaces•External ready control for address-to-data, data-to-data and data-to-next-address wait state types•Support for big or little endian byte ordering to facilitate the porting of existing program code•Unaligned bus accesses performed transparently•Three-deep load/store queue to decouple the bus from the coreUpon reset, the 80960Jx conducts an internal self-test. Then, before executing its first instruction, itperforms an external bus confidence test by performing a checksum on the first words of theinitialization boot record (IBR).2.3Timer UnitThe timer unit (TU) contains two independent 32-bit timers that are capable of counting at severalclock rates and generating interrupts. Each is programmed by use of the TU registers. Thesememory-mapped registers are addressable on 32-bit boundaries. The timers have a single-shotmode and auto-reload capabilities for continuous operation. Each timer has an independentinterrupt request to the 80960Jx’s interrupt controller. The TU may generate a fault whenunauthorized writes from user mode are detected. Clock prescaling is supported.2.4Priority Interrupt ControllerA programmable interrupt controller manages up to 240 external sources through an 8-bit externalinterrupt port. Alternatively, the interrupt inputs may be configured for individual edge- or level-triggered inputs. The interrupt unit (IU) also accepts interrupts from the two on-chip timer channelsand a single Non-Maskable Interrupt (NMI#) pin. Interrupts are serviced according to their prioritylevels relative to the current process priority.Low interrupt latency is critical to many embedded applications. As part of its highly flexibleinterrupt mechanism, the 80960Jx exploits several techniques to minimize latency:•Interrupt vectors and interrupt handler routines may be reserved on-chip.•Register frames for high-priority interrupt handlers may be cached on-chip.•The interrupt stack may be placed in cacheable memory space.•Interrupt microcode executes at two or three times the bus frequency for the 80960JD/JC and 80960JT, respectively.80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor2.5Instruction Set SummaryThe 80960Jx adds several new instructions to the i960 processor core architecture. The newinstructions are:•Conditional Move•Conditional Add•Conditional Subtract•Byte Swap•Halt•Cache Control•Interrupt ControlTable 2 identifies the instructions that the 80960Jx supports. Refer to the i960® Jx MicroprocessorDeveloper’s Manual (272483) for a detailed description of each instruction.2.6Faults and DebuggingThe 80960Jx employs a comprehensive fault model. The processor responds to faults by makingimplicit calls to a fault handling routine. Specific information collected for each fault allows thefault handler to diagnose exceptions and recover appropriately.The processor also has built-in debug capabilities. In software, the 80960Jx may be configured todetect as many as seven different trace event types. Alternatively, mark and fmark instructionsmay generate trace events explicitly in the instruction stream. Hardware breakpoint registers arealso available to trap on execution and data addresses.2.7Low Power OperationIntel fabricates the 80960Jx using an advanced sub-micron manufacturing process. The processor’ssub-micron topology provides the circuit density for optimal cache size and high operating speedswhile dissipating modest power. The processor also uses dynamic power management to turn offclocks to unused circuits.Users may program the 80960Jx to enter Halt mode for maximum power savings. In Halt mode,the processor core stops completely while the integrated peripherals continue to function, reducingoverall power requirements up to 90 percent. Processor execution resumes from internally orexternally generated interrupts.2.8Test FeaturesThe 80960Jx incorporates numerous features that enhance the user’s ability to test both theprocessor and the system to which it is attached. These features include ONCE (On-CircuitEmulation) mode and Boundary Scan (JTAG).80960JA/JF/JD/JS/JC/JT 3.3 V Embedded 32-Bit Microprocessor The 80960Jx provides testability features compatible with IEEE Standard Test Access Port andBoundary Scan Architecture (IEEE Std. 1149.1).One of the boundary scan instructions, HIGHZ, forces the processor to float all its output pins(ONCE mode). ONCE mode may also be initiated at reset without using the boundary scanmechanism.ONCE mode is useful for board-level testing. This feature allows a mounted 80960Jx toelectrically “remove” itself from a circuit board. This allows for system-level testing in which aremote tester, such as an in-circuit emulator, may exercise the processor system.The provided test logic does not interfere with component or circuit board behavior and ensuresthat components function correctly, connections between various components are correct, andvarious components interact correctly on the printed circuit board.The JTAG Boundary Scan feature is an attractive alternative to conventional “bed-of-nails” testing.It may examine connections that might otherwise be inaccessible to a test system.2.9Memory-Mapped Control RegistersThe 80960Jx, although compliant with the i960 processor core, has the added advantage ofmemory-mapped, internal control registers not found on the i960 Kx, Sx or Cx processors. Theseregisters give software the interface to easily read and modify internal control registers.Each of these registers is accessed as a memory-mapped, 32-bit register. Access is accomplishedthrough regular memory-format instructions. The processor ensures that these accesses do notgenerate external bus cycles.2.10Data Types and Memory Addressing ModesAs with all i960 processors, the 80960Jx instruction set supports several data types and formats:•Bit•Bit fields•Integer (8-, 16-, 32-, 64-bit)•Ordinal (8-, 16-, 32-, 64-bit unsigned integers)•Triple word (96 bits)•Quad word (128 bits)The 80960Jx provides a full set of addressing modes for C and assembly programming:•Two Absolute modes•Five Register Indirect modes•Index with displacement•IP with displacement。

MFW28515T资料

B4-3MFW SERIES 70 WATTSDC/DC C ONVERTERS 28 V OLT I NPUTSize (max.): 3.20 x 2.46 x 0.595 inches (81.3 x 62.5 x 15.11 mm)See Section B8, case L, for dimensions.Weight:140 grams typicalScreening: Standard or ES.See Section C2 for screeningoptions, see Section A5 for ordering information.DESCRIPTIONThe MFW Series™of DC/DC converters offers up to 70 watts of power from single, dual, or triple outputs in one package. Using hybrid thick film technology a power density of over 20 watts per cubic inch is achieved. These devices are packaged in hermetically sealed cold rolled steel enclosures with a tin plate finish making them ideal for use in military, aerospace, or other high reliability applications. Unscreened models are guaranteed to pass a gross leak test (maximum leak rate of 0.001 atm-cc/sec). Environmentally screened units (designated by the /ES suffix) are hermetically solder sealed. See Section C2 for screening specifications.D ESIGN M ETHODOLOGYThe MFW Series converters utilize a quasi-square wave forward converter design with a nominal switching frequency of 245 kHz.Isolation between input and output is provided with a transformer in the forward power loop and a wideband, temperature insensitive optical link in the feedback control loop. Output regulation is accom-plished with constant frequency pulse width modulation. In addition,the load regulation of the single output models is further enhanced through the use of remote output voltage sense pins to overcome the adverse effects of line resistance voltage drops. Short circuit protection is provided by detecting peak primary switching current on a cycle by cycle basis and limiting it to approximately 130% of the full load input current. This method results in quick and positive current limiting under short circuit conditions.L OW N OISEThe MFW Series converters offer low noise on both the input and output lines. A two section, four pole LC input filter is included to provide very low reflected line ripple current. Adherence to MIL-STD-461C (CE03) is possible with the addition of the FMB-461 filter.Output ripple is maintained at less than 50 mV p-p for single and dual output models and 85 mV for triple output models.W IDE V OLTAGE R ANGEAll models of the MFW Series are designed to provide full power operation over an input voltage range of 19 to 40 VDC. Operation below an input of 19 volts, including operation in MIL-STD-704E emergency power conditions, is possible with derated output power.Please refer to the derating information and the low voltage drop-out graphs (Figures 10 and 11) on the following pages.W IDE T EMPERATURE R ANGEFull load operation of any of the MFW Series converters is available at case temperatures of –55°C to + 85°C. Operation up to +125°C is possible with derated output power. The MFW Series converters are provided in a flange mount case designed to facilitate the removal of internally generated heat. Because of this, heat sinking requirements are minimal. Sustained full power operation does however require that an efficient heat sink be attached to the base-plate. Please refer to the heat sink requirements section for more information.I NHIBIT /S YNC F EATUREStandard on all models of the MFW Series is a dual mode inhibit/sync pin. This pin serves as both an output inhibit and as a synchronization input. In the inhibit mode an open collector TTL compatible low (<0.8 V) will disable internal switching thereby inhibiting the unit's output. Inhibiting in this manner results in an extremely low quiescent current. Since a pull-up resistor is included internally, this pin may be left open should the inhibit function not be desired.In a digital system it is often desirable to synchronize the input or output ripple with the system clock. For this reason each model of the MFW Series was designed to synchronize with a system clock applied to the inhibit/sync pin. Please refer to the technical data section for timing details for the external sync feature.F EATURES•–55°C to + 85°C operation •19 to 40 VDC input •Fully Isolated•Optocoupler feedback•Fixed frequency, 245 kHz typical •Topology – Push-Pull Forward•50 V for up to 50 ms transient protection •Inhibit/sync function•Indefinite short circuit protection •Remote sense on single models •Up to 84% efficiencyRECOMMENDED OPERATING CONDITIONSABSOLUTE MAXIMUM RATINGSTYPICAL CHARACTERISTICSB4-4MFW SERIES 70 WATTDC/DC CONVERTERSSINGLE OUTPUTS MFW2805S MFW2812S MFW2815S PARAMETER CONDITION MIN TYP MAX MINTYP MAXMIN.TYPMAXUNITS OUTPUT FULL LOAD 4.95 5.00 5.0511.8812.0012.1214.8515.0015.15VDC VOLTAGE OUTPUT V IN = 19 TO 40——12.00—— 5.83—— 4.67A CURRENT OUTPUT Tc = –55°C TO +85°C ——60——70——70W POWER OUTPUT FULL LOAD BW ≤2 MHz —3050—3050—3050mV p-p RIPPLE LINEV IN = 19 TO 40—1020—1020—1020mV REGULATION LOADNO LOAD TO FULL—1020—1025—1025mV REGULATION INPUT VOLTAGE 192840192840192840VDC INPUT NO LOAD —7590—7090—7090mA CURRENT INHIBITED —3035—3035—3035INPUT REFL.FULL LOAD —1025—1025—1025mA p-p RIPPLEBW ≤10 MHz EFFICIENCY 7880—8183—8183—%STARTUP WITH LOW—510—810—810msDELAYIMPEDANCE SOURCEOutput Power•60 to 70 watts depending on modelLead Soldering Temperature (10 sec per lead)•300°CStorage Temperature Range (Case)•–55°C to +125°COutput Voltage Temperature Coefficient •150 ppm/°C, typicalInput to Output Capacitance •160 pF, typical Isolation•100 megohm minimum at 500 V Conversion Frequency•Free run mode 245 kHz, typical Inhibit Pin Voltage (unit enabled)• 4.5 to 5.5 VElectrical Characteristics:25°C Tc,28 VDC Vin,100% load,free run,unless otherwise specified.Input Voltage Range•19 to 40 VDC continuous (see Derating)Case Operating Temperature (Tc)•–55°C to +85°C full powerSYNC AND INHIBITDERATING OUTPUT POWER/CURRENT AND INPUT VOLTAGESync In (245 to 370 kHz.)•Duty cycle 70% min, 98% max •Logic low 0.8 V max •Logic high 4.5 V min•Referenced to input common•If sync is not used, leave unconnected Inhibit TTL Open Collector •Logic low (output disabled)Inhibit pin current 1 mA max •Referenced to input common •Logic high (output enabled)V = ≥4.5 VTemperatures are referenced to the temperature at the converter’s baseplate •Linearly derate output power/current from 100% at 85°C to 0% at 125°C.•Above 105°C linearly derate steady state input voltage to 33 volts at 125°C.•Indefinite short circuit protection is not guaranteed above 85°C case.•Operation below an input voltage of 19 volts, including operation in MIL-STD-704E emergency power conditions, is possible with derated output power. See Figures 10 and 11.B4-5MFW SERIES70 WATTDC/DC CONVERTERSDUAL AND TRIPLE OUTPUTS MFW2812DMFW2815D MFW28512TMFW28515T PARAMETER CONDITION MINTYPMAXMINTYPMAXMINTYPMAXMINTYPMAXUNITS OUTPUT FULL MAIN —————— 4.95 5.05 5.10 4.90 4.95 5.05VOLTAGELOADDUAL ±11.88±12.00±12.12±14.85±15.00±15.15±11.65±11.80±12.05±15.05±15.30±15.55VDCOUTPUT V IN =MAIN ——————— 4.010.0— 4.010.0A CURRENT 1, 219 TO 40DUAL— 2.92 5.5— 2.33 4.4— 1.67 4.2— 1.33 3.33OUTPUT MAIN ———————2050—2050POWER 1, 2±DUAL —3566.5—3566.5—2050—2050W TOTAL ——70——70——60——60OUTPUT FULL LOAD MAIN ———————5085—5085mV p-p RIPPLEBW ≤2 MHzDUAL —3050—3050—5085—5085LINE V IN =MAIN ———————220—220mV REGULATION 19 TO 40DUAL —1025—1025—100200—100200LOAD 3NO LOAD MAIN ———————520—520mVREGULATION TO FULLDUAL—2550—2550—480600—300450CROSS 4DUAL REGULATION +PO = 3 W TO 35 W–PO = 35 W— 1.5 3.0— 1.5 3.0——————+PO = 20 W TO 50 W %–PO = 50 W TO 20 W—2.04.0—2.03.5——————CROSS 5MAIN +PO = 33 W REGULATION DUAL+PO = 3 W TO 27 W ——————— 2.3 6.0— 2.3 5.0–PO = 27 W TO 3 WMAIN%+PO = 3 W TO 30 W DUAL ±PO = 15 W——————— 5.49.0— 5.07.0INPUT VOLTAGE 192840192840192840192840VDC INPUT NO LOAD —7590—7590—60110—60110mA CURRENT INHIBITED —3035—3035—3035—3035INPUT REFL.FULL LOAD —1540—1540—1540—1540mA p-p RIPPLE BW ≤10 MHzEFFICIENCY 8083—8083—8084—8084—%STARTUP —1525—1525—610—610msDELAYElectrical Characteristics:25°C Tc,28 VDC Vin,100% load,free run,unless otherwise specified.Notes1.On dual output models the maximum combined output power is 70 watts.A maximum of 95% (66.5 W) is available from any single output.2.On triple output models the maximum combined output power is 60 watts.A maximum of 50 watts is available from a single output.3.Balanced loads.4.Regulation effect on the negative dual output during the defined conditions.5.Regulation effect on both dual outputs during the defined conditions.B4-6MFW SERIES 70 WATTDC/DC CONVERTERSC ALCULATING M AXIMUM A MBIENT T EMPERATUREThe MFW Series of DC/DC converters has an upper operating temperature of + 85°C at the baseplate of the case. The degree of heat sinking required to remain within this limit may be determined from Figure 1 which shows the maximum allowed internal power dissipation (P DISS vs. ambient temperature for various heat sink thermal resistances. P DISS may be calculated as: P DISS = P OUT / efficiency – P OUTThe efficiency for all combinations of P OUT and V IN for the various models may be obtained from the graphs on the preceding pages. Example:Converter = MFW2815D, T AMB = 70°C,V IN = 28 VDC, P OUT = 45 watts Efficiency = 85% (From Figure 7)P DISS = (45 / 85) – 45 = 7.95 wattsFrom Figure 1 we can see that this situation will require thermal resistance of approximately 4.5°C / watt.Conversely we may also find the maximum ambient temperature which can be tolerated if we know the heat sink thermal resistance. Example:Converter = MFW2805S, V IN = 28 VDC, P OUT = 45 W.Thermal Resistance = 3°C / watt.Efficiency = 83.5% (From Figure 3)P DISS = (45 / 0.835) – 45 = 8.89 watts.From Figure 1 we can see that the maximum allowed ambient temperature is approximately 75°C.H EAT S INK R ECOMMENDATIONSAn MFW Series converter in still air (other than convective currents)and with no conductive cooling paths other than through electrical connections at the pins will exhibit a thermal resistance of approxi-mately 4°C / watt. In cases where this value proves to be too high it is recommended that additional heat sinking be supplied. The simplest method of accomplishing this is to firmly attach the converter to a PCB thereby providing a conductive thermal path.Secondly it is recommended that airflow be provided over the converter. Although each situation requires a thorough thermal analysis these two measures can reduce the thermal resistance to as low as 2°C / watt. If calculations indicate further heat sinking is required it is recommended that additional thermal mass be provided either under the base plate or on top of the converter's mounting flanges or both.THERMAL MANAGEMENTB4-7MFW SERIES70 WATTDC/DC C ONVERTERSB4-8MFW SERIES 70 WATTDC/DC CONVERTERSTypical Performance Curves:25°C Tc ,28 VDC Vin,100% load,free run,unless otherwise specified.IGUREF IGURE 9IGURE IGURE 20621-001-DTS Rev A DQ# 1016All technical information is believed to be accurate, but no responsibility is assumed for errors or omissions. Interpoint reserves the right to make changes in products or specifications without notice. MFW Series is a trademark of Interpoint.Copyright ©1991- 1999 Interpoint. All rights reserved.C ASESCASE LB8-31CASE L C ASESB8-32C2-12QA SCREENING 85°C PRODUCTSTEST (85°C Products excluding HR products)STANDARD/ESPRE-CAP INSPECTION Method 2017yesyesTEMPERATURE CYCLE (10 times)Method 1010, Cond. B, -55°C to 125°C noyesCONSTANT ACCELERATION Method 2001, 500 g noyesBURN-IN96 hours at 70°C ambient (typical)noyesFINAL ELECTRICAL TEST MIL-PRF-38534, Group A Subgroups 1 and 4: +25°C case yesyesHERMETICITY TESTINGFine Leak, Method 1014, Cond. A no yes Gross Leak, Method 1014, Cond. C no yes Gross Leak, Dip (1 x 10-3)yesnoFINAL VISUAL INSPECTION Method 2009yesyesTest methods are referenced to MIL-STD-883 as determined by MIL-PRF-38534.MFW Series MTW SeriesMHE/MLP Series MHL Series MRH Series MTO Series MSR Series DCH SeriesFM/FMA/FMB EMI Filters MSF EMI Filter85°C P RODUCTSApplies to the following products:。

MC-7856中文资料

ELECTRICAL CHARACTERISTICS (T CASE = 30 °C, V DD = 24 V, Z S = Z I = 75 Ω)PART NUMBER MC-7856G SYMBOLSPARAMETERSUNITS MIN TYP MAX CONDITIONSBW Frequency RangeMHz 50860G A Gain dB 21.523.0 f = 860 MHz S Gain Slope dB 02.050 to 860 MHzGf Gain Flatness dB 1.050 to 860 MHz; Peak to Valley S 11Input Return LossdB 18.050 to 160 MHzdB 17.0160 to 320 MHz dB 16.0320 to 640 MHz dB 14.5640 to 860 MHz S 22Output Return LossdB 18.050 to 160 MHz dB 17.0160 to 320 MHz dB 16.0320 to 640 MHz dB 14.5640 to 860 MHz S 12Reverse IsolationdB 3050 to 860 MHz CTB Composite Triple Beat,110 Channels dB -60-55V OUT = +44 dBmV/ch CSO Composite Second Order, 110 Channels dB -63-55V OUT = +44 dBmV/ch XMod Cross Modulation, 110 Channels dB -63-55V OUT = +44 dBmV/chI DD DC Current mA 220240NFNoise FiguredB 5.3 6.250 MHz dB5.76.5860 MHzCalifornia Eastern LaboratoriesOUTLINE DIMENSIONS (Units in mm)PACKAGE OUTLINEFEATURES•GALLIUM ARSENIDE ACTIVE DEVICES •LOW DISTORTION •LOW NOISE FIGURE (5.7 dB TYP at 860 MHz)•HIGH RELIABILITY(FIT = 125 at heat sink temperature of 100°C,Report available)•INDUSTRY COMPATIBLE PACKAGEDESCRIPTIONThe MC-7856 is a GaAs hybrid integrated circuit designed to be used as the input device in CATV applications up to 860MH z . This unit has a minimum gain of 21.5 dB at 860 MHz,and because it is a GaAs device, it has lower distortion and lower noise figure. Reliability is assured by NEC's stringent quality and process control procedures. Devices are as-sembled and tested using fully automated equipment to maxi-mize the consistency in part to part performance. The MC-7856G features round connection pins and slightly different body dimensions for customers desiring these packaging di-mensions.元器件交易网MC-7856GABSOLUTE MAXIMUM RATINGS 1 (T CASE = 30 °C)SYMBOLSPARAMETERS UNITS RATINGSV DD Supply VoltageV 30V I Input Voltage (Single Tone)dBmV 65T OP Operating Temperature °C -30 to +100T STGStorage Temperature°C-40 to +100Note:1. Operation in excess of any one of these parameters may result in permanent damage.TYPICAL SCATTERING PARAMETERSV DD = 24 VFREQUENCY S 11S 21S 12S 22(MHz)MAG ANG MAGANGMAGANGMAG ANG500.062-165.5011.74-3.982 0.014 -0.058 0.02617.301000.045172.5011.89 -31.570 0.014-23.830 0.049 -31.511500.021 157.4011.94 -54.3000.013-43.140 0.078 -52.402000.00418.3611.97-75.8400.013 -62.090 0.098-65.992500.029-34.0312.06-96.8200.013-80.690 0.119-78.343000.058-41.2612.08-117.7000.012-99.3600.134-87.613500.074-50.8212.10-139.100 0.012-118.6000.137-100.704000.090-60.9812.15-159.4000.012-138.0000.137 -111.904500.085-68.9212.23179.300 0.012 -157.700 0.116-127.805000.076-74.9612.34158.2000.013-177.1000.092-147.005500.059-68.8512.45136.6000.013163.600 0.057 -174.806000.046 -37.7512.55114.6000.013145.8000.036115.306500.066 -19.0412.6092.6600.014128.900 0.04742.647000.100-13.2812.6370.410 0.014 112.7000.08610.897500.132-23.5212.7648.2500.014 96.990 0.109-18.208000.166-34.35 13.03 25.370 0.01382.490 0.130-42.31850 0.191-47.1913.43 1.254 0.013 67.470 0.138-70.149000.205 -66.62 13.78 -25.040 0.01249.570 0.136-97.729500.196-76.9113.63-51.9600.01028.7700.146-111.3010000.220-89.6213.48 -78.8800.00813.2400.184-134.8010500.230-102.3013.34 -108.2000.006-6.1160.210-154.40S 21 MAG:3.0/DIV., 15.00 FS S 12 MAG:0.01/DIV., 0.05 FSEXCLUSIVE NORTH AMERICAN AGENT FOR RF, MICROWAVE & OPTOELECTRONIC SEMICONDUCTORS• Headquarters • 4590 Patrick Henry Drive • Santa Clara, CA 95054-1817 • (408) 988-3500 • Telex 34-6393 • FAX (408) 988-027924-Hour Fax-On-Demand: 800-390-3232 (U.S. and Canada only) • Internet: 05/17/2000DATA SUBJECT TO CHANGE WITHOUT NOTICE元器件交易网。

PC 2856德国拜耳

IEC 60695-11-10

氧指数

27.0 %27.0%

ISO 4589-1/-2

光学性质

公

评论

传输,可见

89.0 %89.0%

ISO 13468-1,-2

加工性能

公

评论

熔体温度

280-320°C280-320°C

300°C300°C

注塑成型; ISO 294

模具温度

80.0°C80.0°C

ISO 1133

力学性能

公

评论

抗拉强度,屈服

66.0MPa66.0兆帕

ISO 527-1/-2

断裂伸长率

>= 50.0 %> = 50.0%

标称ISO 527-1/-2

屈服伸长率

6.10 %6.10%

ISO 527-1/-2

拉伸模量

2.40GPa2.40GPA

ISO 527-1/-2

简支梁冲击缺口

NBNB

热性能

公

评论

线性热膨胀系数,

65.0µm/m-°C65.0μm/m-°C

平行ISO 11359-1/-2

热膨胀系数,线性,横向流动

65.0µm/m-°C65.0μm/m-°C

ISO 11359-1/-2

比热容

1.70J/g-°C1.70J/g-°C

融化

热传导率

0.173W/mK0.173W / mK的

IEC 60093

表面电阻

>=1.00e+15ohm> =1.00E +15欧姆。

IEC 60093

介电常数

3.003.00

IEC 60250

CS5366-CQZ;CS5366-DQZ;CS5366-CQZR;CS5366-DQZR;中文规格书,Datasheet资料

114 dB, 192 kHz, 6-Channel A/D ConverterFeatures♦Advanced Multi-bit Delta-Sigma Architecture ♦24-Bit Conversion ♦114 dB Dynamic Range ♦-105 dB THD+N♦Supports Audio Sample Rates up to 216 kHz ♦Selectable Audio Interface Formats–Left-Justified, I²S, TDM–6-Channel TDM Interface Formats♦Low Latency Digital Filter♦Less than 535 mW Power Consumption ♦On-Chip Oscillator Driver♦Operation as System Clock Master or Slave ♦Auto-Detect Speed in Slave Mode ♦Differential Analog Architecture♦Separate 1.8 V to 5 V Logic Supplies forControl and Serial Ports♦High-Pass Filter for DC Offset Calibration ♦Overflow Detection♦Footprint Compatible with the 8-ChannelCS5368Additional Control Port Features♦Supports Standard I²C™ or SPI™ ControlInterface♦Individual Channel HPF Disable♦Overflow Detection for Individual Channels ♦Mute Control for Individual Channels♦Independent Power-Down Control per ChannelPairCS5366DescriptionThe CS5366 is a complete 6-channel analog-to-digital converter for digital audio systems. It performs sampling, an-alog-to-digital conversion, and anti-alias filtering, generating 24-bit values for all 6-channel inputs in serial form at sample rates up to 216 kHz per channel.The CS5366 uses a 5th-order, multi-bit delta sigma modulator followed by low latency digital filtering and decima-tion, which removes the need for an external anti-aliasing filter. The ADC uses a differential input architecture which provides excellent noise rejection.Dedicated level translators for the Serial Port and Control Port allow seamless interfacing between the CS5366 and other devices operating over a wide range of logic levels. In addition, an on-chip oscillator driver provides clocking flexibility and simplifies design.The CS5366 is the industry’s first audio A/D to support a high-speed TDM interface which provides a serial output of 6 channels of audio data with sample rates up to 216 kHz within a single data stream. It further reduces layout complexity and relieves input/output constraints in digital signal processors.The CS5366 is available in a 48-pin LQFP package in both Commercial (-40°C to 85°C) and Automotive grades (-40°C to +105°C). The CDB5366 Customer Demonstration board is also available for device evaluation and implementation suggestions. Please see “Ordering Information” on page 41 for complete ordering information.The CS5366 is ideal for high-end and pro-audio systems requiring unrivaled sound quality, transparent conversion, wide dynamic range and negligible distortion, such as A/V receivers, digital mixing consoles, multi-channel record-ers, outboard converters, digital effect processors, and automotive audio systems.TABLE OF CONTENTS1. PIN DESCRIPTION (6)2. TYPICAL CONNECTION DIAGRAM (9)3. CHARACTERISTICS AND SPECIFICATIONS (10)RECOMMENDED OPERATING CONDITIONS (10)ABSOLUTE RATINGS (10)SYSTEM CLOCKING (10)DC POWER (11)LOGIC LEVELS (11)PSRR, VQ AND FILT+ CHARACTERISTICS (11)ANALOG CHARACTERISTICS (COMMERCIAL) (12)ANALOG CHARACTERISTICS (AUTOMOTIVE) (13)DIGITAL FILTER CHARACTERISTICS (14)OVERFLOW TIMEOUT (14)SERIAL AUDIO INTERFACE - I²S/LJ TIMING (15)SERIAL AUDIO INTERFACE - TDM TIMING (16)SWITCHING SPECIFICATIONS - CONTROL PORT - I²C TIMING (17)SWITCHING SPECIFICATIONS - CONTROL PORT - SPI TIMING (18)4. APPLICATIONS (19)4.1 Power (19)4.2 Control Port Mode and Stand-Alone Operation (19)4.2.1 Stand-Alone Mode (19)4.2.2 Control Port Mode (19)4.3 Master Clock Source (20)4.3.1 On-Chip Crystal Oscillator Driver (20)4.3.2 Externally Generated Master Clock (20)4.4 Master and Slave Operation (21)4.4.1 Synchronization of Multiple Devices (21)4.5 Serial Audio Interface (SAI) Format (22)4.5.1 I²S and LJ Format (22)4.5.2 TDM Format (23)4.5.3 Configuring Serial Audio Interface Format (23)4.6 Speed Modes (23)4.6.1 Sample Rate Ranges (23)4.6.2 Using M1 and M0 to Set Sampling Parameters (23)4.6.3 Master Mode Clock Dividers (24)4.6.4 Slave Mode Audio Clocking With Auto-Detect (24)4.7 Master and Slave Clock Frequencies (25)4.8 Reset (27)4.8.1 Power-Down Mode (27)4.9 Overflow Detection (27)4.9.1 Overflow in Stand-Alone Mode (27)4.9.2 Overflow in Control Port Mode (27)4.10 Analog Connections (28)4.11 Optimizing Performance in TDM Mode (29)4.12 DC Offset Control (29)4.13 Control Port Operation (30)4.13.1 SPI Mode (30)4.13.2 I²C Mode (31)5. REGISTER MAP (32)5.1 Register Quick Reference (32)5.2 00h (REVI) Chip ID Code & Revision Register (32)5.3 01h (GCTL) Global Mode Control Register (32)5.4 02h (OVFL) Overflow Status Register (33)5.5 03h (OVFM) Overflow Mask Register (33)5.6 04h (HPF) High-Pass Filter Register (34)5.7 05h Reserved (34)5.8 06h (PDN) Power Down Register (34)5.9 07h Reserved (34)5.10 08h (MUTE) Mute Control Register (34)5.11 09h Reserved (35)5.12 0Ah (SDEN) SDOUT Enable Control Register (35)6. FILTER PLOTS (36)7. PARAMETER DEFINITIONS (39)8. PACKAGE DIMENSIONS (40)THERMAL CHARACTERISTICS (40)9. ORDERING INFORMATION (41)10. REVISION HISTORY (41)LIST OF FIGURESFigure 1. CS5368 Pinout (6)Figure 2. Typical Connection Diagram (9)Figure 3. I²S/LJ Timing (15)Figure 4. TDM Timing (16)Figure 5. I²C Timing (17)Figure 6. SPI Timing (18)Figure 7. Crystal Oscillator Topology (20)Figure 8. Master/Slave Clock Flow (21)Figure 9. Master and Slave Clocking for a Multi-Channel Application (21)Figure 10. I²S Format (22)Figure 11. LJ Format (22)Figure 12. TDM Format (23)Figure 13. Master Mode Clock Dividers (24)Figure 14. Slave Mode Auto-Detect Speed (24)Figure 15. Recommended Analog Input Buffer (28)Figure 16. SPI Format (30)Figure 17. I²C Write Format (31)Figure 18. I²C Read Format (31)Figure 19. SSM Passband (36)Figure 20. DSM Passband (36)Figure 21. QSM Passband (36)Figure 22. SSM Stopband (37)Figure 23. DSM Stopband (37)Figure 24. QSM Stopband (37)Figure 25. SSM -1 dB Cutoff (38)Figure 26. DSM -1 dB Cutoff (38)Figure 27. QSM -1 dB Cutoff (38)LIST OF TABLESTable 1. Power Supply Pin Definitions (19)Table 2. DIF1 and DIF0 Pin Settings (23)Table 3. M1 and M0 Settings (23)Table 4. Frequencies for 48 kHz Sample Rate using LJ/I²S (25)Table 5. Frequencies for 96 kHz Sample Rate using LJ/I²S (25)Table 6. Frequencies for 192 kHz Sample Rate using LJ/I²S (25)Table 7. Frequencies for 48 kHz Sample Rate using TDM (25)Table 8. Frequencies for 48 kHz Sample Rate using TDM (25)Table 9. Frequencies for 96 kHz Sample Rate using TDM (26)Table 10. Frequencies for 96 kHz Sample Rate using TDM (26)Table 11. Frequencies for 192 kHz Sample Rate using TDM (26)Table 12. Frequencies for 192 kHz Sample Rate using TDM (26)1.PIN DESCRIPTION ArrayFigure 1. CS5366 PinoutPin Name Pin #Pin DescriptionAIN2+, AIN2-AIN4+, AIN4-AIN3+, AIN3-AIN6+, AIN6-AIN5+, AIN5-AIN1+, AIN1-1,211,1213,1443,4445,4647,48Differential Analog (Inputs) - Audio signals are presented differently to the delta sigma modula-tors via the AIN+/- pins.GND3,810,1516,1718,1929,32Ground (Input) - Ground reference. Must be connected to analog ground.VA4,9Analog Power (Input)- Positive power supply for the analog sectionREF_GND5Reference Ground (Input) - For the internal sampling circuits. Must be connected to analog ground.FILT+6Positive Voltage Reference (Output) - Reference voltage for internal sampling circuits. VQ7Quiescent Voltage (Output) - Filter connection for the internal quiescent reference voltage.VX20Crystal Oscillator Power (Input) - Also powers control logic to enable or disable oscillator cir-cuits.XTI XTO 2122Crystal Oscillator Connections (Input/Output) - I/O pins for an external crystal which may be used to generate MCLK.MCLK23System Master Clock (Input/Output) - When a crystal is used, this pin acts as a buffered MCLK Source (Output). When the oscillator function is not used, this pin acts as an input for the system master clock. In this case, the XTI and XTO pins must be tied low.LRCK/FS24Serial Audio Channel Clock (Input/Output)In I²S mode Serial Audio Channel Select. When low, the odd channels are selected.In LJ mode Serial Audio Channel Select. When high, the odd channels are selected.In TDM Mode a frame sync signal. When high, it marks the beginning of a new frame of serial audio samples. In Slave Mode, this pin acts as an input pin.SCLK25Main timing clock for the Serial Audio Interface (Input/Output) - During Master Mode, this pin acts as an output, and during Slave Mode it acts as an input pin.TSTO26Test Out (Output) - Must be left unconnected.SDOUT227Serial Audio Data (Output) - Channels 3,4VLS28Serial Audio Interface Power - Positive power for the serial audio interface.SDOUT1/TDM30Serial Audio Data (Output) - Channels 1,2, TDM.SDOUT3/TDM31Serial Audio Data (Output) - Channels 5,6, TDM is complementary TDM data.VD33Digital Power (Input) - Positive power supply for the digital section.VLC35Control Port Interface Power - Positive power for the control port interface.OVFL36Overflow (Output, open drain) - Detects an overflow condition on both left and right channels.RST41Reset (Input) - The device enters a low power mode when low.Stand-Alone ModeCLKMODE34CLKMODE(Input) - Setting this pin HIGH places a divide-by-1.5 circuit in the MCLK path to the core device circuitry.DIF1 DIF03738DIF1, DIF0 (Input) - Sets the serial audio interface format.M1 M03940Mode Selection (Input) - Determines the operational mode of the device.MDIV42MCLK Divider (Input) - Setting this pin HIGH places a divide-by-2 circuit in the MCLK path to the core device circuitry.Control Port ModeCLKMODE34CLKMODE (Input) - This pin is ignored in Control Port Mode and the same functionality is obtained from the corresponding bit in the Global Control Register. Note: Should be connected to GND when using the part in Control Port Mode.AD1/CDIN37I²C Format, AD1 (Input) - Forms the device address input AD[1]. SPI Format, CDIN (Input) - Becomes the input data pin.AD0/CS38I²C Format, AD0 (Input) - Forms the device address input AD[0]. SPI Format, CS (Input) - Acts as the active low chip select input.SCL/CCLK39I²C Format, SCL (Input) - Serial clock for the serial control port. An external pull-up resistor is required for I²C control port operation.SPI Format, CCLK (Input) - Serial clock for the serial control port.SDA/CDOUT40I²C Format SDA (Input/Output) - Acts as an input/output data pin. An external pull-up resistor is required for I²C control port operation.SPI Format CDOUT (Output) - Acts as an output only data pin.MDIV42MCLK Divider (Input) - This pin is ignored in Control Port Mode and the same function-ality is obtained from the corresponding bit in the Global Control Register.Note: Should be connected to GND when using the part in Control Port Mode.2.TYPICAL CONNECTION DIAGRAM Array Figure 2. Typical Connection DiagramFor analog buffer configurations, refer to Cirrus Application Note AN241. Also, a low-cost single-ended-to-differen-tial solution is provided on the Customer Evaluation Board.3.CHARACTERISTICS AND SPECIFICATIONS RECOMMENDED OPERATING CONDITIONSGND = 0 V, all voltages with respect to 0 V.1.TDM Quad-Speed Mode specified to operate correctly at VLS ≥ 3.14 V.ABSOLUTE RATINGSOperation beyond these limits may result in permanent damage to the device. Normal operation is not guaranteed at these extremes. Transient currents up to ±100 mA on the analog input pins will not cause SCR latch-up.SYSTEM CLOCKINGParameterSymbol MinTypMax UnitDC Power Supplies:Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control LogicVA VX VD VLS VLC 4.754.753.141.7111.71 5.05.03.33.33.3 5.25VAmbient Operating Temperature(-CQZ) (-DQZ)T AC T AA-40-40--85105°CParameterSymbolMin Typ Max UnitsDC Power Supplies:Positive Analog Positive Crystal Positive Digital Positive Serial Logic Positive Control LogicVA VX VD VLS VLC -0.3-+6.0VInput Current I in -10-+10mA Analog Input Voltage V IN -0.3VA+0.3V Digital Input VoltageV IND VL+0.3Ambient Operating Temperature (Power Applied)T A -50+125°CStorage TemperatureT stg-65+150ParameterSymbolMinTyp MaxUnitInput Master Clock Frequency MCLK 0.51255.05MHz Input Master Clock Duty Cyclet clkhl4060%分销商库存信息:CIRRUS-LOGICCS5366-CQZ CS5366-DQZ CS5366-CQZR CS5366-DQZR。

MC88916中文资料

MC88916OUTLINE DIMENSIONSMotorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. “Typical” parameters can and do vary in different applications. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.Motorola and are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.How to reach us:USA/EUROPE: Motorola Literature Distribution; JAPAN: Nippon Motorola Ltd.; T atsumi–SPD–JLDC, T oshikatsu Otsuki,P.O. Box 20912; Phoenix, Arizona 85036. 1–800–441–2447 6F Seibu–Butsuryu–Center, 3–14–2 T atsumi Koto–Ku, T okyo 135, Japan. 03–3521–8315 MFAX: RMFAX0@ –TOUCHTONE (602) 244–6609HONG KONG: Motorola Semiconductors H.K. Ltd.; 8B T ai Ping Industrial Park, INTERNET: http://Design–51 Ting Kok Road, T ai Po, N.T., Hong Kong. 852–26629298。

2855中文资料

Zoom® ComStar TM 56KSpeakerPhone/FaxModemA Complete CommunicationsCenter For Your Computer!The Zoom ComStar 56K Model 2818 for PC-compatible computers combines a full-featured V.34modem capable of 56,000 Kbps Internet and centralsite downloads with a powerful voice mail system,digital answering machine, 14,400 bps fax, convenientspeed dialer, and a synchronous interface supportingthe ITU H.324 videophone technology standard. It isPlug and Play compatible for easy installation underMicrosoft® Windows® 95 and is also softwareconfigurable.The Zoom ComStar 56K comes complete with a high-quality external microphone and speaker. It comeswith Cheyenne® BitWare® Fax/Voice/Data forWindows; ZOOM/LINK® CD-ROM with modem-enabled games, conferencing software, supportinformation, and more.About the Zoom ComStar 56KZoom ComStar 56K Speakerphone/FaxModem transforms your ordinary computer into anextraordinary telecommunications tool. ComStar 56K (internal) Model 2818 for PC-compatible computers is a high-speed V.34 faxmodem that can download data from compatible sites atspeeds up to 56,000 bps and at higher speeds with compression for fast Internet and LAN access.It combines a full-featured K56flex TM faxmodem, 14,400 bps fax, and full-duplex speakerphone over conventional telephone lines and features flash memory and reprogrammable DSP fordownloading feature enhancements and upgrades to future standards with simple softwarecommands. Other advanced features include a synchronous interface supporting the ITU H.324 videophone technology standard,* digital answering machine, voice mail, convenient speeddialer, and Plug-and-Play compatibility for easy installation. The Zoom ComStar 56K comescomplete with a high-quality external microphone and speaker, and all necessary software. ComStar 56K is built in the U.S.A. by Zoom Telephonics, Inc., a leading supplier of telecommunications equipment since 1977 and is backed by Zoom's outstanding 7-year warranty. Featuresr K56flex technology for 56,000 bps data downloads from compatible sitesr33,600 bps V.34 data transmission speedr14,400 bps Group 3, Class 1 and 2 faxr V.42bis and MNP 5 compression for data speeds up to 230,400 bpsr Reprogrammable Digital Signal Processor (DSP) enables easy software upgradeability to assure superior interoperability and overall performance and easy upgrades to futurestandards.r Flash memory for easy firmware upgradesr56K Faxmodem: Connect to the Internet, World Wide Web and on-line services, anddownload files fast and error-free at up to 56,000 bps with K56flex, the joint development of Rockwell and Lucent Technologies. Send "printer-quality" faxes direct from your PC, plus faxback and fax-on-demand.r Speakerphone: For "hands-free" communications and conference calls. True full-duplex speakerphone lets callers on both ends talk at the same time for natural conversation.r Videophone-Ready: Supports the ITU H.324 video technology standard and H.324compliant software from Intel, PictureTel, VDONet, Smith Micro, and others.*r Digital Answering Machine: An easy-to-use personal answering machine with high-quality recording and playback, pager notification, and other advanced features.r Voice Mail: A full-featured, configurable voice mail system for home or office withmultiple mailboxes, fax-on-demand, and remote retrieval of messages.r Other Features: Plug-and-Play with Windows 95 computers (software configurable also), VoiceView® compatibility, Directory Dialing, Distinctive Ring,** Caller ID,** andZoomGuard lightning protection.Technical SpecificationsData Speeds:r300 to 33,600 bps full-duplex with international standardsr Up to 56,000 bps receive/33,600 bps send with K56flexFax Speeds:r 300 to 14,400 bpsr Group 3, Class 1 and Class 2Standards Supported:r Data: K56flex, V34, V.32bis, V.32, V.22bis, V.22 A/B, V.22, V.23, V.21, Bell 103/212Ar Fax: V.33, V.29, V.17, V.27ter, V.21 channel 2Compression: V.42bis, MNP 5r Error Control: V.42, MNP 2 - 4, MNP 10 and MNP 10ECr Plug and Playr AT and extended AT command set compatibleCommand Set:Hayes AT-Command compatible, with extended MNP 5, MNP 10, and V.42bis commandsVoice Encoding:Enhanced ADPCM, programmable at 2 or 4 bits per sampleSpeakerphone:Full-duplex with microphone and speaker included; headset capability; software volume controlInterface:Plug and Play; COM1 - COM8, IRQ, 3, 4, 5, 7, 9, 10, 12, 15 supports TAPIVideoconferencing enabled:Synchronous interface supports ITU H.324 standard for videoconferencing applications.*Hardware Features:r Dual RJ-11 telephone jacks one for phone line, one for optional phoner Output jack for external 8 ohm audio speaker (8 ohm external speaker included)r Input jack for external microphone (microphone included)r Jumper-selectable electret microphone biasr Telephone cable with RJ-11 connectorsr Buffered 16550 UART to reduce PC interrupts and boost performancer Handset record and playbackDimensions and Power Requirements:r Dimensions: standard IBM PC board 2.7 in. W by 5.4 in. L by 0.75 in. H (fits 16-bit PC-compatible slot)r Power consumption: 1.5W typicalSystem Requirements:r486 or faster PC compatible computer with 1 available 16-bit ISA slotr8 MB RAMr 3.5 in. floppy driver Hard drive with a minimum of 5 MB available r Microsoft Windows 3.1 or higherr Mouse recommendedRegulatory Approvals:rFCC Parts 15B and 68 r UL, C-ULr Industry CanadaWarranty:Warranted against defects in material andworkmanship for a period of seven years from the date of original retail purchase* Requires video camera and video capture support, sound card with microphone input, ITU H.324-compliant videoconferencing application, and appropriate computer and operating system to run the application.** Requires Distinctive Ring or Caller ID support from local telephone company.Zoom Telephonics, Inc.207 South Street Boston, MA 02111617 423-1072800 631-3116Fax: 617 423-3923Web Site: BBS: 617 423-3733Nasdaq: ZOOMZoom is a registered trademark and ComStar, Zoom/FaxModem, ZoomGuard are trademarks of Zoom Telephonics, Inc. K56flex is a trademark of Rockwell International Corporation and Lucent Technologies, Inc. Windows is a registered trademark of Microsoft. MNP is a registered trademark and MNP 10EC is a trademark of Microcom Inc. All other registered trademarks and trademarks are the property of their respective owners.Made in the U.S.A.©2000 Zoom Telephonics, Inc.1777。

MC7806A中文资料