基于CPCI总线的雷达信号处理系统

让军用存储不再瓶颈

让军用存储不再有瓶颈!目前在航空、航天、通信等各军用领域中,数据存储设备都有着广泛的需求和应用,因应用环境和性能的需求不同,物理实现方法也各不相同。

伴随着科学技术水平的提高,尤其是在航空、航天等领域的迅猛发展,无论是星载、弹载还是箭载飞行器飞行过程中需要记录的参数越来越多,数据产生速度越来越高,需要记录的数据量也不断提高,这就要求数据存储设备拥有更高的性能。

同时因高空飞行器一般环境恶劣、空间有限、对所载设备的功耗和重量有严格的限制条件,所以要求数据存储设备还需要具有功耗低、体积小、重量轻、耐高压、工作温度范围广和抗高冲击过载的特点。

因此体积小、容量大、带宽高、耐压强度大、抗冲击震动以及抗磁干扰的小型化存储设备成为航空航天数据存储领域的迫切需求,恒润科技为了满足航空航天等领域关于存储设备的各种需求,恒润科技自主研制、开发了如下系列业界具备一定优势的高带宽、大容量、稳定可靠的数据存储系统。

1)P系列高速采集、存储系统;2)C系列高速采集、存储系统;3)V系列高速采集、存储系统。

1.P系列高速采集、存储系统1)产品简介P系列高速采集、存储系统是恒润科技基于PCIe总线开发的高速信号采集、处理、存储、回放系统级产品。

该产品采用模块化设计和标准PCIe总线架构,易扩展,高可用,可实现高、低速模拟信号及光纤信号的数据采集,同时通过系统内高性能DSP,可以在数据存储的同时并行进行数字信号处理。

通过恒润科技自主研发的PCIe光纤通讯设备和高性能磁盘阵列控制器可使数据回放实测带宽达到2.6GBps。

2)产品特性☐模拟信号采集频率5GHz;☐支持突发存储和连续存储两种模式;☐实测存储写速度2.2GBps;☐实测存储读速度2.6GBps;☐支持数据转储,转储带宽1.6GBps。

☐提供数据在线播放、记录功能软件;☐提供数据回放、分析等功能软件。

3)应用领域☐雷达;☐声纳;☐无线电监控;☐视频采集;☐通信;☐电子对抗等。

基于CPCI总线架构设计的实时图像信号处理平台

鼻材 t

F GA 混 用 的硬 件 系 P

统 就 把 两 者 的 优 点 结 部空间: 支持 2 U 4槽 CP 背板: CI 支持 2个 3 U

合到一起 ,即兼顾 了 C C 电源 。箱体背部双 电源输入接口 , PI 通断式

鼻材 号

支持常开) 。以便响应断 电后 系统重启的 速 度 和 灵 活 性 ,又 满 开关( 足了底层信号处理和 要 求 。

维普资讯

d

3 C 电 源 支 持 U CP I

栏编 I 韩 辑} 目

汝水I I

1 槽空间 ;支持 PC I MG21 .热插拔规范。

板上 D P和 F G 各 自带 有 R S PA AM ,用 于

热 插 拔 ;采 用 和 系统 一

研华科技 龠晓仲

摘要: 本 文 主 要 介 绍 了基 于C C 总 线 设 计 的 实 时信 号处 理 业 务 所 高 层信号处理的要求 。因此,非常适合实时信 PI

需的一种专 用设备平 台。

关键 词 : C C BU P I S;平 台 ;实 时信 号 处 理 ;DS + P P F GA

C CI P 目前最高传输速 度5 8 /, 2 MBs 可用的

频 信 号 的实 时 图 像 处 理 ,D P实现 了部 分 的 图 P I S C —x的最高传输速度可达 16 MB s 0 6 /。

像处理算法和F G P A的控制逻辑 , 并响应中断 ,

实 现 数 据通 信和 存储 实时 信 号 。

座 : 1 P , 3 P , 5 P ,' P, 4 P。 2

出数据 。 我们采用了P MC卡来解决。 MC P P (CI

P1P ,2为 标 准 P I提 供 Meznn ad) 范 IE 8 出 了 m za C, zai eC r 规 E E 1 6给 3 ez.

基于CPCI总线的高速数据记录系统设计

Ke r s y wo d :CPCI DM A; i e ; ; Dr r pC1 0 4 d t e o d v 9 5 ; a rc r a

P 邱 hr mp n n t cn et ( P ) u— ae s m f eoddt rcp o . ei ̄ d c h s m o oio n e ea Co o et ne o nc C CI b s bs s t o cr a eet n W o u etes t cmp s nad l I r d ye r a i n ye i t

4 7

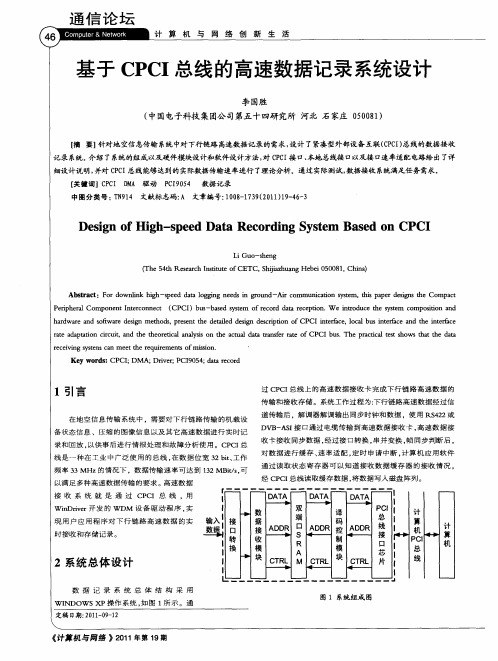

3硬 件 设 计

31C C 接 口 . P I

CP I 术 是 在 周边 元件 扩 展接 口( CI技 术 基 础 上 , C技 P ) 对 板 卡 的机 械 结 构 和 连接 方 式 改 进 而成 ,电气 特 性 与 P I 全 C完

相 同 。 C 总 线 模 块 由 P 10 4来 实现 。 C 9 5 P I C 95 P I0 4是一 个 3 2位 3 3 MHz 总线 主 控 I0 加 速 器 , 实 现 P I . 规 范 的要 求 。 1 能 C 22版 P 95 CI0 4作 为桥 接芯 片 ,在 P I 线 和 L cl 线 之 间 有 P C 总 oa总 CI

定 稿 日期 : 01 0— 2 2 1- 9 1

模 A 块 儿 I C R M C R 丁 L T L C R 片 I T L

l

总 线

机

I

I

图 1 系统组 成 图

《 计算机与网络 》2 1 年第 1 期 01 9

cPCI总线

摘要:介绍了基于cPCI总线的新一代嵌入式遥测前端处理器的体系结构设计和通用OEM硬件选择,重点介绍了多功能双路PcM分路器板的设计与实现,简述了遥测前端处理器中的软件。

关键词:嵌入式遥测前端处理器cPCI总线分路器遥测数据处理系统在航空、航天等军工试验领域有着广泛的应用。

在航空飞行试验中.遥测数据处理系统为各类试飞测试数据的实时处理提供了手段和平台,是试飞员、试飞指挥员及试飞工程师协同完成新机试飞必不可少的重要设施,是确保现代飞机试飞安全、提高试飞效率、缩短试飞周期、实现综合试飞的重要手段。

遥测数据处理系统中的核心设备——遥测前端处理器,技术上经历了从分立式、智能式到嵌入式的快速发展。

我国遥测前端处理器的研发经历了从引进、合作研制到完全自行研制的历程。

遥测前端处理器是一套嵌入式实时计算机系统,承担着遥测PCM数据的同步、分路、工程单位转换、数据计算、数据分配等实时处理任务。

它和遥测系统管理服务器、工作站等设备通过网络联接和系统集成,组成当前流行的基于C/S结构的遥测数据处理系统。

可以说,遥测前端处理器的技术水平代表了遥测数据处理系统的技术水平。

1 系统功能和主要技术指标遥测前端处理器的功能简单地说,就是把来自遥测接收设备送来的多路串行PCM(Pulse Code Modulati on)数据流进行同步、分路、合并、存储,并对转换后的并行数据进行工程单位转换、导出参数计算等实时处理,通过网络把数据传送给显示工作站。

再通过遥测记录数据重放,为用户提供同实时方式一样的处理功能和更为详细的数据分析功能。

遥测前端处理器主要技术指标为:(1)可同时完成2路PCM数据流的同步和分路,每路PCM速率不大于20Mbps。

(2)实时数据处理速率:20Mbps。

(3)数据传输:交换式以太网、网络带宽1000Mbps、广播方式和“点对点”方式。

(4)数据存储:满足在最大速率下数据存储不丢失,磁盘容量满足不小于4小时的记录时间。

基于TMS320C667x和VPX的雷达处理系统设计及应用

基于TMS320C667x和VPX的雷达处理系统设计及应用宋玉霞;李贵;甘峰;邵江雨【摘要】针对基于CPCI或VME构建的雷达信号处理系统数传和处理能力的瓶颈,提出了一种以TI公司多核DSP TMS320C667x为核心处理器、基于VPX架构的高端高速雷达实时信号处理系统,介绍了系统的软硬件架构设计、电气结构设计、背板拓扑结构设计以及在雷达SAR成像处理模式、单脉冲处理模式的应用软件设计。

工程应用中的测试结果表明,该系统具有比传统信号处理系统更高的处理性能和与高性能相匹配的高速数传网络,应用前景广阔。

%For radar processing systems based on CPCI or VME,the data transmission and processing capability is a bottleneck.To address this issue,the design of a highlyreal⁃time processor based on multi⁃core DSP TMS320C667x from TI and VPX is presented,the design of software,hardware,electric structure and backplane topological structure is introduced,and the applications in SAR imaging and monopulse processing are proposed. The testing results in engineering application shown that this system has a better processing performance than traditional signal processor and a high⁃speed data transmission network matching with its high performance,and it has a good prospect of application.【期刊名称】《无线电工程》【年(卷),期】2016(046)011【总页数】4页(P71-74)【关键词】处理系统;TMS320C667x;VPX;SAR成像处理;单脉冲处理【作者】宋玉霞;李贵;甘峰;邵江雨【作者单位】中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036;中国西南电子技术研究所,四川成都610036【正文语种】中文【中图分类】TN958.94过去10多年,雷达信号处理系统常采用TigerSHARC系列DSP或PowerPC系列CPU基于CPCI或VME总线进行构建。

《2024年基于CPCI总线的国产化多功能通信模块的研制》范文

《基于CPCI总线的国产化多功能通信模块的研制》篇一一、引言随着信息化技术的迅猛发展,各领域对通信模块的要求愈发严格,尤其是对数据传输速率、实时性以及稳定性等方面的要求更是日新月异。

为了满足这种日益增长的需求,国产化多功能通信模块的研制成为了一种趋势。

本文以CPCI总线为基础,对多功能通信模块的研制进行了深入探讨。

二、CPCI总线概述CPCI总线(CompactPCI)是一种高性能的计算机扩展总线,具有高带宽、高可靠性、高兼容性等特点。

其设计理念是为了满足高速数据传输和实时性要求,为计算机系统提供一种高性能的扩展方式。

因此,以CPCI总线为基础的通信模块在数据传输速度和稳定性方面具有显著优势。

三、多功能通信模块的设计需求在研制多功能通信模块时,我们需要考虑以下几个方面:1. 传输速度:要满足高速数据传输的需求,保证数据传输的实时性。

2. 兼容性:应具备良好的兼容性,能够适应不同的系统和应用场景。

3. 稳定性:在长时间运行过程中应保持稳定可靠,减少故障率。

4. 功能性:应具备多种通信功能,如串口通信、网络通信等。

四、基于CPCI总线的多功能通信模块设计1. 硬件设计:硬件设计是整个模块的基础,包括主控芯片的选择、接口电路的设计等。

主控芯片应具备高性能、低功耗等特点,接口电路应具备高可靠性、高稳定性等特点。

2. 软件设计:软件设计是实现模块功能的关键,包括驱动程序的开发、通信协议的制定等。

驱动程序应具备高效、稳定的特点,通信协议应满足不同应用场景的需求。

3. 模块测试:在完成硬件和软件设计后,需要对整个模块进行测试,包括功能测试、性能测试、稳定性测试等。

测试结果应符合设计要求。

五、应用领域与前景基于CPCI总线的国产化多功能通信模块在各领域具有广泛的应用前景,如军事、航空、航天、工业控制等领域。

其高带宽、高可靠性、高兼容性等特点使其在数据传输和实时性方面具有显著优势。

随着信息化技术的不断发展,对通信模块的需求将更加严格,多功能通信模块的应用将更加广泛。

实时信号处理系统CPCI接口设计

现 , 细说 明 了 P I9 5 详 C 6 6主 从 工 作 模 式 以及 C I P D对 P I 号 和 局 部 信 号 的 转 换 , 后 给 出 了 电路 框 图和 C 信 最

时序 仿 真 图 。

关 键 词 :实 时信 号 处理 ;接 口设 计 ; P I 线 ; C 6 6芯 片 CC 总 P I95 中 图 分 类 号 : 9 16 T 5 . l TN 1 . ; N9 7 5 文献标识码 : A 文 章 编 号 :6 22 3 (0 6 0 2 80 1 7—3 7 20 )40 2—5

维普资讯

第 4期

20 0 6年 8月

雷 达 科 学 与 技术

R adaF Sc i ence and T echnoI ogy

Vo . L 4 NO 4

A u s 06 gu t20

实 时信 号处 理 系统 C C 接 口设 计 P I

o CI9 5 fP 6 6,a d sg a o v r i n b t e CIb sa d l c l u o d c e y CPI n i n lc n e so e we n P u n o a s c n u t d b b D. Atls ,i g v st e a t t i e h

cr utdigr m nd s he i g pit r . ic i a a a c duln c u e

Ke r s r a i i n lp o e sn y wo d : e lt me sg a r c s ig;i tr a e d sg n e f c e i n;CP u ;P 6 6 c i CIb s CI9 5 h p

基于 CPCI 总线的 FPGA+DSP 架构通用视频图像处理系统的设计

基于 CPCI 总线的 FPGA+DSP 架构通用视频图像处理系统的设计于洪松;韩广良;孙海江;李桂菊;武治国;李赓飞【摘要】为了应对实时视频图像处理复杂的现场环境条件,设计了一种通用视频图像处理系统.该系统便于扩展,可同时应用于多种不同现场环境.FPGA+DSP 架构由于同时吸取了具有优秀运算性能的 DSP 芯片以及具有高实时性的 FP-GA 芯片的优点而在实时图像处理领域中得到了广泛的应用,而 Compact-PCI 总线由于其与工业控制计算机有标准的接口而具有良好的可扩展性,通过对二者的有机结合设计了基于 Compact-PCI 总线的 FPGA+DSP 架构的通用视频图像处理系统.硬件实验表明,系统可对320×256~1024×1024分辨率,8~14 bits,最高帧频100 Hz 的视频图像进行实时采集与处理,并通过 cPCI 总线实现实时控制,取得了良好的效果,表明系统可以应用于红外及可见等复杂环境中,实时性很高,处理效果好,提高了系统的应用范围.为视频信号采集处理提供了一种新的可靠解决方案.%In order to deal with the complicated field environmental conditions that real-time video image process systems have to confront,a general-purpose real-time video image process system is de-signed,which is extendable and can be applied to multiple field environmental conditions simultane-ously. Image process systems based on FPGA+DSP architecture are widely used in the field of image process,because the DSP processor is of high calculating performance and the FPGA is of high real-time performance,while the Compact-PCI bus is extendable because its interface with the computer is already standardized. Combining both advantages,a new general-purpose video image process system is designed based on Compact-PCI bus andFPGA + DSP architecture. Hardware experiments show that,this system can be equal to capturing and processing video images of 320 ×256 ~1 024 ×1 024 pixels,8~14 bits and maximum frequency of 100 Hz real-timely. Besides,it can also realize real-time control by means of the Compact-PCI bus,of which the result is pretty good. It indicates that this system is capable of dealing with complicated environment,such as infrared and visible scenes. It is real-time and effective. It provides a new possible solution to video image capture and process.【期刊名称】《液晶与显示》【年(卷),期】2015(000)002【总页数】7页(P333-339)【关键词】视频图像处理;实时;FPGA;DSP;Compact-PCI总线【作者】于洪松;韩广良;孙海江;李桂菊;武治国;李赓飞【作者单位】中国科学院长春光学精密机械与物理研究所,吉林长春 130033; 中国科学院大学,北京 100049;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033;中国科学院长春光学精密机械与物理研究所,吉林长春 130033; 中国科学院大学,北京 100049【正文语种】中文【中图分类】TN1411 引言高速视频图像处理具有数据量大和实时性高的特点。

一种基于CPCI总线的控制计算机设计

K e y wo r d s : C P Cl , c o n t r o l , b r i d g i n g , i n t r e r f a c e , E t h e r n e t

C P CI ( Co mp a c t P C I ) 总线 属 于 第 二 代 总 线 标 准 , 属 于 并 行

一

种 基 于 CP CI 总 线 的控 制 计 算 机 设 计

一

种基于 C P C I 总线的控制计算机设计

卜 颖 ( 江苏 自 动化研究所, 江苏 连云港 2 2 2 0 0 6 )

摘 要

主 要 阐述 了一 种 基 于 C P CI 总 线 的控 制 计 算机 的设 计技 术 , 提 出 了需 要 实现 的 设 计 目标 , 详 细 描 述 了该 计 算 机 的 总 体 实现 方 法 , 并给 出 了控 制 板 , 测 量 板和 网络 功 能 的 设 计 。 实现 的控 制 计 算机 能够 满足 系统要 求 。

总线 , 其具有开放性 , 兼容性好等特 点 , 是 一 种 技 术 成 熟 的 总 线

标准 , 在 国 内 外 均 有 着 广 泛 的应 用 , 虽 然 第 三 代 总 线 一串行 总 线 已经 出 现 ,但 由于 C P C I 总 线 设 备 长 时 间 的 应 用 基 础 及 技 术 积 累, 目前 在 工 控 等 领 域仍 以 CP CI 总 线 作 为计 算 机 的主 流 总 线 。 本 文 给 出 的控 制 计 算 机 主要 实现 以下 功 能 : 1 ) 发 送 控 制 信号 , 送 出 检测 信 号 并 实 现 采集 , 判断 ; 2 ) 测 量 外 部 通 路 的 阻值 ; 3 ) 实现 对 外 部 设备 网络 地址 的动 态捕 获 以及 对应 f P地址 的 动 态 分 配 和 管理 。 文 中给 出 了 总体 及 各 部 分 功 能 的具 体 实 现 方 法 。

基于CPCI总线的高速大容量通用信号处理机

biiy a o o e sng,s o i nd r ns e rng. The s t m pp i s CPCIbu or t e o t lt m ng pr c s i t rng a ta f r i ys e a le s f h h s i e f c n nt r a e a d FPGA or t c t m f he us o LVDS n e f c i t r a e,t us t y t m s g od e e i lt h he s s e ha o xt nsbi y. i W ih a c t ompu a i a we o 4. t ton lpo rofup t 1 4 GFLOPS an c l bl d s a a e SDRAM o 4 GByt s, ofup t e t y t m s s t b e f e ltm e p o e s ng wih hi p e on i ou t l w .Fi a l he s s e i uia l or r a —i r c s i t gh s e d c tnu s da a fo n ly, is a plc to x m p e o e ltme s nt e i p r ur a a ( t p ia i n e a l n r a — i y h tc a e t e r d r SAR) i a n s i r d e m gi g i nt o uc d. Ke y wor :p r le r e s n ds a a l lp oc s i g;ADSP- TS20 1;CPCI i na nt grt ( ) ;s g li e iy SI

a ei r d e r nt o uc d. W ih a l os — o t o e c upl d p e o p e r hie t e,t y t m a he b l c d a e e rt e ra c t c ur he s s e h s t a an e —

基于FPGA的雷达信号处理板设计与实现

基于FPGA的雷达信号处理板设计与实现林琳【摘要】Based on CPCI bus,a radar signal processing board was designed and implemented with FPGA,which can be used to accomplish the general functions for radar signal processing like DDC,pulse compression of large time-bandwidth pro-duct signals in time-domain and FFT. At last,DDC and the pulse compression of large time-bandwidth product signals in time-domain are realized according to the requirements of some radar signal processing systems. The test results prove the effective-ness of the system.%基于CPCI总线,使用FPGA实现了雷达信号处理板的设计与实现。

实现数字下变频,大时宽带宽积数字脉冲压缩以及FFT等通用雷达信号处理功能。

最后给出了数字下变频和大时宽带宽积数字脉冲压缩在某雷达系统中的测试结果,测试结果满足系统要求。

【期刊名称】《现代电子技术》【年(卷),期】2014(000)011【总页数】6页(P51-56)【关键词】DDS;FPGA;脉冲压缩;雷达信号处理【作者】林琳【作者单位】陕西职业技术学院计算机科学系,陕西西安 710100【正文语种】中文【中图分类】TN958.3-34雷达系统需要对海量数据进行并行、实时处理,设计雷达信号处理板需要考虑三个方面的问题:数据并行实时处理、数据传输总线选择和多通道处理。

3U CPCI 信号采集

产品详细

机箱尺寸、重量

(带风扇模块)外形尺寸:225.40mm(深)×253.00mm(宽)×190.40mm(高)

(不带风扇模块)外形尺寸:225.40mm(深)×253.00mm(宽)×152.40mm(高)

电话:0755-8633 5270 手机:13902479857 sz.yjyang@

后 IO 面板接口

电话:0755-8633 5270 手机:13902479857 sz.yjyang@

7

后 IO 板 CPC-RP3811: USB2.0 x2、1 个 RS232/422/485 DB9 串口可切换、GbE x2 (SFP/RJ45

可选)

环境规格

工作温度:0℃ ~ +55℃(商业级)

4

(带风扇模块)净重:5.05 Kg

(不带风扇模块)净重:4.00 Kg

不锈钢金属箱体,闪银漆喷漆,铝合金包角

背板(CPC-9306)

32bit/33MHz

1 个系统槽、5 个扩展槽,32bit/33MHz CompactPCI 总线

支持 3U CPCI 板卡(160mm×100mm)及其后 IO 板卡(80mm×160mm)

1.25V

1 路模拟量输出

1 路可编程定时/计数器

8 路 TTL 数字量输入和 8 路 TTL 数字量输出

电话:0755-8633 5270 手机:13902479857 sz.yjyang@

10

订购信息

型号 研祥 CPC-I32MF12 研祥 PCLD-8710 研祥 PCL-10168-2M

基于CPCI总线双机通信的设计与实现

基于CPCI总线双机通信的设计与实现

随着信息技术的不断发展和应用,人们对于数据处理的要求也越来越高。

在某些应用场景下,需要同时运行多个任务并且保持高效性和可靠性。

这时,双机通信就成了一种非常有效的解决方法。

本文将介绍基于CPCI(CompactPCI)总线双机通信的设计与实现。

首先,CPCI总线是一种高速的通讯总线,它可以在短时间内传输大量数据,能够满足双机通信的数据传输需求。

基于CPCI总线双机通信的设计和实现,需要两个或多个计算机之间相互通信和协作,从而协同完成一些任务。

其次,为了实现基于CPCI总线双机通信,我们需要首先购买两张或多张CPCI卡,并且安装好相关的驱动程序和软件。

在通过CPCI总线连接双机之后,我们可以使用已有的网络通信协议来处理数据传输的内容,并且利用双机系统之间的通信功能,实现协同完成任务的功能。

在具体实现上,我们可以使用不同的软件平台来完成基于CPCI总线双机通信的设计和实现。

例如,使用

MATLAB/Simulink平台实现双机通信,可以通过数据传输模块来实现不同计算机之间的数据交流和传输。

又例如,在某些需要多台计算机同时协同工作的生产线控制系统中,可以使用Java及相关组件来开发双机通信应用程序,通过CPCI总线来实现云完成生产车间中一些任务的协同工作。

总之,基于CPCI总线双机通信的设计和实现可以帮助我们在

计算机协同工作的场景中提高数据传输的效率和可靠性,构建强大的计算机集群,以此来应对信息化时代的业务需求。

作为一种极端有效的解决方案,CPCI总线双机通信技术也许会在未来的信息技术领域中发挥更大的作用。

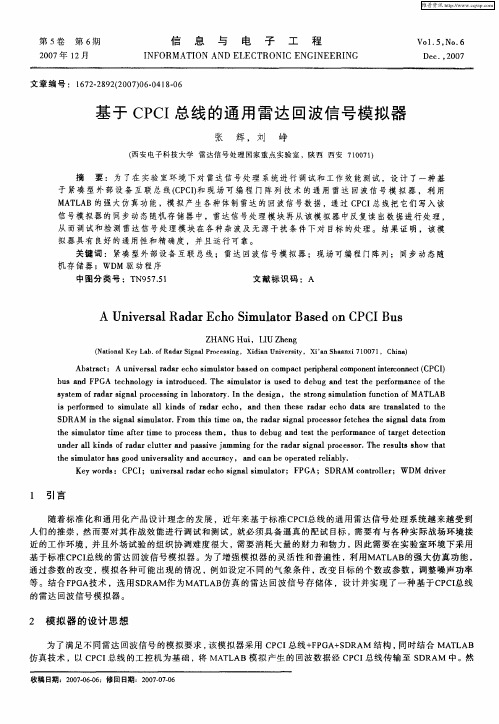

基于CPCI总线的通用雷达回波信号模拟器

摘 要 :为 了在 实验 室环境 下对 雷达信号处理 系统进 行调试 和工作效 能测试 ,设计 了一种基 于 紧凑 型 外部 设备 互 联 总线(P I 现场 可编 程 门 阵列 技术 的通用 雷达 回波信号 模 拟器 ,利用 C C) 和 MA L B的强大仿真 功能 ,模 拟产 生各种体制 雷达 的回波信号数 据 ,通过 C C 总线把 它们写入该 TA PI 信 号模 拟器的 同步动 态随机 存储器 中,雷达信号处理 模块再 从该 模拟器 中反复读 出数据进 行处理 , 从而调试和检 测雷达信 号处理模 块在各 种杂波及 无源干扰 条件 下对 目标 的处理 。结果证 明 ,该模 拟器 具有 良好 的通用 性和精 确度 ,并且运行 可靠。 关键词 :紧凑 型外部设备 互联 总线 ;雷达 回波信 号模 拟器 ;现场 可编程 门阵列 ; 同步 动态随

维普资讯

第 5卷

第 6 期

信 息 与 电 子 工 程

I ORMATI NF ON AND EL ECT RONI C ENGI ERI NE NG

Vo 5, 1. No. 6 De , 0 7 e. 2 0

20 0 7年 1 2月

机 存 储 器 ;WDM 驱 动 程 序

中 图分 类 号 :T 9 75 N 5. l

文 献 标 识 码 :A

A ie s lRa a h i ltrBa e i CPCIBus Un v r a d rEc oS mu a o s d Ol

ZHANG Hu , LI Z e g i U h n ( t n l yL b o d r in l rcsig Nai a Ke a . f o Ra a g a P o esn ,XiinUnvri , X ’nS a n i 10 1 C ia S da iest y ia h a x 7 0 7 , hn )

《2024年基于CPCI总线的扫描AD模块研制》范文

《基于CPCI总线的扫描AD模块研制》篇一一、引言随着现代电子技术的飞速发展,数据采集和处理技术在各个领域的应用越来越广泛。

作为数据采集的重要环节,AD(模数转换)模块的性能直接影响到整个系统的稳定性和可靠性。

CPCI (Compact PCI)总线作为一种高性能的工业总线,在高速数据传输和实时性要求较高的场合具有显著优势。

本文旨在介绍一种基于CPCI总线的扫描AD模块的研制,以提高数据采集和处理的能力。

二、系统概述本系统采用CPCI总线作为数据传输的主要通道,配合高性能的AD模块,实现高速、高精度的数据采集。

扫描AD模块是本系统的核心部分,其作用是将模拟信号转换为数字信号,以便于后续的数据处理和分析。

三、扫描AD模块的研制1. 硬件设计扫描AD模块的硬件设计主要包括AD芯片选型、电路设计、电源设计等。

首先,根据系统需求,选择合适性能的AD芯片。

其次,设计合理的电路,保证信号的稳定传输和准确转换。

最后,为AD模块提供稳定的电源,以保证其正常工作。

2. 软件设计软件设计是扫描AD模块研制的关键部分。

首先,编写驱动程序,实现CPCI总线与AD模块的通信。

其次,编写数据采集程序,实现高速、高精度的数据采集。

此外,还需要编写数据处理程序,对采集到的数据进行处理和分析。

3. 扫描技术为了实现高速、高精度的数据采集,本系统采用扫描技术。

通过扫描多个通道的模拟信号,实现并行处理,提高数据采集的速度和精度。

同时,采用数字滤波技术,降低噪声干扰,提高数据的可靠性。

四、系统实现1. CPCI总线通信实现CPCI总线作为一种高性能的工业总线,具有高速、可靠、实时等特点。

本系统通过编写驱动程序,实现CPCI总线与扫描AD 模块的通信。

在驱动程序中,定义了通信协议和接口函数,以便于数据的传输和处理。

2. 数据采集与处理实现数据采集与处理是本系统的核心功能。

通过编写数据采集程序,实现高速、高精度的数据采集。

同时,通过数据处理程序对采集到的数据进行处理和分析,以便于后续的应用和分析。

一种基于CPCI总线的高速雷达回波信号采集系统

l i l e i d, a i o t l h g e t , o d sa i t , n a ih p a t l l e f xb e d sg e e s yc n r l d, ih r a- me g o t b l y a d h shg r ci a a u . e n l oe l i i c v Ke r s CP It c n l g y wo d : C h o o y;h g —p e aa a q ii o ;r d rs a ;Mi mB a e e ih s e d d t c u st n a a i l i n g c lz

Ab t a t aa a q ii o y t m s d i i e b n a a e e v r i s d e a e n t e C CIb s T e c mp st n s r c :A d t c u st n s se u e n a w d — a d r d rr c i e t i d b s d o h P u . h o o i o i s u i sr c u e h r w r n ot r e in n s l a ay i i i t d c d T e a ay i r s l h w a es se r aie e t t r , ad a e a d s f u wae d sg s d r u t n lss s n r u e . h n l s e u t s o t t h y tm e l st a e o s s h t z h

第 1 9卷 第 1 期 8

Vo .9 11

No 1 .8

电子 设计 工程

El cr n c De i n Engn e e to i sg ie

电子对抗原理_3_雷达系统结构_信号处理

FPGA #B Virtex-7

V585T -1FF1761I

EMIF INT

NOR FLASH

1Gb

DSP #A TMS320C6678

SRIO SRIO

4X

4X

HyperLink

S6

LX9

DDRIII

SDRAM

PLL

ARM

128MX64

DSP #B TMS320C6678

DDRIII SDRAM 128MX64

通信系统最常用的中频是70MHz

7

接收机噪声

雷达接收机噪声的来源主要分为两种: 内部噪声 外部噪声

内部噪声主要由接收机中的馈线、放电保护器、 高频放大器或混频器等产生。接收机内部噪声 在时间上是连续的,而振幅和相位是随机的, 通常称为“起伏噪声”。

外部噪声是由雷达天线进入接收机的各种人为 干扰、天电干扰、工业干扰、宇宙干扰和天线 热噪声等,其中以天线热噪声影响最大。

B型,距离—方位显示器,水平方向表示方位, 垂直方向表示距离

E型 ,距离—仰角显示器, P型 ,环视显示器,也称平面位置显示器

(PPI),其距离由径向距离表示, J型 ,圆周扫描的距离显示器

27

A型和A/R型

B型

器

距离-时间 窗

高度-时间 窗

目标三维 显示窗

14

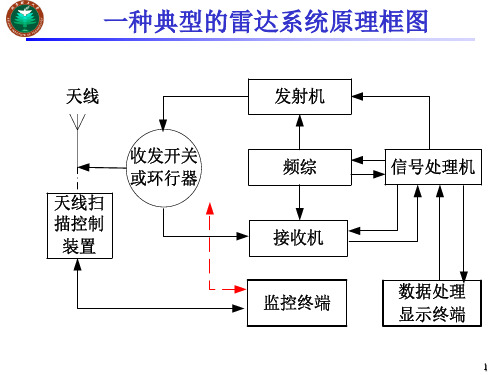

5 信号处理机

雷达信号处理流程 信号处理机结构 信号处理机指标

15

5.1 雷达信号处理流程

雷达信号处理机的任务是对感兴趣的目标 信号进行检测并提取出目标参数(距离、 方位角、高低角、径向速度等)

A/D

脉冲 压缩

滤波

CFAR 处理

目标参数 提取

16

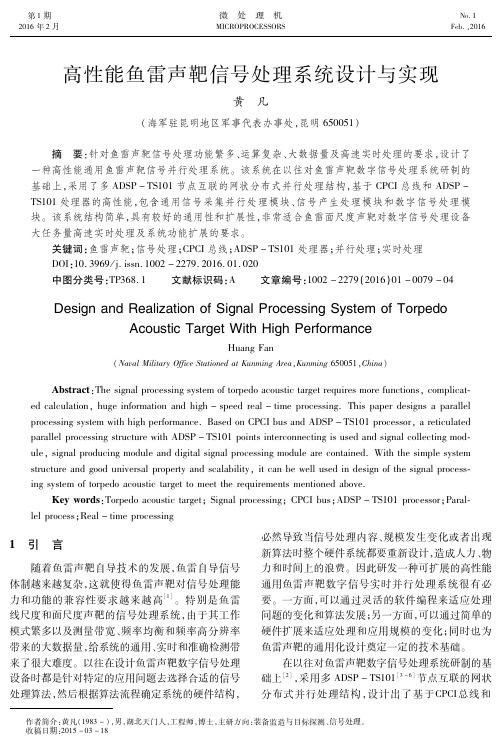

高性能鱼雷声靶信号处理系统设计与实现

1 引 言

随着鱼雷声靶自导技术的发展,鱼雷自导信号 体制越来越复杂,这就使得鱼雷声靶对信号处理能 力和功能 的 兼 容 性 要 求 越 来 越 高[1]。 特 别 是 鱼 雷 线尺度和面尺度声靶的信号处理系统,由于其工作 模式繁多以及测量带宽、频率均衡和频率高分辨率 带来的大数据量,给系统的通用、实时和准确检测带 来了很大难度。以往在设计鱼雷声靶数字信号处理 设备时都是针对特定的应用问题去选择合适的信号 处理算法,然后根据算法流程确定系统的硬件结构,

必然导致当信号处理内容、规模发生变化或者出现 新算法时整个硬件系统都要重新设计,造成人力、物 力和时间上的浪费。因此研发一种可扩展的高性能 通用鱼雷声靶数字信号实时并行处理系统很有必 要。一方面,可以通过灵活的软件编程来适应处理 问题的变化和算法发展;另一方面,可以通过简单的 硬件扩展来适应处理和应用规模的变化;同时也为 鱼雷声靶的通用化设计奠定一定的技术基础。

·80·

微 处 理 机

2016

ADSP-TS101处 理 器 的 高 性 能 通 用 鱼 雷 声 靶 通 用 信号采集并行处理模块、信号产生处理模块和数字 信号处理模块。这些模块具有通用性、可扩展性好 和并行处理效率高等特点。另外可用此模块构成大 规模的并行信号处理系统,其简单清晰的系统拓扑 结构和接口关系的特点,非常适合鱼雷面尺度声靶 对数字信号处理设备大任务量高速实时处理及系统 功能扩展的要求。

基于 CPCI总线的并行高速数字信号处理系统 结构框图如图 1所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于 CPCI总线 的雷达信号处理 系统

鲁 千红 ,杨 军

(空军雷达学院信 息与指挥 自动化系,武汉 430019)

ห้องสมุดไป่ตู้

摘 要 :针对雷达数据 流的高速 、实时传输 问题和非实时操作 系统中信 息传输 的瓶颈 问题 ,基于CPCI国

际标 准总线 、高速 TMS320C6416 DSP芯片以gt_FPGA器件等硬件设备 ,设 计 了一个通用 的雷达信号处理 系统. 实验 结果表明 ,该 系统具有通用性、可编程性 、兼容性 、实时性等特点:该 系统的设 计成功为雷达等 电子设备的 信号处理分机设计提供 了一条新 的思路

目前 ,雷 达信 号处理 系 统 主要 采 用 DSP芯 片 和 FPGA等器件 实现 ,从而使 系统具 有很 强 的可 编 程性 和通用性 .但其 中的总线标 准各式 各样 ,没 有 形成 一个 占主 导地位 或统 一 的总线 标准 ,这在 一 定程 度上 限制 了其通 用性 .

为解决 雷达数 据 流的高速 、实时传 输 问题 ,本 文提 出采 用 CPCI国际标 准 总线 、TI公 司高 速 DSP 芯 片 TMS320C6416 以及 Altera公司 的 FPGA器 件设计 一个通用 的雷达信 号处理 系统 4].在该 系统 中 ,CPCI标准 总线 技术 可保证 该 系统具 有通用性 ; 同时 ,利用 TMS320C6416的 EDMA 功能来 实 现雷 达数 据 流 的高速 、实时传 输 ,此外 利用 CPCI总线 技 术可 实现 DSP软件 、FPGA配 置和测 试 数据 的动 态 、直接加 载 .总体上 ,该 系统 具有 如 下主要 特 点 :① 通用性 ,可编 程性 ,兼容性 .该 系统 可 与多种 雷达 接 口兼 容 ;② 实 时性 .可 实现 雷达 信号 的实 时处 理 ;③ 独立 性 .该 系统可 以作 为一 个独 立 的 雷 达信号 处理 实验 平 台 ,用 于 雷达 信号 处理新 算 法 的研 究与 验证 .

I/O 接 口模 块还 可 以模 拟雷 达 的触 发 脉冲 和时 钟等 时序 ,并 可 通过加 载 数据 文件 模拟 雷达 I、Q数字 视频 .数据 文件 的加 载是 通过 CPCI总线 和显 示软件 的交互 界面 完成 的 ,其 中的 数据 既可 以是采集 的实际雷达数据 ,也可 以是仿真数据.因 此 本 系统可 以作 为相对 独立 的雷达 信号 处理 实验 平 台.

关键 词 :CPCI总线 ;雷 达信 号处 理 :通 用 性 中图分类号 :TN957 文献标识码:A

随着 雷达 技术 的迅 速发 展 ,对 雷达 信号处 理 系统 的要求 越来越 高 ,其更 新 换代 的速 度也 越来 越 快 .将雷 达信 号处理 系统与 CompactPCI【l (简称 CPCI)总线 技术 相结 合 ,加 快产 品开发周 期 ,尽快 将 最新 的雷 达信 号处 理算 法予 以工 程实 现 ,具有 重 要 的现实 意义 .

维普资讯

第21卷 第2期 2007年 6月

空 军 雷 达 学 院 学 报

Journ al of Air Force Radar Academy

VO1.21 No.2 Jun.2007

文 章 编 号 :1673—8691(2007)02—0118-03

r 。

cPcI总线

嘲

自定 义并行高速数据 总线 用 CT总线)

a】CI机箱

图 1 基 于 CPCI总线的雷 达信号处理系 统组成框 图

信号 转接 板将雷 达 的有关 信号(如 I,Q数字 视 频 ,触 发 脉 冲 和时钟 等 )经 驱动 电路 驱动 后 ,通 过 双 绞线传 送 至 I/O接 口模 块.I/O接 口模块 主要 采 用 Altera公 司的 FPGA进 行设 计 J,它 在时钟 的 同步下 完成 I、Q数字 视频 数据 转换 功能 ,使数 据 按 照约 定格式 ,经 由 自定 义高 速数 据传输 通道 ,送 至 DSP模块 .

收 稿 日期 :2007.01.09: 修 订 日期 :2007.01.26 作 者简 介:鲁 千. ̄(1971一),男 ,讲师 ,主要 从事 雷达信 号处 理研究

维普资讯

第2期

鲁千红,等:基于CPCI总线的雷达信号处理 系统

119

DSP模 块 主要 采用 TI公 司 的 TMS320C6416芯 片进 行设 计 ,它 可 以实现 各种 雷 达信 号处 理算 法 (如 MTI处 理 、滑 窗检测 等 ).当一 个 DSP模 块不 能 满足用 户的处 理需求 时 ,可扩展成 2个 或多个 DSP 模块 ,多 DSP模 块之 间 的任务 分配 、协 调 和同步 可 在 CPU模 块 的控制 下完 成 .每个 DSP模块 保 留部 分 I/0连 线 ,用 于 DSP板 间 的硬 件 同步 .DSP模 块 的处 理结 果分 2路送 出 :一路 通 过 CPCI总 线送 到 I/O接 口模 块 ,按 雷达 P显 的数 据格 式进 行 转换 , 供雷 达显 示器 使用 ;另一 路经 CPCI总线 传送 至 CPU模 块 的内存 .

1 系统设计

1.1 系统组成

雷达 信号处理 系统组 成如 图 l所示 .该 系统 主 要 由信号转 接 板 、I/O接 口模 块 、CPU模块 、DSP模 块 和 显示 器等 组成 .其 中 I/O接 口模 块 、cpu模 块 和 DSP模块 安 装在 标准 CPCI机 箱 中 ,通 过 CPCI 总线 传输 数据 .

CPU模块 为通 用计 算 机 ,采 用 Windows 2000 操作 系统 ,负 责提 供 总线 时钟 、总 线仲 裁 、系统 中 断处 理 、复位 、系统 资 源检 测及 自动配 置 .它在 应 用 软 件——显 示软 件 的配合 下完 成数 据显 示 和参 数设 置等 功能 .