高速ADC低抖动时钟稳定电路

高速ADC时钟抖动及其影响的研究

高速ADC时钟抖动及其影响的研究

摘 要: 从ADC的输入信号及时钟源的自身参数着手,主要分析了输入信号幅值、频率、采样频率对时钟抖动及ADC信噪比的影响,根据ADC手册数据提供的信息给出了时钟抖动的计算方法,并对计算结果和实际测量结果进行分析比较,进一步提出了减少时钟抖动方法。关键词: 时钟抖动;SNR;频率

由式(2)可知,时钟抖动引起的信噪比与输入信号的频率 fin有关,随着输入信号频率 fin的增大,信噪比下降。也可知时钟抖动引起的信噪比与输入信号幅度 Ain无关,但由图2可以看出随着输入信号幅度 Ain的降低,时钟抖动Jitter随之减少,因而信噪比与时钟抖动Jitter密切相关。 ADC总噪声由热噪声、量化噪声和抖动三部分组成,如果假定所有的噪声源线性无关,则ADC的信噪比可以用式(3)表示。式(3)中,T表示热噪声在一个周期内的有效值平方,Q表示量化噪声在一个周期内的有效值的平方,这两项与输入信号的频率 fin无关,时钟抖动一个周期有效值的平方δ2则取决于输入信号频率 fin。如果要求ADC 在输入信号 fin较大时SNR高,则必须用抖动小的采样时钟。因此,在高速高精度ADC 的设计中,对时钟电路都采用特别的处理方法来降低时钟抖动,比如Maxim公司的Max104 等。 对于一个确定的ADC,当输入信号幅值 Ain低于一定值时,其信噪比主要取决于热噪声和量化噪声,这种情况下时钟抖动对其影响不大。图3所示为ADS5542工作在78 MSPS和230 MHz输入下的实际噪声基底。图3中的理论曲线是在加上250 fs的抖动和1LSB的热噪声下的条件下由式(2)计算得出的,由图可以看出理论曲线与实际测量的噪声基底曲线非常接近。表1所示为在不同的输入信号频率下的信噪比的大小。表中给出了两组数据,一组为实际测量的信噪比SNR,一组为由式(2)计算出来的信噪比SNR。表1中的测量值是在采样频率fs为60 MS/s,并假定抖动频率为200 fs的条件下测量出的数据。由表1可知,由式(2)估算出来的数据和实际测量的数据之间的误差较小,式(2)比较准确地表达了信噪比与输入信号频率之间的n、fS的关系 时钟信号启动采样保持器进行采样之前,采样保持电路的内部开关处于闭合状态,电容电压跟踪模拟输入信号的变化,时钟信号的一个边沿到来时开关打开,电容电压保持为该时刻的值。,该时刻的电压值为垂直虚线所对应的值,在Δt的采样时间内,产生了一个采样电压误差ΔV,该瞬时误差就是时钟抖动Jitter,采样电压误差的大小取决于输入电压波形。如果没有其他噪声信号,根据图2可以计算出抖动电压的大小和信噪比。如果图1的输入信号为幅值为Ain、频率为fin的正弦波,则采样电压的时钟抖动Jitter正比于输入电压在该时刻的斜率和采样时间。则一个周期的时钟抖动Jitter有效值的平方δ2为:

一种高速低抖动四相位时钟电路的设计

一种高速低抖动四相位时钟电路的设计崔伟;张铁良;杨松【摘要】超高速A/D转换器对精准的时钟电路提出严格要求,时钟抖动是影响其精度的重要因素.文章在分析时钟抖动对A/D转换器的影响后,介绍了一种适用于GHz的低抖动四相位时钟电路.电路采用时钟恢复电路、四相位分布网络和相位校正电路,得到占空比稳定、相位误差小的四相位时钟.采用0.18μm CMOS工艺实现,电路仿真表明,四相位输出时钟抖动102 fs,占空比调整范围30%~70%,功耗**********.【期刊名称】《电子元件与材料》【年(卷),期】2019(038)001【总页数】6页(P67-71,77)【关键词】高速时钟;时钟抖动;多相位;时钟恢复;模数转换器;CMOS【作者】崔伟;张铁良;杨松【作者单位】北京微电子技术研究所, 北京 100076;北京微电子技术研究所, 北京100076;北京微电子技术研究所, 北京 100076【正文语种】中文【中图分类】TN432A/D转换器 (Analog to Digital Converter,ADC)是模拟系统与数字系统接口的关键部件,广泛应用于工业、民用、雷达等领域。

转换器的发展使采样速率不断提升,在超高速A/D转换器中,广泛采用多通道时间交织技术来提高整体采样率,其必须严格按照时间序列进行信号采样和数模转换,因而对时钟电路提出严格要求。

随着工艺技术的提升,时钟的上升、下降时间在整个时钟周期中所占的比例不断增大,占空比失调问题越发严重[1]。

此外,时钟抖动直接影响A/D转换器的信噪比(Signal Noise Ratio,SNR)等参数指标[2]。

目前,有多种方法可以实现低抖动高速时钟电路,包括基于延迟锁相环技术的时钟电路[3-4],基于连续时间积分器的时钟电路[5]和基于脉宽控制环路的时钟电路[6-7],它们各有特点,适用于不同类型的A/D转换器。

本文提出的高速低抖动四相位时钟电路,应用于时间交织ADC,为ADC采样保持电路提供精准的高速四相位时钟。

时间交织ADC的时钟接收及分布网络设计探析

时间交织ADC的时钟接收及分布网络设计探析摘要:时间交织模数转换器(ADC)是现代通信和信号处理系统中的关键组件之一。

在高速和高精度应用中,ADC的性能和可靠性对系统的整体性能至关重要。

基于此,本文针对时间交织模数转换器(ADC)的时钟接收和分布网络设计进行深入研究。

首先,阐述了时间交织ADC的概念,然后详细讨论了时钟接收及分布网络对系统性能的影响。

接着,分析了基于时钟同步技术、时钟恢复技术和低抖动分布网络的高效设计,以期为相关设计提供有益的参考。

关键词:时间交织ADC;时钟接收及分布网络;设计探析前言:时间交织模数转换器(ADC)作为一种高性能的ADC技术,在通信、雷达、无线传感等领域有着广泛的应用。

与传统的并行ADC相比,时间交织ADC 采用时间多路复用技术,将多个模拟信号分时采样,有效提高了采样率。

然而,由于时间交织ADC的时钟接收和分布网络设计较为复杂,因此对其性能有较大影响。

因此,时钟接收和分布网络的设计分析对于提高时间交织ADC的整体性能具有重要意义。

1.时间交织ADC概述时间交织模数转换器(ADC)是一种高性能的ADC技术,其基本原理是采用时间多路复用技术,将多个模拟信号分时采样。

在时间交织ADC中,模拟信号被划分为多个时间片,每个时间片对应一个模拟信号的采样时刻。

这种分时采样的方法使得时间交织ADC能够实现高采样率,从而提高了整个系统的性能。

时间交织ADC采用时钟分配策略来保证各通道之间的采样时刻同步。

时钟分配策略可以根据系统需求进行设计,以满足不同场景下的时钟同步精度要求。

常见的时钟分配策略有时间交织ADC中的全局时钟、本地时钟以及混合时钟等。

这些时钟分配策略可以确保各通道之间的时钟同步,从而提高时间交织ADC的采样精度。

此外,时间交织ADC具有很多优势。

其一,时间交织ADC通过分时采样的方法,实现了对多个模拟信号的高效采样,使得时间交织ADC在通信、雷达、无线传感等领域具有广泛的应用前景。

高速adc 数字接口 阻抗

高速adc 数字接口阻抗全文共四篇示例,供读者参考第一篇示例:高速ADC(Analog to Digital Converter)是一种用于将模拟信号转换为数字信号的器件。

在许多领域,特别是通信领域和高速数据采集领域,高速ADC的应用非常广泛。

而数字接口的设计和阻抗匹配在高速ADC的应用中起着至关重要的作用。

本文将重点讨论高速ADC 数字接口的阻抗设计。

让我们简单了解一下高速ADC数字接口的基本原理。

在高速ADC 的工作过程中,模拟信号首先被采集并转换为数字信号,然后通过数字接口传输到外部系统进行处理。

这个数字接口一般由一组数字信号引脚组成,其中包括数据引脚、时钟引脚、控制引脚等。

在数字信号传输过程中,由于信号具有高频率和快速变化的特性,就会产生信号完整性和阻抗匹配的问题。

阻抗匹配是指传输线上的信号源端和负载端之间的阻抗匹配情况。

在高速ADC数字接口设计中,阻抗匹配的关键在于保持传输线的特性阻抗与信号源和负载的阻抗相匹配。

这样可以最大程度地减小信号反射和传输损耗,提高信号传输的稳定性和可靠性。

为了实现阻抗匹配,设计者需要考虑如下几个方面。

首先是传输线的特性阻抗匹配,一般应该选择合适的传输线类型和特性阻抗值,使其与信号源和负载的阻抗相匹配。

其次是信号源和负载的阻抗匹配,这要求设计者在选择与ADC相连接的器件时要注意其输入输出端的阻抗匹配情况。

最后是信号引脚的阻抗匹配,要确保信号引脚设计合理,避免出现信号反射和传输失真的情况。

在高速ADC数字接口设计中,还需要考虑信号引脚的布局和连接方式。

一般来说,为了尽量减少信号传输线的长度和阻抗失配,设计者应该尽量将ADC和外部系统的数字接口引脚布局在尽可能短的距离范围内,并采用合适的连接方式,如差分对或同轴线连接等。

这样可以有效减小信号传输过程中的串扰和信号损耗,提高信号传输的稳定性和抗干扰能力。

高速ADC数字接口的阻抗设计对于整个系统的性能和可靠性至关重要。

多通道高速ADC硬件设计

要 素 ,随 着被采 样信号 速 度和采 样精

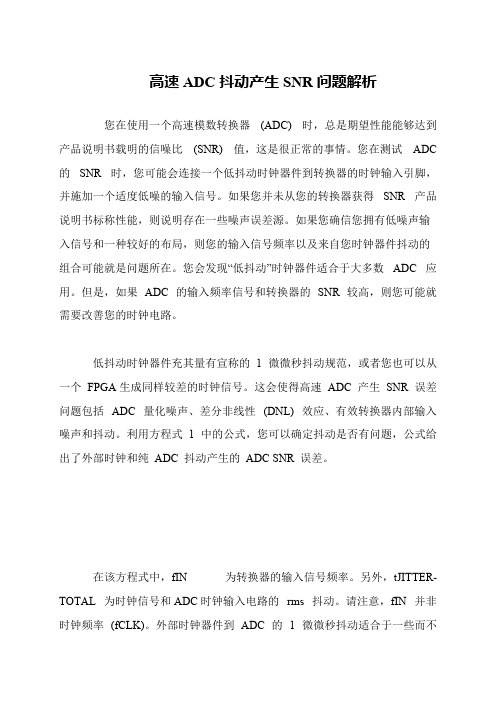

图2硬 件电路 示意 图

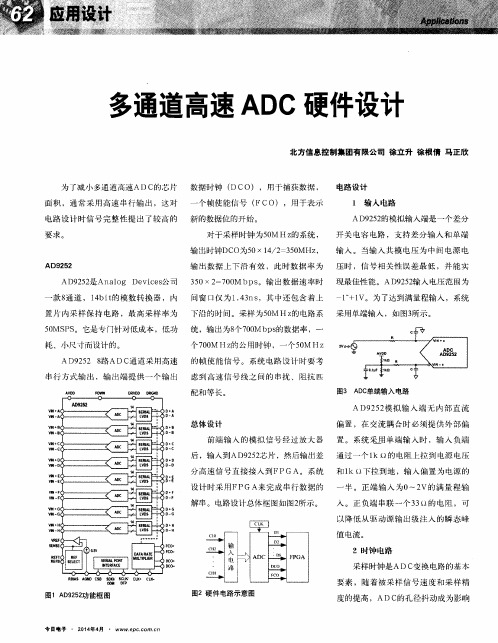

图1 A D 9 2 5 2 功 能框 图

度 的提 高 ,A D C 的孔径抖 动成为影响

今 B电 子

・ 2 0 1 4 年4 月

・ www . e p c , c o n r c

ADC 噪声的主要来源 ,甚至成为ADC 采样精度和睬 样速率提高的限制 因素。

耗 、 小 尺 寸而 设 计 的 。 个7 0 0 MHz 的 公用 时钟 ,一 个 5 0 M Hz

A D9 2 5 2 8 路A D C 通道采 用高 速 的帧 使能信 号 。系统 电路 设计 时要考

串 行 方 式 输 出 ,输 出 端 提 供 一 个 输 出 虑到 高速信 号线 之间 的串扰 、阻抗 匹

为 了保持数 据和 时钟 初始9 0 。的 有效位E N0 B ( E f e c t i v e Nu mb e r O f 相位关系 ,在布线的时候 ,数据线和时 B i t s )。有效位 与A D C的噪声水平相

完整的孔径 抖动应包含A D C 时钟 钟 线要 等长 ,并且 越短越 好 。为 了等 关 。噪 声水 平 表 征 了A D C基 线 涨 落 情 的抖动 以及AD c自身的孔径抖 动。二 长 ,需要 走蛇 形 线 。蛇 形 线 的拐 角 处 采 况 。系 统 测 试 的 时 候 将 AD C 输 入 端 悬

输 出时f  ̄ DC O为5 0×1 4 / 2 3 5 0 MHz ,

AD92 52

输 出数 据 上 下 沿 有 效 ,此 时 数 据 率 为 压 时 , 信 号 相 关 性 误 差 最 低 ,并 能 实

AD 9 2 5 2 是 An a l o g De v i c e s 公 司 3 2 5 2 输 入 电压 范 围 为 5 0×2 7 0 0 Mbp s 。输 出数据 速率时 现 最佳 性 能 。AD9

基于FPGA的宽带ADC采集系统的设计与实现

基于FPGA的宽带ADC采集系统的设计与实现李赛辉;刘剑;蒋廼倜;李伟【摘要】针对宽带采集系统设计中的时钟抖动、高速ADC电路、高速数据缓存和高速数据传输等问题,阐述了一种基于FPGA为主控芯片、DDRII作为缓存模块、采样速率为500 MHz的宽带ADC数据采集系统的设计与实现.分析了各部分对采集系统的影响和在设计中需要注意的问题.对设计的系统进行了性能测试.【期刊名称】《雷达与对抗》【年(卷),期】2016(036)004【总页数】4页(P41-44)【关键词】雷达;信号处理;FPGA;采集系统;ADC【作者】李赛辉;刘剑;蒋廼倜;李伟【作者单位】中国船舶重工集团公司第七二四研究所,南京211153;中国船舶重工集团公司第七二四研究所,南京211153;中国船舶重工集团公司第七二四研究所,南京211153;中国船舶重工集团公司第七二四研究所,南京211153【正文语种】中文【中图分类】TN911.7雷达瞬时工作带宽的扩展可获得复杂目标的精细回波,因而也有效提高了雷达距离分辨力。

因此,针对宽带雷达的宽带采集技术也越来越受到关注。

宽带采集系统的关键技术在于最大时钟抖动的确定、高速ADC电路的设计、高速数据的缓存以及高速数据的传输。

本文针对这些问题,设计了一款以FPGA为核心控制器、采用DDRII作为高速信号缓存模块的宽带信号采集系统,其采样频率为500 MHz,中频信号带宽达到200 MHz。

采集系统将前端模拟信号转换成数字信号。

按照奈奎斯特采样定理,当采样频率fs 满足大于两倍的信号带宽B时,可以不失真重建原信号。

一个典型的宽带采集系统包含信号调理电路、高速ADC转换器、高速数据缓存模块、微控制器及时钟电路等。

本文采用FPGA作为采集系统的微控制器、DDRII缓存器作为高速数据缓存模块,高速ADC转换器采用ADS5463芯片。

FPGA型号为Xilinx Virtex5XC5VLX110T,ADC的量化位数为12位,采样频率为500 MHz,数据锁存时间3.5 个时钟周期,输出电平方式为LVDS,功耗大小为 2.2 W。

高速adc采集电路设计

高速adc采集电路设计高速ADC(模数转换器)采集电路的设计涉及到多个关键组件和参数,这些都需要仔细考虑和优化以确保性能。

以下是一个简化的高速ADC采集电路设计流程:1.选择ADC类型:根据需要,选择适合的高速ADC,例如并行ADC、逐次逼近寄存器(SAR)ADC、流水线ADC等。

每种类型都有其特性和应用场景。

2.确定规格:确定ADC的规格,包括分辨率(位数)、转换速率、输入范围、功耗等。

这些参数将影响电路设计。

3.设计参考电压和基准电路:ADC需要一个稳定的参考电压。

设计一个低噪声、低失真、低抖动的参考电压和基准电路。

4.输入电路设计:根据ADC的输入要求,设计适当的输入电路。

这可能包括缓冲器、去耦电容、抗混叠滤波器等。

5.时钟分配:为ADC提供稳定的时钟信号,并确保时钟网络的分布是低噪声和低抖动的。

6.电源和地平面:设计适当的电源和地平面,以确保ADC的稳定运行和低噪声性能。

7.数字接口:如果ADC有数字输出,设计适当的数字接口。

这可能包括数据总线、地址总线、控制总线等。

8.噪声和电磁兼容性(EMC)考虑:在高速ADC中,噪声和EMC问题可能更为突出。

进行电磁仿真,并采取措施减少辐射和传导干扰。

9.版图和布局考虑:在绘制版图和布局时,考虑信号路径、电源和地平面、去耦电容的最佳放置等。

10.测试和验证:在实际制造之前,使用仿真工具验证设计的正确性。

制造样品进行测试,以确保满足规格和性能要求。

11.优化和迭代:根据测试结果,对设计进行必要的调整和优化。

这可能包括更改元件值、优化布局、改进去耦策略等。

12.文档和归档:整理所有设计文档,以便于未来的维护和修改。

请注意,高速ADC采集电路设计是一个复杂的过程,需要深入的电子工程知识以及对模拟和数字电路设计的理解。

建议在进行此类设计时咨询或雇佣有经验的电子工程师或专家。

ADC参数及其电路形式资料

ADC参数及其电路形式资料ADC(Analog-to-Digital Converter)即模数转换器,是一种电子设备,它可以将连续的模拟电信号转换为离散的数字信号。

ADC广泛应用于各种电子设备中,如通信系统、测量仪器、数据采集系统等。

本文将对ADC的参数及其电路形式进行详细介绍。

一、ADC参数:1. 分辨率(Resolution):分辨率是ADC能够表示的输出数字值的精度。

它由数字编码方式和转换器的比特数决定。

分辨率越高,ADC的精度越高。

2. 采样率(Sampling Rate):采样率是指ADC每秒钟对输入信号进行采样的次数。

采样率过低会导致信号失真,采样率过高会增加系统的计算和存储负载。

3. 噪声(Noise):ADC的输出信号中可能存在各种噪声,如量化噪声、时钟抖动等。

噪声会对ADC的精度和准确性产生影响。

4. 误差(Error):ADC存在各种误差,如非线性误差、增益误差、偏移误差等。

这些误差会导致ADC输出与输入之间存在一定的差异。

5. 功耗(Power Consumption):ADC的功耗是指该设备在正常工作状态下消耗的功率。

功耗高的ADC会产生大量的热量,需要进行散热,增加系统成本。

6. 输入电压范围(Input Voltage Range):输入电压范围是指ADC 能够接受的模拟输入电压的范围。

超出输入电压范围的信号将导致ADC无法正常工作。

7. 输入阻抗(Input Impedance):输入阻抗是指ADC对输入信号的阻抗。

输入阻抗越高,ADC对外部电路的影响就越小。

8. 速度(Speed):ADC的速度是指该设备每秒钟能够完成的转换次数。

速度越高,ADC响应的时间越短。

二、ADC电路形式:1. 逐次逼近型ADC(Successive Approximation ADC):逐次逼近型ADC是一种常用且成熟的ADC电路形式。

它通过逐步逼近输入信号的值,从而进行模拟转数字转换。

基于FPGA的高速ADC同步采集电路的设计与实现

基于FPGA的高速ADC同步采集电路的设计与实现秦艳召*明蕾**庄东曙***摘要在无线通信领域,实时分析及处理的信号带宽越来越大,要求射频前端ADC 的采样率也越来越高,对采样系统的SNR、SFDR以及同步性有着较高的要求。

本文描述了一种基于FPGA的两路高速ADC同步电路,该电路保证了两路宽带信号高速采集,提高了宽带通信的分析处理带宽,同时保证了采集电路的同步性及SNR和SFDR性能。

本设计在无线通信、信号采集、信号处理领域,有着较强的实用性,可广泛用于宽带无线通信、数字仪表、电子对抗等领域。

关键词:无线通信同步采集高速ADCDesign and Implementation of a High-speed ADC Synchronous Acquisition Circuit Based on FPGAQin Yanzhao Ming Lei Zhuang DongshuAbstractIn the field of wireless communication,the signal bandwidth of real-time analysis and pro-cessing is getting larger,which requires high sampling rate of RF front-end,high demand of SNR,SFDR and the synchronization of the sampling system.This paper describes a two -way high-speed ADC synchronous acquisition circuit based on FPGA,which improves the analysis and processing bandwidth of broadband communication,and guarantees the high-speed acquisition of the two-way broadband signal,the synchronization of acquisition circuit,as well as the performance of SNR and SFDR.The design has strong practicability in wireless communication,signal acquisition and processing.It can be widely used in the fields of broadband wireless communication,digital instruments and e-lectronic countermeasures.Key words:Wireless communication Synchronous acquisition High-speed ADC*作者系南京熊猫汉达科技有限公司工程师**作者系南京熊猫汉达科技有限公司工程师***作者系南京熊猫通信科技有限公司高级工程师12019年第3期通信与广播电视一、引言在无线通信中,实时分析及处理的信号带宽越来越大,要求ADC 的采样率也越来越高,同时对采样系统的SNR 、SFDR 以及同步性有着较高的要求,而传统的采集系统不能满足当前需求。

高速adc的设计注意事项

高速adc的设计注意事项高速ADC是一种用于高速信号采集和数字化的模数转换器。

它的设计非常关键,因为它直接影响到信号采集的准确性和频率响应。

下面是一些设计高速ADC时需要注意的事项:1. 时钟和采样:在高速ADC中,时钟的稳定性和准确性是非常重要的。

为了确保准确的采样,时钟必须具有较低的相位噪声和抖动。

此外,时钟频率必须与信号频率匹配,以避免混叠失真。

因此,在设计高速ADC时,应选择高质量的时钟源,并确保时钟电路的稳定性和准确性。

2. 前端模拟电路:前端模拟电路是将输入信号转换为电压或电流的关键部分。

在高速ADC中,应选择低噪声和高速度的操作放大器,并提供适当的滤波器来去除高频噪声和混叠失真。

此外,为了提高信号质量,还可以使用差分信号传输和抗干扰设计技术。

3. 样本保持电路:样本保持电路用于在输入信号到达之后,将其保持在ADC输入端的电压或电流上。

在高速ADC中,样本保持电路必须具有高带宽和低抖动,以确保准确的采样。

此外,为了避免信号交叉耦合和信号失真,应采用差分样本保持电路和布局技术。

4. ADC核心:ADC核心是将模拟信号转换为数字信号的关键部分。

在高速ADC 中,需要选择合适的ADC架构和位数,以满足要求的采样速度和分辨率。

常见的高速ADC架构包括交叉比较器ADC、逐次逼近型ADC和闩锁型ADC。

在选择ADC核心时,还应考虑功耗、线性度、采样速度和动态范围等因素。

5. 数字后处理:数字后处理用于对采样的数字信号进行滤波、解调和数据处理。

在高速ADC中,数字后处理的设计必须满足高速数据传输的要求。

为了提高信号质量,可以使用数字滤波器、数据校正技术和误码校正方法。

此外,为了减少数据传输带宽和存储需求,还可以压缩采样数据。

6. 供电和接地:供电和接地是高速ADC设计中很重要的考虑因素。

为了避免噪声和干扰,应采用适当的电源滤波器和抑制技术。

此外,为了减少电源反馈和信号耦合,应采用适当的电源布局和接地技术。

多通道高速ADC电路PCB设计技术浅谈

多通道高速ADC电路PCB设计技术浅谈李军辉;简育华;袁子乔【摘要】ADC是将模拟信号转换为数字信号的芯片,它在电路系统中的作用决定了它必然和其它大量数字电路一起使用,所以在其PCB设计中除了需要考虑一般PCB 设计中要注意的问题之外,还要在多方面引起特别注意,尤其是在高速应用中[1].本文就针对多通道高速ADC电路设计的特点,以E2V公司的EV10AQ190芯片为例,重点讨论了包含多通道高速ADC的硬件电路设计中印刷电路板布局时所必须引起注意的问题,包括数字地和模拟地,数字电源和模拟电源的处理,ADC输入信号的隔离问题,采样时钟的处理和输出信号的阻抗匹配等问题[2].【期刊名称】《火控雷达技术》【年(卷),期】2013(042)003【总页数】5页(P90-94)【关键词】高速ADC;EV10AQ190;电磁兼容设计;隔离度;印刷电路板【作者】李军辉;简育华;袁子乔【作者单位】西安电子工程研究所西安710100;西安电子工程研究所西安710100;西安电子工程研究所西安710100【正文语种】中文【中图分类】TN8510 引言随着芯片技术的不断发展,ADC的采样频率已经从以前的MHz发展到当前的GHz。

伴随着ADC采样频率的不断提高,ADC的模拟输入信号频率和带宽也在不断提高,从视频信号到现在的中频甚至射频信号。

因此,用于低速ADC采样电路的一些设计方法已经不适用于高速ADC的采样电路[3]。

如何在高速ADC采样电路设计中提高ADC模拟输入信号各通道之间的隔离度变得尤为关键,对于数字地平面和模拟地平面的处理方式也非常关键。

对于高速ADC而言,模拟通道PCB上的每个过孔和走线都通过空间、电源平面和地平面对外进行电磁波的辐射;另一方面,由于高速ADC芯片的带宽都在GHz,它不仅容易受到其它通道模拟信号的干扰,也容易受到系统内或外界高速数字信号的电磁干扰。

所以,在多通道高速ADC电路的设计中,首要的问题就是解决多通道之间的互耦问题,这其中就主要是解决模拟部分地平面的传导耦合以及各通道之间的辐射干扰问题。

高速ADC抖动产生SNR问题解析

高速ADC抖动产生SNR问题解析

您在使用一个高速模数转换器(ADC) 时,总是期望性能能够达到产品说明书载明的信噪比(SNR) 值,这是很正常的事情。

您在测试ADC 的SNR 时,您可能会连接一个低抖动时钟器件到转换器的时钟输入引脚,并施加一个适度低噪的输入信号。

如果您并未从您的转换器获得SNR 产品说明书标称性能,则说明存在一些噪声误差源。

如果您确信您拥有低噪声输入信号和一种较好的布局,则您的输入信号频率以及来自您时钟器件抖动的组合可能就是问题所在。

您会发现“低抖动”时钟器件适合于大多数ADC 应用。

但是,如果ADC 的输入频率信号和转换器的SNR 较高,则您可能就需要改善您的时钟电路。

低抖动时钟器件充其量有宣称的1 微微秒抖动规范,或者您也可以从一个FPGA生成同样较差的时钟信号。

这会使得高速ADC 产生SNR 误差问题包括ADC 量化噪声、差分非线性(DNL) 效应、有效转换器内部输入噪声和抖动。

利用方程式 1 中的公式,您可以确定抖动是否有问题,公式给出了外部时钟和纯ADC 抖动产生的ADC SNR 误差。

在该方程式中,fIN 为转换器的输入信号频率。

另外,tJITTER-TOTAL 为时钟信号和ADC时钟输入电路的rms 抖动。

请注意,fIN 并非时钟频率(fCLK)。

外部时钟器件到ADC 的 1 微微秒抖动适合于一些而不。

时间交织adc原理

时间交织adc原理时间交织ADC原理随着科技的不断进步,模拟-数字转换器(ADC)在现代电子设备中扮演着至关重要的角色。

ADC的作用是将模拟信号转换为数字信号,使得我们能够对信号进行进一步的处理和分析。

而时间交织ADC则是一种常用的ADC架构,它能够提高转换速度和信号精度。

时间交织ADC的原理基于并行采样和时钟插入技术。

在传统的单通道ADC中,只有一个采样保持电路对信号进行采样。

而时间交织ADC通过同时使用多个采样保持电路,提高了采样速率。

通过将多个采样保持电路的输出交织在一起,可以得到更高的采样速度。

在时间交织ADC中,采样保持电路的数量通常是2的幂次方。

假设有N个采样保持电路,那么每个采样保持电路的采样速率就是总采样速率的1/N。

通过将这些采样保持电路的输出按照特定的顺序交织在一起,就可以得到整体的采样结果。

时间交织ADC的核心是时钟插入技术。

在每个采样周期内,时钟信号被插入到采样信号中,以保证采样的准确性和一致性。

具体来说,时钟信号会在采样开始前的瞬间插入到采样信号中,这样可以确保所有采样保持电路在同一时间点对信号进行采样。

通过这种方式,可以消除不同采样保持电路之间的时钟抖动和采样延迟,从而提高采样精度。

除了提高采样速度和精度,时间交织ADC还具有其他一些优势。

首先,时间交织ADC具有较低的功耗。

由于采样保持电路的数量较多,每个采样保持电路只需要处理较低速率的信号,从而降低了功耗。

其次,时间交织ADC具有较低的信号失真。

通过将多个采样保持电路的输出进行平均,可以减小信号失真和噪声。

此外,时间交织ADC还具有较低的抖动和延迟,能够更准确地还原原始信号。

然而,时间交织ADC也存在一些限制。

首先,它需要较多的采样保持电路,从而增加了系统的复杂性和成本。

其次,时间交织ADC对时钟信号的要求较高,需要保证时钟信号的稳定性和准确性。

此外,时间交织ADC在高频率信号的处理上可能会受到限制,因为采样时间较短可能无法完全捕捉到高频信号的细节。

高速adc电路设计及布局布线分析

《工业控制计算机》2019年第32卷第12期模数转换器(ADC)广泛用于各种应用中,尤其是需要处理模拟传感器信号的测量系统,比如测量压力、流量、速度和温度的数据采集系统。

为了能最大限度发挥高速ADC的性能,获得尽量高的有效位数与信噪比等关键参数,在高速采样电路系统设计中,低噪声、低相位失衡等因素是设计人员在设计采样电路时必须考虑的因素,这些参数的获得和提高取决高速AD采集系统的各个电路环节。

本文基于ADC的工作原理,结合工程设计经验,讨论了高速ADC电路设计时需要重点考虑的几个问题,包含模拟输入、输入时钟、基准电压源以及参考平面,希望能够对高速采集系统的设计工作起到一定的借鉴和指导作用。

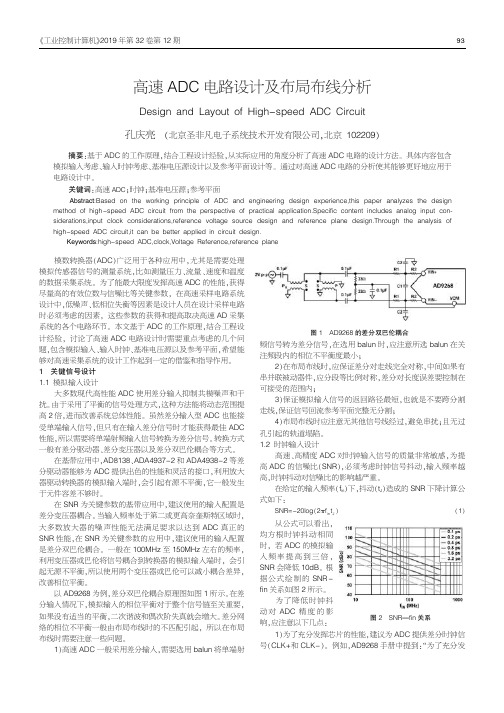

1关键信号设计1.1模拟输入设计大多数现代高性能ADC使用差分输入抑制共模噪声和干扰。

由于采用了平衡的信号处理方式,这种方法能将动态范围提高2倍,进而改善系统总体性能。

虽然差分输入型ADC也能接受单端输入信号,但只有在输入差分信号时才能获得最佳ADC 性能,所以需要将单端射频输入信号转换为差分信号。

转换方式一般有差分驱动器、差分变压器以及差分双巴伦耦合等方式。

在基带应用中,AD8138、ADA4937-2和ADA4938-2等差分驱动器能够为ADC提供出色的性能和灵活的接口,利用放大器驱动转换器的模拟输入端时,会引起有源不平衡,它一般发生于元件容差不够时。

在SNR为关键参数的基带应用中,建议使用的输入配置是差分变压器耦合。

当输入频率处于第二或更高奈奎斯特区域时,大多数放大器的噪声性能无法满足要求以达到ADC真正的SNR性能,在SNR为关键参数的应用中,建议使用的输入配置是差分双巴伦耦合。

一般在100MHz至150MHz左右的频率,利用变压器或巴伦将信号耦合到转换器的模拟输入端时,会引起无源不平衡,所以使用两个变压器或巴伦可以减小耦合差异,改善相位平衡。

以AD9268为例,差分双巴伦耦合原理图如图1所示。

在差分输入情况下,模拟输入的相位平衡对于整个信号链至关重要,如果没有适当的平衡,二次谐波和偶次阶失真就会增大。

时间交替超高速ADC技术解析

时间交替超高速ADC技术解析上网日期: 2010年02月25日采用时间交替模数转换器(ADC),以每秒数十亿次的速度采集同步采样模拟信号,对于设计工程师来说,这是一项极大的技术挑战,需要非常完善的混合信号电路。

时间交替的根本目标是通过增加转换器,在不影响分辨率和动态性能的前提下使采样频率增倍。

本文探讨时间交替模数转换器的主要技术难点,并提供切实可行的系统设计指导,包括可解决上述问题的创新性元件功能和设计方法。

本文还提供从7Gsps双转换器芯片“交替解决方案”测得的FFT结果。

最后,文章还描述了实现高性能所需的应用支持电路,包括时钟源和驱动放大器。

对更高采样速度的需求不断增加何时提高采样频率会更加有益,其中的原因又是什么呢?这个问题有多种答案。

模数转换器的采样速度基本上直接决定了可以在一个采样瞬间进行数字化的瞬时带宽。

尼奎斯特和香农采样定理证明了最大可用采样带宽(BW)相当于采样频率Fs的一半。

3GSPS模数转换器实现了在一次采样期内采集1.5GHz模拟信号频谱。

如果采样速度翻倍,尼奎斯特带宽也倍增至3GHz。

通过时间交替实现采样带宽倍增对于很多应用来说都是有益的。

例如,无线电收发器架构可以增加信息信号载波数,从而增加系统数据输出量。

采样频率倍增还可以提高采用飞行时间(TOF)原理的LIDAR测量系统的分辨率。

实际上,通过缩短有效采样期可以降低飞行时间测量值的不确定性。

数字示波器还需要高采样频率Fs/输入频率FIN比值,以准确采集复合模拟或数字信号。

要采集输入频率的谐波部分,就要求采样频率必须是输入频率(最大值)的倍数。

例如,如果示波器采样频率不够高,且更高阶谐波位于模数转换器的尼奎斯特带宽外,方形波将显示为正弦形。

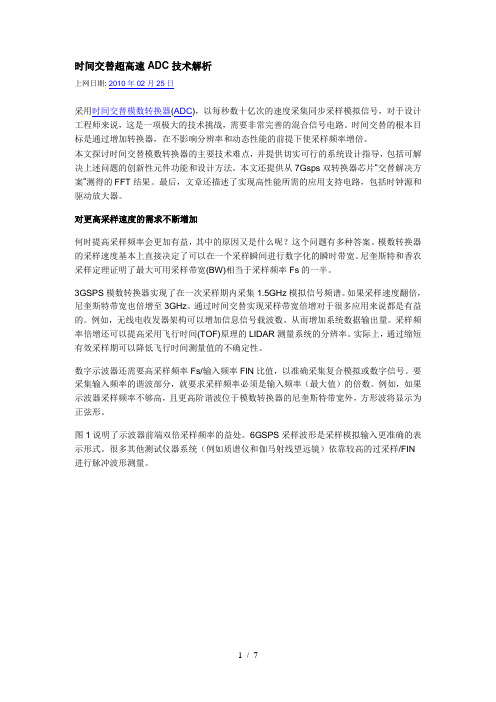

图1说明了示波器前端双倍采样频率的益处。

6GSPS采样波形是采样模拟输入更准确的表示形式。

很多其他测试仪器系统(例如质谱仪和伽马射线望远镜)依靠较高的过采样/FIN进行脉冲波形测量。

图1:以3GSPS和6GSPS采样的247.77MHz信号的时域值图。

SPI 接口的高速ADC控制电路

采用SPI 接口的高速ADC控制电路多数现行微处理器、DSP、现场可编程门阵列都集成了硬件和软件资源,它们支持两种常见接口标准——SPI(串行外设接口)和I2C /SMBus——中的一种或两种。

两种双线接口标准都有几个关键缺点。

例如,I2C 在标准模式、快速模式、高速模式中的吞吐速率分别是100kbps、400kbps或3.4Mbps,因此限制了快速外设数据转换器的采样速率。

不包括成帧比特和开销比特的话,一个100ksps的12比特ADC在接口上必须以至少1.2Mbps 来传输数据,只有I2C的高速模式才支持这个速度。

许多处理器和控制器目前不提供I2C高速模式,因此不能支持快速数据转换器。

I2C 的一个主要优点是减少了主机至目标的互连线路数量。

主机控制器只使用两根线,外加接地,就能应付目标器件和交换数据,而SPI 需要三根线——数据、时钟、芯片选择——外加接地。

多个SPI 目标器件能共享数据和时钟线路,但是每个器件都需要自己的专用芯片选择线路。

由于人们始终需要更高的采样速率和分辨率,因此I2C的有限速度也许会限制它在某些应用中的使用,这迫使设计师选择SPI。

然而,SPI需要主机控制器上有一根额外的I/O引脚。

在无法提供额外引脚,但是应用需要快速SPI总线转换器的情况下,你可以利用图1中的技巧。

例如,德州仪器公司的ADS7816包含200ksps的12比特采样ADC,它需要3Msps的性能,从而以200ksps速率连续采样(参考文献1)。

如果选择ADS7816的低电平有效CS (芯片选择)引脚,就会引起一个转换周期。

在数据传输期间转换并保持CS为低电平之后,CS在传输数据之后返回高电平,完成整个过程。

当时钟线路变为低电平时,它还使CS保持低电平状态。

峰值检测器(由D1、R1、C1组成)的时间常数确保了CS不会变为高电平,直到时钟线路保持高电平的持续时间超过一个时钟周期(图2)。

虽然时钟线路转换并从IC2取回数据,但CS保持为低电平,并且,在数据取回任务完成时,时钟线路变为高电平,CS随后也变为高电平,使电路为另一个转换周期准备就绪。

采样时钟抖动的原因及其对ADC信噪比的影响与抖动时钟电路设计

采样时钟抖动的原因及其对ADC信噪比的影响与抖动时钟电路设计ADC是现代数字解调器和软件无线电接收机中连接模拟信号处理部分和数字信号处理部分的桥梁,其性能在很大程度上决定了接收机的整体性能。

在A/D转换过程中引入的噪声来源较多,主要包括热噪声、ADC电源的纹波、参考电平的纹波、采样时钟抖动引起的相位噪声以及量化错误引起的噪声等。

除由量化错误引入的噪声不可避免外,可以采取许多措施以减小到达ADC前的噪声功率,如采用噪声性能较好的放大器、合理的电路布局、合理设计采样时钟产生电路、合理设计ADC的供电以及采用退耦电容等。

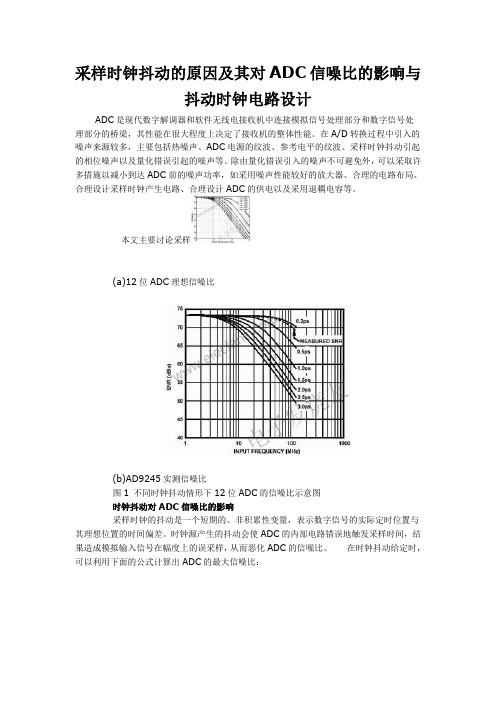

本文主要讨论采样(a)12位ADC理想信噪比(b)AD9245实测信噪比图1 不同时钟抖动情形下12位ADC的信噪比示意图时钟抖动对ADC信噪比的影响采样时钟的抖动是一个短期的、非积累性变量,表示数字信号的实际定时位置与其理想位置的时间偏差。

时钟源产生的抖动会使ADC的内部电路错误地触发采样时间,结果造成模拟输入信号在幅度上的误采样,从而恶化ADC的信噪比。

在时钟抖动给定时,可以利用下面的公式计算出ADC的最大信噪比:根据公式(2),图1分别给出了量化位数为12-bit时不同时钟抖动情形下ADC 理想信噪比和实测信噪比示意图。

由图1可以看出时钟的抖动对ADC信噪比性能的恶化影响是十分明显的,相同时种抖动情形下进入到ADC的信号频率越高,其性能恶化就越大,同一输入信号频率情形下,采样时钟抖动越大,则ADC信噪比性能恶化也越大。

对比图1中两个示意图可以看出实测的采样时钟抖动对ADC信噪比性能的影响同理论分析得到的结果是十分吻合的,这也证明了理论分析的正确性。

因此,在实际应用时不能完全依据理想的信噪比公式来选择A/D 转换芯片,而应该参考芯片制造商给出的实测性能曲线和所设计的采样时钟的抖动性能来合理选择适合设计需要的A/D转换芯片,并留出一定的设计裕量。

图2 一个实用的低抖动时钟产生电路两种实用的低抖动采样时钟产生电路时钟抖动的产生机制直接测量时钟抖动是比较困难的,一般采用间接测量的方法,为此本节首先给出时钟抖动的产生机制。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

此外,还可以得到,运算放大器的闭环增益为75.074 9 dB。0 dB对应的相位为一109.818°,所以它的相位裕度为70.182°。显然,该运算放大器的参数是比较好的。

图6为时钟占空比调整情况。从图中可以看出该DLL能调整占空比到49.4%(1.977 4/4≈49.5%)。实际上该时钟稳定电路在时钟周期4 ns时,能调节25%~75%的占空比接近于50%左右;而在时钟周期10 ns时,可调节的范围达到10%~90%。

该芯片总面积为0.74 mm×1.44 mm。其中,最左边的CLK一,CLK+为输入端,本文只用到CLK一一端作为输入端就足够了;右上角的CHKl、CHK2为输出的大管子;最中间为运算放大器。

4 结语

本文介绍了用一个简单的延迟锁相环来实现高速A/D转换器中的时钟稳定电路。该延迟锁相环具有两个作用:(1)调节采样时钟占空比;(2)控制采样时钟的抖动。本文以一些典型的基奉模拟IC为设计基础,着重对延迟锁相环电路的各个单元电路设计逐一进行了分析和研究,并对总体电路进行了功能和参数的模拟分析,其结果较为满意。在此基础上进行了工艺及版图设计和分析,在完成工艺版图设计后,采用DRC、ERC、Calibre、Extract和LVS等CAD工具对版图进行了参数提取及验证工作,保证了电路和版图的一致性。

式中:f为模拟输入频率;t为抖动。求解t则式(1)变为式(2)。如果已知工作频率和RSN要求,则式(2)就可确定时钟抖动要求

只要在模拟输入频率增大时观察到信噪比下降,就可以很方便地使用数据转换器(特别是模数转换器ADC),通过快速傅里叶变换(FFT)技术计算出信噪比。从总噪声中减去ADC产生的噪声,就可以估算出时钟抖动产生的噪声,一旦知道噪声系数,就可以计算出时间抖动。

1 时钟稳定电路

相位噪声和抖动是对同一种现象的两种不同的定量方式。在理想情况下,一个频率固定的完美的脉冲信号(以1 MHz为例)的持续时间应该恰好是1μs,每500 ns有一个跳变沿,但这种信号并不存在。,信号周期的长度总会有一定变化,从而导致下一个沿的到来时间不确定。这种不确定就是相位噪声,或者说是抖动。

抖动是对信号时域变化的测量结果,它从本质上描述了信号周期距离其理想值偏离了多少。通常,10 MHz以下信号的周期变动并不归入抖动一类,而是归入偏移或者漂移。数据转换器的主要目的要么是由定期的时间采样产生模拟波形,要么是由一个模拟信号产生一系列定期的时间采样。因此,采样时钟的稳定性是十分重要的。从数据转换器的角度来看,这种不稳定性,亦即随机的时钟抖动,会在模数转换器何时对输入信号进行采样方面产生不确定性。

高速ADC低抖动时钟稳定电路

0 引言

近年来,由于半导体技术、数字信号处理技术及通信技术的飞速发展,A/D、D/A转换器近年也呈现高速发展的趋势。随着数字信号处理技术在高分辨率图像、视频处理及无线通信等领域的广泛应用,对高速、高精度、基于标准COMS工艺的可嵌入式ADC的需求日益迫切。此外对于正在兴起的基于IP库设计和片上系统(SOC)集成研究来说,对低功耗、小面积、低电压以及可嵌入设计的ADC核心模块需求更甚。

2. 2电路仿真与分析

对图4的电路,在Cadence spectre环境下进行了仿真。输入电平的周期为4 ns,时钟占空比为45%,基准电压为3.3 V。运算放大器与电容c.组成电荷泵。电荷泵的输出见图5。时钟稳定电路稳定工作,Vout有30 mV的波动,Vout波动越小表示压控延迟线时钟输出的抖动越小。

由于高速、高精度A/D转换器(ADC)的发展,尤其是能直接进行中频采样的高分辨率数据转换器的上市,对稳定的采样时钟的需求越来越迫切。随着通信系统中的时钟速度迈人吉赫兹级,相位噪声和时钟抖动成为模拟设计中十分关键的因素。

为了保证电子系统的数据采集、控制反馈和数字处理的能力和性能,现代军用电子系统对A/D转换器的要求也越来越高。尤其是军事数据通信系统、数据采集系统对高速、高分辨率A/D转换器的需求在不断增加,时钟占空比稳定电路作为高速、高精度A/D转换器的核心单元,对转换器的信噪比(RSN)和有效位(ENOB)等性能起至关重要的作用,要保证高速、高精度A/D转换器的性能,必须首先保证采样编码时钟具有合适的占空比和很小的抖动。

缓冲放大器A实际上只是对时钟信号进行缓冲。当采样时钟频率低于DLL工作下限时,开关K1、K2向上闭合,DLL被旁路;开关K1、K2向下闭合,DLL开始作用,调节输入时钟信号相位。由于DLL具有延迟锁相的功能,因此能很好地控制时钟占空比,本设计中通过下文的具体电路能使输入时钟的占空比接近50%,抖动小于0.5 ps。

图7为延迟锁相环的输出眼图。其实在A、B之间有几百条上升沿。从图中可以看出,峰.峰值抖动为341.8l fs。对于250 M这个抖动值已经相当小了。

3 版图设计

利用JAZZ提供的PDK进行工艺接口,版图设计由该公司提供相应规则,具体针对线宽、接触孔、通孔、线距等作了相关规定,并且设计过程中充分利用该公司提供的Pcell作相应的版图设计,这样相应工作得到了很多的简化。具体的设计规则涉及IP问题,故略去。本文给出时钟稳定电路的整个版图,。

延迟线与振荡器相比受噪声较小,这是因为波形中被损坏的过零点在延迟线的末端就消失了,而在振荡器电路中又会再循环,因而产生更多的损坏;其次,DLL中控制电压的变化能迅速改变延迟时间。总之,PLL中用到的振荡器存在不稳定性和相位偏移的积累,因而在补偿时钟分别造成的时间延迟时,会降低PLL的性能。因此DLL的稳定性和稳定速度等问题比PLL要好。

目前,国外几个大公司所设计的A/D转换器中时钟占空比稳定电路的指标如表1所示。由于国内高速、高精度A/D转换器的设计技术、工艺技术和测试技术与国外先进水平还有一定的差距,同时研制的时钟稳定电路性能指标还不理想,目前正在研制的时钟占空比稳定电路频率为65 Msps,抖动为2 ps。

时钟占空比稳定电路框图,它由输入缓冲放大器A,开关Kl、K2和DLL组成。

延迟锁相环在普通锁相环(PLL)的基础上,用电压控制延迟线代替了压控振荡器,其结构框图。其中CKin和CK4之间的相位差用一个鉴相器来检测,产生成比例的平均电压Vcont,通过这个电压的负反馈来调节每一级的延时。对于大的环路增益,CKin和CK4之间的相位差很小,即这四级电路将时钟几乎准确地延时了一个周期,从而建立了准确的时钟沿间隔。这种电路结构被称为延迟锁相环,是为了强调它采用了一个电压控制延迟线电路而不是VCO。实际上,为获得无穷大的环路增益,需要在PD和LPF之间插入电荷泵。

从数据转换器的角度来看,编码带宽可扩展到数百兆赫。在考虑构成数据转换器时钟抖动噪声的带宽时,其范围是从直流到编码的带宽,这远远超过制造商常常当作标准时钟抖动测量值引用的12kHz~20 MHz典型值。由于与抖动有关的是宽带转换器噪声增大,所以只要观察数据转换器噪声性能的下降,就可很方便地评估时钟抖动。式(1)可确定由于时钟抖动而产生的信噪比(RSN)极限

ADI产品与其他公司产品相比之所以能提高采样性能,主要得益于对DCS电路的改进。DCS电路担负着减小时钟信号抖动的作用,而采样时序就取决于时钟信号。各家公司过去的DCS电路只能将抖动控制在0.25 ps左右,而高性能新产品AD9446和LTC2208则将抖动降低到50 fs左右。通常降低抖动就能够改善信噪比,这样便提高了有效分辨率(ENOB:有效比特数),从而在达到16 bit量子化位数的同时,实现100 Msps以上的采样速率。如果不控制抖动就提高采样速率的话,将降低ENOB,无法获得希望的分辨率,也无法提高量子化位数。随着高性能A/D转换器的发展,DCS电路向更高速度、更小抖动和稳定方像是运算放大器的启动电路,在运算放大器不工作时对电容C1充电。电阻R1和电容C1构成一个RC滤波器,对信号起到滤波的作用。m4、m5、m6三个晶体管构成DLL的延迟线(VCDL)。在这个电路中只需要一级延迟就足够了。在这个延迟线旁边的电容C2的值越大,则延迟越多。C2旁边三个反相器构成一个锁存结构,它的主要作用就是输出一个比较理想的方波。

2 电路设计

2.1 电路原理图

图4中,虚框a中的电路为鉴相器(PD),S为鉴相器的控制端,只有为低电平时,鉴相器才起作用。压控延迟线的输出端VCDLout为鉴相器的输入端,这个信号与时钟信号CLK进行比较,得出输出信号A。由于S端低电平有效,CLK信号就是与它的反相延迟信号与非进入后面的锁存结构。其实就是检测下沿与另一个下沿组成一个占空比接近50%的时钟信号。A信号经过一个电阻R传入电荷泵中(其实在鉴相器的输出端可以加一个反相器再加一个电容滤波)。虚框b为电荷泵,由一个运算放大器组成。其中F端接一个电压值为基准的一半的电压,即为1.65 V。