基于MAXPLUSii的数字钟实验(含源程序代码)

max+plus2数电实验报告小红书

max+plus2数电实验报告小红书实验目的实验原理实验器材实验步骤实验结果实验分析实验结论实验目的本次实验旨在通过实践探究max+plus2数电的工作原理和应用,在实验中加深对数电原理的理解,同时提高实验操作能力和解决问题的能力。

实验原理max+plus2数电是一种常用的数字电路开发板,它集成了多种数字电路模块,可进行逻辑设计和数字信号处理等实验。

其主要原理是通过编程控制和数字信号的处理,在实验中能实现各种数字逻辑电路的功能。

实验器材本次实验所需的器材如下:1. max+plus2数电开发板2. 电源线3. 连接线4. 逻辑门模块5. LED灯模块6. 开关模块实验步骤1. 将max+plus2数电开发板连接到电源线,并将电源线插入电源插座,确保电源正常供应。

2. 根据实验设计的逻辑电路图,将逻辑门模块、LED灯模块和开关模块连接到max+plus2数电开发板的相应端口。

3. 打开开发板的电源开关,确保电源正常供电。

4. 编程控制max+plus2数电开发板,将相应的逻辑电路图转化为代码,并加载到开发板中。

5. 通过操作开发板上的开关,观察LED灯的亮灭情况,检查逻辑电路的功能是否正常。

实验结果经过一番调试和观察,实验结果如下:1. 当开关处于某个特定状态时,LED灯亮起。

2. 当开关处于其他状态时,LED灯熄灭。

实验分析通过实验结果的观察和分析,我们可以得出以下结论:1. max+plus2数电开发板可以通过编程控制,实现各种逻辑电路的功能。

2. 实验中所使用的逻辑门模块、LED灯模块和开关模块均能正常工作,与开发板配套使用效果良好。

3. 通过实验,我们进一步理解了逻辑电路的原理和工作方式。

实验结论本次实验通过实践操作max+plus2数电开发板,验证了其能够实现逻辑电路的功能。

实验结果表明,max+plus2数电开发板具有良好的稳定性和可靠性,可以作为数字电路实验的理想工具。

通过这次实验,我们不仅提高了实验操作能力,也深化了对数电原理的理解,为进一步学习和应用数字电路奠定了基础。

实验一MAX+PLUSⅡ软件的使用

实验一MAX+PLUSⅡ软件的使用一、实验目的:1、学习VHDL语言的基本指令及编程方法。

2、熟悉在PC机上运用MAX+PLUSⅡ软件和EPLD进行电路设计的设计和仿真过程。

二、实验设备:PC机三、实验内容:1、设计一个2选1数据选择器,并验证其功能。

用VHDL语言进行设计,并仿真设计结果。

真值表如下所示:2、用VHDL语言输入法设计一个四舍五入判别电路,其输入为8421BCD码,要求当输入大于或等于5时,判别电路输出为1;反之为0。

四、实验步骤:(一)2选1数据选择器的设计1、采用文本编辑器输入2选1数据选择器VHDL语言源程序,建立工程。

VHDL语言源程序如下所示:library ieee;use ieee.std_logic_1164.all;entity mux21 isport(a,b: in std_logic;s: in std_logic;y: out std_logic );end mux21;architecture mux_arch of mux21 isbeginy<=a when s='0' elseb when s= '1';end mux_arch;2、进行编译后,仿真结果如下所示:a、b为输入端,s为控制端,当s为0时,输出与a的值一致,反之与b的值一致。

(二)四舍五入判别电路的设计1、采用文本编辑器输入四舍五入判别电路VHDL语言源程序,建立工程。

VHDL语言源程序如下所示:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY m45 ISpORT(din: IN STD_LOGIC_VECTOR(3 DOWNTO 0);q : OUT STD_LOGIC);END ;ARCHITECTURE ART OF m45 ISBEGINq<= '1' WHEN din>=5 ELSE'0';END ;2、进行编译后,仿真结果如下所示:输入为0~4时,输出y为低电平,输入为5~15时输出为高电平,实现了四舍五入的功能。

MAX+plusⅡ_实验之入门教学

2.编译

单击MAX+plusⅡ→Compiler选项,即可打开编译器。另外,也 可以单击File→Project→Save & Compiler(保存文件同时编译)选项, 系统将把当前设计的若干文件存盘后,自动弹出编译器窗口,单击 【Start】按钮,编译器就开始对当前设计进行编译。

编译完成后,系统弹出错误和警告信息统计对话框,单击【确定】

3.元件符号的复制和移动

可单击准备复制的元件或用鼠标对该元件画矩形框(定位于某 一点,按下鼠标左键并向元件对角方向拖动),元件的轮廓变成红 色的粗实线,表示已经选中该元件,然后按住〈Ctrl〉键,对该元 件拖动,即可拖出一个被复制的元件。 元件需要移动时,可用鼠标拖动图形编辑区中的元件图形符号, 元件就能随着鼠标的滑动而任意移动。左键释放,则图形元件定位。 若要同时移动多个元件,可以用鼠标左键拉出一个大的矩形框,把 要移动的元件都包围起来。这样多个元件同时被选中,就可以一起 被移动了。

单击标题栏的Options→Snap to Grid(对齐网格)去掉前面的对 勾,以方便设置输入电平。

4.波形输入

选中 输入端,如: 然后点击窗口左侧的时钟信号源图标

Hale Waihona Puke 出现如图所示的对话框。例如:选择初始电平为“0”,时钟周期为“200ns”,倍数为“1” (时钟周期倍数只能为整数倍),单击 OK 确认。

打开MAX+PLUS II,输入设计项目和存盘 打开 ,

新建一个设计文件 使用原理图输入方法设计 必须选择打开原理图编辑器

进入MAX+plusII,建立一个新的设计文件 , 进入

选择Graphic Editor File选项后,接受gdf的默认扩展名,单击【OK】按 钮确认。进入图形编辑器的编辑环境。。

max+plus2教程

EDA(VHDL & FPGA)实验指导教程编者林海波长春工程学院电子信息教研室前言本实验指导教程是EDA(VHDL & FPGA)上机实验指导教材,上机实验前,学生应依照教师指定的实验项目,认真预习实验内容,提前确定实验方案、初步设计实验项目的逻辑电路图或编写、设计VHDL程序,编制VHDL程序清单。

上机实验是一个验证和调试过程,只有充分的预习才能最大的发挥学习效果。

学生在实验教学中要认真依据要求完成每个实验项目,并按照要求详细撰写本书中指定实验项目的实验报告。

教师批阅后,将报告发回。

学生所获得的成绩将作为平时上机实验成绩的一部分,记入期末的考核成绩。

在期末必须上交全部实验报告,并装订存档,不及时交回者,实验成绩记为零分。

本实验指导教程可以作为《VHDL与数字系统设计》课程的实验指导书使用,也可以作为《EDA(VHDL)课程设计》的参考书使用。

《VHDL与数字系统设计》课程组2009年5月第一章 MAX+PLUS Ⅱ EDA 软件操作第一节 逻辑设计的输入方法逻辑设计的输入方法有图形输入、文本输入等。

输入方法不同,生成的文件格式也有所不同。

我们分别以图形输入法和文本输入法介绍MAX+plus II 软件的使用方法。

1.1 图形设计输入法我们将用一简单的实例介绍该输入法。

启动MAX+plus II ,该管理器窗口被打开。

1. 项目的建立用户的每个独立设计都对应一个项目,每个项目可包含一个或多个设计文件,其中有一个是顶层文件,顶层文件的名字必须与项目名相同。

编译器时对项目中的顶层文件进行编译,所以必须确定一个文件作为当前项目。

对于每个新的项目应该建立一个单独的子目录,当指定项目名称时,也就同时指定了保存该设计项目的子目录名。

建立项目名称的步骤如下:1.在File 菜单中选择Project 的Name 项(图1.1),将出现图1.2对画框。

图1.1图1.22.在Project Name 框内,键入设计项目名(注意:一定是英文名)和所选的路径,单击OK 。

实验一 MAX-plusII及开发系统使用

实验一 MAX –plusII 及开发系统使用一、实验目的1、 熟悉MAX-plus Ⅱ的使用方法,以及EDA 的基本设计流程;2、 掌握基于文本(VHDL )和原理图输入方法设计简单的组合电路3、 初步掌握层次化设计的方法4、 熟悉DXT-B Ⅲ型EDA 试验开发系统的使用 二、主要实验设备PC 机一台,DXT-B3 EDA 实验系统一台。

三、实验原理EDA 技术系列实验是建立在数字电路基础上,采用先进的EDA 技术完成数字系统设计的一个更高层次的设计性实验。

它是借助大规模可编程逻辑器件(C PLD/FPGA ),采用在系统可编程技术(ISP ),利用电子设计自动化软件和硬件描述语言,在计算机平台上完成系统的设计、编译、仿真、逻辑综合、布局布线,并下载到大规模可编程逻辑器件。

最终完成专用集成电路(ASIC )或片上数字系统(SOC )的设计。

EDA 技术设计主要是在计算机平台上进行,因此实验方式,实验手段和实验仪器与传统的实验有很大的区别,主要体现在以下几个方面:1、 实验的核心部件是大规模可编程逻辑器件,实验的设计基本只针对CPLD/FPGA 进行。

通过相应的管脚安排,利用实验箱外围的辅助电路进行设计的硬件测试和验证。

2、 大规模可编程逻辑器件可重复下载,基本没有耗材;3、 设计的主要过程在计算机上进行,自动化程度高,人机交互性好,修改、验证实验简单.四、Max_plus Ⅱ 10.0的使用。

max+plus Ⅱ软件基本设计流程如图1-1所示:(一)新建项目文件一般可以是图形文件(文件后缀.gdf )或由硬件描述语言编写的文本文件(VHDL 编写的文件后缀为.vhd ,Verilog HDL 编写的文件后缀为.v )。

具体操作过程如下:在File 下拉菜单中选择New 将跳出如图1-2所示新建文件类型选择对话框,然后选择需要建立的文件类型。

四种文件类型分别为:图形编辑文件、符号编辑文件、文本图1-2新建文件类型图1-1 EDA 项目设计流程图编辑文件和波形编辑文件。

maxplus2简明教程三

第三章原理图输入法设计时序逻辑电路时序逻辑电路是数字逻辑电路中最重要的一类,一个时序逻辑电路包含组合逻辑网络和存贮单元两大部分,其中组合逻辑网络部分可用译码器、数据选择器或其他组合网络模块实现,而存储单元部分则用计数器、移位寄存器或通用寄存器等实现。

本章将以一个简易数字钟的分钟和秒部分为例学习如何通过MAX+plus II软件的图形编辑器,利用原理图库中元件进行时序逻辑电路的设计输入,如何用波形编辑器进行输入激励波形输入,再用MAX+plus II的模拟器和时延分析器进行逻辑验证和分析。

并学习用层次显示工具进行自顶向下的设计。

3.1 设计输入和编译通过图形编辑器进行时序逻辑电路设计输入的过程和第二章中组合逻辑设计输入的过程是一样的。

一个简易数字钟的分钟和秒部分都可以认为是一个模60计数器,而模60计数器可以通过两个模10计数器采用同步置0法加上适当的反馈完成。

图3.1 74160的元件符号表3.1 74160的功能表输入输出CLK LDN CLRN ENP ENT D C B A QD QC QB QA RCOX X L X X L L L L L↑L H X X d c b a d c b a *↑H H X L QD QC QB QA *↑H H L X QD QC QB QA L↑H H H H L L L L L↑H H H H L L L H L↑H H H H L L H L L↑H H H H L L H H L↑H H H H L H L L L↑H H H H L H L H L↑H H H H L H H L L↑H H H H L H H H L↑H H H H H L L L L↑H H H H H L L H H* RCO = QD & QA & ENT和组合逻辑电路的设计输入一样,先要建立项目和图形输入文件(示例中两个文件名用的是MOD60),再调入元件符号。

基于MAX+PLUSII的数字电子钟的逻辑设计

Ab t a t Ast e d e e i fc mp trtc n lg n hepu s i fh g u l y l e o e p e, u o td ee . s r c : h e p nngo o u e e h o o a d t ru to ih q a i i fp o l a tmae l c y t f to i q i me tc me i t en whih gv srs o t e dicp i e o i ia lcr n c cr u t. w lcr ni r n c e u p n a n o b i g, c ie ie t h s iln fd g tlee to i ic is No e e to c a tmai n d sg swi ey us d i o e o d a p in e ,es r q a e d sg p n tai g i t v r s e to u o to e in i d l e n h us h l p la c s liu e s u r e in, e er tn n o e ey a p c f

概括地说 , 它是一种用数字显示时间的设备 , 具有高准确性 、 智能化的特性。 个完整 的数 字 电子钟应该包 括如 下几 个部分 : 分秒 计时 器 、 时钟 计数 器 、 选择 电路 和保 持 电路。本设 计项 目是用 6个数 码管显示 时分 秒 的电路 ( 时以 1 时计时制 )首先将 手动或 自动输 入 的脉冲信 号送人 小 2小 ,

时钟电路的MAX+PLUSⅡ软件仿真

转换部 分。假设数码管高电平时显示 , 则采 用真值 表实现了码元转 换部分。 3软件具体 设计 实现 .

3 1计 时 部 分 .

收藕 日期 : 0 —1 —3 2 1 2 0 0

维普资讯

砌

1

海

军

工

程

大

学

电

子

工

一 里

学

院

学

报

总第 6 8捌

At a公 司的 MA lr e x+P U H开 发 系统 是 一 个完 全集 成 化 、 学 易用 的 可 编 程逻 辑 设 计 环 境 , 可 以 在 多 LS 易 它

种平台上运行。ML P U I所提供 的灵活性和高教性是无可 比拟 的。其丰富 的图形界 面, , X+ L SI 辅以完整 的、 可

,

由分钟进位驱动小时 , 秒钟和分钟由模 6 模块组成 , 0 小时由模 2 模块组成 。其中模 6 4 0元件模块 和模 2 元 4 件模块均 由模 l 元件模块 和相关的门构成。 O

模 1 件 模 块 的程 序 清 单 如下 : O元

S D SGN ml UB E I 0

A s a:'d a e t d c s t emr so h r b m ̄ r sp p ri r u e e fa e fA e aMAx + P USIp oj n n belgcd v lp n y tm.I v te i no h L ] r ̄a u a l o i e eo me t s s e t ∞ h ti d l n ot r e l a o ulig co kc ruth  ̄n h n t n fc u i g.s tn ,a d a n L ig t n te h t l a d sf d g wa erai t n o b i n lc i i a gte f ci s I ont zi f d c 4 u o 】 n et g n n o mc me i h i n i

红用maxplus绿灯30秒倒计时计数器代码

红用maxplus绿灯30秒倒计时计数器代码以下是使用 MAX+PLUS II 进行 30 秒倒计时计数器的示例代码:

```

// 定义计数器变量

unsigned int count = 0;

// 初始化计数器

void setup() {

// 设置计数器初始值为 0

count = 0;

// 设置绿灯闪烁频率为 250 Hz

pinMode(13, OUTPUT);

digitalWrite(13, HIGH);

delay(250);

digitalWrite(13, LOW);

delay(250);

}

// 更新计数器值

void loop() {

// 计数器递增

count++;

// 如果计数器值大于 30,则重置计数器并重新开始倒计时

if (count > 30) {

count = 0;

}

// 绿灯闪烁

if (count % 250 == 0) {

digitalWrite(13, HIGH);

delay(500);

digitalWrite(13, LOW);

delay(500);

}

}

```

上述代码使用 MAX+PLUS II 的 COUNT 指令来计算倒计时时间,其中 COUNT 指令的参数为 30,表示需要倒计时 30 秒。

代码中的

`setup()` 函数和 `loop()` 函数分别用于设置计数器和绿灯闪烁

的频率和周期。

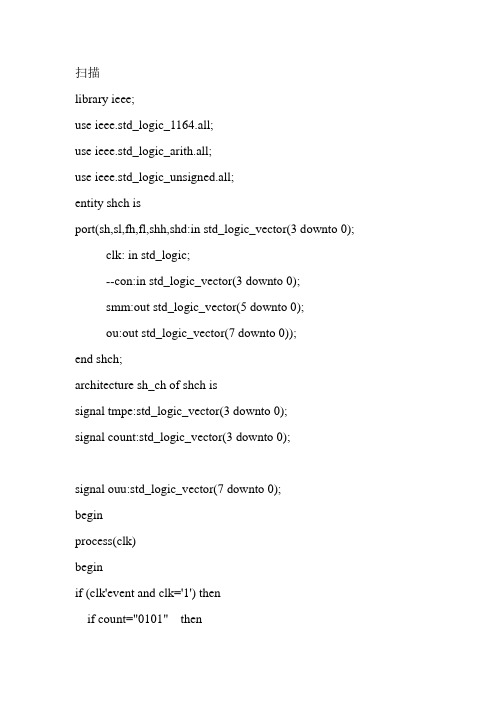

使用maxplus2用VHDL语言设计EDA数字钟

扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity shch isport(sh,sl,fh,fl,shh,shd:in std_logic_vector(3 downto 0);clk: in std_logic;--con:in std_logic_vector(3 downto 0);smm:out std_logic_vector(5 downto 0);ou:out std_logic_vector(7 downto 0));end shch;architecture sh_ch of shch issignal tmpe:std_logic_vector(3 downto 0);signal count:std_logic_vector(3 downto 0);signal ouu:std_logic_vector(7 downto 0);beginprocess(clk)beginif (clk'event and clk='1') thenif count="0101" thencount<="0000";elsecount<=count+'1';end if;end if;end process;smm<="011111" when count="0101" else "101111" when count="0100"else"110111" when count="0011"else"111011" when count="0010"else"111101" when count="0001"else"111110" when count="0000";tmpe<=sl when count="0000" elsesh when count="0001" elsefl when count="0010" elsefh when count="0011" elseshd when count="0100" elseshh when count="0101" ;process(tmpe)begincase tmpe iswhen "0000"=>ouu<="00000011"; when "0001"=>ouu<="10011111"; when "0010"=>ouu<="00100101"; when "0011"=>ouu<="00001101"; when "0100"=>ouu<="10011001"; when "0101"=>ouu<="01001001"; when "0110"=>ouu<="01000001"; when "0111"=>ouu<="00011111"; when "1000"=>ouu<="00000001"; when "1001"=>ouu<="00001001"; when others=>ouu<="00000011"; end case;end process;ou<=ouu;end sh_ch;分频器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all; entity jsq_1000 isport(clk:in std_logic;cs: out std_logic);end jsq_1000;architecture jsq of jsq_1000 is beginprocess(clk)variable count :integer;beginif (clk'event and clk='1') thenif count<1024 thencount:=count+1;cs<='0';elsecount:=0;cs<='1';end if;end if;end process;end jsq;时分秒计数器library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity sfsh isport(rst, clk:in std_logic;sh,sl,fh,fl,shh,shd:out std_logic_vector(3 downto 0));end sfsh;architecture sf_sh of sfsh issignal shw,slw,fhw,flw,shhw,shdw:std_logic_vector(3 downto 0); signal cs,ch: std_logic;beginprocess(clk,rst)beginif rst='0' thenshw<="0100";slw<="0000";elsif (clk'event and clk='1') thenif (shw = "0101") thenif (slw = "1001") then shw<="0000";slw<="0000";cs<='1';elseslw<=slw+1;cs<='0';end if;elsif (slw="1001") then slw<="0000";shw<=shw+1;cs<='0';elseslw<=slw+1;cs<='0';end if;end if;end process;process(cs,rst)beginif rst='0' thenfhw<="0101";flw<="1001";elsif (cs'event and cs='1') then if (fhw = "0101") thenif (flw = "1001") thenfhw<="0000";flw<="0000";ch<='1';elseflw<=flw+1;ch<='0';end if;elsif (flw="1001") thenflw<="0000";fhw<=fhw+1;ch<='0';elseflw<=flw+1;ch<='0';end if;end if;end process;process(ch,rst)beginif rst='0' thenshhw<="0010";shdw<="0011";elsif (ch'event and ch='1') then if (shhw = "0010") thenif (shdw = "0011") then shhw<="0000";shdw<="0000";elseshdw<=shdw+1;end if;elsif (shdw="1001") then shhw<=shhw+1;shdw<="0000";elseshdw<=shdw+1;end if;end if;end process;sh<=shw;sl<=slw;fh<=fhw;fl<=flw;shh<=shhw;shd<=shdw;end sf_sh;元件例化library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity shzh isport(clk,rst: in std_logic;ou:out std_logic_vector(7 downto 0);smmm:out std_logic_vector(5 downto 0));end shzh;architecture sh_zh of shzh iscomponent shchport(sh,sl,fh,fl,shh,shd:in std_logic_vector(3 downto 0);clk: in std_logic;smm:out std_logic_vector(5 downto 0);ou:out std_logic_vector(7 downto 0));end component;component sfshport(rst, clk:in std_logic;sh,sl,fh,fl,shh,shd:out std_logic_vector(3 downto 0)); end component;component jsq_1000port(clk:in std_logic;cs: out std_logic);end component;signal coo:std_logic;signal sshh:std_logic_vector(3 downto 0);signal ssll:std_logic_vector(3 downto 0);signal ffhh:std_logic_vector(3 downto 0);signal ffll:std_logic_vector(3 downto 0);signal sshhh:std_logic_vector(3 downto 0);signal sshdd:std_logic_vector(3 downto 0);beginu2:jsq_1000 port map(clk,coo);u3:sfsh port map(rst,coo,sshh,ssll,ffhh,ffll,sshhh,sshdd);u4:shch port map(sshh,ssll,ffhh,ffll,sshhh,sshdd,clk,smmm,ou); end sh_zh;。

基于MAX plus II 的实时数字钟设计

综合课程设计题 目 基于MAXPLUSII 的实时数字 设计学生姓名 白阳专业名称 电子信息工程指导教师 王晓利2010 年 6 月 25 日1 总体电路设计要求和思想1.1掌握十进制,模12进制计数器的设计方法;1.2巩固多位共阴级扫描显示数码管的驱动及编码;1.3对利用VHDL硬件描述语言设计相关模块有一定的了解;1.4掌握EDA技术的层次化设计方法。

2 设计原理2.1模块设计秒——60进制BCD码计数;分——60进制BCD码计数;时——24进制BCD码计数;整个计数器具有清零,调时功能。

2.2七段译码器VHDL语言文本编辑如下(*.tdf格式),之后生成名7segment1的逻辑符号。

操作为:Flie -> creat default symbol,则可以将用户刚刚设计的电路形成一个模块符号h_adder。

SUBDESIGN 7SEGMENT1( i3,i2,i1,i0:input;a,b,c,d,e,f,g:output;)begintablei3,i2,i1,i0 => a,b,c,d,e,f,g;0,0,0,0 =>0,0,0,0,0,0,1;0,0,0,1 =>1,0,0,1,1,1,1;0,0,1,0 =>0,0,1,0,0,1,00,0,1,1 =>0,0,0,0,1,1,00,1,0,0 =>1,0,0,1,1,0,00,1,0,1 =>0,1,0,0,1,0,00,1,1,0 =>0,1,0,0,0,0,00,1,1,1 =>0,0,0,1,1,1,11,0,0,0 =>0,0,0,0,0,0,01,0,0,1 =>0,0,0,0,1,0,0end table;end;3.关于Max plus II的操作。

3.1Max plus iiMAX+plusII提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。

报告

设计名称:

十二小时制数字钟

指导老师:

班 级:

学 号:

姓 名:

实 验 报 告

实验名称

十二小时制数字钟

设计要求

根据所学知识,通过MAX+plus 2软件设计12小时制数字钟,使得计时为12小时,分和秒同为60的计数,实现61和74ls160计数器芯片集连,完成模12及模60的记数功能,通过2个模60及1个模12的模块集连,完成12小时制数字钟的设计1s的CP时钟信号由EPM7128SLC84-15芯片上1KHZ的时钟源通过模1000的模块产生,秒计数器和分计数器均由模60计数器组成,分别完成对秒和分的计时;时计数器由模12计数器组成,完成对小时的计数。时钟各个位上的4位二进制代码通过7447芯片译码后连接到数码管

实验内容/

实验步骤

(结果)

各个模块图及内容:

12小时计时模块:

打包后的模12

模60

打包后模60如图:

将用7447做成的译码器进行打包

用2个74161计数器芯片,用预置法集连完成模60的功能,留出清零端,再用1个74161计数器芯片,用预置法级连完成模12的功能,留出清零端,仿真并观察输出波形,确认无误后将模块保存并分别打包,模12的为小时的记数功能,模60的为分和秒的记数功能。

分频器如图

打包后的分频器便于仿真

时钟的最小CP信号为1HZ,而EPM7128SLC84-15芯片的时钟源为1KHZ,因此我们需要自制分频器来得到1HZ的CP信号。

将核心器件进行连接锁管脚,将其下载到开发板上,观察结果。结果显示12小时进制无误,复位功能正常,实验成功。

最后的时钟图如下

实验总结及问题和问题的解决方法

由于MAX+plus 2操作步骤不熟,会导致经常忘记设置到顶层文件,导致波形出不来,会多次进行修改。

基于MAXPLUSii的数字钟实验(含源程序代码)

源程序与仿真图CNT24library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt24 isport(clk,rst:in std_logic;co:out std_logic;qh,ql :out std_logic_vector(3 downto 0)); end cnt24;architecture behave of cnt24 issignal tmpl,tmph:std_logic_vector(3 downto 0);beginprocess(rst,clk)beginif(rst='1') then tmpl<="0000";tmph<="0000";co<='0';elsif(clk'event and clk='1')thenif(tmpl=9)thentmpl<="0000";tmph<=tmph+1;else tmpl<=tmpl+1;if(tmph=2) thenif(tmpl=3) then tmpl<="0000";tmph<="0000";co<='1';else tmpl<=tmpl+1;co<='0';end if;end if;end if;end if;ql<=tmpl;qh<=tmph;end process;end behave;CNT60library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt60 isport(clk,rst:in std_logic;co:out std_logic;qh,ql :out std_logic_vector(3 downto 0)); end cnt60;architecture behave of cnt60 issignal tmpl,tmph:std_logic_vector(3 downto 0);beginprocess(rst,clk)beginif(rst='1') then tmpl<="0000";tmph<="0000";co<='0';elsif(clk'event and clk='1')thenif(tmpl=9)then tmpl<="0000";if(tmph=5) then tmph<="0000";co<='1';elsetmph<=tmph+1;co<='0';end if;else tmpl<=tmpl+1;co<='0';end if;end if;ql<=tmpl;qh<=tmph;end process;end behave;DIV1000Library IEEE;Use IEEE.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use IEEE.std_logic_arith.all;Entity div1000 isPort( clk: in std_logic;--from system clock(1KHz)f1hz: out std_logic);-- 1Hz output signalend div1000;architecture arch of div1000 issignal count : integer range 0 to 499;--count from 0 to 499-local sisignal temp:std_logic;beginprocess (clk)beginif rising_edge(clk) thenif count>=499 thentemp<=not temp;count<=0;else count<=count+1;end if;end if;end process;f1hz<=temp;end arch;JIAOZHUNlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jiaozhun isport(clk1,clk2,qo:in std_logic;co:out std_logic);end jiaozhun;architecture behave of jiaozhun isbeginprocess(qo,clk1,clk2)beginif(qo='0') then co<=clk1;else co<=clk2;end if;end process;end behave;SCAN6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity scan6 isport(clk:in std_logic;a1,a2,a4,a5,a7,a8:in std_logic_vector(3 downto 0);seg7: out std_logic_vector(6 downto 0);bt : out std_logic_vector(7 downto 0)); end scan6;architecture behav of scan6 issignal cnt8:std_logic_vector(2 downto 0); signal a: std_logic_vector(3 downto 0); beginprocess(cnt8)begincase cnt8 iswhen "000"=>bt<="00000001";a<=a1; when "001"=>bt<="00000010";a<=a2; when "010"=>bt<="00000100";a<="1010"; when "011"=>bt<="00001000";a<=a4; when "100"=>bt<="00010000";a<=a5; when "101"=>bt<="00100000";a<="1010"; when "110"=>bt<="01000000";a<=a7; when "111"=>bt<="10000000";a<=a8; when others=>null;end case;end process ;process(clk)beginif (clk'event and clk='1')then cnt8<=cnt8+1;end if;end process ;process(a)begincase a iswhen "0000"=>seg7<="1111110";when "0001"=>seg7<="0110000";when "0010"=>seg7<="1101101";when "0011"=>seg7<="1111001";when "0100"=>seg7<="0110011";when "0101"=>seg7<="1011011";when "0110"=>seg7<="1011111";when "0111"=>seg7<="1110000";when "1000"=>seg7<="1111111";when "1001"=>seg7<="1111011";when "1010"=>seg7<="0000001";when others=>null;end case;end process ;end behav;TOPCNT24JIAOZHUNSCAN6。

基于MAX+plus II 的数字钟的设计

摘要电子设计自动化Electronic Design Automation (以下简称EDA)技术已经代替传统的集成电路设计方法,逐渐成为电子系统设计者的主要设计手段。

MAX+plus II是EDA仿真软件之一。

具有功能强大、界面友好和使用方便等特点,是目前教育与工业界流行的集成电路辅助设计软件。

MAX+plus II 软件是一种在电子技术工程与电子技术教学中广泛应用的优秀计算机仿真软件,被誉为“计算机里的电子实验室”。

本文介绍了一种基于MAX+plus II 软件设计数字钟的方法。

关键词:EDA MAX+plus II 软件数字电子钟AbstractElectronic Design Automation Electronic Design Automation (EDA of the following abbreviation) technology has replaced the traditional method of integrated circuit design, has gradually become the main design method of electronic system design.MAX+plus II is one of EDA simulation software.With powerful function, friendly interface and easy to use and other characteristics, is the current education and industry popular integrated circuit computer aided design software.MAX+plus II is a technology in electronic engineering and electronic technology teaching in extensive application of excellent computer simulation software, known as the "computer electronic laboratory".This paper introduced one kind based on the MAX+plus II software design method of digital clock.Key words:EDA MAX+plus II software digital electronic clock基于EDA的多功能数字钟电路设计前言随着计算机在国内的逐渐普及,计算机已经渗入到每一个行业,计算机与每个工作领域紧密地联系在了一起。

基于MAX+plusII数字时钟设计(程序)

数字秒表设计实验任务书一、设计实验目的:在MAX+plusII软件平台上,熟练运用VHDL语言,完成数字时钟设计的软件编程、编译、综合、仿真,使用EDA实验箱,实现数字秒表的硬件功能。

二、设计实验说明及要求:1、数字秒表主要由:分频器、扫描显示译码器、一百进制计数器、六十进制计数器(或十进制计数器与6进制计数器)、十二进制计数器(或二十四进制计数器)电路组成。

在整个秒表中最关键的是如何获得一个精确的100H Z计时脉冲,除此之外,数字秒表需有清零控制端,以及启动控制端、保持保持,以便数字时钟能随意停止及启动。

2、数字秒表显示由时(12或24进制任选)、分(60进制)、秒(60进制)、百分之一秒(一百进制)组成,利用扫描显示译码电路在八个数码管显示。

3、能够完成清零、启动、保持(可以使用键盘或拨码开关置数)功能。

4、时、分、秒、百分之一秒显示准确。

三、数字时钟组成及功能:1、分频率器:用来产生100H Z计时脉冲;2、十二或二十四进制计数器:对时进行计数3、六十进制计数器:对分和秒进行计数;4、六进制计数器:分别对秒十位和分十位进行计数;5、十进制计数器:分别对秒个位和分个位进行计数;6、扫描显示译码器:完成对7字段数码管显示的控制;四、系统硬件要求:1、时钟信号为10MHz;2、FPGA芯片型号EPM7128LC84—15、EP1K30TC144—3或EP1K100QC208—3(根据实验箱上FPGA芯片具体选择);3、8个7段扫描共阴级数码显示管;4、按键开关(清零、启动、保持);五、设计内容及步骤:1、根据电路持点,用层次设计概念。

将此设计任务分成若干模块,规定每一模块的功能和各模块之间的接口,同时加深层次化设计概念;2、软件的元件管理深层含义,以及模块元件之间的连接概念,对于不同目录下的同一设计,如何熔合;3、适配划分前后的仿真内容有何不同概念,仿真信号对象有何不同,有更深一步了解。

熟悉了CPLD/FPGA设计的调试过程中手段的多样化;4、按适配划分后的管脚定位,同相关功能块硬件电路接口连线;5、所有模块尽量采用VHDL语言设计。

数电实验数字钟上机报告_华科

MAX+Plus II多功能数字钟设计自动化1001班刘杰学号U200914402多功能数字钟设计一、实验目的1. 掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程;2. 熟悉一种EDA软件使用;3. 掌握Verilog设计方法;二、实验任务1. 已知条件MAX+Plus II软件FPGA实验开发装置(该装置可以提供3路时钟信号和译码显示电路)基本功能具有“秒”、“分”、“时”计时功能,小时按24小时制计时。

具有校时功能,能对“分”和“小时”进行调整2. 扩展功能仿广播电台正点报时。

在59分51秒、53秒、55秒、57秒、59秒发出音响结束时刻为整点。

定时控制,其时间自定;3. 选做内容任意时刻闹钟自动报整点时数小时计数器改为12翻1三、数字钟设计分析-功能框图四、设计编译1.设计输入module top_clock (Second,ap,CP,nCR,EN,Adj_Min,Adj_Hour,ctrlbell,sethrkey,setminkey,alarm,_1khz,_500hz,rhr,rmin);inputCP,nCR,EN,Adj_Min,Adj_Hour,ctrlbell,_1khz,_500hz,sethrkey,setminkey;output[7:0] rhr,rmin,Second;output alarm;wire[7:0] set_hr,set_min,Hour,Minute;wire alarm_clock,alarm_r,alarm_r1;wire _1khz,_500hz,CP;output ap;reg[7:0] rhr,rmin,Second;supply1 Vdd;wire MinL_EN,MinH_EN,Hour_EN,Ap;wire hrh_equ,hrl_equ,minh_equ,minl_equ;wire time_equ;//Hour:Minute:Second countercounter10 U1(Second[3:0],nCR,EN,CP);counter6 U2(Second[7:4],nCR,(Second[3:0]==4'h9),CP);assign MinL_EN=Adj_Min?Vdd:(Second==8'h59);assignMinH_EN=(Adj_Min&&(Minute[3:0]==4'h9))||(Minute[3:0]==4'h9)&&(Sec ond==8'h59);counter10 U3(Minute[3:0],nCR,MinL_EN,CP);counter6 U4(Minute[7:4],nCR,MinH_EN,CP);assign Hour_EN=Adj_Hour?Vdd:((Minute==8'h59)&&(Second==8'h59));counter24 U5(Hour[7:4],Hour[3:0],nCR,Hour_EN,CP,Ap);//若闹钟调整使能端开启,数码管显示闹铃设置时间,反之显示时钟时间。

maxplus2小数分频

小数分频器的设计摘要:通过小数分频器的基本实现原理进行小数分频器主模块的设计与实现。

程序用VHDL硬件描述语言设计,在MAX+ plus Ⅱ开发软件下分析编译并进行仿真调试。

关键词:小数分频,VHDL一、小数分频的基本原理:小数分频器的功能就是当在输入端给定不通输入数据时,将对输入的时钟信号有不同的分频比,即对较高频率的信号分频,以得到所需要的低频信号。

小数分频器的实现方法很多, 但其基本原理一样,即在若干个分频周期中采取某种方法使某几个周期多计或少计1 个数, 即吞脉冲或插入脉冲的方法,从而在平均意义上获得1 个小数分频比,设要进行分频比为N 的小数分频, N 可表示为N = K + 10- nX式中, n , K, X 均为正整数; n 为到X 的位数,即N 有n 位小数。

另一方面,分频比又可以写成:N = M/ P式中:M 为分频器输入脉冲数; P 为输出脉冲数。

M = N P = ( K + 10- nX) P令P = 10 n ,则有M = 10 nK + X以上是小数分频器的一种实现方法, 即在进行10 nK 次分频时,设法多输入X 个脉冲。

二、仿真软件:MAX-plusⅡ。

可识别编译AHDL,VHDL,V erilog hdl等硬件语言。

三、设计的小数分频器主模块:设计(一):1、源代码:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ClkDivy ISPORT(clk:IN STD_LOGIC;clkdivp:OUT STD_LOGIC);END ClkDivy;ARCHITECTURE rtl OF ClkDivy ISCONSTANT md :STD_LOGIC_VECTOR(1 DOWNTO 0):="10";SIGNAL counter :STD_LOGIC_VECTOR(1 DOWNTO 0);SIGNAL tmpclk :STD_LOGIC;SIGNAL clkdiv5 :STD_LOGIC;SIGNAL tmpdiv2p5 :STD_LOGIC;BEGINp1:PROCESS(tmpclk)BEGINIF(tmpclk'event AND tmpclk='1')THENIF(counter="00")THENcounter<=md;tmpdiv2p5<='1';ELSEcounter<=counter-1;tmpdiv2p5<='0';END IF;END IF;END PROCESS p1;p2:PROCESS(tmpdiv2p5)BEGINIF(tmpdiv2p5'event AND tmpdiv2p5='1')THENclkdiv5<=NOT clkdiv5;END IF;END PROCESS p2;tmpclk<=clk XOR clkdiv5;clkdivp<=tmpdiv2p5;END rtl;2、生成的模块文件图3、仿真时序图:设计(二)1.源代码:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity HalfDivy isport(Inclk : in std_logic;Preset : in std_logic_vector(3 downto 0);Outclk : buffer std_logic);end HalfDivy;architecture Behavioral of HalfDivy issignal clk,divclk : std_logic := '0';signal count : std_logic_vector(3 downto 0) := "0000"; beginclk <= Inclk xor divclk;process(clk)beginif(clk'event and clk = '1') thenif(count = "0000") thencount <= preset-1;Outclk <= '1';elsecount <= count-1;Outclk <= '0';end if;end if;end process;process(Outclk)beginif(Outclk'event and Outclk='1') thendivclk<=not divclk;end if;end process;end Behavioral;2、生成的模块文件图3、仿真时序图:四:总结分频器完成对输入信号的整数或半整数分频功能,当然这只是分频器主模块,我们还要相应设计输入信号产生模块,控制模块等等,从而实现不同需要的信号分频,得到所需频段信号理想的效果。

基于MAX+plusⅡ的数字钟的设计与实现

基于MAX+plusⅡ的数字钟的设计与实现

王爱珍

【期刊名称】《长春师范学院学报(自然科学版)》

【年(卷),期】2008(027)002

【摘要】介绍了一种基于EDA工具--MAX+plusⅡ的多功能数字时钟的设计.在设计了数字时钟的每一个单元电路:分频、计时、显示及整点报时电路之后下载到硬件实现.其设计巧妙结合文本、原理图两种输入方法,思路简洁、新颖,经验证系统功能可靠.

【总页数】5页(P31-35)

【作者】王爱珍

【作者单位】忻州师范学院,山西忻州,034000

【正文语种】中文

【中图分类】TN79

【相关文献】

1.基于FPGA的多功能数字钟的设计与实现 [J], 吴小红

2.基于Proteus和Keil的数字钟的设计与实现 [J], 严敏

3.基于单片机的智能数字钟的设计与实现 [J], 严敏

4.基于多通道理论的六位数字钟的设计与实现 [J], 余云飞;王苹;李中望;沈璐

5.基于PCF8563的数字钟FPGA设计与实现 [J], 付永乐;王崇

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

源程序与仿真图CNT24library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt24 isport(clk,rst:in std_logic;co:out std_logic;qh,ql :out std_logic_vector(3 downto 0)); end cnt24;architecture behave of cnt24 issignal tmpl,tmph:std_logic_vector(3 downto 0);beginprocess(rst,clk)beginif(rst='1') then tmpl<="0000";tmph<="0000";co<='0';elsif(clk'event and clk='1')thenif(tmpl=9)thentmpl<="0000";tmph<=tmph+1;else tmpl<=tmpl+1;if(tmph=2) thenif(tmpl=3) then tmpl<="0000";tmph<="0000";co<='1';else tmpl<=tmpl+1;co<='0';end if;end if;end if;end if;ql<=tmpl;qh<=tmph;end process;end behave;CNT60library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt60 isport(clk,rst:in std_logic;co:out std_logic;qh,ql :out std_logic_vector(3 downto 0)); end cnt60;architecture behave of cnt60 issignal tmpl,tmph:std_logic_vector(3 downto 0);beginprocess(rst,clk)beginif(rst='1') then tmpl<="0000";tmph<="0000";co<='0';elsif(clk'event and clk='1')thenif(tmpl=9)then tmpl<="0000";if(tmph=5) then tmph<="0000";co<='1';elsetmph<=tmph+1;co<='0';end if;else tmpl<=tmpl+1;co<='0';end if;end if;ql<=tmpl;qh<=tmph;end process;end behave;DIV1000Library IEEE;Use IEEE.std_logic_1164.all;Use ieee.std_logic_unsigned.all;Use IEEE.std_logic_arith.all;Entity div1000 isPort( clk: in std_logic;--from system clock(1KHz)f1hz: out std_logic);-- 1Hz output signalend div1000;architecture arch of div1000 issignal count : integer range 0 to 499;--count from 0 to 499-local sisignal temp:std_logic;beginprocess (clk)beginif rising_edge(clk) thenif count>=499 thentemp<=not temp;count<=0;else count<=count+1;end if;end if;end process;f1hz<=temp;end arch;JIAOZHUNlibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jiaozhun isport(clk1,clk2,qo:in std_logic;co:out std_logic);end jiaozhun;architecture behave of jiaozhun isbeginprocess(qo,clk1,clk2)beginif(qo='0') then co<=clk1;else co<=clk2;end if;end process;end behave;SCAN6library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity scan6 isport(clk:in std_logic;a1,a2,a4,a5,a7,a8:in std_logic_vector(3 downto 0);seg7: out std_logic_vector(6 downto 0);bt : out std_logic_vector(7 downto 0)); end scan6;architecture behav of scan6 issignal cnt8:std_logic_vector(2 downto 0); signal a: std_logic_vector(3 downto 0); beginprocess(cnt8)begincase cnt8 iswhen "000"=>bt<="00000001";a<=a1; when "001"=>bt<="00000010";a<=a2; when "010"=>bt<="00000100";a<="1010"; when "011"=>bt<="00001000";a<=a4; when "100"=>bt<="00010000";a<=a5; when "101"=>bt<="00100000";a<="1010"; when "110"=>bt<="01000000";a<=a7; when "111"=>bt<="10000000";a<=a8; when others=>null;end case;end process ;process(clk)beginif (clk'event and clk='1')then cnt8<=cnt8+1;end if;end process ;process(a)begincase a iswhen "0000"=>seg7<="1111110";when "0001"=>seg7<="0110000";when "0010"=>seg7<="1101101";when "0011"=>seg7<="1111001";when "0100"=>seg7<="0110011";when "0101"=>seg7<="1011011";when "0110"=>seg7<="1011111";when "0111"=>seg7<="1110000";when "1000"=>seg7<="1111111";when "1001"=>seg7<="1111011";when "1010"=>seg7<="0000001";when others=>null;end case;end process ;end behav;TOPCNT24JIAOZHUNSCAN6。