(ISE使用流程)逻辑设计实验

ISE硬件实验室实验操作

以后所有实验均按此文件步骤进行操作1)建立新的项目器件选择,如下图2)输入VHDL代码,存盘3)使用ISE Simulator进行仿真4)管脚配置,存盘,按照管脚配置,进行实验箱连线。

4)综合Synthesize5)实现implement design6)下载(此时应连接USB下载线打开实验板的电源)双击generate programming file,产生后缀名为.bit的下载文件,待Generate Programming File" completed successfully“后双击configure device(impact),如下图所示,点击finish。

若此时没有连接USB下载线,或者没有开实验板的电源,则出现如下窗口,待连接好后,重新进行下载设置点击主窗口下boundary scan 对扫描方式进行设置,点击对芯片进行配置,如上图,该实验箱可以对三个芯片:XC3s500e、xcf04s、xc2c64a进行配置,我们只对XC3s500e进行配置,其他两个忽略。

选择需要下载的*.bit文件,点击open,出现对xc40fs进行配置,如下图所示,点击bypass忽略对xc2c64a进行配置,点击忽略bypass,鼠标放在XC3s500e芯片上,点击右键,出现下图:点击programming properties,如下图所示,点击ok,会有下载成功提示。

7)实验箱验证,记录验证结果,并进行分析试验箱相关资源使用:拨码开关:连接端子J8(sw1-sw16)拨上为:高拨下为:低发光二极管:低电平点亮数码管:位选通信号连接端子J10(DIG1-DIG8):低电平有效段码连接端子J15(sa-sg,dp)对应七段数码管a-g,dp :高电平点亮按键J9 (S01-S16)。

ISE设计流程范文

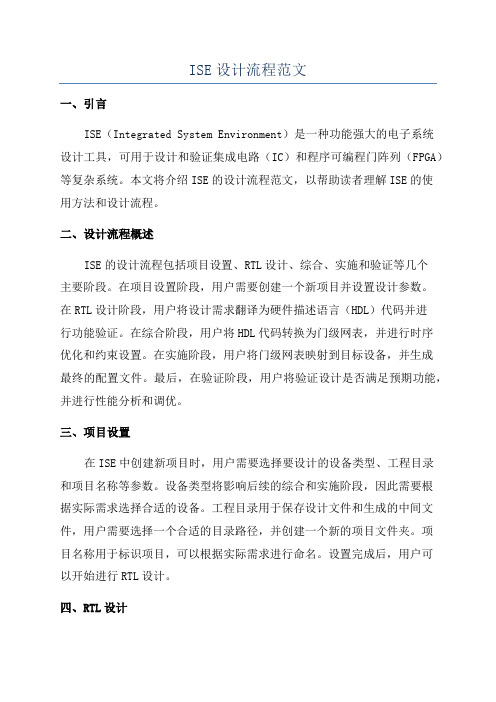

ISE设计流程范文一、引言ISE(Integrated System Environment)是一种功能强大的电子系统设计工具,可用于设计和验证集成电路(IC)和程序可编程门阵列(FPGA)等复杂系统。

本文将介绍ISE的设计流程范文,以帮助读者理解ISE的使用方法和设计流程。

二、设计流程概述ISE的设计流程包括项目设置、RTL设计、综合、实施和验证等几个主要阶段。

在项目设置阶段,用户需要创建一个新项目并设置设计参数。

在RTL设计阶段,用户将设计需求翻译为硬件描述语言(HDL)代码并进行功能验证。

在综合阶段,用户将HDL代码转换为门级网表,并进行时序优化和约束设置。

在实施阶段,用户将门级网表映射到目标设备,并生成最终的配置文件。

最后,在验证阶段,用户将验证设计是否满足预期功能,并进行性能分析和调优。

三、项目设置在ISE中创建新项目时,用户需要选择要设计的设备类型、工程目录和项目名称等参数。

设备类型将影响后续的综合和实施阶段,因此需要根据实际需求选择合适的设备。

工程目录用于保存设计文件和生成的中间文件,用户需要选择一个合适的目录路径,并创建一个新的项目文件夹。

项目名称用于标识项目,可以根据实际需求进行命名。

设置完成后,用户可以开始进行RTL设计。

四、RTL设计RTL设计是ISE设计流程的核心阶段,用户需要将设计需求转化为HDL代码,并进行功能验证。

RTL设计可以使用Verilog、VHDL或SystemVerilog等硬件描述语言来实现。

用户需要根据设计需求,编写相应的代码,并进行模块化设计。

在设计过程中,用户需要合理使用寄存器、组合逻辑和时序逻辑等元件,以满足设计要求。

完成RTL设计后,用户需要进行功能验证,即通过仿真和测试来验证设计是否满足预期的功能和性能。

五、综合综合是将HDL代码转换为门级网表的过程,它将具有不同功能的模块合并为一个整体,优化逻辑电路结构,并对时序进行约束和优化。

在综合过程中,用户需要提供时钟频率和约束文件等参数,以便综合工具可以进行时序优化。

ISE软件使用

实验一:ISE9.1软件基本操作与应用实验

1、实验目的:

(1)掌握ISE9.1软件的基本操作及应用

(2)通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设计方法

(3)掌握组合逻辑ห้องสมุดไป่ตู้路的仿真方法

2、实验步骤:

(1)建立项目存在的路径:注意问题:

1)不能放在根目录下

2)路径名称符合标识符的命名规范

如:E:\\EDAexp

(2) 打开ise集成开发环境:

双击桌面图标如图1-1所示,或者从执行:程序->Xilinx ise 9.1i -> project

navigator

图1-1

(3) 建立一个项目:

首先打开 ISE,每次启动时 ISE 都会默认恢复到最近使用过的工程界面。当第一次使用时,由于此时还没有过去的工程记录,所以工程管理区显示空白。选择 File/New Project 选项,在弹出的新建工程对话框中的工程名称中输入“decoder3_to_8”。在工程路径中单击 Browse 按键,将所建工程放到指定目录,如图 1-2所示。

ISE软件使用说明(两篇)

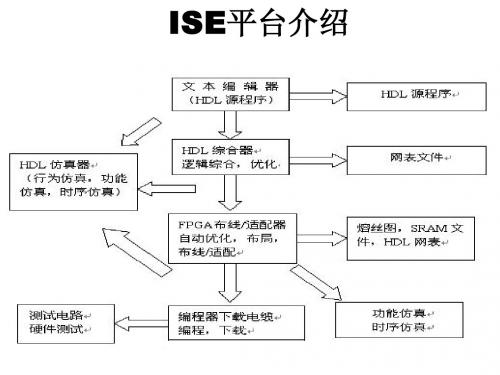

引言:概述:ISE软件是由Xilinx公司开发的一款集成电路设计工具,使用该软件可以进行数字电路设计、仿真、验证以及实现等多个阶段的工作。

在设计阶段,ISE软件提供了丰富的组件库和设计工具,方便用户进行电路原理图的绘制和逻辑设计。

在验证阶段,ISE软件可以进行功能仿真和时序仿真,以确保设计的正确性和稳定性。

在实现阶段,ISE软件提供了先进的布局与布线工具,能够将设计转化为实际的电路板。

正文内容:1.安装与启动1.1ISE软件安装包1.2安装ISE软件1.3启动ISE软件2.项目管理2.1创建新项目2.2导入已有项目2.3添加设计文件2.4设定项目属性2.5保存和备份项目3.设计流程3.1电路原理图设计3.1.1组件选择3.1.2连接元件3.1.3设置元件属性3.2逻辑设计3.2.1设计约束3.2.2逻辑优化3.2.3时序约束3.3约束文件编辑3.3.1约束规则3.3.2约束语法3.3.3约束检查3.4时序仿真3.4.1创建仿真波形3.4.2设定初始状态3.4.3运行仿真3.5功能仿真3.5.1设置输入信号3.5.2运行仿真3.5.3分析仿真结果4.仿真与验证4.1时序分析4.1.1设定时钟4.1.2时序路径分析4.1.3时序优化4.2时序约束验证4.2.1满足约束4.2.2修复时序错误4.3灵敏度分析4.3.1设定输入敏感性4.3.2分析敏感性4.4逻辑分析4.4.1切换敏感性4.4.2分析逻辑状态5.布局与布线5.1物理约束5.1.1面积约束5.1.2信号完整性约束5.1.3电源与接地约束5.2布局5.2.1网表导入5.2.2管理物理资源5.2.3进行布局布线5.3时序优化5.3.1满足时序约束5.3.2缩短信号传输路径5.3.3优化时钟分配5.4布线5.4.1管理布线资源5.4.2进行布线5.4.3路由与优化5.5设计规约检查5.5.1检查布局布线规约5.5.2修复设计规约错误总结:引言概述:ISE软件是一款功能强大的集成开发环境工具,广泛应用于数字电路设计和实现。

ISE实例演示步骤

ISE实例演示步骤ISE(Internet of Services)是一种新型的互联网服务架构,它的核心理念是将互联网服务以服务的形式进行管理和协调,使得用户可以更加方便、快捷地共享和使用各种互联网服务。

本文将通过一个ISE实例的演示步骤,详细介绍ISE的工作过程。

第一步:服务注册ISE的第一步是服务注册,在ISE平台上注册要提供的服务。

ISE平台是一个集成的服务管理平台,在这里,服务提供者可以将自己的服务注册到ISE平台上,以便被其他用户使用。

注册服务的方式可以是通过输入服务的相关信息,也可以是通过上传服务的描述文件。

注册完成后,ISE 平台会对服务进行验证和审核,确保服务的质量和可用性。

第二步:服务发现注册完服务后,ISE平台会将该服务加入到服务目录中,以供用户查找和使用。

用户可以通过ISE平台的功能来查找自己需要的服务,也可以通过浏览不同分类下的服务来发现新的服务。

用户可以通过输入关键词、选择分类、或是根据其他用户的评价来找到满足自己需求的服务。

第三步:服务选择当用户找到合适的服务后,可以进一步对服务进行评估和选择。

用户可以查看服务的详细信息,包括服务的功能、质量指标、服务等级等。

用户还可以查看其他用户的评价和评论,以获得对服务的更多了解。

用户可以根据自己的需求和偏好,选择最适合自己的服务。

第四步:服务组合一般来说,用户的需求可能需要多个服务来实现。

在ISE平台上,用户可以通过服务组合功能,将多个服务组合成一个更复杂的服务。

用户可以指定服务间的调用顺序和参数传递方式,以实现特定的业务逻辑。

通过服务组合,用户可以更加灵活地满足自己的需求,实现更加复杂和完整的功能。

第五步:服务调用当用户确定了所需的服务和服务组合后,可以直接在ISE平台上调用这些服务。

用户可以通过界面上的操作来进行服务的调用,也可以通过API、SDK等方式来集成ISE平台的服务调用功能到自己的应用中。

用户调用服务时,可以选择传递参数、输入数据,服务会根据用户的要求进行处理,并返回结果给用户。

实验软件—ISE使用

ISE设计流程 ISE设计流程

行为仿真

管脚适配

编程下载

1、启动软件

启动program/xilinx Navigator到下图界面 启动program/xilinx ise 9.1/project Navigator到下图界面

2、建立项目工程

project】 【file】--【new project】如下图所示 ,键入项目的名称和 file】--【 保存项目各文件的地址(可以先建好保存项目名的文件夹) 保存项目各文件的地址(可以先建好保存项目名的文件夹)

编程下载实现

右键点击元件,点击 右键点击元件,点击Program,选择相应的 ,选择相应的BIT文件开始下 文件开始下 如图所示。 载。如图所示。

成功下载后就可以在FPGA板上运行和测试了。 板上运行和测试了。 成功下载后就可以在 板上运行和测试了

综合编译

Source 窗中,选中要编译的源文件,双击处理窗 窗中,选中要编译的源文件,双击处理窗Processes中的 中的Synthesize-XST 中的 下的Check Syntax 。对出错报告语句进行修改,直到 对出错报告语句进行修改,直到successfully。如下图 下的 。

设计仿真

【project】--【new source】 ,键入仿真文件名, 】 【 】 键入仿真文件名, 栏选仿真文件地址, 选VHDL Test Bench,Location栏选仿真文件地址,如下图 , 栏选仿真文件地址

设计仿真

单击“下一步”直到完成, 单击“下一步”直到完成,得到仿真文件的输入窗

激励信号的输入

6、新文件输入完善

建然后一直单击“下一步”直到完成 得到下 建然后一直单击“下一步”直到完成,得到下 图

FPGA实验课件--ISE的使用与设计流程

分频器,100MHZ1HZ

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

3位计数器

高等教育出版社

基于verilog语言的ISE设计流程 --对该设计进行行为仿真

选中Simulation选项

选中counter.v,点击鼠标右键 选中New Source…

高等教育出版社 测试代码

ISE13.3集成开发环境介绍 --主界面介绍

工作区子窗口 源文件窗口

处理子窗口

高等教育出版社 脚本子窗口

基于verilog语言的ISE设计流程

--一个数字系统的设计原理

计数器

外部50MHz时钟

1Hz时钟

分频器生成 电路

3位的计 数器

LED灯显示计数值

top.v divider.v clk reset 分频器 1HZ counter.v 3位计数器 out[2:0]

选择Implement Design, 并展开

第三步: 布局和布线 ”Place & Route” 高等教育出版社

基于verilog语言的ISE设计流程 --查看布局布线后结果

选择Place & Route, 并展开 选择View/Edit Routed Design(FPGA Editor)

高等教育出版社

工程名

器件名字

生成了空的工程框架

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

选中器件名字,点击鼠标右键 选中New Source…

高等教育出版社

基于verilog语言的ISE设计流程 --创建一个新的设计文件

块存储器映像文件 在线逻辑分析仪Chipscope定义和连接文件

实验一 ISE软件的基本操作与应用

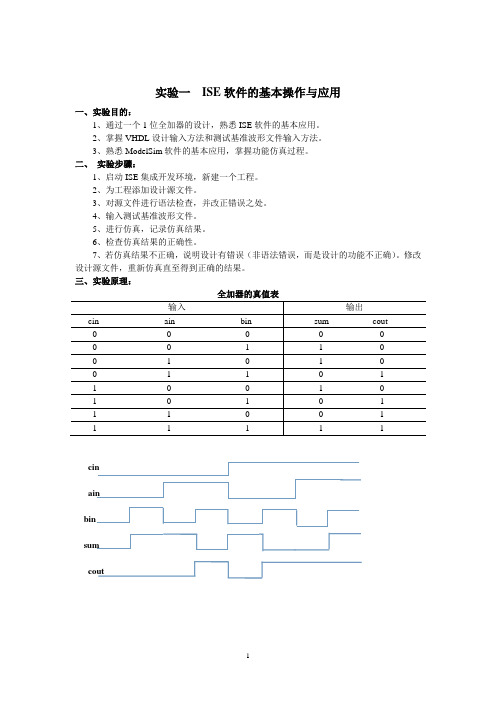

实验一ISE软件的基本操作与应用一、实验目的:1、通过一个1位全加器的设计,熟悉ISE软件的基本应用。

2、掌握VHDL设计输入方法和测试基准波形文件输入方法。

3、熟悉ModelSim软件的基本应用,掌握功能仿真过程。

二、实验步骤:1、启动ISE集成开发环境,新建一个工程。

2、为工程添加设计源文件。

3、对源文件进行语法检查,并改正错误之处。

4、输入测试基准波形文件。

5、进行仿真,记录仿真结果。

6、检查仿真结果的正确性。

7、若仿真结果不正确,说明设计有错误(非语法错误,而是设计的功能不正确)。

修改设计源文件,重新仿真直至得到正确的结果。

三、实验原理:全加器的真值表输入输出cin ain bin sum cout0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1cinainbinsumcout半加器程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_banjq isPort ( a : in STD_LOGIC;b : in STD_LOGIC;co : out STD_LOGIC;so : out STD_LOGIC); end my_banjq;architecture Behavioral of my_banjq is beginco <=a and b;so <=a xor b;end Behavioral;或门程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_or isPort ( a : in STD_LOGIC;b : in STD_LOGIC;c : out STD_LOGIC);end my_or;architecture Behavioral of my_or isbeginc <= a or b;end Behavioral;全加器程序:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity my_fadder isPort ( ain : in STD_LOGIC;bin : in STD_LOGIC;cin : in STD_LOGIC;cout : out STD_LOGIC;sum : out STD_LOGIC);architecture Behavioral of my_fadder iscomponent my_banjqport(a,b: in std_logic;co,so: out std_logic);end component;component my_orport(a,b: in std_logic;c: out std_logic);end component;signal s1,s2,s3:std_logic;beginu1:my_banjq port map(a=>ain,b=>bin,co=>s1,so=>s2);u2:my_banjq port map(a=>s2,b=>cin,co=>s3,so=>sum);u3:my_or port map(a=>s1,b=>s3,c=>cout);end Behavioral;五、实验记录波形功能仿真波形时序仿真波形六、实验心得总的来说,这次实验还是很简单的,但是却花了大量的时间才完成。

实验一 ISE的简单使用

主要功能

1设计输入:原理图、VHDL、Verilog语言 2综合(Synthesize):综合工具 XST 3仿真(ISim Simulator):创建用于仿真的输入 激励文件(VHDL线后的设计文件转换为位流 文件

界面介绍

• 标题栏、菜单栏、工具栏、工程管理区、源文 件编辑区、过程管理区、信息显示区、状态栏。

• 菜单介绍: Project 菜单包含了对工程的各个操作,是设计中 最常用的菜单之一。 Set as Top Module命令:用于将选中的文件设置 成顶层模块。只有设置成顶层模块,才能对其综 合、实现以及生成相应的二进制比特流文件。

操作简介

• 新建工程 • 新建设计文件,代码输入 • 综合:将 HDL 语言、原理图等设计输入翻

译成与、或、非门和 RAM、触发器等基本 逻辑单元的逻辑连接。 在过程管理区双击Synthesize-XST • 双击 View RTL Schematics 来查看RTL级结构 图

• 仿真

1.在工程管理区选择Simulation

2.新建测试文件Test Bench(Project\New source\VHDL test bench)

3.选中Test bench文件,双击processes中的 Simulate Behavioral Model,即可完成功能仿真。

实验内容

1、熟悉ISE开发流程 2、AND-OR电路设计 3、完成综合和功能仿真

ISE实例演示步骤

计周期。该套件可供给MicroBlaze微控制器系统(MCS)使

用。支持面向7系列,如Artix7,Kintex7,Spartan3, Virtex4、5、6等。

ISE特点

1.优良的集成环境

ISE是一个集成环境,可以完成整个FPGA/CPLD开发过程

,其集成了很多设计工具,可以大大提高产品设计效率。 2.简洁流畅的界面风格 其界面秉承了可视化编程技术,界面根据设计流程而组织 ,易学易用。

4.自动使用之前创建工程时所设置的器件

单击下一步

ISE具体步骤

5.选择简单的单核系统

a.选择单核

b.单击下一步

ISE具体步骤

6.对处理器进行简单的设置

a.根据硬件主时钟选择晶振 频率 b.系统时钟选择晶振倍频 后的频率 c.内存选择16KB

这是系统默认的最精简内核

d.单击下一步

ISE具体步骤

7. 进行Peripheral添加与简单设置

a.选择器件系列 b.选择具体器件 c.根据习惯,选择工具 d.选择语言

e.单击下一步

ISE具体步骤

4.刚才所建工程的一些信息

核对所设置的信息 无误后,单击完成

ISE具体步骤

第二步 在工程中添加一个嵌入式软核 1. 选中xc6slx9-2ftg256,右键选择New Source

c.选择嵌入式软核 b.软核名称 a.软核所在文件夹 d.单击下一步

单击添加外设

ISE具体步骤

按键,数据位宽为1

IIC总线

LED,数据位宽为1

串口

单击下一步

ISE具体步骤

单击下一步

ISE具体步骤

8.查看内核地址分配信息

单击完成

ISE具体步骤

EDA实验报告

实验三: 二位比较器的设计与实现一.实验简介:这个实验将指导你通过使用ISE软件进行简单的二位比较器的设计与实现。

二.实验目的:•使用ISE软件设计并仿真。

•学会程序下载。

三.实验原理:1.ISE软件是一个支持数字系统设计的开发2.用ISE软件进行设计开发时基于相应器件型号的。

注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。

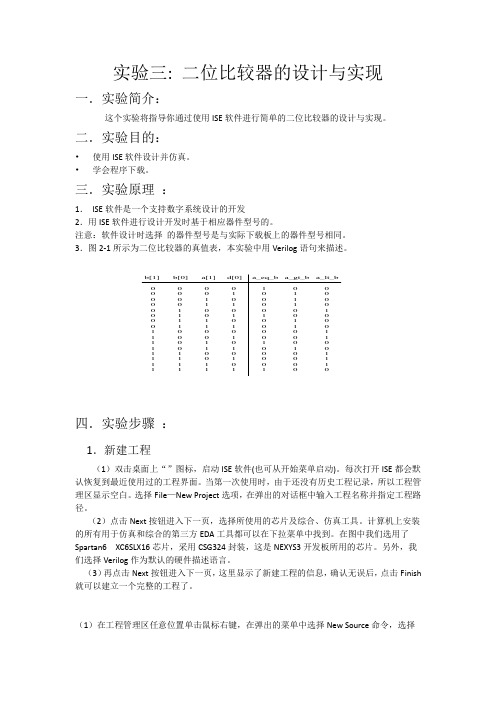

3.图2-1所示为二位比较器的真值表,本实验中用Verilog语句来描述。

b[1] b[0] a[1] d[0]0 0 0 00 0 0 10 0 1 00 0 1 10 1 0 00 1 0 10 1 1 00 1 1 11 0 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 1a_eq_b a_gt_b a_lt_b1 0 00 1 00 1 00 1 00 0 11 0 00 1 00 1 00 0 10 0 11 0 00 1 00 0 10 0 10 0 11 0 0四.实验步骤:1.新建工程(1)双击桌面上“”图标,启动ISE软件(也可从开始菜单启动)。

每次打开ISE都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。

选择File—New Project选项,在弹出的对话框中输入工程名称并指定工程路径。

(2)点击Next按钮进入下一页,选择所使用的芯片及综合、仿真工具。

计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到。

在图中我们选用了Spartan6 XC6SLX16芯片,采用CSG324封装,这是NEXYS3开发板所用的芯片。

另外,我们选择Verilog作为默认的硬件描述语言。

(3)再点击Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish 就可以建立一个完整的工程了。

(1)在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,选择Verilog Module输入,并输入Verilog文件名。

实验一 ISE应用流程实验

实验一ISE应用基础实验ISE是指集成综合环境,本章通过一系列的实验,使学习者对ISE这一工具的应用有较为深刻的认识,并对FPGA的仿真与设计环境有深入的了解,为进一步的工作奠定基础。

ISE9.1 使用流程实验1. 实验背景知识:了解FPGA的实验、项目研发与设计流程,了解ISE软件在FPGA的项目设计的作用、组成部分和基本操作步骤。

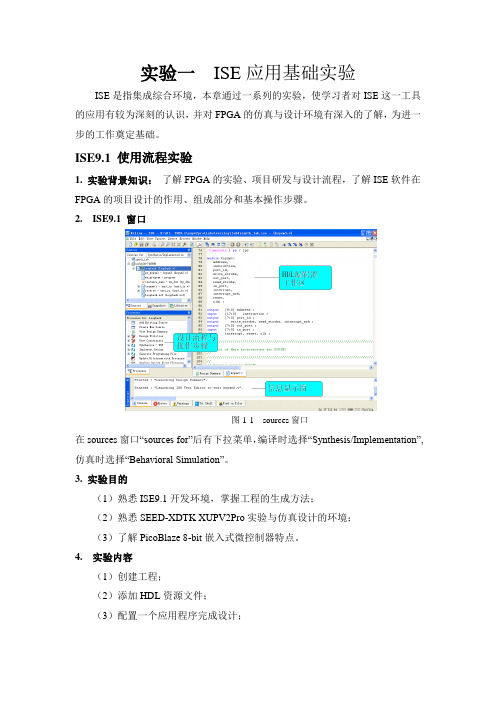

2. ISE9.1 窗口图1-1 sources窗口在sources窗口“sources for”后有下拉菜单,编译时选择“Synthesis/Implementation”,仿真时选择“Behavioral Simulation”。

3. 实验目的(1)熟悉ISE9.1开发环境,掌握工程的生成方法;(2)熟悉SEED-XDTK XUPV2Pro实验与仿真设计的环境;(3)了解PicoBlaze 8-bit嵌入式微控制器特点。

4. 实验内容(1)创建工程;(2)添加HDL资源文件;(3)配置一个应用程序完成设计;(4)设计的仿真及实现。

5. 实验准备(1)将光盘下03. Examples of Program 实验程序目录下的01. ISE9.1文件夹拷贝到E:盘根目录下;(2)将USB下载电缆与计算机及XUPV2Pro板的J8连接好;(3)将RS232串口线一端与计算机连接好,另一端与板卡的J11相连接;(4)启动计算机后,将XUPV2Pro 板的电源开关SW11 打开到ON 上。

观察XUPV2Pro 板上的+2.5V,+3.3V,+1.5V 的电源指示灯是否均亮,若有不亮的,请断开电源,检查电源。

6.实验步骤(1)创建工程1)双击桌面Xilinx ISE9.1 快捷方式打开ISE 工程管理器(Project Navigator)。

2)打开Project Navigator 后,选择File → New Project ,弹出新建工程对话框;图1-2 ISE 工程管理器3)在工程路径中单击“…”按钮,将工程指定到如下目录,单击确定。

iSe软件使用

实验一:ISE9.1软件基本操作与应用实验1、实验目的:(1)掌握ISE9.1软件的基本操作及应用(2)通过一个简单的3-8译码器的设计,掌握组合逻辑电路的设计方法(3)掌握组合逻辑电路的仿真方法2、实验步骤:(1)建立项目存在的路径:注意问题:1)不能放在根目录下2)路径名称符合标识符的命名规范如:E:\\EDAexp(2) 打开ise集成开发环境:双击桌面图标如图1-1所示,或者从执行:程序->Xilinx ise 9.1i -> project navigator图1-1(3) 建立一个项目:首先打开ISE,每次启动时ISE 都会默认恢复到最近使用过的工程界面。

当第一次使用时,由于此时还没有过去的工程记录,所以工程管理区显示空白。

选择File/New Project 选项,在弹出的新建工程对话框中的工程名称中输入“decoder3_to_8”。

在工程路径中单击Browse 按键,将所建工程放到指定目录,如图1-2所示。

图1-2(4)点击“Next”进入下一页,选择所使用的芯片类型以及综合、仿真工具。

计算机上所安装的所有用于仿真和综合的第三方EDA 工具都可以在下拉菜单中找到,如图1-3 所示。

在图中,假设本例采用器件spartan3A系列的XC3S50A芯片,并且指定综合工具为XST(VHDL/verilog),仿真工具选为ISE 自带的ISE simulator,如图1-3所示。

图1-3(5)再点击“Next”进入下一页,可以选择新建源代码文件,也可以直接跳过,进入下一页。

第4页用于添加已有的代码,如果没有源代码,点击“Next”,进入最后一页,单击finish确认后,就可以建立一个完整的工程。

(6)代码输入在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择“New Source”命令,会弹出如图1-4 所示的New Source对话框。

图1-4左侧的列表用于选择代码的类型,各项的意义如下所示:•IP(Coregen & Architecture Wizard):由ISE 的IP Core 生成工具快速生成可靠的源代码,这是目前最流行、最快速的一种设计方法。

ise的使用流程

ise的使用流程1. 简介ise是一款功能强大的集成电路设计软件,可以提供全面的工程设计解决方案。

以下是ise的使用流程。

2. 下载与安装•访问ise官方网站。

•在网站上找到并点击下载按钮。

•根据操作系统选择合适的版本进行下载。

•下载完成后,双击安装程序进行安装。

•按照安装向导的提示进行安装。

3. 打开ise•双击ise的图标以打开软件。

•在启动界面选择新建项目。

•输入项目名称并选择适当的存储路径。

•点击确定以创建项目。

4. 添加设计文件•在项目导航栏中,右键单击Design Sources。

•选择Add Sources。

•在弹出的对话框中选择适当的文件类型。

•点击下一步并选择要添加的设计文件。

•点击完成以将文件添加到项目中。

5. 设计功能模块•在项目导航栏中,右键单击设计文件。

•选择New Source。

•在弹出的对话框中选择设计模块类型。

•点击下一步并输入模块的名称。

•点击完成以创建模块。

6. 添加约束文件•在项目导航栏中,右键单击设计文件。

•选择New Source。

•在弹出的对话框中选择约束文件类型。

•点击下一步并输入约束文件的名称。

•点击完成以创建约束文件。

7. 综合与优化•在项目导航栏中,右键单击设计文件。

•选择Synthesize - XST。

•等待综合过程完成。

8. 实现与布局•在项目导航栏中,右键单击设计文件。

•选择Implement Design。

•等待实现与布局过程完成。

9. 模拟与仿真•在项目导航栏中,右键单击设计文件。

•选择Simulate - ModelSim。

•编写仿真脚本文件并保存。

•运行仿真脚本以进行模拟与仿真。

10. 下载与验证•连接目标板与计算机。

•在ise软件中,点击Generate Programming File。

•将生成的Bitstream文件下载到目标板中。

•验证设计功能正常运行。

11. 导出项目•在ise软件中,选择Export - Export Project。

ISE实验讲义

目标板:Falcon-E25TG

介绍

实验 1: Xilinx ISE 工具流程实验

通过示例程序介绍 ISE™ 工具的基本使用流程。 本实验适合于用户在学习完 ISE 工具设计流程和 PicoBlaze 微控制器的原理后,对所学知识 进行理解验证。

目标

在完成示例实验后, 你将具备以下能力: 创建一个新工程 熟悉 FPGA 设计基本流程 掌握 PicoBlaze 基本技术特点

图 1-7. Command Window 5. 在命令提示符下面输入汇编代码(图 1-7),将自动产生指令存储器输出文件。 > kcpsm3 int_test.psm 注意: 此时在当前目录下可以看到 init_test.vhd(用于生成指令存储器的 VHDL 语言程 序) 、int_test.v(用于生成指令存储器的 Verilog 语言程序) 和 init_test.coe(用于 CoreGenerator 工具生成指令存储器的初始化数据文件)等文件。其实,这三个文件中 存储的都是应用程序汇编后产生的机器码,用户可以打开这三个文件,查看其中的二进 制机器码部分。 6. 在 ISE Project Navigator中, Project Add Copy of Source 在目录路径D: \ ISE-Flows \ labs \ lab1 \ vhdl \KCPSM3 \ Assembler中找到 int_test.vhd 或 int_test.v文件。(图 1-8)

yangrui.wti@

2

步骤 1:开始

查看 8 位微控制器 PicoBlaze 文档,熟悉其结构和指令集。本实验使用 PicoBlaze 中断应 用作为 ISE 设计流程用例,有必要学习 PicoBlaze 结构和指令集,但不是必须的。 PicoBlaze用户手册KCPSM3_manual.pdf存放在D:\ ISE-Flows \ labs \ lab1 \ verilog (或vhdl)\ KCPSM3 \ docs\ 目录中。 打开 ISE Project Navigator,创建一个新的工程。 1. 选择“开始 程序 Xilinx ISE Design suite 12.4 ISE Design Tools Project Navigator”(或者直接双击桌面Xilinx ISE Design suite 12.4 图标 ),启动ISE Project Navigator。

ISE的使用说明

ISE的使用说明ISE是集成电路设计中常用的一种工具,是一种综合软件环境,它用于设计目的,例如创建和测试电路设计的逻辑模型。

本文将详细介绍ISE 的使用说明,包括安装步骤、主要功能、常用操作和调试技巧。

一、安装步骤2.运行安装程序:双击安装程序启动安装流程,按照提示完成安装向导。

3.设置安装选项:在安装向导中,您可以选择安装目录、添加快捷方式和其他个性化设置。

4.完成安装:等待安装程序完成所有必要文件的复制和配置,安装完成后重启计算机。

二、主要功能1.逻辑设计:ISE提供了丰富的逻辑设计工具,包括原理图设计、硬件描述语言编写和逻辑优化等功能。

用户可以通过拖放元件、连接线和逻辑门,创建电路的逻辑模型。

2.约束设置:ISE允许用户定义各种约束条件,如时钟频率、延迟限制和电气规范等。

这些约束条件对于确保设计的正确性和性能至关重要。

3.仿真和验证:ISE提供了强大的仿真和验证工具,以验证设计的功能和时序正确性。

用户可以模拟不同输入情况下的电路行为,并通过波形查看器等工具进行调试和分析。

4.综合和布局布线:ISE可以将逻辑设计综合为电路网表,并根据指定的目标器件和约束条件进行布局布线。

综合和布局布线的结果直接影响电路的性能和可靠性。

6.文档生成:ISE可以根据设计规范和用户的需求,自动生成各种设计文档,如用户手册、接口定义和设计报告等。

这些文档对于设计团队的交流和项目管理非常重要。

三、常用操作2.添加文件:在工程中,用户可以添加设计文件、约束文件和仿真文件等。

这些文件描述了电路的结构、约束条件和仿真模型,是设计的基础。

3.进行综合和优化:在添加文件后,用户需要对设计进行综合和优化,以便生成电路网表。

综合和优化的操作可以通过综合工具和约束文件完成。

4.进行布局布线:综合完成后,用户需要对设计进行布局布线,以生成具体的物理布局。

布局布线的操作可以通过布局布线工具和约束文件完成。

5.进行仿真和验证:在布局布线完成后,用户可以使用ISE提供的仿真和验证工具,对设计进行功能和时序验证。

ISE使用

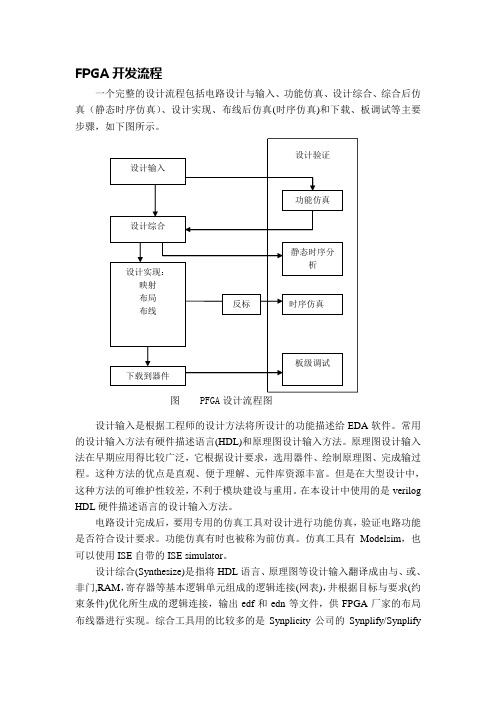

FPGA 开发流程一个完整的设计流程包括电路设计与输入、功能仿真、设计综合、综合后仿真(静态时序仿真)、设计实现、布线后仿真(时序仿真)和下载、板调试等主要步骤,如下图所示。

图 PFGA 设计流程图设计输入是根据工程师的设计方法将所设计的功能描述给EDA 软件。

常用的设计输入方法有硬件描述语言(HDL)和原理图设计输入方法。

原理图设计输入法在早期应用得比较广泛,它根据设计要求,选用器件、绘制原理图、完成输过程。

这种方法的优点是直观、便于理解、元件库资源丰富。

但是在大型设计中,这种方法的可维护性较差,不利于模块建设与重用。

在本设计中使用的是verilog HDL 硬件描述语言的设计输入方法。

电路设计完成后,要用专用的仿真工具对设计进行功能仿真,验证电路功能是否符合设计要求。

功能仿真有时也被称为前仿真。

仿真工具有Modelsim ,也可以使用ISE 自带的ISE simulator 。

设计综合(Synthesize)是指将HDL 语言、原理图等设计输入翻译成由与、或、非门,RAM ,寄存器等基本逻辑单元组成的逻辑连接(网表),井根据目标与要求(约束条件)优化所生成的逻辑连接,输出edf 和edn 等文件,供FPGA 厂家的布局布线器进行实现。

综合工具用的比较多的是Synplicity 公司的Synplify/Synplify 功能仿真设计输入 设计综合 设计实现:映射布局布线 下载到器件 静态时序分析反标 板级调试时序仿真 设计验证pro,以及各大FPGA厂商的集成开发环境中提供的综合工具,如Xilinx ISE中的XST。

使用Synplify/Synplify pro进行综合,该综合工具综合出的结果占用面积小、工作频率高,综合速度快。

综合完成后需要检查综合结果是否与原设计一致,需要做综合后仿真。

在仿真时,把综合生成的延时文件反标到综合仿真模型中去,可估计门延时带来的影响。

综合后仿真虽然比功能仿真精确一些,但是只能估计门延时,而不能估计线延时,仿真结果与布线后的实际情况还有一定的差距,并不十分难确。

(ISE使用流程)逻辑设计实验

(ISE使用流程)逻辑设计实验实验一 ISE工具的使用流程--拨码开关控制LED实验1.1 实验目的1.学会ISE的基本开发流程和常用功能的使用,本实验直接使用新建一个拨码开关控制led 实验来作为设计文件,通过ise 综合、映射、布局布线后,生成FPGA位流配置文件,通过JTAG口对开发板上FPGA进行配置。

2学会最基本拨码开关和led 工作原理。

1.2 实验原理1. 实验开发板的拨码开关向上拨动时处于低电平,向下处于高电平,用此来控制LED 灯。

2. LED灯的的一端已经接高电平,另一端接FPGA的IO口,因此当IO输出低电平是便可点亮LED灯,否则LED为暗。

3. 按键默认为高电平,按键按下时接地为低电平来检测按键的按下的复位信号。

1.3 实验步骤1. 打开ISE应用程序,进入图形化界面图表 12. 点击File->New project,在弹出的对话框中设定工程和工程路径,用HDL源码,NEXT1图表 23. 选定器件和封装,点击NEXT.图表 34. 在工程中创建源文件,选择New Source.,选中Verilog Module,输入源文件名称图表 425. 可在弹出的对话框中输入信号的输入输出定义,也可暂时不定义图表 56.点击下一步,点击finish,然后自动回到 creat a new source 对话框,点击下一步,再击下一步,然后点击finish 。

图表 66. 点击设计的源文件,然后整个界面如图所示图表 737. 将鼠标置于输入输出的下方,点击工具栏中的,然后进入各子目录选择如下,这是一个快捷操作模板。

右键use in file,可在源文件中看到已经添加相应的模板,然后修改一些端口、添加内容完善整个工程设计。

图表 88. 写源文件的代码如下module key_led(clk, key, reset_n, led); input clk; input key; input reset_n; output led; reg led;// Usage of asynchronous resets may negatively impact FPGA resources //and timing. In general faster and smaller FPGA designs will // result from not using asynchronous resets. Please refer to// the Synthesis and Simulation Design Guide for more information.always @(posedge clk or negedge reset_n) if (!reset_n) beginled <= 1; endelse begin if(key==0) led <=0; else led <=1; end endmodule4可用design Utilities点击create schematic symbol下观看所生成的原理图来分析电路的性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验一ISE工具的使用流程--拨码开关控制LED实验1.1 实验目的1.学会ISE的基本开发流程和常用功能的使用,本实验直接使用新建一个拨码开关控制led 实验来作为设计文件,通过ise 综合、映射、布局布线后,生成FPGA位流配置文件,通过JTAG口对开发板上FPGA进行配置。

2学会最基本拨码开关和led 工作原理。

1.2 实验原理1.实验开发板的拨码开关向上拨动时处于低电平,向下处于高电平,用此来控制LED灯。

2.LED灯的的一端已经接高电平,另一端接FPGA的IO口,因此当IO输出低电平是便可点亮LED灯,否则LED为暗。

3.按键默认为高电平,按键按下时接地为低电平来检测按键的按下的复位信号。

1.3 实验步骤1.打开ISE应用程序,进入图形化界面图表 12.点击File->New project,在弹出的对话框中设定工程和工程路径,用HDL源码,NEXT图表 23.选定器件和封装,点击NEXT.图表 34.在工程中创建源文件,选择New Source.,选中Verilog Module,输入源文件名称图表 45.可在弹出的对话框中输入信号的输入输出定义,也可暂时不定义图表 56.点击下一步,点击finish,然后自动回到creat a new source 对话框,点击下一步,再击下一步,然后点击finish 。

图表 66.点击设计的源文件,然后整个界面如图所示图表77.将鼠标置于输入输出的下方,点击工具栏中的,然后进入各子目录选择如下,这是一个快捷操作模板。

右键use in file,可在源文件中看到已经添加相应的模板,然后修改一些端口、添加内容完善整个工程设计。

图表88.写源文件的代码如下module key_led(clk, key, reset_n, led);input clk;input key;input reset_n;output led;reg led;// Usage of asynchronous resets may negatively impact FPGA resources// and timing. In general faster and smaller FPGA designs will// result from not using asynchronous resets. Please refer to// the Synthesis and Simulation Design Guide for more information.always @(posedge clk or negedge reset_n)if (!reset_n) beginled <= 1;endelse beginif(key==0)led <=0;elseled <=1;endendmodule可用design Utilities点击create schematic symbol下观看所生成的原理图来分析电路的性能。

9.添加约束文件,source for 选择在synthesis….,选中源文件,右键new source,选择如图所示,输入文件名,点击next,然后finish.可以看到已经添加到工程中。

图表910.添加测试文件,在source for 选择在behavioral….,new source,然后选择Verilog test fixture,建立测试文件。

Next,选择关联key_led,点击完成图表1011.编写测试文件代码如下:选中测试文件,在processes中的modelsim simulator 中的下拉菜单中双击simulate….这样就可以仿真了。

(注意在仿真之前要进行xilinx library库的编辑,方法见附录1)module key_led_tb_v;// Inputsreg clk;reg key;reg reset_n;// Outputswire led;// Instantiate the Unit Under Test (UUT)key_led uut (.clk(clk),.key(key),.reset_n(reset_n),.led(led));always #5 clk=~clk;initial begin// Initialize Inputsclk = 0;key = 1;reset_n = 1;// Wait 100 ns for global reset to finish#100 key=0;#100 reset_n=0;#100 reset_n=1;#100 key=1;#100 $stop;// Add stimulus hereendendmodule图表1112.管脚分配,回到sythesis…下,选中ucf 文件,在process中双击打开assign package Pins,按照管脚分配图进行相应配置,然后保存。

图表1213.回到主界面选中HDL设计文件,双击generate…,然后修改到成功没有错误为止。

如下图所示图表1314.生成Bit文件,在generate….下拉菜单中,双击第二个,进行JTAG下载配置(先进行实验板上的下载硬件配置连接)。

然后会提示成功与否图表1415.进行开发板验证。

实验步骤结束1.4 实验结果分析1.仿真如图所示图表152.通过实验板验证可以看到,当讲拨码开关拨向ON时,灯亮,拨向OFF时暗,当不论在什么状态下,按下复位键则灯立即变暗,直至松手。

因此简单本设计符合设计预期的要求。

3.通过本实验,了解了最基本的硬件知识和建立一个工程,代码编写、综合、约束、分析、调试、下载观察等过程。

4.通过本次实验,进一步了解了FPGA工程使用的一个简单流程,在实验过程中需要认真做好每一个环节,配合实验说明书找到解决方法。

5.实验过程中遇到的问题和解决方法:1)生成的bit 文件后,下载实验现象没有变化:可能保存的路径错了,导致屡试屡败2)无法正常显示窗口:修改桌面系统主题,该回经典xp等默认主题,这是由于EDK与操作系统的一些不兼容造成的。

3)综合错误:修改成可综合代码。

4)有警告:可稍微看一下警告的内容,但这是正常现象。

附录1:xilinx library 编译方法两种(选其中一种):(一)、在ISE Project Navigator中编译仿真库1、打开文件:安装路径:\Modeltech_6.2b,选中文件夹中的配置文件modelsim.ini ,右击,将文件属性中的只读去掉,变成可写入的,接着用写字板程序打开;2、在sources窗口中选择设计的目标器件xc3s500e-4pq208;在processes窗口中会出现design Utilties,选择Compile HDL Simulation Libraries项。

单击右键,在下拉菜单中选中Properties 命令,打开对话框如图所示。

3、Process Properties按如图选择,单击ok按钮关闭对话框。

4、双击Compile HDL Simulation Libraries,程序会自动完成对库文件的编译。

5、观看是否在modelsim.ini文件中加入以下部份。

; Verilog Sectionunisims_ver = 库文件所在地址/unisims_veruni9000_ver = 库文件所在地址/uni9000_versimprims_ver = 库文件所在地址/simprims_verxilinxcorelib_ver = 库文件所在地址/xilinxcorelib_veraim_ver = 库文件所在地址/abel_ver/aim_vercpld_ver = 库文件所在地址/cpld_ver; VHDL Sectionunisim = 库文件所在地址/unisimsimprim = 库文件所在地址/simprimxilinxcorelib = 库文件所在地址/xilinxcorelibaim = 库文件所在地址/abel/aimpls = 库文件所在地址/abel/plscpld = 库文件所在地址/cpld6、再将modelsim.ini设为只读即可7、可采用modelsim进行仿真了。

(二)、另一种方法1.在桌面上点击开始――运行――输入cmd,进入dos.2.在dos下输入:compxlib –s mti_se –arch all –l all –dir %xilinx%/lib –w3.等编译完成后便可在安装目录下的lib中生成库,将生成的库加入modelsim中。

1)方法:打开文件:安装路径:\Modeltech_6.2b,选中文件夹中的配置文件modelsim.ini ,右击,将文件属性中的只读去掉,变成可写入的,接着用写字板程序打开;2)在modelsim.ini中加入一下内容(库文件所在地址为-> 安装路径:\Xilinx92i\lib,比如有的同学是装在D盘,那就是:D:\Xilinx92i\lib ,这一步完成后将modelsim.ini再设为只读); Verilog Sectionunisims_ver = 库文件所在地址/unisims_veruni9000_ver = 库文件所在地址/uni9000_versimprims_ver = 库文件所在地址/simprims_verxilinxcorelib_ver = 库文件所在地址/xilinxcorelib_veraim_ver = 库文件所在地址/abel_ver/aim_vercpld_ver = 库文件所在地址/cpld_ver; VHDL Sectionunisim = 库文件所在地址/unisimsimprim = 库文件所在地址/simprimxilinxcorelib = 库文件所在地址/xilinxcorelibaim = 库文件所在地址/abel/aimpls = 库文件所在地址/abel/plscpld = 库文件所在地址/cpld实验二用Core Generator生成DCM并进行仿真验证2.1 实验目的学会用core generate 生成dcm ,并使用modelsim进行仿真。

2.2 实验原理1.DCM是数字时钟管理器,它在xilinx的FPGA的设计中应用广泛,dcm 可以产生输入时钟的一倍频、二倍频,或M/D倍频等功能,也可以产生90、180、270度相移的时钟,例如FPGA输入时钟为66M,而我们的系统需要133M的时钟,则可以用到DCM二倍频。

2.编译库,将库文件加入modelsim中,然后可以进行联合仿真调试。