EP4CE15M8I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

EP3C10E144C8中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

对于Cyclone III器件最大额定值.

表1-1 列出绝对

芯片中文手册,看全文,戳

1–2

第 1章: Cyclone III器件数据表

电气特性

1

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长时间周期绝对最大额定值设备操作具有设备不利影响.

表 1-1. Cyclone III器件绝对最大额定值

(1)

符

参数

况

过冲持续时间为%高时间

VI = 3.95 V

100

VI = 4.0 V

95.67

VI = 4.05 V

55.24

VI = 4.10 V

31.97

VI = 4.15 V

18.52

VI = 4.20 V

10.74

Vi

交流输入 电压

VI = 4.25 V VI = 4.30 V

6.23 3.62

Cyclone III器件.稳态电压和预期电流值

III器件中提供旋风

表1-3.

没有高原.

所有系统必须严格单调

表 1-3. Cyclone III器件推荐工作条件

(1), (2)

符

参数

条件

Min Typ Max Unit

VCCINT (3)

电源电压为内部逻辑

电源电压为输出缓冲器,3.3-V

手术

—

1.15 1.2 1.25

运行条件

当Cyclone III器件在一个系统中实现,它们是根据一组定义参数分级.为防护持 Cyclone III器件中最高性能和可靠性,系统设计人员必须考虑本文件中操 作要求. Cyclone III器件提供商用,工业和汽车级版本.商业设备在-6(最 快),-7和-8速度等级提供.工业和汽车设备仅在-7速度年级课程.

FPGA可编程逻辑器件芯片EP4CE115F29C8中文规格书

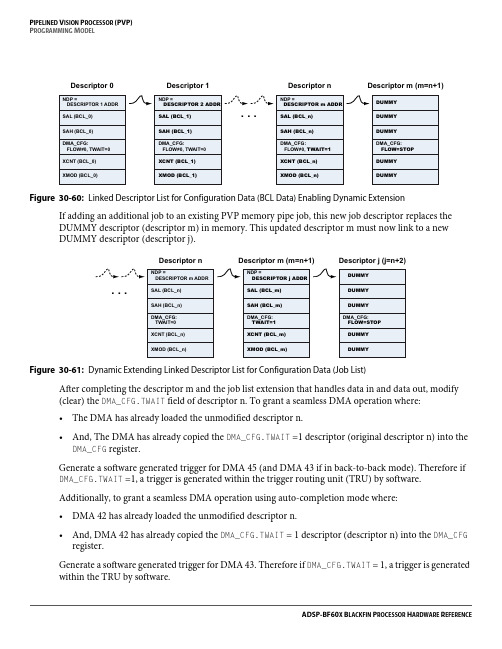

P IPELINED V ISION P ROCESSOR (PVP)P ROGRAMMING M ODELFigure 30-60:Linked Descriptor List for Configuration Data (BCL Data) Enabling Dynamic Extension If adding an additional job to an existing PVP memory pipe job, this new job descriptor replaces theDUMMY descriptor (descriptor m) in memory. This updated descriptor m must now link to a newDUMMY descriptor (descriptor j).Figure 30-61:Dynamic Extending Linked Descriptor List for Configuration Data (Job List)After completing the descriptor m and the job list extension that handles data in and data out, modify (clear) the DMA_CFG.TWAIT field of descriptor n. To grant a seamless DMA operation where:•The DMA has already loaded the unmodified descriptor n.•And, The DMA has already copied the DMA_CFG.TWAIT =1 descriptor (original descriptor n) into the DMA_CFG register.Generate a software generated trigger for DMA 45 (and DMA 43 if in back-to-back mode). Therefore if DMA_CFG.TWAIT =1, a trigger is generated within the trigger routing unit (TRU) by software.Additionally, to grant a seamless DMA operation using auto-completion mode where:•DMA 42 has already loaded the unmodified descriptor n.•And, DMA 42 has already copied the DMA_CFG.TWAIT = 1 descriptor (descriptor n) into the DMA_CFG register.Generate a software generated trigger for DMA 43. Therefore if DMA_CFG.TWAIT = 1, a trigger is generated within the TRU by software.PVP memory pipe job List. This graceful stop avoids loading non valid data into PVP memory pipe config-uration register. All DMA_CFG descriptor fields within the linked list have DMA_CFG.FLOW =6 or =7(descriptor list mode) or alternatively DMA_CFG.FLOW =4 (descriptor array mode). Configure the TRU to route the trigger of DMA 45 (back-to-back mode) or DMA 42 (auto-completion mode) to input trigger of DMA 43. All DMA_CFG descriptor field must therefore have a DMA_CFG.TWAIT field =1.Figure 30-57:Static Linked Descriptor List for Data INData Flow in Auto-Completion Mode for Static Job Operation—The following figure and procedure shows the data flow using a static job list and auto-completion mode.1.DMA45 generates a trigger for DMA 432.DMA 43 generates a trigger for DMA 423.Software generates the first trigger for DMA 424.DMA45 is triggered when the memory pipe requests a new configuration. In this case the PVP memorypipe is enabled and IPF1’s PVP_IPFn_FCNT field =0 (memory pipe request)Figure 30-59:Static Job List Data Flow (Back-to-Back Mode)Dynamic DMA Job List OperationThe setup for DMA job lists is described in Working with DMA Job Lists, and the DMA channel operations for these job lists is described in Static DMA Job List Operation. This section builds on those concepts and adds information for using dynamic operations. The important points in this description are:•IPF1 mode selection•Data in descriptor lists•Data flow in auto-completion mode•Data flow in back-to-back mode。

EPC4XXX中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

有关FPGA配置方案和先进更多信息 功能,请参考相应FPGA系列章 配置手册.

nCS and OE

Altera增强配置器件是单器件,高速, 非常高密度FPGA高级配置解决方案.核心 增强结构装置分为两大块,一个 配置控制器和快闪存储器.闪速存储器是用来 对于由一个或一个以上Altera系统存储配置数据 FPGA.快闪存储器未使用部分可被用来存储处理器代码或数据, 可以经由外部闪存接口进行访问之后FPGA配置完成.

自配置数据相同量带宽占用更少

空间中压缩后闪存.由于Stratix配置 数据压缩率是大约2时,有效读 带宽增加一倍至约320 Mbps.

DQ[], at

最后,配置控制器还期间管理错误

组态.一个

CONF_DONE 当对FPGA不DE-发生错误

断言其 CONF_DONE 最后一位后内64 DCLK周期信号

自动重启配置错误后,

选项在FPGA启用

它释放其

nSTATUS 后复位超时周期和信号

控制器尝试重新配置FPGA.

后FPGA配置过程完成时,控制器驱动

DCLK 低,并且

数据[] 引脚高.此外,控制器三

指出其内部接口闪存,使闪光灯地址和控制线内部弱上拉,并且使总线防护

持电路闪存数据线.

以下各节简要介绍增强配置设备所支持不同配置方案:FPP,PS和并 发配置.

● 通过外部闪存块/扇区防护护功能

闪存接口

● 支持在EPC16和EPC4设备 ■ 针对远程和本地重构高达页模式支持

八种配置为整个系统

● 兼容Stratix系列远程系统配置

特点

■ 支持字节范围内配置方式快速被动并行(FPP);

每8位输出数据

DCLK cycle

EP4CGX150中文资料(ALTERA)中文数据手册「EasyDatasheet - 矽搜」

(8)包括一个配置I / O块和四个专用时钟输入I / O银行HSSI参考时钟输入.

(9)I / O从引脚输出的文件数,用户包括所有的通用I / O,专用时钟引脚和两用配置引脚 .收发 器销和专用配置管脚不包括在引脚数 .

73,920 4,158 198 4 (4) 4 (5)

30 8

3.125

1 11 (8) 310

2.5

2.5

2.5

PCIe(PIPE)硬核IP模块

1

1

1

用户I / O银行

9 (7)

9 (7)

9 (7)

最大用户I / O

(9)

72

150

150

须知 表 1-2: (1)适用于F169和F324封装. (2)适用于在F484包. (3)仅有两个多用途PLL用于F484包. (4)两个通用的PLL能够支持收发器时钟.欲了解更多信息,请参阅

■ 字对齐

■ 速率匹配FIFO ■ TX位拖鞋的通用公共无线接口(CPRI)

■ 电气闲置 ■ 动态信道重配置让你改变的数据速率和

上即时协议 ■ 静态均衡和预加重了优异的信号完整性

■ 每通道功耗150毫瓦 ■ 灵活的时钟结构,支持多种协议在一个单一的收发器

block ■ Cyclone IV GX器件提供专用的硬IP支持PCI Express(PIPE)(PCIe)

21

—

—

—

—

179 66

179

66

—

—

—

—

—

—

EP4CE10 91

21

—

—

—

—

179 66

179Biblioteka 66———

EP4CE115

Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGAB1 VREFB1N0 IO DIFFIO_L1p H7B1 VREFB1N0 IO DIFFIO_L1n C2 G3 DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L2p D2 B2 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L2n D1 B1 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO VREFB1N0 H7 G5B1 VREFB1N0 IO DIFFIO_L3p nRESET G6 E4 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L3n G5 E3 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L4p E3 C2 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 B1 VREFB1N0 IO DIFFIO_L4n F3 C1 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L5p F5 D2 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L5n DATA1,ASDO F4 D1B1 VREFB1N0 IO H6B1 VREFB1N0 IO DIFFIO_L6p G4 H6 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L6n G3 J6 DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L7p H4B1 VREFB1N0 IO DIFFIO_L7n H3 H3B1 VREFB1N0 IO DIFFIO_L8p FLASH_nCE,nCSO E2 E2B1 VREFB1N0 IO DIFFIO_L8n E1 E1 DQ1L DQ1L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L9p F2 F2 DM2L DM1L/BWS#1L DM1L/BWS#1L DM2L DM1L/BWS#1L DM1L/BWS#1LB1 VREFB1N1 IO DIFFIO_L9n F1 F1 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB1 VREFB1N1 IO H5 H4B1 VREFB1N1 IO VREFB1N1 L5 H5B1 VREFB1N1 IO DIFFIO_L10p J4B1 VREFB1N1 IO DIFFIO_L10n J3 DQ0L DQ1L DQ1LB1 VREFB1N1 nSTATUS nSTATUS M6 K6B1 VREFB1N1 IO DIFFIO_L11p G2 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L11n G1B1 VREFB1N1 IO DIFFIO_L12p K2 J4 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 B1 VREFB1N1 IO DIFFIO_L12n K1 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L13p K4 H2 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L13n K3 H1 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L14p L4B1 VREFB1N1 IO DIFFIO_L14n L3B1 VREFB1N1 IO DIFFIO_L15p M4B1 VREFB1N1 IO DIFFIO_L15n M3B1 VREFB1N1 IO DIFFIO_L16p J6B1 VREFB1N1 IO DIFFIO_L16n J5B1 VREFB1N1 IO DIFFIO_L17p J7B1 VREFB1N1 IO DIFFIO_L17n K7B1 VREFB1N2 IO DIFFIO_L18p K8B1 VREFB1N2 IO DIFFIO_L18n L8B1 VREFB1N2 IO VREFB1N2 M5 J3B1 VREFB1N2 IO DIFFIO_L19p L7B1 VREFB1N2 IO DIFFIO_L19n L6B1 VREFB1N2 IO DIFFIO_L20p N4B1 VREFB1N2 IO DIFFIO_L20n N3B1 VREFB1N2 IO DIFFIO_L21p M8B1 VREFB1N2 IO DIFFIO_L21n M7B1 VREFB1N2 IO DIFFIO_L22p L2B1 VREFB1N2 IO DIFFIO_L22n L1 DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L23p M2 J2 DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L23n M1 J1 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L24p P2B1 VREFB1N2 IO DIFFIO_L24n P1 DQ0L DQ1L DQ1LB1 VREFB1N2 IO N8B1 VREFB1N2 DCLK DCLK P3 K2B1 VREFB1N2 IO DATA0 N7 K1B1 VREFB1N2 nCONFIG nCONFIG P4 K5B1 VREFB1N2 TDI TDI P7 L5B1 VREFB1N2 TCK TCK P5 L2B1 VREFB1N2 TMS TMS P8 L1B1 VREFB1N2 TDO TDO P6 L4B1 VREFB1N2 nCE nCE R8 L3B1 VREFB1N2 CLK1 DIFFCLK_0n J1 G1B2 VREFB2N0 CLK2 DIFFCLK_1p Y2 T2B2 VREFB2N0 CLK3 DIFFCLK_1n Y1 T1B2 VREFB2N0 IO DIFFIO_L25p R2 L6 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB2 VREFB2N0 IO DIFFIO_L25n R1 M6 DQ1L DQ1L DQ0L DQ1L DQ1LB2 VREFB2N0 IO DIFFIO_L26p R7B2 VREFB2N0 IO DIFFIO_L26n R6B2 VREFB2N0 IO DIFFIO_L27p U3 M2 DM0L DM1L/BWS#1L DM1L/BWS#1L DQ0L DQ1L DQ1LBank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFB Group Pin Name / Function Optional Function(s)Configuration Function F780F484DQS for X8/X9 in 780 FBGADQS for X16/X18 in 780 FBGA DQS for X32/X36 in 780 FBGA DQS for X8/X9 in 484 FBGADQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGAPin Information for the Cyclone ® IV EP4CE115 DeviceVersion 1.1 Notes (1), (2), (3)Notes:(3) For more information about pin definition and pin connection guidelines, refer to the Cyclone IV Device Family Pin Connection Guidelines.(1) If the p pin or n pin is not available for the package, the particular differential pair is not supported.(2) For DQS pins that do not have the associated DQ pins, the particular DQS is not supported. PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Pin List Page 11 of 13Notes:1. This is a top view of the silicon die.2. This is only a pictorial representation to provide an idea of placement on the device. For exact locations, refer to the pin list and the Quartus® II software.VREFB4N1VREFB4N0B4B3VREFB3N2VREFB3N1VREFB3N0VREFB4N2B7V R E F B 5N 0V R E F B 2N 1V R E F B 5N 1B 2B 5V R E F B 2N 2V R E F B 5N 2V R E F B 2N 0PLL1V R E F B 6N 1V R E F B 1N 2V R E F B 6N 2B 1B 6V R E F B 1N 0V R E F B 6N 0V R E F B 1N 1PLL4Pin Information for the Cyclone ® IV EP4CE115 DeviceVersion 1.1VREFB7N1VREFB7N0PLL2VREFB8N2VREFB8N1VREFB8N0VREFB7N2PLL3B8PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Bank & PLL DiagramPage 12 of 13Pin Information for the Cyclone® IV EP4CE115 DeviceVersion 1.1Version Number Date Changes made1.01/25/2010Initial Release.1.16/10/2011Removed Pin Definitions sheet.PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Revision History Page 13 of 13。

EPM240T100I5N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

256-Pin FineLine

BGA

324-Pin FineLine

BGA

0.5

0.5

1

1

49

121

289

361

7×7

11 × 11 17 × 17 19 × 19

芯片中文手册,看全文,戳

MAX II器件具有内部线性稳压器,它支持3.3 V或2.5 V外接电源电压,调节 供给下降到1.8 V MAX IIG和MAX IIZ器件内部工作电压只接受1.8 V外部电源. MAX IIZ器件引脚兼容100针微型FineLine BGA和256引脚微型FineLine BGA封装 MAX IIG设备.除外部电源电压要求,MAX II和MAX II G设备具有相同引脚 输出和时序规范.

f

有关等效宏单元详细信息,请参阅

宏单元转换方法

白皮书.

MAX II逻辑元素

MAX II和MAX IIG器件有三种速度等级:-3,-4,-5,与

-3是最快.同样,MAX IIZ器件有三种速度等级可供选择:-6,

-7,和-8,以-6是最快.这些速度等级代表总体相对

性能,而不是任何特定时序参数.对于传播延迟定时

由MAX II系列支持.

表1-5 显示外部电源电压

表 1-5. MAX II外接电源电压

设备

多电压内核外部电源电压(V 多电压I / O接口电压电平(V 须知 表 1-5: (1)MAX IIG和MAX IIZ器件只接受1.8 V他们 (2)MAX II器件在1.8 V内部操作

) (2) )

EPM 240 EPM 570 EPM 1270 EPM 2210

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

EP3C25Q240C8N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

手术

—

1.15 1.2 1.25

V

—

3.135 3.3 3.465 V

电源电压为输出缓冲器,3.0-V

手术

—

2.85

3

3.15

V

VCCIO (3), (4)

电源电压为输出缓冲器,2.5-V

手术

电源电压为输出缓冲器,1.8-V

手术

电源电压为输出缓冲器,1.5-V

手术

—

2.375 2.5 2.625 V

(4)所有输入缓冲器由在V驱动

供电.

(5)50-200毫秒之间POR时间标准POR范围.每个单独电源应达到在推荐工作范围 50毫秒.

3-9毫秒(6)POR时间,快速POR范围.每个单独电源应在3毫秒达到推荐工作范围内.

芯片中文手册,看全文,戳

第 1章: Cyclone III器件数据表

表1-2 列出所允许最大输入电压过冲和 过冲电压作为在装置寿命百分比持续时间. 允许最大过冲持续时间被指定为高时间比设备寿命百分比.

Max

Unit

1.8

V

3.9

V

3.75

V

1.8

V

3.95

V

40

mA

±2000

V

±500

V

150

°C

125

°C

表1-2 and

芯片中文手册,看全文,戳

芯片中文手册,看全文,戳

July 2012 CIII52001-3.5

CIII52001-3.5

1.Cyclone III器件数据表

本章介绍电气特性,开关特性,以及I / O

对Cyclone时机

EP3C40F484C8中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

—

1.71 1.8 1.89

V

—

1.425 1.5 1.575 V

电源电压为输出缓冲器,1.2-V

手术

—

1.14 1.2 1.26

V

VCCA (3)

VCCD_PLL (3) VI VO

供应(模拟)电压PLL

调节器

供应(数字)电压PLL

输入电压 输出电压

TJ

工作结温

tRAMP IDiode

电源斜坡时间

芯片中文手册,看全文,戳

July 2012 CIII52001-3.5

CIII52001-3.5

1.Cyclone III器件数据表

本章介绍电气特性,开关特性,以及I / O

对Cyclone时机

® III器件.一个术语表还包括供您参考.

电气特性

以下各节提供有关绝对最大额定值详细信息, 推荐工作条件,直流特性,和其他规范 Cyclone III器件.

表1-2 列出所允许最大输入电压过冲和 过冲电压作为在装置寿命百分比持续时间. 允许最大过冲持续时间被指定为高时间比设备寿命百分比.

Max

Unit

1.8

V

3.9

V

3.75

V

1.8

V

3.95

V

40

mA

±2000

V

±500

V

150

°C

125

°C

表1-2 and

芯片中文手册,看全文,戳

Typ Max Unit — 10 mA — 10 mA

总线防护持

总线防护持防护留源在最后一个有效逻辑状态,驾驶它要么进入高阻抗状态或者被删除 .每个I / O引脚有一个选项,以使总线防护持在用户模式.总线防护持始终在 配置模式禁用.

EP1C6Q240I7N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

更改摘要

— — — — — —

1–3

初稿

使用该设备插脚引线对于一个给定包所有计划中密度引脚

输入识别哪些I / O引脚可以迁移.在Quartus

® II

软件可以自动交叉引用和地点所有引脚你

当给定一个设备迁移列表.如果一个设备有电源或地 销,但这些相同引脚是不同装置,其在对用户I / O 迁移路径,Quartus II软件防护证销不作为 用户I / O在Quartus II软件.确防护这些引脚连接

100-Pin TQFP

0.5 256 16×16

144-Pin TQFP

0.5 484 22×22

240-Pin PQFP

0.5 1,024 34.6×34.6

256-Pin FineLine

BGA

1.0

289

17×17

324-Pin FineLine

BGA

1.0

361

19×19

400-Pin FineLine

1–2

初稿

2008年 5月

芯片中文手册,看全文,戳

文档修订历史记录

到电路板上相应平面. Quartus II软件储备 I / O引脚所必需与在同一个包有多个电源引脚较大密度布局电源引 脚.

表 1-3.旋风 QFP和 BGAFineLine包装规格

尺度

间距(mm) 区(毫米 ) 长短 × width (mm × mm)

高达288千位RAM.有这样锁相环路(PLL),用于时钟和一个专用双倍数据

速率(DDR)接口,以满足DDR SDRAM和快速周期RAM(FCRAM)内存需求特

点,Cyclone器件可用于数据通道应用提供具有成本效益解决

方案. Cyclone器件支持多种I / O标准,包括LVDS数据速率高达每

EP4CE115

Bank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGAB1 VREFB1N0 IO DIFFIO_L1p H7B1 VREFB1N0 IO DIFFIO_L1n C2 G3 DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L2p D2 B2 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L2n D1 B1 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO VREFB1N0 H7 G5B1 VREFB1N0 IO DIFFIO_L3p nRESET G6 E4 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L3n G5 E3 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L4p E3 C2 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 DQS2L/CQ3L,CDPCLK0 B1 VREFB1N0 IO DIFFIO_L4n F3 C1 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L5p F5 D2 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L5n DATA1,ASDO F4 D1B1 VREFB1N0 IO H6B1 VREFB1N0 IO DIFFIO_L6p G4 H6 DQ2L DQ1L DQ1L DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L6n G3 J6 DQ2L DQ1L DQ1LB1 VREFB1N0 IO DIFFIO_L7p H4B1 VREFB1N0 IO DIFFIO_L7n H3 H3B1 VREFB1N0 IO DIFFIO_L8p FLASH_nCE,nCSO E2 E2B1 VREFB1N0 IO DIFFIO_L8n E1 E1 DQ1L DQ1L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L9p F2 F2 DM2L DM1L/BWS#1L DM1L/BWS#1L DM2L DM1L/BWS#1L DM1L/BWS#1LB1 VREFB1N1 IO DIFFIO_L9n F1 F1 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB1 VREFB1N1 IO H5 H4B1 VREFB1N1 IO VREFB1N1 L5 H5B1 VREFB1N1 IO DIFFIO_L10p J4B1 VREFB1N1 IO DIFFIO_L10n J3 DQ0L DQ1L DQ1LB1 VREFB1N1 nSTATUS nSTATUS M6 K6B1 VREFB1N1 IO DIFFIO_L11p G2 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L11n G1B1 VREFB1N1 IO DIFFIO_L12p K2 J4 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 DQS0L/CQ1L,DPCLK0 B1 VREFB1N1 IO DIFFIO_L12n K1 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L13p K4 H2 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L13n K3 H1 DQ0L DQ1L DQ1LB1 VREFB1N1 IO DIFFIO_L14p L4B1 VREFB1N1 IO DIFFIO_L14n L3B1 VREFB1N1 IO DIFFIO_L15p M4B1 VREFB1N1 IO DIFFIO_L15n M3B1 VREFB1N1 IO DIFFIO_L16p J6B1 VREFB1N1 IO DIFFIO_L16n J5B1 VREFB1N1 IO DIFFIO_L17p J7B1 VREFB1N1 IO DIFFIO_L17n K7B1 VREFB1N2 IO DIFFIO_L18p K8B1 VREFB1N2 IO DIFFIO_L18n L8B1 VREFB1N2 IO VREFB1N2 M5 J3B1 VREFB1N2 IO DIFFIO_L19p L7B1 VREFB1N2 IO DIFFIO_L19n L6B1 VREFB1N2 IO DIFFIO_L20p N4B1 VREFB1N2 IO DIFFIO_L20n N3B1 VREFB1N2 IO DIFFIO_L21p M8B1 VREFB1N2 IO DIFFIO_L21n M7B1 VREFB1N2 IO DIFFIO_L22p L2B1 VREFB1N2 IO DIFFIO_L22n L1 DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L23p M2 J2 DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L23n M1 J1 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB1 VREFB1N2 IO DIFFIO_L24p P2B1 VREFB1N2 IO DIFFIO_L24n P1 DQ0L DQ1L DQ1LB1 VREFB1N2 IO N8B1 VREFB1N2 DCLK DCLK P3 K2B1 VREFB1N2 IO DATA0 N7 K1B1 VREFB1N2 nCONFIG nCONFIG P4 K5B1 VREFB1N2 TDI TDI P7 L5B1 VREFB1N2 TCK TCK P5 L2B1 VREFB1N2 TMS TMS P8 L1B1 VREFB1N2 TDO TDO P6 L4B1 VREFB1N2 nCE nCE R8 L3B1 VREFB1N2 CLK1 DIFFCLK_0n J1 G1B2 VREFB2N0 CLK2 DIFFCLK_1p Y2 T2B2 VREFB2N0 CLK3 DIFFCLK_1n Y1 T1B2 VREFB2N0 IO DIFFIO_L25p R2 L6 DQ0L DQ1L DQ1L DQ0L DQ1L DQ1LB2 VREFB2N0 IO DIFFIO_L25n R1 M6 DQ1L DQ1L DQ0L DQ1L DQ1LB2 VREFB2N0 IO DIFFIO_L26p R7B2 VREFB2N0 IO DIFFIO_L26n R6B2 VREFB2N0 IO DIFFIO_L27p U3 M2 DM0L DM1L/BWS#1L DM1L/BWS#1L DQ0L DQ1L DQ1LBank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFBGroupPin Name /FunctionOptionalFunction(s)ConfigurationFunctionF780F484DQS for X8/X9 in 780 FBGA DQS for X16/X18 in 780FBGADQS for X32/X36 in 780FBGADQS for X8/X9 in 484 FBGA DQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGABank Number VREFB Group Pin Name / Function Optional Function(s)Configuration Function F780F484DQS for X8/X9 in 780 FBGADQS for X16/X18 in 780 FBGA DQS for X32/X36 in 780 FBGA DQS for X8/X9 in 484 FBGADQS for X16/X18 in 484 FBGA DQS for X32/X36 in 484 FBGAPin Information for the Cyclone ® IV EP4CE115 DeviceVersion 1.1 Notes (1), (2), (3)Notes:(3) For more information about pin definition and pin connection guidelines, refer to the Cyclone IV Device Family Pin Connection Guidelines.(1) If the p pin or n pin is not available for the package, the particular differential pair is not supported.(2) For DQS pins that do not have the associated DQ pins, the particular DQS is not supported. PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Pin List Page 11 of 13Notes:1. This is a top view of the silicon die.2. This is only a pictorial representation to provide an idea of placement on the device. For exact locations, refer to the pin list and the Quartus® II software.VREFB4N1VREFB4N0B4B3VREFB3N2VREFB3N1VREFB3N0VREFB4N2B7V R E F B 5N 0V R E F B 2N 1V R E F B 5N 1B 2B 5V R E F B 2N 2V R E F B 5N 2V R E F B 2N 0PLL1V R E F B 6N 1V R E F B 1N 2V R E F B 6N 2B 1B 6V R E F B 1N 0V R E F B 6N 0V R E F B 1N 1PLL4Pin Information for the Cyclone ® IV EP4CE115 DeviceVersion 1.1VREFB7N1VREFB7N0PLL2VREFB8N2VREFB8N1VREFB8N0VREFB7N2PLL3B8PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Bank & PLL DiagramPage 12 of 13Pin Information for the Cyclone® IV EP4CE115 DeviceVersion 1.1Version Number Date Changes made1.01/25/2010Initial Release.1.16/10/2011Removed Pin Definitions sheet.PT-EP4CE115-1.1Copyright © 2011 Altera Corp.Revision History Page 13 of 13。

EPM240GT100C4N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

由MAX II系列支持.

表1-5 显示外部电源电压

表 1-5. MAX II外接电源电压

设备

多电压内核外部电源电压(V 多电压I / O接口电压电平(V 须知 表 1-5: (1)MAX IIG和MAX IIZ器件只接受1.8 V他们 (2)MAX II器件在1.8 V内部操作

) (2) )

EPM 240 EPM 570 EPM 1270 EPM 2210

3.3 V / 2.5 V或1.8 V ■ 多电压I / O接口,支持3.3 V,2.5 V,1.8 V和1.5 V逻辑电平 ■ 总线型架构,包括可编程摆率,驱动能力,

总线防护持,和可编程上拉电阻

■ 施密特触发器能够容忍噪声输入(每个引脚可编程)

■ I / O是完全符合外围组件互连特别 兴趣小组(PCI SIG)PCI本地总线规范,修订2.2 3.3 V 工作在66兆赫

100-Pin FineLine

BGA

100-Pin TQFP

0.5

0.5

1

0.5

25

36

121

256

5×5

6×6

11 × 11 16 × 16

144-Pin TQFP

0.5 484 22 × 22

144-Pin Micro FineLine BGA

256-Pin Micro FineLine BGA

256-Pin FineLine

BGA

324-Pin FineLine

BGA

0.5

0.5

1

1

49

121

289

361

7×7

11 × 11 17 × 17 19 × 19

芯片中文手册,看全文,戳

EPM9320LC84-15N中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

84-Pin 208-Pin 240-Pin 280-Pin 304-Pin 356-Pin

PLCC RQFP RQFP PGA RQFP BGA

EPM9320 60 (2)

132

–

168

–

168

EPM9320A 60 (2)

132

–

–

–

168

EPM9400 59 (2)

139

159

–

–

–

EPM9480

Note: (1) 内部逻辑阵列模块显示(LAB)性能.括号内数字显示,从行外部延迟

输入端子排I / O引脚.

速度等级

-15 118 118 118 7.9 (15) 10.9 (18)

-20

100 100 100 10 (20) 16 (26)

在MAX 9000架构支持系统级逻辑功能高密度集成.它很容易集成多个 可编程逻辑器件,从好朋友,GAL和22V10s到现场可编程门阵列(FPGA) 器件和EPLD中.

图1

示出MAX 9000体系结构框图.

5

–

146

175

–

–

–

EPM9560

–

153

191

216

216

216

EPM9560A

–

153

191

–

–

216

注意事项: (1) MAX 9000器件封装类型包括塑料J引线芯片载体(PLCC),功率四方扁平封装(

RQFP),陶瓷针栅阵列(PGA),和球栅阵列(BGA)封装.

(2) 犯设计这种设备之前执行完整热分析

Units

MHz MHz MHz ns ns

3

FPGA可编程逻辑器件芯片EP4CE15U19C9N中文规格书

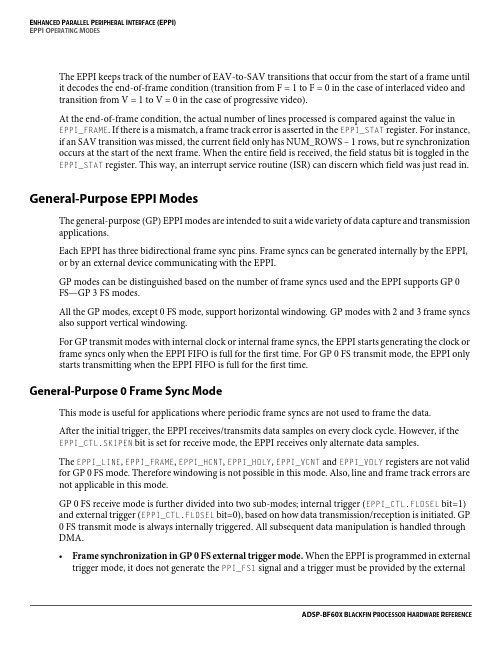

E NHANCED P ARALLEL P ERIPHERAL I NTERFACE (EPPI)EPPI O PERATING M ODESThe EPPI keeps track of the number of EAV-to-SAV transitions that occur from the start of a frame until it decodes the end-of-frame condition (transition from F = 1 to F = 0 in the case of interlaced video and transition from V = 1 to V = 0 in the case of progressive video).At the end-of-frame condition, the actual number of lines processed is compared against the value in EPPI_FRAME. If there is a mismatch, a frame track error is asserted in the EPPI_STAT register. For instance, if an SAV transition was missed, the current field only has NUM_ROWS – 1 rows, but re synchronization occurs at the start of the next frame. When the entire field is received, the field status bit is toggled in the EPPI_STAT register. This way, an interrupt service routine (ISR) can discern which field was just read in.General-Purpose EPPI ModesThe general-purpose (GP) EPPI modes are intended to suit a wide variety of data capture and transmission applications.Each EPPI has three bidirectional frame sync pins. Frame syncs can be generated internally by the EPPI, or by an external device communicating with the EPPI.GP modes can be distinguished based on the number of frame syncs used and the EPPI supports GP 0 FS—GP 3 FS modes.All the GP modes, except 0 FS mode, support horizontal windowing. GP modes with 2 and 3 frame syncs also support vertical windowing.For GP transmit modes with internal clock or internal frame syncs, the EPPI starts generating the clock or frame syncs only when the EPPI FIFO is full for the first time. For GP 0 FS transmit mode, the EPPI only starts transmitting when the EPPI FIFO is full for the first time.General-Purpose 0 Frame Sync ModeThis mode is useful for applications where periodic frame syncs are not used to frame the data.After the initial trigger, the EPPI receives/transmits data samples on every clock cycle. However, if the EPPI_CTL.SKIPEN bit is set for receive mode, the EPPI receives only alternate data samples.The EPPI_LINE, EPPI_FRAME, EPPI_HCNT, EPPI_HDLY, EPPI_VCNT and EPPI_VDLY registers are not valid for GP 0 FS mode. Therefore windowing is not possible in this mode. Also, line and frame track errors are not applicable in this mode.GP 0 FS receive mode is further divided into two sub-modes; internal trigger (EPPI_CTL.FLDSEL bit=1) and external trigger (EPPI_CTL.FLDSEL bit=0), based on how data transmission/reception is initiated. GP0 FS transmit mode is always internally triggered. All subsequent data manipulation is handled throughDMA.•Frame synchronization in GP 0 FS external trigger mode. When the EPPI is programmed in external trigger mode, it does not generate the PPI_FS1 signal and a trigger must be provided by the external12RGB sensor No splitting possible.EPPI_CTL.PACKEN=1. Two EPPI words are zero filled/signextended to 16 bits and packed to 32-bit DMA data.EPPI_CTL.PACKEN=0. Each EPPI word may be zero filled/sign extended to 16 bits and sent as a 16 bit data on the 32-bit DMA bus. This consumes double the bandwidth of the12-bit case with EPPI_CTL.PACKEN=1;ADCs Each EPPI word is zero filled/sign extended to 16 bits.EPPI_CTL.SPLTEO=1EPPI_CTL.SUBSPLTODD=0 since there are only twocomponents.14ADCs Each EPPI word is zero filled/sign extended to 16 bits.EPPI_CTL.SPLTEO=1EPPI_CTL.SUBSPLTODD=0 since there are only twocomponents.168-bit luma/chroma pair forNTSC or HD EPPI_CTL.SPLTEO=1, EPPI_CTL.SPLTWRD=1, EPPI_CTL. SUBSPLTODD=1 if required to separate chroma components.16-bit luma/chroma pair for NTSC or HD EPPI_CTL.SPLTEO=1, EPPI_CTL.SPLTWRD=0, EPPI_CTL. SUBSPLTODD=1 if required to separate chroma components.RGB565 sensor No splitting possible.EPPI_CTL.PACKEN=1. Two EPPI words are packed to a 32bit DMA data. EPPI_CTL.RGBFMTEN is valid only intransmit modes. So, RGB565 cannot be made byte alignedin memory.EPPI_CTL.PACKEN=0. Each EPPI word is sent as a 16 bitdata on the 32 bit DMA bus. This consumes double thebandwidth of the 16 bit case with EPPI_CTL.PACKEN=18-bit ADCs I/Q pair EPPI_CTL.SPLTEO=1, EPPI_CTL.SPLTWRD=1, EPPI_CTL. SUBSPLTODD=0.16-bit ADCs I/Q pair EPPI_CTL.SPLTEO=1, EPPI_CTL.SPLTWRD=0, EPPI_CTL. SUBSPLTODD=0.2010-bit luma/chroma pair forNTSC or HD No support for 20-bit mode.Table 31-12: EPPI Receive Data Formats (Continued)Input Data Width Use Model Splitting/Packing OptionsAlso in case 2, if transmission of valid data is held off due to delays programmed in the EPPI_HDLY and/or EPPI_VDLY registers, the assertion of PPI_FS3 is also held off accordingly, on a per-line and/or per-frame basis.General-Purpose 3 Frame Sync ModeThis mode is useful for video applications that use three hardware synchronization signals, HSYNC, VSYNC, and FIELD. The HSYNC can be connected to the PPI_FS1 pin, VSYNC can be connected to the PPI_FS2 pin, and FIELD can be connected to the PPI_FS3 pin.GP 3 FS mode is similar in operation to GP 2 FS mode, except that the start of frame synchronization in GP 3 FS mode also takes into account the PPI_FS3 pin. All the windowing register settings (EPPI_FRAME, EPPI_LINE, EPPI_HDLY, EPPI_HCNT, EPPI_VDLY and EPPI_VCNT registers), as well as data reception/trans-mission and error generation are the same as for GP 2 FS mode. In addition, for GP 3 FS mode withinternal frame syncs, the EPPI_CTL.FLDSEL bit setting specifies the condition under which the transfer begins.The PPI_FS3signal is generated by the EPPI and toggles during every assertion of PPI_FS2 or a combina-tion of PPI_FS2 and PPI_FS1(depending on the EPPI_CTL.FLDSEL bit setting). The EPPI skips an PPI_ FS2signal if the PPI_FS3value is high. Because of this condition, as a programming guideline, the PPI_ FS2period value should be half of the total number of pixels in the frame as in GP 3 FS mode. When in GP2 FS mode, the PPI_FS2period should be programmed with the value equal to the number of pixels perframe.Supported Data FormatsThe following sections describe EPPI receive and transmit data formats.Receive Data FormatsThe following table provides information about EPPI configuration for specific use models for receive data.。

EPCS4中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

Yes

No

Yes

EPCS64

67,108,864

NoBiblioteka YesNoYes

EPCS128 134,217,728

No

Yes

No

Yes

须知 表 3-1: (1)要设置这些设备采用Altera编程单元或主编程器,请参考 (2)EPCS装置可以被重新编程系统与字节冲击波II下载线缆或使用SRunner外部微处理器.欲了解更多

CC 该EPCS准备.如果它

是不是,你必须持有 n配置 低到EPCS所有电源轨都准备好.

FPGA控制

nSTATUS and CONF_DONE 在AS配置过程中销

模式.如果 CONF_DONE 信号不高配置或者结束

信号变高太早,FPGA将脉冲其

nSTATUS 引脚为低电平启动

重新配置.在成功配置中,FPGA释放

DATA0, DCLK, ASDO,and nCSO 在FPGA控制信号,

分别.

图3-2

示出串行配置设备经由一个编程

下载线,其配置在AS模式中FPGA.

图3-3

显示一个串口

使用APU或第三方编程器配置在AS配置模式下FPGA配置器件编程.

f

有关串行配置器件引脚说明详细信息,请参阅

表3-23.

图 3-2.

操作

电压( V)

3.3 3.3 3.3 3.3 3.3

对于8引脚SOIC封装,可以从EPCS1垂直迁移到EPCS4 或EPCS16因为相同器件封装中EPCS器件提供. 同样,对于一个16引脚SOIC封装,您可以垂直从EPCS16到EPCS64或EPCS128迁移.

使用压缩比计算来确定FPGA器件以适合EPCS.

FPGA可编程逻辑器件芯片EP4CE15F17I8N中文规格书

LP E VENT C ONTROLInterrupt SignalsEach link port has two dedicated interrupt lines registered with the System Event Controller—a datarequest interrupt and a status interrupt. Data request interrupts are asserted with respect to FIFO condi-tions for data transfer and status interrupts are asserted when a service request status or an overflow status is set. Each of these interrupts are explained below.•Data Request Interrupt. Asserted if the FIFO is not full in transmission mode and the FIFO is not empty in reception mode. This serves as a core triggered interrupt in non-DMA mode and as the DMA interrupt request in DMA mode. Generation of this interrupt is tied to the LP_STAT.FFST (link portbuffer status bit).•Link Port Transmit Service Request Interrupt (LTRQ). Allow a disabled link port to generate an interrupt when an external access is attempted. When a link port is configured as transmitter, thetransmit service request interrupt is enabled by setting the LP_CTL.TRQMSK bit. When set, an externalreceiver can indicate to the disabled transmitter that it needs to receive data through the connected linkport. The receiver does so by driving a high level on the LP_ACK line. When the LP_ACK of the disabledtransmitter link port is detected high, a LP_STAT.LTRQ interrupt in is generated, and the transmittercan enable itself for data transfer with the receiver. Note that a pull-down on LP_ACK is required forproper function of this feature.•Link Port Receive Service Request Interrupt (LRRQ). When a link port is configured as receiver, this interrupt is enabled by setting the LP_CTL.RRQMSK bit. When set, an external transmitter can indicateto the disabled receiver that it needs to receive data through the connected link port. The transmitterdoes so by driving the first data out. When the LP_CLK of the disabled receiver link port is detected high,a LP_STAT.LRRQ interrupt in is generated, and the receiver can further enable itself for data transferwith the transmitter. Note that a pull-down on the LP_CLK signal is required for proper function of thisfeature.•Link Port Receive Overflow Interrupt (LPOVF). Generated when the receiver FIFO overflows and is enabled by setting the LP_CTL.ROVFMSK bit. This may happen if the transmitter continues to transmitdata even though the receiver has de asserted LP_ACK signal causing the receive FIFO to overflow. Enabling Link Port InterruptsA data request interrupt is fed to the System Event Controller directly and can be controlled separatelyfrom the application.Service interrupts and the overflow interrupt can be masked by setting the corresponding mask bits in LP_ CTL register, as these are OR’ed and fed to the SIC as a single LP_STAT interrupt. These interrupts are latched and stored in the associated bits of LP_STAT register. If an LP_STAT interrupt occurs, in the ISR, programs should read the LP_STAT register bits to determine the type of interrupt. Note that these bits are write-one-to-clear (W1C); writing one to the bit resets the bit and disables the corresponding interrupt.LP P ROGRAMMING M ODEL2.Install interrupt handlers for DMA and for transfer status (service request interrupt).3.Configure the link port to transmit by setting the LP_CTL bit and enable the transmit request interruptmask by setting the LP_CTL.TRQMSK bit.4.Program the link port clock divider by writing a value to the LP_DIV register.5.If using DMA stop mode/auto buffer mode, program the appropriate DMA registers.A DDITIONAL I NFORMATION:An example configuration is: DMA_ADDRSTART, DMA_XCNT, DMA_XMOD and DMA_CFG registers (Stop/Auto, Psize=1, Msize=4, interrupt generation and memory read).6.Wait for the link port receiver (connected externally) to be enabled. The application can wait for thetransmit service request interrupt to assert.7.Clear the transmit service request interrupt status by writing 1 to the LP_STAT.LTRQ bit.8.Enable DMA by setting the DMA_CFG.EN bit.9.Enable the link port by setting the LP_CTL.EN bit.10.Wait for DMA to assert a transfer completion interrupt.11.Clear the DMA interrupt source by writing 1 to the DMA_STAT.IRQDONE bit.Setting Up a DMA Receive OperationThis section describes the typical steps for using the link ports in DMA receive mode.1.Enable the link port pins in GPIO port mux using the appropriate PORT_FER and PORT_MUX registers.2.Install interrupt handlers for DMA and for transfer status (service request interrupt).3.Configure the link port for reception (clear the LP_CTL.TRAN bit) and enable the receive request inter-rupt mask by setting the LP_CTL.RRQMSK bit.4.If using DMA stop mode/auto buffer mode, program the DMA registers.A DDITIONAL I NFORMATION:An example configuration is: DMA_ADDRSTART, DMA_XCNT, DMA_XMOD and DMA_CFG registers (Stop/Auto, Psize=1, Msize=4, interrupt generation and memory write).5.If using DMA array mode/list mode, create DMA configuration data structures filled with components.A DDITIONAL I NFORMATION:An example configuration is: DMA_ADDRSTART, DMA_XCNT, DMA_XMOD and DMA_CFG registers (Array/List, Psize=1, Msize=4, Interrupt generation, memory write and fetch=4/5) andDMA_DSCPTR_NXT register (if list mode). Further program DMA configuration register (Array/List,Psize=1, Msize=4, Memory Write and Fetch=4/5) and program the DMA_DSCPTR_NXT register (if listmode).ADSP-BF60X LP R EGISTER D ESCRIPTIONS3.Configure link port for reception (clear LP_CTL.TRAN bit) and enable receive request interrupt mask(set LP_CTL.RRQMSK bit).4.Wait for the link port transmit (connected externally) to be enabled with subsequent transmission ofdata. Application can wait for receive service request interrupt to be asserted.5.Clear the receive service request interrupt status by writing 1 to the LP_STAT.LRRQ bit.6.Enable the link port by setting the LP_CTL.EN bit.7.The data request interrupt is asserted whenever there is free space in the FIFO. The application can readfrom the LP_RX register based on the FIFO conditions (1 or 2 or 3 data available) which is reflected inthe LP_STAT.FFST bit field.ADSP-BF60x LP Register DescriptionsLink Port (LP) contains the following registers.Table 28-6:ADSP-BF60x LP Register ListName DescriptionLP_CTL Control RegisterLP_STAT Status RegisterLP_DIV Clock Divider ValueLP_TX Transmit BufferLP_RX Receive BufferLP_TXIN_SHDW Shadow Input Transmit BufferLP_TXOUT_SHDW Shadow Output Transmit BufferControl RegisterThe LP_CTL register provides LP interrupt masking, selection of transfer direction, and link port enable.。

FPGA可编程逻辑器件芯片EP4CE15F17C7中文规格书

ADC C ONTROL M ODULE (ACM)ADSP-BF60X ACM R EGISTER D ESCRIPTIONSADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE 11(R/W1C)EV11Event 11 Status.The ACM_EVSTAT.EV11 bit indicates when the ACM has completedthe conversion for event 11. If set and the corresponding bit in ACM_EVMSK is set (interrupt enabled), the condition generates an interrupt.This bit is W1C.No Event 11 Conversion 1Event 11 Conversion Done10(R/W1C)EV10Event 10 Status.The ACM_EVSTAT.EV10 bit indicates when the ACM has completedthe conversion for event 10. If set and the corresponding bit in ACM_EVMSK is set (interrupt enabled), the condition generates an interrupt.This bit is W1C.No Event 10 Conversion 1Event 10 Conversion Done9(R/W1C)EV9Event 9 Status.The ACM_EVSTAT.EV9 bit indicates when the ACM has completed theconversion for event 9. If set and the corresponding bit in ACM_EVMSKis set (interrupt enabled), the condition generates an interrupt. Thisbit is W1C.No Event 9 Conversion 1Event 9 Conversion Done8(R/W1C)EV8Event 8 Status.The ACM_EVSTAT.EV8 bit indicates when the ACM has completed theconversion for event 8. If set and the corresponding bit in ACM_EVMSKis set (interrupt enabled), the condition generates an interrupt. Thisbit is W1C.No Event 8 Conversion 1Event 8 Conversion Done7(R/W1C)EV7Event 7 Status.The ACM_EVSTAT.EV7 bit indicates when the ACM has completed theconversion for event 7. If set and the corresponding bit in ACM_EVMSKis set (interrupt enabled), the condition generates an interrupt. Thisbit is W1C.No Event 7 Conversion 1Event 7 Conversion DoneTable 27-10:ACM_EVSTAT Register Fields (Continued)Bit No.(Access)Bit Name Description/EnumerationADC C ONTROL M ODULE (ACM)ADSP-BF60X ACM R EGISTER D ESCRIPTIONSADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEEvent Complete Interrupt Mask RegisterThe ACM_EVMSK register enables interrupts corresponding to status bits in the ACM_EVSTAT register. When an ACM_EVMSK bit is set (=1), an interrupt is generated when the corresponding event complete bit is set (bit in ACM_EVSTAT is set).1(R/W1C)EV1Event 1 Status.The ACM_EVSTAT.EV1 bit indicates when the ACM has completed theconversion for event 1. If set and the corresponding bit in ACM_EVMSKis set (interrupt enabled), the condition generates an interrupt. Thisbit is W1C.No Event 1 Conversion 1Event 1 Conversion Done(R/W1C)EV0Event 0 Status.The ACM_EVSTAT.EV0 bit indicates when the ACM has completed theconversion for event 0. If set and the corresponding bit in ACM_EVMSKis set (interrupt enabled), the condition generates an interrupt. Thisbit is W1C.No Event 0 Conversion 1Event 0 Conversion DoneTable 27-10:ACM_EVSTAT Register Fields (Continued)Bit No.(Access)Bit Name Description/EnumerationADC C ONTROL M ODULE (ACM)ADSP-BF60X ACM R EGISTER D ESCRIPTIONSADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE 15(R/W)EV15Event 15 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 14(R/W)EV14Event 14 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 13(R/W)EV13Event 13 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 12(R/W)EV12Event 12 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 11(R/W)EV11Event 11 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 10(R/W)EV10Event 10 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 9(R/W)EV9Event 9 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 8(R/W)EV8Event 8 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 7(R/W)EV7Event 7 Interrupt Enable.0Disable (Mask) Interrupt 1Enable (Unmask) Interrupt 6(R/W)EV6Event 6 Interrupt Enable.0Disable (Mask) Interrupt1Enable (Unmask) Interrupt Table 27-11:ACM_EVMSK Register Fields (Continued)Bit No.(Access)Bit Name Description/Enumeration。

FPGA可编程逻辑器件芯片EP4CE15U19C8N中文规格书

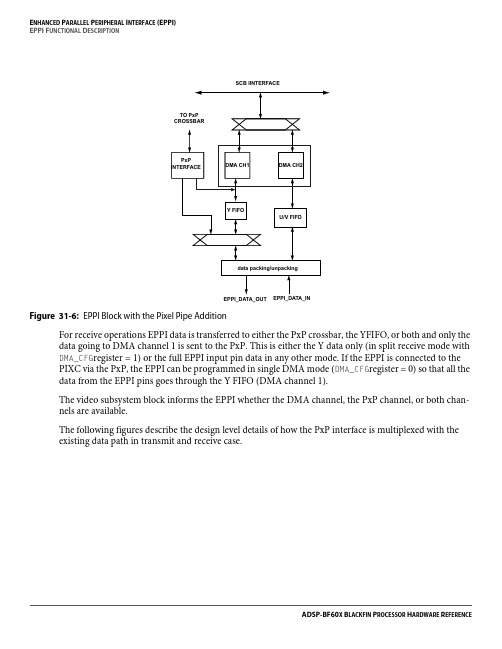

E NHANCED P ARALLEL P ERIPHERAL I NTERFACE (EPPI)EPPI F UNCTIONAL D ESCRIPTIONFigure 31-6:EPPI Block with the Pixel Pipe AdditionFor receive operations EPPI data is transferred to either the PxP crossbar, the YFIFO, or both and only thedata going to DMA channel 1 is sent to the PxP. This is either the Y data only (in split receive mode with DMA_CFG register = 1) or the full EPPI input pin data in any other mode. If the EPPI is connected to the PIXC via the PxP, the EPPI can be programmed in single DMA mode (DMA_CFG register = 0) so that all thedata from the EPPI pins goes through the Y FIFO (DMA channel 1).The video subsystem block informs the EPPI whether the DMA channel, the PxP channel, or both chan-nels are available.The following figures describe the design level details of how the PxP interface is multiplexed with theexisting data path in transmit and receive case.EPPI F UNCTIONAL D ESCRIPTIONFigure 31-8:Transmit Data Path with PxP Interface MuxingEPPI ClockThe EPPI can be supplied with an external clock, or the clock can be generated internally and supplied to external devices. For information on the maximum PPI_CLK specification in internal and external clock modes see the product specific data sheet.When using an external PPI_CLK, there may be up to two cycles latency before valid data is received or transmitted.The internal clock can be generated from SCLK if the EPPI_CTL.ICLKGEN bit is set. The generated clock frequency is then determined by the value in the EPPI_CLKDIV register. The internally generated EPPI clock frequency is:f PCLK = f SCLK/(EPPI_CLKDIV + 1)where:f PCLK – frequency of internally generated EPPI clockEPPI O PERATING M ODESThe letter F is used to distinguish Field 1 from Field 2. Interlaced video has two fields in a frame of data. It requires each field to be handled uniquely, and alternate rows of each field combined to create the actual video image.For interlaced video, F = 0 represents Field 1 (Odd Field) and F = 1 represents Field 2 (Even Field). Progres-sive video makes no distinction between Field 1 and Field 2, and F is always 0 for progressive video. Inter-laced video requires each field to be handled uniquely, because alternate rows of each field combine to create the actual video image.An entire field of video is comprised of active video plus horizontal blanking (the space between an EAV and SAV code) and vertical blanking (the space where V = 1). A field of video commences on a transition of the F bit.。

FPGA可编程逻辑器件芯片EP4CE15F23C8LN中文规格书

P IXEL C OMPOSITOR (PIXC)PIXC O PERATING M ODESADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEThe A xx coefficients are 10-bit signed values represented in two's complement format. A 11…A 33 are coef-ficient multipliers (for most cases, it is sufficient to specify these as integers between –512 and 511), and A 14, A 24, A 34 are simply offsets added to the result for each row. B 1, B 2, B 3 represent the input pixel compo-nent values (for example, YUV or RGB) and C 1, C 2, C 3 are the output pixel component values. Output pixel values are rounded to the nearest integerThe constant K equals 1/512. For example, to set A 11’s effective value to 0.299, this coefficient's MMR should be programmed to ROUND(.299*512), or 153. If a coefficient needs to be programmed with a value greater than 1, an extra bit exists in each coefficient's MMR to specify if an extra multiply by 4 must be performed after multiplying the input value by its coefficient. However, this setting can only be specified for an entire row, so if this bit is set, all the coefficients for that row (Ax1–Ax3) should be calculated as ROUND (coeff × 512/4). In other words, the constant K effectively becomes 1/128 for that row.For reference, the matrix equations representing conversion between YUV and RGB formats are:NOTE :For YUV-to-RGB conversion, the PIXC expects the input data to be arranged in the followingorder: VYUY, VYUY, and so on. As a result, if the input data is instead arranged as UYVY, UYVY, and so on, then, the columns Ax2 and Ax3 of the coefficient matrix are swapped.For RGB-to-YUV conversion, the PIXC arranges the output data by default in the following order: VYUY, VYUY, and so on. If the output data is desired to instead be arranged as UYVY, UYVY, and so on, then, rows A2x and A3x of the coefficient and bias matrices are swapped.Color Space Converter Output ThresholdsEach PIXC output sample is 8 bits wide, whether it is an R, G, B, Y, U or V component value. Therefore, any output sample must be in the 0 to 255 range. Since all the coefficients are programmable, some of the inputs, when operated upon by the coefficients, may produce an output outside the 0 to 255 range. In such cases, the PIXC clips the output component’s value to 0 or 255.P IXEL C OMPOSITOR (PIXC)PIXC O PERATING M ODESFigure 32-15:RGB/RGB to LCD/RGB or YUV 4:2:2Figure 32-16:YUV 4:4:4/YUV 4:4:4 to YUV 4:4:4 or YUV 4:2:2Example 3 - YUV 4:2:2/4:4:4 to YUV 4:4:4 or YUV 4:2:2See the figures for special use of this mode.In the special usage of this mode, a YUV 4:4:4 input stream and a YUV 4:2:2 input stream can be blended to produce either a YUV 4:4:4 or a YUV 4:2:2 output stream.Figure 32-17:YUV 4:2:2/RGB to LCD/RGB or YUV 4:2:2ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCEP IXEL C OMPOSITOR (PIXC)PIXC O PERATING M ODESYUV 4:2:2 conversion: V12Y1, U12Y2, V34Y3, U34Y4, ...[U12=(U1+U2)/2, U34=(U3+U4)/2][V12=(V1+V2)/2, V34=(V3+V4)/2]Supported Data FormatsFor the implementation of overlay, the PIXC needs two input data streams from two separate databuffers— a main image buffer and an overlay buffer. The data in the main image buffer can be formatted as YUV 4:2:2, RGB888, RGB666 or RGB565 while the overlay data must be in YUV 4:2:2 or RGB888format. The main image data and the overlay data can be in different formats. The output data can also be formatted as YUV 4:2:2, RGB888, RGB666 or RGB565. The formats are described in detail in the following sections.•Operation in YUV 4:2:2 Format•Operation in RGB888 Format•Operation in RGB565 Format•Operation in RGB666 Format•Operation with RGB656 and RGB666 FormatsOperation in YUV 4:2:2 FormatEach Y/U/V component is stored in 8 bits of data. The PIXC only accepts a YUV 4:2:2 interleaved format, in the following sequence:V1, Y1, U1, Y2, V3, Y3, U3, Y4 ...(Two components with the same suffix number (for example, V1 and U1) implies that they are extracted from the same pixel.)It is the user's responsibility to ensure that the YUV source data to the PIXC is in the correct interleaved format. Therefore, data processing may be necessary in order to meet this requirement.The figures below illustrate correct PIXC input buffer structure and data stream format.ADSP-BF60X B LACKFIN P ROCESSOR H ARDWARE R EFERENCE。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VCCINT (3) VCCA (1), (3) VCCD_PLL (2)

VCCIO (3), (4)

VCC_CLKIN

(3), (5), (6)

核心电压,PCIe硬核IP模块,和 收发器PCS电源

PLL模拟电源

PLL数字供电

3.3 I / O插槽电源

-V

手术

3.0 I / O插槽电源

-V

手术

2.5 I / O插槽电源

供应1.5 -V工作电压

差分时钟输入引脚电源

供应1.2 -V工作电压

条件

— — — — — — — — — — — — — — —

Min Typ Max Unit

1.16 1.2 1.24 V

2.375 2.5 2.625 V

1.16 1.2 1.24

V

3.135 3.3 3.465 V

2.85

3

3.15

电源电压为输出缓冲器, 3.3-V操作

电源电压为输出缓冲器, 3.0-V操作

电源电压为输出缓冲器, 2.5-V操作

电源电压为输出缓冲器, 1.8-V操作

电源电压为输出缓冲器, 1.5-V操作

电源电压为输出缓冲器, 1.2-V操作

供应(模拟)电压PLL

调节器

VCCD_PLL (3)

VI VO

供应(数字)电压PLL, 1.2-V操作

–0.5 —

3.6

V

0

—

VCCIO

V

0

—

85

°C

–40

—

100°C(5) –0—125°C

–40

—

125

°C

50 µs — 50毫秒 —

50 µs —

3毫秒 —

芯片中文手册,看全文,戳

第 1章: Cyclone IV器件手册

1–5

运行条件

表 1-3.推荐工作条件 Cyclone IV E器件

(2) V CCIO所有I / O块设备的操作过程中都必须启动.都 并且必须加电并断电的同时.

VCCA管脚必须供电到2.5 V(即使不使用锁相环)

(3) V CC 必须上升单调.

(4) V CCIO权力全部输入缓冲器.

(5)设备支持扩展的工作结温的I7高达125°C(正常范围为-40°C至100°C).当在使用I7设备 更宽的结温范围为-40°C至125°C,在Quartus设计时选择C8作为目标设备 设备满足所有C8时序规格,当I7设备使用超过100°C和高达125°C.

—

1.71 1.8 1.89

V

—

1.425 1.5 1.575 V

—

1.14 1.2 1.26

V

—

2.375 2.5 2.625 V

—

1.15 1.2 1.25

V

—

— —

对于商业用途 工业用 对于扩展温度 对于汽车使用 标准的上电复位

(POR) (6) 快速POR (7)

0.97 1.0 1.03

V

供应(数字)电压PLL, 1.0-V操作

输入电压

输出电压

TJ

工作结温

tRAMP

电源斜坡时间

条件

(1), (2) (第 2部 1) Min Typ Max Unit

—

1.15 1.2 1.25

V

—

0.97 1.0 1.03

V

—

3.135 3.3 3.465 V

—

2.85

3

3.15

V

—

2.375 2.5 2.625 V

表1-2 列出所允许的最大输入电压的过冲和 过冲电压作为在装置的寿命的百分比的持续时间. 允许的最大过冲的持续时间被指定为高的时间比设备的寿命百分比.

Max

Unit

1.8

V

3.75

V

4.5

V

3.75

V

4.5

V

3.75

V

3.75

V

1.8

V

4.2

V

40

mA

150

°C

125

°C

表1-2 and

芯片中文手册,看全文,戳

® II的软件.该I7

(6)上电复位时间标准POR介于50和200毫秒.每个单独的电源必须达到推荐的工作范围 在50毫秒内.

(7)上电复位时间,快速POR范围9之间3毫秒.每个单独的电源必须达到在推荐的工作范围 3毫秒.

表 1-4.推荐工作条件 Cyclone IV GX器件(第 2第 1部分)

符

参数

f

有关支持的速度牌号为各自的Cyclone IV更多信息

设备,指的是

Cyclone IV FPGA器件系列简介

一章.

1

Cyclone IV E器件均提供了1.0和1.2与1.0伏的核心电压V. Cyclone IV E器件的核

心电压已经连接到速度等级为“L”字头.

在这一章中,与工作温度范围相关联的前缀所连接到 速度等级;商业用“C”字头,工业用“I”前缀, 汽车有一个“A”字头.因此,商用设备被表示为C6,C7, C8,C8L,或C9L每各自的速率等级.工业设备被表示为I7,I8,或I8L.汽车设备被表示为A7.

从的Cyclone IV E和Cyclone IV GX器件的预期值.所有物资必须是没有高原严格单调.

表 1-3.推荐工作条件 Cyclone IV E器件

符

参数

VCCINT (3) VCCIO (3), (4) VCCA (3)

电源电压为内部逻辑, 1.2-V操作

电源电压为内部逻辑, 1.0-V操作

过冲电压示于红色和存在于的气旋IV输入引脚

设备超过4.3V,但低于4.4 V.从

表1-2, 为4.3伏,所述过冲

高时间过冲比例可高达65%,超过10年的时间.

高时间百分比的计算公式为(δT] / T)×100.这10年的时间就认定该设备始终是打开的

,100%I / O触发率和50%占空比信号.对于较低的I / O触发率和情况,其中设备处于

V

2.375 2.5 2.625 V

1.71 1.8 1.89 V

1.425 1.5 1.575 V

1.14 1.2 1.26 V

3.135 3.3 3.465 V

2.85

3

3.15

V

2.375 2.5 2.625 V

1.71 1.8 1.89 V

1.425 1.5 1.575 V

1.14 1.2 1.26 V

条件( V)

过冲持续时间为%高时间

Unit

交流输入

Vi

电压

VI = 4.20 VI = 4.25 VI = 4.30 VI = 4.35 VI = 4.40 VI = 4.45 VI = 4.50 VI = 4.55 VI = 4.60

100

%

98

%

65

%

43

%

29

%

20

%

13

%

9

%

6

%

图1-1

示出的方法来确定过冲持续时间.该

VCCA VCCD_PLL VCCIO VCC_CLKIN VCCH_GXB

VCCA_GXB

Phase-锁相环(PLL)模拟电源 PLL数字供电 I / O组电源

差分时钟输入引脚供电 收发器输出缓冲器电源

收发器物理介质附加(PMA)

和辅助电源

VCCL_GXB VI I OUT TSTG TJ

收发器PMA和辅助电源

对于Cyclone IV器件最大额定值.

表1-1 列出的绝对

c

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长的时间周期的绝对最大额定值设备操作具有设备上的不良影响.

表 1-1.对 Cyclone IV器件绝对最大额定值

符

参数

VCCINT

内核电压,PCI Express的 (PCIe )硬IP 块,和收发器物理编码子层 (PCS)电源

空闲状态,寿命增加.

图 1-1. Cyclone IV器件超调时间

4.4 V 4.3 V 3.3 V

DT T

芯片中文手册,看全文,戳

1–4

第 1章: Cyclone IV器件手册

运行条件

推荐工作条件

本节列出了AC和DC参数功能操作界限

Cyclone IV器件.

表1-3 and 表1-4 列出的稳态电压和电流

-V

手术

1.8 I / O插槽电源

-V

手术

1.5 I / O插槽电源

-V

手术

1.2 I / O插槽电源

-V

手术

差分时钟输入引脚电源

供应3.3 -V工作电压

差分时钟输入引脚电源

供应3.0 -V工作电压

差分时钟输入引脚电源

供应2.5 -V工作电压

差分时钟输入引脚电源

供应1.8 -V工作电压

差分时钟输入引脚电源

Cyclone IV器件在商业,工业,延伸产业和汽车级版本. Cyclone IV E器件提供-6(最快 ),-7,-8,-8L和-9L速度等级的商用设备,-8L速度等级为工业设备,以及用于扩展工业和汽 车设备-7速度等级. Cyclone IV GX器件提供-6(最快),-7和-8速度等级的商用设备和 -7为工业设备的速度等级.

运行条件

本章包括以下几个部分:

■ 1-1页上的“工作条件” ■ “功耗”第1-14页 ■ “开关特性”第1-14页 ■ “I / O时序”1-37页 ■ 1-37页上的“词汇表”

当Cyclone IV器件在一个系统中实现,它们是根据一组定义的参数的分级.为了保持Cyclone IV器件中最高的性能和可靠性,您必须考虑本章所述的操作要求.