380-第十七讲6.4 译码器

第一学期广东中职一年级劳动版《数字逻辑电路(第四版)》第二章第四节+译码器与显示器+课件

S5

S4

S3

S2

S1

Y3 Y2 Y1

Y0

的状态

1

1

1

1

1

1

1

1

1

0

×

×

×

×

×

×

×

×

1

0

×

×

×

×

×

×

×

1

1

0

×

×

×

×

×

×

1

1

1

0

×

×

×

×

×

1

1

1

1

0

×

×

×

×

1

1

1

1

1

0

×

×

×

1

1

1

1

1

1

0

×

×

1

1

1

1

1

1

1

0

×

1

1

1

1

1

1

1

1

0

五、 实训总结

1. 完成测试记录, 并分析测量结果。 测量电路中为什么要 加集成电路 CD4069? 2. 在安装测试过程中遇到哪些问题, 是如何解决的? 3. 该电路可以移植应用于哪些场合?

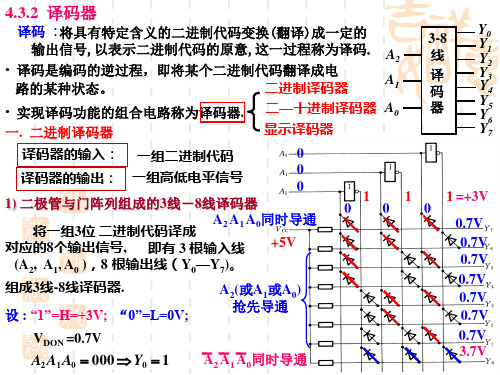

一、二进制译码器

二进制译码器——将二进制代码按其原意“翻译” 成相应的输出信号的电路。

1. 二位二进制译码器的真值表

S BA 1 ×× 0 00 0 01 0 10 0 11

Y3 Y2 Y1 Y0

1111 1110 1101 1011 0111

2线—4线译码器真值表

2. 逻辑表达式

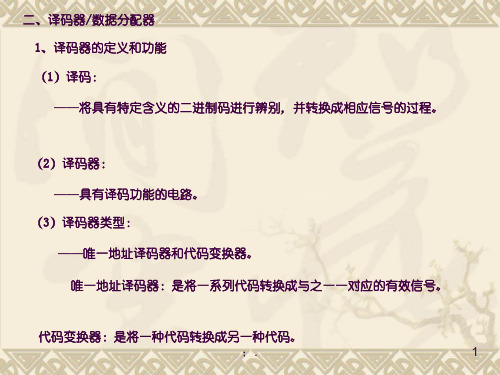

第四章-译码器

一般LED的工作电流选在5~10mA,但不允许超过最大值(通常为

50mA)。 LED可以直接由门电路驱动。

14

① 半导体发光二极管。

图(a)是输出为低电平时,LED发光,称为低电平驱动; 图(b)是输出为高电平时,LED发光,称为高电平驱动; 采用高电平驱动方式的TTL门最好选用OC门。

R为限流电阻

74HC138的功能表:

输

入

输

出

S1

S

' 2

S3'

0X

A2 A1 A0 Y7' Y6' Y5' Y4' Y3' Y2' Y1' Y0'

X XX 1 1 1 1 1 1 1 1

X 1 X XX 1 1 1 1 1 1 1 1

1 0 0 00 1 1 1 1 1 1 1 0

1 0 0 01 1 1 1 1 1 1 0 1

4

74LS138的逻辑功能 三个译码输入端(又称地址输入端)A2、

A1、A0,八个译码输出端 Y0~Y7,以及三个控制 端(又称使能端)S1、S2 、S3。

S1 、S2 ,S3 是译码器的控制输入端,当 S1 = 1、S2+ S3 = 0 (即 S1 = 1,S2 和S3 均为0)时,S 输出为高电平,译码器处于工作状态。否则,译 码器被禁止,所有的输出端被封锁在高电平。

1 0 0 10 1 1 1 1 1 0 1 1

1 0 0 11 1 1 1 1 0 1 1 1

1 0 1 00 1 1 1 0 1 1 1 1

1 0 1 01 1 1 0 1 1 1 1 1

1 0 1 10 1 0 1 1 1 1 1 1

译码器引脚图

74LS138译码器引脚图,逻辑图及功能表74LS138与74HC的引脚图用与非门组成的3线-8线译码器74LS1383线-8线译码器74LS138的功能表无论从逻辑图还是功能表我们都可以看到74LS138的八个输出引脚,任何时刻要么全为高电平1—芯片处于不工作状态,要么只有一个为低电平0,其余7个输出引脚全为高电平1。

如果出现两个输出引脚同时为0的情况,说明该芯片已经损坏。

当附加控制门的输出为高电平(S=1)时,可由逻辑图写出功能介绍:就是38译码器,是TTL系列的,也就是74系列。

有三个输入端A0,A1,A2,其中A2是高位,输出是八个低电平输出Y0 ~ Y7,工作电压一般的5V就可以了,举个例子,你A0,A1,A2依次输入000,输出就是Y0,输入依次是001,输出就是Y1。

74ls381引脚图集成算术/逻辑运算单元(ALU)能够完成一系列算术运算和逻辑运算。

在这里我们介绍一种常用的集成算术/逻辑运算单元74LS381,它是四位算术/逻辑运算单元,管脚图如图3.3所示,A和B是预定的输入状态,根据输入信号S2~S0选择八种不同的功能。

图3.3 74LS381集成算术/逻辑运算单元(a)符号图(b)引脚图下面我们可以通过74LS381的功能表了解其功能。

表3.3 74LS381功能表由表3.3可知,74LS381能够进行六种算术和逻辑运算,并有清零和预置功能。

所谓清零是将各数据输出端的状态全为0;预置是使数据输出端输出预定的状态,进行预置操作时,预定的状态从A和B端输入.74ls00,74ls08引脚图[日期:2009-01-01 ] [来源:net 作者:佚名] [字体:大中小] (投递新闻)74ls00 是常用的2输入四与非门集成电路,他的作用很简单顾名思义就是实现一个与非门。

Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS00引脚图>74LS00真值表:A=1 B=1 Y=0A=0 B=1 Y=1A=1 B=0 Y=1A=0 B=0 Y=1Vcc 4B 4A 4Y 3B 3A 3Y┌┴—┴—┴—┴—┴—┴—┴┐__ │14 13 12 11 10 9 8│Y = AB )│2输入四正与非门74LS00 │1 2 3 4 5 6 7│└┬—┬—┬—┬—┬—┬—┬┘1A 1B 1Y 2A 2B 2Y GND<74LS08引脚图>是常用的2输入四正与门电路74LS08真值表:a b y0 0 00 1 01 0 01 1 1基本RS触发器原理基本RS触发器原理1 基本RS触发器的工作原理基本RS触发器的电路如图1(a)所示。

数字电子电路第4章3

• 数码显示译码器

1. 半导体数码管

例: 共阴极接法

由七段发光二极管构成 a f f e d 低 电 平 时 a b c d e f g 发 光 共阳极接法 g

a b c d e f g 0 1 1 0 0 0 0 1 1 0 1 1 0 1

高 电 平 时 发 光

a b c d e f g

b

c +

共阴极接法

2. 七段译码显示器

二

十 进 制 代 码 Q0 4位 Q1 Q2 Q3

1 0 0 1

译 码 器

1 1 1 1 0 1 1

a

b

c d e

f

g

7个

(共阴极)

2、显示译码器

真值表

真值表仅适用于共阴极LED

24

a的卡诺图

A3 A2 A1 A0 00 01 11 10 00 1 0 1 1 01 0 1 1 0 11 × × × × 10 1 1 × ×

逻辑图

Y5 & Y4 &

3 线-8 线译码器

Y3 & Y2 & Y1 & Y0 &

1 A2

1 A1

1 A0

电路特点:与门组成的阵列

4

2、集成二进制译码器CT54LS138

1

VCC Y0

1

Y1

1

Y2

1

Y3

0

Y4

1

Y5

1

Y6

9

0 译码输出端 低电平有效

Y

16

15

14

13

1 2

1 1

10

Y0 A0

CT54LS138 1 2 3 4 5 6 7 8

练习4-四位BCD译码器

1.4 4位BCD译码器的设计4位BCD译码器可将BCD码转换成数字显示码,有4个输入引脚和7个输出引脚。

4位BCD译码器可分为共阴与共阳两种,下面以设计共阳4位BCD译码器为例来说明其设计方法。

1.实验原理共阳4位BCD译码器有4个输入端用来输入BCD码,7个输出端分别对应到七段显示4位BCD译码器应具备的脚位:输入端:D3、D2、D1、D0:输出端:S6、S5、S4、S3、S2、Sl、S0。

2.原理图输入由于原理图输入法较复杂,所以在这里不再详述。

3.文本输入(1)建立新文件:选取窗口菜单File—New,出现对话框,选Text Editor file选项,单击OK按钮,进入文本编辑画面。

(2)保存:选取窗口菜单File—save,出现对话框,键入文件名sevenBcD.vhd,单击OK按钮。

(3)指定项目名称,要求与文件名相同:选取窗口菜单File—Project—Name,键入文件名sevenBCD,单击OK按钮。

或也可以通过如下操作把当前设计项目设置成工程文件:选择菜单File|Project|Set Project to Current File命令,即将当前设计文件设置成Project。

选择此项后可以看到标题栏显示出所设文件的路径。

(4)选择实际编程器件型号:选取窗口菜单Assign—Device,出现对话框,选择ACEXlK 系列的EPlK30TCl44一3。

(5)输入VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY sevenBCD ISPORT(D:IN STD_LOGIC_VECTOR(3 DOWNTO 0);S :OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END sevenBCD;ARCHITECTURE a OF sevenBCD ISBEGINPROCESS (D)BEGINCASE D ISWHEN 0000=>S<=“0000001”;一0WHEN 0001l=>S<=“1001111”;一1WHEN 0010=>S<=“0010010”;一2WHEN 0011=>S<=“0000110”;—3WHEN 0100=>S<:“1001100”;一4WHEN 0101=>S<=“0100lOO”;—5WHEN 0110=>S<=“0100000”;—6WHEN 0111=>S<=“0001111”;一7WHEN 1000=>S<=“0000000”;一8WHEN 1001=>S<=“0000100”;一9WHEN OTHERS=>S<=“111111l”;END CASE;END PROCESS;END a;(6)保存并查错:选取窗口菜单File—Project—Save&Check,即可针对电路文件进行检查。

第十七讲应答器

2 .主要特性 电源: 10~36 VDC / 20W ; 获取报文间隔: 500 ms ; 驱动应答器数量: 4 个独立应答器; 传输距离: 3 . 5km ; 安全通信:采用 FBFS / 2 安全协议。

7 . 4 . 2 LEU 结构 1 .双机比较型地面电子单元( LEU ) 地面电子单元( LEU )由数据采集电路、 控制电路( CPU )、滤波放大电路组成。采用 双机校核,框图如图 7-12 所示。

我国设计天线的水平作用距离至少为 900mm (实

际大于 1m ) ,仍以上述列车时速 300 km / h 为例计

算,作用时间为 10. 8 ms ( T=900÷83 . 3=10. 8 ms ,电路启动时间忽略不计);

收码总量 M=10.8 ms×400 kbit /S =4320 bit ;

4 )报文的所有位反转后仍然可以被译码器识别。

5 )不需要在报文的开始传送起始帧(或结尾帧)。

6 )对于未知的将来的格式变化具有兼容性。

(3)欧洲标准应答器报文编码算法整个编码算法包 括两个部分:候选报文的生成、候选报文的测试。图 7-

10 是算法流程。

4. 解码原理 解码是编码的逆 过程,解码过程参见 图 7-11 。

用户数据包有 772 bit ,有 11 种用户数据包类型: 应答器链接、线路坡度、线路速度、等级转换、 CTCS 数 据、调车危险、轨道区段、临时限速、区段反向运行和大 号码道岔。帧结束标志有 8 bit 。 830 bit 的初始用户数据经过 FFFIS 信道编码算法 (欧洲标准应答器编码算法)处理后,变成 913 bit 的成 型数据,再加上算法中用到的一些参数(包括: 3 bit 控 制位、 12 bit 扰码位、 10 bit 附加成形位和 85 bit 校验 位),就形成了 1023 bit 的长报文(图 7-9 )。该报文 由应答器发送出去( FSK 调制模式),经过车载设备的接 收和译码,最终还原成初始用户数据。

数字逻辑课件——译码器

图3-3-10 4线-7线译码器/驱动 器7448逻辑符号

28

用7448驱动BS201A的基本接法如图3-3-11(a)所 示。当B3B2B1B0 输入0000~1111这16种不同信 号时,相应的显示字形如图3-3-11(b)所示。

图3-3-11 7448驱动BS201A

29

接线时务必防止将+5V直接与a~g段输入短接,否则 会烧毁PN结,用7448的输出Ya~Yg驱动BS201A的段输 入则没有这种危险,这是因为Ya~Yg为集电极开路输

19

常用的半导体数码管、液晶显示器及其BCD – 七段显示 译码器。 4. 半导体数码管 半导体数码管是分段式半导体显示器件,其基本结构为 PN结,一些特殊半导体材料作成的PN结具有这样的性质: 当外加正向偏压时,P区的多数载流子空穴流向N区,N区 的多数载流子电子流向P区,而少数载流子注入PN结与多 数载流子复合,在这个过程中会发出一定波长的光束。

e

c

d

27

配合半导体数码管BS201A工作的4线 — 7线译码 器/驱动器7448 (1)7448的逻辑功能

7448的逻辑符号如图3-3-10所示,其功能如表3-3-7,

它的基本输入信号是 四位二进制数(也可 以是8421BCD码)A3, A2,A1,A0,

基本输出端有7个: Ya,Yb,Yc,Yd,Ye, Yf,Yg。

出结构,并已有上拉电阻2kΩ。

在7448中,除了上述基本输入端和基本输出端 外,还有几个辅助输入、输出端:

(1)灯测试输入(LT ); (2)灭零输入(RBI ); (3)灭灯输入/灭零输出 (BI / RBO) : 这个端钮 比较特殊,它既可作输入用,也可作输出用。

30

4线-7线译码器/驱动器7448功能表

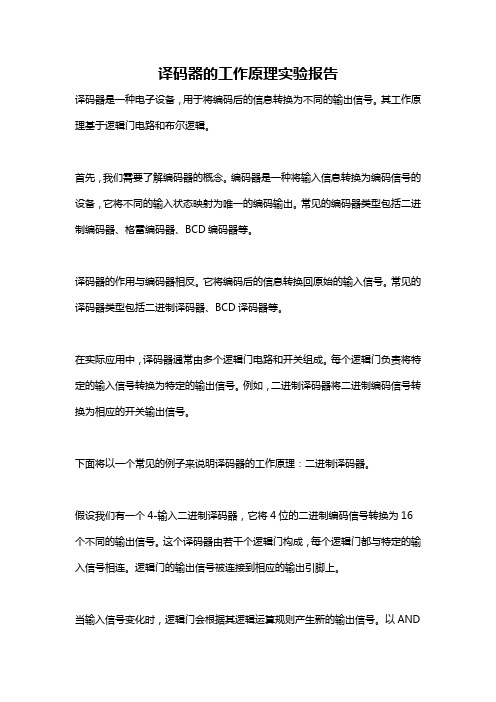

译码器的工作原理实验报告

译码器的工作原理实验报告译码器是一种电子设备,用于将编码后的信息转换为不同的输出信号。

其工作原理基于逻辑门电路和布尔逻辑。

首先,我们需要了解编码器的概念。

编码器是一种将输入信息转换为编码信号的设备,它将不同的输入状态映射为唯一的编码输出。

常见的编码器类型包括二进制编码器、格雷编码器、BCD编码器等。

译码器的作用与编码器相反。

它将编码后的信息转换回原始的输入信号。

常见的译码器类型包括二进制译码器、BCD译码器等。

在实际应用中,译码器通常由多个逻辑门电路和开关组成。

每个逻辑门负责将特定的输入信号转换为特定的输出信号。

例如,二进制译码器将二进制编码信号转换为相应的开关输出信号。

下面将以一个常见的例子来说明译码器的工作原理:二进制译码器。

假设我们有一个4-输入二进制译码器,它将4位的二进制编码信号转换为16个不同的输出信号。

这个译码器由若干个逻辑门构成,每个逻辑门都与特定的输入信号相连。

逻辑门的输出信号被连接到相应的输出引脚上。

当输入信号变化时,逻辑门会根据其逻辑运算规则产生新的输出信号。

以AND门为例,当所有输入信号都为1时,AND门的输出信号才为1;否则输出为0。

通过逻辑门的组合和配置,译码器可以实现将不同的输入信号转换为不同的输出信号。

通过将特定的输入信号连接到逻辑门上,我们可以控制输出信号。

例如,当输入信号为“0001”时,译码器的第一个输出引脚为1,其他引脚均为0。

当输入信号为“0010”时,译码器的第二个输出引脚为1,其他引脚均为0。

以此类推,译码器可以将不同的二进制编码信号转换为相应的输出信号。

总结起来,译码器的工作原理基于逻辑门电路和布尔逻辑。

它将编码后的信息转换回原始的输入信号。

通过逻辑门的组合和配置,译码器可以将不同的输入信号转换为不同的输出信号,从而实现对编码信息的解码。

数字电子技术04译码器ppt课件

74HC42

Y7 Y8

Y3 Y4

Y5

D

Y9

Y6

Y7 Y8

Y9

;.

15

(2)功能分析

功能表

输入为无效码时,输出均为高电平, 无有效码输出

BCD输入

输出

A3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9 00000111111111

00011011111111

00101101111111

EN

I2 I3

EN

2线—4线译码器组 成4线--16线译码器

;.

5

2、集成电路译码器 (1)二进制译码器 常用的有CMOS(74HC138)和TTL(74LS138),可用74X138表示。

①74X139介绍: 74X139是双2线-4线译码器

E

E

Y0

Y0

Y1

Y1

A0

A0

Y2

Y2

A1

A1

Y3

Y3

1/2 74X139逻辑符号

例4.4.3 四片74HC138和一片74HC139构成5线32线译码器。

解:

首先列出5线-32线译码器的真值表,如表4.4.7所示。

;.

10

B4B3从00~11 共4种组合

对B4B3的一种组合 B2B1B0从000~111

;.

11

例4.4.3的逻辑图

对输入的任一组5位 码,只有一个输出端 为有效低电平。

由于译码器是低电平有效输出,所 以将最小项变换(双非)为反函数 的形式,得到:

CBA

L= m0 ·m2 ·m6 ·m7

= Y0 ·Y2 ·Y6 ·Y7

Y0

以3-8译码器构建4-16译码器设计论文

毕业设计(论文)题目:以3-8译码器构建4-16译码器学院(系):专业班级:学生学号:学生姓名:指导教师:导师评语及成绩目录1 引言 ............1.1 电子密码锁的特点 (1)1.2 市场前景 (2)2系统设计方案的研究 (3)2.1 本系统设计的任务 (3)2.2设计方案的比较 (3)2.3 系统的控制特点与性能要求 (5)2.4 系统实现的原理 (6)2.5 系统实现功能分析 (7)3 系统的设计 (9)3.1 A T89S52单片机 (9)3.2单片机串行通信原理 (12)3.3红外通信原理...............................................................4.程序设计 (21)4.1模块介绍 (21)4.2 程序流程图 (21)5实验测试与结果分析 ..........................5.4结果 (27)参考文献 (29)附录 (30)致谢 (5)摘要为了设计一个4-16译码器,可将两个3-8译码器(74LS138)和一个六反向器(74LS04)级联而得。

设计时,可分为三部分:电平输入控制部分、译码器及脸部分、译码显示部分。

出于方便取材、节约简单的因素,电平控制部分采用开关控制高低电平,用发光二极管显示;译码器部分用两块74LS138(74HC138)级联;译码显示部分用16个编号(0---15)的发光二极管显示,对应编号的灯亮,则为响应便哈所对应的型号输出。

关键词:译码;级联;电平输入;译码显示AbstractIn order to design a line decoder 4-16, two3-8decodgn can be divided into three parts: Level input control of the decoder of the cascade, as some decoding. For er(74LS138) derived from Cascade. Desiconvenience of material savings simple, level control switch control of the use of high-low, with light-emitting diodes display; decoding part by two 74LS138(74HC138) Cascade; decoding of the show with16 numbers(0---15), light-emitting diodes,the lights corresponding code, the corresponding numbers for the corresponding output-signal.Keyword:decoding;Cascade;levelinput;decoding show译码器的功能简介译码是编码的逆过程,它的功能是将具有特定含义的二进制码进行辨别,并转换成控制信号,具有译码功能的逻辑电路称为译码器。

数字电路基础_D03-03A译码器

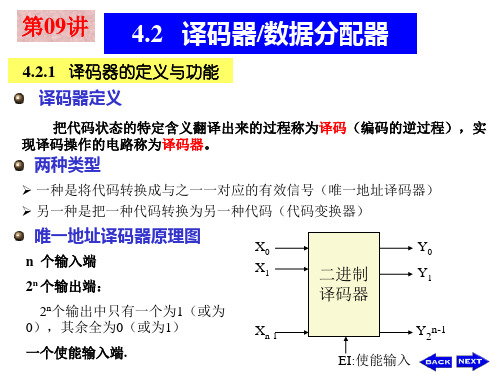

3.3.2译码器译码是编码的逆过程,它的逻辑功能是将每一组代码的含义“翻译”出来,即将每一组代码译为一个特定的输出信号表示它原来所代表的信息。

能完成译码功能的逻辑电路称为译码器。

1.二进制译码器二进制译码器的原理图如图3-3-6所示。

二进制译码器有n位二进制代码输入端,2n个译码输出端,还可以有一个或多个输入使能端。

当输入使能端为有效电平时,对应每一组的代码输入,仅有一个与该代码相对应的输出端为有效电平,其他2n -1个输出端均为无效电平。

图3-3-7所示为由与非门组成的3线 -- 8线译码器74LSl38的逻辑电路图和逻辑符号图。

图中A 2、A l 、A O 为3位二进制代码输入端(也称地址输入端),7Y ~ 0Y 万是8个译码输出端,S l 、2S 、3S 为3个输入使能端(或称控制端)。

S l 、2S 、3S 的作用是:只有当Sl =1,2S =3S =0时,才能使译码器处于译码工作状态。

否则,译码器禁止译码,7Y ~ 0Y 均为高电平。

故又称S l 、2S 、3S 为片选端,利用片选的作用可将多片连接起来进而扩展译码器的功能。

由图3-3-7(a)写出译码器输出逻辑函数的逻辑表达式:( P 106 )由上式列出74LSl38译码器的逻辑功能如表3-3-4所示。

由表3-3-4可知:当Sl =l ,2S =3S =0时,7Y ~ 0Y 二进制译码器的每一输出均是输入代码的最小项的非。

Y7~ Y0 每一输出均是输入代码的最小项 ( P106) Yo =moY1=mIY2=m2Y3=m3Y4=m4Y5=m5Y6=m 6Y7=m7一个n 变量二进制译码器的输出包含了n 变量的所有最小项。

[由3—3—2]试用两片74LSl38接成4线 一16线译码器。

解:由于74LSl38只有3个代码输入端A 2,A l ,Ao 。

而4线一16线译码器应有4个代码输入端,所以可以选用控制端作为第四个代码输入端A 3。

第十七讲译码器

第十七讲译码器第十七讲译码器6.4.1 二进制译码器一、二进制译码器二、译码器CT74LS1381.逻辑图。

2.真值表。

3.逻辑功能:4.全译码器:5.功能扩展6.4.2 二-十进制译码器一、二一十进制译码器二、4线一10线译码器CT74LS421.逻辑图。

2.真值表。

3.逻辑函数式4.功能变化6.4.4 用译码器实现组合逻辑函数一、实现原理:二、实例6.4 译码器课堂讨论:日常生活中什么地方用到了译码器?译码是编码的逆过程。

译码:将表示特定意义信息的二进制代码翻译出来。

译码器:实现译码功能的电路。

二进制译码原则:用n位二进制代码可以表示个信号则,对n位代码译码时,应由来确定译码信号位数N。

提问:8位电话号码能供多少用户使用?(电话号码为十进制)6.4.1 二进制译码器一、二进制译码器:将输入二进制代码译成相应输出信号的电路。

二、MSI译码器CT74LS138由于它有3个输入端、8个输出端,因此,又称3线一8线译码器。

1.逻辑图。

输入端:A2 、A1 、A0 ,为二进制代码;输出端:,低电平有效;使能端:STA(高电平有效)、(低电平有效)和(低电平有效),且。

2.真值表。

表6.4.1 3线一8译码器CT74LS138的真值表现代教学方法与手段:用DLCCAI演示MSI 器件74LS138的功能。

(5分钟)3.逻辑功能:(1)当STA=0,或+=1时,EN=0,译码器禁止译码,输出都为高电平1。

(2)当STA=1且+=1时,EN=1,译码器工作,输出低电平0有效。

这时,译码器输出由输入二进制代码决定输出逻辑函数式为4.全译码器:二进制译码器的输出将输入二进制代码的各种状态都译出来了。

因此,二进制译码器又称全译码器,它的输出提供了输入变量的全部最小项。

5.功能扩展:用两片CT74LS138组成4线一16线译码器。

(利用使能端)CT74LS138(1)为低位片,CT74LS138(2)为高位片。

并将高位片的STA和低位片的相连作A3,同时将低位片的和高位片、相连作使能端E,便组成了4线一16线译码器。

38译码器实现逻辑电路

Y ∑ mi

《数字电子技术基础》第五版

2. 举例

例:利用74HC138设计一个多输出的组合逻辑电路,输出 逻辑函数式为: Z1 AC ' A' BC AB 'C

D3=1

Zi' mi'

《数字电子技术基础》第五版

二、二—十进制译码器

• 将输入BCD码的10个代码译成10个高、低电平的输出信号 BCD码以外的伪码,输出均无低电平信号产生 • 例:74HC42

Y m (i 0 ~ 9)

' i ' i

《数字电子技术基础》第五版

三、用译码器设计组合逻辑电路

A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0

0 0 0 0 1 1 1

0 0 1 1 0 0 1

0 1 0 1 0 1 0

0 0 0 0 0 0 0

0 0 0 0 0 0 1

0 0 0 0 0 1 0

0 0 0 0 1 0 0

0 0 0 1 0 0 0

0 0 1 0 0 0 0

0 1 0 0 0 0 0

1 1 1 1 1 0 1 1 1 1

1 1 1 1 0 1 1 1 1 1

1 1 1 0 1 1 1 1 1 1

1 1 0 1 1 1 1 1 1 1

《数字电子技术基础》第五版

• 利用附加控制端进行扩展 例: 用74HC138(3线—8线译码器)

4线—16线译码器

《数字电子技术基础》第五版

哈夫曼(huffman)编译码器课程设计

兰州商学院陇桥学院工学系课程设计报告设计题目:哈夫曼(huffman)编译码器系别:专业 (方向):年级、班:学生姓名:学生学号:指导教师:年月日目录哈夫曼(huffman )编译码器 (3)一、编译码器开发的背景 (3)二、系统的分析与设计 (3)(一)系统功能要求 (3)(二)系统模块结构设计 (4)三、系统的设计与实现 (6)(一)main() (6)(二)运算 (7)1. 权值运算quanzhi() (7)2. 印二叉树函数huffmantree( ) (7)3.编译码运算huffmancode() (9)4. 输出运算 shuchu() (9)四、系统测试 (10)(一)测试主函数 (10)(二)测试印二叉树函数 (10)(三)测试译码运算函数 (11)五、总结 (12)六、附件(代码、部分图表) (13)哈夫曼(huffman )编译码器一、编译码器开发的背景利用哈夫曼编码进行通信可以大大提高信道利用率,缩短信息传输时间,降低传输成本。

但是,这要求在发送端通过一个编码系统对待传数据预先编码,在接收端将传来的数据进行译码(复原)。

对于双工信道(即可以双向传输信息的信道),每端都需要一个完整的编/译码系统。

二、系统的分析与设计(一)系统功能要求一个完整的系统应具有以下功能:1)I:初始化(Initialization)。

从终端读入字符集大小n,以及n个字符和n个权值,建立哈夫曼树,并将它存于文件hfmTree中。

2)E:编码(Encoding)。

利用以建好的哈夫曼树(如不在内存,则从文件hfmTree中读入),对文件ToBeTran中的正文进行编码,然后将结果存入文件CodeFile中。

3)D:译码(Decoding)。

利用已建好的哈夫曼树将文件CodeFile中的代码进行译码,结果存入文件TextFile中。

4)P:印代码文件(Print)。

将文件CodeFile以紧凑格式显示在终端上,每行50个代码。

二进制译码器

与

与非

同或

非

A& B

F

A& B

F

A B

1

FA 1

F

A ≥1 B

F

或

A B

≥1

F

A B

=1

F

或非

异或

第十五页,编辑于星期五:九点 十七分。

画逻辑图

根据函数表达式画出相关的门电路,并标明变量与函数

(1 ) F A B ; (2)F A B ; (3)F A B ; (4)F A • B ; (5)F A • B ; (6)F A B (7 )F A • B C

&

F0

&

F1

&

F2

&

F3

第十七页,编辑于星期五:九点 十七分。

画逻辑图

交流:在独立完成、协作完成逻辑图时,你 最愉快的感受是什么?与大家分享。

第十八页,编辑于星期五:九点 十七分。

课堂小结

这节課我们学习了二进制译码器。 我们的学习方法有自学法、合作学习法、他

人求助法,听老师讲解法等,你都参与了吗? 有什么收获? 我们学习二进制译码器的工作原理、二变量 译码器的设计过程。你有哪些知识技能收获, 与大家分享一下。

第九页,编辑于星期五:九点 十七分。

学习材料一

第十页,编辑于星期五:九点 十七分。

学习材料二

第十一页,编辑于星期五:九点 十七分。

总结

根据阅读完成填空

由真值表写逻辑表达式的方法比较

以输出端 0/1为标准

第一种 0

每行输入变 量运算形式

对0和1 的处理

各表达式间的 运算方法

相加

见0取原,见1取反

第三页,编辑于星期五:九点 十七分。

第09讲42译码器、数据分配器.

b=c=f=g=1

a=d=e=0

共阴极

c=d=e=f=g=1

a=b=0时

(2)7448集成 显示译码器 功能表 (仅适用于共阴极LED)

观察a段与DCBA的关系,用卡诺图化简方法,写出其逻辑表达式

a的卡诺图

DC BA 00 01 11 10 00 1 0 1 1 01 0 1 1 0 11 × × × × 10 1 1 × ×

kHz

计数脉冲

计数器

译码器

驱动器

显示器

数码显示方式

字型重叠式、分段式、点阵式三种

数码显示类型(按发光物质分类)

发光二极管显示器、荧光数字显示器、液晶数字显示器、气体放电显示器

(1)七段数字显示器(外加小数点)

a b a f e g d b c c d a b c d e f g h e f g h (b) 共阴极 (a) 外形图 a b c d e f g h (c) 共阳极 +VCC

0 1 0 1 0 1 0 1

1 1 1 1 1

D 0 1 1

1 1 1 1 1 1 D 1 1

逻辑表达式

如当CBA 010时 Y2 ( G1 G2 A G2 B ) C B A ( 1 G2 A 0 ) 0 1 0 G2 A

本节小结

把代码状态的特定含义翻译出来的过程称为译 码,实现译码操作的电路称为译码器。实际上译 码器就是把一种代码转换为另一种代码的电路。 二进制译码器能产生输入变量的全部最小项, 而任一组合逻辑函数总能表示成最小项之和的形 式,所以,由二进制译码器加上或门即可实现任 何组合逻辑函数。此外,用4线-16线译码器还可 实现BCD码到十进制码的变换。

0 0 0 0 0 0 0 0

十编码及译码器工作原理

第十课:编码及译码器工作原理这节课主要为下节课的存储器存储原理打基础,学过数字电路对编码译码了解的朋友可以跳过这节课。

把所使用的每一种二进制代码状态都赋于特定的含义,表示一个特定的信号或对象,叫编码。

如用四位二进制数的0000~1001 这十种状太,分别表示0~9 这十个十进制数码,称为8421 编码。

反过来把代码的特定含义翻译出来,称为译码。

计算机在处理各种文字符号或数码时,必须把这些信息进行二进制编码,在编码时所使用的第一种二进制代码状态都赋予了特定的含义,即表示一个确定的信号或者对象,实现这种功能的电路叫编码器,如用于键盘的BCD码,ASCII码编码器等。

单片机外围电路用译码器较多,所以在这节课我们主要与大家一起来学习下译码器的工作原理(购买了本站产品的朋友,在我们配套的多媒体教学光盘中有相关的教学内容,建议大家观看),把代码的含义‘翻译'成相应的输出信号,以表示其原意。

其功能恰恰与编码器相反。

译码器可以将输入代码的状态翻译成相应的输出信号,以高、低电平的形式在各自的输出端口送出,以表示其意愿。

译码器有多个输入端和多个输出端。

假如输入的端个数为,每个输出端只能有两个状态,则输出端个数最多有2n个。

常用译码器输入、输出端头数来称呼译码器,如3线-8线译码器,4线-10线译码器等。

我们经常用到的74138就是一个三线-八线译码器,朋友们可以到我们网站的《芯片资料》频道下载74138的中文资料。

编码、译码的概念我们了解下,下面我们就来重点来讲一下三-八译码器的工作原理,这在我们51单片机的接口电路中也是经常用到的。

74138的工作原理如下图所示:于| | AO Al A2SI S2S3 kitp:/Aw. isMCU.^om中山单片机学习岡从上图可看出,74138有三个输入端:AO、A1、A2和八个输出端Q0~Q7。

当输入端AO、A1、A2的编码为000时,译码器输出为Q0=0,而Q1~Q7=1。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

6 . 4 . 1 二进制译码器

一、二进制译码器

二、译码器CT74LS138

1.逻辑图

2.真值表

3.逻辑功能

4.全译码器

5.功能扩展

6 . 4 . 2 二-十进制译码器

一、二一十进制译码器

二、4线一10线译码器CT74LS42

1.逻辑图

课 时 授

2.真值表 3.逻辑函数式 4.功能变化

课

6 . 4 . 4 用译码器实现组合逻辑函数

提

一、实现原理

纲

二、实例

课 程 内 容

课 程内 容

动画

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

动画

课 程 内 容

课 程 内 容

动画

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

课 程 内 容

课 时 授 课 计 划

教学方法设计: 1. 由于编码与译码是逆过程,所以回顾已经讲过的 编码器,引入译码器。 2. 讲解中注意基本概念的建立。 3. 强调MSI器件的使用,培养查手册的能力。

课堂讨论: 日常生活中什么地方用到了译码器?

现代教学方法与手段:

课 时

用DLCCAI演示MSI 器件74LS138的功能。

第十七讲

课时授课计划

提

纲

数 电

课 程 内 容

精

品

课

程

课题:6.4 译码器

目的与要求: 1. 掌握译码原理、译码器的设计方法。 2. 掌握MSI 器件74LS138的功能、使用、功能扩展、 逻辑符号。 3. 掌握查手册了解MSI器件功能的方法。 4. 掌握用译码器实现组合逻辑函数的方法。

重点与难点: MSI 器件74LS138的功能和实现组合逻辑函数的方法。

授

课

计

划

复习(提问): 1.译码原则? 2. 8位电话号码能供多少用户使用?(电话号码 为十进制) 3.若要对8421BCD码进行译码,输出信号应有 多少个? 4.逻辑函数的标准最小项之和式? 5.译码器CT74LS138的输出逻辑函数式?

课 时 授 课 计 划

译码 、译码器 、译码原则

6 . 4 译码器