Y=~版图设计

Y=~(A+B(C+D))版图设计

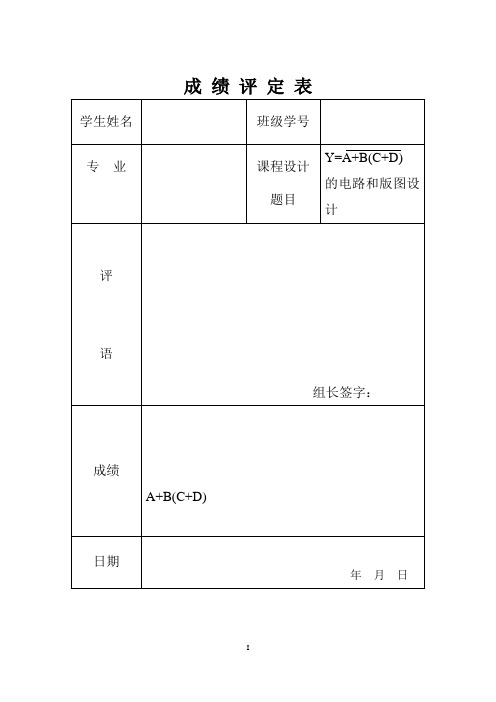

成绩评定表课程设计任务书目录1绪论 (1)1.1设计背景 (1)1.2 设计目标 (1)2 Y=A+B(C+D)的电路和版图设计 (3)2.1电路原理图 (3)2.2 Y=A+B(C+D) 的电路仿真观察波形 (4)2.3 Y=A+B(C+D) 的版图绘制 (5)2.4 Y=A+B(C+D) 的版图仿真观察波形 (5)2.5 LVS检查匹配 (6)总结 (8)参考文献 (9)附录一电路原理图网表 (10)附录二版图图网表 (10)1绪论1.1设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证[2]。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

电路版图设计一般流程

电路版图设计一般流程1. 确定需求和规格在开始设计电路板之前,首先需要明确产品的具体需求和规格。

这包括产品的功能要求、性能要求、工作环境等。

只有清楚明确了需求和规格,才能够确定电路板设计的方向和目标。

2. 选择器件根据产品的需求和规格,选择适合的器件和元器件。

这包括集成电路、传感器、连接器等各种器件。

在选择器件时,需要考虑器件的性能、价格、供货周期等因素,确保选择的器件能够满足产品的需求。

3. 电路原理图设计根据选定的器件,绘制电路原理图。

电路原理图是电路板设计的基础,它反映了整个电路的连接关系和工作原理。

在设计电路原理图时,需要考虑电路的稳定性、可靠性和性能,确保电路能够正常工作。

4. PCB布局设计根据电路原理图,设计PCB(Printed Circuit Board)的布局。

PCB布局设计是电路板设计的关键环节,它直接影响到电路板的性能和可靠性。

在进行PCB布局设计时,需要考虑到器件的布局、信号的传输路径、电源的分布等因素,确保布局的合理性和稳定性。

5. 电路仿真和调试完成PCB布局设计后,需要进行电路仿真和调试。

通过电路仿真软件模拟电路的工作过程,检验电路的稳定性和性能。

根据仿真结果进行调整和优化,直到满足产品的需求为止。

6. PCB制造和组装完成电路板设计后,需要将PCB制造出来,并进行元器件的组装。

选择信誉良好的PCB制造厂商和组装厂商,确保PCB的质量和可靠性。

在组装过程中,需要注意器件的焊接、布线和测试,确保电路板能够正常工作。

7. 电路测试和验证完成PCB制造和组装后,需要进行电路的测试和验证。

通过各种测试方法对电路板进行验证,确保电路的稳定性和性能。

如果测试通过,就可以将电路板用于产品中;如果测试不通过,需要进行调整和优化,直到满足产品的要求为止。

总的来说,电路板设计是一项复杂而严谨的工作,需要经过多个环节的精心设计和调试。

只有经过严密的设计流程,才能确保最终产品的质量和性能。

版图设计课件 PPT

一、双极集成电路工艺的基本流程

实现选择性掺杂的三道基本工序

(3)掺杂:在半导体基片的一定区域掺入一定浓度的杂质 元素,形成不同类型的半导体层,来制作各种器件。掺 杂工艺主要有两种:扩散和离子注入。

扩散:在热运动的作用下,物质的微粒都有一种从高浓 度的地方向低浓度的地方运动的趋势。在IC生产中,扩 散的同时进行氧化。

结论:对采用PN结隔离的双极IC基本工艺,与制作NPN 晶体管的基本工艺相比,只需增加外延工艺,当然工艺步 骤要增加不少。

一、双极集成电路工艺的基本流程

PN结隔离双极IC工艺基本流程

衬底材料(P型硅)- 埋层氧化-埋层光刻 -埋层掺杂(Sb)外延 (N型硅)隔离氧化-隔离光刻 -隔离掺杂(B)- 基区氧化-基区光刻 -基区掺杂(B)和发射区氧化-

一、双极集成电路工艺的基本流程

工艺类型简介

按照制造器件的结构不同可以分为: 双极型:由电子和空穴这两种极性的载流子作为在有源

区中运载电流的工具。 MOS型:PMOS工艺、NMOS工艺、CMOS工艺 BiCMOS集成电路:双极与MOS混合集成电路

按照MOS的栅电极的不同可以分为: 铝栅工艺、硅栅工艺(CMOS制造中的主流工艺)

(2) 光刻2:场氧光刻,又称为有源区光刻。将以后作为有源区区域的 氧(3化) 氧层化和氮层化生硅长层。保在留没,有其氮余化区硅域层的保氧护化的层区和氮化硅全部去除。 域(即场区)生长一层较厚的氧化层。图中 表面没有氧化层的区域即为有源区。

三、CMOS集成电路工艺流程

3. 生长栅氧化层和生成多晶硅栅电极 确定了有源区以后,就可以制作MOS晶体管。首先按下述步骤生长栅 氧化层和制作栅电极。 (1) 生长栅氧化层。去除掉有源区上的氮化硅层及薄氧化层以后,生长 一层作为栅氧化层的高质量薄氧化层。 (2) 在栅氧化层上再淀积一层作为栅电极材料的多晶硅。 (3) 光刻3:光刻多晶硅,只保留作栅电极以及起互连作用的多晶硅。 光刻后的剖面图如图所示。

版图设计及举例教学课件

原则: 对称性

对称性可以帮助创建平衡和 稳定感,使版图更加美观和 整齐。

原则: 平衡性

平衡性是指在版图中平衡各 个元素的重量和空间分布。

原则: 重复性

通过重复使用某些元素,可以增加版图的统一 性和可读性。

原则: 简洁性

简洁性是指通过精练的信息和简单的设计元素 来传达清晰的信息。

PPT是一个简便实用的工具,可以于制作简单而有效的版图设计。

制作一个版图设计的教学PPT

通过详细讲解PPT基本操作、选择场景和主题、制定版图设计要素和原则、 界面元素的选择与搭配以及制作过程中的技巧和注意事项,让观众学会制作 精美的版图设计教学PPT。

结束语

总结版图设计的重要性和作用,告诉观众掌握版图设计技能的必要性。 感谢观众的收听和观看!

版图设计的要素和原则

要素: 布局

布局是指将内容元素有机地组合在一起,创造 出视觉上的平衡和整体感。

要素: 色彩

色彩可以增加版图的视觉吸引力,并传达特定 的情感和氛围。

要素: 字体

字体的选择和排版可以影响版图的可读性和视 觉效果。

要素: 图片与图标

图片和图标可以增加版图的信息量和吸引力。

原则: 单一性

实例:版图设计要素和原则

通过选取一个场景,分析其版图设计要素和原则,并呈现一些成功的版图设计案例。

版图设计的实现方法

Photoshop、Illustrator、Sketch等工具

可以使用专业设计软件进行版图设计和编辑。

在线版图设计工具

有一些在线工具可以让您快速创建精美的版图设计。

使用PPT制作版图

版图设计及举例教学课件 PPT

版图设计基础

(1)检查内容丰富、准确

(2)具有两种文件运行方式

(3)运行结果浏览方便。通过Calibre RVE和版图编辑器分 析DRC的结果并进行查错,准确快捷,一目了然

• Diva DRC工具

是Cadence公司开发,嵌入版图设计工具 之中。可以在版图设计工具Virtuoso中,通 过单击图形界面中的Verify菜单,并点击其 中的DRC子菜单,就可以进行DRC检查

- 验证工具 - 设计规则验证工具 - LVS工具 - 提取工具 - 节电高亮工具

用整套Tanner软件设计集成电路的流程

L-edit版图编辑器简介

• 安装在window下,简单易学,价格便宜 • 采用以单元为基础的层次化设计 • 嵌入了DRC工具、版图提取工具、截面观

察器、节点高亮

Oasis格式文件比GDSII紧凑,而且能够更有效 的表达平面数据。可以处理64位数据

Tanner research 公司 Tanner EDA工具

• 前端设计工具 -电路设计工具(S-Edit) -仿真验证工具(T-Spice) -波形分析工具(W-Edit) • 物理版图设计工具

L-Edit版图编辑器 - L-Edit交互式DRC验证工具 - 电路驱动版图设计工具 - 标准单元布局布线工具

• CIF格式 用文本命令来表示掩膜分层和版图图形,通过对

基本图形的描述、图形定义描述、附加图样调用 功能,可以实现对版图的层次性描述。采用字符 格式,可读性较强 EDIF格式 是电路的一种二进制描述,带有电路的单元符号 (symbol)信息,也是纯文本,主要用于电路数 据交换。EDIF文件可读性强 Oasis格式

ERC检查的主要错误有如下几种:

1.2基本门电路设计-版图绘制

集成电路设计实习Integrated Circuits Design LabsI t t d Ci it D i L b单元实验一(第二次课)基本门电路设计--版图设计2006-2007 Institute of Microelectronics Peking University实验目的及时间安排z内容一:z掌握基本门电路的版图设计z熟悉Cadence版图设计、版图验证工具的使用z内容二:z完成2与非门的设计,包括原理图输入、电路仿真、版图设计、版图验证Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page21. 版图图层z本课程中使用CSMC双硅三铝混合信号工艺,主要的设计层包括z TB:tub,n阱,作为pmos器件衬底z TO:Thin Oxide,有源区,作为mos的源漏区Thin Oxidez GT:gate,多晶硅1,作为mos栅极z SP:P+注入区z SN:N+注入区z W1:接触孔,金属1到多晶硅和有源区的接触孔z A1:铝1,第一层金属z W2:通孔1,金属1和金属2的接触孔z A2:铝2,第二层金属z W3:通孔2,金属2和金属3的接触孔z CP:bond pad,pad开孔z IM:第二层多晶硅电阻阻挡层z PC:poly Cap,用作多晶硅电容上极板和多晶硅电阻的第二层多晶硅l Cz PT:p tub,p阱,作为nmos器件衬底z详细的工艺信息请参考设计规则(在CSMC05MS/docs目录下)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page32. 由电路图产生初始版图z VirtuosoXL为cadence的连接关系驱动定制版图设计工具z启动Virtuoso XLz第一步:打开inv的schematic viewz第二步:Schematic窗口:Tools->Design Synthesis->Layout XLz Create Newz OKz OK,弹出Virtuoso XL窗口Vi t XLz在Virtuoso XL窗口中,Design->GenFrom Source Layout,弹出yGeneration Options对话框(下页)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page4z Layout Generation部分z选中I/O Pins,Instances,Transistor Chaining,TransistorTransistor Chaining TransistorFoldingz I/O Pins部分z DefaultsD f lz Layer/Master选择A1层z选中Createz Applyz Pin Label Shapez点击Pin Label Options,在弹出的对话框中选中Layer Name后面的SameLayer Name SameAs Pinz点击OK后出现下页图,按照前面的设计要求进行版图设计Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page5Inv的版图设计z在此基础上添加电源线vdd,地线gnd(可参考下页快捷键)z按照电路图用相应的层把mos管的各端连线画出来z把vdd和N阱相连(用CSMC05MS库中的ntap),把gnd和衬底相连(用tCSMC05MS库中的ptap )z按照标准单元的画法,单元有统一的高度(这里是24um),统一的vdd和gnd走线宽度(2um)和位置(vdd走线在单元的最上端,gnd在最下端)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page6Virtuoso Layout Editor常用操作z Instance(添加元件,快捷键i)g(画矩形,快捷键),yg(画多边形,快捷键z Rectangle r PolygonP),Path(画长连线,快捷键p)pyz Copy(c),Move(m),Stretch(s)z Merge(把多个相互重叠的图形合并成一块,M)Create Ruler Clear All Rulersz Create Ruler(添加标尺,快捷键k),Clear All Rulers(K)z Descend(X),Return(B)z Zoom in by 2(^z),Zoom out by 2(Z),Fit(f)z Option->Display(e)中可以设置一些参数z在命令过程中可以利用F3键打开该命令相关的选项,帮助我们调整命令参数(很有帮助!)Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page73. 版图的验证DRCz在Layout窗口中,Verify->DRCz在Rules File一项中,填入divaDRC.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OKz在CIW中可以看到DRC的结果,按说明改掉图中的error,直到Total errors found为0Institute of Microelectronics, Peking University集成电路设计实习-单元实验一Page84. 版图的器件提取和LVS检查z在做LVS之前,要把版图中的管子信息和pin的信息提取出来,这就是Extractz在Layout窗口中,Verify->Extractz Rules File一项中,填入在Rules FiledivaEXT.rul,若该文件不在启动目录下,还应写上路径z取消Rules Library选项Rules Libraryz OK在中可以看到是否成z CIW Extract功,一般情况下Total errorsfound都为0z执行的结果是cell inv产生了一个extracted viewInstitute of Microelectronics, Peking University集成电路设计实习-单元实验一Page9LVSz在Layout窗口中,Verify->LVSz Library和Cell中分别填入库名字design03和单元名字inv,View中对应于schematic的填入schematic,对应于extracted的填入extracted(这些信息也可以通过Browse或者BSel by Cursor得到)在一项中,填入z Rules FiledivaLVS.rul,若该文件不在启动目录下,还应写上路径z点击Run,运行几秒后会出现“Analysis Job Succeeded”的提示z点击Output,观看结果。

版图设计基础new

硅芯片上的电子世界--电容

• 电容:一对电极中间夹一层电介质的三明治结构; • 硅芯片上的薄膜电容:

几十微米

上电极:金属或多晶硅 氧化硅电介质 下电极:金属或多晶硅 硅片

• 集成电路中的集成电容

• 金属-金属(多层金属工艺,MIM) • 金属-多晶硅 • 多晶硅-多晶硅(双层多晶硅工艺,PIP)

方块电阻: R=ρL/S=ρL/dW=(ρ/d)L/W R = ρ/d R=R L/W 方块电阻与半导体的掺杂水平和掺杂区的结深有关 对于集成电路来说,方块电阻是基本单位,量纲是Ω/ 只要知道材料的方块电阻,就可以根据所需要的电阻值计算 出电阻的方块数,即电阻条的长度和宽度比 栅极多晶:2-3 Ω/ ;金属:20-100m Ω/ 多晶:20-30 Ω/ ;扩散区:2-200 Ω/

接触孔层和通孔层

• 接触孔包括有源区接触孔(Active Contact)和多晶硅接 触孔(poly contact) • 有源区接触孔用来连接第一层金属和N+或P+区域,在版 图设计中有源区接触孔的形状通常是正方形。 • 应该尽可能多地打接触孔,这是因为接触孔是由金属形成, 存在一定的阻值,假设每个接触孔的阻值是R,多个接触 孔相当于多个并联的电阻

版图设计(物理层设计)

• 版图设计的目标:实现电路正确物理连接,将设计好的 电路映射到硅片上进行生产。芯片面积最小,性能优化 (连线总延迟最小) 集成电路设计的最终目标

• 版图设计的重要性:

电路功能和性能的物理实现;

布局、布线方案决定着芯片正常工作、面积、速度; • 经验很重要。 版图设计包括: 基本元器件版图设计; 布局和布线; 版图检验与分析。

绘图层

• • • • • • • • • • N阱层(N Well) 有源区层(Active) 多晶硅栅层(Poly) P选择层(P Select) N选择层(N Select) 接触孔层(Contact) 通孔层(Via) 金属层(Metal) 文字标注层(Text) 焊盘层(Pad)

版图设计实验报告

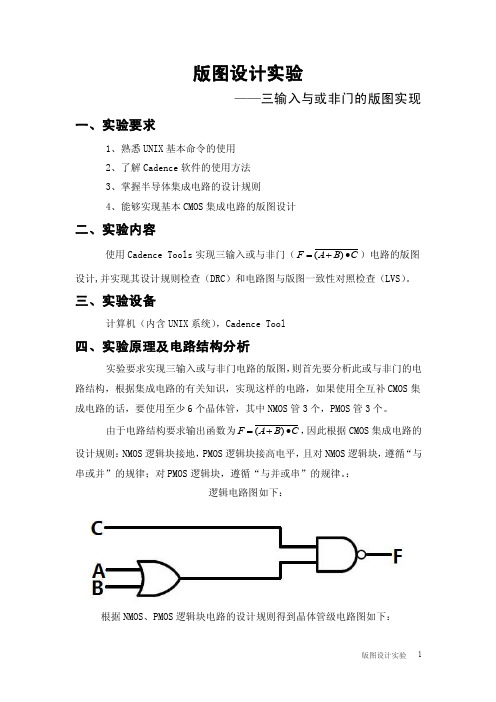

版图设计实验——三输入与或非门的版图实现一、实验要求1、熟悉UNIX基本命令的使用2、了解Cadence软件的使用方法3、掌握半导体集成电路的设计规则4、能够实现基本CMOS集成电路的版图设计二、实验内容使用Cadence Tools实现三输入或与非门(C=)()电路的版图+F∙AB设计,并实现其设计规则检查(DRC)和电路图与版图一致性对照检查(LVS)。

三、实验设备计算机(内含UNIX系统),Cadence Tool四、实验原理及电路结构分析实验要求实现三输入或与非门电路的版图,则首先要分析此或与非门的电路结构,根据集成电路的有关知识,实现这样的电路,如果使用全互补CMOS集成电路的话,要使用至少6个晶体管,其中NMOS管3个,PMOS管3个。

由于电路结构要求输出函数为C+(,因此根据CMOS集成电路的=)F∙AB设计规则:NMOS逻辑块接地,PMOS逻辑块接高电平,且对NMOS逻辑块,遵循“与串或并”的规律;对PMOS逻辑块,遵循“与并或串”的规律。

:逻辑电路图如下:根据NMOS、PMOS逻辑块电路的设计规则得到晶体管级电路图如下:该电路图实现的逻辑功能 A B C管子工作状态 输出C B A F ∙+=)( 0 0 0 P 管导通;N 管截止 10 0 1 t1、t2导通,t3截止;t4导通,t5、t6截止 10 1 0 t1、t2截止,t3导通;t4、t5、t6截止 10 1 1 t1、t2、t3截止;t4、t5导通,t6截止 01 0 0 t1、t2截止,t3导通;t4、t5、t6截止 11 0 1 t1、t2、t3截止;t4、t6导通,t5截止 01 1 0 t1、t2截止,t3导通;t4、t5、t6截止 11 1 1 P 管截止;N 管道通0 在初步分析了电路的结构和逻辑功能之后,接下来就是要具体的进行该电路的版图设计工作了,首先要明确几个概念。

1、版图设计规则。

主要有两种,一种是微米(um-microm )设计规则,它是一种以微米为单位的直接描述版图的最小允许尺寸,是一种绝对单位的设计规则;另一种是λ为单位的设计规则,该规则是一种相对单位,若某工艺的特征尺寸为A ,则m A μλ2=,规定最小线宽为λ2,其它最小允许尺寸均表示为λ的整数倍。

版图设计

版图设计:

版图设计是创建工程制图(网表)的精确的物理描述 过程,即定义各工艺层图形的形状、尺寸以及不同工 艺层的相对位置的过程。

1. 版图设计入门 版图设计的内容

设计内容:

布局:安排各个晶体管、基本单元、复杂单元 在芯片上的位置

布线:设计走线,实现管间、门间、单元间的 互连

λ由IC制造厂提 供,与具体的工 艺类型有关,m、 n、l、h为比例因 子,与图形类形 有关

2. 设计规则 宽度规则(width rule)(1)

宽度指封闭几何图形的内边之间的距离

最小宽度 最大宽度

2. 设计规则 间距规则(Separation rule)(1)

间距指各几何图形外边界之间的距离

同一工艺层的间距 (spacing)

注意,随着电路复杂度的增加,例如设计中使用到的晶 体管数量的增加,可能的版图数量也会增加。

2. 设计规则 最小宽度与最小间距(1)

2. 设计规则 最小宽度与最小间距(2)

2. 设计规则

距离周边最小距离

2. 设计规则

最短露头

2. 设计规则

通孔与接触孔

2. 设计规则

层间互连约束

Metal2不能直接 接有源区、多晶

进行DRC(设计规则检查)之后,就在完成的版 图上进行电路参数提取来决定实际的晶体管尺寸, 更重要的是确定每个节点的寄生电容。提取步骤 完成后,提取工具会自动生成一个详细的SPICE 输入文件。

现在就可以使用提取的网表通过SPICE仿真确定 电路的实际性能。

2. 设计规则

如果仿真出的电路性能(如瞬态响应时间 或功耗)与期望值不相符,就必须对版图 进行修改并重复上面的过程。版图修改主 要是对晶体管尺寸中的宽长比进行修改。 这是因为管子的宽长比决定器件的跨导和 寄生源极和漏极电容。

版图设计知识点

版图设计知识点版图设计是指在平面设计中对于页面布局、元素排列以及配色等方面的设计。

在版图设计中,有许多重要的知识点需要注意和掌握。

本文将就版图设计的知识点进行详细论述。

一、页面尺寸与比例在版图设计中,页面尺寸与比例是首要考虑的因素之一。

根据设计需求和输出媒介的不同,选择适合的页面尺寸是非常重要的。

常见的页面尺寸包括A4、A5、网页尺寸等。

除了尺寸外,比例也需要考虑。

常见的比例有黄金比例、对称比例等,选择合适的比例可以使得版面更加平衡美观。

二、栏目设置与结构栏目设置是版图设计中的重要环节。

通过合理设置栏目,可以使得信息的展示更加清晰、有序。

在进行栏目设置时,需要考虑到内容的重要性、相似性以及层次关系。

常用的栏目设置有单栏、双栏、多栏等,根据设计需求选择合适的栏目布局。

三、文字排版文字排版是版图设计中不可忽略的一环。

合理的文字排版可以提升版面的可读性和美观度。

在进行文字排版时,需要注意字体的选择与搭配、字号的调整以及字距的设置等。

同时,还需要注意段落的分隔与缩进、文字的对齐方式等,确保文字排版整齐、清晰。

四、色彩运用色彩是版图设计中的重要元素之一,能够给人带来不同的情绪和感受。

在进行色彩运用时,需要考虑到色彩的搭配、主次关系以及色彩的饱和度和明度等因素。

同时,还需要注意色彩的运用要与设计主题相符合,避免色彩过于花哨或不协调而影响整体设计效果。

五、图片与图形元素图片与图形元素在版图设计中起到了画龙点睛的作用。

通过巧妙的图片与图形元素的运用,可以提升版面的视觉效果和吸引力。

在选择图片与图形元素时,需要注意其与设计主题的契合度,避免过多或不相关的图片与图形元素的使用。

同时,还需要注意图片的清晰度以及图形元素的简洁性和美观性。

六、空白与留白空白与留白是版图设计中的重要设计元素之一。

合理的运用空白与留白可以使版面更加清爽、简洁。

空白的选择需要考虑到信息的紧凑性与层次关系,留白的运用则需要考虑到版面的平衡性与美感。

版图设计流程及设计方法

版图设计流程及设计方法下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!版图设计流程。

1. 项目需求分析。

收集客户要求,确定版图设计目标和范围。

版图设计流程及设计方法

版图设计流程及设计方法Designing a layout is a complex and iterative process that involves various steps to ensure a successful outcome. 版图设计是一个复杂而迭代的过程,涉及多个步骤以确保成功的结果。

First and foremost, the design process begins with understanding the requirements and objectives of the project. 首先,设计过程始于理解项目的要求和目标。

This involves conducting thorough research on the target audience, the brand, and the message the layout is intended to convey. 这涉及对目标受众、品牌以及版面打算传达的信息进行深入的研究。

In addition, it is crucial to gather all the necessary resources, such as images, text, and other visual elements, before starting the layout design. 此外,在开始版图设计之前,收集所有必要的资源,如图像、文本和其他视觉元素,是至关重要的。

Once the initial groundwork is laid out, the next step is to brainstorm and sketch out different layout ideas that align with the project'sobjectives. 一旦初步工作完成,下一步是集思广益,勾画出符合项目目标的不同版面构想。

Y=~(A+B(C+D))版图设计

成绩评定表学生姓名班级学号专业课程设计题目Y=A+B(C+D) 的电路和版图设计评语组长签字:成绩A+B(C+D)日期年月日课程设计任务书学院信息科学与工程学院专业学生姓名班级学号课程设计题目Y=A+B(C+D) 的电路和版图设计实践教学要求与任务:1、学习和掌握tanner软件的设计流程2、熟悉Y=A+B(C+D)工作原理,根据电路原理图,绘制版图,设计仿真网表文件,利用仿真工具完成电路分析流程。

3、完成全部设计内容,撰写设计报告。

工作计划与进度安排:第一周周一:教师布置课设任务,学生收集资料,做方案设计。

周二:熟悉软件操作方法。

周三~四:画电路图周五:电路仿真。

第二周周一~二:画版图。

周三:版图仿真。

周四:验证。

周五:写报告书,验收。

指导教师:年月日专业负责人:年月日学院教学副院长:年月日目录1绪论 (1)1.1设计背景 (1)1.2 设计目标 (1)2 Y=A+B(C+D)的电路和版图设计 (3)2.1电路原理图 (3)2.2 Y=A+B(C+D) 的电路仿真观察波形 (4)2.3 Y=A+B(C+D) 的版图绘制 (5)2.4 Y=A+B(C+D) 的版图仿真观察波形 (5)2.5 LVS检查匹配 (6)总结 (8)参考文献 (9)附录一电路原理图网表 (10)附录二版图图网表 (10)1绪论1.1设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证[2]。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

版图设计规则操作说明

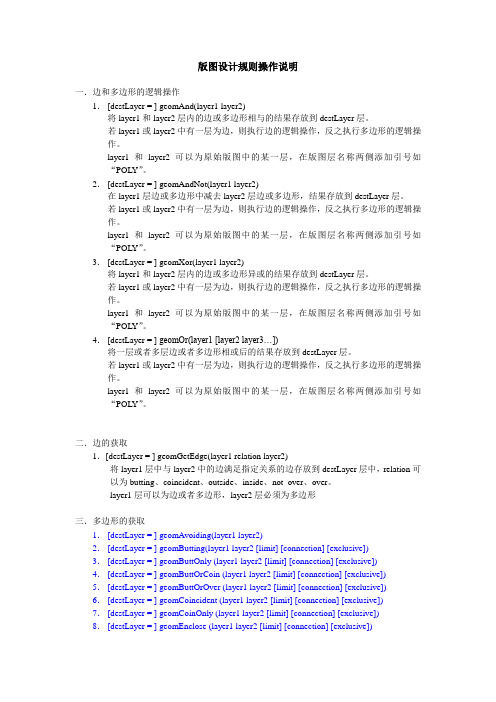

版图设计规则操作说明一.边和多边形的逻辑操作1.[destLayer = ] geomAnd(layer1 layer2)将layer1和layer2层内的边或多边形相与的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

2.[destLayer = ] geomAndNot(layer1 layer2)在layer1层边或多边形中减去layer2层边或多边形,结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

3.[destLayer = ] geomXor(layer1 layer2)将layer1和layer2层内的边或多边形异或的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

4.[destLayer = ] geomOr(layer1 [layer2 layer3…])将一层或者多层边或者多边形相或后的结果存放到destLayer层。

若layer1或layer2中有一层为边,则执行边的逻辑操作,反之执行多边形的逻辑操作。

layer1和layer2可以为原始版图中的某一层,在版图层名称两侧添加引号如“POL Y”。

二.边的获取1.[destLayer = ] geomGetEdge(layer1 relation layer2)将layer1层中与layer2中的边满足指定关系的边存放到destLayer层中,relation可以为butting、coincident、outside、inside、not_over、over。

版图设计规则(最新版).ppt

设计规则(design rule)

•TSMC_0.35μm CMOS工艺中各版图层的线条最小宽 度

设计规则(design rule)

2、最小间距(minSep) 间距指各几何图形外边界之间的距离。

TSMC_0.35μm CMOS工艺版图 各层图形之间的最小间距

设计规则

3、最小交叠(minOverlap) 交叠有两种形式: a)一几何图形内边界到另一图形的内边界长度(overlap),

DRC规则文件

saveDerived 语句输出坏的接触孔图形到错 误层中。

举例: saveDerived( geomAndNot( W1 geomOr( TO GT ) ) "Contact not inside Active or Poly" ) saveDerived( geomAndNot( W1 A1 ) "Contacts not covered by Metal" ) drc( W1 width < 4.0 "Contact width < 4.0" ) drc( W1 sep < 2.0 "Contact to Contact spacing < 2.0" ) drc( TO W1 enc < 1.5 "Contact inside Active < 1.5" )

;接触孔

A1 = geomOr( "A1" )

;铝线

drc(GT TO (enc<2) "Poly Overhang out of Active into Field<2.0")

DRC规则文件

geomAnd()把括号内层次“与”之后再 赋给前面的新层次。

版图设计重要知识点

版图设计重要知识点版图设计是指在平面传媒中利用文字、图片、色彩等元素进行排版,使之达到美观、易读和传达信息的目的。

良好的版图设计能够吸引读者的眼球,提升阅读体验,下面将介绍版图设计中的几个重要知识点。

一、页面布局页面布局是版图设计的基础,它决定了各个元素的位置、大小、顺序和比例。

常见的页面布局有对称布局、平衡布局和协同布局等。

对称布局指的是页面元素在水平或竖直方向上的对称排列,能够给人以稳定、整齐的感觉;平衡布局指的是页面元素在整个页面上的均衡分布,使得视觉上的重量平衡;协同布局则是指页面元素之间相互协调,形成整体效果。

二、字体选择在版图设计中,字体的选择很重要,它直接影响到文字的易读性和美观性。

在选择字体时,应考虑到字体的风格与内容的一致性,同时还要考虑到字体的大小和行间距,以确保文字清晰可读。

常见的字体有宋体、黑体、楷体等,它们在不同的设计场景中有不同的应用。

三、色彩运用色彩是版图设计中的重要元素之一,它能够给人以视觉冲击力和情感表达。

在运用色彩时,需要考虑到色彩的搭配和对比,避免过于花哨或造成视觉疲劳。

一般情况下,可采用类似的色系进行配色,同时保持页面整体的统一性和和谐感。

四、图片选择图片在版图设计中有很大的作用,能够直观地传达信息和吸引读者。

在选择图片时,应根据内容和风格的需要进行挑选,同时要保证图片的清晰度和分辨率。

此外,在版图设计中,还可以通过调整图片的大小、位置和透明度等方式,与文字和其他元素进行融合,形成更好的视觉效果。

五、白空间利用白空间是指页面中没有被文字、图片和其他元素填充的空白区域。

合理利用白空间可以提升版图设计的美感和阅读体验,使页面显得更加整洁和舒适。

白空间不仅能够使得内容更加突出,还能够提高文字的可读性。

总之,版图设计是一门独特的艺术,需要设计师兼顾美观性和功能性,灵活运用各种元素来达到理想的效果。

通过合理的页面布局、字体选择、色彩运用、图片选择和白空间利用等知识点的运用,可以制作出吸引人眼球、易读且传递信息的版图设计作品。

版图设计流程

版图设计流程版图设计是一项非常重要的工作,它直接关系到产品或者项目的整体形象和用户体验。

一个好的版图设计可以提升产品的吸引力和竞争力,因此,版图设计流程的规范性和有效性显得尤为重要。

在进行版图设计时,我们需要遵循一定的流程,以确保设计的高质量和高效率。

第一步,需求分析。

在进行版图设计之前,我们需要对产品或项目的需求进行充分的分析。

这包括对目标用户群体的需求分析,对产品功能和特性的分析,以及对市场和竞争对手的分析。

只有充分了解需求,我们才能进行有针对性的版图设计,满足用户的实际需求。

第二步,概念构思。

在完成需求分析后,我们需要进行概念构思。

这一阶段是版图设计的灵感迸发阶段,我们可以进行大胆的构思和创意的发挥。

在这个阶段,可以进行头脑风暴,绘制草图,或者进行一些简单的设计尝试,以寻找最合适的设计方向。

第三步,结构规划。

在完成概念构思后,我们需要进行版图设计的结构规划。

这包括对版图的整体结构进行规划,确定版面布局、内容分区、色彩搭配等。

在这一阶段,我们需要考虑版图的视觉引导和信息传达,确保用户在浏览版图时能够快速获取所需信息。

第四步,细节设计。

在完成结构规划后,我们需要进行版图设计的细节设计。

这包括对版面的各个细节进行精细化设计,包括文字排版、图标设计、配色搭配等。

在这一阶段,我们需要注重细节,确保版图的每一个元素都能够完美地融入整体设计中。

第五步,评审修改。

在完成版图设计后,我们需要进行评审和修改。

这一阶段需要邀请相关的人员对版图进行评审,包括设计师、产品经理、市场人员等。

根据评审意见,我们需要对版图进行适当的修改和调整,以确保设计符合实际需求和市场需求。

第六步,输出交付。

最后,我们需要将完成的版图设计进行输出和交付。

这包括将设计稿转化为可用的格式,如图片、PDF等,并交付给相关的部门或人员使用。

在交付时,我们需要确保设计的质量和准确性,以满足后续的使用需求。

总结。

版图设计流程是一个复杂而严谨的过程,需要设计师和相关人员的共同努力和配合。

版图设计需要的知识点

版图设计需要的知识点在进行版图设计时,我们需要掌握一些基本的知识点,以确保设计出整洁美观、功能合理的版图。

以下是一些常用的版图设计知识点。

一、版图设计的基本原则1. 对齐原则:确保版面上的元素在水平和垂直方向上保持对齐,使版面看起来整齐有序。

2. 平衡原则:在版面上合理分布内容,避免让某些部分显得过于空旷或过于拥挤。

3. 留白原则:适当运用留白,使版面更加清晰和易读,也能凸显出重要信息。

4. 重点突出原则:通过字体、颜色、大小等手段,突出版面中的重点内容,引导读者关注。

二、版图设计的基本要素1. 标题:标题应该简洁明了,具有吸引力,能够准确传达信息。

2. 副标题:副标题可以补充主标题的内容,增加版面的丰富度。

3. 正文:正文的排版要求清晰易读,段落之间要有适当的间距,字体大小要一致,文字要有层次感。

4. 图片和插图:图片和插图的使用可以使版面更加生动有趣,但要注意与正文的配合,避免过于拥挤。

5. 表格和图表:表格和图表的使用可以清晰地展示数据,但要保持简洁明了,避免信息过多造成混乱。

6. 色彩和字体:选择合适的色彩和字体可以增加版面的美观度,但要注意搭配的和谐性和统一性。

三、版图设计的流程1. 确定需求:根据设计的目的,明确版图所要传达的信息和目标群体。

2. 规划布局:根据版图的内容和要求,合理规划版面,确定各部分的位置和大小比例。

3. 设计元素:根据布局确定的位置和大小比例,安排标题、副标题、正文、图片等元素的分布。

4. 调整细节:对版面的各个部分进行微调,使之更符合设计要求和审美标准。

5. 审核修改:对设计的版图进行审核,并根据需要进行适当修改,以确保版面的质量和可读性。

6. 最终呈现:将设计好的版图输出为相应的格式,准备用于印刷或网络发布。

四、版图设计的软件工具1. Adobe InDesign:广泛应用于版面设计,具有丰富的功能和灵活的排版方式。

2. Adobe Photoshop:用于图像处理和编辑,可用于调整图片大小、裁剪、色彩处理等。

微电子笔试(笔试和面试题)

第一部分:基础篇(该部分共有试题8题,为必答题,每位应聘者按自己对问题的理解去回答,尽可能多回答你所知道的内容。

若不清楚就写不清楚)。

1、我们公司的产品是集成电路,请描述一下你对集成电路的认识,列举一些与集成电路相关的内容(如讲清楚模拟、数字、双极型、CMOS、MCU、RISC、CISC、DSP、ASIC、FPGA等的概念)。

数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统。

模拟信号,是指幅度随时间连续变化的信号。

例如,人对着话筒讲话,话筒输出的音频电信号就是模拟信号,收音机、收录机、音响设备及电视机中接收、放大的音频信号、电视信号,也是模拟信号。

数字信号,是指在时间上和幅度上离散取值的信号,例如,电报电码信号,按一下电键,产生一个电信号,而产生的电信号是不连续的。

这种不连续的电信号,一般叫做电脉冲或脉冲信号,计算机中运行的信号是脉冲信号,但这些脉冲信号均代表着确切的数字,因而又叫做数字信号。

在电子技术中,通常又把模拟信号以外的非连续变化的信号,统称为数字信号。

FPGA是英文Field-Programmable Gate Array的缩写,即现场可编程门阵列,它是在PAL、GAL、EPLD等可编程器件的基础上进一步发展的产物。

它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

2、你认为你从事研发工作有哪些特点?3、基尔霍夫定理的内容是什么?基尔霍夫电流定律:流入一个节点的电流总和等于流出节点的电流总和。

基尔霍夫电压定律:环路电压的总和为零。

欧姆定律: 电阻两端的电压等于电阻阻值和流过电阻的电流的乘积。

4、描述你对集成电路设计流程的认识。

5、描述你对集成电路工艺的认识。

把电路所需要的晶体管、二极管、电阻器和电容器等元件用一定工艺方式制作在一小块硅片、玻璃或陶瓷衬底上,再用适当的工艺进行互连,然后封装在一个管壳内,使整个电路的体积大大缩小,引出线和焊接点的数目也大为减少。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

成绩评定表课程设计任务书目录1绪论................................................. 错误!未定义书签。

设计背景.................................................. 错误!未定义书签。

设计目标................................................. 错误!未定义书签。

2 Y=A+B(C+D)的电路和版图设计........................... 错误!未定义书签。

电路原理图................................................ 错误!未定义书签。

Y=A+B(C+D) 的电路仿真观察波形............................ 错误!未定义书签。

Y=A+B(C+D) 的版图绘制.................................... 错误!未定义书签。

Y=A+B(C+D) 的版图仿真观察波形............................ 错误!未定义书签。

LVS检查匹配............................................. 错误!未定义书签。

总结..................................................... 错误!未定义书签。

参考文献.................................................. 错误!未定义书签。

附录一电路原理图网表..................................... 错误!未定义书签。

附录二版图图网表......................................... 错误!未定义书签。

1绪论设计背景随着集成电路技术的日益进步,使得计算机辅助设计(CAD)技术已成为电路设计师不可缺少的有力工具[1]。

国内外电子线路CAD软件的相继推出与版本更新,使CAD技术的应用渗透到电子线路与系统设计的各个领域,如芯片版图的绘制、电路的绘图、模拟电路仿真、逻辑电路仿真、优化设计、印刷电路板的布线等。

CAD技术的发展使得电子线路设计的速度、质量和精度得以保证[2]。

在众多的CAD工具软件中,Spice程序是精度最高、最受欢迎的软件工具,tanner是用来IC版图绘制软件,许多EDA系统软件的电路模拟部分是应用Spice程序来完成的,而tanner软件是一款学习阶段应用的版图绘制软件,对于初学者是一个上手快,操作简单的EDA软件。

Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows 平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

设计目标1.用tanner软件中的原理图编辑器S-Edit编辑Y=A+B(C+D)电路原理图。

2.用tanner软件中的W-Edit对Y=A+B(C+D)的电路进行仿真,并观察波形。

3.用tanner软件中的L-Edit绘制Y=A+B(C+D)的版图,并进行DRC验证。

4.用W-Edit对Y=A+B(C+D)的版图电路进行仿真并观察波形。

5.用tanner软件中的layout-Edit对Y=A+B(C+D)进行LVS检验观察原理图版图的匹配程度。

2.Y=A+B(C+D)的电路和版图设计电路原理图Y=A+B(C+D)的电路原理如图所示。

当输入的信号ABCD满足0000、0001,或0010等,即满足上拉网络导通的条件时,输出Y为高电平。

当输入信号为1010或1000等满足下拉网络导通的条件时,输出Y为低电平。

实现Y=A+B(C+D) 的逻辑运算。

通过真值表可以得出当输入信号为0000、0001、0010、0011、0100时输出Y为高电平,其余的输入信号可以的到低电平。

图 Y=A+B(C+D)的电路原理图Y=A+B(C+D)的电路仿真观察波形给Y=A+B(C+D) 的输入加激励,高电平为Vdd=5V,低电平为Gnd,将输入信号设置成不同的周期,ABCD信号的周期分别为800ns、400ns、200ns和100ns。

此时能将输入为0000—1111所产生的结果都输出。

并添加输入输出延迟时间,进行仿真,并输出波形;波形图如图所示。

当输入为0000、0001、0010、0011、0100时输出为高电平。

其余的输出都为低电平。

由于竞争冒险,所以将上升延时下降延时时间降低。

再将B信号的输入提前10ns输入来去掉竞争冒险产生的毛刺。

图 Y=A+B(C+D)电路输入输出波形图Y=A+B(C+D)的版图绘制用L-Edit版图绘制软件对Y=A+B(C+D)电路进行版图绘制,同时进行DRC验证,查看输出结果,检查无错误;版图和输出结果如图所示。

在对节点进行标注时注意输入法的设置要使用美式键盘,否则会在生成网表时产生错误。

图 Y=A+B(C+D)与或门电路版图及DRC验证结果Y=A+B(C+D)的版图仿真观察波形与Y=A+B(C+D)电路原理图仿真相同,添加激励、电源和地,同时观察输入输出波形;波形如图所示。

Y=A+B(C+D)电路的版图仿真波形与原理图的仿真输出波形基本一致,并且符合输入输出的逻辑关系,电路的设计正确无误。

同样为了去掉竞争冒险我将B输入信号提前10ns输入。

图 Y=A+B(C+B)版图输入输出波形图LVS检查匹配用layout-Edit对Y=A+B(C+D) 电路进行LVS检查验证,首先添加输入输出文件即电路原理图和版图的输出网表分别为.sp文件和.spc文件,选择要查看的输出,在进行匹配时要现将电路原理图和版图的输入激励进行屏蔽否则会在匹配过程中产生警告。

观察输出结果检电路原理图与版图的匹配程度,输出结果如图所示。

图 Y=A+B(C+D)电路的LVS检查匹配图从以上可以看出完全匹配。

这里为了匹配时无警告已经将输入激励和电源屏蔽掉总结经过多次的修改和调试,本次设计经过验证,可以达到所需的功能,达到了设计的要求。

以下是本次试验的心得:在实验的开始阶段,对所设计的电路进行了波形仿真,发现波形仿真的结果有竞争冒险的毛刺,为了去除竞争冒险我将上升下降延时变小、将时钟周期变大,同时将B信号提前10ns输入。

在进行版图的网表生成时注意网表上标注的节点要使用美式键盘输入否则网表上会出现错误的节点信息。

在进行原理图和版图对比匹配时要注意屏蔽掉输入的电源和激励。

我觉得我们学习不能完全以来波形仿真,否则,出现任何一点小的误差就会导致整个文件系统的编译出错。

总之,模拟集成电路版图设计作为前沿学科,对于我们专业的学生来说,学习对我们知识面以及运用知识的能力的提高有很大的帮助。

相信自己学习的脚步不会停止!感谢老师孜孜不倦的教诲。

相信在学习过程中自己思维能力、学习能力、思考方式的提高,定会在以后的学习过程中给我带来很大的帮助。

参考文献[1]廖裕平,陆瑞强.Tanner pro集成电路设计与布局实战指导.全华科技图书股份有限公司印行,2006.[2]张志刚等著.模拟电路版图的艺术.科学出版社,2009.附录一电路原理图网表:* SPICE netlist written by S-Edit Win32* Written on Jul 2, 2013 at 23:31:28* Waveform probing commands*.probe.include D:\tanner\TSpice70\models\.options probefilename="D:\tanner\LIE\"+ probesdbfile="D:\tanner\LIE\"+ probetopmodule="Module0"*.param l=*Vdd Vdd Gnd 5*.tran/op 10n 800n method=bdf*.print tran v(A) v(B) v(C) v(D) v(Y)*va A GND PULSE (0 5 400n 400n 800n)*vb B GND PULSE (0 5 210n 200n 400n)*vc C GND PULSE (0 5 90n 100n 200n)*vd D GND PULSE (0 5 50n 50n 100n)* Main circuit: Module0M1 Y B N3 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M2 Gnd D N3 Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M3 N3 C Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M4 Y A Gnd Gnd NMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M5 N1 A Vdd Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M6 N2 C N1 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u M7 Y B N1 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24uM8 Y D N2 Vdd PMOS L=2u W=22u AD=66p PD=24u AS=66p PS=24u* End of main circuit: Module0附录二版图网表:* Circuit Extracted by Tanner Research's L-Edit Version / Extract Version ;* TDB File: D:\tanner\LIE\* Cell: Cell0 Version* Extract Definition File: ..\LEdit90\Samples\SPR\example1\* Extract Date and Time: 07/05/2013 - 09:38.include D:\tanner\TSpice70\models\* Warning: Layers with Unassigned AREA Capacitance.* <P Diff Resistor ID>* <Poly Resistor ID>* <N Diff Resistor ID>* <Poly2 Resistor ID>* <P Base Resistor ID>* <N Well Resistor ID>* Warning: Layers with Unassigned FRINGE Capacitance.* <P Diff Resistor ID>* <Poly1-Poly2 Capacitor ID>* <Poly Resistor ID>* <N Diff Resistor ID>* <Poly2 Resistor ID>* <P Base Resistor ID>* <N Well Resistor ID>* <Pad Comment>* Warning: Layers with Zero Resistance.* <NMOS Capacitor ID>* <Poly1-Poly2 Capacitor ID>* <PMOS Capacitor ID>* <Pad Comment>* NODE NAME ALIASES* 1 = C (38,-35)* 2 = D ,-35)* 3 = B (22,* 4 = A (14,* 5 = GND ,* 6 = Vdd ,* 7 = Y ,*.include D:\tanner\TSpice70\models\*.options probefilename="D:\tanner\LIE\"*+ probesdbfile="D:\tanner\LIE\"*+ probetopmodule="Module0"*.param l=*Vdd Vdd Gnd 5*.tran/op 10n 800n method=bdf*.print tran v(A) v(B) v(C) v(D) v(Y)*va A GND PULSE (0 5 400n 400n 800n)*vb B GND PULSE (0 5 210n 200n 400n)*vc C GND PULSE (0 5 90n 100n 200n)*vd D GND PULSE (0 5 50n 50n 100n)M1 9 C 10 Vdd PMOS L=2u W=6u* M1 DRAIN GATE SOURCE BULK (38 16 40 22) M2 10 D Y Vdd PMOS L=2u W=6u* M2 DRAIN GATE SOURCE BULK (30 16 32 22) M3 Y B 9 Vdd PMOS L=2u W=6u* M3 DRAIN GATE SOURCE BULK (22 16 24 22) M4 9 A Vdd Vdd PMOS L=2u W=6u* M4 DRAIN GATE SOURCE BULK (14 16 16 22) M5 8 C GND GND NMOS L=2u W=6u* M5 DRAIN GATE SOURCE BULK (38 -11 40 -5) M6 GND D 8 GND NMOS L=2u W=6u* M6 DRAIN GATE SOURCE BULK (30 -11 32 -5)M7 8 B Y GND NMOS L=2u W=6u* M7 DRAIN GATE SOURCE BULK (22 -11 24 -5)M8 Y A GND GND NMOS L=2u W=6u* M8 DRAIN GATE SOURCE BULK (14 -11 16 -5)* Total Nodes: 10* Total Elements: 8* Total Number of Shorted Elements not written to the SPICE file: 0 * Extract Elapsed Time: 0 seconds.END。