verilog经典材料

Verilog的135个经典设计实例

Verilog的135个经典设计实例1、立即数放大器:立即数放大器是一种用于将输入电平放大到更高电平的电路,它可以实现任意输入到输出的映射,并且可以在Verilog中使用。

立即数放大器的Verilog实现如下:module immedamp(in, out);input in;output out;reg [3:0] immed;assign out = immed[3];begincase (in)4'b0000: immed = 4'b1000;4'b0001: immed = 4'b1001;4'b0010: immed = 4'b1010;4'b0011: immed = 4'b1011;4'b0100: immed = 4'b1100;4'b0101: immed = 4'b1101;4'b0110: immed = 4'b1110;4'b0111: immed = 4'b1111;4'b1000: immed = 4'b1000;4'b1001: immed = 4'b1001;4'b1010: immed = 4'b1010;4'b1011: immed = 4'b1011;4'b1100: immed = 4'b1100;4'b1101: immed = 4'b1101;4'b1110: immed = 4'b1110;4'b1111: immed = 4'b1111;endcaseendendmodule2、多路复用器:多路复用器是一种用于将多个输入选择转换为单个输出的电路,它可以实现由多种方式选择的输出,并可以使用Verilog实现。

verilog第二章简单的Verilog模块

and #1 u2(sela, a, nsl);

and #1 u3(selb, b, sl);

or #1 u4(out, sela, selb);

endmodule

/*一个名为adder的三位加法器的例子。*/

module adder ( count,sum,a,b,cin ); //模块定义开始

// 选择逻辑组合

2.2.2 模块的概念

一个设计是由一个个模块构成的。一个模块的设计如下:

1 模块内容是嵌套在module和endmodule两个语句之间。每个

模块实现特定的功能,模块是可以进行层次嵌套的。正因为

如此,才可以将大型的数字电路设计分割成不同的小模块来

实现特定的功能,最后通过顶层模块调用子模块来实现整体

endmodule

数据流语句

▪这个例子描述了一个三位的加法器。从例子中可以看出整个

Verilog HDL程序是嵌套在module和endmodule声明语句里

的,只出现了一个assign语句。

例SR触发器模块

S

Q

//SR 触发器

module SR_FF (Q, Q_n,S,R);

R

Q_n

output Q, Q_n; //端口声明

input S,R;

nand n1(Q, S,Q_n);

nand n2(Q_n,R,Q);

nand为verilog

中的与非门门级

原语部件

endmodule

模块中的5个部分并没全部出现,只出现在

低层次模块实例化

D触发器模块

//D 触发器

module D_FF (d, clk,clr,q,qb);

verilog hdl语言100例详解

verilog hdl语言100例详解Verilog HDL语言是一种硬件描述语言,用于描述数字电路和系统的行为和结构。

它是硬件设计工程师在数字电路设计中的重要工具。

本文将介绍100个例子,详细解释Verilog HDL语言的应用。

1. 基本门电路:Verilog HDL可以用于描述基本门电路,如与门、或门、非门等。

例如,下面是一个描述与门电路的Verilog HDL代码:```verilogmodule and_gate(input a, input b, output y);assign y = a & b;endmodule```2. 多路选择器:Verilog HDL也可以用于描述多路选择器。

例如,下面是一个描述2:1多路选择器的Verilog HDL代码:```verilogmodule mux_2to1(input a, input b, input sel, output y);assign y = sel ? b : a;endmodule```3. 寄存器:Verilog HDL可以用于描述寄存器。

例如,下面是一个描述8位寄存器的Verilog HDL代码:```verilogmodule register_8bit(input [7:0] d, input clk, input reset, output reg [7:0] q);always @(posedge clk or posedge reset)if (reset)q <= 0;elseq <= d;endmodule```4. 计数器:Verilog HDL可以用于描述计数器。

例如,下面是一个描述8位计数器的Verilog HDL代码:```verilogmodule counter_8bit(input clk, input reset, output reg [7:0] count);always @(posedge clk or posedge reset)if (reset)count <= 0;elsecount <= count + 1;endmodule```5. 加法器:Verilog HDL可以用于描述加法器。

Verilog语言基础知识

在Verilog HDL中,用parameter来定义常量,即用parameter来定义一个标志符,代表一个常量,称为符号常量。其定义格式如下:

parameter 参数名1=表达式,参数名2=表达式,参数名3=表达式……;

例如:

parameter sel=8,code=8'ha3;

//分别定义参数sel为常数8(十进制),参数code为常数a3(十六进制)

Verilog HDL中共有19种数据类型。数据类型是用来表示数字电路中的数据存储和传送单元的。在此介绍4个最基本的数据类型:integer型、parameter型、reg型和wire型。

Verilog HDL中也有常量和变量之分,他们分属以上这些类型。

6.2.1 常量

在程序运行过程中,其值不能被改变的量称为常量。

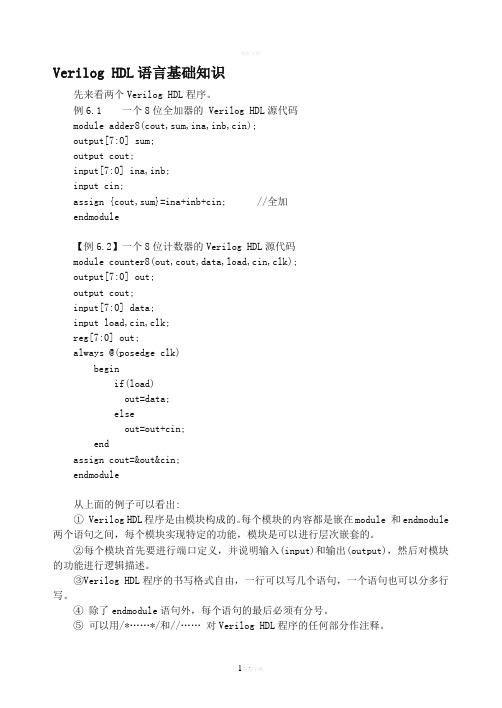

assign {cout,sum}=ina+inb+cin;//全加

endmodule

【例6.2】一个8位计数器的Verilog HDL源代码

module counter8(out,cout,data,load,cin,clk);

output[7:0]out;

output cout;

input[7:0] data;

6.1.2 Verilog HDL模块的结构

Verilog HDL的基本设计单元是"模块(block)"。一个模块是由两部分组成的,一部分描述接口;另一部分描述逻辑功能,即定义输入是如何影响输出的。下面举例说明,图6.1示出了一个"与-或-非"门电路。

图6.1"与-或-非"电路

该电路表示的逻辑函数可以写为:

6.2.2 变量

用verilog-a写的一些电路模块的例子

用verilog-a写的一些电路模块的例子以下是几个用Verilog-A 语言编写的电路模块的例子:1. 增益电路模块````include "disciplines.vams"module gain_circuit(va, vb, vout, g);input va, vb;output vout;parameter real g=10.0;analog beginvout = g * (va - vb);endendmodule```这个例子展示了一个简单的增益电路模块,其中输入是两个电压va、vb,输出是vout,增益系数为g。

在模块中使用了Verilog-A 的`analog begin` 语句来定义电路的行为。

2. RC 低通滤波器模块````include "disciplines.vams"module rc_lowpass_filter(vin, vout, r, c);input vin;output vout;parameter real r=1.0, c=1e-6;real v1;analog begini(vin, v1) <+ (vin - v1)/(r*c);vout <+ v1;endendmodule```这个例子展示了一个基于RC 电路的低通滤波器模块,其中输入为vin,输出为vout,RC 电路的参数由r 和c 决定。

在模块中使用了Verilog-A 的`i()` 语句来定义电路的行为。

3. 三角波发生器模块````include "disciplines.vams"module triangle_wave_generator(vout, freq, amp, dc);output vout;parameter real freq=1e3, amp=1.0, dc=0.0;real t;analog begint = $abstime;vout <+ amp * (2 * (t * freq - floor(t * freq + 0.5)) - 1) + dc;endendmodule```这个例子展示了一个简单的三角波发生器模块,其中输出为vout,频率由freq 决定,幅值由amp 决定,直流分量由dc 决定。

verilog 组合逻辑例子

verilog 组合逻辑例子Verilog组合逻辑例子Verilog是一种硬件描述语言,常用于数字逻辑综合和编写硬件模块。

组合逻辑是Verilog中的一种基本类型,用于描述没有存储功能,只有输入和输出之间逻辑关系的电路。

以下是一些Verilog组合逻辑例子及其详细讲解。

1. 逻辑门AND门module and_gate(input a,input b,output y);assign y = a && b;endmodule在这个例子中,我们定义了一个AND门的模块。

它有两个输入a 和b,一个输出y。

通过assign语句,我们将输出y赋值为输入a和b 的逻辑与结果。

OR门module or_gate(input a,input b,output y);assign y = a || b;endmodule这是一个OR门的例子。

和AND门类似,我们通过assign语句将输出y赋值为输入a和b的逻辑或结果。

2. 多路选择器module mux(input a,input b,input c,input d,input [1:0] sel,output y);assign y = (sel == 2'b00) ? a :(sel == 2'b01) ? b :(sel == 2'b10) ? c :d;endmodule这个例子演示了一个4路多路选择器。

它有4个输入a、b、c和d,一个2位选择信号sel,一个输出y。

根据选择信号的不同值,输出y将根据如下规则选择不同的输入信号:00选择a,01选择b,10选择c,11选择d。

3. 比较器module comparator(input [3:0] a,input [3:0] b,output eq,output gt,output lt);assign eq = (a == b);assign gt = (a > b);assign lt = (a < b);endmodule上面的例子展示了一个比较器。

verilog hdl应用程序设计实例精讲

verilog hdl应用程序设计实例精讲网上现在有很多关于verilog hdl应用程序设计的资料,但是并没有一个很系统和全面的教程来帮助初学者快速入门。

本文就verilog hdl应用程序设计实例进行了精讲,从基本概念到应用实例一步一步地回答了初学者的问题,帮助大家理解verilog hdl的设计和应用。

一、verilog hdl的基本概念Verilog HDL是一种硬件描述语言,用于描述数字系统,包括逻辑电路、集成电路等等。

它既可以进行仿真验证,也可以直接生成硬件电路。

简单来说,verilog hdl就是一种用来描述数字系统的语言。

1.1 模块与实例化在verilog hdl中,模块是最基本的设计单元,每个模块包含一个或多个端口和内部逻辑电路。

模块可以包含其他模块,这被称为实例化。

实例化可以理解为创建一个模块的实例,并根据实例进行连接。

1.2 端口和内部信号模块的端口是与其他模块或外部电路连接的接口,可以是输入、输出或双向。

内部信号是模块内部产生和使用的信号,只在模块内部可见。

1.3 组合逻辑与时序逻辑组合逻辑是指只有输入信号改变时才会改变输出信号的逻辑电路,而时序逻辑是指输出信号的改变还受到时钟信号的控制。

在verilog hdl中,可以使用逻辑门、逻辑运算符和条件语句来实现组合逻辑和时序逻辑。

二、verilog hdl应用程序设计实例接下来,我们通过一些实例来展示verilog hdl的应用程序设计。

2.1 4位全加器我们首先来实现一个4位全加器。

全加器是用来实现两个二进制数的加法的电路,它能够实现两个输入和一个进位的相加操作,输出结果和进位。

在verilog hdl 中,可以使用逻辑运算符和条件语句来实现全加器。

2.2 4位加法器我们可以使用四个全加器来实现一个4位加法器。

加法器是用来实现两个二进制数的加法的电路,它能够实现多位的相加操作,输出结果和进位。

2.3 4位计数器计数器是一种能够实现计数功能的电路,它能够根据时钟信号进行计数,并在达到一定数值时输出特定信号。

硬件描述语言VerilogHDL基础

入zz x x x

CSLG

4、设计举例

试用Verilog语言的门级 元件描述2线-4线译码器.

E1

& Y0

//Gate-level description of a 2-to-4-

line decoder

module _2to4decoder (A1,A0,E,Y);

input A,B,E;

output [3:0] Y;

常量

格式为:<+/-><位宽>’<基数符号><数 例值如>:3’b101、5’o37、8’he3,8’b1001_0011

实数型常量 十进制记数法 如: 0.1、2.0、5.67

科学记数法 如: 23_5.1e2、5E-4

23510.0、 0.0005

CSLG

❖Verilog允许用参数定义语句定义一个标识 符来代表一个常量,称为符号常量。

CSLG

CSLG

用Verilog HDL描述组合逻辑电路

用VerilogHDL描述组合逻辑电路

❖用VerilogHDL描述组合逻辑电路有三种不 同抽象级别:

▪ 门级描述 ▪ 数据流描述 ▪ 行为级描述

❖VerilogHDL描述的电路就是该电路的 VerilogHDL模型。

CSLG

•门级描述:

一般使用Primitive(内部元件)、自定义的下层模块对电 路描述。主要用于层次化设计中。

多输入端的或非门

多输入端的异或非门

多输出端的反相器

控制信号高电平有效的 三态反相器

控制信号低电平有效的 三态反相器

CSLG

Verilog 基本门级元件

and n-input AND gate

可综合的verilog语句

可综合的verilog语句摘要:一、引言1.Verilog 简介2.Verilog 语句的可综合性二、可综合的Verilog 语句1.基本赋值语句2.组合逻辑实现3.时序逻辑实现4.实例化模块三、Verilog 语句的可综合性分析1.基本赋值语句的可综合性2.组合逻辑实现的可综合性3.时序逻辑实现的可综合性4.实例化模块的可综合性四、提高Verilog 代码可综合性的方法1.遵循可综合编程规范2.使用可综合的语法结构3.模块划分与层次设计五、总结1.Verilog 语句可综合性的重要性2.提高代码可综合性的实际应用价值正文:【引言】Verilog 是一种广泛应用于数字电路设计和验证的硬件描述语言。

在Verilog 中,语句的可综合性指的是能否将Verilog 代码转换为实际硬件电路。

了解可综合的Verilog 语句对于编写高效的硬件描述语言代码至关重要。

本文将介绍可综合的Verilog 语句及其可综合性分析,并提出提高代码可综合性的方法。

【可综合的Verilog 语句】Verilog 中有很多可综合的语句,包括基本赋值语句、组合逻辑实现、时序逻辑实现和实例化模块。

1.基本赋值语句基本赋值语句包括阻塞赋值(assignment)和非阻塞赋值(non-blocking assignment)。

这两种赋值语句都是可综合的。

2.组合逻辑实现组合逻辑实现通常使用与门(and)、或门(or)、非门(not)等基本逻辑门实现。

这些逻辑门的Verilog 实现都是可综合的。

3.时序逻辑实现时序逻辑实现通常使用寄存器(register)、计数器(counter)等元件实现。

这些元件的Verilog 实现都是可综合的。

4.实例化模块实例化模块是通过使用`实例化`关键字将一个模块复制多次。

实例化模块的Verilog 实现也是可综合的。

【Verilog 语句的可综合性分析】1.基本赋值语句的可综合性基本赋值语句的可综合性取决于赋值的目标。

verilog(1)

Z or z

High Impedance

0、1代表常见的布尔状态或者电平的状态 X常用于仿真中表示发生冲突或者错误,也可用于表示“don’t care” Z代表电路中的高阻状态 0、1、Z状态存在于真实的电路当中

9

常量

整数型:

8’b0100_1011

实数:1.34,1.3e2(130) 字符串:“FourValue”

基于名字

7

语法规范与注释

标志符由数字、字母、符号($)和下划线构成,但

是必须以字母或者下划线作为首字符 标志符区分大小写 语句遵循自由格式,可以每一条语句占用一行或者 多条语句共用一行 基本语句以“;”结束 注释有两种形式“//”和“/* */”

//单行注释 /* 多行注释 可以单行也可以跨行 */

有关Verilog的 全部权利都移交 OVI Cadence购买 Verilog版权 Verilog XL 诞生 1980 s

,

1990

Verilog IEEE1364-2001 标准发布

1987 1989 Synopsys公 司支持 Verilog输入

4

Verilog is a HDL

软件编程语言最终被转换为机器指令,可以在一台

– ABEL、ISPS、VHDL、Verilog、SystemC、SystemVerilog ……

3

Verilog语言的发展历史

“Verilog”= “Verification” + “Logic”

Verilog IEEE1364-2005 标准发布 使用模拟和数字 的Verilog 标准 发布 1995 1999 Verilog IEEE1364-1995 标准发布 Verilog HDL 公开发表 2001 2005 并入 SystemVerilog 标准IEEE 1800 2009

Verilog简明教程

附录A Verilog 参考资料本附录叙述了书中所用到的Verilog 语法。

其目的在于为读者查阅参考资料提供方便,因此只提供了一些简明的描述,并附带一些例子。

附录A 中绝大多数的例子是符合原始的Verilog 1995标准的,同时也介绍了一些Verilog 2001标准[8]中最重要的语法。

建议读者先学习2.10节中的Verilog 入门。

本附录不是想编写成Verilog 语法大全。

尽管我们讨论了Verilog 语言中对逻辑电路综合有用的几乎所有的语法,但是并未叙述对电路仿真有用的许多语法。

虽然本附录中省略的语法,在本书中并没有一个例子需要用到,但我们仍建议想进一步学习Verilog 的读者,参阅本附录指定的参考资料[1~7]。

如何编写Verilog 代码新手编写Verilog 代码时往往采用类似编写计算机程序的方式,即在程序中包含许多变量和循环。

计算机辅助设计工具综合这样的代码,究竟能生成什么样的逻辑电路是很难确定的。

综合工具的任务是分析一段Verilog 代码,根据语法确定究竟用什么电路来实现这段代码。

考虑如下的代码:按照语句的顺序,考虑每条语句的含义,我们就能理解语义,仿真工具也是这样理解程序段的。

这段代码使得f 根据s 的值,被赋予w 0或者w 1。

综合工具通常会用多路器电路来实现这段代码。

一般来说,综合工具必须能根据代码识别出该代码段对应某种电路结构,例如上面的多路器。

从实际观点出发,只有当用户编写的程序符合大家共同使用的风格时,综合工具才能做到这一点。

因此,刚开始学习使用Verilog 设计的用户应该采用经验丰富的设计者建议的编码风格。

本书共包含有140多个Verilog 代码的范例,各自与不同类型的逻辑电路相对应。

在所有这些范例中,它们的代码非常容易地对应于描述的逻辑电路。

建议读者在编写程序时采用相同的编码风格。

好的方法是:“编写Verilog 代码时,就知道代码代表的是什么样的逻辑电路。

verilog编程实例

verilog编程实例我们需要明确这个电路的功能和设计要求。

假设我们需要实现一个4位二进制加法器,即输入两个4位的二进制数,输出它们的和。

为了简化问题,我们先考虑只有无符号整数的加法,即只需要实现两个正整数的相加。

接下来,我们可以使用Verilog语言来描述这个电路的结构和行为。

我们首先声明输入端口和输出端口的位宽,即4位。

然后,我们定义一个module,命名为"binary_adder"。

在这个module中,我们定义了两个4位的输入信号a和b,以及一个4位的输出信号sum。

同时,我们还定义了一个内部信号carry,用于记录进位信息。

在module的主体部分,我们使用assign语句来实现信号之间的逻辑关系。

具体地,我们可以通过逐位相加的方式,将输入信号a和b的每一位与进位carry相加,并将结果存储在输出信号sum的对应位上。

同时,我们还需要更新进位carry的值,以确保加法运算的正确性。

为了实现这个逻辑,我们可以使用Verilog中的加法运算符"+"和逻辑与运算符"&"。

通过对输入信号的每一位进行逐位运算,我们可以得到输出信号sum的每一位的值。

同时,我们还需要根据输入信号和进位carry的值,计算出新的进位carry的值。

在实际的Verilog编程中,我们需要注意信号的声明和赋值的顺序。

一般而言,我们需要先声明信号,然后再通过assign语句对信号进行赋值。

这样可以确保信号的值能够正确传递和计算。

完成Verilog代码的编写后,我们需要使用相应的仿真工具来验证电路的功能。

常用的仿真工具有ModelSim和Xilinx ISE等。

通过仿真工具,我们可以为输入信号a和b设置不同的值,并观察输出信号sum的变化。

通过比较输出信号sum和预期的结果,我们可以验证电路的正确性。

除了验证电路的正确性外,我们还可以通过综合工具将Verilog代码转换成对应的门级电路。

verilog语法PPT教学课件

2020/12/10

13

Verilog中reg与wire的不同点

➢ 用寄存器 (reg)类型变量生成组合逻辑举例:

module rw1( a, b, out1, out2 ) ;

input a, b;

output out1, out2;

a

BUFF out2

reg out1;

wire out2;

assign out2 = a ;

2020/12/10

12

Verilog模块中的信号

➢ 只有两种主要的信号类型: - 寄存器类型: reg

在always 块中被赋值的信号,往往代表

触发器,但不一定是触发器。 - 连线(网络)类型: wire

用 assign 关键词指定的组合逻辑的信号 或连线

➢ 寄存器 ( reg )类型不一定是触发器。 ➢ 它只是在 always 块中赋值的信号。

解 ➢ 开关级:有关物理形状和布局参数的模块,非

常难理解

2020/12/10

7

抽象级别和综合与仿真的关系

➢ 行为仿真:行为的验证和验证模块分割的合理性 ➢ 前仿真:即RTL级仿真,检查有关模块逻辑执行

步骤是否正确。 ➢ 逻辑综合:把RTL级模块转换成门级。 ➢ 后仿真:用门级模型做验证,检查门的互连逻辑

➢研究并行快速算法

➢电路实现问题

➢设计并研制具有并行结构的数字和计算 逻辑结构。

➢电路实现的两个方向:

➢ FPGA

➢专用集成电路

➢Verilog HDL建模、仿真、综合和全面 验证。

2020/12/10

2

什么是复杂的数字逻辑系统?

➢ 嵌入式微处理机系统 ➢ 数字信号处理系统 ➢ 高速并行计算逻辑 ➢ 高速通信协议电路 ➢ 高速编码/解码、加密/解密电路 ➢ 复杂的多功能智能接口 ➢ 门逻辑总数超过几万门达到几百甚至达几

Verilog HDL黑金资料FPGA

根据上面两个例子的三路加法器,一个是由组合逻辑级建模而成,另外一个则是由 RTL 级建模而成。 组合逻辑级建模给人最直接的印象就是模块都不带 “时钟信号” , 反之 RTL 级建模的最大特征性,就是模块都会伴随 “时钟信号” 。当然,笔者不可能仅以“时钟 信号”来区分组合逻辑级建模和 RTL 级建模。 在实际的学习中过于在意区分“什么是组合逻辑级建模,什么是 RTL 级建模”是对学 习没有任何帮助的 (不知道为什么很多参考书都很习注重区分) , 凡是有关 Verilog HDL 语言的建模它们都被需要。话虽如此,但是在这一本笔记里笔者还是比较注重 RTL 级 的建模。

0.2 HDL 语言的层次

有一个很好笑的话题,老师常常都说 HDL 语言的层次是汇编语言和 C 语言的之间。假 设汇编语言是低级语言,C 语言是高级语言,那么 HDL 语言既是不上又不小?啊哈哈 哈,如果站在人类之中它亦是不男也不女。我们不需要为这个无聊的话题,浪费太多思 考的时间。HDL 语言的英文全名是 Hardware Description Language ,中文译名就是硬 件描述语言。事实上无论是汇编语言也好还是 C 语言也好,它们的作用就是用来控制处 理器,反之 HDL 语言的作用只是用来建立一个硬件的模块而已。

module Add_module ( input CLK, input RSTn, input [7:0]A, input [7:0]B, input [7:0]C, Output[15:0]) ; reg [15:0]rTemp; alawys @ ( posedge CLK negedge RSTn ) if( !RSTn ) rTemp <= 4'0; else rTemp <= A + B + C; assign Output = rTemp; endmodule

Verilog设计练习十例及答案

Verilog设计练习⼗例及答案设计练习进阶前⾔:在前⾯九章学习得基础上, 通过本章得练习,⼀定能逐步掌握Verilog HDL设计得要点。

我们可以先理解样板模块中每⼀条语句得作⽤,然后对样板模块进⾏综合前与综合后仿真,再独⽴完成每⼀阶段规定得练习。

当⼗个阶段得练习做完后,便可以开始设计⼀些简单得逻辑电路与系统。

很快我们就能过渡到设计相当复杂得数字逻辑系统。

当然,复杂得数字逻辑系统得设计与验证,不但需要系统结构得知识与经验得积累,还需要了解更多得语法现象与掌握⾼级得Verilog HDL系统任务,以及与C语⾔模块接⼝得⽅法(即PLI),这些已超出得本书得范围。

有兴趣得同学可以阅读Verilog语法参考资料与有关⽂献,⾃⼰学习,我们将在下⼀本书中介绍Verilog较⾼级得⽤法。

练习⼀.简单得组合逻辑设计⽬得: 掌握基本组合逻辑电路得实现⽅法。

这就是⼀个可综合得数据⽐较器,很容易瞧出它得功能就是⽐较数据a与数据b,如果两个数据相同,则给出结果1,否则给出结果0。

在Verilog HDL中,描述组合逻辑时常使⽤assign 结构。

注意equal=(a==b)?1:0,这就是⼀种在组合逻辑实现分⽀判断时常使⽤得格式。

模块源代码:// pare、vmodule pare(equal,a,b);input a,b;output equal;assign equal=(a==b)?1:0; //a等于b时,equal输出为1;a不等于b时,//equal输出为0。

endmodule测试模块⽤于检测模块设计得正确与否,它给出模块得输⼊信号,观察模块得内部信号与输出信号,如果发现结果与预期得有所偏差,则要对设计模块进⾏修改。

测试模块源代码:`timescale 1ns/1ns //定义时间单位。

`include "、/pare、v" //包含模块⽂件。

在有得仿真调试环境中并不需要此语句。

//⽽需要从调试环境得菜单中键⼊有关模块⽂件得路径与名称module paretest;reg a,b;wire equal;initial //initial常⽤于仿真时信号得给出。

Verilog的135个经典设计实例

Verilog的135个经典设计实例王金明:《Verilog HDL程序设计教程》【例3.1】4位全加器module adder4(cout,sum,ina,inb,cin);output[3:0] sum;output cout;input[3:0] ina,inb;input cin;assign {cout,sum}=ina+inb+cin;endmodule【例3.2】4位计数器module count4(out,reset,clk);output[3:0] out;input reset,clk;reg[3:0] out;always @(posedge clk)beginif (reset) out<=0; //同步复位else out<=out+1; //计数endendmodule【例3.3】4位全加器的仿真程序`timescale 1ns/1ns`include "adder4.v"module adder_tp; //测试模块的名字reg[3:0] a,b; //测试输入信号定义为reg型reg cin;wire[3:0] sum; //测试输出信号定义为wire型wire cout;integer i,j;adder4 adder(sum,cout,a,b,cin); //调用测试对象always #5 cin=~cin; //设定cin的取值initialbegina=0;b=0;cin=0;for(i=1;i<16;i=i+1)#10 a=i; //设定a的取值end- 1 - 程序文本initialbeginfor(j=1;j<16;j=j+1)#10 b=j; //设定b的取值endinitial //定义结果显示格式begin$monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum);#160 $finish;endendmodule【例3.4】4位计数器的仿真程序`timescale 1ns/1ns`include "count4.v"module coun4_tp;reg clk,reset; //测试输入信号定义为reg型wire[3:0] out; //测试输出信号定义为wire型parameter DELY=100;count4 mycount(out,reset,clk); //调用测试对象always #(DELY/2) clk = ~clk; //产生时钟波形initialbegin //激励信号定义clk =0; reset=0;#DELY reset=1;#DELY reset=0;#(DELY*20) $finish;end//定义结果显示格式initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out);endmodule【例3.5】“与-或-非”门电路module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F)input A,B,C,D; //模块的输入端口为A,B,C,Doutput F; //模块的输出端口为F- 2 -王金明:《Verilog HDL程序设计教程》wire A,B,C,D,F; //定义信号的数据类型assign F= ~((A&B)|(C&D)); //逻辑功能描述endmodule【例5.1】用case语句描述的4选1数据选择器module mux4_1(out,in0,in1,in2,in3,sel);output out;input in0,in1,in2,in3;input[1:0] sel;reg out;always @(in0 or in1 or in2 or in3 or sel) //敏感信号列表case(sel)2'b00: out=in0;2'b01: out=in1;2'b10: out=in2;2'b11: out=in3;default: out=2'bx;endcaseendmodule【例5.2】同步置数、同步清零的计数器module count(out,data,load,reset,clk);output[7:0] out;input[7:0] data;input load,clk,reset;reg[7:0] out;always @(posedge clk) //clk上升沿触发beginif (!reset) out = 8'h00; //同步清0,低电平有效else if (load) out = data; //同步预置else out = out + 1; //计数endendmodule【例5.3】用always过程语句描述的简单算术逻辑单元`define add 3'd0`define minus 3'd1`define band 3'd2`define bor 3'd3`define bnot 3'd4- 3 - 程序文本module alu(out,opcode,a,b);output[7:0] out;reg[7:0] out;input[2:0] opcode; //操作码input[7:0] a,b; //操作数always@(opcode or a or b) //电平敏感的always块begincase(opcode)`add: out = a+b; //加操作`minus: out = a-b; //减操作`band: out = a&b; //求与`bor: out = a|b; //求或`bnot: out=~a; //求反default: out=8'hx; //未收到指令时,输出任意态endcaseendendmodule【例5.4】用initial过程语句对测试变量A、B、C赋值`timescale 1ns/1nsmodule test;reg A,B,C;initialbeginA = 0;B = 1;C = 0;#50 A = 1; B = 0;#50 A = 0; C = 1;#50 B = 1;#50 B = 0; C = 0;#50 $finish ;endendmodule【例5.5】用begin-end串行块产生信号波形`timescale 10ns/1nsmodule wave1;reg wave;parameter cycle=10;initialbegin- 4 -王金明:《Verilog HDL程序设计教程》wave=0;#(cycle/2) wave=1;#(cycle/2) wave=0;#(cycle/2) wave=1;#(cycle/2) wave=0;#(cycle/2) wave=1;#(cycle/2) $finish ;endinitial $monitor($time,,,"wave=%b",wave); endmodule【例5.6】用fork-join并行块产生信号波形`timescale 10ns/1nsmodule wave2;reg wave;parameter cycle=5;initialforkwave=0;#(cycle) wave=1;#(2*cycle) wave=0;#(3*cycle) wave=1;#(4*cycle) wave=0;#(5*cycle) wave=1;#(6*cycle) $finish;initial $monitor($time,,,"wave=%b",wave); endmodule【例5.7】持续赋值方式定义的2选1多路选择器module MUX21_1(out,a,b,sel);input a,b,sel;output out;assign out=(sel==0)?a:b;//持续赋值,如果sel为0,则out=a ;否则out=b endmodule【例5.8】阻塞赋值方式定义的2选1多路选择器module MUX21_2(out,a,b,sel);input a,b,sel;- 5 - 程序文本output out;reg out;always@(a or b or sel)beginif(sel==0) out=a; //阻塞赋值else out=b;endendmodule【例5.9】非阻塞赋值module non_block(c,b,a,clk);output c,b;input clk,a;reg c,b;always @(posedge clk)beginb<=a;endendmodule【例5.10】阻塞赋值module block(c,b,a,clk);output c,b;input clk,a;reg c,b;always @(posedge clk)beginb=a;c=b;endendmodule【例5.11】模为60的BCD码加法计数器module count60(qout,cout,data,load,cin,reset,clk); output[7:0] qout;output cout;input[7:0] data;input load,cin,clk,reset;reg[7:0] qout;always @(posedge clk) //clk上升沿时刻计数- 6 - 王金明:《Verilog HDL程序设计教程》beginif (reset) qout<=0; //同步复位else if(load) qout<=data; //同步置数else if(cin)beginif(qout[3:0]==9) //低位是否为9,是则beginqout[3:0]<=0; //回0,并判断高位是否为5if (qout[7:4]==5) qout[7:4]<=0;elseqout[7:4]<=qout[7:4]+1; //高位不为5,则加1endelse //低位不为9,则加1qout[3:0]<=qout[3:0]+1;endendassign cout=((qout==8'h59)&cin)?1:0; //产生进位输出信号endmodule【例5.12】BCD码—七段数码管显示译码器module decode4_7(decodeout,indec);output[6:0] decodeout;input[3:0] indec;reg[6:0] decodeout;always @(indec)begincase(indec) //用case语句进行译码4'd0:decodeout=7'b1111110;4'd1:decodeout=7'b0110000;4'd2:decodeout=7'b1101101;4'd3:decodeout=7'b1111001;4'd4:decodeout=7'b0110011;4'd5:decodeout=7'b1011011;4'd6:decodeout=7'b1011111;4'd7:decodeout=7'b1110000;4'd8:decodeout=7'b1111111;4'd9:decodeout=7'b1111011;default: decodeout=7'bx;endcaseend- 7 - 程序文本endmodule【例5.13】用casez描述的数据选择器module mux_casez(out,a,b,c,d,select); output out;input a,b,c,d;input[3:0] select;reg out;always @(select or a or b or c or d) begincasez(select)4'b1: out = a;4'b??1?: out = b;4'b?1??: out = c;4'b1: out = d;endcaseendendmodule【例5.14】隐含锁存器举例module buried_ff(c,b,a);output c;input b,a;reg c;always @(a or b)beginif((b==1)&&(a==1)) c=a&b;endendmodule【例5.15】用for语句描述的七人投票表决器module voter7(pass,vote);output pass;input[6:0] vote;reg[2:0] sum;integer i;reg pass;always @(vote)beginsum=0;- 8 -王金明:《Verilog HDL程序设计教程》for(i=0;i<=6;i=i+1) //for语句if(vote[i]) sum=sum+1;if(sum[2]) pass=1; //若超过4人赞成,则pass=1 else pass=0;endendmodule【例5.16】用for语句实现2个8位数相乘module mult_for(outcome,a,b);parameter size=8;input[size:1] a,b; //两个操作数output[2*size:1] outcome; //结果reg[2*size:1] outcome;integer i;always @(a or b)beginoutcome=0;for(i=1; i<=size; i=i+1) //for语句if(b[i]) outcome=outcome +(a << (i-1));endendmodule【例5.17】用repeat实现8位二进制数的乘法module mult_repeat(outcome,a,b);parameter size=8;input[size:1] a,b;output[2*size:1] outcome;reg[2*size:1] temp_a,outcome;reg[size:1] temp_b;always @(a or b)beginoutcome=0;temp_a=a;temp_b=b;repeat(size) //repeat语句,size为循环次数beginif(temp_b[1]) //如果temp_b的最低位为1,就执行下面的加法outcome=outcome+temp_a;temp_a=temp_a<<1; //操作数a左移一位- 9 - 程序文本temp_b=temp_b>>1; //操作数b右移一位endendendmodule【例5.18】同一循环的不同实现方式module loop1; //方式1integer i;initialfor(i=0;i<4;i=i+1) //for语句begin$display(“i=%h”,i);endendmodulemodule loop2; //方式2integer i;initial begini=0;while(i<4) //while语句begin$display ("i=%h",i);i=i+1;endendendmodulemodule loop3; //方式3integer i;initial begini=0;repeat(4) //repeat语句begin$display ("i=%h",i);i=i+1;endendendmodule【例5.19】使用了`include语句的16位加法器- 10 -王金明:《Verilog HDL程序设计教程》`include "adder.v" module adder16(cout,sum,a,b,cin);output cout;parameter my_size=16;output[my_size-1:0] sum;input[my_size-1:0] a,b;input cin;adder my_adder(cout,sum,a,b,cin); //调用adder模块endmodule//下面是adder模块代码module adder(cout,sum,a,b,cin);parameter size=16;output cout;output[size-1:0] sum;input cin;input[size-1:0] a,b;assign {cout,sum}=a+b+cin;endmodule【例5.20】条件编译举例module compile(out,A,B);output out;input A,B;`ifdef add //宏名为addassign out=A+B;`elseassign out=A-B;`endifendmodule【例6.1】加法计数器中的进程module count(data,clk,reset,load,cout,qout);output cout;output[3:0] qout;reg[3:0] qout;input[3:0] data;input clk,reset,load;- 11 - 程序文本always @(posedge clk) //进程1,always过程块beginif (!reset) qout= 4'h00; //同步清0,低电平有效else if (load) qout= data; //同步预置else qout=qout + 1; //加法计数endassign cout=(qout==4'hf)?1:0; //进程2,用持续赋值产生进位信号endmodule【例6.2】任务举例module alutask(code,a,b,c);input[1:0] code;input[3:0] a,b;output[4:0] c;reg[4:0] c;task my_and; //任务定义,注意无端口列表input[3:0] a,b; //a,b,out名称的作用域范围为task任务内部output[4:0] out;integer i;beginfor(i=3;i>=0;i=i-1)out[i]=a[i]&b[i]; //按位与endendtaskalways@(code or a or b)begincase(code)2'b00: my_and(a,b,c);/* 用任务my_and,需注意端口列表的顺序应与任务定义中的一致,这里的a,b,c分别对应任务定义中的a,b,out */2'b01: c=a|b; //或2'b10: c=a-b; //相减2'b11: c=a+b; //相加endcaseendendmodule- 12 -王金明:《Verilog HDL程序设计教程》【例6.3】测试程序`include "alutask.v"module alu_tp;reg[3:0] a,b;reg[1:0] code;wire[4:0] c;parameter DELY = 100;alutask ADD(code,a,b,c); //调用被测试模块initial begincode=4'd0; a= 4'b0000; b= 4'b1111;#DELY code=4'd0; a= 4'b0111; b= 4'b1101;#DELY code=4'd1; a= 4'b0001; b= 4'b0011;#DELY code=4'd2; a= 4'b1001; b= 4'b0011;#DELY code=4'd3; a= 4'b0011; b= 4'b0001;#DELY code=4'd3; a= 4'b0111; b= 4'b1001;#DELY $finish;endinitial $monitor($time,,,"code=%b a=%b b=%b c=%b", code,a,b,c);endmodule【例6.4】函数function[7:0] get0;input[7:0] x;reg[7:0] count;integer i;begincount=0;for (i=0;i<=7;i=i+1)if (x[i]=1'b0) count=count+1;get0=count;endendfunction【例6.5】用函数和case语句描述的编码器(不含优先顺序)module code_83(din,dout);input[7:0] din;output[2:0] dout;- 13 - 程序文本function[2:0] code; //函数定义input[7:0] din; //函数只有输入,输出为函数名本身casex (din)8'b1xxx_xxxx : code = 3'h7;8'b01xx_xxxx : code = 3'h6;8'b001x_xxxx : code = 3'h5;8'b0001_xxxx : code = 3'h4;8'b0000_1xxx : code = 3'h3;8'b0000_01xx : code = 3'h2;8'b0000_001x : code = 3'h1;8'b0000_000x : code = 3'h0;default: code = 3'hx;endcaseendfunctionassign dout = code(din) ; //函数调用endmodule【例6.6】阶乘运算函数module funct(clk,n,result,reset);output[31:0] result;input[3:0] n;input reset,clk;reg[31:0] result;always @(posedge clk) //在clk的上升沿时执行运算beginif(!reset) result<=0; //复位else beginresult <= 2 * factorial(n); //调用factorial函数endendfunction[31:0] factorial; //阶乘运算函数定义(注意无端口列表)input[3:0] opa; //函数只能定义输入端,输出端口为函数名本身reg[3:0] i;beginfactorial = opa ? 1 : 0;for(i= 2; i <= opa; i = i+1) //该句若要综合通过,opa应赋具体的数值factorial = i* factorial; //阶乘运算end- 14 -王金明:《Verilog HDL程序设计教程》endfunction【例6.7】测试程序`define clk_cycle 50`include "funct.v"module funct_tp;reg[3:0] n;reg reset,clk;wire[31:0] result;initial //定义激励向量beginn=0; reset=1; clk=0;for(n=0;n<=15;n=n+1)#100 n=n;endinitial $monitor($time,,,"n=%d result=%d",n,result);//定义输出显示格式always # `clk_cycle clk=~clk; //产生时钟信号funct funct_try(.clk(clk),.n(n),.result(result),.reset(reset)); //调用被测试模块endmodule【例6.8】顺序执行模块1module serial1(q,a,clk);output q,a;input clk;reg q,a;always @(posedge clk)beginq=~q;a=~q;end【例6.9】顺序执行模块2 module serial2(q,a,clk); output q,a;- 15 - 程序文本input clk;reg q,a;always @(posedge clk) begina=~q;q=~q;endendmodule【例6.10】并行执行模块1 module paral1(q,a,clk); output q,a;input clk;reg q,a;always @(posedge clk) beginq=~q;endalways @(posedge clk) begina=~q;endendmodule【例6.11】并行执行模块2 module paral2(q,a,clk); output q,a;input clk;reg q,a;always @(posedge clk)begina=~q;endalways @(posedge clk)beginq=~q;endendmodule【例7.1】调用门元件实现的4选1 MUX- 16 -王金明:《Verilog HDL程序设计教程》module mux4_1a(out,in1,in2,in3,in4,cntrl1,cntrl2);output out;input in1,in2,in3,in4,cntrl1,cntrl2;wire notcntrl1,notcntrl2,w,x,y,z;not notcntrl1,cntrl2),(notcntrl2,cntrl2);and (w,in1,notcntrl1,notcntrl2),(x,in2,notcntrl1,cntrl2),(y,in3,cntrl1,notcntrl2),(z,in4,cntrl1,cntrl2);or (out,w,x,y,z);endmodule【例7.2】用case语句描述的4选1 MUXmodule mux4_1b(out,in1,in2,in3,in4,cntrl1,cntrl2);output out;input in1,in2,in3,in4,cntrl1,cntrl2;reg out;always@(in1 or in2 or in3 or in4 or cntrl1 or cntrl2)case({cntrl1,cntrl2})2'b00:out=in1;2'b01:out=in2;2'b10:out=in3;2'b11:out=in4;default:out=2'bx;endcaseendmodule【例7.3】行为描述方式实现的4位计数器module count4(clk,clr,out);input clk,clr;output[3:0] out;reg[3:0] out;always @(posedge clk or posedge clr)beginif (clr) out<=0;else out<=out+1;endendmodule- 17 - 程序文本【例7.4】数据流方式描述的4选1 MUXmodule mux4_1c(out,in1,in2,in3,in4,cntrl1,cntrl2);output out;input in1,in2,in3,in4,cntrl1,cntrl2;assign out=(in1 & ~cntrl1 & ~cntrl2)|(in2 & ~cntrl1 & cntrl2)|(in3 & cntrl1 & ~cntrl2)|(in4 & cntrl1 & cntrl2);endmodule【例7.5】用条件运算符描述的4选1 MUXmodule mux4_1d(out,in1,in2,in3,in4,cntrl1,cntrl2); output out;input in1,in2,in3,in4,cntrl1,cntrl2;assign out=cntrl1 ? (cntrl2 ? in4:in3):(cntrl2 ? in2:in1); endmodule【例7.6】门级结构描述的2选1MUXmodule mux2_1a(out,a,b,sel);output out;input a,b,sel;not (sel_,sel);and a1,a,sel_),(a2,b,sel);or (out,a1,a2);endmodule【例7.7】行为描述的2选1MUXmodule mux2_1b(out,a,b,sel);output out;input a,b,sel;reg out;always @(a or b or sel)beginif(sel) out = b;else out = a;endendmodule【例7.8】数据流描述的2选1MUXmodule MUX2_1c(out,a,b,sel);output out;- 18 -王金明:《Verilog HDL程序设计教程》input a,b,sel;assign out = sel ? b : a; endmodule【例7.9】调用门元件实现的1位半加器module half_add1(a,b,sum,cout); input a,b;output sum,cout;and cout,a,b);xor sum,a,b);endmodule【例7.10】数据流方式描述的1位半加器module half_add2(a,b,sum,cout); input a,b;output sum,cout;assign sum=a^b;assign cout=a&b;endmodule【例7.11】采用行为描述的1位半加器module half_add3(a,b,sum,cout); input a,b;output sum,cout;reg sum,cout;always @(a or b)begincase ({a,b}) //真值表描述2'b00: begin sum=0; cout=0; end2'b01: begin sum=1; cout=0; end2'b10: begin sum=1; cout=0; end2'b11: begin sum=0; cout=1; end endcaseendendmodule【例7.12】采用行为描述的1位半加器module half_add4(a,b,sum,cout); input a,b;output sum,cout;- 19 - 程序文本reg sum,cout;always @(a or b)beginsum= a^b;cout=a&b;endendmodule【例7.13】调用门元件实现的1位全加器module full_add1(a,b,cin,sum,cout); input a,b,cin;output sum,cout;wire s1,m1,m2,m3;and m1,a,b),(m2,b,cin),(m3,a,cin);xor s1,a,b),(sum,s1,cin);or (cout,m1,m2,m3);endmodule【例7.14】数据流描述的1位全加器module full_add2(a,b,cin,sum,cout); input a,b,cin;output sum,cout;assign sum = a ^ b ^ cin;assign cout = (a & b)|(b & cin)|(cin & a);endmodule【例7.15】1位全加器module full_add3(a,b,cin,sum,cout);input a,b,cin;output sum,cout;assign {cout,sum}=a+b+cin;endmodule【例7.16】行为描述的1位全加器module full_add4(a,b,cin,sum,cout);input a,b,cin;output sum,cout;- 20 -王金明:《Verilog HDL程序设计教程》reg sum,cout; //在always块中被赋值的变量应定义为reg型reg m1,m2,m3;always @(a or b or cin)beginsum = (a ^ b) ^ cin;m1 = a & b;m2 = b & cin;m3 = a & cin;cout = (m1|m2)|m3;endendmodule【例7.17】混合描述的1位全加器module full_add5(a,b,cin,sum,cout);input a,b,cin;output sum,cout;reg cout,m1,m2,m3; //在always块中被赋值的变量应定义为reg型wire s1;xor x1(s1,a,b); //调用门元件always @(a or b or cin) //always块语句beginm1 = a & b;m2 = b & cin;m3 = a & cin;cout = (m1| m2) | m3;endassign sum = s1 ^ cin; //assign持续赋值语句endmodule【例7.18】结构描述的4位级连全加器`include "full_add1.v"module add4_1(sum,cout,a,b,cin);output[3:0] sum;output cout;input[3:0] a,b;input cin;full_add1 f0(a[0],b[0],cin,sum[0],cin1); //级连描述full_add1 f1(a[1],b[1],cin1,sum[1],cin2);full_add1 f2(a[2],b[2],cin2,sum[2],cin3);- 21 - 程序文本full_add1 f3(a[3],b[3],cin3,sum[3],cout); endmodule【例7.19】数据流描述的4位全加器module add4_2(cout,sum,a,b,cin);output[3:0] sum;output cout;input[3:0] a,b;input cin;assign {cout,sum}=a+b+cin;endmodule【例7.20】行为描述的4位全加器module add4_3(cout,sum,a,b,cin);output[3:0] sum;output cout;input[3:0] a,b;input cin;reg[3:0] sum;reg cout;always @(a or b or cin)begin{cout,sum}=a+b+cin;endendmodule【例8.1】$time与$realtime的区别`timescale 10ns/1nsmodule time_dif;reg ts;parameter delay=2.6;initialbegin#delay ts=1;#delay ts=0;#delay ts=1;#delay ts=0;endinitial $monitor($time,,,"ts=%b",ts); //使用函数$time- 22 - 王金明:《Verilog HDL程序设计教程》endmodule【例8.2】$random函数的使用`timescale 10ns/1nsmodule random_tp;integer data;integer i;parameter delay=10;initial $monitor($time,,,"data=%b",data);initial beginfor(i=0; i<=100; i=i+1)#delay data=$random; //每次产生一个随机数endendmodule【例8.3】1位全加器进位输出UDP元件primitive carry_udp(cout,cin,a,b);input cin,a,b;output cout;table//cin a b : cout //真值表0 0 0 : 0;0 1 0 : 0;0 0 1 : 0;0 1 1 : 1;1 0 0 : 0;1 0 1 : 1;1 1 0 : 1;1 1 1 : 1;endtableendprimitive【例8.4】包含x态输入的1位全加器进位输出UDP元件primitive carry_udpx1(cout,cin,a,b);input cin,a,b;output cout;table// cin a b : cout //真值表0 0 0 : 0;- 23 - 程序文本0 1 0 : 0;0 0 1 : 0;0 1 1 : 1;1 0 0 : 0;1 0 1 : 1;1 1 0 : 1;1 1 1 : 1;0 0 x : 0; //只要有两个输入为0,则进位输出肯定为0 0 x 0 : 0;x 0 0 : 0;1 1 x : 1; //只要有两个输入为1,则进位输出肯定为1 1 x 1 : 1;x 1 1 : 1;endtableendprimitive【例8.5】用简缩符“?”表述的1位全加器进位输出UDP元件primitive carry_udpx2(cout,cin,a,b);input cin,a,b;output cout;table// cin a b : cout //真值表0 0 : 0; //只要有两个输入为0,则进位输出肯定为00 ? 0 : 0;0 0 ? : 0;1 1 : 1; //只要有两个输入为1,则进位输出肯定为11 ? 1 : 1;1 1 ? : 1;endtableendprimitive【例8.6】3选1多路选择器UDP元件primitive mux31(Y,in0,in1,in2,s2,s1);input in0,in1,in2,s2,s1;output Y;table//in0 in1 in2 s2 s1 : Y0 ? ? 0 0 : 0; //当s2s1=00时,Y=in01 ? ? 0 0 : 1;0 ? 0 1 : 0; //当s2s1=01时,Y=in1 - 24 -王金明:《Verilog HDL程序设计教程》1 ? 0 1 : 1;0 1 ? : 0; //当s2s1=1?时,Y=in21 1 ? : 1;0 0 ? 0 ? : 0;1 1 ? 0 ? : 1;0 ? 0 ? 0 : 0;1 ? 1 ? 0 : 1;0 0 ? 1 : 0;1 1 ? 1 : 1;endtableendprimitive【例8.7】电平敏感的1位数据锁存器UDP元件primitive latch(Q,clk,reset,D);input clk,reset,D;output Q;reg Q;initial Q = 1'b1; //初始化table// clk reset D : state : Q1 ? : ? : 0 ; //reset=1,则不管其他端口为什么值,输出都为00 0 0 : ? : 0 ; //clk=0,锁存器把D端的输入值输出0 0 1 : ? : 1 ;1 0 ? : ? : - ; //clk=1,锁存器的输出保持原值,用符号“-”表示endtableendprimitive【例8.8】上升沿触发的D触发器UDP元件primitive DFF(Q,D,clk);output Q;input D,clk;reg Q;table//clk D : state : Q(01) 0 : ? : 0; //上升沿到来,输出Q=D(01) 1 : ? : 1;(0x) 1 : 1 : 1;(0x) 0 : 0 : 0;(?0) ? : ? : -; //没有上升沿到来,输出Q保持原值(??) : ? : - ; //时钟不变,输出也不变- 25 - 程序文本endtableendprimitive【例8.9】带异步置1和异步清零的上升沿触发的D触发器UDP 元件primitive DFF_UDP(Q,D,clk,clr,set);output Q;input D,clk,clr,set;reg Q;table// clk D clr et state : Q (01) 1 0 0 : ? : 0; (01) 1 0 x : ? : 0;0 x : 0 : 0;(01) 0 0 0 : ? : 1; (01) 0 x 0 : ? : 1;x 0 : 1 : 1;(x1) 1 0 0 : 0 : 0;(x1) 0 0 0 : 1 : 1;(0x) 1 0 0 : 0 : 0;(0x) 0 0 0 : 1 : 1;1 ? : ? : 1; //异步复位0 1 : ? : 0; //异步置1 n ? 0 0 : ? : -;* ? ? : ? : -;(?0) ? : ? : -;(?0): ? : -;: ? : x;endtableendprimitive【例8.12】延迟定义块举例module delay(out,a,b,c); output out;input a,b,c;and a1(n1,a,b);or o1(out,c,n1);specify(a=>out)=2;(b=>out)=3;(c=>out)=1;- 26 -王金明:《Verilog HDL程序设计教程》endspecifyendmodule【例8.13】激励波形的描述'timescale 1ns/1nsmodule test1;reg A,B,C;initialbegin //激励波形描述A = 0;B = 1;C = 0;#100 C = 1;#100 A = 1; B = 0;#100 A = 0;#100 C = 0;#100 $finish;endinitial $monitor($time,,,"A=%d B=%d C=%d",A,B,C); //显示endmodule【例8.15】用always过程块产生两个时钟信号module test2;reg clk1,clk2;parameter CYCLE = 100;alwaysbegin{clk1,clk2} = 2'b10;#(CYCLE/4) {clk1,clk2} = 2'b01;#(CYCLE/4) {clk1,clk2} = 2'b11;#(CYCLE/4) {clk1,clk2} = 2'b00;#(CYCLE/4) {clk1,clk2} = 2'b10;endinitial $monitor($time,,,"clk1=%b clk2=%b",clk1,clk2); endmodule【例8.17】存储器在仿真程序中的应用module ROM(addr,data,oe);output[7:0] data; //数据信号input[14:0] addr; //地址信号input oe; //读使能信号,低电平有效- 27 - 程序文本reg[7:0] mem[0:255]; //存储器定义parameter DELAY = 100;assign #DELAY data=(oe==0) ? mem[addr] : 8'hzz; initial $readmemh("rom.hex",mem); //从文件中读入数据endmodule【例8.18】8位乘法器的仿真程序`timescale 10ns/1nsmodule mult_tp; //测试模块的名字reg[7:0] a,b; //测试输入信号定义为reg型wire [15:0] out; //测试输出信号定义为wire型integer i,j;mult8 m1(out,a,b); //调用测试对象//激励波形设定initialbegina=0;b=0;for(i=1;i<255;i=i+1)#10 a=i;endinitialbeginfor(j=1;j<255;j=j+1)#10 b=j;endinitial //定义结果显示格式begin$monitor($time,,,"%d * %d= %d",a,b,out);#2560 $finish;endendmodulemodule mult8(out, a, b); //8位乘法器源代码parameter size=8;input[size:1] a,b; //两个操作数output[2*size:1] out; //结果assign out=a*b; //乘法运算符- 28 -王金明:《Verilog HDL程序设计教程》endmodule 【例8.19】8位加法器的仿真程序`timescale 1ns/1nsmodule add8_tp; //仿真模块无端口列表reg[7:0] A,B; //输入激励信号定义为reg型reg cin;wire[7:0] SUM; //输出信号定义为wire型wire cout;parameter DELY = 100;add8 AD1(SUM,cout,A,B,cin); //调用测试对象initial begin //激励波形设定A= 8'd0; B= 8'd0; cin=1'b0;#DELY A= 8'd100; B= 8'd200; cin=1'b1;#DELY A= 8'd200; B= 8'd88;#DELY A= 8'd210; B= 8'd18; cin=1'b0;#DELY A= 8'd12; B= 8'd12;#DELY A= 8'd100; B= 8'd154;#DELY A= 8'd255; B= 8'd255; cin=1'b1;#DELY $finish;end//输出格式定义initial $monitor($time,,,"%d + %d + %b = {%b, %d}",A,B,cin,cout,SUM);endmodulemodule add8(SUM,cout,A,B,cin); //待测试的8位加法器模块output[7:0] SUM;output cout;input[7:0] A,B;input cin;assign {cout,SUM}=A+B+cin;endmodule【例8.20】2选1多路选择器的仿真`timescale 1ns/1nsmodule mux_tp;reg a,b,sel;wire out;- 29 - 程序文本MUX2_1 m1(out,a,b,sel); //调用待测试模块initialbegina=1'b0; b=1'b0; sel=1'b0;#5 sel=1'b1;#5 a=1'b1; el=1'b0;#5 sel=1'b1;#5 a=1'b0; b=1'b1; el=1'b0;#5 sel=1'b1;#5 a=1'b1; b=1'b1; sel=1'b0;#5 sel=1'b1;endinitial $monitor($time,,,"a=%b b=%b sel=%b out=%b",a,b,sel,out);endmodulemodule MUX2_1(out,a,b,sel); //待测试的2选1MUX模块input a,b,sel;output out;not #(0.4,0.3) (sel_,sel); //#(0.4,0.3)为门延时and #(0.7,0.6) (a1,a,sel_);and #(0.7,0.6) (a2,b,sel);or #(0.7,0.6) (out,a1,a2);endmodule【例8.21】8位计数器的仿真`timescale 10ns/1nsmodule count8_tp;reg clk,reset; //输入激励信号定义为reg型wire[7:0] qout; //输出信号定义为wire型parameter DELY=100;counter C1(qout,reset,clk); //调用测试对象always #(DELY/2) clk = ~clk; //产生时钟波形initialbegin //激励波形定义clk =0; reset=0;- 30 -王金明:《Verilog HDL程序设计教程》#DELY reset=1;#DELY reset=0;#(DELY*300) $finish;end//结果显示initial $monitor($time,,,"clk=%d reset=%d qout=%d",clk,reset,qout);endmodulemodule counter(qout,reset,clk); //待测试的8位计数器模块output[7:0] qout;input clk,reset;reg[7:0] qout;always @(posedge clk)begin if (reset) qout<=0;else qout<=qout+1;endendmodule【例9.1】基本门电路的几种描述方法(1)门级结构描述module gate1(F,A,B,C,D);input A,B,C,D;output F;nand(F1,A,B); //调用门元件and(F2,B,C,D);or(F,F1,F2);endmodule(2)数据流描述module gate2(F,A,B,C,D);input A,B,C,D;output F;assign F=(A&B)|(B&C&D); //assign持续赋值endmodule(3)行为描述module gate3(F,A,B,C,D);input A,B,C,D;output F;- 31 - 程序文本reg F;always @(A or B or C or D) //过程赋值beginF=(A&B)|(B&C&D);endendmodule【例9.2】用bufif1关键字描述的三态门module tri_1(in,en,out);input in,en;output out;tri out;bufif1 b1(out,in,en); //注意三态门端口的排列顺序endmodule【例9.3】用assign语句描述的三态门module tri_2(out,in,en);output out;input in,en;assign out = en ? in : 'bz;//若en=1,则out=in;若en=0,则out为高阻态endmodule【例9.4】三态双向驱动器module bidir(tri_inout,out,in,en,b);inout tri_inout;output out;input in,en,b;assign tri_inout = en ? in : 'bz;assign out = tri_inout ^ b; endmodule【例9.5】三态双向驱动器module bidir2(bidir,en,clk);inout[7:0] bidir;input en,clk;reg[7:0] temp;assign bidir= en ? temp : 8'bz; always @(posedge clk)begin- 32 -王金明:《Verilog HDL程序设计教程》if(en) temp=bidir;else temp=temp+1;endendmodule【例9.6】3-8译码器module decoder_38(out,in);output[7:0] out;input[2:0] in;reg[7:0] out;always @(in)begincase(in)3'd0: out=8'b11111110;3'd1: out=8'b11111101;3'd2: out=8'b11111011;3'd3: out=8'b11110111;3'd4: out=8'b11101111;3'd5: out=8'b11011111;3'd6: out=8'b10111111;3'd7: out=8'b01111111;endcaseendendmodule【例9.7】8-3优先编码器module encoder8_3(none_on,outcode,a,b,c,d,e,f,g,h); output none_on;output[2:0] outcode;input a,b,c,d,e,f,g,h;reg[3:0] outtemp;assign {none_on,outcode}=outtemp;always @(a or b or c or d or e or f or g or h)beginif(h) outtemp=4'b0111;else if(g) outtemp=4'b0110;else if(f) outtemp=4'b0101;else if(e) outtemp=4'b0100;else if(d) outtemp=4'b0011;else if(c) outtemp=4'b0010;- 33 - 程序文本else if(b) outtemp=4'b0001;else if(a) outtemp=4'b0000;else outtemp=4'b1000;endendmodule【例9.8】用函数定义的8-3优先编码器module code_83(din, dout);input[7:0] din;output[2:0] dout;function[2:0] code; //函数定义input[7:0] din; //函数只有输入端口,输出为函数名本身if (din[7]) code = 3'd7;else if (din[6]) code = 3'd6;else if (din[5]) code = 3'd5;else if (din[4]) code = 3'd4;else if (din[3]) code = 3'd3;else if (din[2]) code = 3'd2;else if (din[1]) code = 3'd1;else code = 3'd0;endfunctionassign dout = code(din); //函数调用endmodule【例9.9】七段数码管译码器module decode47(a,b,c,d,e,f,g,D3,D2,D1,D0);output a,b,c,d,e,f,g;input D3,D2,D1,D0; //输入的4位BCD码reg a,b,c,d,e,f,g;always @(D3 or D2 or D1 or D0)begincase({D3,D2,D1,D0}) //用case语句进行译码4'd0: {a,b,c,d,e,f,g}=7'b1111110;4'd1: {a,b,c,d,e,f,g}=7'b0110000;4'd2: {a,b,c,d,e,f,g}=7'b1101101;4'd3: {a,b,c,d,e,f,g}=7'b1111001;4'd4: {a,b,c,d,e,f,g}=7'b0110011;4'd5: {a,b,c,d,e,f,g}=7'b1011011;- 34 -王金明:《Verilog HDL程序设计教程》4'd6: {a,b,c,d,e,f,g}=7'b1011111;。

verilog hdl语法书籍经典

verilog hdl语法书籍经典Verilog HDL是一种硬件描述语言,用于设计数字电路和系统。

它是一种高级语言,可以用于描述电路的行为和结构。

Verilog HDL语法书籍是学习Verilog HDL的必备工具之一。

在这篇文章中,我们将介绍一些经典的Verilog HDL语法书籍。

1.《Verilog HDL: A Guide to Digital Design and Synthesis》这本书是Verilog HDL的入门书籍,适合初学者。

它详细介绍了Verilog HDL的语法和基本概念,包括模块、端口、数据类型、运算符、控制结构等。

此外,它还介绍了如何使用Verilog HDL进行数字电路设计和综合。

这本书是学习Verilog HDL的好起点。

2.《Verilog HDL Synthesis: A Practical Primer》这本书是一本实用的Verilog HDL综合指南。

它介绍了如何使用Verilog HDL进行综合,包括综合的基本概念、综合工具的使用、综合优化等。

此外,它还介绍了如何使用Verilog HDL进行时序约束和时序分析。

这本书对于想要深入了解Verilog HDL综合的人来说是非常有用的。

3.《Verilog HDL: Digital Design and Modeling》这本书是一本全面的Verilog HDL教程,适合有一定经验的人。

它详细介绍了Verilog HDL的语法和概念,包括模块、端口、数据类型、运算符、控制结构、任务和函数等。

此外,它还介绍了如何使用Verilog HDL进行数字电路设计和仿真。

这本书对于想要深入了解Verilog HDL的人来说是非常有用的。

4.《Verilog HDL: A Comprehensive Guide to Digital Electronic Design and Automation》这本书是一本综合性的Verilog HDL教程,适合有一定经验的人。

verilog语言参考五

y fopen 和$fclose

$fopen(“FileName”);

{Return an integer}

$fclose(Mcd);

$fopen 是一个系统函数,它可以打开文件为写文件做准备。

而$fclose也是一个系统函数,它关闭由 $fopen 打开的文件。

以上8个系统任务均为常用的定时检查系统任务。这些专用的系统任务只能在specify block(指定块)里被调用,详细说明请参阅后面的材料。

y Value Change Dump Tasks 储存数值变化的系统任务 1) $dumpfile(“FileName”); 2) $dumpvars[( Levels, ModuleOrVariable,...)]; 3) $dumpoff; 4) $dumpon; 5) $dumpall; 6) $dumplimit( FileSize); 7) $dumpflush;

81

7) $dist_t( Seed, DegreeOfFreedom); 8) $dist_uniform( Seed, Start, End); 当重复调用上述函数时,根据不同概率分布的随机数产生函数条件返回其相应的随机数 序列。若伪随机序列的源种相同,则伪随机序列也总是一样的。请参考关于概率与统计 理论的教科书,详细了解其中分布函数及其应用部分。

y $scope and $showscopes $scope( ModuleInstance); $showscopes[( N)];

本系统命令用于在交互模式中设置和显示当前范围,若给定 N 并为非零,则还显示下面的范 围。

y $key, $nokey, $log and $nolog $key[(“FileName”)]; $nokey; $log[(“FileName”)]; $nolog;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1.0 Verilog Synthesis Methodology Finbarr O’Regan (finbarr@ee.ucd.ie) October 2001Synthesis is a contraint driven process i.e. the synthesis script needs timing constraintsFollow the following methodology for best results1.Draw a simple block diagram, labelling all signals, widths etc.2.Draw a timing diagram with as much detail as possible3.Code the HDL according to the synthesizable templates4.Do a quick,low effort,compile-just to see if it is synthesizable before pare this to the block dia-gram. Look at the inference report:•count the number of flip flops - is it the same as the number of flip flops in the code.•check for latches - did you want them. If not, latches are inferred in combinational procedures - the inferrence report tells you which combinational procedure and the name of the latch.Fully specify all variables in all cases to eliminate latches.•Check the case statement inferrence. Was it full/parallel?•Check any incomplete event list warnings?•Check to see if there are any combinational feedback loops (typically only after a compile). Combinational feed-back loops can be identified by the signal names in the timing loop.•Check the schematic - any ports unconnected?•Check to see if Designware and Ambitware components have been built correctly.Are these the components that you wanted? How many did you want?•Never ignore any warning that the synthesis tool flags. All warnings need to be understood and typically signed off.5.Simulate and compare with the timing diagram•If your design doesn’t meet timing by more than10%of the clock period,then go back to the code.If you are within 10% of the clock period, then try a different compile strategy.2.0 Synthesizeable Templates 2.1 Combinational Logicab c// Using a reg// -----------------------------wire a,b;reg c;always @ (a or b)c = a & b;// Using a wire// -----------------------------wire a,b,c;assign c = a & b;// using a built in primitive (without instance name)// -----------------------------reg a,b;wire c;and (c,a,b); // output is always first in the list// using a built in primitive (with instance name)// -----------------------------reg a,b;wire c;and u1 (c,a,b); // output is always first in the list// if c is an output// -----------------------------output c;reg a,b;assign c = a & b;b2.2 Multiplexers2.2.1 Multiplexer using a procedure2.2.2 Multiplexer using the ternary operator2.2.3 Multiplexer using the case statement// 1. using an always always@(a or b or sel) if (sel == 1’b1) c = a; else c = b;a b sel1Use default assignments to prevent latches:every// 2. using the ternary operator wire c = sel ? a : b;// 3. using the case statement always @ (a or b or sel) case (sel) 1’b1: c = a; 1’b0: c = b; endcasea bsel10cc2.3 Priority Decoders2.3.1 Priority Decoder using a case statement// 1. using a case statement always @ (sl or a or b or c)case (sel)2’b11: d = a;2’b10: d = b;default: d = c;endcase1. Both case and if statements result in priority structures.2. The order of the variables determines the priorityb adc sel2’b112’b10==101022.3.2 Priority Decoder using an if/else statement// 2. using an if statement always @ (sl or a or b or c)if (sel == 2’b11)d = a;else if (sel ==2’b10)d = b;elsed = c;b adc sel2’b112’b10==101022.4 Parallel Priority Decoders2.4.1 Parallel Priority Decoders Using a Synthesis Directive// using a synthesis directive always @ (sl or a or b or c)case (sel) // parallel_case2’b11: d = a;2’b10: d = b;default:d = c;endcaseb ac sel2’b112’b102’b0x d22.5 Bus Logic, Splitting and Reordering 2.5.1 Bus Enablingenable44c[3:0]d[3:0]// A1. using a wirewire [3:0] d = ({4{enable}} & c); // A2. using a regreg [3:0] d;always @ (c or enable)d = c & {4{enable}};2.5.2 Bus Concatenationa[3]b[3] e = {a[1],b[3:2]}// B1. using a wirewire [2:0] e = {a[1],b[3:2]};// B2. using a reg reg [2:0] e;always @ (a or b) e = {a[1],b[3:2]};b[2]b[1]b[0]a[2]a[1]a[0]e[2]e[1]e[0]2.5.3 Bus Replicationa[0]a[1]b[0] b[1] b[2] b[3]// bus replication wire [1:0] a;wire [3:0] b; assign b = {2{a}};2.6 Comparators44c[3:0]d1a[3:0]// 1. using a wire wire d;assign d = (a == c);// 2. using a reg reg d;always @ (a or c) d = (a == c);=2.7 D Type Flip Flops// 1. positive edge triggered D flip flop always @ (posedge clock)q <= d;// 2. negative edge triggered D flip flop always @ (negedge clock)q <= d;dqclockdqclockUse non-blocking assignments (<=) in clocked procedures.2.8 Resettable D Type Flip Flops// 1.synchronously resettable D flip flop always @ (posedge clock)if (reset)q <= 1’b0;elseq <= d;// 2. asynchronously resettable D flip flop // (active high async reset)always @ (posedge clock or posedge reset)if (reset)q <= 1’b0;elseq <= d;dqclockreset1’b0dqclockreset// 3. asynchronously resettable D flip flop// (active low reset)always @ (posedge clock or negedge reset)if (~reset)resetq <= 1’b0;elseq <= d;d qclock2.9 Data Enabled and Clock Gated Flip Flops// 1. data enabled flip flop always @ (posedge clock)if (enable)q <= d;// 2. D flip flop with gated clock wire gclk = (clock && enable);always @ (posedge gclk)q <= d;enable signal must be glitch freed qclockenabledqclock enablegclk2.10 Latches// 1. latchalways @ (enable or d) if (enable) q = d;// 2.resettable latchalways @ (enable or d or reset) if (reset)q = 1’b0;else if (enable)q = d;dqenableedqenableresete2.11 Tri-state Driversenabled y// 1. using a reg reg y;always @ (d or enable) if (enable)y = d;elsey = 1’bz;// 2. using a wire wire y;assign y = enable ? d : 1’bz;// 3. using a primitive bufif1 (y,d,enable);2.12 Counter3bit asynchronously resettable counter which counts 0,1,2,3,4,5,// 3 bit asynchronously resettable // partial range counteralways @ (posedge clock or posedge reset)if (reset)count <= 3’b0;elseif (count == 3’b101)count <= 3’b0;elsecount <= count + 3’b001;countclockenable3’b000103’b0013’b101=33reset2.13 Enabled Shift Registermodule enabled_shift_reg (clock,enable,data_in,data_out);input clock;input enable;input [3:0] data_in;output [3:0] data_out;reg [3:0] data_out;reg [3:0] shift_reg_1;reg [3:0] shift_reg_2;reg [3:0] shift_reg_2;always @ (posedge clock) if (enable) beginshift_reg_1 <= data_in;shift_reg_2 <= shift_reg_1; shift_reg_3 <= shift_reg_2; data_out <= shift_reg_3; end endmoduleenableclock data_in data_out2.14 Unsigned Adders and MultipliersNote that the * and + and - signs give you unsigned arithmetic. If you need signed arithmetic, you may need special instaces recognizable to the synthesis tool.•Adding two five bit numbers gives a siz bit result (the extra bit is the carry out bit).•The multiplication of two number means that the output is twice the width of the inputs.wire [5:0] c = a + b;wire [11:0] e = c * d;abcde5566123.0 Coding GuidelinesThese coding guidelines assume that you are able to write correct synthesizeable code. You can always check the synthesizeablilty of your code by parsing it using the synthesis tool.•Use non-blocking assignments (<=) in clocked procedures. Don’t use blocking assignments (=).always @ (posedge clock)q <= d;•Use blocking assignments (=) in combinational procedures:always @ (a or b or sl)if (sl)d = a;elsed = b;•Make sure that the event lists are completealways @ (a or b) // this event list is missing signal slif (sl)d = a;elsed = b;•Take care of indentation. Develop your own identation guidelines and stick to them. Make sure others can read them. It helps readability and debugging greatly if it is done properly.•Comment code properly. The theory about good commenting is that you should be able to remove all functional code and the comments remaining should almost document the block you are designing.// example of bad comments// add a and b togetheralways @ (a or b)c = a + b;// Good commenting// 8 bit unsigned adder for data signals ‘a’ and ‘b’// output is sent to UART2always @ (a or b)c = a + b;•Always completely specify literals.always @ (c)if (c == 4’b0101)a = 2’bxx;elsea = 2’b10;•Use named port mapping when instantiating.state_machine u1 (.sm_in (in1),.sm_clock (clk),.reset (reset),.sm_out (data_mux));•Don’t make the code any more complicated than it needs to be. Your priorities should be correctness, then read-ability and finally code efficiency.4.0 State Machine Guidelines4.1 Guidelines•Draw a state diagram.•Label the states.•Allocate state encoding.•Label the transition conditions.•Label the output values.•Use parameters for the state variables.•Use two procedures (one clocked for the state register and one combinational for the next state logic and the out-put decode logic).•Use a case statement in the combinational procedure.•Have a reset strategy (asynchronous or synchronous).•Use default assignments and then corner cases.•Keep state machine code separate from other code (i.e. don’t mix other logic in with the state machine clocked and combinational procedures).4.2 State DiagramIDLERUN PAUSE FINISHstart transmitwaitstop ack = 1’b0offline = 1’b1online = 1’b0ack = 1’b0offline = 1’b0online = 1’b1ack = 1’b1offline = 1’b0online = 1’b1ack = 1’b1offline = 1’b0online = 1’b1state encodingstate label output values 2’b002’b012’b102’b11transition conditionstop4.3 State Machine Verilog Codemodule state_machine (clock,reset,start,transmit,wait,stop,ack,offline,online); // parameter declarationsparameter pIDLE = 2’b10; // state labels and state encodingparameter pRUN = 2’b00;parameter pPAUSE = 2’b01;parameter pFINISH = 2’b11;// IO declaration sectioninput clock;input reset;input start, transmit, wait, stop;output ack, offline, online;// interal variables declaration sectionreg [1:0] state, next_state;reg ack, offline, online;// clocked procedure with synchronous resetalways @ (posedge clock)if (reset) // reset strategystate <= pIDLE;elsestate <= next_state;// combinational procedure with case statement and output logicalways @ (start or transmit or stop or wait or state)beginnext_state = state; // default assignment to state and output variablesack = 1’b0;offline = 1’b0;online = 1’b1;case (state)pIDLE:beginoffline = 1’b1;online = 1’b0;if (start)next_state = pRUN;endpRUN:beginif (wait)next_state = pPAUSE;if (stop)next_state = pFINISH; // this has priority over the wait transition endpPAUSE:beginack = 1’b1;if (transmit)next_state = pRUN;if (stop)next_state = pFINISH;endpFINISH:ack = 1’b1;endcaseendendmodule。