基于DSP和AVR单片机的主从式双CPU导航计算机

基于DSP和单片机的双CPU数据处理系统

基于DSP和ARM的车载组合导航计算机设计

收稿日期:2010-08-08作者简介:龚柏春(1987—),男,江西南昌人,硕士研究生,主要研究方向为惯性导航与组合导航。

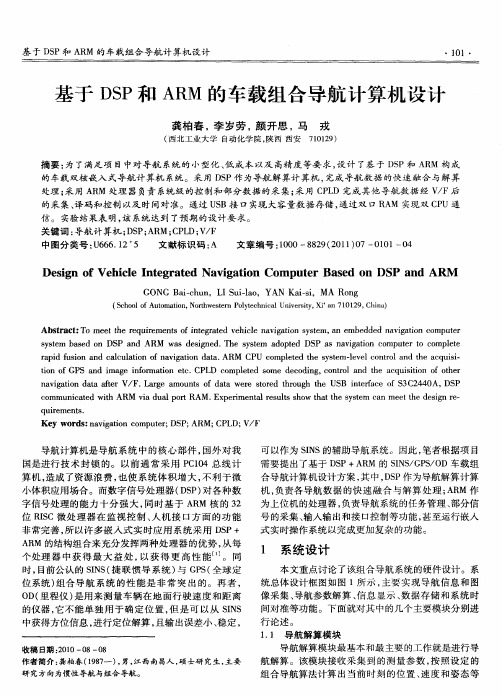

基于DSP 和ARM 的车载组合导航计算机设计龚柏春,李岁劳,颜开思,马戎(西北工业大学自动化学院,陕西西安710129)摘要:为了满足项目中对导航系统的小型化、低成本以及高精度等要求,设计了基于DSP 和ARM 构成的车载双核嵌入式导航计算机系统。

采用DSP 作为导航解算计算机,完成导航数据的快速融合与解算处理;采用ARM 处理器负责系统级的控制和部分数据的采集;采用CPLD 完成其他导航数据经V /F 后的采集、译码和控制以及时间对准。

通过USB 接口实现大容量数据存储,通过双口RAM 实现双CPU 通信。

实验结果表明,该系统达到了预期的设计要求。

关键词:导航计算机;DSP ;ARM ;CPLD ;V /F中图分类号:U666.12+5文献标识码:A 文章编号:1000-8829(2011)07-0101-04Design of Vehicle Integrated Navigation Computer Based on DSP and ARMGONG Bai-chun,LI Sui-lao,YAN Kai-si,MA Rong(School of Automation,Northwestern Polytechnical University,Xi an 710129,China)Abstract:To meet the requirements of integrated vehicle navigation system,an embedded navigation computer system based on DSP and ARM was designed.The system adopted DSP as navigation computer to complete rapid fusion and calculation of navigation data.ARM CPU completed the system-level control and the acquisi-tion of GPS and image information etc.CPLD completed some decoding,control and the acquisition of other navigation data after V /F.Large amounts of data were stored through the USB interface of S3C2440A,DSP communicated with ARM via dual port RAM.Experimental results show that the system can meet the design re-quirements.Key words:navigation computer;DSP;ARM;CPLD;V /F 导航计算机是导航系统中的核心部件,国外对我国是进行技术封锁的。

DSP与单片机构建双CPU平台的方案研究

MOVS ON,5 H; 串口方式 l每一 帧 1 C #0 置 , 0位数据 , 允许

接收

MOVP ON。 8 H; 置 S C #0 设 MOD I =

ห้องสมุดไป่ตู้

V 50 C 4 2波 特 率 /C 1波 特 率 = (9 5 /2 0 ) 5 3 21 6 45 9

S TM# RGR2。 P Al S S S

S M# D 0 S S 1 T 3 0 H,P D ; 内部采样率发生器时钟 由 C U驱动 P

C 1 始化 : 5 初

M OV TMOD, 0H #2 MOVTL , F 1 #F H

这两种数 据多级缓 冲方式使 得数据搬移 和片外数 据通信能够 同时进行。 (2) 控制通路 负责 内部时钟产生 , 帧同步信号产生 , 信号控制和多通道 选择。另外.还具有 向 C U发送 中断信号 P 和向 D MAC发送 同步事件 的功能。MC S B P时钟和帧 1同步信

(. 1广州市广播 电视大学, 广东 广州 5 0 9 ;2上海交通大学, 101 . 上海 2 0 4 ) 0 2 0

【 摘 要】 基于 嵌入式系 统发展的需 将D P 要, S 和单片 成双C U处理器平台, 充分利用D P 机构 P 可以 S 对大容量数据和复

杂 算法的处理能力 , 以及单 片机接 口的控制 能力。 本文提 出 了T 3 0 C 4 2 S 与 A 8 C 1 片机通信的三种设计方案 。 MS2 V 50 D P T 9 5单 利

【 关键词 】 单片 D P通信 机; S ; 【 中图分类号 】 T 26 P1 【 文献标识码 】 A

【 文章编 号 】 10—63 08 6 8 — 3 03 27( 0) — 0 0 2 0

一种基于DSP内核和FPGA内核的双核数字式控制板

专利名称:一种基于DSP内核和FPGA内核的双核数字式控制板

专利类型:实用新型专利

发明人:蔡清源,余鹏鹏,何月朗,曹骥,曹政

申请号:CN202122006056.6

申请日:20210824

公开号:CN215642313U

公开日:

20220125

专利内容由知识产权出版社提供

摘要:一种基于DSP内核和FPGA内核的双核数字式控制板,包括PCB板,PCB板上设置有线性电源接口、DSP内核控制结构、FPGA内核控制结构、AD采样结构以及通信结构,DSP内核控制结构包括DSP最小系统、DSP仿真器接口以及随机存储器,用于实现程序烧写以及最大2M数据缓存存储功能;FPGA内核控制结构包括FPGA电路、FPGA程序存储器、FPGA仿真器接口,用于实现FPGA烧写和FPGA程序存储功能;AD采样结构包括AD并行采样装置、切换采样电路以及64路采样输入接口、64路PWM输出接口和32路预留输出控制口,用于实现64路采样;以及通信结构包括以太网通信模块和以太网接口,用于与外部通信。

本实用新型的有益效果是:PWM通道数量多,周期值灵活,占空比,死区,接口丰富,可并行处理事件。

申请人:浙江杭可科技股份有限公司

地址:311251 浙江省杭州市萧山经济技术开发区桥南区块高新十一路77号

国籍:CN

代理机构:杭州天正专利事务所有限公司

更多信息请下载全文后查看。

基于DSP和FPGA双CPU架构的导航微机系统

Ab s t r a c t : I n o r d e r t o me e t t h e d e v e l o p me n t O f t h e i n e r t i a l s y s t e m ,a n e w k i n d o f n a v i g a t i o n c o mp u t e r wi t h t h e c h a r - a c t e r i s t i c s o f s ma l l s i z e,l o w p o w e r ,l o w c o s t a n d h i g h p e f r o r ma n c e w a s p r e s e n t e d i n t h i s p a p e r .T h e n a v i g a t i o n

基于DSP和单片机的双CPU导航计算机设计

542003.4/下半月 www.eepw.com.cn引言惯性及组合导航技术的不断发展和成熟,使得导航技术向更宽的应用领域渗透,比如战术导弹、智能炸药等。

这些微小型应用领域对导航系统提出了体积小、功耗低、成本低等要求。

微惯性测量组件(MIMU-Micro InertialMeasurement Unit)的出现使导航技术在这些微小型领域应用成为可能。

因此,承担导航系统运算任务的导航计算机的微型化,成为整个系统微型化的关键。

目前,惯性机载、舰载导航系统中,导航计算机大多以通用计算机为平台,其系统体积大、功耗大、成本高,无法用于微小型应用场合。

因此应用现代芯片发展成果,研制并开发基于其它微处理器的导航计算机具有重要的意义和应用价值。

本文针对导航系统微型化的要求,以DSP为核心处理器,设计了一种双CPU、主从式体系结构,小体积、低成本、低功耗的导航计算机。

系统组成随着导航技术的发展,导航系统已经从单一的捷联惯性系统(INS)发展到INS/GPS组合导航及多传感器数据融合导航系统,这要求导航计算机在保证导航运算速度和精度的同时,具有较丰富的外设接口,方便与外部多传感器进行数据通信。

分析导航系统功能及特点,其与一般的数字信号采集与处理类似,将其分为3部分:数据采集部分,包括采集惯性传感器、GPS、磁航向仪等的输出信号和数据;导航参数运算部分,包括初始对准、误差补偿、卡尔曼滤波等;数据输出部分,主要是输出计算后的导航参数。

如果所有的这些功能都由一个CPU来完成,CPU在进行运算的同时,还要兼顾系统控制和数据I/O,并响应频繁的中断,必然降低系统运行效率,所以,为兼顾系基于DSP和单片机的双CPU导航计算机设计南京航空航天大学自动化学院导航研究中心 薛志宏 刘建业图1系统结构框图本文2002年2月21日收到,3月17日收到修改稿。

薛志宏:硕士研究生,研究方向卫星导航、捷联惯性组合导航与DSP系统。

统数据I/O功能和运算功能,将两者合理的分配给两个处理器,同时保证双CPU间高速的数据通信,是理想的提高系统性能的方法,系统设计即采用单片机+DSP的方案。

双CPU结构捷联导航数据处理系统硬件设计的开题报告

双CPU结构捷联导航数据处理系统硬件设计的开题报告一、选题依据随着我国航空事业的发展,航空导航系统正在迅速更新换代,飞行器导航系统日趋复杂,对导航数据处理系统的性能也提出了更高的要求。

传统的单CPU结构已经无法满足现代导航系统的需求,因此双CPU结构的导航数据处理系统开始受到关注。

本课题将着重研究双CPU结构捷联导航数据处理系统的硬件设计,包括系统整体架构、CPU选择、外围设备接口设计等,旨在提高导航数据处理系统的性能和稳定性,为航空导航技术的进一步发展提供支持。

二、研究内容本课题的研究内容主要包括以下几个方面:1. 系统整体架构设计根据导航系统的需要,设计具有双CPU结构的导航数据处理系统,确定系统的整体架构和各个板卡之间的连接方式,保证系统的稳定性和性能。

2. CPU选择根据导航数据处理系统的需求和现有的CPU技术,选择最适合的处理器,通过综合考虑运算速度、存储器大小、功耗等因素,尽可能满足导航系统对数据处理的要求。

3. 外围设备接口设计设计基于通用接口的外围设备接口,实现数据的输入、输出和存储,同时与导航系统的其它部分连接,保证数据处理系统的协同工作。

4. 硬件测试通过各种型号的模拟器对硬件进行测试,验证系统的性能和稳定性,确保导航数据处理系统的合格率和可靠性。

三、研究意义本课题的研究意义在于:1. 提高航空导航技术的水平作为航空导航系统中的核心部分,导航数据处理系统的性能和稳定性对系统的运行和安全有着至关重要的影响。

本课题的研究结果可以提高导航数据处理系统的性能和稳定性,从而提高航空导航技术的水平。

2. 推动CPU技术的进步导航数据处理系统需要大量处理器来完成数据处理任务,因此对CPU技术的需求也很高。

本课题的研究可以促进CPU技术的进步,推动信息技术的发展。

3. 为国防事业提供支持航空导航系统是军事技术领域的重要组成部分,导航数据处理系统的性能和稳定性直接关系到作战效果。

本课题的研究可以提高导航数据处理系统的性能和稳定性,为国防事业提供支持。

基于DSP的水下机器人组合导航系统设计

基于 D P的水下机器人组合导航系统设计 S

De in o sg f AUV I t g a e Na i t n Sy t m s d o P ne rt d vga i se Ba e n DS o

图 1 组 合 导 航 系 统 总体 设 导 航 运 算 速 度 和 精 度 的 同 时 ,还 要 具 有

丰 富 的外 设 接 口 , 便 与 外 部 多 传 感 器 进 行 数 据 通信 。 方 木文 所 研

2 1 串 口 电路 设 计 .

究 的导 航 计 算 机 采 用 了单 片 机 和 D P 的双 CP 方 案 ,可 以兼 S U 顾 系统 数 据 IO 功 能 和 运 算 功 能 , 现 两 者 合 理 的分 配 , 时保 / 实 同

测 值作 为卡 尔 曼 滤 波 的 量 测 值 ,既 可 以用 精 度 高 的子 系 统 的 信

基。的据 模 于s数 算块 运

2 系统 硬 件 设 计

[! ! j

息 修正 惯 导 误 差 ,又 可 以 用 惯 导 对 动 态 响应 慢 的子 系统 作 补偿 和 校正 , 而综 合 发 挥 各 自优 点 。 从

证 双 CP 间 高 速 的数 据 通 信 。 U 1 系统 结 构 组 成

本 系 统 的 I 和磁 罗 盘 均 以 R 2 2串 口形 式 输 出 数 据 , MU S3

Ke wors: t grt Navg t sem , y d l er aed n ia i Sy t on DSP, MCU, l Kaman Fier l t

微 小 型 自主 水 下 机 器 人 导 航 方 式 作 为 其 关 键 技 术 之 一 , 成 为 近 些 年来 国 内外 研 究 的热 点 。捷 联 惯 性 导 航 是 最 常 见 和 应 用

基于DSP和ARM的车载组合导航计算机设计

De i n o hil n e r t d N a i a i n Co p e s d o sg fVe ce I t g a e v g to m ut r Ba e n DSP n a d ARM

GONG a— h n B ic u ,L u —a , YAN is, MA n IS i o l Ka—i Ro g

s se b s d o P a d ARM s d s n d T e s se a o td DS s n v g t n c mp tr t o lt y tm a e n DS n wa e i e . h y tm d p e P a a ia i o u e o c mp ee g o rp d f s n a d c lu a in o a ia in d t . a i u i n a c l t fn v g t a a ARM P o l td t e s se l v l o t la d t e a q i — o o o C U c mp ee h y tm— e n r n h c u s e c o i t n o S a d i g n o ma in ec C L o l td s me d c d n , o t la d t e a q i t n o t e i fGP n ma e i f r t t . P D c mp ee o e o i g c n r n h c u s i f oh r o o o io

基于DSP的导航计算机硬件设计分析

An a l y s i s o f t h e Na v i g a t i o n Co mp u t e r Ba s e d o n DS P Ha r d wa r e De s i g n

LI U We i Fra bibliotek1 引言

目前在我国的捷联 惯导 系统一 般都 是 I n t e l 系列等 通 用型处理器为硬件核心来处理导航系统产生 的大量 实时的 数据 。伴随着科 技技 术 的发展 , 出现 了运 算能力 极为 强大 的数字信号处理 器 ( DS P ) , 它是专 门为快 速 实现各 种数 字 信号处 理算 法 而设 计 的 , 它 具 有 特 殊 结 构 的微 处 理器 。

C P U 的设计方案 , D S P主要 是 负责导 航数 据 的处理 , 单 片 机负责系统的 I / O接 口和外部接 口设备控制 。 D S P芯 片的选择应该 根据 实际 的应 用 系统来确 定 , 最

使数据 的处 理 速度 大大 提 高。具有 精确 高 、 速 度快 、 成 本

总第 2 8 0期 2 0 1 3 年第 2 期

计 算 机 与 数 字 工 程

Co mp u t e r& Di g i t a l En g i n e e r i n g

Vo 1 . 4 l No . 2

24 8

基 于 DS P的 导 航计 算 机硬 件 设 计 分 析

( Wu h a n Di g i t a l En g i n e e r i ng I n s i t u t e,W u h a n 4 3 0 0 7 4 )

Abs t r a c t Thi s pa p e r d e s i g n b y u s i n g DS P+ M CU d o u b l e CPU a r c h i t e c t ur e p l a n,DS P i s ma i n l y r e s p o n s i bl e f o r d a t a p r o c e s s n g,M CU i s ma i n l y r e s p o n s i bl e f o r t h e s y s t e m i n p u t a n d o u t p u t c o n t r o l ,t o r e a l i z e t h e c o mb i n a t i o n o f c o mp l e me nt a r y a d v a n t a g e s ,a n d g i v e i u l l p l a y t o t he i r s k i l l s . Thi s p a p e r wi l l e x a mi n e t h e d i g i t a l s i g n a l p r o c e s s i n g c h i p i n t h e na v i g a t i o n c o mp ut e r ,a n d c o ns t r u c t na v i g a t i o n c o mp ut e r s y s t e m h a r d wa r e o f t h e n e w me t h o d t hr o u g h t h e M CU ,DS P a nd ma s s c a n p r e p a r e l o g i c d e v i c e K ey W or d s M CU ,DS P,n a v i g a t i o n c o mp u t e r ,AD c o n v e r t e r Cl a s s Nu mb e r TP3 9 ]

基于DSP和单片机的双CPU导航计算机设计

基于DSP和单片机的双CPU导航计算机设计

薛志宏;刘建业

【期刊名称】《导航》

【年(卷),期】2003(039)002

【摘要】结合现代导航技术发展的特点,以DSP作为算法实现核心处理器,以单片机作为数据采集处理器,设计了双CPU结构的导航计算机.文中给出系统整体组成结构的同时,还论述了软、硬件设计中的关键技术.实验证明,强大的数据采集及处理能力,使其可作为纯捷联惯导或是INS/GPS组合导航的实现平台.同时体积的减小、功耗和成本的大大降低,拓展了导航技术的应用领域,对导航系统的微型化具有重要意义。

【总页数】7页(P86-92)

【作者】薛志宏;刘建业

【作者单位】南京航空航天大学210016

【正文语种】中文

【中图分类】TN962

【相关文献】

1.基于DSP和单片机的双CPU导航计算机设计

2.基于DSP和单片机的双CPU导航计算机设计

3.基于DSP和FPGA技术的导航计算机设计与实现

4.基于

DSP+FPGA的导航制导一体化计算机设计5.基于DSP和AVR单片机的主从式双CPU导航计算机

因版权原因,仅展示原文概要,查看原文内容请购买。

实时监控中单片机和DSP相结合的双CPU硬件设计方案

实时监控中单片机和DSP相结合的双CPU硬件设计方案摘要通信电源、机房空调环境集中监控系统主要对通信电源系统中的高低压配电设备、变压器、开关电源、蓄电池、空调、油机等通信机房的电源设备,以及机房环境的温度、湿度、门禁、烟雾等环境因素,进行实时集中化监测、控制与管理。

关键词实时监控;单片机;DSP;双CPU硬件嵌入式微机监控系统是面向用户、面向产品、面向应用的,如果独立于应用自行发展,则会失去市场。

嵌入式处理器的功耗、体积、成本、可靠度、速度、处理能力、电磁兼容性等方面均受到应用要求的制约,这些也是各个半导体厂商之间竞争的热点。

1液压装置的总体布置方式嵌入式微机监控系统应用软件是实现嵌入式微机监控系统功能的关键。

软件要求固化存储,软件代码要求高质量、高可靠度,系统软件的高实时效性是基本要求。

嵌入式微机监控系统一般由以下3个部分构成。

1)嵌入式微机监控系统硬件。

嵌入式微机监控系统硬件包括嵌入式核心芯片、存储器系统以及外部接口。

其中嵌入式核心芯片指嵌入式微控制器、嵌入式数字信号处理器、嵌入式片上系统、嵌人式可编程片上系统;存储器系统包括嵌入式存储器(ROM、FLASH、EPROM),数据存储器等;外部接口包括通用设备接口和I/O接口(A/D、D/A、I/O等)。

2)嵌入式微机监控系统的软件嵌入式微机监控系统的软件主要包括两大部分:嵌入式操作系统和嵌入式微机监控软件。

嵌入式操作系统具有一定的通用性,虽然目前使用的嵌入式操作系统有几十种,但是常用的不过几种,一种操作系统适合于一定的应用范围。

嵌入式操作系统种类多,不同的操作系统具有完全不同的嵌入式应用软件。

3)嵌入式微机监控系统中间层。

硬件层和软件层之间为中间层,也称为硬件抽象层(Hardware Abstract Layer,HAL)或板级支持包(Board Support Package,BSP),它将系统上层软件与底层硬件分离开来,使系统的底层驱动程序与硬件无关,上层软件开发人员无需关心底层硬件的具体情况,根据BSP层提供的接口即可进行开发。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

收稿日期:2003-05-21 作者简介:刘勇(1970-),男,重庆渝北人,高级工程师,主要从事惯性导航技术及系统的研究。

文章编号:1004-2474(2003)05-0456-03基于DSP 和AVR 单片机的主从式双CPU 导航计算机刘 勇(四川压电与声光技术研究所,重庆400060) 摘 要:介绍了一种小体积、低功耗、低价位的高性能导航计算机。

此导航计算机由数字信号处理器(DSP )和A VR 单片机两种CP U 组成,DSP 主要完成数据处理和制导算法运算,A V R 单片机主要完成信息的采集和相关控制,两种CP U 各自充分发挥自己的特点,协调地工作,能出色地完成导航计算机的功能。

关键词:导航计算机;捷联惯性制导;数字信号处理器(DSP );A VR 单片机中图分类号:V 247 文献标识码:APrincipal and Subordinate Navigation Computer with Dual CPUBased on DSP and AVR Single -chip ProcessorLIU Yong(Sichuan Ins titu te of Piezoelectric and Acousto op tic T echnolog y,Ch on gqing 400060,Chin a) Abstract :T his paper pr esents a new kind o f navigat ion co mput er with the cha racter istics of sma ll size,low pow er,low co st and high per for mance.T his computer consist of DSP (Digital Signal P ro cessing )and A V R sing le-chip pr ocessor ,A V R sing le -chip pr o cessor has funct ions o f dat a collected and I /O contr olled et c ;DSP is used t opro cess the data.T he AV R sing le-chip pr ocessor and DSP are desig ned o n t he sam e circuit diag r am to realize the algo rithm of integ r ated nav ig atio n sy st em.Key words :na vig ation computer ;strap -dow n iner tial guidance ;Digit al Signal P ro cessing (D SP );A VR sing le -chip pr ocessor 1 引言随着战术弹、水雷、智能炮弹等小型、低成本战术武器的发展,对小型、低成本的捷联制导系统提出了要求,从而对导航计算机也提出了小体积、低功耗、低价位的要求。

传统的导航计算机大多为专用计算机、通用计算机平台、嵌入式工控机(PC 104)等,它们体积大,功耗大,价格高,不适用于小型制导场合。

随着现代电子技术的发展,出现了运算能力强大的数字信号处理器(DSP )和可以在线编程的AVR 单片机,使设计一种体小价廉、低功耗的导航计算机成为可能。

本文结合基于压电陀螺的捷联制导系统的要求,设计了一种用DSP 和AVR 单片机两种CPU 构成的主从式双CPU 导航计算机。

2 导航计算机总体结构导航计算机是捷联制导系统的中心处理器,它控制输入接口进行模/数转换,信息的摄取,控制输出接口正确发送数据,此外,还有一个繁重的工作,也是很重要的一个工作,即捷联制导计算,它包括初始对准、误差补偿、姿态计算和信息融合等。

要求导航计算机既要有较强的数学运算能力,又要有较灵活的控制功能。

图1为导航计算机硬件组成框图。

DSP 是专为高速数据处理而设计的微处理器,其改进的哈佛结构、先进的多地址/数据总线和多级流水线机制、专用的硬件乘法器、高效的指令集使芯片的指令周期图1 导航计算机硬件组成框图第25卷第6期压 电 与 声 光Vo l .25N o .62003年12月PI EZOEL ECT R ICS &A COU ST OO PT ICSDec.2003降到10ns以下。

先进的制造工艺使其功耗仅有数十毫瓦,体积通常在25m m×25mm左右。

捷联制导系统的数据处理与计算,包括误差补偿、初始对准、垂直水平基准计算、在线校正、滤波等,DSP可很好的完成,但输入/输出涉及与外界进行大量的数据交换和外设控制等I/O操作,这是DSP的弱项,勉强令其完成此工作,则它赖以进行高速数据处理的多级缓冲和高速流水线机制将被频繁打断,同时低速的外设和I/O操作要求在DSP的操作时序中插入大量的等待周期,最终使DSP的优势大大消弱[1]。

那么,数据输入,包括采集IM U的信号、输入初始对准数据、接收系统校正信息等由谁来完成呢?在本导航计算机中,用AVR单片机完成。

AVR单片机通过在单一的时钟周期内执行功能强大的指令,每兆赫兹可以实现1M ips的处理能力,使设计可以优化功耗与速度之间的矛盾。

AVR 核为32个通用工作寄存器与丰富指令集的组合,这种组合机构具备的代码率比完成同样处理能力的常规CISC微控制器要快十倍。

AVR单片机运用了AT MEL公司的高密度、非易失存储器技术。

片内可下载的Flash存储器可以通过SPI串行接口进行在线编程[2]。

它是一种可满足许多要求、具有高度灵活性和低成本的嵌入式微控制器。

这样的单片机完成I/O控制和输入/输出,可以说是得心应手。

3 DSP与A V R单片机协调工作设计 在导航计算机中,采用的DSP是T I公司的TM S320F206[3],F206在5V工作电压下有50ns 的指令周期,片内集成有U ART、SPI总线接口,一个16位定时器,三个外部中断源,32K×16B的可编程Flash存储器,4K×16B可编程数据存储器, 544×16B随机存储器,使导航计算机无需扩展外部ROM和RAM。

同时,F206具有C2XX系列DSP 的低功耗特点。

单片机采用ATM EL公司的90S8151,该型AVR单片机与MCS51单片机的8X51/51引脚兼容,仅复位电平不同,改变复位电路,将使导航计算机更灵活。

90S8151片内有8K字节可在线编程的Flash,512字节SRAM和512字节可在线编程EEPROM;集成有UART、SPI总线接口,可以方便地与多种外设接口。

F206和8151都无HPI口,也就是说,它们内部没有集成双口RAM,那么,它们之间怎么交换信息呢?本导航计算机采用FIFO作为F206和8151沟通信息的桥梁。

硬件连接如图2所示。

图2 F206与8515硬件连接图单片机不断采集的数据放入FIFO中,完成一周期的采样后,产生中断信号,告诉DSP取数,DSP 接到取数指令后,立即把数据取走,并产生中断信号,告诉单片机可以存放采样数据,同时全速处理数据,将处理结果存放到RAM的指定地址,单片机响应中断后,继续采集数据存入RAM中,开始一个新的周期。

就这样DSP与单片机协调有序的运行,完成捷联制导系统的工作。

4 信息输入通道设计输入通道负责压电捷联制导系统的所有信息输入,包括陀螺、加速度计、GPS和里程计等,根据不同的输入信息格式,要设计不同的接口形式。

通常, GPS和里程计的信息为串行数据,利用8151单片机的片上UART进行数据输入;陀螺和加速度计的输出,一般有数字脉冲和模拟电压两种,如果是数字脉冲,用计数器计数后就可进入CPU,计数器的设计就成为输入接口的关键,常用的计数器有74(54) HC193,74(54)LS590,82C53(54)等,用它们设计的计数器还需要译码器、锁存器等,体积大,调试困难。

随着电子技术的发展,PLD、CPLD和FPGA等可编程逻辑器件以其强大的功能得到了普遍应用,根据计数器的功能,用CPLD进行设计,不但体积小,而且可靠性大大提高。

如果IM U的输出是模拟电压,就要用A/D转换器把模拟信号转换为数字信号,才能进入CPU。

A/D转换器件非常关键,它的转换精度直接关系到计算机摄入IM U信息的准确性和可信度。

压电捷联制导系统所用陀螺和加速度计的输出为模拟电压,导航计算机采用A/D进行数据转换,根据制导系统精度要求,使用了BB公司的16位A/D转换器ADS7805。

ADS7805具有±10V的宽电压输入范围,内置采样保持和电压基准,信号捕获快(2 s),典型数 第6期刘 勇等:基于DSP和A VR单片机的主从式双CP U导航计算机457 据转换时间为7.6 s,它具有1×16B(或2×8B)并行数据接口,方便与微处理器连接(见图3)。

ADS7805拥有一个模拟输入通道,而系统要求至少需要6个通道,怎么办?通常是采用多路模拟开关,但模拟开关频繁的通断,不但产生额外噪声,而且影响系统的动态特性。

为了解决这个矛盾,凡是具有动态输入特性的通道独立使用一个A/D,低频特性的所有通道共用一个A /D,形成A/D转换阵列。

图3 A /D 转换示意图5 信息输出通道设计制导参数的输出是必不可少的,根据不同的要求,也有模拟电压输出和数字接口输出等多种形式。

数字接口有串行接口(RS232、RS422、RS485)、并行接口、现场总线等等,相应的集成功能芯片很多,设计简单。

模拟输出要将数字量转换为模拟量,D /A 转换器不可少,导航计算机采用A/D 公司的14位D/A 转换器,它具有标准的片选和写逻辑,片内集成双缓冲数据寄存器,可以一次(14位)或两次(8位+6位)输入数据,与8位和16位微处理器都可以方便接口。

多通道的输出用M AXIM 公司的模拟开关MAX368完成,它的最大特点是具有数据锁存器,可以把通道锁存,以使输出稳定。

同样,开关的切换会使输出跳动,利用硬件与软件的密切配合,巧妙设计达到输出平滑的目的。

首先,硬件留有富裕通道(空闲通道),当从一个有用通道输出数据后,延时适当的时间,迅速将开关掷于空闲通道,使不同通道的数据跳动发生在空闲通道,能很好地解决数据输出平滑问题。

6 导航计算机的实际应用组织在应用中,导航计算机设计成总线栈接结构,板的大小小于78mm ×78m m 。

主板(见图4(a))包括DSP 、AVR 单片机、FIFO 及少量为CPU 服务的外围电路,具有永久固化特点;扩展板(见图4(b ))包括输入/输出通道、控制电路及其他可选电路。