基于FPGA的通用异步收发器设计(串口通信)

基于fpga的串口设计及实现

基于fpga的串口设计及实现

基于FPGA的串口设计及实现是一个涉及数字电路设计和通信协

议的复杂课题。

首先,让我们从串口通信的基本原理开始。

串口通信是一种通过串行传输数据的通信方式,它使用一个或

多个数据线(通常是一对)来逐位地传输数据。

常见的串口通信标

准包括RS-232、RS-485、UART等。

在FPGA中实现串口通信,需要

考虑以下几个方面:

1. 串口通信协议选择,根据具体的应用场景和需求,选择合适

的串口通信协议。

例如,UART是一种常见的串口通信协议,它使用

起始位、数据位、校验位和停止位来传输数据。

2. 串口通信接口设计,在FPGA中设计串口通信接口,需要考

虑数据的发送和接收,时钟信号的同步等问题。

通常需要使用FPGA

的IO资源来实现串口通信接口。

3. 串口通信协议的实现,在FPGA中实现选择的串口通信协议,包括数据的发送和接收、时序控制、校验等功能。

这通常需要使用Verilog或VHDL等硬件描述语言进行开发。

4. 硬件调试和验证,设计完成后,需要进行硬件调试和验证,包括时序分析、波形仿真等工作,确保串口通信的稳定和可靠。

在实际的FPGA串口设计中,还需要考虑时钟频率、数据传输速率、数据格式、数据校验、中断处理等问题。

此外,还需要考虑FPGA与外部设备的接口,如与传感器、显示器、存储器等设备的接口设计。

总之,基于FPGA的串口设计及实现涉及到硬件设计、数字电路设计、通信协议等多个方面的知识,需要综合考虑各种因素,进行全面的设计和实现。

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

基于FPGA的串口通信设计

基于FPGA的串口通信设计引言:串口通信是现代计算机通信系统中的常见通信方式。

它可以在计算机和外部设备之间传输数据,具有低成本、简单易懂、可靠性高等特点。

然而,在一些应用场景下,传统的软件串口通信无法满足需求,因此使用FPGA来实现硬件串口通信变得愈发重要。

本文将重点介绍基于FPGA的串口通信设计,包括串口通信原理、FPGA硬件实现以及设计注意事项。

一、串口通信原理:串口通信的原理很简单,将数据通过一根导线(或多根导线)依次发送和接收。

它使用一个起始位、数据位(常为8位)、奇偶校验位(可选)和一个或多个停止位来组成一个数据帧。

发送数据时,串口将数据帧从最低位开始逐位发送,并在每位发送完毕后根据波特率发送下一位。

接收数据时,串口根据波特率和起始位检测到数据的到来,并从起始位开始逐位接收。

二、FPGA硬件实现:FPGA可以通过其可编程逻辑单元(FPGA的核心组件)实现硬件串口通信。

下面是基于FPGA的串口通信设计主要步骤:1.FPGA引脚分配:首先,选择合适的FPGA芯片,并确定通信所需的引脚数量。

然后,根据引脚分配表将引脚与FPGA的可编程逻辑单元相连接。

2.接口电平转换:在FPGA和外设之间可能存在电平不匹配的情况。

为了实现正确的数据传输,需要使用电平转换电路进行适配。

3.帧同步信号生成:FPGA需要生成适当的时钟信号和帧同步信号,以使数据能够正确地按位传输和接收。

帧同步信号指示数据的起始和终止。

4.数据传输实现:FPGA需要根据串口通信原理,按照波特率逐位地发送和接收数据。

在发送数据时,FPGA将数据从最低位开始逐位输出到引脚,并根据起始位、数据位、奇偶校验位和停止位生成完整的数据帧。

在接收数据时,FPGA根据时钟信号和帧同步信号,逐位地接收到达的数据,以获得完整的数据帧。

5.数据校验和处理:FPGA可以实现奇偶校验的功能,以检测接收到的数据是否正确。

此外,还可以在FPGA内部对接收到的数据进行处理,例如数据解码、错误检测等。

基于FPGA实现CRC校验功能的通用异步串口通信

T ONG a .o g.S Xio r n HENG h n . io Z o g ba ( o eeo te t sa dIfr t nS i c ,We a ec es iesy We a 10 0 hn ) C l g f l Mahma c n nomai ce e i o n i nT ah r vri , i n74 0 ,C ia n Un t n

Ab t a t U T i u e d l st e i tr c fRS 2 2,t ba n a c r t e a o sr c : AR s s d wie y a h e a e o - 3 n f o o ti c u ae s r lc mmu i ain o i nc t f o dt aa,asmp e a d p a t a c e o i l n r ci l h me frUAR e in a d x aia in w sp t o w r .C ci e u d n y c s T d s n e l t a u r a d y l r d n a c g ; z o f c

Tas t r 一种应 用 广 泛 的于 短距 离 串行 传 输 rnmie)是 t 接 口, 常用 于 短 距 离 、 速 、 成 本 通 信 中 , 于 常 低 低 基

FG P A实现起来简单, 方便_ 。为保证传输 的可靠 1 ] 性, 就需要对通信过程进行差错控制 , R C C循环冗 余校验模块是一种查错能力强 , 高效, 可靠的方法 , 在

论分析一致 ,达到 了 预期设计的 目 标。提高了通信的速度 、可靠性和效率。 关键 词 :F G C C检验 ; 用异 步收 发器 ; 靠性 P A; R 通 可

基于fpga的串口通信

基于FPGA的串口通信设计学号:姓名:班级:指导教师:电子与控制工程学院一、串行通信系统1.1概述在计算机系统和微机网络的快速发展领域里串行通信在数据通信及控制系统中得到广泛的应用。

UART 即Universal AsynchronousReceiver Transmitter 通用异步收发器 协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议 在实际工业生产中有时并不使用UART的全部功能。

只需将其核心功能集成即可。

波特率发生器、接收器和发送器是UART的三个核心功能模块 利用Verilog-HDL语言对这三个功能模块进行描述并加以整合UART是广泛使用的串行数据传输协议。

UART允许在串行链路上进行全双工的通信。

串行外设用到RS232-C异步串行接口 一般采用专用的集成电路即UART实现。

如8250、8251、NS16450等芯片都是常见的UART器件 这类芯片已经相当复杂有的含有许多辅助的模块 如FIFO有时我们不需要使用完整UART的功能和这些辅助功能。

或者设计上用到了FPGA/CPLD器件那么我们就可以将所需要的UART功能集成到FPGA内部。

使用VHDL或Veriolog -HDL将UART的核心功能集成从而使整个设计更加紧凑、稳定且可靠。

本文应用EDA技术 基于FPGA/CPLD器件设计与实现UART。

通信指人与人或人与自然之间通过某种行为或媒介进行的信息交流与传递从广义上指需要信息的双方或多方在不违背各自意愿的情况下无论采用何种方法使用何种媒质 将信息从某方准确安全传送到另方。

通信在不同的环境下有不同的解释在出现电波传递通信后通信(Communication)被单一解释为信息的传递是指由一地向另一地进行信息的传输与交换其目的是传输消息。

然而通信是在人类实践过程中随着社会生产力的发展对传递消息的要求不断提升使得人类文明不断进步。

在各种各样的通信方式中利用“电”来传递消息的通信方法称为电信(Telecommunication) 这种通信具有迅速、准确、可靠等特点且几乎不受时间、地点、空间、距离的限制 因而得到了飞速发展和广泛应用。

基于FPGA的通用异步收发器设计

基于FPGA的通用异步收发器设计

串行通信要求的传输线少,可靠性高,传输距离远,被广泛应用于计算机和外设的数据交换。

通常都由通用异步收发器(UART)来实现串口通信的功能。

在实际应用中,往往只需要UART的几个主要功能,专用的接口芯片会造成资源浪费和成本提高。

随着FPGA/CPLD的飞速发展与其在现代电子设计中的广泛应用,FPGA/CPLD功能强大、开发过程投资小、周期短、可反复编程、保密性好等特点也越来越明显。

因此可以充分利用其资源,在芯片上集成UART功能模块,从而简化了电路、缩小了体积、提高了可靠性,而且设计时的灵活性更大,周期更短。

鉴于此本文提出了一种采用FPGA实现UART功能的方法,可以有效地解决上述问题。

1 UART的工作原理

UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是广泛使用的异步串行数据传输协议。

在串行通信中,数据以字节为单位的字节帧进行传送。

发送端和接收端必须按照相同的字节帧格式和波特率进行通信。

UART控制器所传输的一帧串行数据包括1位起始位(低电平)、5~8。

基于FPGA的串口通讯电路设计毕业论文

本科学生毕业论文论文题目:学院: 年级:专业:姓名: 学号: 指导教师:基于FPGA勺串口通信电路设计集成电路设计与集成系统i串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持RS-232接口(又称EIA RS-232-C)的通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART),本文设计了一个串口数据采集和处理程序,详细介绍了用Verilog HDL硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用Quartus II软件进行仿真并给出结果,分别验证各个模块的正确性。

本设计还使用基于ALTERA 公司的Cyclone II EP2C5T144芯片的FPGA开发板,在FPGA开发板上实现和PC 通过串口调试软件完成双向通信,不仅要求将开发板的数据显示在PC的串口调试助手软件上,还要求用PC发送数据的ASCII码来驱动电路的8个LED 灯,验证用FPGA实现串行通信的可行性。

关键词串行通信;RS-232; UART ;Verilog HDL ;FPGAAbstractSerial com muni cati on in terface is a widely used com muni cati on in terface. At prese nt, most of processor in tegrated RS-232(EIA RS-232-C) in terface to support UART (Uni versal Asynchronous Receiver/Tra nsmitter) com muni cati on, This thesis desig n a data acquisiti on and treatme nt program. Besides that, the thesis in troduced Baud Rate Generator module、Receiver module、Send module based on Ianguage Verilog HDL and give the results by simulate in Quartus II software. This desig n also uses EP2C5T144 FPGA chip to achieve the two-way com muni cati on by simulate with Quartus II and PC through the serial port debuggi ng software. Not only requires the developme nt board's data displayed in the PC's serial port debugg ing software, also ask ASCII data sent by PC Code to drive eight LED lights, mean while verified the serial com muni cati on with FPGA.Key wordsSerial commu ni catio n; RS-232; UART; Verilog HDL; FPGA摘要 (I)Abstract (II)第1章语言和工具 (2)1.1 Verilog HDL 语言概述 (2)1.2 FPGA 概述 (4)1.3 Quartus II 软件介绍 (8)1.4 FPGA开发板介绍 (9)1.5本章小结 (12)第2章串口通信协议简介 (13)2.1串口通信接口 (13)2.2 RS232通信协议 (13)2.3串口通信时序分析 (15)2.4本章小结 (16)第3章串口通信的VerilogHDL实现 (17)3.1设计功能说明 (17)3.2波特率发生器模块的VerilogHDL实现 (17)3.3发送模块的Verilog HDL实现 (19)3.4接收模块的Verilog HDL 实现 (25)3.5本章小结 (31)第4章串口通信的硬件调试 (32)4.1板级调试说明 (32)4.2下载配置FPGA (33)4.3配置串口调试软件 (35)4.4调试结果 (35)4.5本章小结 (38)结论 (39)参考文献.......................................................... 错误!未定义书签。

基于FPGACPLD的通用异步通信接口UART建模与设计-精品

目录【内容摘要】 (2)【关键词】 (2)一、FPGA (3)(一)FPGA设计流程及概述 (3)(二)自顶向下原理 (4)二、UART (4)(一)UART简述 (4)(二)RS-232串口通信 (4)1.简介 (4)2.实现方案 (5)三、设计软件 (5)(一)Synplify的性能特点 (5)(二)ModelSim的性能特点 (5)四、UART实现原理 (6)(一)UART各个小模块的功能和实现程序 (6)1.信号监测器 (6)2.移位寄存器 (7)3.波特率发生器 (8)4.奇偶校验器 (9)5.总线选择器 (10)6.计数器 (11)(二)UART内核模块状态机的实现 (11)1.有限状态机(FSM)简介 (11)2.数据接收过程 (12)3.数据加载和发送过程 (12)4.UART内核、电路图及仿真图 (13)(三)UART工作流程 (15)1.接收过程 (15)2.发送过程 (16)五、设计小结 (17)[参考文献及相关资料] (17)【Abstract 】 (18)【Key words】 (19)基于FPGA/CPLD的通用异步通信接口UART建模与设计电子信息工程 2003080264廖泽雷指导教师冯昌昆【内容摘要】FPGA/CPLD是大规模集成电路技术发展的产物,是一种半定制的集成电路。

结合计算机软件技术(EDA技术)可以快速、方便地构建数字系统。

FPGA是电子设计领域中最具有活力和发展前途的一项技术,它的影响丝毫不亚于20世纪70年代单片机的发明和使用。

可以毫不夸张地讲,FPGA能完成任何数字器件的功能。

随着EDA软件和硬件描述语言(HDL)的进步, FPGA的开发周期越来越短,产品功能越来越强。

FPGA在复杂逻辑电路以及数字信号处理领域中扮演者越来越重要的角色。

UART(通用异步接受/发送器)是一种短距离串行传输接口。

在数字通信和控制系统中得到广泛应用。

本设计采用了多模块化实现方法,介绍了采用Verilog DHL硬件描述语言来开发基于FPGA/CPLD的通用异步通信接口UART的设计。

基于FPGA的通用异步收发器的设计

基于FPGA的通用异步收发器的设计陈永刚;杨海兴【摘要】随着FPGA/CPLD器件在控制领域的广泛使用,开发嵌于FPGA/CPLD器件内部的通用异步收发器,以实现FPGA/CPLD开发系统与PC机之间的数据通信成为当前FPGA/CPLD领域的一个研究热点.利用Altera公司的Cyclone系列EP1C3T144芯片及QuartusⅡ7.1开发环境设计,实现了符合RS-232标准的UART的设计.详细论述了UART的组成及各模块工作原理,给出了各主要模块的时序仿真结果.功能验证结果表明:所设计的UART能正确完成串行数据的收发.【期刊名称】《兰州交通大学学报》【年(卷),期】2010(029)001【总页数】5页(P16-20)【关键词】通用异步收发器;FPGA【作者】陈永刚;杨海兴【作者单位】兰州交通大学,自动化与电气工程学院,甘肃,兰州730070;西南交通大学科技园创新科技有限公司,四川,成都610031【正文语种】中文【中图分类】TN470 引言通用异步收发器(Universal A synchronous Receiver Transmitter,简称为UART)由于具有数据通信时需要的连线少,具有相关工业标准提供的标准的接口电平规范等优点,在工业控制领域被广泛采用[1-2].近年来,随着FPGA/CPLD器件在控制领域的广泛使用[1-3],开发嵌于FPGA/CPLD器件内部的通用异步收发器,以实现FPGA/CPLD开发系统与PC机之间的数据通信引起了FPGA/CPLD领域研究人员的关注.为此,基于FPGA器件设计了符合RS-232标准的UART,便于实现FPGA/ CPLD开发系统与PC机之间的串口数据交换.1 UART的组成及工作原理UART包含异步接收器和发送器,分别独立完成串行数据的发送和接收,收发两端各自有相互独立的定时时钟,两部分互不干扰,收方利用数据本身来进行同步.UART结构如图1所示.由图1可见,接收器和发送器中都包含有波特率发生器和数据位计数器模块.波特率发生器模块的功能是产生和RS-232通信所采用的波特率同步的时钟,以便按照RS-232串行通信的时序进行数据的接收和发送.设计中选择波特率为19 200 bit/s,则同步的波特率时钟频率为19 200 H z,周期为0.052 1 m s.数据位计数器模块主要用于帧数据的检测,采用收发数据的帧格式定义为:1位起始位、8位数据位和1位停止位,即10位二进制数为一帧.UART接收器在工作时,信号检测器一直监视RxD线上的电平,当RxD线上出现低电平时,通知串行接收控制器有数据需要接收,此时接收控制器启动移位寄存器、波特率发生器和数据位计数器.在波特率时钟的驱动下移位寄存器将RxD线上的电平值依次移入内部寄存器,当计数器的计数值达到10时表示一帧数据接收完成,这时接收控制器产生数据接收完成中断,并从接收的数据帧中提取出数据并锁存,供后续模块使用.UART发送器在工作时,发送信号检测器一直监视发送请求信号是否有效,若检测发送请求信号有效,则发送信号检测器停止接收发送请求.发送请求信号传到串行发送控制器后,控制器启动发送移位寄存器、波特率发生器和数据位计数器,在波特率时钟的驱动下,发送移位寄存器先发送一位起始位(逻辑0),然后将待发送的并行数据从最低位开始逐位发出,数据发送完后,再发送一位停止位(逻辑1).在移位寄存器移出一位逻辑值后数据位计数器加1,当数据位计数器记满10表示一帧数据发送完成,此时控制器停止各个辅助部件并且再次启动发送信号检测器,开始监视下一次发送请求.图1 UART结构框图Fig.1 Block diagram of UART2 UART主要组成模块的功能实现及仿真2.1 信号检测器接收信号检测模块的功能是检测RS-232输入端的信号,当有新的数据需要传输时通知串行接收控制器开始接收数据.发送信号检测模块的功能是当第一次的发送请求到来后先停止响应下一次发送请求,等到待发送的数据发送完成后由串行发送控制器将其复位,发送信号检测器才允许响应下一个发送请求.该模块主要为了解决串口发送数据速度较慢,如果发送请求频率过高,那么就可能出现没有完成第一次发送请求响应就开始响应第二次发送请求的情况.图2a、图2b分别为接收及发送信号检测器的时序仿真结果,由图2a可知,接收信号检测器在复位后开始监视RxD线上的信号,当RxD上第一次出现低电平时new_data信号有效,说明有数据需要接收,之后信号检测器停止监视RxD线上的电平信号,直到控制器向其发送复位信号后,再次启动监视功能,进行下一次有效信号的捕捉.由图 2b可知,发送信号检测器在复位后开始检测send信号,当send第一次有效时,该次的发送请求将保持,直到复位信号到来后结束,这时就可以允许响应第二次的发送请求.图2 信号检测器的时序仿真结果Fig.2 Tim ing simu lation results of signal detector2.2 串行接收/发送控制器串行接收/发送控制器模块的功能是协调它们各自的辅助子模块正常工作.这两个模块均采用状态机[4-5]方式进行描述,图3a、图3b所示分别为接收及发送控制器的状态转换图.图3 接收及发送控制器的状态转换图Fig.3 States transformation chart for controller of recep tion and transm ission由图3可知串行接收控制器状态机由空闲uart _idle、接收uart_rec和接收完成uart_end_rec3种状态组成.串行发送控制器状态机由空闲uart_idle和发送uart_send两个状态组成.图4a、图4b分别为串行接收和发送控制器的时序仿真结果.图4 串行控制器的时序仿真结果Fig.4 Tim ing simu lation results of series controllers从图4a可知接收一帧数据时,串行接收控制器的工作时序.当状态机处于空闲状态时,不断地从nb端口检测接收信号检测器输出new_data信号是否为高电平并且从reset_parts输出低电平使得需要复位的模块复位,从reset_dog输出高电平使得信号检测模块处于开启状态,从en_parts输出低电平使得需要停止的模块停止工作.当nb端检测到有效信号时,就进入接收状态.当状态机处于接收状态时,先使各个模块的复位信号变为无效,使能信号有效,然后不断地检测帧数据检测信号ovf,当ov f信号有效时使各个模块的复位信号变为有效,使能信号无效并且从recv端口输出接收完成信号,最后进入接收完成状态.当状态机处于接收完成状态时,它使信号检测器复位,并且让 recv变为低电平,最后转入空闲状态.从图4b可知发送一帧数据时串行发送控制器的工作时序.在空闲状态时,该模块将reset_dog置高来允许发送信号检测器接收发送请求,将en_cnt置低使数据位计数器停止计数,将en_mov置低使发送移位寄存器停止发送.然后不断地检测send信号的有效性(高电平有效),若send信号有效就转入发送状态.在发送状态时,该模块就使en_cnt和en_ m ov信号有效来启动数据位计数器和发送移位寄存器进行数据的发送,然后不断地检测帧数据检测信号ovf,一旦ovf信号有效就使en_cnt和en_mov信号无效来停止数据位计数器和发送移位寄存器工作,并且将 reset_dog 信号置低来复位发送信号检测器,最后将状态转入空闲状态.图4a、图4b所示接收及发送控制器的时序仿真结果表明所设计的串行控制器具有正确的工作时序.2.3 接收/发送移位寄存器接收移位寄存器的基本工作原理是在波特率时钟信号的驱动下依次将接收到的数据移入内部寄存器,为锁存器提供锁存数据,实现串并转换.发送移位寄存器的功能是在波特率时钟的驱动下将待发送的并行数据从低位开始逐位的从 TxD移出,实现并串转换,并且在数据发送开始及结束时发送一个起始位(逻辑0)及停止位(逻辑1).图5 移位积存器的时序仿真结果Fig.5 Tim ing simulation results of shift-registers图5a、图5b分别为接收及发送移位寄存器的时序仿真结果,由图5a可以看出,加在RS-232的RxD端的二进制序列10010010(92 H)信号随着波特率时钟依次移入了接收移位寄存器的data_out数据接收端.由图5b可以看出,在波特率时钟baud_clk的驱动下,起始位、待发送数据data(4DH,二进制序列为01001101),停止位依次被传送到信号线TxD上.3 UART功能验证为了验证UART功能,将FPGA的串口和PC机的串口用串口线连接,然后将FPGA 的配置文件下载到FPGA中.数据接收完成的中断信号直接连接到发送模块的发送请求端,以使接收模块接收的数据再通过发送模块发送出去,下载配置文件成功后,打开串口调试助手,选择端口为COM 1、波特率为19 200 bit/s、数据位8、停止位1、校验位None,然后打开串口如图6所示,在发送编辑框中输入一些字符(“我的UART控制器”),然后点击发送就会在接收窗口中看到所发的字符.图6 UART功能验证Fig.6 Function verified result of UART4 结论利用A ltera公司的Cyclone系列EP1C3T144芯片及QuartusⅡ7.1开发环境,设计了UART.各模块时序仿真及UART功能验证结果表明所设计的UART能正确完成串行数据的收发.将所设计的UART功能块移植于可控正弦信号发生器的设计中,顺利实现了PC机通过UART与FPGA中正弦信号发生器模块的通信,完成了PC 机对正弦信号波形的控制及显示.利用FPGA器件实现UART,具有设计灵活、便于移植等特点,具有广阔的应用前景.参考文献:【相关文献】[1] 任艳颖,王彬.IC设计基础[M].西安:西安电子科技大学出版社,2003.[2] 潘松,黄继业,曾毓.SOPC技术实用教程[M].北京:清华大学出版社,2005.[3] 张彩珍.步进控制电路的一种CPLD实现方案[J].兰州交通大学学报,2004,23(6):97-100.[4] 潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2007.[5] 侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,2004.。

基于FPGA的串口通信电路设计

基于FPGA的串口通信电路设计[摘要]串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持rs-232接口的通用异步收发器,本文基于fpga开发板设计了一个串口数据采集和处理程序,介绍了用verilog hdl硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用quartus ii软件进行仿真并给出结果,分别验证各个模块的正确性及用fpga实现串行通信的可行性。

[关键词]串行通信 rs-232 verilog hdl fpga中图分类号:tn 文献标识码:a 文章编号:1009-914x(2013)08-320-011.fpga概述fpga现场可编程逻辑门阵列是数字系统设计的主要硬件平台,其主要特点是完全由用户通过软件进行配置和编程,从而完成某种特定的功能,且可以反复擦写。

fpga具有运算速度快、根据需求在内部嵌入硬/软ip核,以及反复编程,擦写,使用的特点,被广泛应用于通信,数字信号处理,工业控制等领域。

2.rs232串口通信接口串口即串行数据接口主要用于网管控制或主业务数据的传输,支持数据的双向传输,速率9600-115200bps,即可以完成和pc的通信,也可以完成与带有标准串口的外设相连。

其中串口接口分为带插孔和带插针的两种,其中插针端称为dce,插孔端称为dte。

3.串口通信的verilog hdl实现本设计要求在fpga开发板上实现波特率为115200bps,停止位为1比特、1比特校验位的串口通信,并要求和pc机通过串口调试助手完成双向通信。

3.1波特率发生器模块的verilog hdl实现波特率发生器实际上是一个分频器,从给定的系统时钟频率得到要求的波特率。

一般来讲,为了提高系统的容错性处理,要求波特率发生器的输出时钟为实际串口数据波特率的n倍,n可以取值为8、16、32、64等。

在本设计中,系统的时钟为50mhz,取n为16,则分频系数为50000000/(16*115200)=27.127,取整为27。

基于FPGA_CPLD的通用异步通信接口UART的设计

基于FPG A/CP LD 的通用异步通信接口UART 的设计The Design of UART (Universal Asynchronous Receiver Transmitter )based on FPG A/CP LD姜 宁3 范多旺JIANG Ning F AN Duo 2wang摘 要 UART (通用异步接收发送设备)是一种短距离串行传输接口。

在数字通信和控制系统中得到广泛应用。

FPG A/CP LD 是大规模集成电路技术发展的产物,是一种半定制的集成电路。

结合计算机软件技术(E DA技术)可以快速、方便地构建数字系统。

本文介绍一种采用可编程逻辑器件FPG A/CP LD 实现UART 的方法,将UART 的核心功能集成到FPG A/CP LD 上,本设计包含UART 的发送模块、接收模块和波特率发生器,所有功能的实现全部采用VH D L 硬件描述语言来进行描述。

设计、综合、仿真在QUART USII 软件开发环境下实现。

关键词 UART VH D L FPG A/CP LD 仿真 Abstract UART (Universal Asynchronous Receiver T ransmitter )is a short 2haul serial communication inter face which is applied widely in digital communication and control system.The result of LSI (Large Scale Integration )is FP 2G A/CP LD ,it is the attribute of semi 2custom Integrate Circuit ,combining E DA with FPG A/CP LD will construct the digi 2tal system quickly and expediently.This article introduces a method to design uart based on the programmable logic de 2vice FPG A/CP LD.The core function of UART is integrated in FPG A/CP LD.This design includes the T ransmitter Log 2ic 、the Receiver Logic and the Baudrate G enerator.All function are given by VH D L.The im plementation of design 、sim 2ulation 、synthesis is the s oftware of QUART USII.K eyw ords UART VH D L FPG A/CP LD S imulation3光电技术与智能控制教育部重点实验室兰州交通大学自动控制研究所 甘肃 兰州 730070 随着E DA 技术的发展,FPG A/CP LD 已经在许多方面得到了广泛应用,而UART (Universal Asynchronous Receiver T rans 2mitter 通用异步收发器)是广泛使用的串行数据传输协议。

基于FPGA实现异步串行通信

基于FPGA实现异步串行通信佚名【摘要】为了适应全数字化自动控制更加广泛的应用,采用现场可编程门阵列(FPGA)对异步串行通信控制器(UART)进行多模块的系统设计的方法,使串口通信的集成度更高。

对UART系统结构进行了模块化分解,可分为三个模块:FPGA波特率发生器控制模块、FPGA数据发送模块及数据接收模块。

采用Verilog语言描述硬件功能,利用Xilinx公司的FPGA芯片,在Xilinx ISE Design Suite 13.4环境下进行设计、编译、综合、下载。

采用第三方仿真工具ModelSim进行模拟仿真。

%In order to adapt to the widely applications of full digital automatic control,a multi⁃module system is designed with FPGA for UART,to make the integration level of the serial communication higher. The UART system structure is discom⁃posed into three modules:FPGA baud rate generator control module,FPGA data sending module and the data receiving mod⁃ule. The hardware functionality is described by Verilog language. By using FPGA chip of Xilinx,the design,compiling,synthe⁃sis and download could be completed in Xilinx ISE Design Suite 13.4 environment. The simulation is conducted by ModelSim.【期刊名称】《现代电子技术》【年(卷),期】2013(000)013【总页数】3页(P71-73)【关键词】FPGA;UART;多模块;Verilog;Xilinx ISE【正文语种】中文【中图分类】TN911-34异步串行通信(UART)是一种广泛应用的串行数据传输协议,UART[1-3]的要求是传输线少,可靠性高而且传输距离远。

基于FPGA的异步串口通信技术

基于FPGA的异步串口通信技术一、异步串口通信技术综述:接口通信技术是通信的主要研究领域之一,从数字通信的角度来看,当前主流接口通信技术分为串行通信和并行通信两种。

卫星通信和常见的USB接口通信一般都是采用串口通信技术。

微机系统与其外部I/O设备的接口,如RS232、RS422、RS485等,都是采用串口通信协议。

所谓串行通信,是指两个设备之间,以一个字节(8bit)为一个单位逐位按顺序传送信息,这样可大幅度节省总线资源。

由于使用的是按位传送,即每次只传送一个数据状态,因此使用串行接口的两个设备之间最少可以只使用一根数据线(如果是半双功或是双功情况下,应至少有两根数据线)。

这种接口通信技术的优点是成本较低,但传送距离较远。

与此相对的是并行通信技术,所谓并行通信是指两个设备之间有至少8根数据线(单工情况),在同一时间内8根数据线同时传送数据,这样一次就完成了1个字节的传送。

显而易见,并行通信技术速率更快,但成本也更高。

异步则是指对于设备一和设备二,即发送端和接收端而言,可以使用两个独立的时钟源来分别控制数据信号的发送和接受,系统中不存在全域时钟信号。

为了便于设备发送和接受收据,我们规定在数据线上处于高电平状态“1”时,数据线闲置,此时数据线的发送端并没有数据发出。

当设备1准备发出数据时,首先向数据线上发出一个低电平状态信号“0”,当设备2检测到数据线上的低电平信号时,就开始接受来自设备1的数据信号。

可以看出,逻辑低电平是数据传送的开始,它是数据的起始位。

当数据从低到高依次逐位传送完成后(数据的位数至多就是8位,也可以低于8位),此时发送奇偶校验位用于数据的有限差错检测,奇偶校验位是冗余位,一般情况下,没有校验位也是可以的。

接着奇偶校验位之后是停止位,一般是1--2位的逻辑高电平信号“1”,停止位表示数据传输结束。

异步串口通信数据格式二、RS232接口简述:RS232是常见的采用串行接口协议的接口之一,其通信协议与串口通信标准是一致的。

基于FPGA的通用异步收发器设计

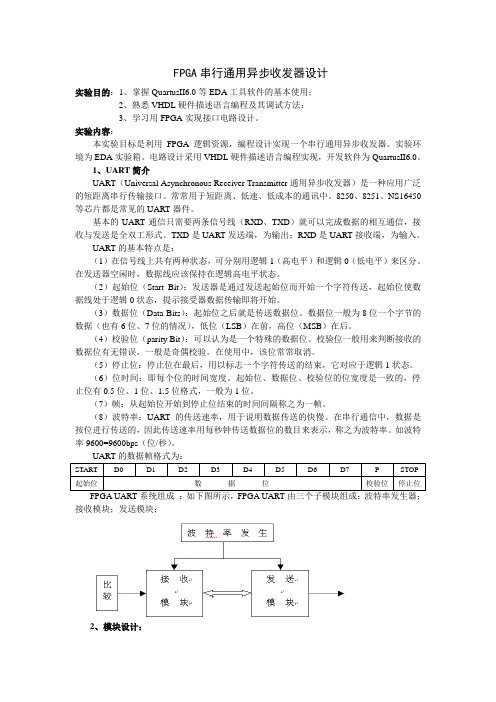

FPGA串行通用异步收发器设计实验目的:1、掌握QuartusII6.0等EDA工具软件的基本使用;2、熟悉VHDL硬件描述语言编程及其调试方法;3、学习用FPGA实现接口电路设计。

实验内容:本实验目标是利用FPGA逻辑资源,编程设计实现一个串行通用异步收发器。

实验环境为EDA实验箱。

电路设计采用VHDL硬件描述语言编程实现,开发软件为QuartusII6.0。

1、UART简介UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。

常常用于短距离、低速、低成本的通讯中。

8250、8251、NS16450等芯片都是常见的UART器件。

基本的UART通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接收与发送是全双工形式。

TXD是UART发送端,为输出;RXD是UART接收端,为输入。

UART的基本特点是:(1)在信号线上共有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。

在发送器空闲时,数据线应该保持在逻辑高电平状态。

(2)起始位(Start Bit):发送器是通过发送起始位而开始一个字符传送,起始位使数据线处于逻辑0状态,提示接受器数据传输即将开始。

(3)数据位(Data Bits):起始位之后就是传送数据位。

数据位一般为8位一个字节的数据(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后。

(4)校验位(parity Bit):可以认为是一个特殊的数据位。

校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。

在使用中,该位常常取消。

(5)停止位:停止位在最后,用以标志一个字符传送的结束,它对应于逻辑1状态。

(6)位时间:即每个位的时间宽度。

起始位、数据位、校验位的位宽度是一致的,停止位有0.5位、1位、1.5位格式,一般为1位。

(7)帧:从起始位开始到停止位结束的时间间隔称之为一帧。

基于PLDFPGA的通用异步收发器设计

摘要:通用异步收发器是一种能同时支持短距离和长距离数据传输的串行通信接口,被广泛应用于微机和外设之间的数据交换,本文对FPGA的通用异步收发器设计进行分析。

关键词:通用异步收发器数据传输数据交换串行通信方式传递数据所传输的距离比较远,所用的数据线也很少,并且其稳定性也高。

因此在数据通信方面能够被广泛的使用。

异步收发器(UART)是经常被使用来进行串口通信的设备。

本文就是用VHDL语言编写的应用在FPGA上的一个UART。

在传递数据时,我们仅仅需要使用UART的几个作用,所以如果专门购置专用的UART,则会造成资金和功能上的浪费。

恰好VHDL可以用硬件语言搭建出UART的模型,可以根据所需要的功能来进行程序的编写,这样既省费用又省步骤。

1UART的工作原理UART(Universal Asynchronous Receiver Trans-mitter,通用异步收发器)是通常使用的异步串行传递数据的传输协议。

在串行通信中,数据是一个字节帧一个字节帧来发送信息的。

发送端和接收端在接收数据帧的时候必须有约定的格式和约定的波特率。

一个数据帧由1位起始位(低电平)、5~8位数据位、1位校验位(可选可不选)和停止位来组成。

一个数据帧的开始便是起始位,起始位处于逻辑0状态,处于逻辑0状态就表明发送端已经准备开始发送数据了。

一个数据帧的结束是停止位,停止位处于逻辑1状态,处于逻辑1就表明接收端已经停止接收数据了。

而波特率采用标准速率9600字节每秒。

数据在传输时,低位在前,高位在后。

接收端检测并确认起始位后,开始接收数据位。

当接到停止位后,FPGA向CPU发出中断信号。

发送数据时,CPU设置波特率为9600字节每秒,然后FPGA将数据一帧一帧的通过总线传递给CPU,当CPU接收到低电平时,表示此时数据传送结束。

2程序设计与仿真顶层程序与仿真:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity top isport(clk32mhz,reset,rxd,xmit_cmd_p_in:in std_log-ic;rec_ready,txd_out,txd_done_out:out std_logic;txdbuf_in:in std_logic_vector(7downto0);rec_buf:out std_logic_vector(7downto0);bclkout:out std_logic);end top;architecture Behavioral of top iscomponent recieverport(bclkr,resetr,rxdr:in std_logic;r_ready:out std_logic;rbuf:out std_logic_vector(7downto0));end component;component transferport(bclkt,resett,xmit_cmd_p:in std_logic;txdbuf:in std_logic_vector(7downto0);txd:out std_logic;txd_done:out std_logic);end component;component baudport(clk,resetb:in std_logic;bclk:out std_logic);end component;signal b:std_logic;beginu1:baud port map(clk=>clk32mhz,resetb=>reset, bclk=>b);u2:reciever port map(bclkr=>b,resetr=>reset,rx-dr=>rxd,r_ready=>rec_ready,rbuf=>rec_buf);u3:transfer port map(bclkt=>b,resett=>reset, xmit_cmd_p=>xmit_cmd_p_in,txdbuf=>txdbuf_in,txd=>txd_out,txd_done=>txd_done_out);bclkout<=b;endBehavioral;3总结UlART经常用于数据之间的串行通信,它所需要使用的线路较少,并且稳定性高,数据可以传输很长的距离,因此芯片或计算机系统之间进行数据传送时经常用UART。

基于FPGA 的异步串行通信控制器的设计与实现

基于FPGA 的异步串行通信控制器的设计与实现摘要】本论文采用VHDL 语言描述硬件功能,利用Altera 公司的FPGA 芯片,采用模块化设计方法设计UART(通用异步收发器)的各个模块,在QuartusII 和ModelSim 环境下进行设计、编译、仿真和下载。

而上位机利用VC6.0 实现PC 机与UART 的通信。

最后的通信测试表明系统数据完全正确。

【关键词】UART FPGA VHDL VC【中图分类号】TN02 【文献标识码】A 【文章编号】1006-9682(2009)01-0023-03【Abstract】This paper described the hardware functions by VHDL and designed the UART modules in modularization method by usingFPGA COMS chip of Altera company, which was designed, compiled, simulated and downloaded in QuartusII and ModelSim. However, uppermachine used VC6.0 to realize the communication between PC and UART. The final simulation results show the system data is completedcorrect.【Key words】UART FPGA VHDL VC一、引言UART(Universal Asynchronous Receiver Transmitter)通用异步收发器、是一种应用非常广泛的短距离串行传输接口,主要应用于短距离、低速低成本的微机与下位机的实时通讯中,串行外设接口芯片的型号有很多,如16550 等,然而这类芯片本身已经相当复杂,有的甚至含有许多辅助的功能模块(如FIFO),但是实际应用中常常不需要使用如此完整的UART 的功能以及这些辅助功能。

基于FPGA实现CRC校验功能的通用异步串口通信

基于FPGA实现CRC校验功能的通用异步串口通信同晓荣;盛仲飙【期刊名称】《信息技术》【年(卷),期】2012(000)003【摘要】UART作为RS-232协议的控制接口得到了广泛的应用,为实现准确的数据串口通信,在分析CRC生成算法的基础上,提出了一种简单、实用的UART设计与实现方案.该方案在串口通信中采用CRC-5校验,基于FPGA采用Verilog语言实现CRC-5校验模块,仿真结果与理论分析一致,达到了预期设计的目标.提高了通信的速度、可靠性和效率.%UART is used widely as the interface of RS-232, to obtain accurate serial communication of data, a simple and practical scheme for UART design and realization was put forward. Cyclic redundancy check (CRC) in serial communication greatly improves the reliability of communication system, and realization of CRC-5 check module with Verilog language on the basis of FPGA and the analysis of CRC-5 algorithm generation obtains consistence between the results of simulation and theoretical analysis. Therefore, the expected design target was met, and the communication speed and efficiency were unproved.【总页数】4页(P27-29,32)【作者】同晓荣;盛仲飙【作者单位】渭南师范学院数学与信息科学学院,渭南714000;渭南师范学院数学与信息科学学院,渭南714000【正文语种】中文【中图分类】TP391【相关文献】1.基于LFSR的CRC校验码在FPGA上的实现 [J], 李永基;魏文军2.基于FPGA的CRC校验算法的实现 [J], 张焱;任勇峰;齐蕾;姚宗3.基于FPGA的带CRC校验的异步串口通信 [J], 田佳;王一平4.专川异步串口通信电路的FPGA实现 [J], 苏明;姚冬苹5.基于FPGA的通用异步接收/发送器设计与实现 [J], 叶林朋因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA串行通用异步收发器设计实验目的:1、掌握QuartusII6.0等EDA工具软件的基本使用;2、熟悉VHDL硬件描述语言编程及其调试方法;3、学习用FPGA实现接口电路设计。

实验内容:本实验目标是利用FPGA逻辑资源,编程设计实现一个串行通用异步收发器。

实验环境为EDA实验箱。

电路设计采用VHDL硬件描述语言编程实现,开发软件为QuartusII6.0。

1、UART简介UART(Universal Asynchronous Receiver Transmitter通用异步收发器)是一种应用广泛的短距离串行传输接口。

常常用于短距离、低速、低成本的通讯中。

8250、8251、NS16450等芯片都是常见的UART器件。

基本的UART通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接收与发送是全双工形式。

TXD是UART发送端,为输出;RXD是UART接收端,为输入。

UART的基本特点是:(1)在信号线上共有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。

在发送器空闲时,数据线应该保持在逻辑高电平状态。

(2)起始位(Start Bit):发送器是通过发送起始位而开始一个字符传送,起始位使数据线处于逻辑0状态,提示接受器数据传输即将开始。

(3)数据位(Data Bits):起始位之后就是传送数据位。

数据位一般为8位一个字节的数据(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后。

(4)校验位(parity Bit):可以认为是一个特殊的数据位。

校验位一般用来判断接收的数据位有无错误,一般是奇偶校验。

在使用中,该位常常取消。

(5)停止位:停止位在最后,用以标志一个字符传送的结束,它对应于逻辑1状态。

(6)位时间:即每个位的时间宽度。

起始位、数据位、校验位的位宽度是一致的,停止位有0.5位、1位、1.5位格式,一般为1位。

(7)帧:从起始位开始到停止位结束的时间间隔称之为一帧。

(8)波特率:UART的传送速率,用于说明数据传送的快慢。

在串行通信中,数据是按位进行传送的,因此传送速率用每秒钟传送数据位的数目来表示,称之为波特率。

如波特率9600=9600bps(位/秒)。

UART的数据帧格式为:START D0 D1 D2 D3 D4 D5 D6 D7 P STOP 起始位数据位校验位停止位FPGA UART系统组成:如下图所示,FPGA UART由三个子模块组成:波特率发生器;接收模块;发送模块;2、模块设计:系统由四部部分组成:顶层模块;波特率发生器;UART接收器;UART发送器1)顶层模块异步收发器的顶层模块由波特率发生器、UART接收器和UART发送器构成。

UART发送器的用途是将准备输出的并行数据按照基本UART帧格式转为TXD信号串行输出。

UART接收器接收RXD串行信号,并将其转化为并行数据。

波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入RXD不断采样,使接收器与发送器保持同步。

2)波特率发生器波特率发生器实际上就是一个分频器。

可以根据给定的系统时钟频率(晶振时钟)和要求的波特率算出波特率分频因子,算出的波特率分频因子作为分频器的分频数。

波特率分频因子可以根据不同的应用需要更改。

3)UART接收器由于串行数据帧和接收时钟是异步的,由逻辑1转为逻辑0可以被视为一个数据帧的起始位。

然而,为了避免毛刺影响,能够得到正确的起始位信号,必须要求接收到的起始位在波特率时钟采样的过程中至少有一半都是属于逻辑0才可认定接收到的是起始位。

由于内部采样时钟bclk周期(由波特率发生器产生)是发送或接收波特率时钟频率的16倍,所以起始位需要至少8个连续bclk周期的逻辑0被接收到,才认为起始位接收到,接着数据位和奇偶校验位将每隔16个bclk周期被采样一次(即每一个波特率时钟被采样一次)。

如果起始位的确是16个bclk周期长,那么接下来的数据将在每个位的中点处被采样。

UART接收器的接收状态机接收状态机一共有5个状态:R_START(等待起始位);R_CENTER(求中点);R_W AIT(等待采样);R_SAMPLE(采样);R_STOP(停止位接收)。

R_START状态当UART接收器复位后,接收状态机将处于这一个状态。

在此状态,状态机一直在等待RXD的电平跳转,从逻辑1变为逻辑0,即起始位,这意味着新的一帧UART数据帧的开始,一旦起始位被确定,状态机将转入R_CENTER状态。

状态图中的RXD_SYNC信号是RXD的同步信号,因为在进行逻辑1或逻辑0判断时,不希望检测的信号是不稳定的,所以不直接检测RXD信号,而是检测经过同步后的RXD_SYNC信号。

R_CENTER状态对于异步串行信号,为了使每一次都检测到正确的位信号,而且在较后的数据位检测时累计误差较小,显然在每位的中点检测是最为理想的。

在本状态,就是由起始位求出每位的中点,通过对bclk的个数进行计数(RCNT16),但计数值不是想当然的“1000”,要考虑经过一个状态,也即经过了一个bclk周期,所希望得到的是在采样时1/2位。

另外,可能在R_START状态检测到的起始位不是真正的起始位,可能是一个偶然出现的干扰尖脉冲(负脉冲)。

这种干扰脉冲的周期是很短的,所以可以认为保持逻辑0超过1/4个位时间的信号一定是起始位。

R_W AIT状态当状态机处于这一状态,等待计满15个bclk,在第16个bclk是进入R_SAMPLE状态进行数据位的采样检测,同时也判断是否采集的数据位长度已达到数据帧的长度(FRAMELEN),如果到来,就说明停止位来临了。

FRAMELEN在设计时是可更改的(使用了Generic),在本设计中默认为8,即对应的UART工作在8位数据位、无校验位格式。

R_SAMPLE状态即数据位采样检测,完成后无条件状态机转入R_W AIT状态,等待下次数据位的到来。

R_STOP状态无论停止位是1还是1.5位,或是2位,状态机在R_STOP不具体检测RXD,只是输出帧接收完毕信号(REC_DONE<=‘1’),停止位后状态机转回到R_START状态,等待下一个帧的起始位。

4)UART发送器发送器只要每隔16个bclk周期输出1个数据即可,次序遵循第1位是起始位,最后一位是停止位。

在本设计中没有校验位,但只要改变Generic参数FrameLen,也可以加入校验位,停止位是固定的1位格式。

发送状态机的状态图发送状态机一共有5个状态:X_IDLE(空闲);X_START(起始位);X_W AIT(移位等待);X_SHIFT(移位);X_STOP(停止位)。

X_IDLE状态:当UART被复位信号复位后,状态机将立刻进入这一状态。

在这个状态下,UART的发送器一直在等待一个数据帧发送命令XMIT_CMD。

XMIT_CMD_P信号是对XMIT_CMD的处理,XMIT_CMD_P是一个短脉冲信号。

这时由于XMIT_CMD是一个外加信号,在FPGA之外,不可能对XMIT_CMD的脉冲宽度进行限制,如果XMIT_CMD有效在UART发完一个数据帧后仍然有效,那么就会错误地被认为,一个新的数据发送命令又到来了,UART发送器就会再次启动UART帧的发送,显然该帧的发送是错误的。

在此对XMIT_CMD进行了脉冲宽度的限定,XMIT_CMD_P就是一个处理后的信号。

当XMIT_CMD_P=‘1’,状态机转入X_START,准备发送起始位。

X_START状态:在这个状态下,UART的发送器一个位时间宽度的逻辑0信号至TXD,即起始位。

紧接着状态机转入X_W AIT状态。

XCNT16是bclk的计数器X_WAIT状态同UART接收状态机中的R_W AIT状态类似。

X_SHIFT状态当状态机处于这一状态时,实现待发数据的并串转换。

转换完成立即回到X_WAIT状态。

X_STOP停止位发送状态,当数据帧发送完毕,状态机转入该状态,并发送16个bclk周期的逻辑1信号,即1位停止位。

状态机送完停止位后回到X_IDLE状态,并等待另一个数据帧的发送命令。

实验步骤:1、创建工程文件按照Quartus软件新建工程向导建立工程,工程名设为:uart_test(可自行命名)。

2、子模块电路设计(包括各个模块的功能仿真)1)波特率发生器程序编写:在“文件”菜单下选择“New”,在弹出的窗口点击“VHDL File”点击“OK”打开vhdl编辑窗口。

编辑输入波特率发生器程序,编辑完毕后保存,文件名保存为“baud”(注:文件名必须与程序中实体名一致)选中“Add file to current project”选项,添加当前文件到项目。

--文件名:baud.vhd.--功能:本实验想要实现的波特率为:9600,EDA实验箱上晶振频率为:4MHZ,--波特率发生器的分频数计算如下式:--4000000/(16*9600)=26library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity baud isgeneric(framlenr:integer:=26);Port (clk,resetb:in std_logic;bclk :out std_logic);end baud;architecture Behavioral of baud isbeginprocess(clk,resetb)variable cnt:integer;beginif resetb='1' then cnt:=0; bclk<='0'; --复位elsif rising_edge(clk) thenif cnt>=framlenr then cnt:=0; bclk<='1';--设置分频系数else cnt:=cnt+1; bclk<='0';end if;end if;end process;end Behavioral;文件编译:保存文件后,选择“Project”菜单,点击“Set as Top-Level Entity”项,把当前文件设置为顶层实体。

(注:Quartus环境下所有操作(综合、编译、仿真、下载等)都只对顶层实体进行,所以编译任何程序前,必须先设置该选项,把当前要编译的文件设置为顶层实体后,才能对该文件进行编译等操作)打开“Processing”菜单,点击“Start Compilation”执行完全编译状态窗口显示编译过程进度信息编译结束,系统会弹出编译结束窗口,报告错误与警告数,点击“确定”。