基于FPGA的串口控制器设计

基于fpga的串口设计及实现

基于fpga的串口设计及实现

基于FPGA的串口设计及实现是一个涉及数字电路设计和通信协

议的复杂课题。

首先,让我们从串口通信的基本原理开始。

串口通信是一种通过串行传输数据的通信方式,它使用一个或

多个数据线(通常是一对)来逐位地传输数据。

常见的串口通信标

准包括RS-232、RS-485、UART等。

在FPGA中实现串口通信,需要

考虑以下几个方面:

1. 串口通信协议选择,根据具体的应用场景和需求,选择合适

的串口通信协议。

例如,UART是一种常见的串口通信协议,它使用

起始位、数据位、校验位和停止位来传输数据。

2. 串口通信接口设计,在FPGA中设计串口通信接口,需要考

虑数据的发送和接收,时钟信号的同步等问题。

通常需要使用FPGA

的IO资源来实现串口通信接口。

3. 串口通信协议的实现,在FPGA中实现选择的串口通信协议,包括数据的发送和接收、时序控制、校验等功能。

这通常需要使用Verilog或VHDL等硬件描述语言进行开发。

4. 硬件调试和验证,设计完成后,需要进行硬件调试和验证,包括时序分析、波形仿真等工作,确保串口通信的稳定和可靠。

在实际的FPGA串口设计中,还需要考虑时钟频率、数据传输速率、数据格式、数据校验、中断处理等问题。

此外,还需要考虑FPGA与外部设备的接口,如与传感器、显示器、存储器等设备的接口设计。

总之,基于FPGA的串口设计及实现涉及到硬件设计、数字电路设计、通信协议等多个方面的知识,需要综合考虑各种因素,进行全面的设计和实现。

基于FPGA的SOC系统中的串口设计

基于FPGA的SOC系统中的串口设计1概述在基于FPGA的SOC设计中,常使用串口作为通信接口,但直接用FPGA进行串口通信数据的处理是比较繁杂的,特别是直接使用FPGA 进行串口通信的协议的解释和数据打包等处理,将会消耗大量的FPG A硬件资源。

为简化设计,降低硬件资源开销,可以在FPGA中利用IP核实现的嵌入式微处理器来对串口数据进行处理。

本文中的设计采用了XILINX的FPGA,可选用的嵌入式微处理器IP核种类繁多,但基于对硬件资源开销最少的考虑,最终选用了Picobl aze。

嵌入式微处理器PicoBlaze适用于Spartan-II/E、CoolRunner-II和Virtex系列FPGA,运行速度可达到40MIPS以上,提供49个不同的指令,16个寄存器,256个地址端口,1个可屏蔽的中断。

其性能超过了传统的8bit微处理器。

嵌入式微处理器Picoblaze的功能、原理见参考文献[1]。

Picoblaze使用灵活,但其缺点是可寻址的存储空间非常有限,因此为满足实际需要本文同时也提出了使用片外SDRAM器件对其存储能力进行扩展的设计方法。

2串口收发接口设计2.1串口收发接口硬件设计嵌入式微处理器PicoBlaze本身并不具备串行接口,因此必须在F PGA中设计串口接收和发送模块并通过总线结构与Picoblaze连接。

串口接收和发送模块的设计可采用成熟的IP核。

实际设计中采用了XLINX的串口收发IP核,其特点是串口波特率,符号规则都可以灵活地定制,同时具有16字节的接收FIFO和16字节的发送FIFO。

串口收发IP核的功能、原理见参考文献[2]。

使用Picoblaze和串口收发IP核构成的串口收发系统结构见图1。

在设计中,发送模块、接收模块和标志寄存器分别有不同的地址, Picoblaze通过地址端口对串口收发模块进行访问。

设计中的标志寄存器,可用于指示发送模块和接收模块中FIFO的状态,Picoblaze通过查询标志寄存器来完成对串口数据的收发控制。

基于FPGA的串口通信设计

基于FPGA的串口通信设计引言:串口通信是现代计算机通信系统中的常见通信方式。

它可以在计算机和外部设备之间传输数据,具有低成本、简单易懂、可靠性高等特点。

然而,在一些应用场景下,传统的软件串口通信无法满足需求,因此使用FPGA来实现硬件串口通信变得愈发重要。

本文将重点介绍基于FPGA的串口通信设计,包括串口通信原理、FPGA硬件实现以及设计注意事项。

一、串口通信原理:串口通信的原理很简单,将数据通过一根导线(或多根导线)依次发送和接收。

它使用一个起始位、数据位(常为8位)、奇偶校验位(可选)和一个或多个停止位来组成一个数据帧。

发送数据时,串口将数据帧从最低位开始逐位发送,并在每位发送完毕后根据波特率发送下一位。

接收数据时,串口根据波特率和起始位检测到数据的到来,并从起始位开始逐位接收。

二、FPGA硬件实现:FPGA可以通过其可编程逻辑单元(FPGA的核心组件)实现硬件串口通信。

下面是基于FPGA的串口通信设计主要步骤:1.FPGA引脚分配:首先,选择合适的FPGA芯片,并确定通信所需的引脚数量。

然后,根据引脚分配表将引脚与FPGA的可编程逻辑单元相连接。

2.接口电平转换:在FPGA和外设之间可能存在电平不匹配的情况。

为了实现正确的数据传输,需要使用电平转换电路进行适配。

3.帧同步信号生成:FPGA需要生成适当的时钟信号和帧同步信号,以使数据能够正确地按位传输和接收。

帧同步信号指示数据的起始和终止。

4.数据传输实现:FPGA需要根据串口通信原理,按照波特率逐位地发送和接收数据。

在发送数据时,FPGA将数据从最低位开始逐位输出到引脚,并根据起始位、数据位、奇偶校验位和停止位生成完整的数据帧。

在接收数据时,FPGA根据时钟信号和帧同步信号,逐位地接收到达的数据,以获得完整的数据帧。

5.数据校验和处理:FPGA可以实现奇偶校验的功能,以检测接收到的数据是否正确。

此外,还可以在FPGA内部对接收到的数据进行处理,例如数据解码、错误检测等。

基于FPGA的串口设计设计39893934

基于FPGA的串口设计设计39893934基于FPGA的串口设计目录前言 (1)1 引言 (1)1.1 课题来源 (1)1.2 课题研究的研究背景 (1)1.3 国内外的发展现状、发展趋势及存在的主要问题 (2)1.4 课题研究的指导思想与技术路线 (3)1.5 基于FPGA串口设计的技术要求 (4)2 UART原理介绍 (5)2.1UART结构和工作原理 (5)3 方案选择 (6)3.1 设计语言的选择 (6)3.2 电平转换方式的选择 (7)3.3 FPGA核心芯片的选择 (7)4 系统硬件设计 (9)4.1 器件芯片介绍 (9)4.2 系统硬件框图 (14)4.3 主要组成电路分析 (14)4.4 总电路图设计 (17)5 系统软件设计 (17)5.1 主程序流程图 (17)5.2 中断子程序流程图 (19)5.3 DDS控制软件设计 (19)5.4 AD7886 软件驱动设计 (20)5.5 系统源程序 (21)6 制作位移测量装置的步骤 (21)7 总结 (22)参考文献 (23)致谢 (24)附录1 (25)附录2 (26)附录3 (27)前言随着FPGA/CPLD器件在控制领域的广泛使用,开发嵌于FPGA/CPLD器件内部的通用异步收发器,以实现FPGA/CPLD开发系统与PC机之间的数据通信是很有实际意义的。

FPGA/CPLD器件与单片机、ARM等器件不同,内部没有集成UART,因此要实现串行通信,必须要独立开发UART模块。

本设计对于深入理解串口的工作原理和理解FPGA的工作流程具有启示意义,并通过设计的过程FPGA的应用能力和系统综合设计能力将得到加强。

1 引言1.1 课题来源结合科研1.2课题研究的研究背景当今社会是数字化的社会,是数字集成电路广泛应用的社会。

数字集成电路本身在不断地进行更新换代。

它由早期的电子管、晶体管、小中规模集成电路、发展到超大规模集成电路(VLSIC,几万门以上)以及许多具有特定功能的专用集成电路。

基于FPGA的RS-232串口通信控制器设计汇总

基于FPGA的RS-232串口通信控制器设计摘要串口是可以在使用一根线发送数据的同时用另一根线接收数据。

串口通信协议也可以用于获取远程采集设备的数据。

通过RS-232以实现计算机之间、计算机与设备之间相互通信,目前仍是通讯领域广泛使用的方法之一。

几乎每台计算机都有一两个串行接口,用来与调制解调器、实验室设备、工控设备、POS终端等进行数据传输。

RS-232以其方便、经济的实现特点,一直深受工程界的青睐。

不论是在电力、工控还是电信、金融交通等诸多行业都有广泛的应用。

系统主芯片采用RS-232串口通信控制器,由基本时钟发生电路模块,复位电路模块,波特率选择模块,数据帧格式选择模块,串并转换模块组成。

经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,结合FPGA技术高度灵活性与模块化的特点,实现基本RS-232总线通信的功能,以实现串口数据帧结构选择,串并转换,波特率选择等功能。

通过软件仿真,得到功能的验证,并进行功能逻辑模块的整合,从而验证设计的可行性与可靠性。

关键词:RS-232串口通信控制器;硬件描述语言;FPGAAbstractcommunications between equipment, is still widely used method of communication field. Almost every computer has a serial interface, used and modems, laboratory equipment, industrial equipment, POS terminals, etc for data transmission. With its rs-five 232 convenient, economical realization of engineering characteristics, has been deeply favored. Whether in electric power, telecommunications, financial traffic control or many industries have widely application.The master chip adopt rs-five 232 serial communication controller, the basic clock circuit module, reset circuit happened module, baud rate, data frame format selection module choice module, and conversion module composition string. The compiler and simulation design program, in programmable logic devices on FPGA technology, combining download highly flexible and modular characteristics, basic RS - 232 fieldbus communication function, in order to realize the serial data frame structure, and the conversion of choice, baud rate etc. Function. Through the simulation test, the function and the integration of the logical module function, which verified the feasibility and reliability of the design.Keywords: RS - 232 serial communication controller, Hardware description language, The FPGA目录1 绪论 (1)1.1 选题背景 (1)1.1.1 课题相关技术的发展 (1)1.1.2 课题研究的必要性 (2)1.2 课题研究的内容 (3)2 FPGA及RS-232简介 (4)2.1 FPGA概述 (4)2.1.2 FPGA基本结构 (6)2.1.3 FPGA系统设计流程 (8)2.1.4 FPGA开发编程原理 (11)2.2 RS-232概述 (12)2.2.1 RS-232电气特性 (13)2.2.2 RS-232连接器的机械特性 (13)2.2.3 RS-232的接口信号 (14)3 RS-232串口通信控制器硬件设计方案 (18)3.1 锁相环设计 (18)3.2 模式选择模块设计 (19)3.3 接收模块设计 (19)3.4 发送模块设计 (21)4 RS-232控制器软件设计 (23)4.1 模式选择模块软件设计 (23)4.2 接收模块软件设计 (24)4.3 发送模块软件设计 (26)5 研究展望 (28)实验结论 (29)致谢 (30)参考文献 (31)附录 (32)1 绪论现代社会的标志之一就是信息产品的广泛使用,而且是产品的性能越来越强,复杂程度越来越高,更新步伐越来越快。

基于FPGA的串口通讯电路设计毕业论文

本科学生毕业论文论文题目:学院: 年级:专业:姓名: 学号: 指导教师:基于FPGA勺串口通信电路设计集成电路设计与集成系统i串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持RS-232接口(又称EIA RS-232-C)的通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART),本文设计了一个串口数据采集和处理程序,详细介绍了用Verilog HDL硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用Quartus II软件进行仿真并给出结果,分别验证各个模块的正确性。

本设计还使用基于ALTERA 公司的Cyclone II EP2C5T144芯片的FPGA开发板,在FPGA开发板上实现和PC 通过串口调试软件完成双向通信,不仅要求将开发板的数据显示在PC的串口调试助手软件上,还要求用PC发送数据的ASCII码来驱动电路的8个LED 灯,验证用FPGA实现串行通信的可行性。

关键词串行通信;RS-232; UART ;Verilog HDL ;FPGAAbstractSerial com muni cati on in terface is a widely used com muni cati on in terface. At prese nt, most of processor in tegrated RS-232(EIA RS-232-C) in terface to support UART (Uni versal Asynchronous Receiver/Tra nsmitter) com muni cati on, This thesis desig n a data acquisiti on and treatme nt program. Besides that, the thesis in troduced Baud Rate Generator module、Receiver module、Send module based on Ianguage Verilog HDL and give the results by simulate in Quartus II software. This desig n also uses EP2C5T144 FPGA chip to achieve the two-way com muni cati on by simulate with Quartus II and PC through the serial port debuggi ng software. Not only requires the developme nt board's data displayed in the PC's serial port debugg ing software, also ask ASCII data sent by PC Code to drive eight LED lights, mean while verified the serial com muni cati on with FPGA.Key wordsSerial commu ni catio n; RS-232; UART; Verilog HDL; FPGA摘要 (I)Abstract (II)第1章语言和工具 (2)1.1 Verilog HDL 语言概述 (2)1.2 FPGA 概述 (4)1.3 Quartus II 软件介绍 (8)1.4 FPGA开发板介绍 (9)1.5本章小结 (12)第2章串口通信协议简介 (13)2.1串口通信接口 (13)2.2 RS232通信协议 (13)2.3串口通信时序分析 (15)2.4本章小结 (16)第3章串口通信的VerilogHDL实现 (17)3.1设计功能说明 (17)3.2波特率发生器模块的VerilogHDL实现 (17)3.3发送模块的Verilog HDL实现 (19)3.4接收模块的Verilog HDL 实现 (25)3.5本章小结 (31)第4章串口通信的硬件调试 (32)4.1板级调试说明 (32)4.2下载配置FPGA (33)4.3配置串口调试软件 (35)4.4调试结果 (35)4.5本章小结 (38)结论 (39)参考文献.......................................................... 错误!未定义书签。

基于FPGA的RS-232串口通信控制器设计毕业设计

基于FPGA的RS-232串口通信控制器设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日指导教师评阅书评阅教师评阅书教研室(或答辩小组)及教学系意见摘要串口是可以在使用一根线发送数据的同时用另一根线接收数据。

串口通信协议也可以用于获取远程采集设备的数据。

通过RS-232以实现计算机之间、计算机与设备之间相互通信,目前仍是通讯领域广泛使用的方法之一。

基于FPGA的串口通讯设计

基于FPGA的串口通讯设计随着科技的不断发展,现场可编程门阵列(FPGA)因其高度的灵活性和强大的数据处理能力,日益成为通讯系统设计的重要选择。

串口通讯作为一种常见的通讯方式,广泛应用于各种设备之间的数据传输。

本文将探讨如何将FPGA应用于串口通讯设计,以期提高通讯效率和稳定性。

在本文中,我们将首先确定合适的主控芯片,然后设计基于FPGA的串口通讯电路,并对FPGA资源进行合理配置。

接下来,我们将介绍如何实现串口通讯算法,以提高通讯效率和稳定性。

在基于FPGA的串口通讯设计中,我们需要考虑以下电路元件的选择和设计:电阻分压器:用于降低输入信号的电压,以适应FPGA的输入范围。

晶体振荡器:为FPGA提供时钟信号,确保设备的同步运行。

电源转换器:将外部电源转换为FPGA所需的电压和电流范围。

我们还需要根据实际需求,设计串口通讯电路的功能模块,如数据发送、数据接收等。

在基于FPGA的串口通讯设计中,我们需要根据实际需求,合理分配FPGA内部资源。

具体来说,我们需要:锁相环(PLL):用于倍频和分频时钟信号,实现高速数据传输。

信号输出:驱动外部设备,如LED、LCD等。

在实现串口通讯算法时,我们首先需要定义通讯协议,包括数据格式、波特率、校验位等。

然后,我们可以使用流程图等方式,明确算法实现步骤。

例如:实验验证为了验证基于FPGA的串口通讯设计的可行性和可靠性,我们搭建了实验环境,并进行了以下测试:功能测试:检测电路各功能模块是否正常工作,如数据发送、数据接收等。

性能测试:测试通讯速率、稳定性、抗干扰能力等指标。

协议兼容性测试:检测算法是否兼容不同串口通讯协议。

长时间运行测试:检测系统在长时间运行下的稳定性和可靠性。

通过以上实验测试,我们发现基于FPGA的串口通讯设计在通讯速率、稳定性、抗干扰能力等方面均具有显著优势,能满足多种应用场景的需求。

同时,该设计具有较好的协议兼容性和可扩展性,能根据不同需求进行定制化扩展。

基于FPGA的串口控制器设计外文文献翻译、中英文翻译

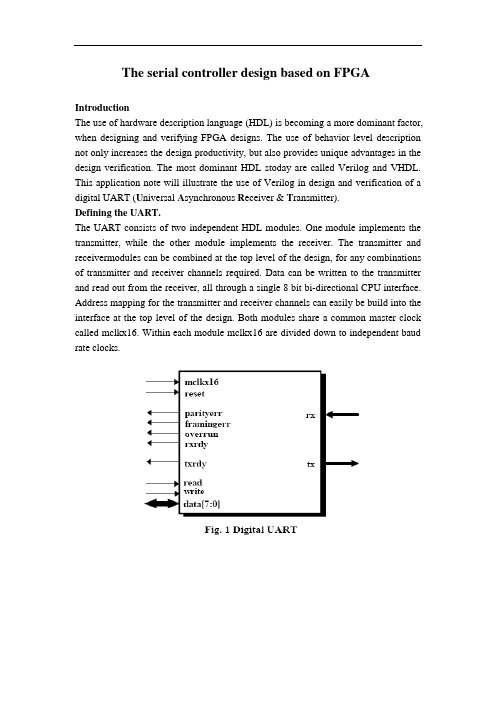

The serial controller design based on FPGAIntroductionThe use of hardware description language (HDL) is becoming a more dominant factor, when designing and verifying FPGA designs. The use of behavior level description not only increases the design productivity, but also provides unique advantages in the design verification. The most dominant HDL stoday are called Verilog and VHDL. This application note will illustrate the use of Verilog in design and verification of a digital UART (U niversal A synchronous R eceiver & T ransmitter).Defining the UART.The UART consists of two independent HDL modules. One module implements the transmitter, while the other module implements the receiver. The transmitter and receivermodules can be combined at the top level of the design, for any combinations of transmitter and receiver channels required. Data can be written to the transmitter and read out from the receiver, all through a single 8 bit bi-directional CPU interface. Address mapping for the transmitter and receiver channels can easily be build into the interface at the top level of the design. Both modules share a common master clock called mclkx16. Within each module mclkx16 are divided down to independent baud rate clocks.UART functional overview.A basic overview of the UART is shown below. At the left hand side is shown “transmit hold register”,“transmit shift register” and the transmitter “control logic” block, all contained within the transmitter module called “txmit”. At the right hand side is shown the “receive shift register”, “receive hold register”and the receiver “control logic” block, all contained within the receiver module called “rxcver”. The two modules have separate inputs and outputs for most of their control lines, only the bi-directional data bus, master clock and reset lines are shared by both modules.UART timing diagrams.Below is shown, how data written to the “transmit hold register” gets loaded into the “transmit shift register”, and at the rising edge of the baud rate clock, shifted to tx output.The Transmitter module.The master clock called mclkx16 are divided down to the proper baud rate called txclk and equals to mclkx16/16. Data written in parallel format to the module are latched internally, and shifted in serial format to the tx output at the frequency of the baud rate clock. Data shifted to the tx output follows the UART data format shown in fig. 6.Behavioral description of the transmitter.The transmitter waits for new data to be written to the module. When new data are written a transmit sequence is initialized. Data that was written in parallel to the module gets transmitted as serial data frames at the tx output. When no transmit sequence are in place, the tx output is held high.Implementation of the transmitter module.Internal signals in Verilog are declared as “wire” or “reg” data types. Signals of the “wire” type are used for continuos assignments, also called combinatorial statements. Signals of the “reg” type are used for assignments within the Verilog “always” block, often use for sequential logic assignments, but not necessarily. For further explanation see a Verilog reference book. Data types of the internal signals of the module can be referred to in table 3.We have now passed by all necessary declarations, and are now ready to look at the actual implementation. Using hardware description language allows us to describe the function of the transmitter in a more behavioral manner, rather than focus on it’s actual implementation at gate level.In software programming language, functions and procedures breaks larger programsinto more readable, manageable and certainly maintainable pieces.A Verilog function and task are used as the equivalent to multiple lines of Verilog code, where certain inputs or signals affects certain outputs or variables. The use of functions and tasks usually takes place where multiple lines of code are repeat edly used in a design, and hence makes the design easier to read and certainly maintain.A Verilog function can have multiple inputs, but always have only one output, while the Verilog task can have both multiple inputs, and multiple outputs. Below is shown the Verilog task, that hold all necessary seque ntial statements, to describe the transmitter in the “shift” mode.We here see the two tag bits called tag1 and tag2 concatenated to the “transmit shift register.Similar tasks were created to describe the transmitter in “idle” and “load”modes.By using these Verilog tasks, we can now create a very“ easy to read”behavioral model of the hole transmit process.If tx done and tx datardy both are true, the transmitter enter load mode. Next to the lo ad mode, the transmitter enters shift mode. At the rising edge of the baud rate clock, the contents of tsr are shifted to the tx output. Parity generation takes place during shifting of the tsr, as shown below.Simulation of a transmit sequenceThe contents of the data bus are latched into thr at the rising edge of write. At the next rising edge of txclk, the contents of thr are loaded into tsr, the active low start bit is a asserted to tx, and the txrdy flag indicates, that thr again is ready for new data to be written. At each rising edge of txclk, the contents of tsr is shifted to tx. Parity generati on takes place during shifting of data. Parity cycle is high one cycle next to last cycle, and tx gets the parity result.The Receiver module.The master clock mclkx16 are divided down to the proper baud rate clock called rxclk, and equals to mclkx16/16. Serial data to be received at the rx input of the module,mu st follow the UART data format. Data received in serial format can be read out inparallel format, through the 8 bit data bus.Behavioral description of the receiver.Between successive transmissions, the transmission line is held high, according to standard UART behavior. The receiver waits in “idle” mode for the rx input to go low. At the falling edge of rx the receiver enter “hunting” mode, now searching for a validstart bit of a new data frame to be received. If a valid start bit is detected, the receiver enter “shift data” mode. During receive of a data frame, various parity and error checks are performed. When a complete data frame has been received the receiver returns to idle mode. The basic operation of the receiver works as shown below.Implementation of the receiver module.In order to create an easy to read and easy to maintain behavioral model of the recei ver two Verilog tasks are written to describe the different modes of the receiver. The Verilog tas k called “idle_reset” holds all necessary sequential statements to describe the receiver at reset condition, and when the receiver is in it’s idle mode.When the receiver is not at it’s reset condition, and not in it’s idle mode, the receiver samples data at the rx input, shifts the data to the “receive shift register”, and generates parity based on the incoming data. The Verilog task called “shift_data” holds all necessary sequential statements to describe all above actions.Using the two Verilog tasks described above, we are now able to create the behavioral level description of the receiver at it’s reset condition, idle mode or when shifting in date . All above actions is synchronous to the baudrate clock called rxclk, and the im plementation is shown below.A complete data frame has been received, when the leading low start bit reaches rsr[0], and the receiver returns to idle mode again at the next rising edge of rxclk. At return to “idle” mode the receiver raises the “receive data ready” interrup t to indicate, that the new data received now can be read out in parallel format. Error flags are updated as well upon return to “idle” mode, and cleared when data are read out of the receiver. At the falling edge of read, the contents of the rhr are latched to the data bus. In table 8 shown below are the various error checks supported by the receiver.Simulation of a receive sequence.Between successive transmissions, the transmission line is held high. At the falling edge of rx input, the internal rxcnt starts counting up, synchronous to mclkx16. If rx input stays low for 8 cycles of mclkx16, the internal status bit idle is reset, and there by enable generation of rxclk. Rxclk is now synchronized to the center point of the l ow start bit. At the rising edge of rxclk, data are shifted from the rx input to rsr. When the leading low start bit reach rsr[0], the next rising edge of rxclk forces idle high aga in and there by disable generation of rxclk.At return to idle mode, the contents of rsr are loaded into rhr, the status flags are updated. The flag “rxrdy” now indicates, that the contents of rhr can be read out. At the falling edge of read, the contents of rhr are applied to the data bus.Using Hardware Description Language for Simulation.We have now studied how HDL can be used for the behavioral level design impleme ntation of a digital UART. While HDL make the design implementation easier to read and hopefully to understand as well, it also provides the ability to easily describe dep endency in between various processes that usually occur in such a complex event dri ven systems, as for example the UART. This ability to describe dependency in betwe en various processes is extremely need for simulation purposes as we will see very so on.Simulation stimulu s in Verilog HDL is called a “test fixture”. A test-fixture is a Verilog module that holds all lines of HDL code necessary to generate the simulation stimulus, while it at the same time port maps these signals to the design that are to be simulated. The port mapping is done by hierarchical module instantiation of the UAR T top level module into the test-fixture, as shown below.This allows simulation stimulus to be applied to the inputs of the design, while monit oring the outputs of the design. Input stimulus can be made conditionally to the response on the outputs ect. In fig. 19 shown below is illustrated, how the test-fixture port maps to the top level of the UART.Within the test-fixture the tx output of the transmitter module is looped back to the rx input of the receiver module. This allows the transmitter module to be used as test sig nal generator for the receiver module. Data can be written in parallel format to the tra nsmitter module and looped back in serial format to the rx input of the receiver modu al and data received can finally be read out in parallel format from the receiver modu al. In order to automate the testing of the UART as much as possible, tree independent Verilog tasks were written as follows. The Verilog task“write_to_transmitter” holds all necessary statements required to generate a single parallel data write sequence to the transmitter module. Data that are written to the transmitter upon execution of the “write_to_transmitter” task, get latched internal to the test-fixture for later analysis. The Verilog task “read_out_receiver” holds all necessary statements required to ge nerate a single parallel data read out sequence from the receiver module. Data that are read out of the receiver upon execution of the “read_out_receiver” task, get latchedinternal to the test-fixture for later analysis. The Verilog task “compare_data” holds all necessary statements required to compare the previous data written to the transmit ter module, to the corresponding and most recent data received and read out from the receiver module. If any discrepancy occurs, the “compare_data” task flags for an err or by writing out the data values that were written to the transmitter module, as well as the corresponding data values that were received by and read out from the receiver module.Silicon for synthesis.While HDL as design implementation method offers several advantages over traditio nal FPGA design entry approaches such as schematic capture, it meanwhile require great flexibility as well as high performance by the target devices for the synthesis flow. The synthesis flow for the UART has been targeted two flexible and high perfo rmance FPGA architectures available from QuickLogic, called the pASIC-1 and the pASIC-2 families.After synthesis, the design were placed & routed using the Place & Route tools from QuickLogic. After the Place & Route, the UART design were simulated using back-annotated Verilog post-layout timing models. The fast Verilog simulator called Silos III from Simucad were used for the post-layout simulation. All used tools are available within the QuickWorks tool suite from QuickLogic.基于FPGA的串口控制器设计简介使用硬件描述语言 (HDL) 设计和开发验证FPGA成为当前的主流因素。

基于FPGA的智能串口模块设计

基 于 F G 的 智 能 串 口模 块 设计 PA

基于 F G P A的智能串 口模块设计

De in o ne l e tSe i lP r Mo l s d o F GA sg f It lg n r o t i a due Ba e n P

杨 茂 林 ( 江苏自动化研究所, 江苏 连云港 2 2 0 ) 2 0 6

s il or at rns s i ,e cig a ce fda a ls i te tan m iso pr es er p t a d a ta misonr du n ch n o t o s n h r s s in oc s

Ke wors: r l r, t l y d sei poti el a n i t m a t C1 PGA gen, Co pc P . F

R 2 2标 准是 美 国 EA( 子 工 业 联 合 会 ) B L S3 I 电 与 E L公 司一 起 开 发 的通 讯 协 议 。 目前 已经 广 泛 地 应 用 于计 算 机 与终 端 或 外

设 之 间 的 近端 连 接 。

电源 ,模 块 将 从 连 接 器 输 入 的 5 电源 转 换 为 F G 适 用 的 电 V PA 源。 本设计中 F G 通过 3 b/3 在 PA 2 i3 MHz的 P I 线 与 主模 块 t C总 交换 数 据 。本 板 的手 动复 位 输 入 信 号 与 来 自连接 器 的 系统 复 位 信 号 一 起 作 为 复位 控 制 电 路 的 输 入 ,复 位控 制 电路 的输 出 直 接 连接 到 F GA。从 F GA 扩展 出 的 4路 串 口信号 经 过 光 电隔 离 P P

芯片( P 9 5 ) 如 CI 2 i 0  ̄合使 用 , 由主机 通 过 P I C 总线 对 数 据传 输 进 行 管理 。 种设 计 存在 两 个 问题 。 一个 问 题是 , 这 第 当计算 机 处理 的

基于FPGA的串口通信电路设计与实现

基于FPGA的串口通信电路设计与实现摘要:由于现代工业企业中在线监测的日益增长。

需要PC机与更多设备进行通信,串口通信具有实现简单,使用灵活。

数据传输准确等优点。

在工业监控和实时监控系统中得到了广泛应用。

由于监测设备的增加。

PC机原有的串口不能再满足通信的需求,传统的设计方法是使用硬件扩展八个串口,但是额外增加了硬件设计成本和实际编程的难度。

然而FPGA的UARTIP可灵活定制的优点使得基于黜的设计方法无需额外的硬件串口扩展,减少了硬件开发调试的难度,同时满足串行传输的要求。

基于此,本文主要对基于FPGA的串口通信电路设计与实现进行分析探讨。

关键词:基于FPGA;串口通信;电路设计;实现1、前言FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路领域中一种半定制电路出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA中具有丰富的触发器和I/O口,采用描述语言(VHDL和VerilogHDL)进行设计,用户可以根据需要,描述出具有各种功能的电路。

基于以上原因,我们可以利用FPGA实现多串口通信中的数据转换和中断控制功能,从而简化电路、缩小PCB面积,也可以很方便的进行升级改动和模块移植。

2、设计要求整个设计的硬件电路以DSP和FPGA为主构架,DSP和FPGA之间通过DSP的EMIF接口连接。

其中,DSP是主处理器,用于实现串口数据的处理,FPGA作为DSP的外围电路,实现UART模块的串行数据的接收和发送、数据的串并/并串转换及接收中断的产生,同时,实现多串口的中断控制功能。

当有接收数据时,FPGA通过中断方式通知DSP。

UART模块的数据格式:波特率可以按标准波特率设置;按字节接收,每个字节前包含一个起始位(低电平,逻辑值0),无校验位,最后是一位停止位和不定长度的空闲位(高电平,逻辑值1);接收到一个完整字节后产生一个中断(高电平,逻辑值1),当数据被读取后,中断信号复位(低电平,逻辑值0)。

一种基于FPGA的多路串口控制器设计

理, 利用 F P G A灵 活性 的优 势 , 读取 C o m p a c t F l a s h上 的 经 处理 过 的数 据 , 并 通过 相 应 串 口同 时发 送 。 实

验结果显示 , 该方案实现简单 , 每 个文件对应的 串口发送数据准确 , 系统运行稳定可靠, 解决了单片机 串 口资源有 限的 问题 , 为一 些类似 应 用提供 了参考 。 关 键词 : F P G A; 文件 处理 ; C F卡 ; 多路 串口 中 图分 类 号 : T P 3 3 6 文献 标识 码 : A 文章 编号 : 1 0 0 0—8 8 2 9 ( 2 0 1 3 ) 0 9— 0 1 3 7— 0 3

De s g i n o f Mu l t i ・ Cha n ne l S e r i a l Co n t r o l l e r Ba s e d o n FPGA

X I O N G H a i - j u n , WA N G Y a o — q i n g

p r o b l e m o f l i mi t e d s e ia r l po ts r o f mi c r o c o n t r o l l e r . Th e r e f o r e , i t c a n p r o v i d e a r e f e r e n c e f o r s o me p r a c t i c a l a p p l i —

Ab s t r a c t : C o n s i d e i r n g t h e l i mi t e d r e s o u r c e s o f mi c r o c o n t r o l l e r c h i p s e i r a l p o r t s , i t i s d i ic f u l t t o me e t t h e n e e d s o f s o me p r a c t i c a l a p p l i c a t i o n s , a n i mp l e me n t a t i o n s c h e me i s d e s i g n e d t h a t t h e d a t a c a n b e s e n t t h r o u g h C O I T e — s p o n d i n g s e i r a l p o r t s a t t h e s a me t i me . T h e d e s i g n s c h e me i s d e s c ib r e d i n d e t a i l a b o u t h o w t o p r o c e s s t h e d a t a

基于某FPGA地串口通信设计

基于FPGA的UART设计与实现0引言通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART)可以和各种标准串行接口,如RS 232和RS 485等进行全双工异步通信,具有传输距离远、成本低、可靠性高等优点。

一般UART由专用芯片如8250,16450来实现,但专用芯片引脚都较多,内含许多辅助功能,在实际使用时往往只需要用到UART的基本功能,使用专用芯片会造成资源浪费和成本提高。

一般而言UART和外界通信只需要两条信号线RXD和TXD,其中RXD是UART 的接收端,TXD是UART的发送端,接收与发送是全双工形式。

由于可编程逻辑器件技术的快速发展,FPGA的功能日益强大,其开发周期短、可重复编程的优点也越来越明显,在FPGA芯片上集成UART功能模块并和其他模块组合可以很方便地实现一个能与其他设备进行串行通信的片上系统。

FPGA(Field Programmable Gate Array)现场可编程门阵列在数字电路的设计中已经被广泛使用。

这种设计方式可以将以前需要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活性。

1 UART 功能设计1.1UART的工作原理异步通信时,UART发送/接收数据的传输格式表1所示,一个字符单位由开始位、数据位、停止位组成。

表1 UART发送/接收数据的传输格式异步通信的一帧传输经历以下步骤:(1)无传输。

发送方连续发送信号,处于信息“1”状态。

(2)起始传输。

发送方在任何时刻将传号变成空号,即“1”跳变到“O”,并持续1位时间表明发送方开始传输数据。

而同时,接收方收到空号后,开始与发送方同步,并期望收到随后的数据。

(3)奇偶传输。

数据传输之后是可供选择的奇偶位发送或接收。

(4)停止传输。

最后是发送或接收的停止位,其状态恒为“1”。

发送或接收一个完整的字节信息,首先是一个作为起始位的逻辑“0”位,接着是8个数据位,然后是停止位逻辑“1”位,数据线空闲时为高或“1”状态。

FPGA芯片的抗强电磁干扰串口控制器设计

F PG A芯片的抗强电磁干扰串口控制器设计*张旭,彭月祥(北京工业大学理学部,北京100124)*基金项目:国家重大科研仪器研制项目资助 大气中N O x /P A N /C C l 4在线分析仪的研制(41727805)㊂摘要:为了增强抗干扰能力,提升电子控制系统稳定性,设计了一种基于F P G A 的R S 485抗干扰串口控制继电器核心板,采用F P G A 芯片来实现串口数据的读取和继电器控制㊂串口接收部分使用7选4表决器实现物理层抗干扰,并且使用C R C 校验和可靠协议进行通信㊂最终仿真测试和实际干扰测试表明,该系统具有一定的抗干扰能力㊂关键词:F P G A ;抗干扰;R S 485;E P 4C E 6E 22C 8中图分类号:T P 23 文献标识码:AD e s i g n o f A n t i -e l e c t r o m a gn e t i c I n t e r f e r e n c e S e r i a l P o r t C o n t r o l l e r B a s e d o n F P G A Z h a n g X u ,P e n g Y u e x i a n g(F a c u l t y o f S c i e n c e ,B e i j i n g U n i v e r s i t y o f T e c h n o l o g y ,B e i j i n g 100124,C h i n a )A b s t r a c t :I n o r d e r t o e n h a n c e t h e a n t i -i n t e r f e r e n c e a b i l i t y a n d i m p r o v e t h e s t a b i l i t y o f t h e e l e c t r o n i c c o n t r o l s ys t e m ,a n F P G A -b a s e d R S 485a n t i -i n t e r f e r e n c e s e r i a l p o r t c o n t r o l r e l a y c o r e b o a r d i s d e s i g n e d ,a n d t h e F P G A c h i p i s u s e d t o r e a l i z e t h e s e r i a l p o r t d a t a r e a d i n g an d r e l a y c o n t r o l .T h e r e c e i v i n g p a r t o f t h e s e r i a l p o r t u s e s 7-c h o s e n 4v o t e r t o a c h i e v e p h y s i c a l l a ye r a n t i -i n t e rf e r e n c e ,a n d u s e s C R C c h e c k a n d r e l i a b l e p r o t o c o l f o r c o mm u n i c a t i o n .F i n a l l y ,t h e s i m u l a t i o n t e s t a n d a c t u a l i n t e r f e r e n c e t e s t s h o w t h a t t h e s y s t e m h a s a c e r t a i n a n t i -i n t e r f e r e n c e a b i l i t y.K e yw o r d s :F P G A ;a n t i -i n t e r f e r e n c e ;R S -485;E P 4C E 6E 22C 80 引 言串口控制继电器模块是一种可通过串口指令来控制其内部继电器通断的装置,由于很多自动化设备中经常会用到串口控制继电器,但在某些强电磁干扰场合(如汽车火花塞[1]㊁电压击穿设备[2]启停等),经常会出现串口数据丢失㊁误码㊁M C U 重启甚至死机等现象㊂由于F P G A 具有很高的可靠性[3],可增强其在恶劣环境下的表现,而信号为差分形式的R S 485通信方式也可抑制共模电信号干扰,使其在短距离㊁中距离通信中具有高于R S 232的可靠性,并且本身与U A R T 兼容,因此研发了基于F P G A和R S 485的抗干扰串口控制继电器核心板,在数据链路层使用可靠的通信协议,并编写t e s t b e n c h 进行仿真通信测试,最终干扰测试结果表明,该系统具有一定的抗干扰能力㊂1 设计方案1.1 硬件设计硬件设计使用两层电路板作为主控板,在空间充足的基础上降低了成本,F P G A 芯片采用A l t e r a 公司(被英特尔收购)的C yc l o n e I V 系列E P 4C E 6E 22C 8作为主控F P -G A 芯片,该芯片拥有6272个逻辑门㊁144个引脚㊂收发器采用MA X 485作为R S 485物理层芯片,其电源为5V 供电,传输速率可达2.5M b p s ,可以满足绝大多数场合,电源采用5V 供电,然后使用线性稳压芯片进行3.3V ㊁2.5V 和1.2V 供电㊂1.1.1 原理图设计硬件原理图使用A l t i u m d e s i gn e r 进行设计,A l t i u m d e s i gn e r 系列软件是当前较流行的电路设计软件,使用该软件可以在单个应用程序内完成整个P C B 的开发[4],成本较低,开发周期相对较短㊂下面列出F P G A 最小系统中比较重要的几部分㊂F PG A 最小系统中使用的电源由U S B 5V 供电或用端子额外接5V 电源,经过开关之后再通过电容滤波,原理图如图所示㊂图1 电源接口和滤波电平转换芯片为线性稳压芯片A M S 11173.3㊁A M S 11171.2和A M S 11172.5,提供线性稳压㊂M A X 485电路如图2所示,其中端接电阻为经典值120Ω㊂由于F P G A 内部为R AM 结构,掉电之后程序会丢失,因此需要外置配置芯片,E P C S 4作为A l t e r a 的专用配置芯片,容量为4M B ,已经足够,因此选择E P C S 4作为图2 M A X 485模块原理图F PG A 的外置配置芯片,原理图如图3所示㊂图3 E P C S 4原理图F PG A 和继电器部分总共连接7条信号线(见图4左),继电器部分通过组排和7个三极管对应7个继电器,其中包含5个机械继电器㊁两个固态继电器㊂机械继电器对应7个24V 通断端口㊂图4 外设原理图1.1.2 P C B 绘制原理图设计好后,进行P C B 的绘制以及走线,由于使用的是两层板,因此只将重要引脚引出,并且尽量走线在t o p 层,将F P G A 电源电容贴在芯片背后,以增强滤波能力,最终P C B ㊁3D 模型和实物图如图5所示㊂1.2 F P G A 模块设计F PG A 的功能为接收R S 485数据,解析协议并向下控制继电器动作,因此F P G A 内部电路分为以下几个模块:串行收发模块㊁解协议模块㊁继电器控制模块,分别对应协议的中层和上层㊂图5 P C B ㊁3D 模型以及实物图1.2.1 串行收发模块由于R S 485底层为半双工通信,因此用串行收发模块将接收和发送模块封装到一起,其内部集成串行接收和发送模块,串行发送模块结构较简单,为简单发送序列机,因此不再赘述㊂接收模块采用7选4表决器方法滤除相关的干扰[5],将每一位数据拆分为16份,15个点取中间第5~11点做7选4表决,如图6所示㊂图6 采样示意图通过增加/R E 和D E 使能信号使发送和接收区分开,方法为将三态门默认高阻态,只有当发送计数器开始工作时才转换为发送,并且作为从机,只回复主机的命令,主机每条命令之间需至少间隔3条指令的时间,以便接收命令回复㊂1.2.2 解协议模块上位机需要在发送之前缓存指令,并且在收到回复之后清空缓存并发送下一条指令,若超时未收到回复(1.5倍指令时间),则重新发送该条指令,多次发送未回复则表明连接丢失㊂解协议模块将要发送的数据保存㊁识别并转换为可识别命令,继续向下发送㊂由于下位机需要进行C R C 校验,因此解协议模块端使用并行C R C 校验模块,由于命令只有前4字节需校验,因此收到第4字节之后将C R C 值保存,清空C R C 并等待下一命令进入㊂使用简单状态机控制,使用简单有限状态机共三种状态,状态转移如下::等待一字节信号输入,有信号输入则进入状态C H E C K ,无信号则t i m e o u t 计数器+1,若计数器时间到,则接收字节清零㊂②C H E C K :t i m e o u t 计数器置零,接收一字节信号,在此状态等待4个时钟信号,之后计数并返回WA I T 继续接收下一字节㊂等待状态使用c o u n t 来区分:c o u n t =0时,将接收到的信号存入移位寄存器;c o u n t =1时,将移位寄存器和命令+计算出C R C 校验码进行比较,若满足某一条则更改命令寄存器值;c o u n t =2时,若命令寄存器值不为0,则状态转移至S E N D ,否则等待;c o u n t =3时,返回WA I T 继续接收下一字节㊂③S E N D :下发命令,回复数据,接收字节数清零,状态转移至WA I T ㊂1.2.3 继电器控制模块继电器控制部分只需将接收到的命令存储在r e g 中并保存输出电平的高/低状态,实现部分代码如下:a l w a y s @(p o s e d g e s y s _c l k o r n e g e d g e s y s _r s t _n )b e gi n i f (!s ys _r s t _n ) r e l a y_o u t <=5'b 0; e l s e c a s e (c o mm e n d _r e g) 4'h 1:r e l a y _o u t [0]<=1'b 1; //继电器1~7吸合 4'h 7:r e l a y _o u t [6]<=1'b 1; 4'h 8:r e l a y_o u t [0]<=1'b 0; //继电器1~7断开 4'h e :r e l a y _o u t [6]<=1'b 0; d e f a u l t :; e n d c a s ee n d1.3 通信协议设计上位机发送:8位从机地址 8位功能号 8位数据地址 8位数据 16位C R C 校验下位机回复:8位从机地址 8位功能号 8位数据地址 8位数据 16位C R C 校验上位机若3个命令周期内未收到任何回复,则下条指令继续发送此命令,直到回复正确,若连续发送10次仍未回复(约0.25s),则表明连接丢失,应通知上层㊂地址:F P G A 下位机地址设为0x 40,A S C I I 码为 @ ㊂功能号:操作继电器为0x 4A ,A S C I I 为大写 J㊂数据地址:0x 31~37表示1~7的7个继电器,其中36㊁37为固态继电器,A S C I I 分别为数字1~数字7㊂0x 38表示对全部继电器的操作㊂数据:0x 30表示关,0x 31表示开,A S C I I 分别为数字0和㊂例如,上位机发送:0x 40,0x 4A ,0x (31~37),0x (30~31),16位校验㊂下位机回复:0x 40,0x 4A ,0x (31~37),0x (30~31),16位校验㊂此协议为可靠连接,便于扩展,类似于M o d b u s 协议,可挂载于R S 485总线上㊂1.4 资源优化在F P G A 设计时,为了节省F P G A 内部逻辑门使用数量,以便增强此系统移植性,一般在设计时进行资源优化设计[6]㊂为了减少使用逻辑门数,可采用单C R C 校验模块,即收/发均使用单一C R C 校验模块,可节省104逻辑门,其中d e c o d e 占用337逻辑门㊁r e l a y 占用21逻辑门㊁U a r t 485占用298逻辑门,最终逻辑门如图7所示,占用资源仅为10%左右,说明此系统占用资源较少㊂2 仿真与测试为了验证此设计的正确性以及抗干扰能力,首先进行图7 优化后总体资源使用情况逻辑仿真测试,编写t e s t b e n c h 进行测试,t e s t b e n c h 命令为:继电器从1~7轮番开启并关闭一次,经仿真得出图8㊂由图可得出结论:总共发送14条命令,每次发送命令之后均有回复和继电器动作,说明逻辑仿真正常㊂图8 串口控制继电器逻辑仿真2.1 物理层干扰测试通过在t e s t b e n c h 中加入$r a n d o m 函数来产生随机噪声,代码如下:a l w a y sb e gi n r a n d =$r a n d o m%10;//产生一个在-10~10范围的随机数 T x _o u t =T x ; r e p e a t (20000)b e gi n #r a n d ; T x _o u t =T x ; e n dT x _o u t =~T x ; #r a n d ; T x _o u t =T x ; r e p e a t (20000)b e gi n #r a n d; T x _o u t =T x ; e n de n d通过改变r e pe a t 和r a n d o m 来产生强㊁弱两种干扰,仍然发送14条命令㊂将加扰之后的信号作为输入信号对系统稳定性进行测试,进行两组仿真,强弱干扰下的物理层抗干扰结果和其对比测试㊂得出仿真结果如下:在弱干扰下,经7选4表决的物理层14条命令可成功接收13条,强干扰下也可成功接收10条㊂相比之下,未经7选4表决的接收系统物理层,弱干扰下只能接收3条,强干扰下14条命令全部丢失㊂7选4表决在物理层抗干扰具有一定的优势㊂2.2 增加了上层协议的抗干扰测试在t e s t b e n c h 中加入读取数据的命令,并按协议所述增加重发,加强干扰状态下的仿真结果如图9所示㊂图9 增加了上层协议之后的抗干扰测试由图9可知,在增加了上层协议之后,14条指令全部传送成功,因此该抗干扰系统具有一定的效果㊂2.3 实际应用该装置现已作为项目 大气中N O x /P A N /C C l 4在线分析仪的研制 中P A N 标定方法研究设备中的一部分,在长时间的运行中未出现故障[7],说明此装置在实际运行中满足需求㊂3 结 语使用A l t i u m d e s i gn e r 绘制了基于F P G A 的抗干扰串口控制继电器的电路原理图和P C B 并且制板,通过q u a r -t u s 编写v e r i l o g 程序和te s t b e n c h 仿真文件,并使用m o d e -l s i m 进行仿真对比测试㊂测试结果表明,该系统在一定的噪声干扰下依然能够正常运行,并且在强电磁干扰下不会丢失命令,可将此系统应用于恶劣电磁环境的串口控制继电器中,可增强系统控制稳定性㊂该电子系统现已应用在P A N 自动标定系统中,效果良好㊂参考文献[1]唐静娴.汽车电器电磁干扰及防护的探讨[J ].科技与创新,2020(16):7778.[2]宁可庆,蒋林,薛连恺,等.绝缘材料电压击穿检测系统设计[J ].电子世界,2019(12):173174.[3]杨海钢,孙嘉斌,王慰.F P G A 器件设计技术发展综述[J ].电子与信息学报,2010,32(3):714727.[4]赵鸣宇.基于A l t i u m D e s i gn e r 的航空发动机振动监测硬件系统的研究[D ].天津:中国民航大学,2016.[5]张名淑,张雅迪,王旭,等.基于F P G A 的U A R T 抗干扰接收装置设计与实现[J ].信息技术与信化,2020(8):122124.[6]董秀洁,杨艳,周游.F P G A /C P L D 选型与设计优化[J ].化工自动化及仪表,2009,36(3):6063.[7]陈瑾一.P A N 分析仪的标定方法及标定系统的研究[D ].北京:北京工业大学,2020.张旭(硕士研究生),主要研究方向为F P G A 开发㊁计算机测控仪器仪表;彭月祥(副教授),主要研究方向为光电信息处理㊁计算机测控仪表开发等㊂(责任编辑:薛士然 收稿日期:2020-10-21) [8]田冰,王裕宜,洪勇.泥石流预报中前期降水量与始发日降水量的权重关系[J ].水土保持通报,2008,28(2):7175.[9]魏永明.降雨型泥石流(水石流)预报模型研究[J ].自然灾害学报,1997,6(4):4854,57.[10]李铁锋,丛威青.基于L o gi s t i c 回归及前期有效雨量的降雨诱发型滑坡预测方法[J ].中国地质灾害与防治学报,2006,17(1):3941.[11]丛威青,潘憋,李铁锋,等.降雨型泥石流临界雨量定量分析[J ].岩石力学与工程学报,2006(1):28082812.[12]李桥,巨能攀,黄健,等.基于主成分分析的P S O E L M 与A d a b o o s t 算法耦合模型在极震区泥石流物源动储量计算中的应用[J ].科学技术与工程,2020,20(15):59615970.[13]李璐,温宗周,张阳阳,等.基于R B F 神经网络滑坡灾害发生概率预报方法[J ].西安工程大学学报,2017(4):521526.[14]孔令智,高迎彬,李红增,等.一种快速的多个主成分并行提取算法[J ].自动化学报,2017,43(5):835842.[15]F u j i t s u L i m i t e d .A p pa r a t u s A n d M e t h o d F o r O n l i n e G e n e r a -t i o n o f A n O p t i m u m R o u t e G r a p h (U S P T O 10,401,185)[J ].C o m p u t e r s ,N e t w o r k s &C o mm u n i c a t i o n s ,2017(1).[16]C a r l o s E V a l e n c i a ,M a r c o s C V a r g a s .O p t i m u m m a t c h i n gs i n w e i g h t e d b i p a r t i t e g r a ph s [J ].B o l e t ín d e l a S o c i e d a d M a t e m át i c a M e x i c a n a ,2016,22(1).(责任编辑:薛士然 收稿日期:2020-10-21)e 络盟社区助力工程师拓展专业技能安富利旗下全球电子元器件产品与解决方案分销商e 络盟为其在线社区平台上的基础课程学习项目引入更多创新学习资源,涉及可实现高效功率转换的G a N F E T ㊁面向纯电动汽车/混合动力汽车(E V /H E V )应用的汽车传感器,以及飞行时间(T o F )传感器㊂e 络盟社区基础 课程项目由e 络盟与其重要合作伙伴联手共同打造,旨在帮助社区成员提升专业技能,便于他们及时掌握行业发展趋势及创新技术㊂新增 基础 课程模块包括:①G a N F E T ,实现高效功率转换(由N e x pe r i a 提供):随着全球向低排放汽车㊁可再生能源使用及更高工业自动化的目标迈进,业界对电源模块的性能和效率提出了更多新的要求,以提高电能转换效率驱动动态负载㊂本课程阐述了功率转换应用对电子元器件的要求,并分析了现有解决方案的局限性,以及G a N F E T 技术在可再生能源和电动汽车领域的巨大应用潜能㊂②T o F 传感器(由意法半导体提供):红外(I R )三角测量㊁激光㊁超声波和飞行时间(T o F )是数十年来各工程领域最常用的测距和检测方法,覆盖机器人㊁存在监测㊁光学导航㊁医疗科技和汽车应用等㊂该课程介绍了意法半导体T o F 接近检测和距离传感器及F l i g h t S e n s e 专利技术,能够让社区成员了解到T o F 传感器的基础知识㊁飞行时间测量方法㊁多种距离感测技术㊁T o F 传感器设计与挑战,以及多种场景应用㊂。

基于FPGA的串口通信控制器设计

引用 格式 : 贾亮 , 冀源 .基于 F P G A的 串 口通 信 控制器 设计 [ J ] . 微型 机与应 用 , 2 0 1 6, 3 5 ( 2 2 ) : 3 3 ・ 3 5 , 3 9 .

De s i g n o f s e r i a l c o mmu n i c a t i o n c o n t r o l l e r b a s e d o n F PGA

于低 速 率 异 步 通 信 。

关键 词 : U A R T 串口通信 ; F P G A;V H D L; R S 2 3 2

中图分类 号 : T N 9 1 4 . 3 文献标 识码 : A D O I : 1 0 . 1 9 3 5 8 / j . i s s n . 1 6 7 4 - 7 7 2 0 . 2 0 1 6 . 2 2 . 0 0 9

s i mul a t e d b y Mo de l s i m s o f t wa r e. Fi na l l y,t he pr o g r a m wa s b u r nt a n d wr i t t e n o n c h i p.Af te r t e s t i ng a n d ve r i f i ng by s e r i a l p o r t a s s i s t a n t ,t he e x —

Har d wa r e a n d Ar c hi t e c t ur e

基于 F P G A 的 串 口通 信 控 制器 设 计

贾 亮 , 冀 源

( 1 . 沈 阳航 空 航 天 大 学 辽 宁省 通 用 航 空重 点 实 验 室 , 辽宁 沈 阳 1 1 0 1 3 6 ;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的串口控制器设计

简介

使用硬件描述语言 (HDL) 设计和开发验证FPGA的成为当前的主流因素。

使用行为级描述不只增加了产品的设计效率,也在设计中有独特的验证方式。

目前最流行的HDL语言为Verilog 和 VHDL。

这篇文章将会举例说明用 Verilog语言的设计和验证数字异步串行收发器UART。

UART介绍

通用异步串行收发器UART中有二个独立的VHDL模块。

一个模块实现发射功能, 当另一个实现接收功能,发射和接收功能模块在顶端设计时组合到一起使用,接收和发射的组合是通信通道所必需的。

数据写入发射器,从接收器读出,所有的数据是以二进制8字节的信号通过CPU接口。

在顶端设计时,地址有发射器映射,而且接收器通道能容易地建立从儿进入接口,两者工用一个称为mclkx 16主控时钟,在每个模块中 mclkx 16 被分成独立的波特率时钟。

UART的功能概况

UART的基本功能概况见下表. 在左边显示传输保持记录,移位记录,传输控制时钟,全部集中在发射机的txmit端。

在右边的是显示接收移位寄存器, 接收记录和控制逻辑时钟,所有都包含在接收模块的rxcver端,这两个模组都单独的投入与产出,大部分的控制线,只有双向数据总线, 主时钟和复位线共享的模块。

顶层UART系统的I/O功能描述

UART的标准数据格式

图3显示了UART的串行数据格式,串行数据包含在帧8个数据字节,以及编码信息比特,在连续传输线路高通,在传输初始化时开始低一点.,接下来的低一点开始到8比特的数据信息, 低位对于后边高位有重要的作用。

然后后边的8 bits数据进行奇偶校验 ,反馈8位数据的结果。

UART时序图

下面显示怎么将从寄存器里出来的数据写给移位寄存器,并在上升沿速率时钟时,转向tx输出。

发送时间如下表,如何得到数据从rx传输到接收移位寄存器然后存储。

发送器

主控时钟称为mclkx16,分频成正确的等于mclkx16/16的txclk波特率。

数据以平行的形式锁存模块,而转向以串行格式的tx输出波特率时钟频率。

数据转到tx输出跟随串行数据格式显示在图6。

发送器行为描述

发送器等待新的数据来写入模块,新的数据在发送器初始化后发送。

数据以并行方式传送串行数据帧的tx输出. 当没有传输序列的地方, tx输出是高通。

发送器实现

产生逻辑的Verilog始于模块端口的声明,这里定义的信号,是移植到从单元,没有方向指明这一点。

在下一个端口定义来自端口的方向,方向指定为输入,输出或(双向) ,见表1。

指明端口方向来声明内部信号,内部信号的Verilog称为wire和reg数据类型,WIRE被数字低音的分配,REG用在分配Verilog里的always时钟,座,常常使用逻辑顺序的分配,但不是一定的,进一步解释见Verilog参考书,数据类型的内部信号如表3 。

我们现在已经通过了所有必要的声明,并已作好准备,看看实际执行,用硬件描述语言使我们描述的功能的发送器更加行为化, 而不是把重点放在它门级。

在软件编程语言,职能和工作程序分成更具可读性和易处理,一个Verilog 的功能及任务是作为相当于复线Verilog代码, 如果某些输入信号或某些影响产出或变数. 使用的职能和任务,通常发生在多行代码都是重复使用的设计, 从而使得设计易于阅读和维护肯定,一个Verilog的功能,可以有多种输入,但始终只有一个输出, 虽然Verilog任务可以兼得多投入,多产出,甚至在某些情况下, 非取长补短,下面显示了Verilog任务,即拥有所有必要的顺序语句,用来描述发送器的转移模式。

我们可以看到在移位寄存器有2个标志位tag1和tag2,在描述空闲和置位模块时产生相同的作用,使用这些 Verilog 工作, 现在我们可以产生一个容易阅读的行为模型的空穴传输过程。

如果txdone and txdatardy都是正确的,进入发送器负荷模式. 接下来的负载模式下,进入发送模式转变.,在上升沿的速率时钟,内容tsr转移到tx输出. 奇偶校验过程产生于tsr变化中,如下所示。

重要的一点,就是tsr为零发生在传输过程,在不同的数据传输时标志位tag 和tsr赋零。

传输序列的模拟

在写上升沿时数据总线容量被锁存,在下一上升沿txclk,thr的容量载入tsr,低电平开始位进入tx,发送标志位显示,thr再次等待新的数据的写入。

在每个发送时钟上升沿,tsr的容量被送入tx,在数据传输过程中发生奇偶校验,周期循环时奇偶校验为高,tx产生奇偶检验结果。

接收模块

主控时钟mclkx16分频到合适的波也率时钟称为rxclk,它等于mclkx16/16 . 串行数据为收到的rx输入模块,要按照UART的数据格式显示为图3,收到的数据格式以并行形式读出,通过8位数据总线。

接收模块行为描述

在连续发送时,发送保持高,根据标准异步串行UART,接收器在等待闲置模式的rx输入要低,在rx下降沿接收进入保持模式,现在寻求一种有效的开始位等待新的数据帧的到来,当有效的开始位被检测到时,接收器回到闲置模式,在接收一个数据帧,各种校验和检查错误,当一个完整的数据帧收到接收端返回待机模式.,接收器基本运作如下所示。

接收频率为mclkx16,和第一上升沿的rxclk常常发生在中心点开始位,如下图显示,对于中心点的起始位及后边的数据字节,波特率时钟是同步。

接收器模块的实现

为了产生一个易读易操作的接收器模块,用两中Verilog功能来描述不同的接收方式,当接收在空闲状态时,其中一个Verilog称为空闲复位,而它需要所有必要的顺序语句来描述接收机复位条件。

当接收器不在复位状态,也不在空闲状态下,rx输入端的采样数据,传输到移位寄存器中,在进入的数据中产生奇偶校验位,另外一个Verilog称为数据移位,需要所有必要的顺序语句来描述上述行为。

利用两个Verilog实现上述功能,现在在复位状态,空闲状态或者数据传输状态,我们可以产生行为级描述的接收器,所有上述行为是和接收时钟同步的,它们的实现如下所示。

当低电平开始位到达rsr[0]时,一个完整的数据帧将会给接收到,在下一个接收时钟上升沿到来是又回到空闲状态,当返回空闲状态时,接收器显示数据接收准备,然后数据以并行方式读出,错误的标识更新,并返回空闲状态,在数据读出后清除,在读下降沿,rhr的容量锁存在数据总线,表8所示接收器各种错误检查。

接收序列的模拟

在连续传输时线路高通,在rx输入下降沿,,内部rxcnt开始计数,和mclkx16同步,如果rx输入在mclkx16的 8个周期循环,内部空闲复位,接收时钟产生使能,和中心低开始位同步,在接受时钟上升沿,数据从RX传输到RSR,当低开始位到底rsr[0]时,在下一个接收时钟上升沿又被置空闲位,此时失效,在接收序列,刚好产生rxclk的11个周期,为采样一位低开始位,一位数据位,一位奇偶位,一位置高停止位。

在返回空闲状态,rsr被置入rhr,内部标志位更新,接收位产生,rhr容量给读出,在读下降沿,rhr应用到数据总线。

硬件描述语言仿真

我们现正研究如何HDL可用于行为级设计,实现了数字UART 。

在HDL进行设计的实施更容易阅读,并希望能理解, 它还规定,能够方便的描述依存度之间的各种程序,通常是发生在这样一个复杂事件驱动系统,例如UART,我们很快将看到这种依靠各种进程来描述的能力对于实现模拟是确实必须的。

Verilog语言中的模拟激励叫做测试工具,测试工具的Verilog模块,拥有各线路的HDL代码要生成仿真激励, 而在同一时间端口影射,这些产生的信号将会模拟。

端口影射是完成了被异步通用步收发传输器的级层模块实例化顶端水平进入测试工具,如下所示。

这使得仿真激励适用于输入的设计,同时检测输出的设计,输入激励,可以有条件地反应与输出,图19显示说明如何测试工具端口影射到UART的顶层。

在测试工具的输出的传输模块又循环到接收器的输入模块,这使得发送器模块用来作为测试信号发生器接收器模块,数据可以并行的方式向发送器,同时回送到输入的接收机模块,收到的数据最终从接收器以并行格式读出,为了尽可能实现UART的自动化测试,独立书Verilog功能如下,发送写入功能需要一切必要的声明来产生一个并行的数据写序的发送器,数据写入发送器来完成写入接收功能,锁存内部测试工具供以后的分析。

接收读出功能需要一切必要的声明来产生一个并行的数据写序的接收器,数据读出接收器来完成读出功能,锁存内部测试工具供以后的分析。

数据比较功能需要一切必要的声明来同先前写入发送器,相应的最新接收数据和接收模块读出的数据比较,如果发生任何误差,数据比较标志一个从发送器写出的数据定义错误,相应的数据也从接收模块接收和读出,有任何误差发生时,笔记比较数据功能将立即停止模拟仿真。

综合

HDL作为设计方法比传统的FPGA设计输入方式如原理图方式有若干优势,它同时规定了极大的灵活性以及高性能的目标装置的综合流程,UART综合流程已针对两个灵活和高性能的可编程逻辑器件FPGA系列,如pASIC-1和pASIC。

UART 设计和模拟的文件进入叫做使用HDL语言编辑器的Saros Technologies的turbow软件,HDL设计合成了快速高效的正确综合工具,综合以后,设计布局使用spde可编程逻辑工具,在布局之后,UART使用有标注的Verilog布局时序模块,快速Verilog仿真为来自Simucad的SilosIII后布局仿真,所有使用过的工具中可用的

工具来自于快速逻辑。

11。