基于FPGA的串口通信设计与实现

基于fpga的串口设计及实现

基于fpga的串口设计及实现

基于FPGA的串口设计及实现是一个涉及数字电路设计和通信协

议的复杂课题。

首先,让我们从串口通信的基本原理开始。

串口通信是一种通过串行传输数据的通信方式,它使用一个或

多个数据线(通常是一对)来逐位地传输数据。

常见的串口通信标

准包括RS-232、RS-485、UART等。

在FPGA中实现串口通信,需要

考虑以下几个方面:

1. 串口通信协议选择,根据具体的应用场景和需求,选择合适

的串口通信协议。

例如,UART是一种常见的串口通信协议,它使用

起始位、数据位、校验位和停止位来传输数据。

2. 串口通信接口设计,在FPGA中设计串口通信接口,需要考

虑数据的发送和接收,时钟信号的同步等问题。

通常需要使用FPGA

的IO资源来实现串口通信接口。

3. 串口通信协议的实现,在FPGA中实现选择的串口通信协议,包括数据的发送和接收、时序控制、校验等功能。

这通常需要使用Verilog或VHDL等硬件描述语言进行开发。

4. 硬件调试和验证,设计完成后,需要进行硬件调试和验证,包括时序分析、波形仿真等工作,确保串口通信的稳定和可靠。

在实际的FPGA串口设计中,还需要考虑时钟频率、数据传输速率、数据格式、数据校验、中断处理等问题。

此外,还需要考虑FPGA与外部设备的接口,如与传感器、显示器、存储器等设备的接口设计。

总之,基于FPGA的串口设计及实现涉及到硬件设计、数字电路设计、通信协议等多个方面的知识,需要综合考虑各种因素,进行全面的设计和实现。

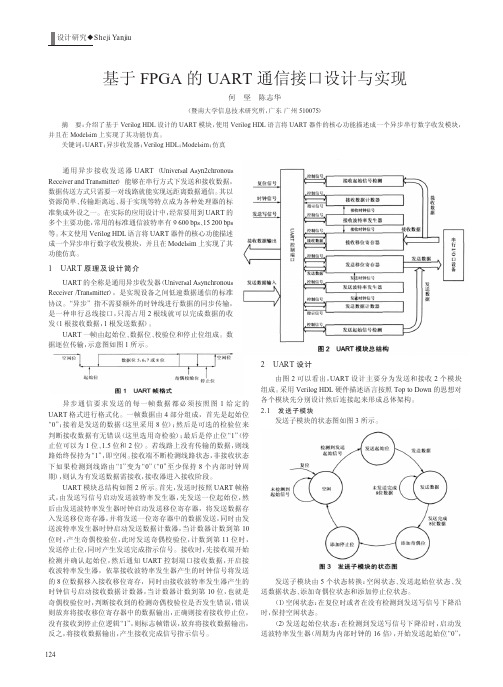

基于FPGA的UART通信接口设计与实现

通用异步接收发送器UART (Universal Asyn2chronousReceiver and Transmitter )能够在串行方式下发送和接收数据,数据传送方式只需要一对线路就能实现远距离数据通信。

其以资源简单、传输距离远、易于实现等特点成为各种处理器的标准集成外设之一。

在实际的应用设计中,经常要用到UART 的多个主要功能,常用的标准通信波特率有9600bps 、15200bps 等。

本文使用Verilog HDL 语言将UART 器件的核心功能描述成一个异步串行数字收发模块,并且在Modelsim 上实现了其功能仿真。

1UART 原理及设计简介UART 的全称是通用异步收发器(Universal Asynchronous Receiver /Transmitter ),是实现设备之间低速数据通信的标准协议。

“异步”指不需要额外的时钟线进行数据的同步传输,是一种串行总线接口,只需占用2根线就可以完成数据的收发(1根接收数据,1根发送数据)。

UART 一帧由起始位、数据位、校验位和停止位组成。

数据逐位传输,示意图如图1所示。

异步通信要求发送的每一帧数据都必须按照图1给定的UART 格式进行格式化。

一帧数据由4部分组成,首先是起始位“0”;接着是发送的数据(这里采用8位);然后是可选的检验位来判断接收数据有无错误(这里选用奇检验);最后是停止位“1”(停止位可以为1位、1.5位和2位)。

若线路上没有传输的数据,则线路始终保持为“1”,即空闲。

接收端不断检测线路状态,非接收状态下如果检测到线路由“1”变为“0”(“0”至少保持8个内部时钟周期),则认为有发送数据需接收,接收器进入接收阶段。

UART 模块总结构如图2所示。

首先,发送时按照UART 帧格式,由发送写信号启动发送波特率发生器,先发送一位起始位,然后由发送波特率发生器时钟启动发送移位寄存器,将发送数据存入发送移位寄存器,并将发送一位寄存器中的数据发送,同时由发送波特率发生器时钟启动发送数据计数器,当计数器计数到第10位时,产生奇偶校验位,此时发送奇偶校验位,计数到第11位时,发送停止位,同时产生发送完成指示信号。

基于FPGA的串口通信设计与实现

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

基于FPGA的串口通信设计与实现

2017年11月基于FPGA的串口通信设计与实现王闽,张静(南京熊猫汉达科技有限公司,210014)【摘要】此次研究重点分析FPGA的串口通信设计和实现的过程,在分析相关问题的过程中,充分的了解FPGA实现RS232串行数据通信的具体方案,明确这种方案的实行对UART模块化设计的影响,从根本上避免UART芯片的复杂性,同时克服移植性较差产生的弊端。

【关键词】FPGA;UART;通信设计;实现方案【中图分类号】TN791【文献标识码】A【文章编号】1006-4222(2017)22-0052-01因为串行接口的应用相对宽泛,所以为了更好的体现出相应的通信功能,多是采用专用的串行接口芯片,这样的目的就是为实现相关的功能提供保障,但是此类接口芯片还是存有较多的问题,如体积较大、接口复杂、成本较高等,导致某些硬件在具体设计的过程中更加复杂,因此结构及功能已经保持固定,难以依照实际的需要展开设计,更无法实现对其逻辑控制的灵活修改。

1串口通信协议的基本概述设备处理器主要是对串行通信的数据进行接收并发送,整个过程离不开主要的器件,这种器件必须要完成对串行数据的转换,同时还应该对并行的数据展开处理,UART通用异步收发器的使用是关键。

UART可以及时的将计算机内部的并行数据转换为需要输出的串行数据流,同时也可以将计算机外部收集的相关串行数据信息转换为具体的字节,保证计算机内部更好的运用相关信息,也可满足并行数据器件的使用需求[1]。

2UART模块设计2.1内核模块UART内核模块属于串口通信设计的核心内容,面对数据接收的过程,应该重视内核模块发挥出的实用价值,其主要是负责着波特率发生器的控制过程,同时也关系到移位寄存器同步的接收功能,对于相关串行数据的保存有着非常重要的作用[2]。

在对相关的数据信息进行发送的时候,内核模块还是应该明确相对完整的发送序列,确保控制移位寄存器能够更好的完成加载任务,控制好波特率发生器的驱动过程,让其更好的完成串行数据的输出任务。

《基于FPGA的串口通信电路设计与实现》

《基于FPGA的串口通信电路设计与实现》摘要:信息时代的到来,给计算机等终端带来了挑战,文章以串口通信电路为研究对象,以FPGA的应用为切入点,对电路设计要点进行了归纳,例如,协议设计、串口发送等,希望能够给人以积极影响,使FPGA所拥有效能,在该领域得到应有发挥。

关键词:串口通信;FPGA;电路设计前言:首先应当明确一点,连接计算机和相关设备的通信电路,通常为串口通信电路,这是因为该电路拥有良好的可靠性,近几年,不断发展的科技,使人们对通信电路提出了更加严格的要求,通过优化电路的方式,对系统速度进行提高,成为大势所趋,这也是FPGA被用于电路设计的背景,本文所研究课题的价值不言而喻。

1协议设计通信协议指的是发生在通信双方间的约定,所约定内容主要有字符定义、数据格式及传输速度,需要通信双方严格遵守。

现有通信协议均为分层结构,高层协议被用来对校验方式、数据包格式进行定义,底层协议所强调重点为UART。

1.1高层协议FPGA向上位机所发送数据,即为上行数据,反之,上位机向FPGA所发送数据,通常被称为下行数据。

上行数据包拥有固定的数据长度,下行数据包往往以参数地址为研究重点,这是因为一旦有断电情况出现,无法保存的FPGA数据极易出现丢失情况,只有在EEPROM对数据进行保存,才能避免数据丢失,导致更加严重的后果出现[1]。

1.2底层协议研究表明,UART能否发挥作用,通常取决于起始位、停止位与波特率的设置。

目前,社会各界所认可的参数设置为:起始位对应低电平;停止位对应高电平;数据位为8bit,且不存在校验位。

而该协议的功能,可被概括如下:对数据进行发送时,用串行数据流对电路所传递并行数据进行代替,在加设停止位、起始位的基础上,以通信协议所确定波特率为依据,完成发送数据流的操作。

若要对数据进行接收,则应第一时间将停止位、起始位去掉,用字节对数据流进行代替,并向电路进行传递。

2电路设计FPGA无UART存在,UART又是组成串口通信所不可或缺的部分,通过连接电平转换芯片的方式,为数据传输提供支持。

基于FPGA的串口设计_毕业设计论文

目录基于FPGA的串口设计目录任务书 (Ⅰ)开题报告 (Ⅱ)指导教师审查意见 (Ⅲ)评阅教师评语 (Ⅳ)答辩会议记录 (Ⅴ)中文摘要 (Ⅵ)外文摘要 (Ⅶ)前言 (3)1 引言 (3)1.1 课题来源 (3)1.2 课题研究的研究背景 (3)1.3 国内外的发展现状、发展趋势及存在的主要问题 (5)1.4 课题研究的指导思想与技术路线 ....................................... 错误!未定义书签。

1.5 基于FPGA串口设计的技术要求....................................... 错误!未定义书签。

2 UART原理介绍 (8)2.1UART结构和工作原理 (8)3 方案选择 (8)3.1 设计语言的选择 (9)3.2 电平转换方式的选择 ........................................................... 错误!未定义书签。

3.3 FPGA核心芯片的选择 (10)4 系统硬件设计 (11)4.1 器件芯片介绍 (11)4.2 系统硬件框图 (18)4.3 主要组成电路分析 (18)4.4 总电路图设计 (25)5 系统软件设计 (26)5.1 主程序流程图 (26)5.2 中断子程序流程图 (27)5.3 DDS控制软件设计 ............................................................ 错误!未定义书签。

5.4 AD7886 软件驱动设计 ..................................................... 错误!未定义书签。

5.5 系统源程序 (28)6 制作位移测量装置的步骤 (28)7 总结 ........................................................... - 28 -参考文献 .......................................................... - 28 -致谢 .. (31)附录1 (32)附录2 (1)附录3 (2)前言基于FPGA的串口设计冉峰:陈晓静,电子信息学院陈晓静:电子信息学院[摘要]随着微电子技术的快速发展,电子设备逐渐向着小型化.集成化方向的发展。

基于FPGA的高速串口通信协议设计与实现

基于FPGA的高速串口通信协议设计与实现随着信息技术的不断涌现和发展,串口通信已经成为了数码设备间数据交换的重要手段。

而在当前的通信领域中,高速串口通信协议设计和实现已经成为了一个必不可少的领域。

其中,基于FPGA的高速串口通信协议设计更是受到了广泛的关注。

本文将就此问题展开深入的探讨,着重介绍了基于FPGA的高速串口通信协议的基础概念、设计模式、实现流程及其他相关内容。

一、基础概念首先,我们来了解一下什么是FPGA和串口通信。

FPGA的全称是“Field Programmable Gate Array”,是一种可编程逻辑芯片。

它能够根据设计者的要求和需求来充分发挥自己的功能特点,并且可以在不用重新设计或加工硬件的前提下灵活地改变其电路结构。

而串口通信是一种在计算机和外围设备之间进行数据交换的通信方式,可以在一根通信线上同时传输多个二进制信号,可以实现设备之间的快速、稳定的数据传输,互操作性也比较高。

基于以上两个概念,基于FPGA的高速串口通信协议设计和实现就是一种利用FPGA芯片中可编程资源的特性,以此编写通信协议,达到快速、高效地实现数据传输的过程。

二、设计模式在设计基于FPGA的高速串口通信协议时,我们通常会采用一些设计模式。

下面,我们就分别来介绍几种常见的设计模式。

1、主从模式主从模式是一种常用的通信模式,其特点是主设备控制从设备的数据传输,从设备仅向主设备传输接收到的数据。

在基于FPGA的高速串口通信协议设计中,我们可以使用主从模式实现设备之间高速的数据传输。

2、同步/异步模式同步/异步模式是根据通信时钟信号是否同步进行区分的。

在同步模式下,数据传输的时钟信号是由控制器提供的,而在异步模式下,时钟信号则是由数据本身提供的。

在基于FPGA的高速串口通信协议设计中,我们可以根据具体需求选择合适的同步/异步模式。

3、中断/轮询模式中断/轮询模式是根据不同的数据传输方式进行区分的。

在中断模式下,外部设备向中央处理器传输的数据是基于中断机制的,而在轮询模式下,则是中央处理器不断地轮询外部设备是否有数据要传输。

基于FPGA的串口通信设计

基于FPGA的串口通信设计引言:串口通信是现代计算机通信系统中的常见通信方式。

它可以在计算机和外部设备之间传输数据,具有低成本、简单易懂、可靠性高等特点。

然而,在一些应用场景下,传统的软件串口通信无法满足需求,因此使用FPGA来实现硬件串口通信变得愈发重要。

本文将重点介绍基于FPGA的串口通信设计,包括串口通信原理、FPGA硬件实现以及设计注意事项。

一、串口通信原理:串口通信的原理很简单,将数据通过一根导线(或多根导线)依次发送和接收。

它使用一个起始位、数据位(常为8位)、奇偶校验位(可选)和一个或多个停止位来组成一个数据帧。

发送数据时,串口将数据帧从最低位开始逐位发送,并在每位发送完毕后根据波特率发送下一位。

接收数据时,串口根据波特率和起始位检测到数据的到来,并从起始位开始逐位接收。

二、FPGA硬件实现:FPGA可以通过其可编程逻辑单元(FPGA的核心组件)实现硬件串口通信。

下面是基于FPGA的串口通信设计主要步骤:1.FPGA引脚分配:首先,选择合适的FPGA芯片,并确定通信所需的引脚数量。

然后,根据引脚分配表将引脚与FPGA的可编程逻辑单元相连接。

2.接口电平转换:在FPGA和外设之间可能存在电平不匹配的情况。

为了实现正确的数据传输,需要使用电平转换电路进行适配。

3.帧同步信号生成:FPGA需要生成适当的时钟信号和帧同步信号,以使数据能够正确地按位传输和接收。

帧同步信号指示数据的起始和终止。

4.数据传输实现:FPGA需要根据串口通信原理,按照波特率逐位地发送和接收数据。

在发送数据时,FPGA将数据从最低位开始逐位输出到引脚,并根据起始位、数据位、奇偶校验位和停止位生成完整的数据帧。

在接收数据时,FPGA根据时钟信号和帧同步信号,逐位地接收到达的数据,以获得完整的数据帧。

5.数据校验和处理:FPGA可以实现奇偶校验的功能,以检测接收到的数据是否正确。

此外,还可以在FPGA内部对接收到的数据进行处理,例如数据解码、错误检测等。

基于FPGA串口通信的电路和程序设计

中北大学毕业设计中期总结学生姓名:袁财源学号:1206044145 学院:仪器科学与技术专业:电子科学与技术设计题目:基于FPGA串口通信的电路和程序设计指导教师: 郭涛2015 年1月5日毕业设计中期总结MAX232芯片结构第一部分是电荷泵电路。

由1、2、3、4、5、6脚和4只电容构成。

功能是产生+12v 和-12v两个电源,提供给RS-232串口电平的需要。

第二部分是数据转换通道。

由7、8、9、10、11、12、13、14脚构成两个数据通道。

其中13脚(R1IN)、12脚(R1OUT)、11脚(T1IN)、14脚(T1OUT)为第一数据通道。

8脚(R2IN)、9脚(R2OUT)、10脚(T2IN)、7脚(T2OUT)为第二数据通道。

TTL/CMOS数据从11引脚(T1IN)、10引脚(T2IN)输入转换成RS-232数据从14脚(T1OUT)、7脚(T2OUT)送到电脑DB9插头;DB9插头的RS-232数据从13引脚(R1IN)、8引脚(R2IN)输入转换成TTL/CMOS数据后从12引脚(R1OUT)、9引脚(R2OUT)输出。

第三部分是供电。

15脚GND、16脚VCC(+5v)。

RS232 (DB9)引脚定义1 :DCD :载波检测。

主要用于Modem通知计算机其处于在线状态,即Modem检测到拨号音,处于在线状态。

2 :RXD:此引脚用于接收外部设备送来的数据;在你使用Modem时,你会发现RXD指示灯在闪烁,说明RXD引脚上有数据进入。

3 :TXD:此引脚将计算机的数据发送给外部设备;在你使用Modem时,你会发现TXD指示灯在闪烁,说明计算机正在通过TXD引脚发送数据。

4 :DTR:数据终端就绪;当此引脚高电平时,通知Modem可以进行数据传输,计算机已经准备好。

5 :GND:信号地;此位不做过多解释。

6 :DSR:数据设备就绪;此引脚高电平时,通知计算机Modem已经准备好,可以进行数据通讯了。

基于fpga的串口通信

基于FPGA的串口通信设计学号:姓名:班级:指导教师:电子与控制工程学院一、串行通信系统1.1概述在计算机系统和微机网络的快速发展领域里串行通信在数据通信及控制系统中得到广泛的应用。

UART 即Universal AsynchronousReceiver Transmitter 通用异步收发器 协议是数据通信及控制系统中广泛使用的一种全双工串行数据传输协议 在实际工业生产中有时并不使用UART的全部功能。

只需将其核心功能集成即可。

波特率发生器、接收器和发送器是UART的三个核心功能模块 利用Verilog-HDL语言对这三个功能模块进行描述并加以整合UART是广泛使用的串行数据传输协议。

UART允许在串行链路上进行全双工的通信。

串行外设用到RS232-C异步串行接口 一般采用专用的集成电路即UART实现。

如8250、8251、NS16450等芯片都是常见的UART器件 这类芯片已经相当复杂有的含有许多辅助的模块 如FIFO有时我们不需要使用完整UART的功能和这些辅助功能。

或者设计上用到了FPGA/CPLD器件那么我们就可以将所需要的UART功能集成到FPGA内部。

使用VHDL或Veriolog -HDL将UART的核心功能集成从而使整个设计更加紧凑、稳定且可靠。

本文应用EDA技术 基于FPGA/CPLD器件设计与实现UART。

通信指人与人或人与自然之间通过某种行为或媒介进行的信息交流与传递从广义上指需要信息的双方或多方在不违背各自意愿的情况下无论采用何种方法使用何种媒质 将信息从某方准确安全传送到另方。

通信在不同的环境下有不同的解释在出现电波传递通信后通信(Communication)被单一解释为信息的传递是指由一地向另一地进行信息的传输与交换其目的是传输消息。

然而通信是在人类实践过程中随着社会生产力的发展对传递消息的要求不断提升使得人类文明不断进步。

在各种各样的通信方式中利用“电”来传递消息的通信方法称为电信(Telecommunication) 这种通信具有迅速、准确、可靠等特点且几乎不受时间、地点、空间、距离的限制 因而得到了飞速发展和广泛应用。

基于FPGA的串口通讯电路设计毕业论文

本科学生毕业论文论文题目:学院: 年级:专业:姓名: 学号: 指导教师:基于FPGA勺串口通信电路设计集成电路设计与集成系统i串行通信接口是一种应用广泛的通信接口。

目前,大部分处理器都集成了支持RS-232接口(又称EIA RS-232-C)的通用异步收发器(Universal Asynchronous Receiver/Transmitter,UART),本文设计了一个串口数据采集和处理程序,详细介绍了用Verilog HDL硬件描述语言来开发波特率发生器、接收模块和发送模块这三个模块,以及系统各个模块的具体设计方法和原理,用Quartus II软件进行仿真并给出结果,分别验证各个模块的正确性。

本设计还使用基于ALTERA 公司的Cyclone II EP2C5T144芯片的FPGA开发板,在FPGA开发板上实现和PC 通过串口调试软件完成双向通信,不仅要求将开发板的数据显示在PC的串口调试助手软件上,还要求用PC发送数据的ASCII码来驱动电路的8个LED 灯,验证用FPGA实现串行通信的可行性。

关键词串行通信;RS-232; UART ;Verilog HDL ;FPGAAbstractSerial com muni cati on in terface is a widely used com muni cati on in terface. At prese nt, most of processor in tegrated RS-232(EIA RS-232-C) in terface to support UART (Uni versal Asynchronous Receiver/Tra nsmitter) com muni cati on, This thesis desig n a data acquisiti on and treatme nt program. Besides that, the thesis in troduced Baud Rate Generator module、Receiver module、Send module based on Ianguage Verilog HDL and give the results by simulate in Quartus II software. This desig n also uses EP2C5T144 FPGA chip to achieve the two-way com muni cati on by simulate with Quartus II and PC through the serial port debuggi ng software. Not only requires the developme nt board's data displayed in the PC's serial port debugg ing software, also ask ASCII data sent by PC Code to drive eight LED lights, mean while verified the serial com muni cati on with FPGA.Key wordsSerial commu ni catio n; RS-232; UART; Verilog HDL; FPGA摘要 (I)Abstract (II)第1章语言和工具 (2)1.1 Verilog HDL 语言概述 (2)1.2 FPGA 概述 (4)1.3 Quartus II 软件介绍 (8)1.4 FPGA开发板介绍 (9)1.5本章小结 (12)第2章串口通信协议简介 (13)2.1串口通信接口 (13)2.2 RS232通信协议 (13)2.3串口通信时序分析 (15)2.4本章小结 (16)第3章串口通信的VerilogHDL实现 (17)3.1设计功能说明 (17)3.2波特率发生器模块的VerilogHDL实现 (17)3.3发送模块的Verilog HDL实现 (19)3.4接收模块的Verilog HDL 实现 (25)3.5本章小结 (31)第4章串口通信的硬件调试 (32)4.1板级调试说明 (32)4.2下载配置FPGA (33)4.3配置串口调试软件 (35)4.4调试结果 (35)4.5本章小结 (38)结论 (39)参考文献.......................................................... 错误!未定义书签。

基于FPGA的串口通讯设计

基于FPGA的串口通讯设计随着科技的不断发展,现场可编程门阵列(FPGA)因其高度的灵活性和强大的数据处理能力,日益成为通讯系统设计的重要选择。

串口通讯作为一种常见的通讯方式,广泛应用于各种设备之间的数据传输。

本文将探讨如何将FPGA应用于串口通讯设计,以期提高通讯效率和稳定性。

在本文中,我们将首先确定合适的主控芯片,然后设计基于FPGA的串口通讯电路,并对FPGA资源进行合理配置。

接下来,我们将介绍如何实现串口通讯算法,以提高通讯效率和稳定性。

在基于FPGA的串口通讯设计中,我们需要考虑以下电路元件的选择和设计:电阻分压器:用于降低输入信号的电压,以适应FPGA的输入范围。

晶体振荡器:为FPGA提供时钟信号,确保设备的同步运行。

电源转换器:将外部电源转换为FPGA所需的电压和电流范围。

我们还需要根据实际需求,设计串口通讯电路的功能模块,如数据发送、数据接收等。

在基于FPGA的串口通讯设计中,我们需要根据实际需求,合理分配FPGA内部资源。

具体来说,我们需要:锁相环(PLL):用于倍频和分频时钟信号,实现高速数据传输。

信号输出:驱动外部设备,如LED、LCD等。

在实现串口通讯算法时,我们首先需要定义通讯协议,包括数据格式、波特率、校验位等。

然后,我们可以使用流程图等方式,明确算法实现步骤。

例如:实验验证为了验证基于FPGA的串口通讯设计的可行性和可靠性,我们搭建了实验环境,并进行了以下测试:功能测试:检测电路各功能模块是否正常工作,如数据发送、数据接收等。

性能测试:测试通讯速率、稳定性、抗干扰能力等指标。

协议兼容性测试:检测算法是否兼容不同串口通讯协议。

长时间运行测试:检测系统在长时间运行下的稳定性和可靠性。

通过以上实验测试,我们发现基于FPGA的串口通讯设计在通讯速率、稳定性、抗干扰能力等方面均具有显著优势,能满足多种应用场景的需求。

同时,该设计具有较好的协议兼容性和可扩展性,能根据不同需求进行定制化扩展。

基于fpga的频率计与串口通信实现

基于fpga的频率计与串口通信实现下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!基于FPGA的频率计与串口通信实现随着科学技术的不断发展,FPGA技术在数字电子系统中得到了越来越广泛的应用。

基于FPGA的串口通信电路设计与实现

基于FPGA的串口通信电路设计与实现摘要:由于现代工业企业中在线监测的日益增长。

需要PC机与更多设备进行通信,串口通信具有实现简单,使用灵活。

数据传输准确等优点。

在工业监控和实时监控系统中得到了广泛应用。

由于监测设备的增加。

PC机原有的串口不能再满足通信的需求,传统的设计方法是使用硬件扩展八个串口,但是额外增加了硬件设计成本和实际编程的难度。

然而FPGA的UARTIP可灵活定制的优点使得基于黜的设计方法无需额外的硬件串口扩展,减少了硬件开发调试的难度,同时满足串行传输的要求。

基于此,本文主要对基于FPGA的串口通信电路设计与实现进行分析探讨。

关键词:基于FPGA;串口通信;电路设计;实现1、前言FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是作为专用集成电路领域中一种半定制电路出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

FPGA中具有丰富的触发器和I/O口,采用描述语言(VHDL和VerilogHDL)进行设计,用户可以根据需要,描述出具有各种功能的电路。

基于以上原因,我们可以利用FPGA实现多串口通信中的数据转换和中断控制功能,从而简化电路、缩小PCB面积,也可以很方便的进行升级改动和模块移植。

2、设计要求整个设计的硬件电路以DSP和FPGA为主构架,DSP和FPGA之间通过DSP的EMIF接口连接。

其中,DSP是主处理器,用于实现串口数据的处理,FPGA作为DSP的外围电路,实现UART模块的串行数据的接收和发送、数据的串并/并串转换及接收中断的产生,同时,实现多串口的中断控制功能。

当有接收数据时,FPGA通过中断方式通知DSP。

UART模块的数据格式:波特率可以按标准波特率设置;按字节接收,每个字节前包含一个起始位(低电平,逻辑值0),无校验位,最后是一位停止位和不定长度的空闲位(高电平,逻辑值1);接收到一个完整字节后产生一个中断(高电平,逻辑值1),当数据被读取后,中断信号复位(低电平,逻辑值0)。

基于FPGA实现的高速串口传输技术与实现

(5)将配置位流文件下载到FPGA芯片中,进行实际运行和测试。

4、结论

本次演示设计和实现了一种基于FPGA的以太网和串口数据传输系统,实现了 高速、高效的数据传输和共享。本系统的优点在于具有高度的灵活性和可扩展性, 可以方便地根据实际需要进行功能扩展和优化。由于采用了FPGA技术,本系统还 具有体积小、功耗低、可靠性高等优点,可以广泛应用于各种嵌入式系统和智能 设备中。

为了更好地实现基于FPGA的高速光纤通信数据传输技术,需要以下几个方面:

1.优化硬件设计:根据具体的应用场景和需求,选择合适的FPGA芯片和硬件 组件,并对其进行优化设计,以实现更高效的数据传输和处理。

2.完善软件算法:利用FPGA的并行处理能力和数字信号处理算法,进一步完 善软件算法,提高数据处理速度和可靠性。

最后,为了提高稳定性和可靠性,可以研究更为高效的错误检测和纠正算法, 以及研究如何提高数据传输的鲁棒性。

总结

本次演示介绍了基于FPGA实现的高速串口传输技术与实现。通过利用FPGA的 灵活性和高效性,我们成功地实现了高速串口传输技术,并在速度测试中验证了 其优势。然而,也需要注意到这种技术存在的不足和挑战。未来,高速串口传输 技术将会朝着更高速度、更低成本、更稳定可靠的方向发展。

参考内容

随着信息时代的到来,数据传输的速度和可靠性成为了关键的要素。光纤通 信作为一种现代化的数据传输方式,具有传输速度快、容量大、抗干扰能力强等 优点,被广泛应用于各个领域。为了进一步提升光纤通信的性能,基于FPGA(现 场可编程门阵列)的高速光纤通信数据传输技术得到了广泛的研究与实现。

FPGA是一种高度灵活的芯片,可以由用户进行编程配置,实现各种不同的逻 辑功能。在光纤通信领域,FPGA可以被用于实现数据编解码、信号调制解调、误 码纠正等功能,从而提升数据传输的速度和可靠性。

基于FPGA与MCU的多串口通信接口设计与实现的开题报告

基于FPGA与MCU的多串口通信接口设计与实现的开题报告1. 研究背景多串口通信是现代通信系统中广泛使用的一种通信方式,特别适用于需要同时与多个设备进行通信的场景。

在电子设备控制、网络通信以及工业过程自动化等方面都有广泛应用。

目前,市场上有很多基于单片机的多串口通信模块,但是其通信速率和并发能力都受到限制。

而FPGA 具有并发处理和可编程性等优势,可以实现高速的多串口通信。

2. 研究内容本项目计划设计并实现一个基于FPGA与MCU的多串口通信接口。

具体研究内容包括:(1)设计多串口通信接口的硬件电路结构,包括FPGA与MCU之间的通信协议和接口电路设计。

(2)掌握多串口通信的原理和相关协议,包括UART、SPI、I2C等协议,并在FPGA上实现多串口通信控制器的设计。

(3)设计并实现多串口通信控制器的驱动程序,并与MCU通信,实现更高层次的数据处理和系统控制。

(4)对设计的系统进行测试和调试,验证其多串口通信速率和并发能力。

3. 研究意义本项目的研究成果可以实现更高速的多串口通信,并满足同时控制多个设备的需求。

基于FPGA的多串口通信控制器可以大大提高通信效率和并发能力,使得数据传输更加快速和稳定。

该研究成果可以应用于自动化控制、仪器仪表等领域,有一定的实用价值和推广价值。

4. 研究方法本项目采用FPGA开发板和MCU模块进行设计和实现。

在硬件、软件方面分别进行设计,以达到多串口通信功能的实现。

具体方法包括:(1)研究多串口通信原理和相关协议,分析其特点和应用场景。

(2)进行FPGA与MCU接口电路设计和通信协议的制定。

(3)在FPGA上进行多串口通信控制器的设计和开发,生成FPGA配置文件。

(4)在MCU上编写驱动程序,实现与FPGA通信以及更高层次的数据处理和控制。

(5)对系统进行测试和调试,验证系统的多串口通信速率和并发能力。

5. 进度安排本项目的研究进度安排如下:(1)第1-2周:研究多串口通信原理和相关协议。

基于FPGA的SSI通信模块设计

基于FPGA的SSI通信模块设计引言:SSI(Synchronous Serial Interface)是一种高速串行同步通信接口,广泛应用于数据传输、通信和控制系统中。

本文将介绍基于FPGA的SSI通信模块的设计原理、功能设计和硬件实现流程。

一、设计原理SSI通信模块使用基于FPGA的串行通信协议,通过使用FPGA的并行输入输出引脚,将输入并行数据转换成串行数据流,并通过通信线路将数据发送到接收端。

接收端将串行数据流反转回并行数据,并输出到引脚上。

通过这种方式,可以实现高速、可靠的数据通信。

二、功能设计1.并行串行转换:设计一个并行串行转换器,将输入的并行数据转换成串行数据,并通过SSI接口发送。

2.串行并行转换:设计一个串行并行转换器,将接收到的串行数据流转换成并行数据,并输出到引脚上。

3.帧同步:设计一个帧同步模块,通过检测特定的帧同步信号,将数据从串行流中分割成帧,方便后续处理。

4.数据校验:设计一个数据校验模块,对传输的数据进行校验,确保数据的正确性和完整性。

5.时序控制:设计一个时序控制模块,控制数据的传输速率和时序,保证数据的稳定性和可靠性。

三、硬件实现流程1.确定通信协议:根据应用场景和需要传输的数据类型,选择合适的通信协议,并了解其通信格式和时序。

2.FPGA引脚规划:根据通信协议和需要传输的数据位宽,分配FPGA 的引脚,并进行引脚规划。

3.搭建电路结构:根据引脚规划,搭建电路结构,包括并行串行转换器、串行并行转换器、帧同步模块、数据校验模块和时序控制模块。

4.时序优化:根据设计的电路结构,进行时序优化,确保数据的稳定性和可靠性。

5.静态时序分析:对设计的电路进行静态时序分析,以检测和解决时序冲突。

6.功能验证:通过实际测试,验证设计的功能和性能是否满足要求,并对设计进行调优和优化。

总结:本文介绍了基于FPGA的SSI通信模块的设计原理、功能设计和硬件实现流程。

通过使用FPGA的并行输入输出引脚,将输入并行数据转换成串行数据流,并通过通信线路传输数据。

基于FPGA的多串口通信设计与实现

Ke y Wo  ̄S : s e r i a l p o r t ; AS I C; F P GA; UAl k T; i n t e =u p t c o n t r o l l e r ; VHDL

串行通信 因为具有传输线少、 成本低、 配置灵活等特 点, 得到了 广泛应用 , 通用异步收发传 输器 ( Un i v e r s a l As y n c h r o n o u s Re — c e i v e r / Tr a n s mi t t e r ) , 是一种 比较常用的接 口电路 , 主要用于 串行数 据和并行数据的转换。 一般该接 口由专用的UAR T 芯片完成 , 例如 S Cl 6 C 5 5 4 B I B 6 4 , 该接 口芯片具有4 路独立 的通道 , 同时提供多种控 制功能 , 但在实际使用 中往往只使用一种特定控制方式 , 这 不仅造 成 电路复杂和浪费 , 而且会使P C B 面积增 大, 布线复杂 。 [ 1 1 F P G A( F i e l d - P r o g r a mma b l e G a t e Ar r a y ) , 即现场可编程 门 阵列 , 它是作为专用集成电路领域中一种 半定制电路出现 的 , 既解 决了定制 电路的不足, 又克服了原有可编程器件 门电路数有 限的缺 点。 F P G A中具有 丰富的触发器和I / O口, 采用描述语言(ቤተ መጻሕፍቲ ባይዱVHD L 和 V e r i l o g HD L )  ̄行设计 , 用户可以根据需要, 描述 出具有各种功 能的

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

介绍了一种基于FPGA的UART电路实现方法,采用有限状态机设计了发送模块和接收模块,给出了系统的功能仿真结果,验证了系统设计的正确性.整个 UART接口电路结构简单、功能升级方便、工作稳定敬美.杨春玲.WANG Jing-mei.YANG Chun-ling 基于FPGA和UART的数据采集器设计 -电子器件

2009,32(2)

设计一种基于FPGA和UART串口传输技术的数据采集器.设计中采用12位、20 Msample/s的ADS805高速A/D芯片和Altera公司的Cyclone系列FPGA芯片 .整个设计完全采用硬件逻辑,集成在一片FPGA内,不需要微处理器,实现了数据的采集、缓存和UART串口的发送与接收,设计电路简单,具有较高的采集速 度,传输接口通用性强,便于互联;FPGA的重构性和通用性,也便于设计功能的升级.

信l息 产 业

科赫

基于FPGA的串口通信设计与实现

王利民 屠玲刚 潘忠鸽 朱志亮 (温州大学物理与电子信息3-程学院,浙江温州325035)

摘要:介绍了一种利用FPGA来实现RS232串行数据通信的方案。,基于FPGA的方案既实现了UART模块化设计,且避免了常用UART芯 片复杂与移植性差的缺点。

置和输人数据计算出响应

的奇偶校验位,它是通过

纯组合逻辑来实现的。

2.6总线选择模块

总线选择模块用于

选择奇偶校验器的输入是

数据发送总线还是数据接

收总线。

2.7计数器模块

计数器模块的功能

是记录串行数据发送或者

接收的数日,在计数到某

数值时通知UART内核模

块。 3 UART程序设计 UART完整的工作流程可以分为接收过程

万方数据

一89—

基于FPGA的串口通信设计与实现

作者: 作者单位: 刊名:

英文刊名: 年,卷(期): 被引用次数:

王利民, 屠玲刚, 潘忠鸽, 朱志亮 温州大学物理与电子信息工程学院,浙江,温州,325035

黑龙江科技信息 HEILONGJIANG SCIENCE AND TECHNOLOGY INFORMATION 2010,""(21) 0次

作者简介:王利民(1986~),男,温州大学物 理与电子信息工程学院,学生,研究方向:嵌入 式设计。

潘忠鸽f1986~),男,温州大学物理与电子 信息工程学院,学生,研究方向:嵌入式设计。

屠玲刚(1988~),男,温州大学物理与电子 信息工程学院,学生,研究方向:嵌入式设计。

朱志亮(1982~),男,温州大学物理与电子 信息工程学院,助教,研究方向:通信信号处理。

7.期刊论文 马游春.王文杰.李锦明 基于FPGA和UART接口的多路数据采集系统的实现 -火力与指挥控制2010,35(9)

为了满足对采集后的数据进行快速、远距离的串行传输、并实时储存的需求,研制了一种基于FPGA和UART接口的多路数据采集系统.采用FPGA实现数 据的采集模块、模拟信号路数选择以及数字信号的并串转换等功能;同时利用RS-422接口实现了数字信号远距离的串行传输.功能仿真和实际测量验证了 设计的可行性.

UAKT通信模式以其简单连接方式,可靠的传输效率广泛应用于现代化工业生产的各个方面,本文讨论的是51单片机与FPGA芯片的之间的UART通信模式 .从二者的硬件连接,通信编程和软件仿真三个方面分析该模式的实现方式,并仿真了其实际通信效果,阐明了其实际可行性和使用可靠性.

2.期刊论文 高军建.苗志英.Gao Junjian.Miao Zhiying 基于FPGA的UART模块化设计 -价值工程2010,29(19)

和发送过程两部分。 接收过程是指UART监测到RS一232总线

上的数据,顺序读取串行数据并将其输出给 CPU的过程。当信号监测到新的数据(RS一232 输入逻辑变为0,即RS一232传输协议的起始 位)就会触发接收流程。首先UART内核会重置 波特率发生器和移位寄存器,并且设置移位寄 存器的工作模式为波特率模式,以准备接收数 据。其次,移位寄存器在波特率时钟的驱动下工 作,不断渎取RS一232串行总线的输入数据,并 且将数据保存在内部的寄存器内。接收完成后, UART内核会对已接收的数据进行奇偶校验并 且输出校验结果。最后,UARql内核会重置信号 检测器,以准备进行下一次数据接收。

关键词:FPGA:UART:RS232

引言 串行接口的应用非常广泛,为实现串口通 信功能一般使用专用串行接口芯片,但是这种 接口芯片存在体积较大、接口复杂以及成本较 高的缺点,使得硬件设计更加复杂,并且结构与 功能相对固定,无法根据设计的需要对其逻辑 控制进行灵活的修改。介绍了一种采用FPGA 实现串口通信的方法。 1串口通信协议 对一个设备的处理器来说,要接收和发送 串行通信的数据,需要一个器件将串行的数据 转换为并行的数据以便于处理器进行处理,这 种器件就是UART(Universal Asynchronous Re— ceiver/Transmitter)通用异步收发器。作为接iSl的 一部分,UART提供以下功能: 1.1将由计算机内部传送过来的并行数据 转换为输出的串行数据流; 1.2将计算机外部来的串行数据转换为字 节,供计算机内部使用并行数据的器件使用; 1.3在输出的串行数据流中加入奇偶校验 位,并对从外部接收的数据流进行奇偶校验: 1.4在输出数据流中加入启停标记,并从 接收数据流中删除启停标记。 2 UART模块设计 UART主要由UART内核、信号检测器、移 位寄存器、波特率发生器、计数器、总线选择器 和奇偶校验器7个模块组成。(见图1) 2.1 UART内核模块 UART内核模块是整个设计的核心。在数 据接收时,UART内核模块负责控制波特率发 生器和移位寄存器同步的接收并且保存 RS一232接收端口上的串行数据。在数据发送 时,UART内核模块首先产生完整的发送序列, 之后控制移位寄存器将序列加载到移位寄存器 的内部寄存器里,最后再控制波特率发生器驱 动移位寄存器将数据串行输出。 2_2信号检测模块 信号检测器用于对RS一232的输入信号进 行实时检测,一旦发现新的数据则立即通知 UART内核。需要注意的是,这里所说的 RS一232输入输出信号都指经过电平转换后的 逻辑信号,而不是RS一232总线上的电平信号。 2_3移位寄存器模块 移位寄存器的作用是存储输入或者输出 的数据。 2.4波特率发生器模块 由于RS一232传输必定是工作在某种波特 率下,比如9600,为了便于和RS一232总线进行 同步,需要产生符合RS一232传输波特率的时 钟。 2.5奇偶校验器模块 奇偶校验器的功能是根据奇偶校验的设

发送过程是由加载和发送两个步骤组成。 加载步骤是UART内核按RS一232串行发送的

图1 UART实现原理图

方案也是未来电子产品开发的发展趋势。 参考文献

『11韩德红.基于FPGA的串口控制器设计与实 现[J].空军雷达学院学报,2008,6(02):113—116. [2]蒋璇,臧春华.数字系统设计与PLD应用[M】. 北京:电子工业出版社,2005. [3]李广弟,朱月秀,王秀山.单片机基础[M].北 京:北京航天航空大学出版社,2003.

加载的数据发送到RS一232的发送端TXD,这 条新的途径,积累了一迪!成功的经验。

样就产生了RS一232的数据发送时序。

参考文献

4 FPGA实现 把实验板上电,’下载完成后在PC上打开 串口调试助手,在上方接收区的串【_:l选择 COMl,波特率选择1 15200,校验位选择无校验 位,8个数据位1个停止位。每按下reset,可以 在接收区看到FPGA通过串口向PC发送的一 个字符串“welcome to WZII”。测试结果验证了程

UART 因其可靠性高,传输距离远,线路简单而成为比较广泛的串行数据通信电路,而现在大部分集成电路通信用的UART芯片,存在成本高,电路复杂,移 植性较差等缺点,本文提出了一种基于FPGA的嵌入式 UART模块化设计方法,将UART模块集成到FPGA上,而这些模块功能全部基于verilogHDL硬件描述语言 ,并通过有限状态机来实现,增强了设计的灵活性,降低了成本,并可以作为一个IP核,移植到其它FPGA嵌入式系统中,可移植性增强.

顺序将起始位、数据位、奇偶校验位和停止位加

载到移位寄存器内,这个过程工作在系统时钟 下,相对于RS一232传输速度来说非常快。完成

加载步骤后,UART内核会重置波特率发生器, (上接303页)

汛和优化调度提供了可靠的

并且设置移位寄存器工作在波特率模式下,于 是移位寄存器便在波特率时钟的驱动下依次将

保障,提高了水库的防洪效益和经济效益。同时,也 为周围地区推广建立水隋自动测报系统探索了一

6.期刊论文 郑宝华.程德福.ZHENG Bao-hua.CHENG De-fu 基于FPGA的UART模块设计与实现 -吉林化工学院学报

2009,26(4)

介绍了 UART 的基本特点,提出了一种UART 收发器的FPGA实现方法,实现了FPGA 与其他数字系统的直接通信,测试结果表明用该UART模块实现的串行 通信高速、稳定、可靠.

3.期刊论文 聂涛.许世宏.NIE Tao.XU Shihong 基于FPGA的UART设计 -现代电子技术2006,29(2)

UART是一种广泛应用于短距离、低速、低成本通信的串行传输接口.由于常用UART芯片比较复杂且移植性差,提出一种采用可编程器件FPGA实现 UART的方法, 实现了对UART的模块化设计.首先简要介绍UART的基本特点,然后依据其系统组成设计顶层模块,再采用有限状态机设计接收器模块和发送器 模块,所有功能的实现全部采用VHDL进行描述,并用Modelsim软件对所有模块仿真实现.最后将UART的核心功能集成到FPGA上,使整体设计紧凑,小巧,实现 的UART功能稳定、可靠.