Multithreaded Decoupled AccessExecute Processors Joan-Manuel Parcerisa, Antonio Gonzlez Uni

爱迪尔门锁系统接口函数(SDK)说明

爱迪尔门锁系统接口函数(SDK)说明(动态联接库函数说明)适用门锁接口:Lock3200.DLL,Lock3200K.DLL,Lock4200.DLL,Lock4200D.DLL,Lock5200.DLL,Lock6200.DLL,Lock7200.DLL,Lock7200D.DLL,Lock9200.DLL,Lock9200T.DLL。

适用门锁系统:V5.1及以上,V6.5以下版本。

一、门锁函数(必须已经安装并设置好门锁系统)1、Init初始化。

函数原形:int Init(char *server, int port, int Encoder, int TMEncoder);参数:server [in]:字符指针,指定门锁系统数据库安装的服务器(SQL Server)名。

Port [in]:串口号,1-COM1,2-COM2,3-COM3,4-COM4依次类推。

Encoder [in]:发行机类型,0-手动发行机,1-自动发行机。

TMEncoder [in]:TM发行机类型,1-DS9097E,5-DS9097U返回值:见注1。

2、EndSession结束工作期。

函数原形:int EndSession(void);参数:无返回值:见注1。

3、IssueCard发行客人卡。

函数原形:int IssueCard(char *room,char *gate,char *stime,char *guestname,char *guestid, int overflag, long *cardno,char * track1,char * track2);参数:room [in]:房号,6字节字符串,必须是门锁系统设置的房号。

gate [in]:公共通道,字符串参数,“00”表示按默认授权通道,“99”表示授权所有公共通道,其他为指定通道代码。

例如:“010203”表示授权01、02、03三个通道。

Stime [in]:起止时间,24字节字符串,格式yyyymmddhhnnyyyymmddhhnn,例如:“200012311230200101011230”表示2000年12月31日12时30分到2001年1月1日12时30分。

dbcp连接池不合理的锁导致连接耗尽解决方案

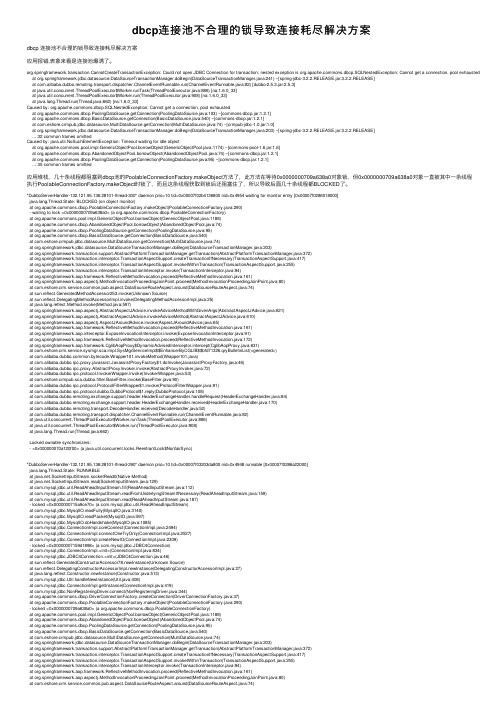

dbcp连接池不合理的锁导致连接耗尽解决⽅案dbcp 连接池不合理的锁导致连接耗尽解决⽅案应⽤报错,表象来看是连接池爆满了。

org.springframework.transaction.CannotCreateTransactionException: Could not open JDBC Connection for transaction; nested exception is mons.dbcp.SQLNestedException: Cannot get a connection, pool exhausted at org.springframework.jdbc.datasource.DataSourceTransactionManager.doBegin(DataSourceTransactionManager.java:241) ~[spring-jdbc-3.2.2.RELEASE.jar:3.2.2.RELEASE]at com.alibaba.dubbo.remoting.transport.dispatcher.ChannelEventRunnable.run(ChannelEventRunnable.java:82) [dubbo-2.5.3.jar:2.5.3]at java.util.concurrent.ThreadPoolExecutor$Worker.runTask(ThreadPoolExecutor.java:886) [na:1.6.0_33]at java.util.concurrent.ThreadPoolExecutor$Worker.run(ThreadPoolExecutor.java:908) [na:1.6.0_33]at ng.Thread.run(Thread.java:662) [na:1.6.0_33]Caused by: mons.dbcp.SQLNestedException: Cannot get a connection, pool exhaustedat mons.dbcp.PoolingDataSource.getConnection(PoolingDataSource.java:103) ~[commons-dbcp.jar:1.2.1]at mons.dbcp.BasicDataSource.getConnection(BasicDataSource.java:540) ~[commons-dbcp.jar:1.2.1]at com.eshore.crmpub.jdbc.datasource.MultiDataSource.getConnection(MultiDataSource.java:74) ~[crmpub-jdbc-1.0.jar:1.0]at org.springframework.jdbc.datasource.DataSourceTransactionManager.doBegin(DataSourceTransactionManager.java:203) ~[spring-jdbc-3.2.2.RELEASE.jar:3.2.2.RELEASE]... 32 common frames omittedCaused by: java.util.NoSuchElementException: Timeout waiting for idle objectat mons.pool.impl.GenericObjectPool.borrowObject(GenericObjectPool.java:1174) ~[commons-pool-1.6.jar:1.6]at mons.dbcp.AbandonedObjectPool.borrowObject(AbandonedObjectPool.java:74) ~[commons-dbcp.jar:1.2.1]at mons.dbcp.PoolingDataSource.getConnection(PoolingDataSource.java:95) ~[commons-dbcp.jar:1.2.1]... 35 common frames omitted应⽤堆栈,⼏⼗条线程都阻塞到dbcp池的PoolableConnectionFactory.makeObject⽅法了,此⽅法在等待0x0000000709a638a0对象锁,但0x0000000709a638a0对象⼀直被其中⼀条线程执⾏PoolableConnectionFactory.makeObject时锁了,⽽且这条线程获取到锁后还阻塞住了,所以导致后⾯⼏⼗条线程都BLOCKED了。

多线程写excel concurrentmodificationexception-概述说明以及解释

多线程写excel concurrentmodificationexception-概述说明以及解释1.引言1.1 概述在当今信息化的时代,数据的处理和分析变得越来越重要。

而Excel 作为一种常用的电子表格软件,广泛应用于各个领域,尤其是在数据处理和数据分析方面。

然而,随着数据量的增加和处理需求的复杂化,使用Excel进行数据的读写操作往往变得缓慢和低效。

传统的Excel文件读写操作往往是单线程进行的,即一次只能读取或写入一个单元格或一行数据。

这种方式在处理大量数据时会面临诸多挑战,例如处理时间较长、性能较低等问题。

为了提高Excel文件的读写效率和性能,我们可以考虑使用多线程技术来并发地读写Excel文件。

多线程指的是在一个程序中同时运行多个线程,每个线程独立地执行不同的任务。

通过利用多核处理器的优势,多线程可以使任务并行地运行,从而加快程序的执行速度。

在处理大数据量的Excel文件时,多线程可以将读写任务分配给不同的线程并行执行,从而提高读写效率和性能。

然而,多线程读写Excel也会引发一些问题。

其中之一就是当多个线程同时访问并修改Excel文件时,可能会出现ConcurrentModificationException异常。

这个异常通常发生在遍历容器(如ArrayList)的过程中,当一个线程正在遍历容器,而另一个线程在修改容器时,就可能导致ConcurrentModificationException异常的出现。

本文将以多线程写Excel的场景为例,探讨多线程读写Excel可能引发的问题,并提供解决ConcurrentModificationException异常的方法。

通过深入探究多线程读写Excel的原理和技术,我们可以更好地理解和应用多线程技术,提高程序的效率和性能。

同时,也能够为其他类似的并发读写操作提供一定的参考和借鉴。

1.2 文章结构本文将从以下几个方面对多线程写Excel过程中可能引发的问题以及解决ConcurrentModificationException异常的方法进行详细探讨:1. 引言1.1 概述- 介绍多线程写Excel的背景和重要性,以及在实际应用中可能遇到的问题。

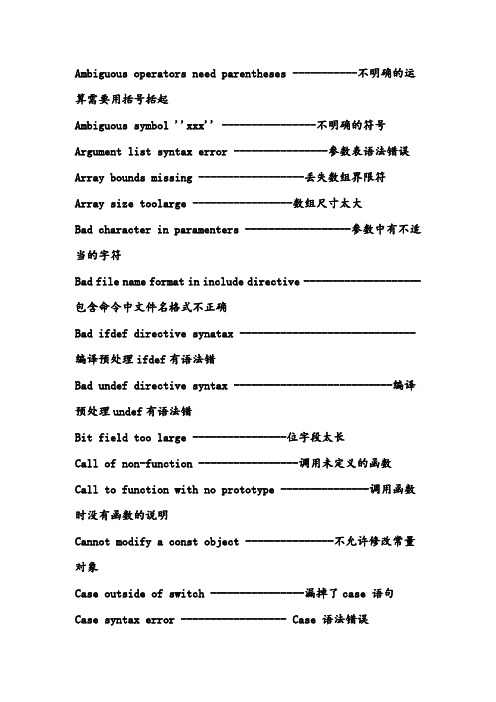

C++出错提示英汉对照表

Ambiguous operators need parentheses -----------不明确的运算需要用括号括起Ambiguous symbol ''xxx'' ----------------不明确的符号Argument list syntax error ----------------参数表语法错误Array bounds missing ------------------丢失数组界限符Array size toolarge -----------------数组尺寸太大Bad character in paramenters ------------------参数中有不适当的字符Bad file name format in include directive --------------------包含命令中文件名格式不正确Bad ifdef directive synatax ------------------------------编译预处理ifdef有语法错Bad undef directive syntax ---------------------------编译预处理undef有语法错Bit field too large ----------------位字段太长Call of non-function -----------------调用未定义的函数Call to function with no prototype ---------------调用函数时没有函数的说明Cannot modify a const object ---------------不允许修改常量对象Case outside of switch ----------------漏掉了case 语句Case syntax error ------------------ Case 语法错误Code has no effect -----------------代码不可述不可能执行到Compound statement missing{ --------------------分程序漏掉"{"Conflicting type modifiers ------------------不明确的类型说明符Constant expression required ----------------要求常量表达式Constant out of range in comparison -----------------在比较中常量超出范围Conversion may lose significant digits -----------------转换时会丢失意义的数字Conversion of near pointer not allowed -----------------不允许转换近指针Could not find file ''xxx'' -----------------------找不到XXX 文件Declaration missing ; ----------------说明缺少";" Declaration syntax error -----------------说明中出现语法错误Default outside of switch ------------------ Default 出现在switch语句之外Define directive needs an identifier ------------------定义编译预处理需要标识符Division by zero ------------------用零作除数Do statement must have while ------------------ Do-while语句中缺少while部分Enum syntax error ---------------------枚举类型语法错误Enumeration constant syntax error -----------------枚举常数语法错误Error directive :xxx ------------------------错误的编译预处理命令Error writing output file ---------------------写输出文件错误Expression syntax error -----------------------表达式语法错误Extra parameter in call ------------------------调用时出现多余错误File name too long ----------------文件名太长Function call missing -----------------函数调用缺少右括号Fuction definition out of place ------------------函数定义位置错误Fuction should return a value ------------------函数必需返回一个值Goto statement missing label ------------------ Goto语句没有标号Hexadecimal or octal constant too large ------------------16进制或8进制常数太大Illegal character ''x'' ------------------非法字符x Illegal initialization ------------------非法的初始化Illegal octal digit ------------------非法的8进制数字houjiumingIllegal pointer subtraction ------------------非法的指针相减Illegal structure operation ------------------非法的结构体操作Illegal use of floating point -----------------非法的浮点运算Illegal use of pointer --------------------指针使用非法Improper use of a typedefsymbol ----------------类型定义符号使用不恰当In-line assembly not allowed -----------------不允许使用行间汇编Incompatible storage class -----------------存储类别不相容Incompatible type conversion --------------------不相容的类型转换Incorrect number format -----------------------错误的数据格式Incorrect use of default --------------------- Default使用不当Invalid indirection ---------------------无效的间接运算Invalid pointer addition ------------------指针相加无效Irreducible expression tree -----------------------无法执行的表达式运算Lvalue required ---------------------------需要逻辑值0或非0值Macro argument syntax error -------------------宏参数语法错误Macro expansion too long ----------------------宏的扩展以后太长Mismatched number of parameters in definition---------------------定义中参数个数不匹配Misplaced break ---------------------此处不应出现break语句Misplaced continue ------------------------此处不应出现continue语句Misplaced decimal point --------------------此处不应出现小数点Misplaced elif directive --------------------不应编译预处理elifMisplaced else ----------------------此处不应出现else Misplaced else directive ------------------此处不应出现编译预处理elseMisplaced endif directive -------------------此处不应出现编译预处理endifMust be addressable ----------------------必须是可以编址的Must take address of memory location ------------------必须存储定位的地址No declaration for function ''xxx'' -------------------没有函数xxx的说明No stack ---------------缺少堆栈No type information ------------------没有类型信息Non-portable pointer assignment --------------------不可移动的指针(地址常数)赋值Non-portable pointer comparison --------------------不可移动的指针(地址常数)比较Non-portable pointer conversion ----------------------不可移动的指针(地址常数)转换Not a valid expression format type ---------------------不合法的表达式格式Not an allowed type ---------------------不允许使用的类型Numeric constant too large -------------------数值常太大Out of memory -------------------内存不够用Parameter ''xxx'' is never used ------------------能数xxx没有用到Pointer required on left side of -> -----------------------符号->的左边必须是指针Possible use of ''xxx'' before definition -------------------在定义之前就使用了xxx(警告)Possibly incorrect assignment ----------------赋值可能不正确Redeclaration of ''xxx'' -------------------重复定义了xxx Redefinition of ''xxx'' is not identical ------------------- xxx的两次定义不一致Register allocation failure ------------------寄存器定址失败Repeat count needs an lvalue ------------------重复计数需要逻辑值Size of structure or array not known ------------------结构体或数给大小不确定Statement missing ; ------------------语句后缺少";" Structure or union syntax error --------------结构体或联合体语法错误Structure size too large ----------------结构体尺寸太大Sub scripting missing ] ----------------下标缺少右方括号Superfluous & with function or array ------------------函数或数组中有多余的"&"Suspicious pointer conversion ---------------------可疑的指针转换Symbol limit exceeded ---------------符号超限Too few parameters in call -----------------函数调用时的实参少于函数的参数不Too many default cases ------------------- Default太多(switch 语句中一个)Too many error or warning messages --------------------错误或警告信息太多Too many type in declaration -----------------说明中类型太多Too much auto memory in function -----------------函数用到的局部存储太多Too much global data defined in file ------------------文件中全局数据太多Two consecutive dots -----------------两个连续的句点Type mismatch in parameter xxx ----------------参数xxx类型不匹配Type mismatch in redeclaration of ''xxx'' ---------------- xxx 重定义的类型不匹配Unable to create output file ''xxx'' ----------------无法建立输出文件xxxUnable to open include file ''xxx'' ---------------无法打开被包含的文件xxxUnable to open input file ''xxx'' ----------------无法打开输入文件xxxUndefined label ''xxx'' -------------------没有定义的标号xxx Undefined structure ''xxx'' -----------------没有定义的结构xxxUndefined symbol ''xxx'' -----------------没有定义的符号xxx Unexpected end of file in comment started on line xxx----------从xxx行开始的注解尚未结束文件不能结束Unexpected end of file in conditional started on line xxx ----从xxx 开始的条件语句尚未结束文件不能结束Unknown assemble instruction ----------------未知的汇编结构Unknown option ---------------未知的操作Unknown preprocessor directive: ''xxx'' -----------------不认识的预处理命令xxxUnreachable code ------------------无路可达的代码Unterminated string or character constant -----------------字符串缺少引号User break ----------------用户强行中断了程序Void functions may not return a value ----------------- Void类型的函数不应有返回值Wrong number of arguments -----------------调用函数的参数数目错''xxx'' not an argument ----------------- xxx不是参数''xxx'' not part of structure -------------------- xxx不是结构体的一部分xxx statement missing ( -------------------- xxx语句缺少左括号xxx statement missing ) ------------------ xxx语句缺少右括号xxx statement missing ; -------------------- xxx缺少分号xxx'' declared but never used -------------------说明了xxx 但没有使用xxx'' is assigned a value which is never used----------------------给xxx赋了值但未用过Zero length structure ------------------结构体的长度为零。

executescalar 多条语句

一、介绍在程序开发中,执行SQL语句是一项常见的操作。

在使用等数据库访问技术时,我们经常会遇到需要执行多条SQL语句的场景。

而在执行多条SQL语句时,有一种常见的方法是使用ExecuteScalar方法。

本文将就ExecuteScalar方法执行多条语句进行深入探讨,包括其优缺点、应用场景及注意事项。

二、ExecuteScalar方法的原理ExecuteScalar方法是中Command对象的一个常用方法,它用于执行SQL语句并返回结果集的第一行第一列的值。

在执行一条查询语句时,如果我们只关心结果集的第一行第一列的值,可以使用ExecuteScalar方法来获取该值。

ExecuteScalar方法的示例代码如下所示:```csharpstring sql = "SELECT COUNT(*) FROM TableName"; SqlCommandmand = new SqlCommand(sql, connection);object result =mand.ExecuteScalar();```在上述代码中,ExecuteScalar方法执行了一条查询语句,并返回了结果集的第一行第一列的值,即表中数据的总数。

然而,对于执行多条SQL语句的情况,ExecuteScalar方法并不直接支持。

三、使用ExecuteScalar执行多条语句的方法虽然ExecuteScalar方法通常用于执行单条SQL查询语句,但我们可以通过一些技巧来实现ExecuteScalar方法执行多条语句的效果。

具体来说,我们可以将多条SQL语句合并成一条,并使用ExecuteScalar方法执行该合并后的SQL语句。

在执行合并后的SQL 语句时,我们可以通过使用分号(;)来分隔各条SQL语句。

示例代码如下:```csharpstring sql = "SELECT COUNT(*) FROM TableName; SELECT MAX(Salary) FROM Employees";SqlCommandmand = new SqlCommand(sql, connection); object result =mand.ExecuteScalar();```在上述代码中,我们将两条SQL语句合并成一条,并在它们之间使用分号进行分隔。

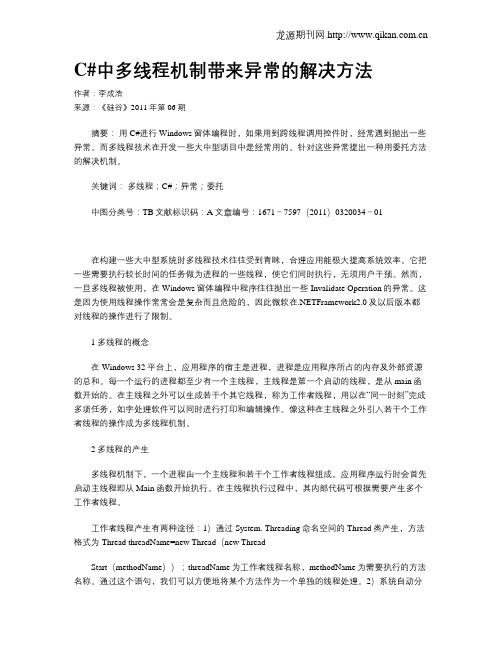

C#中多线程机制带来异常的解决方法

C#中多线程机制带来异常的解决方法作者:李成浩来源:《硅谷》2011年第06期摘要:用C#进行Windows窗体编程时,如果用到跨线程调用控件时,经常遇到抛出一些异常。

而多线程技术在开发一些大中型项目中是经常用的。

针对这些异常提出一种用委托方法的解决机制。

关键词:多线程;C#;异常;委托中图分类号:TB文献标识码:A文章编号:1671-7597(2011)0320034-01在构建一些大中型系统时多线程技术往往受到青睐,合理应用能极大提高系统效率。

它把一些需要执行较长时间的任务做为进程的一些线程,使它们同时执行,无须用户干预。

然而,一旦多线程被使用,在Windows窗体编程中程序往往抛出一些Invalidate Operation的异常。

这是因为使用线程操作常常会是复杂而且危险的,因此微软在.NETFramework2.0及以后版本都对线程的操作进行了限制。

1 多线程的概念在Windows 32平台上,应用程序的宿主是进程,进程是应用程序所占的内存及外部资源的总和。

每一个运行的进程都至少有一个主线程,主线程是第一个启动的线程,是从main函数开始的。

在主线程之外可以生成若干个其它线程,称为工作者线程,用以在“同一时刻”完成多项任务,如字处理软件可以同时进行打印和编辑操作。

像这种在主线程之外引入若干个工作者线程的操作成为多线程机制。

2 多线程的产生多线程机制下,一个进程由一个主线程和若干个工作者线程组成。

应用程序运行时会首先启动主线程即从Main函数开始执行。

在主线程执行过程中,其内部代码可根据需要产生多个工作者线程。

工作者线程产生有两种途径:1)通过System. Threading命名空间的Thread类产生,方法格式为Thread threadName=new Thread(new ThreadStart(methodName));threadName为工作者线程名称,methodName为需要执行的方法名称。

uncaughtexceptionhandler 原理 -回复

uncaughtexceptionhandler 原理-回复"uncaughtexceptionhandler 原理"是指当Java程序运行过程中发生未捕获的异常时,通过设置全局的异常处理器进行异常处理的机制。

本文将从异常处理机制的基本概念开始,深入探讨uncaughtexceptionhandler 的原理,并逐步分析其实现步骤。

一、异常处理机制的基本概念在编程过程中,我们经常会遇到各种异常情况,如空指针异常、数组越界异常等等。

这些异常会导致程序运行出错或崩溃,为了使程序能够更好地处理这些异常情况,Java提供了异常处理机制。

在Java中,异常是一个对象,用于表示程序执行过程中出现的异常情况。

当异常发生时,会创建一个异常对象,并将该对象抛出(throw),接着程序会查找能够处理该异常的代码块,如try-catch语句块。

二、uncaughtexceptionhandler的作用在Java中,如果程序中的某个线程发生未捕获的异常时,该线程会立即终止执行,并且默认情况下,异常信息会打印到标准错误输出流(System.err)。

然而,在一些特殊情况下,我们可能需要自定义处理未捕获异常的方式,这时就可以使用uncaughtexceptionhandler。

三、uncaughtexceptionhandler的原理uncaughtexceptionhandler是一个接口,用于处理未捕获的异常。

该接口只有一个方法:uncaughtException(Thread t, Throwable e)。

当一个线程中的未捕获异常导致该线程终止时,JVM会在终止前调用该方法,将线程对象和异常对象作为参数传递给该方法。

四、uncaughtexceptionhandler的使用要使用uncaughtexceptionhandler,我们需要实现该接口,并将实现的对象注册到线程对象上。

可以通过Thread类提供的setUncaughtExceptionHandler方法来进行注册。

dao openrecordset方法

Dao OpenRecordset方法一、概述在使用Visual Basic for Applications (VBA)或Visual Basic语言时,我们经常需要和数据库进行交互。

对于Microsoft Access数据库而言,我们可以使用Data Access Objects (DAO)来实现数据库的访问和操作。

而在DAO中,OpenRecordset方法是非常常用的一个方法,它用于打开指定的记录集并返回一个Recordset对象,从而可以对该记录集进行诸如查询、筛选、更新、删除等操作。

二、OpenRecordset方法的语法OpenRecordset方法的基本语法如下:```expression.OpenRecordset(Name, Type, Options, LockEdits)```其中,expression代表一个DAO.Database或DAO.Recordset对象,Name代表要打开的表、查询或SQL语句的名称,Type代表记录集的类型,取值可以为dbOpenTable、dbOpenDynaset、dbOpenSnapshot、dbOpenForwardOnly等,Options代表选项,可以为dbReadOnly、dbAppendOnly等,LockEdits代表是否锁定编辑,取值可以为True或False。

三、OpenRecordset方法的使用示例下面我们将通过一个具体的示例来演示OpenRecordset方法的使用。

我们假设我们有一个名为"Employees"的表,该表包含员工的尊称、工号、部门等信息,并且我们需要在VBA中使用DAO打开该表并对其进行一些操作。

首先我们需要创建一个DAO.Database对象,并打开指定的数据库:```vbDim db As DAO.DatabaseSet db = CurrentDb```我们可以使用OpenRecordset方法来打开"Employees"表的记录集:```vbDim rst As DAO.RecordsetSet rst = db.OpenRecordset("Employees", dbOpenDynaset)```现在,我们已经成功使用OpenRecordset方法打开了"Employees"表的记录集,并得到了一个Recordset对象rst。

interlocked.decrement 返回值 -回复

interlocked.decrement 返回值-回复interlocked.decrement 返回值是一个用于表示操作之后的结果的整数类型。

在多线程编程中,interlocked.decrement 是一种线程安全的操作,用于将整型变量的值减1,并且保证在并发情况下操作的正确性。

本文将深入探讨interlocked.decrement 返回值的性质、用法和相关应用。

首先,我们需要了解interlocked.decrement 的基本用法和工作原理。

该方法是通过原子操作来减少一个整数变量的值。

原子操作是指不可被中断的操作,要么完成,要么不做任何事情。

例如,当多个线程同时访问并修改同一个整数变量时,使用普通的减法运算符可能会导致竞态条件和不可预测的结果。

而使用interlocked.decrement 方法可以确保所有线程按照正确的顺序执行减法操作,且相互不会干扰。

此外,interlocked.decrement 还会返回执行减法操作后的结果。

接下来,我们来讨论interlocked.decrement 返回值的性质。

该返回值是一个表示减法操作后的结果的整数。

它是线程安全的,意味着无论多少个线程并发调用interlocked.decrement 方法,都能获取到准确的结果。

这个返回值对于我们在编程中决策、判断和后续操作都非常重要。

例如,我们可以根据返回值来判断减法操作后的结果是否为零,从而做出相应的处理。

此外,interlocked.decrement 返回值还可以与其他整数进行比较或进行进一步的运算,以满足特定的业务需求。

在实际应用中,interlocked.decrement 返回值有许多实用的用途。

以下是几个常见的应用场景:1. 计数器的操作:在多线程环境下,我们经常需要对一个计数器进行操作,例如统计某个事件发生的次数或控制并发访问资源的数量。

这时,我们可以使用interlocked.decrement 返回值来检查是否达到预设的阈值,以触发特定的行为或控制逻辑。

waitformultipleobjects的返回值

waitformultipleobjects的返回值

全文共四篇示例,供读者参考

第一篇示例:

3. 返回正整数:当等待的某个对象的状态改变时,返回值为该对

象在对象数组中的索引。

根据返回的索引值,可以确定是哪一个对象

的状态发生了改变,从而在程序中做出相应处理。

第二篇示例:

3. 返回值为其他值:表示部分或所有对象已经发生信号。

根据返

回值的位图信息,可以判断哪些对象已经发生了信号,哪些对象还处

于非信号状态。

第三篇示例:

在实际应用中,我们可以根据需求选择不同的等待对象和等待时

间参数,来实现不同的等待策略。

比如可以选择等待任意一个对象变

为有信号状态,也可以选择等待所有对象变为有信号状态。

根据返回

值来判断等待哪个对象已经完成,然后执行相应的操作。

第四篇示例:

返回值中的每一位都对应着一个被等待的对象,比如线程或者事件。

当返回值中的某一位为1时,表示对应的对象状态已经发生了变化,

而当为0时表示对应的对象状态仍然未发生变化。

通过分析返回值的二进制数值,程序员可以获取到相应的对象状态信息,从而实现程序的逻辑控制。

statement executequery 的返回值

statement executequery 的返回值statement executeQuery的返回值是一个ResultSet对象。

在Java编程中,当需要从数据库中检索数据时,我们可以使用JDBC(Java 数据库连接)来与数据库进行交互。

在执行查询语句时,可以使用Statement接口的executeQuery方法来发送并执行SQL查询,并返回结果集。

ResultSet对象代表了查询的结果集,它包含了满足查询条件的记录的集合。

结果集是一个二维表格状的数据结构,它包含了行和列。

每一行代表了一个记录,每一列代表了记录中的一个字段。

以下是关于ResultSet对象的一些重要特点:1. 可以使用next()方法来遍历结果集。

初始时ResultSet指针指向第一个记录的前面,通过调用next()方法可以将指针移到下一行。

如果指针指向了有效的记录,则方法返回true,否则返回false。

2. 可以使用getXXX()方法来获取记录中字段的值。

其中XXX表示数据类型,如getInt、getString等。

这些方法接受一个整数参数,用于指定要获取的列的索引或一个字符串参数,用于指定要获取的列的名称。

在接下来的文章中,我们将更加详细地讨论ResultSet对象及其使用。

第一部分:ResultSet对象的创建和使用首先,我们需要创建一个Statement对象来执行查询操作,该对象可以通过Connection的createStatement()方法来创建。

然后,我们可以使用Statement对象的executeQuery方法来执行SQL查询,并将结果存储在ResultSet对象中。

下面是一个示例代码:javaStatement statement = connection.createStatement(); ResultSet resultSet = statement.executeQuery("SELECT * FROM employees");在上面的代码中,我们执行了一个SELECT语句并将结果存储在resultSet 对象中。

Dao层处理数据时使用execute()、executeQuery()、executeUp。。。

Dao层处理数据时使⽤execute()、executeQuery()、executeUp。

在⽤纯JSP做⼀个页⾯报警功能的时候习惯性的⽤executeQuery来执⾏SQL语句,结果执⾏update时就遇到问题,语句能执⾏,但返回结果出现问题,另外还忽略了executeUpdate的返回值不是结果集ResultSet,⽽是数值!特收藏如下⼀篇⽂章(感谢⽹友们对各种信息的贡献):JDBCTM中Statement接⼝提供的execute()、executeQuery()和executeUpdate()之间的区别Statement 接⼝提供了三种执⾏ SQL 语句的⽅法:executeQuery、executeUpdate 和 execute。

使⽤哪⼀个⽅法由 SQL 语句所产⽣的内容决定。

⽅法executeQuery()⽤于产⽣单个结果集的语句,例如 SELECT 语句。

被使⽤最多的执⾏ SQL 语句的⽅法是 executeQuery()。

这个⽅法被⽤来执⾏ SELECT 语句,它⼏乎是使⽤最多的 SQL 语句。

⽅法executeUpdate()⽤于执⾏ INSERT、UPDATE 或 DELETE 语句以及 SQL DDL(数据定义语⾔)语句,例如 CREATE TABLE 和 DROP TABLE。

INSERT、UPDATE 或 DELETE 语句的效果是修改表中零⾏或多⾏中的⼀列或多列。

executeUpdate() 的返回值是⼀个整数,指⽰受影响的⾏数(即更新计数)。

对于 CREATE TABLE 或 DROP TABLE 等不操作⾏的语句,executeUpdate() 的返回值总为零。

使⽤executeUpdate⽅法是因为在 createTableCoffees 中的 SQL 语句是 DDL (数据定义语⾔)语句。

创建表,改变表,删除表都是 DDL 语句的例⼦,要⽤ executeUpdate ⽅法来执⾏。

单片机无符号整形除法溢出

单片机无符号整形除法溢出单片机无符号整形除法溢出是一种常见的编程错误,它发生在执行除法操作时,当除数不能被被除数整除时。

在无符号整形数中,这种溢出会导致结果不正确,甚至可能导致程序崩溃。

下面将详细介绍单片机无符号整形除法溢出的原因、影响以及如何避免这种错误。

一、原因1. 除数溢出:当被除数过大,而除数过小,导致无法整除时,就会发生溢出。

例如,一个无符号整形数最大为65535,如果用一个较小的数去除它,就会发生溢出。

2. 除数和被除数不匹配:在执行除法操作时,如果被除数和除数的位数不匹配,也可能导致溢出。

例如,用一个16位无符号整形数去除一个32位无符号整形数,由于位数不匹配,可能会导致溢出。

二、影响1. 结果错误:由于溢出导致结果不正确,程序可能会产生错误的结果。

2. 程序崩溃:如果溢出严重,可能会导致程序崩溃,无法正常运行。

3. 系统稳定性:溢出问题可能会影响系统的稳定性,导致系统出现异常。

三、避免方法1. 检查除数和被除数:在执行除法操作之前,应该检查除数和被除数的位数是否匹配,以及是否有可能导致溢出。

2. 使用有符号整形数:在需要执行除法操作时,可以考虑使用有符号整形数代替无符号整形数。

有符号整形数的范围更大,可以避免因溢出而导致的问题。

3. 使用取模操作:在执行除法操作之前,可以先将被除数取模,以避免溢出。

例如,如果被除数是n,除数是m,可以先将n取模m,然后再进行除法操作。

这样可以确保结果在m的范围内,避免溢出。

4. 使用库函数:许多编程语言提供了库函数来执行除法操作,这些函数通常会处理溢出问题。

因此,在执行除法操作时,可以考虑使用这些库函数来避免溢出问题。

5. 增加溢出检测:在执行除法操作时,可以增加溢出检测机制。

如果检测到溢出,可以采取相应的措施来处理溢出问题,例如抛出异常或返回错误码等。

6. 调整数据类型:根据实际需求调整数据类型的大小和范围,以避免因数据类型不匹配而导致的问题。

dolphinscheduler 调用返回参数存储过程报错-概述说明以及解释

dolphinscheduler 调用返回参数存储过程报错-概述说明以及解释1.引言1.1 概述引言部分是文章的开头部分,用于概述整篇文章的主要内容和目的。

在这里,我们可以简要介绍文章的主题和关键问题。

以下是一个可能的概述内容:概述:本文讨论了在使用Dolphinscheduler调用返回参数存储过程时可能遇到的问题。

Dolphinscheduler是一个开源的分布式任务调度系统,广泛应用于数据处理和任务调度的场景中。

然而,在调用返回参数存储过程的过程中,一些用户报告了出现错误的情况。

本文将对这个问题进行深入研究,分析可能的原因并提供解决方案。

首先,我们将介绍Dolphinscheduler的背景和基本情况,以便读者能够更好地理解这个调度系统的使用场景和特点。

然后,我们将重点分析Dolphinscheduler调用返回参数存储过程时出现的错误,并对可能的原因进行深入探讨。

最后,我们将总结问题并提供一些解决方案,同时展望未来Dolphinscheduler在这个领域的发展前景。

通过本文的阅读,读者将能够了解在使用Dolphinscheduler调用返回参数存储过程时可能遇到的问题,并掌握解决这些问题的方法和技巧。

无论你是一个Dolphinscheduler的新手还是一个有经验的用户,本文都将为你带来有价值的信息和见解。

接下来,让我们进入正文部分,介绍Dolphinscheduler的背景以及调用返回参数存储过程的问题。

1.2 文章结构本文分为三个主要部分:引言、正文和结论。

引言部分将对本文的主题进行概述,介绍Dolphinscheduler调用返回参数存储过程报错的问题,并说明本文的目的。

正文部分分为三个小节。

首先,背景介绍将提供有关Dolphinscheduler的一般背景信息,包括其用途和特点。

其次,将详细介绍Dolphinscheduler调用返回参数存储过程时可能遇到的问题,包括具体的错误信息和可能的原因。

interlocked.decrement 返回值 -回复

interlocked.decrement 返回值-回复主题:interlocked.decrement 返回值及其用法引言:在编程过程中,经常会遇到多线程同时操作一个共享资源的情况。

为了确保并发操作的正确性和准确性,我们需要使用线程同步机制来保护这些共享资源。

在.NET平台上,为我们提供了一系列用于线程同步的工具和方法,其中interlocked.decrement就是其中之一。

本文将详细介绍interlocked.decrement方法的返回值及其用法,帮助读者更好地理解和应用这个方法。

1. 什么是interlocked.decrement方法?Interlocked类是.NET提供的一个用于实现线程同步的类,其中的decrement方法可以对一个整型变量进行原子性的自减操作。

原子性操作是指不会被其他线程中断的操作,它相当于一个不可分割的单位,要么执行完毕,要么未执行。

这样可以避免多线程并发操作时出现的竞态条件和不一致性问题。

2. interlocked.decrement方法的语法和返回值interlocked.decrement方法的语法如下:public static int Decrement(ref int location);其中,ref int location是需进行自减操作的整型变量的引用。

返回值是自减后的变量值。

3. interlocked.decrement方法的用法下面我们将一步一步介绍interlocked.decrement方法的具体用法。

(1)创建一个整型变量count,并初始化为一个正整数。

int count = 10;(2)调用interlocked.decrement方法对count进行自减操作:int result = Interlocked.Decrement(ref count);(3)根据interlocked.decrement方法的返回值进行相应的处理。

unhandled access violation reading 2016 -回复

unhandled access violation reading 2016 -回复题:unhandled access violation reading 2016 异常解析与解决方案摘要:本文将介绍unhandled access violation reading 2016 异常的含义、可能的原因以及解决方案。

通过逐步分析,读者将了解如何定位和解决该异常,以提高代码的稳定性和可靠性。

第一部分:简介在计算机编程中,unhandled access violation reading 2016 是一种常见的异常类型,它通常指出程序在读取内存时遇到了问题。

这个异常的主要特点是它没有被程序有效地捕获和处理,进而导致程序的崩溃。

第二部分:常见原因unhandled access violation reading 2016 异常的产生原因多种多样,以下是一些常见的原因:1. 无效的指针:最常见的原因是程序试图使用一个未初始化的指针或已被释放的指针进行内存读取操作。

在这种情况下,访问无效的内存地址会触发异常。

2. 缓冲区溢出:当程序试图访问超过已分配内存空间的数据时,缓冲区溢出异常可能会发生。

这可能会导致访问无效的内存地址,从而引发unhandled access violation reading 2016 异常。

3. 资源管理错误:当程序在使用资源(如文件、网络连接等)时,未正确管理这些资源可能导致异常。

例如,试图读取一个已关闭的文件或试图使用已关闭的网络连接都有可能引发异常。

4. 多线程同步错误:如果多个线程同时访问共享资源而没有正确同步,可能会导致unhandled access violation reading 2016 异常。

以上仅列举了一部分常见的原因,还有其他可能的原因。

第三部分:异常处理策略当遭遇unhandled access violation reading 2016 异常时,以下是一些常用的异常处理策略。

waitformultipleobjects的返回值

waitformultipleobjects的返回值

WaitForMultipleObjects 是一个Windows API函数,用于等待多个内核对象(如线程、进程、信号量、互斥量等)的状态改变。

这个函数在同步多个线程或进程时非常有用。

WaitForMultipleObjects的返回值是一个DWORD(32位无符号整数),它表示函数执行的结果。

返回值的可能情况如下:

WAIT_OBJECT_0 (0x00000000): 指定对象集中的第一个对象变为信号状态。

WAIT_OBJECT_0 + n (其中n是1到dwCount-1之间的一个值): 指定对象集中的第n个对象变为信号状态。

WAIT_TIMEOUT (0x00000102): 超时已过,没有任何对象变为信号状态。

WAIT_FAILED (0xFFFFFFFF): 函数执行失败。

你可以通过调用GetLastError函数来获取更详细的错误信息。

请注意,如果你正在等待多个对象,并且多个对象几乎同时变为信号状态,那么WaitForMultipleObjects可能会返回任何一个变为信号状态的对象的索引。

此外,WaitForMultipleObjects还有一个超时参数,允许你指定一个最大的等待时

间。

如果在这个时间内没有对象变为信号状态,函数将返回WAIT_TIMEOUT。

这个函数在同步操作中非常有用,特别是在需要等待多个线程或进程完成它们的任务时。

currentdb.openrecordset 参数

currentdb.openrecordset 参数「currentdb.openrecordset 参数」指的是在Microsoft Access数据库中使用CurrentDb对象的OpenRecordset方法时所能传递的参数。

这些参数用于指定需要访问和操作的数据库记录集的条件和排序方式。

本文将详细介绍这些参数的使用方法,以帮助读者更好地了解和使用Access数据库。

首先,我们需要明确OpenRecordset方法的基本语法。

它的一般形式如下:Set rs = CurrentDb.OpenRecordset(Source, Type, Options, LockEdit)其中:- rs表示一个Recordset对象,用于引用返回的记录集。

- Source是必需的参数,用于指定需要访问的数据库表名、查询(Query)名、SQL语句等。

例如:表名或查询名可以直接使用字符串,而SQL语句可以使用字符串变量或字符串常量等。

- Type是一个可选参数,用于指定打开记录集的类型。

这个参数可以是RecordsetTypeEnum中的一个常量,例如:dbOpenTable、dbOpenDynaset、dbOpenSnapshot等。

- Options也是一个可选参数,用于指定打开记录集时的选项。

这个参数可以是RecordsetOptionEnum中的一个常量,例如:dbReadOnly、dbAppendOnly、dbConsistent等。

- LockEdit也是一个可选参数,用于指定是否锁定记录集以进行编辑。

这个参数可以是RecordsetLockTypeEnum中的一个常量,例如:dbOptimistic、dbPessimistic等。

接下来,我们将逐个介绍这些参数的使用方法。

首先是Source 参数。

在使用Source参数时,我们可以传递字符串、变量或SQL 语句来指定要访问和操作的数据库记录集。

例如,我们可以使用下列代码打开名为"Customers"的表的记录集:Set rs = CurrentDb.OpenRecordset("Customers")在这个例子中,我们直接使用了表名作为字符串来指定需要打开的记录集。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Joan-Manuel Parcerisa, Antonio GonzálezUniversitat Politècnica de CatalunyaDepartament d’Arquitectura de ComputadorsJordi Girona 1-3, Mòdul C6E 08034 Barcelona (Spain)Email: {jmanel, antonio}@ac.upc.esPhone: + 34 3 4011653; Fax: + 34 3 4017055AbstractThis work presents and evaluates a novel processor microarchitecture which combines two paradigms: access/execute decoupling and simultaneous multithreading.We investigate how both techniques complement each other in the design of high performance next generation ILP processors. While decoupling features an excellent memory latency hiding efficiency, simultaneous multithreading supplies the in-order issue stage with enough ILP to hide the functional unit latencies. Furthermore, since its in-order issue policy is substantially less complex, in terms of critical path delays, than a more general out-of-order mechanism, we believe that it is well suited for future increases in issue-width and clock speed.First, a generic decoupled access/execute architecture is defined and evaluated. Then the benefits of a lockup-free cache, control speculation and a store-load bypass mechanism under such architecture are evaluated. Our analysis indicates that memory latency can be almost completely hidden by such techniques. However, functional unit latencies still penalize each time that a true data dependence has not been solved by the compile-time scheduler. These penalties become the major source of wasted cycles in decoupled architectures, and they worsen with growing issue widths.Then, a new microarchitecture, which adds simultaneous multithreading to the decoupled access/ execute model to compensate its lack of dynamic scheduling, is defined and evaluated. The simulations show that few threads are enough to achieve almost peak performance. It is observed that decoupling, by making memory data readily available to the threads, increases the number of instructions that can be selected for issue, thus needing fewer threads to achieve peak performance.One of the problems of multithreading is the degradation of the memory system performance. This impact is significantly reduced by the ability of decoupling to tolerate long memory latencies. Our analysis shows that performance is ultimately limited by the external memory bus bandwidth. W e show that this bottleneck can be significantly reduced by the use of XOR-based placement functions for the cache, which show better performance than set associative caches.Finally, we propose to use dynamic register renaming in order to avoid the duplication of memory instructions. This technique can increase the performance of an eight-issue processor by 20%. Keywords: Access/execute decoupling, simultaneous multithreading, latency hiding, instruction-level parallelism, dynamic register renaming, XOR-based placement functions, lockup-free cache.AbstractThis work presents and evaluates a novel processor microarchitecture which combines two paradigms: access/execute decoupling and simultaneous multithreading.We investigate how both techniques complement each other in the design of high performance next generation ILP processors. While decoupling features an excellent memory latency hiding efficiency, simultaneous multithreading supplies the in-order issue stage with enough ILP to hide the functional unit latencies. Furthermore, since its in-order issue policy is substantially less complex, in terms of critical path delays, than a more general out-of-order mechanism, we believe that it is well suited for future increases in issue-width and clock speed.First, a generic decoupled access/execute architecture is defined and evaluated. Then the benefits of a lockup-free cache, control speculation and a store-load bypass mechanism under such architecture are evaluated. Our analysis indicates that memory latency can be almost completely hidden by such techniques. However, functional unit latencies still penalize each time that a true data dependence has not been solved by the compile-time scheduler. These penalties become the major source of wasted cycles in decoupled architectures, and they worsen with growing issue widths.Then, a new microarchitecture, which adds simultaneous multithreading to the decoupled access/ execute model to compensate its lack of dynamic scheduling, is defined and evaluated. The simulations show that few threads are enough to achieve almost peak performance. It is observed that decoupling, by making memory data readily available to the threads, increases the number of instructions that can be selected for issue, thus needing fewer threads to achieve peak performance.One of the problems of multithreading is the degradation of the memory system performance. This impact is significantly reduced by the ability of decoupling to tolerate long memory latencies. Our analysis shows that performance is ultimately limited by the external memory bus bandwidth. W e show that this bottleneck can be significantly reduced by the use of XOR-based placement functions for the cache, which show better performance than set associative caches.Finally, we propose to use dynamic register renaming in order to avoid the duplication of memory instructions. This technique can increase the performance of an eight-issue processor by 20%. Keywords: Access/execute decoupling, simultaneous multithreading, latency hiding, instruction-level parallelism, dynamic register renaming, XOR-based placement functions, lockup-free cache.1.IntroductionThe gap between the speeds of processors and memories has kept increasing in the past decade and it is expected to sustain the same trend in the near future. This divergence implies, in terms of clock cycles, an increasing latency of those memory operations that cross the chip boundaries. In addition, processors keep growing their capabilities to exploit parallelism by means of greater issue widths and deeper pipelines, which makes even higher the negative impact of memory latencies on the performance. To alleviate this problem, most current processors devote a high fraction of their transistors to on-chip caches [23], in order to reduce the average memory access time. Several prefetching techniques have been also developed, both hardware and software [3].Some processors, commonly known as out-of-order issue [38, 20, 18, 9, 10], include dynamic scheduling techniques, most of them based on the Tomasulo algorithm [32] or variations of it, that allow them to tolerate both memory an functional unit latency, by overlapping it with useful computations ofother independent instructions. To implement it, the processor is capable of filling issue slots with independent instructions by looking forward in the instruction stream, into a limited instruction window. This is a general mechanism that aggressively extracts the instruction parallelism available in the instruction window.A decoupled access/execute architecture [25, 26, 8, 37, 36, 22, 2, 13] includes some limited kind of dynamic scheduling which is especially oriented to tolerate memory latency. It splits - statically or dynamically - the instruction stream into two. One stream is composed of all those instructions involved in the fetch of data from memory, and it executes asynchronously respect the other one, which is formed with the instructions that process these data. Both streams are executed on independent processing units (called AP and EP respectively, in this paper) which communicate mutually and with the memory system through queues. The AP is expected to execute in advance of the EP and to prefetch the data from memory so that the EP can consume the data without any delay. This anticipation or slippage may involve multiple conditional branches, so it actually performs a kind of dynamic loop unrolling, and is even capable to completely unroll a loop [6]. However, the amount of slippage between the AP and the EP highly depends on the program ILP, because data and control dependencies can force both units to synchronize - the so called Loss of Decoupling events [2, 33] - producing a serious performance degradation.As memory latencies continue to grow in the future, out-of-order processors will need longer issue windows to find independent instructions to fill the increasing number of empty issue slots, and this number will grow even faster with greater issue widths. The increase in the instruction window size will have an obvious influence on the chip area, but its major negative impact will strike at the processor clock cycle time. As reported recently [21], the networks involved in the issue stage, and also - although to a less extent - those of the renaming stage, are in the critical path that determines the clock cycle time. In their analysis, the authors of that study state that the delay function of these networks has a component that increases quadratically with the window length. And, although linearly, it also depends strongly on the issue width. Moreover, higher density technologies only aggravate the problem because they make these latencies to grow even faster. Their analysis suggest that out-of-order architectures could find in the future a serious boundary on their clock speeds.A decoupled processor provides an alternative to this problem. It has a reduced issue and data bypass logic complexity, not only because of its in-order issue policy, but also because these tasks are subdivided into two processing units, with independent register files and pipelines. Therefore, it adapts to higher memory latencies by scaling much simpler structures than an out-of-order, i.e. scaling at a lower hardware cost, or conversely scaling at a higher degree with similar cost. However, since each instruction stream in a traditional decoupled processor is executed sequentially, it exploits a lower degree of parallelism than an out-of-order machine.Therefore, we propose a new decoupled architecture which provides both the AP and the EP with a powerful dynamic scheduling mechanism: simultaneous multithreading [35, 34]. Each processing unit has several contexts, each issuing instructions in-order, which are active simultaneously and compete for the issue slots, so that instructions from different contexts can be issued in the same cycle. The combination of decoupling and mulithreading takes advantage of their best features: while decoupling is a simple but effective technique for hiding long memory latencies with a reduced issue complexity, multithreading provides enough parallelism to hide functional unit latencies, and scalability to wider issue architectures. In addition, multithreading also helps to hide memory latency when a program decouples badly. However, as far as decoupling hides memory latency, few threads are needed to achieve a high issue rate. On the other hand, multithreading increases memory pressure, but this problem is significantly relieved by decoupling.Therefore, we believe that a decoupled access/execute architecture can regain progressively interest as far as issue widths and memory latencies keep growing and demanding larger instruction windows,because these trends will make it worth trading issue complexity for clock speed. This is the motivation for this work.We first analyze a generic decoupled architecture with dynamic instruction split [26, 13, 37] and a data cache. Other studies on decoupled machines have been carried out before [1, 25, 8, 28, 26, 37, 36, 19, 11, 15], but they did not analyze techniques like store-load forwarding, control speculation or lockup-free caches. In this paper we evaluate specifically the impact of these techniques when applied to a decoupled processor, and quantify the memory latency sensitivity of this architecture. Then, we propose a multithreaded decoupled microarchitecture and evaluate its performance and latency sensitivity. We show that this architecture can exploit a high degree of ILP while being quite latency tolerant even with very few threads. Data dependencies and memory latency hardly cause any penalty in this architecture and the main performance bottleneck becomes the external memory bus bandwidth. It is shown that external memory bandwidth requirements are significantly reduced by XOR-mapped cache memories, which exhibit a better performance than set associative caches with the same miss ratio, due to a more uniform distribution of the cache misses. Finally, a dynamic register renaming scheme is proposed in order to avoid the duplication of memory instructions.The rest of this paper is organized as follows. Section 2 describes the basic decoupled architecture, analyzes the effectiveness of several architectural features, and provides justification for multithreading. Section 3 describes the proposed multithreaded decoupled architecture, evaluates it, identifies its major strengths and weaknesses, and proposes several alternatives for further improving its performance. Finally, we summarize our conclusions in Section 4.2.Quantitative Evaluation of a Decoupled ProcessorIn this section we identify through experimental evaluation the major sources of wasted cycles in a typical decoupled architecture, and the effectiveness of several techniques commonly used to alleviate these problems: lockup-free caches, store-load forwarding and control speculation. W e also evaluate the latency hiding effectiveness of this architecture. The discussion highlights the major weaknesses and strengths of the decoupled approach and provides motivation for a multithreaded decoupled architecture that is analized in the next section.2.1.The Basic Decoupled Architecture ModelThe baseline architecture evaluated in this paper (Figure1) consists of two superscalar decoupled processing units: the Address Processing unit (AP) and the Execute Processing unit (EP). The decoupled processor executes a single instruction stream, based on the DEC-alpha ISA [5], by splitting it dynamically and dispatching the instructions to either the AP or the EP. There are two separate register files, one in the AP with 32 integer registers, the other in the EP with 32 FP registers. Both units share a common fetch and dispatch stages, while they have separate issue, execute and write-back stage pipelines. Next, there is a brief description of each stage:The fetch stage reads up to 4 consecutive instructions per cycle from an ideal I-cache (less than 4 if there is a taken branch among them). It is also provided with a conditional branch prediction scheme based on a 2K entry Branch History Table, with a 2-bit saturating counter per entry [24].The dispatch stage decodes up to 4 instructions per cycle and sends them to either the AP or the EP instruction queue, depending on whether they are integer or floating point instructions, respectively, in a similar way to the ZS-1 [26] or the MIPS R8000 [13]. These queues have 4 and 64 entries, respectively. As an exception, Floads and Fstores are sent to both the AP and the EP, because while they move data to/from EP registers, their effective address calculation involves AP registers. This leads to some degree of code expansion which could be avoided by providing random access to the entries of the Load Data Queue andFigure 1:Scheme of the basic decoupled processorby renaming the EP registers to either the Load Data Queue entries or the physical register file (as analyzed in Section 3.6). Whether a conditional branch is dispatched to the AP or to the EP depends on the kind of comparison. The instructions that follow the branch are fetched based on a prediction, and some of them will be sent to the same processing unit than the branch, while others will be sent to the other processing unit. Each processing unit must be able to identify exactly which are the instructions that follow this branch, and to squash them in case of misprediction. It is easy to identify those instructions sent to the same processing unit than the branch, but there is nothing that distinguishes those sent to the other processing unit. The more simple solution would be to send the branch to both processing units, like in the ZS-1[26] among others, one of them being just a single token to indicate that the instructions following it are speculative. However, to avoid such code expansion, since this token has no operands, it has been replaced by a single bit added to the first next instruction dispatched to that processing unit. When the branch is resolved, the outcome is sent to the other processing unit through a Condition Queue.Since the AP usually executes ahead of the EP, and such slippage is a key factor on performance, in most of our experiments we assume that the AP can issue and execute speculatively instructions beyond a certain number of EP branches. However, this requires that the AP has the appropriate hardware to recover from mispredicted branches. Just for comparison, we have also implemented a non-speculative model where AP stalls and waits for EP branches to be resolved before issuing the instructions that follow them. Speculative execution has not been implemented in the EP because the required hardware is quite complex, and the EP does not naturally tend to execute ahead of the AP.Each processing unit is provided with 2 general purpose and fully pipelined functional units. Each processing unit can read and issue up to 2 instructions per cycle. For the sake of simplicity, the latencies of all operations in the EP are assumed to be 4 cycles, while those in the AP are only 1 cycle, except accesses to the data cache, which need one additional cycle in case of hit, and some more cycles in case of miss.The AP portion of an Fload calculates the effective address and sends it to the memory system. The data is finally delivered to the Load Data Queue (LDQ), from where it will be popped out, and written to a register, by the corresponding dummy Fload in the EP. Similarly, the AP calculates Fstore effective addresses and holds them in the Store Queue (SQ), until the data is delivered by the corresponding dummy Fstore in the EP. Both queues have 32 entries. Loads are allowed to execute ahead of uncompleted stores, after being disambiguated against all the addresses held in the SQ. In most of our experiments there existsalso a forwarding mechanism that allows dependent loads to be put aside in a pending queue until they receive the data directly from the store, thus avoiding to stall the AP .The primary data cache is on-chip, 2-ported [29], 8 KB, direct-mapped, with a 32 byte block length,and it implements a write-back policy to minimize off-chip bus traffic. We assume that primary cache misses always hit in a large ideal off-chip L2 cache, and they have a 16 cycle latency plus any penalty due to bus contention. On most of our experiments, we also assume a lockup-free L1 data cache [17] modelled like that of the Alpha 21164 [5], but augmenting to 16 the number of (primary) misses to different lines because the miss latency is also longer. It can also merge up to 4 (secondary) misses per pending line. The L1-L2 interface consists of a 128-bit wide data bus which completes one transaction each 2 CPU cycles (i.e. every cache line keeps the bus busy during 4 cycles) by overlapping several transactions.To maintain precise exceptions we assume that there exists an elementary reorder buffer, a graduation mechanism and some exception recovery hardware [14, 27] for the AP . The recovery hardware for the EP is greatly simplified by just preventing the EP from issuing ahead of uncompleted AP instructions (including conditional branches). As far as the AP executes ahead of the EP , this constraint saves lots of hardware complexity at the expense of very little penalties.2.2.Simulation Methodology and WorkloadExperiments are carried out with a trace driven simulator . The binary code is obtained by compiling the SPEC FP95 benchmark suite [31], for a DEC AlphaStation 600 5/266, with the DEC compiler applying full optimizations. The trace is generated by running this code previously instrumented with the A TOM tool[30]. The simulator models, cycle-by-cycle, the architecture described in the previous section, and runs the SPEC FP95 benchmarks, fed with their largest available input data sets.Because of the detail of the simulations they are very slow. Therefore we simulate only a portion of 100million instructions of each benchmark, after skipping an initial start-up phase. To determine the appropriate initial discarded offset we compared the instruction-type frequencies of such a fragment starting at different points, with the full run frequencies. We found that this phase has not the same length for all the benchmarks: about 5000 M instructions for 101.tomcatv and 103.su2cor; 1000 M for 104.hydro2d and 146.wave5; and just 100 M for the rest of the benchmarks.2.3.Sources of wasted cyclesWe have first measured the throughput of the Issue stage in terms of the percentage of committed instructions over the total issue slot count (i.e. % of cycles where it is really doing useful work) for a basic architecture having disabled the lockup-free cache, the store-load forwarding and the AP speculation. Thet o m c a t s w i m s u 2c o r h y d r o m g r i d a p p l u t u r b 3d a p s i f p p p p w a v e 5A V E R A G E Benchmark % o f I s s u e C y c l es memory data hazard cache busy wait register operandcontrol hazarduseful work Figure 2:AP (left) and EP (right) issue cycle breakdowns, for a basic decoupled architecture with non-blocking, forwarding and AP speculation disabled.t o m c a t s w i m s u 2c o r h y d r o m g r i d a p p l u t u r b 3d a p s if p p p p w a v e 5A V E R A G E Benchmark% o f I s s u e C y c l e sresults are shown in Figure 2. Figure 3 shows the results of a similar analysis (only the average of the ten benchmarks) when these three techniques are enabled separately, and also when they are combined in several ways.The wasted throughput is also characterized, by recording the cause for each empty issue slot. The label control hazard means that the AP cannot issue an instruction because it depends on an unresolved EP conditional branch. Register interlocks are labelled wait register operand . The label cache busy means that a memory instruction cannot be executed because the L1 cache is either being accessed by the L2 cache (for a line replacement), or it is processing a blocking miss. The label memory data hazard means that a Load stalls the AP because it references the same address than a previous pending Fstore. The label wait memory operand means that a Load instruction in the EP can not read its data because this is not yet delivered to the Load Data Queue. The label EP ahead of AP means that the EP is stalled in order not to overtake the AP, due to the restriction imposed to simplify precise exceptions. Finally, the label empty i-queue includes the slots wasted with uncommitted instructions (those squashed in case of a branch misprediction) and the slots lost because the instruction queue is empty. This latter cause is observed in programs that show a bad load balance between both processing units. Since more than one of these causes may overlap for a given instruction in a clock cycle, the stall is accounted to the first of these causes, in the order given in the legend of the plot (top-down order). W e discuss below the main conclusions drawn from these figures.2.3.1.Effectiveness of a lockup-free cache (load miss stalls)As shown in Figure 2 (labels cache busy and wait memory operand ), when a lockup-free cache is not used,the AP is stalled by load misses and the EP is waiting for memory data, for most of the time. Miss latency increases the AP cycle count far above the EP cycle count. The AP execution time becomes the bounding limit of the global performance, and decoupling can hardly hide memory latencies. The nature of these stalls is a structural hazard, and they can be reduced by providing the processor with a lockup-free cache.As shown in Figure 3 (column labelled nonbl ), with this cache, this kind of stalls are almost eliminated. Of course, this uncovers other overlapped causes, but the overall improvement in the performance achieves an impressive 89.7% increase (from 0.88 IPC to 1.67 IPC).2.3.2.Effectiveness of store-load forwarding (memory data hazard stalls).Another source of wasted cycles are memory data hazards (Figure 2, left) detected during memory disambiguation. With forwarding disabled, when a load matches the effective address of a pending Fstore,the AP pipeline is blocked until the store is issued to the cache. The EP is indirectly affected by these stalls:the slippage between the AP and the EP gets reduced - we call this event a loss of decoupling, or LOD [2,+forwd +spec +forwd+spec CPU Model% o f I s s u e C y c l es Figure 3:A summary of AP (left) and EP (right) issue cycle breakdowns, with the “average” columns ofall the models +forwd +spec +forwd+specCPU Model% o f I s s u e C y c l e s33] - and any other subsequent Fload is exposed to be penalized by the memory latency in case of a cache miss.Our experiments (Figure3 left, column forwd), show that store-load forwarding removes completely these stalls, but since most of the benchmarks are compute bound (except for turb3d), the overall speed-up will be, at most, that of the EP, and it depends on how much it was penalized by these LODs. That is, it depends on how frequent the stalls were, whether they made the amount of slippage drop below the threshold of the memory latency, and whether a subsequent Fload missed in the cache before the AP recovered the decoupling. Figure3 (columns forwd) shows that, despite the significant amount of saved stalls achieved by forwarding in the AP (labelled memory data hazards), the EP lost slots (labelled wait memory operand) are very little reduced. The average performance improvement is just a 2.27% increase (from 0.88 IPC to 0.90 IPC).2.3.3.Effectiveness of AP speculative execution (control hazard stalls)Another source of wasted cycles are control hazards originated by FP conditional branches. When speculative execution is disabled, the AP instructions that follow the branch must wait until the condition is delivered by the EP to the Condition Queue. This kind of LODs are removed by enabling the AP to execute speculatively instructions beyond one ore more branches. In case one of the branches is found to be mispredicted, the hardware must be able to recover the state previous to the branch [14, 27]. The cost of this hardware depends on the particular implementation and the speculation depth, which is the number of unresolved EP branches beyond which the instruction issue mechanism stalls. We have assumed a speculation depth of 4, which is the same as the MIPS R10000 [38] and the PowerPC 620 [20].Our experiments show that, although control hazard stalls are almost completely removed (Figure3, left), the average IPC increases only by 2.2%. This is due to the low average frequency of these branches (0.36% of all the instructions). However, this technique provides significant improvements to particular programs where they are more frequent. These is the case of hydro2d (2.35% of the completed instructions), which experiments a 20% increase of the IPC. It can be also noticed that when combining speculation with a lockup-free cache, the benefits of this technique are slightly higher (3.5% IPC increase) because the extra slippage provided to the AP by speculation is not lost by miss stalls, so that the latency perceived by Floads in the EP is reduced.In summary, we can conclude that store-load forwarding has a minor influence on performance. AP control speculation has also little impact on performance, but it is slightly higher if a lockup-free cache is present. In contrast, a lockup-free cache produces by itself such a high improvement that it is essential to a decoupled processor.tency hiding effectivenessThe interest of a decoupled architecture is closely related to its ability to hide long memory latencies. The latency hiding potential of a decoupled processor depends strongly on the decoupling behaviour of the programs being tested. For some programs, the scheduling ability of the compiler to remove LOD events, which force the AP and the EP to synchronize, is also a key factor. However, the compiler we have used (Digital f77) is not especially tailored to a decoupled processor. Therefore, to validate our conclusions, we are interested in having an assessment of the latency hiding effectiveness of our basic architecture without any specific compiler support.We have run the 10 benchmarks with the external L2 memory latency varying from 1 to 256 cycles. The simulations assume that the cache is 64 KB direct mapped, and the length of the processor architectural queues and the number of pending misses supported by the lockup-free cache are scaled up proportionally to the L2 latency. We have measured the miss ratio, the performance, the utilization of the EP instruction。