NiosII软处理器快速入门- 10分钟学会NiosII

NIOS2完整教程

NIOS2完整教程NIOS II 是一款高度可配置的32位嵌入式软核处理器,由Intel旗下的Altera(现在归属于英特尔)推出。

它具有低功耗、高性能和可扩展性的特点,适用于各种嵌入式应用领域。

下面是一份简要的NIOSII完整教程,帮助您了解如何开始使用NIOSII。

1. Nios II 架构Nios II 架构包括处理器核、总线接口、存储器和外设设备。

处理器核包括CPU和一些协处理器,如乘法器、除法器等。

总线接口用于连接处理器核、存储器和外设设备。

存储器用于存储指令和数据。

外设设备包括UART、GPIO、SPI、I2C等。

2. Nios II 开发环境搭建首先,您需要安装Altera的Quartus软件来进行Nios II的开发。

Quartus提供了一个开发工具套件,包括编译器、仿真器和调试器。

您还需要安装Nios II EDS,这是一个集成开发环境,用于配置和生成Nios II处理器的软件。

安装完软件后,您可以创建一个新的Nios II项目。

3. Nios II 项目配置在Quartus中创建新的Nios II项目时,您需要指定处理器类型、时钟频率和存储器大小等参数。

您还可以选择添加外设设备和协处理器。

一旦项目创建完成,您可以使用Nios II EDS来配置处理器和外设设备,并生成相关的软件。

4. Nios II 软件开发Nios II 支持多种软件开发工具,包括C/C++编译器、汇编器和调试器。

您可以使用C/C++编译器来编写和调试应用程序。

您还可以使用汇编器来编写高性能的关键代码。

调试器可以帮助您检测和修复应用程序中的错误。

5. Nios II 系统调试在开发过程中,您可能需要进行系统调试,以解决应用程序的问题。

Nios II 支持硬件和软件调试。

硬件调试通过连接JTAG接口进行,可以在硬件级别上进行调试。

软件调试使用Nios II调试器进行,可以在软件级别上进行调试。

6. Nios II 系统验证在完成软件开发和调试后,您可以进行系统验证,确保系统的正确性和稳定性。

NiosII 快速入门

NiosII 快速入门(在QuartusII中使用上述niosII系统) 3:在QuartusII中使用上述niosII系统在SOPC Builder正确运行完毕后,可以在QuartusII中,打开SOPC Builder生成的niosII_e.bsf,检查一下引脚,看看跟你的设想是否有误,如下图,niosII_e有两个input:clk,reset_n,一组output:out_port_from_the_piop[7:0]如下图:你可以使用上述的niosII_e,来构造你自己的系统。

如下图,我简单得创建了nisoSmall.bdf,来使用该niosII_e。

nios clk to clkniso reset_n to VCCout_port_from_the_pio_0[7:0] to LED[7:0]第三节:编写程序。

在Alter SOPC Builder中,点击Run Nios II IDE,启动Nios II IDE,如下图:在Nios II IDE中,选择File -> New -> Project,开启New Project 对话框选择C/C++ Application,如下图。

然后选择Next,进入下一步。

填写你自己的Project Name,比如我填写hello_led_1;在Select Project Template中,我选择Hello LED(因为存放程序的sram只有2kbytes,所以许多Template不可用),如下图。

然后选择Next,进入下一步。

选择Create a new system library named:,最后点击Finish,创建项目。

如下图:打开项目中的文件:hello_led.c,进行适当的修改。

比如,我将PIO的基地址修改为PIO_0_BASE;while(i<200000)修改为while(i<20000).你可以依照你的需求修改!然后选择Project->Build All(Ctrl+B),编译整个项目。

nios-ii-入门手册教学文案

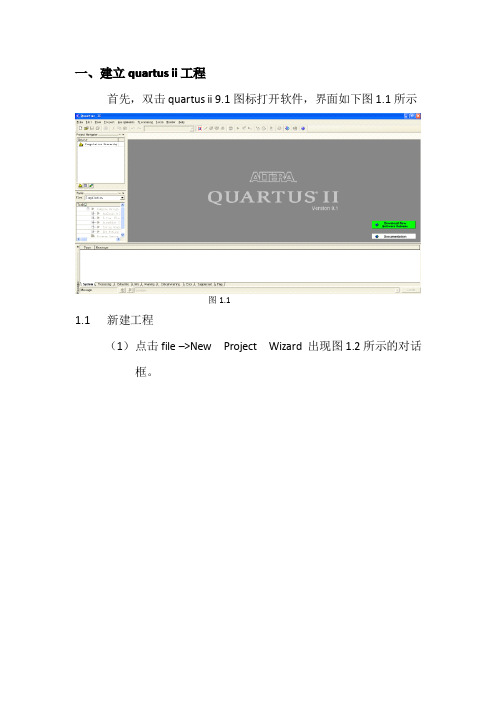

n i o s-i i-入门手册一、建立quartus ii工程首先,双击quartus ii 9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file –>New Project Wizard 出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file –>New ->Block Diagram/Schematic File 后如图1.7所示。

图1.7二、构建一个nios ii 软核(1)首先点击Tools ->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors -> Nios ii Processor 如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

NIOSII教程

最小逻辑占用的优化

7

7.1 Nios Ⅱ嵌入式处理器简介

Nios Ⅱ vs Nios

Nios Ⅱ

Pipelined RISC Architecture 32-Bit Instructions Flat Register File 32-Bit Data Path 32 Prioritized Interrupts Optional Instruction & Data Cache Custom Instructions Branch Prediction

一、第一代Nios嵌入式处理器 二、第二代Nios嵌入式处理器 三、可配置的软核嵌入式处理器的优势

2

7.1 Nios Ⅱ嵌入式处理器简介 一、第一代Nios嵌入式处理器

2000年,Altera发布了Nios处理器,这是第一款可 用于可编程逻辑器件的可配置的软核处理器。 基于RISC技术 16位指令集 16/32位数据通道 5级流水线 在一个时钟周期内完成一条指令的处理 具有一种基于JTAG的OCI(片上仪器)芯核

二、软件开发流程

21

7.2 Nios Ⅱ嵌入式处理器软、硬件开发流程

Nios Ⅱ Design Flow

Processor Library Peripheral Library

(1)

SOPC Builder GUI

Configure Processor Select & Configure Peripherals, IP Connect Blocks

Custom Instructions IP Modules

(2) Hardware Development

NIOS_II手把手入门

NIOS II手把手入门前言:NIOS II是什么?也许你第一次听到这个词。

通俗地讲,NIOS II其实是一个软核,那什么是软核?软核是一个基于哈佛结构的可配置处理器。

哈佛结构,联想到了吧,其实51单片机也是基于哈佛结构的处理器。

至于为什么是哈佛结构,我觉得可能是哈佛结构的处理速度较快,因为他可以在一个周期读取数据和指令。

(关于哈佛结构的详细信息请自己查阅!)因此NIOS II是把指令存储器和数据存储器分开的。

在此我想详细介绍下可配置处理器的概念。

我们都知道51单片机或者ARM里面的硬件资源都是固定的,是固化的,不能修改的。

但是软核可配置就不一样啦,它里面的CPU,外围器件都是可选择的。

因此我们可以根据实际的情况来选择需要的资源,这样可以提高利用率。

总之,大家把它当做单片机来学习就行了!讲了一大堆,相信大家还是有点模糊,下面就以流水灯介绍NIOS II吧,让我们进入NIOS II的神奇世界!(在此相信大家都已经掌握quartus的基本使用和安装了与quartus 同样版本的NIOS II软件!)Quartus环境操作:第一步:建立一个Quartus II工程和原理图文件第二步:打开配置NIOS II窗口第三步:配置NIOS II内核和外围器件(双击system contents窗口中component library下拉菜单的Nios II processor)接下来选择程序存储区和数据存储器还有通用8位IO 口。

然后配置通用IO口:(下面是选择器件区窗口,可以看到上面配置的器件!!)双击CPU,把复位矢量和异常矢量分配好:第四步:好了,到现在为止我们已经配置好一个简单的NIOS II内核,接下来就是漫长的等待吧!第五步:在原理图中添加内核symbol(其中内核复位信号是低电平复位!!)第六步:软件(C或C++)编程现在看一下NIOS II软件编写窗口吧,是不是跟单片机开发的有点类似!清空其他工程后,建立一个应用项目:file—new—Nios II C/C++ Application然后建立一个C程序文件:大家可以先把程序写下来,按下保存!等下会有相应的解释。

NIosII软处理器快速入门

NIosII软处理器快速入门2007-08-15 20:18:01 来源:与非网关键字:FPGA NIosIINios简单介绍:Nios II是一个用户可配置的通用RISC嵌入式处理器。

在这儿,我引用了Altera公司关于NiosII的官方介绍:Altera推出的Nios? II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获得超过200 DMIPS的性能,用户可以从三种处理器以及超过60个的IP核中选择所需要的,Nios II系统为用户提供了最基本的多功能性,设计师可以以此来创建一个最适合他们需求的嵌入式系统。

Nios II处理器的优点和特性使用Nios II处理器的用户可以根据他们的需要来调整嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

提高系统性能* 一系列的处理器核可供选择,其中包括了超过200 DMIPS性能的核* 实现任何数量的处理器或将不同的处理器核组和在一起* 增加了已有的处理器,在FPGA中添加一个或更多的Nios II软核处理器更低的系统成本* 通过将处理器、外设、存储器和I/O接口集成到一个单一的FPGA中,从而降低了系统成本、复杂性和功耗* 通过将Nios II处理器嵌入到低成本的FPGA中只需花费35美分或者更低(编者:对大多数用户而言,NiosII所占逻辑资源的成本大约是10-20元人民币,具体取决于所选FPGA 的类型和NiosII的配置)应对产品的生命周期* 提供易用的设计工具从而快速将产品推向市场。

* 提供永久的,免费的许可从而使基于Nios II处理器的产品避免了处理器的更新换代而带来的损失。

功能强大、易用的开发工具* 通过使用Nios II集成开发环境(IDE),从而加速了软件的开发* 利用Altera的强大的SOPC Builder系统开发工具和Quartus II设计软件可以在几分钟内设计一个系统使用完全功能的开发包* 使用易用的Nios II 开发包开始一个设计* 使用易用的Nios II开发包开始设计* 可以选择具有低成本特性的Cyclone FPGA开发套件,或高性能的Stratix FPGA开发套件稍微了解一下NiosII后,我们就来开始设计、应用它吧!下面我们就设计一个最简单的NiosII系统,使用NiosII去控制一个LED灯,通过这个例子我们可以了解整个介绍NiosII的设计流程第一节:EDA软件的安装。

NIOS_ II软核处理学习资料

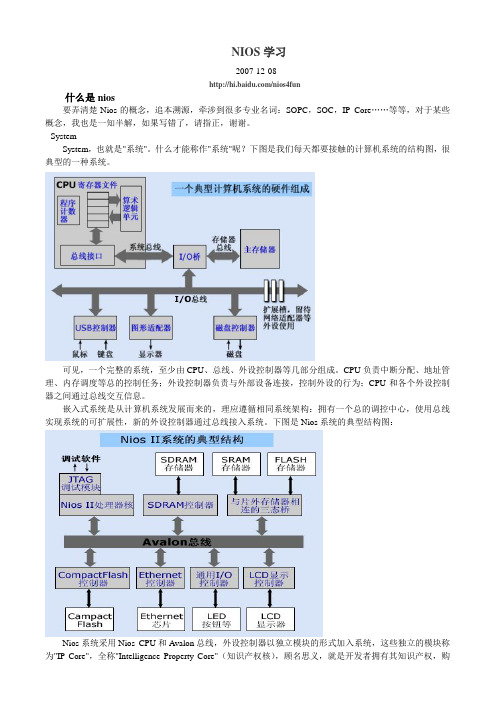

DSP是另外一种系统设计方法,与MCU专注于控制不同,DSP强调各种数字信号处理算法的快速实现。区别在于:

MCU采用的硬件结构是冯-诺依曼型,即在同一个存储空间取指令和数据,两者不能同时进行,因而地址总线和数据总线的宽度必须一致;DSP采用改进型哈佛结构,即指令和数据空间完全分开,并且有多个指令和数据空间,由于可以对程序和数据同时进行访问,所以提高了数据吞吐率,当然,地址总线和数据总线可以采用不同的宽度。除此之外,DSP具有专门的硬件乘法器,广泛采用流水线操作(即一条指令被执行时,允许下一条指令同时被取出),这些特性大大提高了DSP处理数据的能力。

SOPC可以理解为SOC在可编程器件上的实现,如果硬件调试成功后直接投片生产成“固定结构的芯片”,则其为普通的SOC;如果其硬件就是基于FPGA的,也就是说它是“用FPGA做为最终实现”的,它在以后也可以随时进行硬件升级与调试的,我们就叫它为SOPC的设计方法,所以说SOPC是SOC的一种解决方案。

--硬核,软核

上面提到,FPGA由存放在片内RAM中的程序进行配置,MPU是System不可或缺的一部分,如果设计者用到的MPU产品是一段VHDL或Verilog HDL代码,那么他在使用的时候可以对MPU进行修改,以满足自己所需要的功能。这种MPU称为"软核",典型代表有Nios软核和MicroBlaze软核。

软核与硬核的优缺点是很明显的,如果追求性能的稳定和应用的简便,应该选择硬核;硬核固然有很多优势,但它在灵活性上还是受到了制约。道理很简单:一旦你在某个型号的FPGA中加入了一个硬核MPU,硬核MPU也就将其“不灵活”的属性带给了这个平台——MPU过时了,也就意味着平台过时了。因此,如果想追求更大限度的灵活性,设计者可以选择在FPGA中“写”入一个软核,而不是“固化”一个硬核。

nios-ii-入门手册复习课程

n i o s-i i-入门手册一、建立quartus ii工程首先,双击quartus ii 9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file –>New Project Wizard 出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file –>New ->Block Diagram/Schematic File 后如图1.7所示。

图1.7二、构建一个nios ii 软核(1)首先点击Tools ->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors -> Nios ii Processor 如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

Nios II 快速入门

Nios II快速入门Nios II的开发涉及到多个软件工具,由于文档需要面向最广泛的开发者,在这一篇中以一般的开发流程,图文并列的方式进行探讨,假设读者已经正确安装Altera公司的Quartus II5.1或更高版本、Nios II Development Kit 5.1或更高版本的软件,对软件安装不再赘述。

1软件工具介绍Nios II的开发包括了以32位Nios II软核处理器为核心的硬件配置、硬件设计、软件仿真、软件设计、软件调试等,基本的软件工具有:1.1Quartus II,用于完成Nios II系统的综合、硬件优化、适配、编程下载和硬件测试1.2SOPC Builder是Altera Nios II嵌入式处理器开发软件包,用于实现Nios II系统的配置、生成、Nios II系统相关的软件的生成1.3ModelSim用于对SOPC Builder生成的Nios II的HDL描述进行系统功能仿真1.4Matlab/DSP Builder,生成Nios II系统硬件加速器,并为定制新指令提供支持。

1.5Nios II IDE,软件开发调试环境。

我们主要使用上述工具1、2、5,对3、4工具的开发使用可以根据大家的具体需求另行探讨。

2Nios II应用系统开发设计流程介绍II开发分硬件开发和软件开发两个流程,硬件开发过程主要由用户定制系统硬件, Nios然后由SOPC Builder等工具完成系统硬件和对应的开发软件生成;软件设计和传统方式类似,接近于unix/linux系统开发,软件开发又可以细分为HAL驱动程序开发和应用系统开发。

在以后的实践中我们会体会到Nios II的开发是一个灵活的软硬件融合的开发过程。

3Nios II系统硬件设计实例导航我们以一个简单的基于Nios II的系统开发过程来介绍Nios II系统的开发过程,该系统具有四个按钮,8个LED输出,SDRAM,FLASH硬件,实现简单的流水灯。

Nios II 处理器

Altera®FPGA和HardCopy®SIC的3种可配置32位嵌入式

处理器系列

快速(/f内核):针对最佳性能进行了优化,提供可选存储器管理单元

(MMU),或者存储器保护单元(MPU)

经济(/e内核):针对最小容量进行了优化

标准(/s内核):性能和容量达到均衡

全部支持

256条定调试内核

C2H编译器,将ANSIC语言算法转换为硬件加速器

SOPCBuilder可用知识产权(IP)内核

丰富的嵌入式外设内核系列(定时器、UART、直接存储器访问

(DMA)、以太网,等)

全面的嵌入式开发套装(编译器、调试器、集成开发环境(IDE)、驱动

器、硬件抽象层(HAL))

NiosII处理器

NiosII系列软核处理器是Altera的第二代FPGA嵌入式处理

器,其性能超过200DMIPS,在AlteraFPGA中实现仅需35美分。Altera的

StraTIx、StraTIxGX、StraTIxII和Cyclone系列FPGA全面支持NiosII处

理器,以后推出的FPGA器件也将支持NiosII

低成本IP许可;免费评估

NIOSII教程

NIOSII教程NIOS II 是一种基于软核的处理器,可用于 FPGA 设计中。

它是由Altera 公司所开发的。

NIOS II 可以在 FPGA 中进行快速原型设计,并且具有高度可配置性和可扩展性。

本文将介绍 NIOS II 的基本架构和使用方法。

NIOSII架构基于RISC架构,它是一个32位的处理器,并且具有可选的指令扩展。

它的流水线深度可以根据设计的需求进行配置,以实现不同的性能要求。

NIOSII支持多种功能,包括硬件中断、异常处理以及浮点运算等。

在开始使用NIOSII进行开发之前,首先要进行软核处理器的配置。

配置包括选择所需的指令集、流水线深度和其他性能参数。

配置完成后,可以将软核处理器添加到FPGA设计中。

一旦软核处理器被添加到FPGA设计中,就可以开始编写应用程序。

NIOSII支持标准的C/C++语法,并且还提供了一些特殊的函数和指令,用于访问FPGA的硬件资源。

例如,可以使用特殊函数来配置GPIO引脚、读取和写入存储器以及执行其他与硬件交互的操作。

使用NIOSII进行FPGA开发具有许多优点。

首先,它提供了一种快速原型设计的方法,可以大大加快开发进程。

其次,NIOSII的可扩展性和高度可配置性使得它适用于各种不同的FPGA设计需求。

最后,NIOSII的开发工具和调试接口使得开发和调试过程更加简单和高效。

总结起来,NIOS II 是一种基于软核的处理器,适用于 FPGA 设计中。

它具有灵活性和可配置性,可以使用 C/C++ 或 HDL 进行开发,并通过Altera 公司提供的工具链进行编译和调试。

NIOS II 提供了一种快速原型设计的方法,并且适用于各种不同的 FPGA 设计需求。

Nios II嵌入式软处理器提升系统性能方式详解

Nios II嵌入式软处理器提升系统性能方式详解Altera的嵌入式软处理器系列使您能够充分利用FPGA内在的并行优势,实现高级系统性能。

多个处理器可以同时执行代码,而硬件加速器也能够同时卸载大计算量算法。

不需要重新设计电路板或者手动优化汇编程序,便能够在产品生命周期的任何阶段更新嵌入式系统的性能。

以下介绍更新系统性能的几种方式:软核处理器;定制指令;硬件加速器;可配置高速缓冲和紧耦合存储器;多处理器系统;宽带系统互联。

方式1:软核处理器如果您使用Altera的Nios® II 处理器,可以从三种代码兼容的软核处理器中进行选择(参见图1):一种针对最佳系统性能进行了优化;一种针对最少逻辑占用进行了优化;还有一种是二者之间达到平衡。

采用乘法器、用户设定的高速缓存、定制指令、硬件调试逻辑等特性来配置这些内核,能满足用户的特殊性能需求。

Nios II 处理器内核性能Altera嵌入式系列产品的其他软核处理器包括:MP32处理器:业界第一款100%兼容MIPS®的软核处理器。

ARM® Cortex-M1处理器:三级32位ARM Cortex处理器。

Freescale V1 ColdFire处理器:具有全综合内核以及长度可调RISC 16位、32位和48位指令。

Intel® Atom® E6x5C处理器:在多芯片封装中组合了Intel Atom处理器E6xx系列以及Altera® FPGA。

方式2:定制指令在Nios II 处理器指令集中加入定制指令来加速对时间要求较高的软件算法。

您可以在每一处理器内核中加入256条定制指令,从而减少了数值计算、位操作以及其他复杂处理算法所需的时钟周期数(如下图所示)。

定制指令支持Nios II设计人员将部分软件代码在硬件功能中实现,从而提升了系统性能。

但是,定制指令是在处理器边界内实现的,扩展了CPU指令集以加速对时间要求较高的软件。

NIOS2完整教程

NIOS2完整教程NIOSII是一种32位可配置的软核处理器,支持使用硬件描述语言(HDL)进行快速设计和开发。

下面是一个完整的NIOSII教程,介绍了NIOSII的基本概念和使用方法。

第一部分:NIOSII概述(300字)NIOS II是Altera公司推出的一种可配置软核处理器。

它可以根据需要进行配置,包括选择处理器指令集的大小和功能,以及设置外设和存储器的接口。

NIOS II是基于经典的RISC架构,具有高性能和灵活性。

第二部分:NIOSII的基本构成(300字)NIOSII处理器由五个核心组件组成:指令集体系结构(ISA)、处理器核心、数据存储器、指令存储器和外设接口。

ISA定义了NIOSII支持的指令集,包括整数指令、浮点指令和多媒体指令。

处理器核心执行指令,并且可以执行单周期、多周期或流水线处理。

数据存储器用于存储数据,指令存储器用于存储程序指令。

外设接口用于连接NIOSII处理器和外部设备。

第三部分:NIOSII的配置和开发环境(300字)第四部分:NIOSII的应用场景(300字)NIOSII可用于各种应用场景,包括但不限于嵌入式系统、通信系统、工业自动化和军事应用。

NIOSII的可配置性使得它非常适合于各种需求和资源约束的项目。

NIOSII的性能和可扩展性使得它能够满足高带宽和实时性要求的应用。

此外,NIOSII的软件开发环境也非常成熟和易于使用,可以加快开发过程。

第五部分:NIOSII的优势和挑战(300字)NIOSII相对于其他软核处理器的主要优势在于其可配置性和性能。

NIOSII可以根据需求进行定制,并且可以实现高度优化的硬件和嵌入式软件系统。

然而,NIOSII的可配置性也带来了一些挑战,例如设计复杂性和调试困难。

此外,NIOSII的性能也受限于硬件资源的可用性和设计的质量。

总结(200字)在本教程中,我们介绍了NIOSII的基本概念和使用方法。

NIOSII是一种可配置的软核处理器,支持使用HDL进行快速设计和开发。

nios_ii_入门手册

一、建立quartus ii工程首先,双击quartus ii9.1图标打开软件,界面如下图1.1所示图1.11.1新建工程(1)点击file–>New Project Wizard出现图1.2所示的对话框。

图1.2(2)点击Next。

如图1.3所示:第一行是工程的路径,二、三行为实体名。

填好后点击Next。

图1.3(3)此处可选择加入已设计好的文件到工程,点击Next。

图1.4(4)选择设计器件如图1.5所示。

接着点击Next。

图1.5(5)接着点击Next。

无需改动,点击finish,显示如下图所示。

图1.6(6)此时,工程已经建立完成,接下来需要建立一个原理图输入文件,点击file–>New->Block Diagram/Schematic File后如图1.7所示。

图1.7二、构建一个nios ii软核(1)首先点击Tools->Sopc Builder图2.1在System Name中输入软核的名称,注意:软核的名称不能和quartus工程的实体名相同,否则编译会出现错误,接着点击ok。

图2.2图中clk_0为时钟名称,100.0为时钟值双击可修改其值。

即软核的时钟就是100MHZ。

(2)建立nios ii处理器点击Processors->Nios ii Processor如图2.3所示图2.3点击后,将出现下图,在下图中选择软核的类型。

这里提供了三种类型,Nios II/e占用资源最少600-800LEs,功能也最简单,速度最慢。

Nios II/s占资源比,前者多一些,功能也多了,速度也忚一些Nios II/f占资源最多,功能也最多,速度就最快,用户可根据实际的需要选择不同的类型。

此处选择Nios II/f型,速度和功能都能满足。

下方Reset Vector是复位后启动的Memory类型和偏移量。

待SDRAM设置号以后再来设置此处。

图2.4点击Next,如下图所示,将Data Cache设置为None,即关闭Data Cache。

NIOSII教程

NIOSII教程1.NIOSII概述:介绍NIOSII的特点、应用领域和产品系列。

2.NIOSII架构和指令集:介绍NIOSII的架构和指令集。

NIOSII的架构包括处理器核、存储器和外设接口等。

处理器核由五个主要部分组成:指令译码器、执行单元、数据通路、存储器接口和外设接口。

NIOSII的指令集包括常见的RISC指令,如加载、存储、算术逻辑和分支等。

3.NIOSII的软件开发环境:介绍NIOSII的软件开发环境和相关工具。

4.NIOSII的软件编程:介绍NIOSII的软件编程方法和技术。

在NIOSII上进行软件编程可以使用C语言和汇编语言。

用户可以使用开发工具来编写、调试和运行自己的软件。

此外,NIOSII还支持外设驱动程序的编写和集成,以实现与外部设备的交互。

5.NIOSII硬件设计:介绍如何进行NIOSII的硬件设计和集成。

6.NIOSII的调试和性能优化:介绍如何进行NIOSII的调试和性能优化。

在NIOSII的开发过程中,调试和性能优化是非常重要的环节。

用户可以使用调试器来调试和分析程序的执行过程,以发现和修复错误。

此外,用户还可以通过改进代码结构和算法来提高程序的性能。

7.NIOSII的应用案例:介绍一些NIOSII在实际应用中的案例。

总结:NIOSII教程主要介绍了NIOSII的概述、架构、指令集、软件开发环境、软件编程、硬件设计、调试优化和应用案例等内容。

通过学习NIOSII教程,用户可以获得关于NIOSII的全面知识,并能够利用NIOSII 进行快速设计和开发嵌入式系统。

NOIS II简介

异常控制器:Nios II体系结构提供一个简单(jiǎndān)的非向量异常控

制器来处理运行时产生的所有类型的异常。一旦在程序运行过程中产

生了异常(包括硬件中断),CPU就会转到异常地址中运行异常处理

程序。异常处理程序判别异常产生的原因,并运行相应的服务子程序。

中断控制器:Nios II体系结构支持32个外部硬件中断,即

2.建立Quartus II工程,建立顶层实体;

3.调用SOPC Bulider生成用户定制的系统模块

(包括标准外设);

4.将SOPC系统模块集成到硬件工程中,并添加

其他模块;

5.在顶层实体中,将这些连接起来;

6.分配引脚和编译工程,生成硬件系统的配置

文件.sof和.pof文件;

第八页,共162页。

r17

子程序要保存的寄存器

r2习惯上,子程序必须保证

函数返回值(低32位)

r18

子程序要保存的寄存器

r3这些寄存器中的值在调用

函数返回值(高32位)

r19

子程序要保存的寄存器

r4

r20

子程序要保存的寄存器

r21

子程序要保存的寄存器

r22

子程序要保存的寄存器

r23

子程序要保存的寄存器

r1r16~r23:

at

前后保持不变,即要么在

传递给函数的参数

子程序执行时不使用它们

r5(tā men),要么使用前把

传递给函数的参数

r6它们(tā men)保存在堆栈

传递给函数的参数

r24或et:

中并在退出时恢复。

r7

传递给函数的参数

在异常处理时使用。使用时,

r25或bt:

NIOS II初级入门教程

NIOSII初级入门教程前言NIOSII教程可谓多入牛毛,尤其是在互联网高度发达的今天,大家可以baidu、google到不少的教程。

网上的许多达人也纷纷开设了自己的Blog来记录学习NIOSII的体会,以分享给大家。

虽然网上有很多教程了,但都没有详细到每一步的操作,这让不少入门者不知道该怎么操作,笔者就是属于这样的人。

以前在网上看了别人的教程,跟着做,却怎么也做不对,因为到了一些看似简单的步骤,都是跳过的。

笔者经过不断的摸索总结,终于还是打算自己编写一个初级的入门教程,方便那些刚接触NIOSII的人员学习。

由于笔者水平有限,教程中难免出现错误,请广大读者不吝指出。

笔者2009年12月13日第一章软件安装Altera公司的QuartusII目前已经推出了9.1版本,大家可以到Altera官方网站下载,也可以找国内的代理商邮寄光盘。

由于笔者手里只有QuartusII8.1版本,因此本教程中均以QuartusII8.1为准。

1.下载Altera官方网站上提供了QuartusIIweb版下载,其功能可能有限制,其实Altera还有FTP提供大家下载软件,只是这个地址没有明显的标注出来。

我把QuartusII8.1的FTP下载地址列出,方便大家下载。

QuartusII8.1:ftp:///outgoing/release/81_quartus_windows.exe DspBbuilde:ftp:///outgoing/release/81_dsp_builder.exeNIOSII:ftp:///outgoing/release/81_nios2eds_windows.exeModelsim:ftp:///outgoing/release/81_modelsim_ae_windows.exe2.QuartusII安装下载完成后解压缩,如图2.1所示。

开始安装,安装比较简单,就像其他windows程序一样,双击setup.exe图2.1和其他windows程序安装一样,只需要双击setup.exe就开始安装了,在弹出的界面中选择Next,进入下一步,如图2.2所示。

【翻译】NiosII处理器简介(NiosII)

【翻译】NiosII处理器简介(NiosII)处理器简介本⽂介绍的Altera Nios II处理器是⼀个可在Altera FPGA器件⾥实现的软核处理器。

主要讲述Nios II的基本架构和其指令集。

配合Quartus II 软件,使⽤Altera的SOPC Builder可以很容易的把Nios II处理器和它的内存及外围组件例化。

关于Nios II处理的完整描述请参阅《Nios II处理器参考⼿册》,在Altera官⽹的⽂献区可找到该⼿册。

SOPC Builder的简介在⼊门简介⾥有提供,也可在官⽹的⼤学计划板块找到。

本⽂包含的内容:⽬录Altera Nios II处理器是⼀个软核处理器,⽤硬件描述语⾔定义,使⽤Quartus II软件可在Altera的FPGA器件⾥实现。

本⽂为想要在Altera DE2开发板上实现⼀个基本Nios II系统的⽤户提供⼀个关于Nios II处理器的简介。

系统Nios II处理器可使⽤许多其他组件构成⼀个完整的系统。

这些组件包括许多标准外设之外,还可由⽤户⾃定义外设。

Altera DE2开发板含有⼏个可集成在Nios II系统⾥的组件。

图1就是⼀个这样的系统。

Nios II处理器和⽤来连接DE2上其他芯⽚的接⼝都在Cyclone II FPGA⾥实现。

这些组件通过Avalon 交换结构连接。

Cyclone II器件的内存块可为Nios II处理器提供⽚上内存。

它们可直接或通过Avalon⽹络与处理连接。

通过相应的接⼝访问DE2上的SRAM和SDRAM。

系统使⽤的I/O设备例化为I/O接⼝。

连接主机和DE2的USB线缆接⼝由⼀个特殊的JTAG UART接⼝提供。

这个接⼝电路和其相应的软件叫做USB_Blaster。

另⼀个名为JTAG Debug的模块,⽤来使主机控制Nios II处理器。

这样,就可以执⾏操作,⽐如,下载程序到内存⾥,启动和停⽌执⾏,设置程序断点,和搜集实时数据。

NIOS ii 配置及例程使用教程

NIOS ii 配置及例程使用教程本教程为nios ii在FPGA板上的配置入门教程,仅使用在xsyan设计制作EP2C5/EP2C8开发板上。

下面将会详细的说明如何使用nios ii在FPGA上配置一个altera公司提供的CPU,并利用这个CPU来调试和执行相应C程序。

并且,最后会有两个例程。

一,硬件要求:1,EP2C5/EP2C8开发板一块。

2,USB电源线一条。

3,并口线一条。

4,串口线一条。

二,软件要求:1,quartus II 7.0.2,MegaCore IP 7.0.3,Nios II EDS 7.0.三,主要步骤:1,在quartus上创建一个工程。

2,在此工程里面调用SOPC,并配置CPU。

3,创建cpu.4,定义FPGA引脚并综合。

5,调用NIOS,配置相应设置。

6,再次编译综合工程。

7,下载FPGA。

四,详细步骤:1,在quartus上创建一个工程。

a)打开quartus,选择File->New project wizard.b)在打开的窗口上选择Nextc)选择工程路径,并且指定工程名字。

d)添加文件,因为没有设计文档,所以跳过,直接Next。

e)选择器件,请根据自己的开发板选择EP2C5T144C8/ EP2C8T144C8f)然后直接点Finish,创建工程完毕。

2,用SOPC配置一个CPU。

a)在quartus里面调用SOPC。

b)在打开的SOPC里面,输入系统名字,选择HDL语言种类c)点确定后开始配置CPU,双击左边栏的Nios ii Processor.d)这里选择经济型,然后点Next,直到下个页面。

e)然后点finish,Process配置结束,双击UART,配置串口f)直接用默认配置,点Finish即可,然后双击on-chip-memory配置memory。

g)配置如上图配一个8K内部ram后点Finish,用来存放程序代码和初始化代码,然后继续创建memory用来存放变量,再创建两个4K内部ram,步骤同上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

NiosII软处理器快速入门- 10分钟学会NiosIINios简单介绍:Nios II是一个用户可配置的通用RISC嵌入式处理器。

在这儿,我引用了Altera公司关于NiosII的官方介绍:Altera推出的Nios? II系列嵌入式处理器扩展了目前世界上最流行的软核嵌入式处理器的性能,把Nios II嵌入到Altera的所有FPGA中,例如StratixII、Stratix、CycloneII,Cyclone、APEX,ACEX和HardCopy系列器件中,用户可以获得超过200 DMIPS的性能,用户可以从三种处理器以及超过60个的IP 核中选择所需要的,Nios II系统为用户提供了最基本的多功能性,设计师可以以此来创建一个最适合他们需求的嵌入式系统。

Nios II处理器的优点和特性使用Nios II处理器的用户可以根据他们的需要来调整嵌入式系统的特性、性能以及成本,快速使得产品推向市场,扩展产品的生命周期,并且避免处理器的更新换代。

提高系统性能* 一系列的处理器核可供选择,其中包括了超过200 DMIPS性能的核* 实现任何数量的处理器或将不同的处理器核组和在一起* 增加了已有的处理器,在FPGA中添加一个或更多的Nios II软核处理器更低的系统成本* 通过将处理器、外设、存储器和I/O接口集成到一个单一的FPGA中,从而降低了系统成本、复杂性和功耗* 通过将Nios II处理器嵌入到低成本的FPGA中只需花费35美分或者更低(编者:对大多数用户而言,NiosII所占逻辑资源的成本大约是10-20元人民币,具体取决于所选FPGA的类型和NiosII的配置)应对产品的生命周期* 提供易用的设计工具从而快速将产品推向市场。

* 提供永久的,免费的许可从而使基于Nios II处理器的产品避免了处理器的更新换代而带来的损失。

功能强大、易用的开发工具* 通过使用Nios II集成开发环境(IDE),从而加速了软件的开发* 利用Altera的强大的SOPC Builder系统开发工具和Quartus II设计软件可以在几分钟内设计一个系统使用完全功能的开发包* 使用易用的Nios II 开发包开始一个设计* 使用易用的Nios II开发包开始设计* 可以选择具有低成本特性的Cyclone FPGA开发套件,或高性能的Stratix FPGA开发套件稍微了解一下NiosII后,我们就来开始设计、应用它吧!下面我们就设计一个最简单的NiosII系统,使用NiosII去控制一个LED灯,通过这个例子我们可以了解整个介绍NiosII的设计流程第一节:EDA软件的安装。

许多朋友在配置EDA环境的时候,就遇到了更多问题,我现在总结一下:1。

安装QuartusII4.22。

安装NiosII IDE 用于软件开发3。

安装ModelSim6.0。

用于系统仿真如下是ModelSim下的安装说明:1.Install, Select Full product instllation. When asked for security key, select no. When you see License Wizard dialog, select close because license wizard dont know our license's format.e our keygen to generate license.dat, copy it to c:\flexlm directory.3.set enviroment string: LM_LICENSE_FILE = c:\flexlm\license.dat4.Start Modelsim and have fun.仍有许多人表示搞不定,通常是因为第三步有问题,可以如下设置:在W2K下,在开始 -〉系统 -〉设置 -〉 系统 -〉 高级 -〉 环境变量 -〉系统变量中设置变量名为 LM_LICENSE_FILE ,值为 你的存放license.dat的路径 + 文件名,比如c:\flexlm\license.dat,(在unix/linux下,在.bashrc中exportLM_LICENSE_FILE=/thePathOfLicenseFile/yourLicenseFileName就可以了!)第二节:建立niosII系统。

1:建立项目。

建立一个目录,比如H:\DB2005\project\niosDK\Example\NiosSmall启动QuartusII4.2软件。

选择File -> New Project Wizard在Diectory,Name,Top-Level Entity中如下填写,在你自己的项目中,你可以类比着填写:在Add Files中如下填写,在你自己的项目中,你可以类比着填写:在EDA Tools Setting中如下填写,在你自己的项目中,你可以类比着填写:最后,选择Finish,就OK了!在H:\DB2005\project\niosDK\Example\NiosSmall下建立一个name为Setup.tcl的file,其内容如下:#Setup.tcl# Setup pin settingset_global_assignment -name RESERVE_ALL_UNUSED_PINS "AS OUTPUT DRIVING GROUND"set_global_assignment -name ENABLE_INIT_DONE_OUTPUT OFFset_location_assignment PIN_16 -to clkset_location_assignment PIN_37 -to led\[0\]set_location_assignment PIN_39 -to led\[1\]set_location_assignment PIN_1 -to led\[2\]set_location_assignment PIN_41 -to led\[3\]set_location_assignment PIN_42 -to led\[4\]set_location_assignment PIN_49 -to led\[5\]set_location_assignment PIN_50 -to led\[6\]set_location_assignment PIN_51 -to led\[7\]很浅显的Script,你可以根据需要修改。

然后打开Tools -> Tcl Scripts,选中刚才编辑的Script文件:Setup,并点击Run2:生成一个可调试的nios 最小系统选择 Tools -> SopcBuilder,启动Altera SOPC Builder启动Altera SOPC Builder后,SOPC Builder会立刻弹出对话框填入System Name,比如niosII_e;HDL Language ,比如选择verilog,如下图:选择Board Target ,比如,我选择Unspecified Board;选择Target Device Family,比如,我选择Cyclone;填入Clock,比如,我 填入22.1184如下图:添加Nios II到项目中:双击 Nios II Processor -Altera Corporation,会弹出Altera niosII 对话框,在NiosII core配置选项中,点击Nios II/e区域,选择Nios II/e,如下图。

然后Next,进入下一步。

在JTAG Debug Module配置选项中,选择Level 1,如下图。

然后Next,进入下一步。

在Custom Instructions配置选项中,我由于无需增加任何定制指令,所以为空,如下图:最后选择Finish,你的项目中会增加一个niosII 处理器,名字为cpu_0,为了简便起见,我没有将它改名。

你可以依照你自己的喜好,为该处理器取个名字。

如下图:然后双击On-Chip Memory(RAM or ROM),(在Avalon Modules -> Memory -> 下),为系统添加RAM.Memory Type选择RAM;Data Width选择32bits,Total Memory Size 可以选择2K bytes,然后选择Finish确认。

如下图,系统中会添加name 为onchip_memory_0的ram,为了简便起见,我没有将它改名。

你可以依照你自己的喜好,为其取个名字。

之后,双击PIO(在Parallel I/O)(在Avalon Modules -> Other 下),为系统添加输出接口。

Width 选择8 bits,然后点击 Finish如下图如下图,系统中会添加name 为pio_0的PIO,为了简便起见,我没有将它改名。

你可以依照你自己的喜好,为其取个名字。

然后,选择System ->Auto-Assign Base Addresses,让系统自动分配基地址。

如下图:然后,选择Sysetm->Auto-Assign IRQs,让系统自动分配中断。

如下图:点击Nios II More "cpu_0" settings选项卡,进行处理器设定。

在该例中,无需做任何更改;Reset Address、Exceptiong Address、Break Location 默认值如下图所示。

点击System Generation选项卡,进行最后的设定并生成系统。

选中HDL.Generate system module logic in Verilog,如果需要仿真,也请选中Simulation.Create ModelSim(tm) project files然后点击Generate,进行系统生成的任务。

如下图:然后,就是漫长的等待,你可以悠闲得喝一杯咖啡(因为等待的时间还是蛮长的,比如我,要等近10分钟)。

一般没有问题的话,可以看到系统提示:SUCCESS: SYSTEM GENERATION COMPLETED.如果看到此信息,恭喜恭喜,系统被正确生成了。

如果失败,请返回并检查、修改!如下图:3:在QuartusII中使用上述niosII系统在 SOPC Builder正确运行完毕后,可以在QuartusII中,打开SOPC Builder生成的niosII_e.bsf,检查一下引脚,看看跟你的设想是否有误,如下图,niosII_e有两个input:clk,reset_n,一组output:out_port_from_the_piop[7:0]如下图:你可以使用上述的niosII_e,来构造你自己的系统。