74ACTQ16373MTD中文资料

74LVT16373MTD资料

© 2005 Fairchild Semiconductor Corporation DS012021January 1999Revised June 200574LVT16373 • 74LVTH16373 Low Voltage 16-Bit Transparent Latch with 3-STATE Outputs74LVT16373 • 74LVTH16373Low Voltage 16-Bit Transparent Latch with 3-STATE OutputsGeneral DescriptionThe LVT16373 and LVTH16373 contain sixteen non-invert-ing latches with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state.The LVTH16373 data inputs include bushold, eliminating the need for external pull-up resistors to hold unused inputs.These latches are designed for low-voltage (3.3V) V CC applications, but with the capability to provide a TTL inter-face to a 5V environment. The LVT16373 and LVTH16373are fabricated with an advanced BiCMOS technology to achieve high speed operation similar to 5V ABT while maintaining a low power dissipation.Featuress Input and output interface capability to systems at 5V V CC s Bushold data inputs eliminate the need for external pull-up resistors to hold unused inputs (74LVTH16373),also available without bushold feature (74LVT16373)s Live insertion/extraction permitteds Power Up/Power Down high impedance provides glitch-free bus loading s Outputs source/sink 32 mA/ 64 mAs Functionally compatible with the 74 series 16373s Latch-up performance exceeds 500 mA s ESD performance:Human-body model ! 2000V Machine model ! 200V Charged-device model ! 1000Vs Also packaged in plastic Fine-Pitch Ball Grid Array (FBGA) (Preliminary)Ordering Code:Note 1: BGA package available in Tape and Reel only.Note 2: Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic SymbolOrder Number Package Number Package Description74LVT16373GX (Note 1)BGA54A (Preliminary)54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL]74LVT16373MEA (Note 2)MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide 74LVT16373MTD (Note 2)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 74LVTH16373GX (Note 1)BGA54A (Preliminary)54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide [TAPE and REEL]74LVTH16373MEA (Note 2)MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide 74LVTH16373MTD (Note 2)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 274L V T 16373 • 74L V T H 16373Connection DiagramsPin Assignment for SSOP and TSSOPPin Assignment for FBGA(Top Thru View)Pin DescriptionsFBGA Pin Assignments Truth TablesH HIGH Voltage LevelL LOW Voltage Level X ImmaterialZ HIGH ImpedanceO o Previous output prior to HIGH-to-LOW transition of LEPin Names DescriptionOE nOutput Enable Input (Active LOW)LE nLatch Enable Input I 0–I 15 Inputs O 0–O 15 3-STATE Outputs NC No Connect123456A O 0NC OE 1LE 1NC I 0BO 2O 1NCNC I 1I 2C O 4O 3V CC V CC I 3I 4D O 6O 5GND GND I 5I 6E O 8O 7GND GND I 7I 8F O 10O 9GND GND I 9I 10G O 12O 11V CC V CC I 11I 12H O 14O 13NC NC I 13I 14JO 15NCOE 2LE 2NCI 15InputsOutputs LE 1OE 1 I 0–I 7 O 0–O 7X H X ZH LL L H L H H LL XO o InputsOutputs LE 2OE 2 I 8–I 15 O 8–O 15X H XZ H L L L HL H H LLXO o74LVT16373 • 74LVTH16373Functional DescriptionThe LVT16373 and LVTH16373 contain sixteen D-typelatches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but inde-pendent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LE n ) input is HIGH, data on the D n enters the latches. In this condition the latches are transparent, i.e, a latch output will change states each time its D input changes. When LE n is LOW,the latches store information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LE n . The 3-STATE standard outputs are controlled by the Output Enable (OE n ) input. When OE n is LOW, the standard outputs are in the 2-state mode. When OE n is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.Logic DiagramsPlease note that these diagrams are provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474L V T 16373 • 74L V T H 16373Absolute Maximum Ratings (Note 3)Recommended Operating ConditionsNote 3: Absolute Maximum continuous ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions beyond those indicated may adversely affect device reliability. Functional operation under absolute maximum rated conditions is not implied.Note 4: I O Absolute Maximum Rating must be observed.DC Electrical CharacteristicsSymbol ParameterValueConditionsUnits V CC Supply Voltage 0.5 to 4.6V V I DC Input Voltage 0.5 to 7.0VV O DC Output Voltage 0.5 to 7.0Output in 3-STATEV 0.5 to 7.0Output in HIGH or LOW State (Note 4)I IK DC Input Diode Current 50V I GND mA I OK DC Output Diode Current 50V O GND mA I O DC Output Current64V O ! V CC Output at HIGH State mA 128V O ! V CCOutput at LOW StateI CC DC Supply Current per Supply Pin r 64mA I GND DC Ground Current per Ground Pin r 128mAT STGStorage Temperature65 to 150q CSymbol ParameterMin Max Units V CC Supply Voltage 2.7 3.6V V I Input Voltage5.5V I OH HIGH Level Output Current 32mA I OL LOW Level Output Current 64mAT AFree-Air Operating Temperature4085q C 't/'VInput Edge Rate, V IN 0.8V –2.0V, V CC 3.0V10ns/VSymbol ParameterV CC T A 40q C to 85q C Units Conditions(V)MinMax V IK Input Clamp Diode Voltage 2.7 1.2V I I 18 mA V IH Input HIGH Voltage 2.7–3.6 2.0V V O d 0.1V or V IL Input LOW Voltage 2.7–3.60.8VV O t V CC 0.1V V OHOutput HIGH Voltage2.7–3.6V CC 0.2VI OH 100 P A 2.7 2.4I OH 8 mA 3.02.0I OH 32 mA V OLOutput LOW Voltage2.70.2V I OL 100 P A 2.70.5I OL 24 mA3.00.4I OL 16 mA 3.00.5I OL 32 mA 3.00.55I OL 64 mA I I(HOLD)Bushold Input Minimum Drive3.075P A V I 0.8V (Note 5) 75V I 2.0V I I(OD)Bushold Input Over-Drive 3.0500P A (Note 6)(Note 5)Current to Change State 500(Note 7)I IInput Current3.610P AV I 5.5V Control Pins 3.6r 1V I 0V or V CC Data Pins3.6 5V I 0V 1V I V CCI OFF Power Off Leakage Current 0r 100P A 0V d V I or V O d 5.5V I PU/PD Power Up/Down 3-STATE 0–1.5V r 100P A V O 0.5V to 3.0V Output CurrentV I GND or V CC I OZL 3-STATE Output Leakage Current 3.6 5P A V O 0.5V I OZH 3-STATE Output Leakage Current 3.65P A V O 3.0V I OZH3-STATE Output Leakage Current 3.610P A V CC V O d 5.5V74LVT16373 • 74LVTH16373DC Electrical Characteristics (Continued)Note 5: Applies to bushold versions only (74LVTH16373).Note 6: An external driver must source at least the specified current to switch from LOW-to-HIGH.Note 7: An external driver must sink at least the specified current to switch from HIGH-to-LOW.Note 8: This is the increase in supply current for each input that is at the specified voltage level rather than V CC or GND.Dynamic Switching Characteristics (Note 9)Note 9: Characterized in SSOP package. Guaranteed parameter, but not tested.Note 10: Max number of outputs defined as (n). n 1 data inputs are driven 0V to 3V. Output under test held LOW.AC Electrical CharacteristicsNote 11: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ).Capacitance (Note 12)Note 12: Capacitance is measured at frequency f 1 MHz, per MIL-STD-883, Method 3012.Symbol ParameterV CC T A 40q C to 85q C Units Conditions(V)MinMax I CCH Power Supply Current 3.60.19mA Outputs HIGH I CCL Power Supply Current 3.65mA Outputs LOW I CCZ Power Supply Current 3.60.19mA Outputs Disabled I CCZ Power Supply Current3.60.19mA V CC d V O d 5.5V,Outputs Disabled 'I CCIncrease in Power Supply Current 3.60.2mAOne Input at V CC 0.6V (Note 8)Other Inputs at V CC or GNDSymbol ParameterV CC T A 25q C Units Conditions (V)MinTyp MaxC L 50 pF, R L 500:V OLP Quiet Output Maximum Dynamic V OL 3.30.8V (Note 10)V OLVQuiet Output Minimum Dynamic V OL3.30.8V(Note 10)Symbol ParameterT A 40q C to 85q C, C L 50pF, R L 500:UnitsV CC 3.3V r 0.3V V CC 2.7VMin Max Min Max t PHL Propagation Delay 1.5 3.9 1.5 4.3ns t PLH D n to O n1.5 3.8 1.5 4.2t PHL Propagation Delay 1.9 4.2 1.9 4.4ns t PLH LE to O n1.6 4.3 1.6 4.8t PZL Output Enable Time1.3 4.3 1.3 4.9ns t PZH 1.0 4.3 1.0 5.1t PLZ Output Disable Time1.5 4.7 1.5 4.8ns t PHZ2.0 5.02.0 5.4t S Setup Time, D n to LE 1.00.8ns t H Hold Time, D n to LE 1.0 1.1ns t W LE Pulse Width3.03.0ns t OSHL Output to Output Skew (Note 11) 1.0 1.0ns t OSLH1.0 1.0Symbol ParameterConditionsTypical Units C IN Input Capacitance V CC Open, V I 0V or V CC 4pF C OUTOutput CapacitanceV CC 3.0V, V O 0V or V CC8pF 674L V T 16373 • 74L V T H 16373Physical Dimensionsinches (millimeters) unless otherwise noted54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm WidePackage Number BGA54APreliminary74LVT16373 • 74LVTH16373Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" WidePackage Number MS48A874L V T 16373 • 74L V T H 16373 L o w V o l t a g e 16-B i t T r a n s p a r e n t L a t c h w i t h 3-S T A T E O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm WidePackage Number MTD48Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

74ACTQ00MTC中文资料

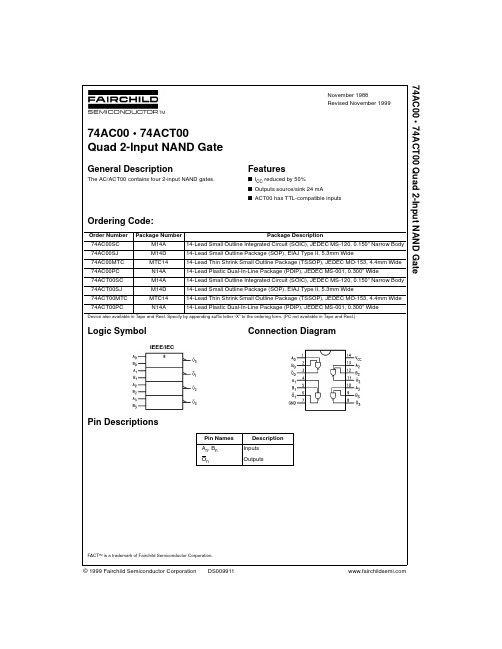

© 2005 Fairchild Semiconductor Corporation DS010888August 1990Revised February 200574ACTQ00 Quiet Series ¥ Quad 2-Input NAND Gate74ACTQ00Quiet Series ¥ Quad 2-Input NAND GateGeneral DescriptionThe ACTQ00 contains four 2-input NAND gates and uti-lizes Fairchild FACT Quiet Series ¥ technology to guaran-tee quiet output switching and improve dynamic threshold performance FACT Quiet Series features GTO ¥ output control and undershoot corrector in addition to a split ground bus for superior ACMOS performance.Featuress I CC reduced by 50%s Guaranteed simultaneous switching noise level and dynamic threshold performance s Improved latch-up immunity s Outputs source/sink 24 mA s Has TTL-compatible inputsOrdering Code:Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic SymbolIEEE/IECConnection DiagramPin DescriptionsFACT ¥, Quiet Series ¥, FACT Quiet Series ¥, and GTO ¥ are trademarks of Fairchild Semiconductor Corporation.Order Number Package NumberPackage Description74ACTQ00SC M14A 14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow 74ACTQ00MTC MTC1414-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm Wide 74ACTQ00PCN14A14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePin Names Description A n , B n Inputs O nOutputs 274A C T Q 00Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, with-out exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation outside databook specifications.DC Electrical CharacteristicsNote 2: All outputs loaded; thresholds on input associated with output under test.Note 3: Maximum test duration 2.0 ms, one output loaded at a time.Note 4: DIP package.Note 5: Max number of outputs defined as (n). Data inputs are 0V to 3V. One output @ GND.Note 6: Max number of data inputs (n) switching. (n 1) inputs switching 0V to 3V. Input-under-test switching: 3V to threshold (V ILD ),0V to threshold (V IHD ), f 1 MHz.Supply Voltage (V CC ) 0.5V to 7.0VDC Input Diode Current (I IK )V I 0.5V 20 mA V I V CC 0.5V 20 mADC Input Voltage (V I )0.5V to V CC 0.5VDC Output Diode Current (I OK )V O 0.5V 20 mA V O V CC 0.5V 20 mADC Output Voltage (V O ) 0.5V to V CC 0.5VDC Output Source or Sink Current (I O )r 50 mA DC V CC or Ground Current per Output Pin (I CC or I GND )r 50 mAStorage Temperature (T STG ) 65q C to 150q CDC Latch-up Sourceor Sink Current r 300 mA Junction Temperature (T J )PDIP140q CSupply Voltage (V CC ) 4.5V to 5.5V Input Voltage (V I )0V to V CC Output Voltage (V O )0V to V CCOperating Temperature (T A ) 40q C to 85q CMinimum Input Edge Rate ('V/'t)V IN from 0.8V to 2.0V 125 mV/nsV CC @ 4.5V, 5.5VSymbol ParameterV CC T A 25q C T A 40q C to 85q C Units Conditions (V)Typ Guaranteed LimitsV IH Minimum HIGH Level 4.5 1.5 2.0 2.0V V OUT 0.1V Input Voltage 5.5 1.5 2.0 2.0or V CC 0.1V V IL Maximum LOW Level 4.5 1.50.80.8V V OUT 0.1V Input Voltage 5.5 1.50.80.8or V CC 0.1V V OHMinimum HIGH Level 4.5 4.49 4.4 4.4VI OUT 50 P A Output Voltage5.5 5.495.4 5.4V IN V IL or V IH4.5 3.86 3.76VI OH 24 mA 5.54.864.76I OH 24 mA (Note 2)V OLMaximum LOW Level 4.50.0010.10.1VI OUT 50 P A Output Voltage5.50.0010.10.1V IN V IL or V IH4.50.360.44V I OL 24 mA5.50.360.44I OL 24 mA (Note 2)I IN Maximum Input Leakage Current 5.5r 0.1r 1.0P A V I V CC , GND I CCT Maximum I CC /Input 5.50.61.5mA V I V CC2.1V I OLD Minimum Dynamic 5.575mA V OLD 1.65V Max I OHD Output Current (Note 3)5.5 75mA V OHD 3.85V Min I CC Maximum Quiescent Supply Current 5.5 2.020.0P A V IN V CC or GND V OLP Quiet Output Maximum Dynamic 5.01.11.5VFigure 1, Figure 2V OL(Note 4)(Note 5)V OLV Quiet Output Minimum Dynamic 5.0 0.6 1.2V Figure 1, Figure 2V OL(Note 4)(Note 5)V IHD Minimum HIGH Level 5.0 1.9 2.2V (Note 4)(Note 6)Dynamic Input Voltage V ILDMaximum LOW Level 5.01.20.8V(Note 4)(Note 6)Dynamic Input Voltage74ACTQ00AC Electrical CharacteristicsNote 7: Voltage Range 5.0 is 5.0V r 0.5V.Note 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ). Parameter guaranteed by design.CapacitanceV CCT A 25q C T A 40q C to 85q CSymbol Parameter(V)C L 50 pFC L 50 pF Units(Note 7)Min TypMax Min Max t PLH Propagation Delay 5.0 2.07.5 2.08.0ns Data to Output t PHL Propagation Delay 5.0 2.07.5 2.08.0ns Data to Output t OSHL Output to Output 5.00.5 1.01.0ns t OSLHSkew (Note 8)Symbol ParameterTyp Units ConditionsC IN Input Capacitance4.5pF V CC OPEN C PDPower Dissipation Capacitance74pFV CC 5.0V 474A C T Q 00FACT ¥Noise CharacteristicsThe setup of a noise characteristics measurement is critical to the accuracy and repeatability of the tests. The following is a brief description of the setup used to measure the noise characteristics of FACT.Equipment:Hewlett Packard Model 8180A Word Generator PC-163A Test FixtureTektronics Model 7854 OscilloscopeProcedure:1.Verify Test Fixture Loading: Standard Load 50 pF,500:.2.Deskew the HFS generator so that no two channelshave greater than 150 ps skew between them. This requires that the oscilloscope be deskewed first. It is important to deskew the word generator channels before testing. This will ensure that the outputs switch simultaneously.3.Terminate all inputs and outputs to ensure proper load-ing of the outputs and that the input levels are at the correct voltage.4.Set the HFS generator to toggle all but one output at afrequency of 1 MHz. Greater frequencies will increase DUT heating and effect the results of the measure-ment.5.Set the HFS generator input levels at 0V LOW and 3VHIGH for ACT devices and 0V LOW and 5V HIGH for AC devices. Verify levels with an oscilloscopeNote 9: V OHV and V OLP are measured with respect to ground reference.Note 10: Input pulses have the following characteristics: f 1 MHz, t r 3ns,t f 3 ns, skew 150 ps.FIGURE 1. Quiet Output Noise Voltage WaveformsV OLP /V OLV and V OHP /V OHV :•Determine the quiet output pin that demonstrates the greatest noise levels. The worst case pin will usually be the furthest from the ground pin. Monitor the output volt-ages using a 50: coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.•Measure V OLP and V OLV on the quiet output during the worst case transition for active and enable. Measure V OHP and V OHV on the quiet output during the worst case active and enable transition.•Verify that the GND reference recorded on the oscillo-scope has not drifted to ensure the accuracy and repeat-ability of the measurements.V ILD and V IHD :•Monitor one of the switching outputs using a 50: coaxial cable plugged into a standard SMB type connector on the test fixture. Do not use an active FET probe.•First increase the input LOW voltage level, V IL , until the output begins to oscillate or steps out a min of 2 ns.Oscillation is defined as noise on the output LOW level that exceeds V IL limits, or on output HIGH levels that exceed V IH limits. The input LOW voltage level at which oscillation occurs is defined as V ILD .•Next decrease the input HIGH voltage level.V IH until the output begins to oscillate or steps out a mine of 2 ns.Oscillation is defined as noise on the output LOW level that exceeds V IL limits, or on output HIGH levels that exceed V IH limits. The input HIGH voltage level at which oscillation occurs is defined as V IHD .•Verify that the GND reference recorded on the oscillo-scope has not drifted to ensure the accuracy and repeat-ability of the measurements.FIGURE 2. Simultaneous Switching Test Circuit 74ACTQ00Physical Dimensions inches (millimeters) unless otherwise noted14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage Number M14A 674A C T Q 00Physical Dimensionsinches (millimeters) unless otherwise noted (Continued)14-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 4.4mm WidePackage Number MTC14774ACTQ00 Quiet Series ¥ Quad 2-Input NAND GatePhysical Dimensions inches (millimeters) unless otherwise noted (Continued)14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N14AFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

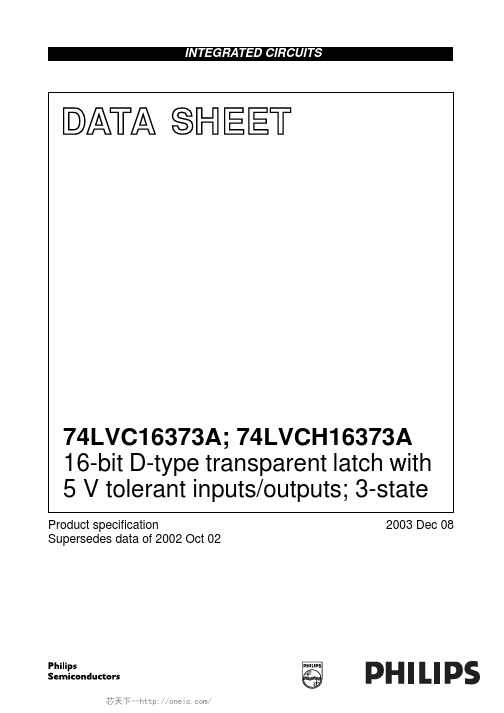

74ACT00MTC中文资料

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering form. (PC not available in Tape and Reel.)

74ACT323PCX中文资料

June 1988Revised October 199874ACT323 8-Bit Universal Shift/Storage Register with Synchronous Reset and Common I/O Pins © 1999 Fairchild Semiconductor Corporation DS009787.prf 74ACT3238-Bit Universal Shift/Storage Register withSynchronous Reset and Common I/O PinsGeneral DescriptionThe ACT323 is an 8-bit universal shift/storage register with3-STATE outputs. Parallel load inputs and flip-flop outputsare multiplexed to minimize pin count. Separate serialinputs and outputs are provided for Q0 and Q7 to alloweasy cascading. Four operation modes are possible: hold(store), shift left, shift right and parallel load.Featuress I CC and I OZ reduced by 50%s Common parallel I/O for reduced pin counts Additional serial inputs and outputs for expansions Four operating modes: shift left, shift right, load andstores3-STATE outputs for bus-oriented applicationss Outputs source/sink 24 mAs TTL-compatible inputsOrdering Code:Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.Logic Symbols Connection DiagramPin Assignmentfor DIPPin DescriptionsFACT™ is a trademark of Fairchild Semiconductor Corporation.Order Number Package Number Package Description74ACT323PC N20A20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePin Name DescriptionCP Clock Pulse InputDS0Serial Data Input for Right ShiftDS7Serial Data Input for Left ShiftS0, S1Mode Select InputsSR Synchronous Reset InputOE1, OE23-STATE Output Enable InputsI/O0–I/O7Multiplexed Parallel Data Inputs or3-ST ATE Parallel Data OutputsQ0, Q7Serial Outputs 274A C T 323Functional DescriptionThe ACT323 contains eight edge-triggered D-type flip-flops and the interstage logic necessary to perform synchronous reset, shift left, shift right, parallel load and hold operations.The type of operation is determined by S 0 and S 1 as shown in the Mode Select Table. All flip-flop outputs are brought out through 3-STATE buffers to separate I/O pins that also serve as data inputs in the parallel load mode. Q 0 and Q 7are also brought out on other pins for expansion in serial shifting of longer words.A LOW signal on SR overrides the Select inputs and allows the flip-flops to be reset by the next rising edge of CP . Allother state changes are also initiated by the LOW-to-HIGH CP transition. Inputs can change when the clock is in either state provided only that the recommended setup and hold times, relative to the rising edge of CP , are observed.A HIGH signal on either OE 1 or OE 2 disables the 3-ST ATE buffers and puts the I/O pins in the high impedance state.In this condition the shift, load, hold and reset operations can still occur. The 3-STA TE buffers are also disabled by HIGH signals on both S 0 and S 1 in preparation for a paral-lel load operation.Mode Select TableH = HIGH Voltage Level L = LOW Voltage Level X = Immaterial= LOW-to-HIGH Clock T ransitionInputsResponseSR S 1S 0CP L X X Synchronous Reset; Q 0–Q 7 = LOW H H HParallel Load; I/O n →Q nH LHShift Right; DS 0→Q 0, Q 0→Q 1, etc.H H L Shift Left; DS 7→Q 7, Q 7→Q 6, etc. HLLXHold 74ACT323Logic DiagramPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474A C T 323Absolute Maximum Ratings (Note 1)Recommended Operating ConditionsNote 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, with-out exception, to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT ™ circuits outside databook specifications.DC Electrical CharacteristicsNote 2: All outputs loaded; thresholds on input associated with output under test.Note 3: Maximum test duration 2.0 ms, one output loaded at a time.Supply Voltage (V CC )−0.5V to +7.0VDC Input Diode Current (I IK )V I = −0.5V −20 mA V I = V CC + 0.5V +20 mADC Input Voltage (V I )−0.5V to V CC + 0.5VDC Output Diode Current (I OK ) V O = −0.5V −20 mA V O = V CC + 0.5V +20 mADC Output Voltage (V O )−0.5V to V CC + 0.5VDC Output Source or Sink Current (I O ) ±50 mA DC V CC or Ground Current Per Output Pin (I CC or I GND )±50 mAStorage Temperature (T STG )−65°C to +150°CJunction Temperature (T J )PDIP140°CSupply Voltage (V CC ) 4.5V to 5.5V Input Voltage (V I )0V to V CC Output Voltage (V O )0V to V CCOperating Temperature (T A )−40°C to +85°CMinimum Input Edge Rate (∆V/∆t)V IN from 0.8V to 2.0V V CC @ 4.5V , 5.5V125 mV/nsSymbol ParameterV CC T A = +25°C T A = −40°C to +85°C Units Conditions (V)Typ Guaranteed LimitsV IH Minimum High Level 4.5 1.5 2.0 2.0V V OUT = 0.1V Input Voltage 5.5 1.5 2.0 2.0or V CC − 0.1V V IL Maximum Low Level 4.5 1.50.80.8V V OUT = 0.1V Input Voltage 5.5 1.50.80.8or V CC − 0.1V V OHMinimum High Level 4.5 4.49 4.4 4.4VI OUT = −50 µA Output Voltage5.5 5.495.4 5.4V IN = V IL or V IH4.5 3.86 3.76V I OH = −24 mA5.54.864.76I OH = −24 mA (Note 2)V OLMaximum Low Level 4.50.0010.10.1VI OUT = 50 µA Output Voltage5.50.0010.10.1V IN = V IL or V IH4.50.360.44V I OL = −24 mA5.50.360.44I OL = −24 mA (Note 2)I IN Maximum Input 5.5±0.1±1.0µA V I = V CC , GND Leakage Current I OZT Maximum I/O 5.5±0.3±3.0µA V I/O = V CC or GND Leakage Current V IN = V IH , V IL I CCT Maximum I CC /Input 5.5 0.61.5mA V I = V CC −2.1V I OLD Minimum Dynamic 5.575mA V OLD = 1.65V Max I OHD Output Current (Note 3) 5.5 −75mA V OHD = 3.85V Min I CCMaximum Quiescent 5.54.040.0µAV IN = V CC or GNDSupply Current74ACT323AC Electrical CharacteristicsNote 4: Voltage Range 5.0 is 5.0V ±0.5VAC Operating RequirementsNote 5: Voltage Range 5.0 is 5.0V ±0.5VCapacitanceV CCT A = 25°C T A = −40°C to +85°CSymbol Parameter(V)C L = 50 pFC L = 50 pF Units(Note 4)Min Typ MaxMin Maxf max Maximum Input Frequency 5.0120125 110MHz t PLH Propagation Delay 5.05.09.012.5 4.014.0ns CP to Q 0 or Q 7t PHL Propagation Delay 5.05.09.013.54.515.0nsCP to Q 0 or Q 7t PLH Propagation Delay 5.05.08.512.54.514.5nsCP to I/O nt PHL Propagation Delay 5.06.010.014.55.016.0nsCP to I/O nt PZH Output Enable Time 5.0 3.57.511.0 3.012.5ns t PZL Output Enable Time 5.0 3.57.511.5 3.013.0ns t PHZ Output Disable Time 5.0 4.08.512.5 3.013.5ns t PLZOutput Disable Time5.03.08.011.52.512.5nsT A = 25°CT A = −40°C to +85°CSymbolParameterV CC C L = 50 pF C L = 50 pF Units(V)V CC = +5.0V V CC = +5.0V(Note 5)Typ Guaranteed Minimum t SSetup Time, HIGH or LOW 5.02.05.05.0ns S 0 or S 1 to CPt HHold Time, HIGH or LOW 5.00 1.5 1.5 nsS 0 or S 1 to CPt SSetup Time, HIGH or LOW 5.0 1.0 4.0 4.5 nsI/O n , DS 0, DS 7 to CPt HHold Time, HIGH or LOW 5.00 1.0 1.0 nsI/O n , DS 0, DS 7 to CPt SSetup Time, HIGH or LOW 5.0 1.0 2.5 2.5 nsSR to CPt HHold Time, HIGH or LOW 5.00 1.0 1.0 nsSR to CPt WCP Pulse Width 5.0 2.0 4.0 4.5 nsHIGH or LOWSymbol ParameterTyp Units ConditionsC IN Input Capacitance4.5 pF V CC = OPEN C PDPower Dissipation Capacitance170pFV CC = 5.0VF a irch ild d o e s n o t a ssu m e a n y re spo n sib ility fo r u se o f a n y circu itry de scrib e d , n o circu it pa ten t lice nse s a re im p lie d a nd F a irch ild re se rv e s the rig h t a t a n y tim e w ith ou t n o tice to cha n g e sa id circu itry an d sp e cifica tio n s.74A C T 323 8-B i t U n i v e r s a l S h i f t /S t o r a g e R e g i s t e r w i t h S y n c h r o n o u s R e s e t a n d C o m m o n I /O P i n sLIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or Physical Dimensions inches (millimeters) unless otherwise noted20-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300” WidePackage Number N20A。

74LVC16373ADGG,118,74LVC16373ADGG,518,74LVC16373ADGG,118,74LVC16373ADGG,118,规格书,Datasheet 资料

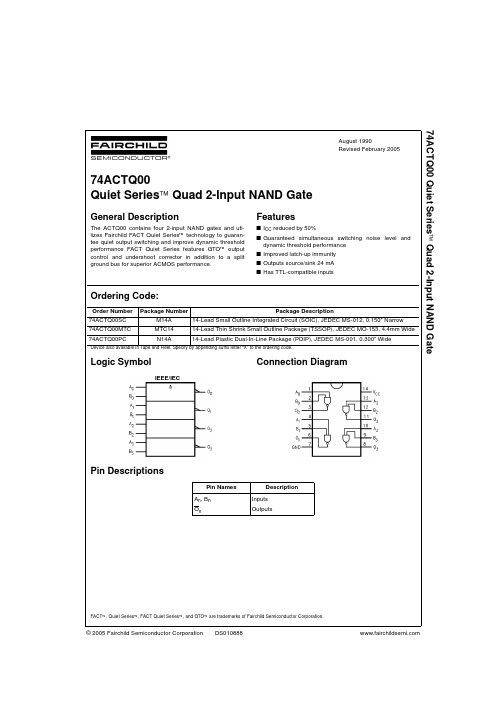

74LVC16373A; 74LVCH16373A

DESCRIPTION data input data input latch enable input (active HIGH)

4, 10, 15, 21, 28, ground (0 V) 34, 39, 45 5 6 7, 18, 31, 42 8 9 11 12 13 14 16 17 19 20 22 23 24 25 26 27 29 30 32 33 35 36 37 38 40 41 43 44 data output data output supply voltage data output data output data output data output data output data output data output data output data output data output data output data output output enable input (active LOW) latch enable input (active HIGH) data input data input data input data input data input data input data input data input data input data input data input data input data input data input Fig.1 Pin configuration SSOP48 and TSSOP48.

2003 Dec 08

2

芯天下--/

Philips Semiconductors

Product specification

16-bit D-type transparent latch with 5 V tolerant inputs/outputs; 3-state

74ACTQ74SC资料

2ห้องสมุดไป่ตู้

元器件交易网

74ACTQ74

Absolute Maximum Ratings(Note 1)

Supply Voltage (VCC) DC Input Diode Current (IIK) VI = −0.5V VI = VCC + 0.5V DC Input Voltage (VI) DC Output Diode Current (IOK) VO = −0.5V VO = VCC + 0.5V DC Output Voltage (VO) DC Output Source or Sink Current (IO) DC VCC or Ground Current per Output Pin (ICC or IGND ) Storage Temperature (TSTG) DC Latch-Up Source or Sink Current Junction Temperature (TJ) PDIP ± 50 mA −65°C to +150°C ± 300 mA 140°C ± 50 mA −20 mA +20 mA −0.5V to VCC + 0.5V −20 mA +20 mA −0.5V to VCC + 0.5V −0.5V to +7.0V

L

X

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial = LOW-to-HIGH Clock Transition Q0(Q0) = Previous Q(Q) before LOW-to-HIGH Transition of Clock

74ACT253SC资料

74AC253 • 74ACT253

Functional Description

The AC/ACT253 contains two identical 4-input multiplexers with 3-STATE outputs. They select two bits from four sources selected by common Select inputs (S0, S1). The 4input multiplexers have individual Output Enable (OEa, OEb) inputs which, when HIGH, force the outputs to a high impedance (High Z) state. This device is the logic implementation of a 2-pole, 4-position switch, where the position of the switch is determined by the logic levels supplied to the two select inputs. The logic equations for the outputs are shown: Za = OEa • Zb = OEb • (I0a • S1 • S0 + I1a • S1 • S0 + I2a • S1 • S0 + I3a • S1 • S0) (I0b • S1 • S0 + I1b • S1 • S0 + I2b • S1 • S0 + I3b • S1 • S0) If the outputs of 3-STATE devices are tied together, all but one device must be in the high impedance state to avoid high currents that would exceed the maximum ratings. Designers should ensure that Output Enable signals to 3STATE devices whose outputs are tied together are designed so that there is no overlap.

LED驱动控制专用芯片TM1637介绍

LED驱动控制专用芯片TM1637介绍特性描述TM1637是一种带键盘扫描接口的LED(发光二极管显示器)驱动控制专用电路,内部集成有MCU 数字接口、数据锁存器、LED 高压驱动、键盘扫描等电路。

功能特点显示模式(8 段×6 位),支持共阳数码管输出键扫描(8×2bit),增强型抗干扰按键识别电路辉度调节电路(占空比 8 级可调)两线串行接口(CLK,DIO)振荡方式:内置RC 振荡(450KHz+5%)封装形式:DIP20/SOP20管脚信息管脚功能读键扫数据键扫矩阵为8×2bit,如下所示:在有按键按下时,读键数据如下:注意:在无按键按下时,读键数据为:1111_1111,低位在前,高位在后。

显示寄存器地址和显示模式该寄存器存储通过串行接口从外部器件传送到TM1637 的数据,地址00H-05H共6个字节单元,分别与芯片SGE和GRID管脚所接的LED 灯对应,分配如下图:写LED显示数据的时候,按照从显示地址从低位到高位,从数据字节的低位到高位操作。

接口说明微处理器的数据通过两线总线接口和TM1637 通信,在输入数据时当CLK 是高电平时,DIO 上的信号必须保持不变;只有CLK 上的时钟信号为低电平时,DIO 上的信号才能改变。

数据输入的开始条件是CLK为高电平时,DIO 由高变低;结束条件是CLK 为高时,DIO 由低电平变为高电平。

TM1637 的数据传输带有应答信号ACK,当传输数据正确时,会在第八个时钟的下降沿,芯片内部会产生一个应答信号ACK 将DIO 管脚拉低,在第九个时钟结束之后释放DIO 口线。

1、指令数据传输过程如下图(读按键数据时序)Command :读按键指令;S0、S1、S2、K1、K2 组成按键信息编码,S0、S1、S2 为SGn 的编码,K1、K2 为K1 和K2 键的编码,读按键时,时钟频率应小于250K ,先读低位,后读高位。

Protues元件库和元件中文对照

7407 驱动门1N914 二极管74LS00 与非门74LS04 非门74LS08与门74LS390 TTL双十进制计数器7SEG 4针BCD-LED 输出从0-9对应于4 根线的BCD码7SEG 3-8译码器电路BCD-7SEG转换电路ALTERNA TOR 交流发电机AMMETER-MILLI mA 安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK时钟信号源CRYSTAL 晶振D-FLIPFLOP D 触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2 行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

没背光,和常用的1602B功能和引脚一样(除了调背光的二个线脚)LOGIC ANAL YSER 逻辑分析器LOGICPROBE 逻辑探针LOGICPROBE[BIG] 逻辑探针用来显示连接位置的逻辑状态LOGICSTATE 逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE 逻辑触发MASTERSWITCH 按钮手动闭合,立即自动打开MOTOR 马达OR或门POT-LIN 三引线可变电阻器POWER 电源RES 电阻RESISTOR 电阻器SWITCH 按钮手动按一下一个状态SWITCH-SPDT 二选通一按钮VOLTMETER 伏特计VOLTMETER-MILLI mV 伏特计VTERM 串行口终端Electromechanical 电机In ductors 变压器Laplace Primitives 拉普拉斯变换Memory IcsMicroprocessor IcsMiscellaneous 各种器件AERIAL-天线;ATA HDD ;ATA接口的硬盘ATMEGA64 ;AT公司的mage系列单片机BATTERY ;电池CELL ;CRYSTAL-晶振;FUSE ;熔丝METER-仪表;Model ling Primitives各种仿真器件是典型的基本元器模拟,不表示具体型号,只用于仿真,没有PCBOptoelectronics各种发光器件发光二极管,LED,液晶等等PLDs & FPGAs ;Resistors;各种电阻Simulator Primitives 常用的器件Speakers & Soun dersSwitches & Relays开关,继电器,键盘Switchi ng Devices 晶阊管Transistors晶体管(三极管,场效应管)TTL 74 seriesTTL 74ALS seriesTTL 74AS seriesTTL 74F seriesTTL 74HC seriesTTL 74HCT seriesTTL 74LS seriesTTL 74S seriesAnalog Ics模拟电路集成芯片OPAMP 运放PELAY-DPDT 双刀双掷继电器 RES1.2电阻RES3.4可变电阻RESISTOR BRIDGE ? 桥式电阻 RESPACK ?电阻 SCR 晶闸管 PLUG ?插头PLUG AC FEMALE 三相交流插头 SOCKET ?插座SOURCE CURRENT 电流源 SOURCE VOLTAGE 电压源 SPEAKER 扬声器 SW ?开关SW-DPDY ?双刀双掷开关 SW-SPST ?单刀单掷开关 SW-PB 按钮THERM系列p cMO 热调管集成块元件库TRANS1变压器 TRANS2可调变压器 TRIAC ?三端双向可控硅 TRIODE ?三极真空管 VARISTOR 变阻器ECL 10000 Series 各种常用集成电路 MOTOR AC 交流电机Capacitors 电容集合 CMOS 4000 series Conn ectors 排座,排插 MOTOR SERVO 伺服电机 NAND 与非门 NOR 或非门Data Converters ADC,DACNOT 非门 p D otues 1元件库标识和中文说明三极管AND 与门NPN-PHOTO 感光三极管 ANTENNA 天线原理TER 常用库文件:BELL 铃钟OR 或门PHOTO 感光二极管 PNP 三极管NPN DAR NPN 三极管2缓整流Ce 集成块.ddbPNP DAR PNP 三极管POT 滑线变阻器In BiPEIp abO 鸣器S.ddbCAP 电容P C Ot pA DOS ? S 电hbmatic Libraries.ddb CAPACITOR POL 有极性电容 CAPVAR 可调电容P CIRC U 元B fe 常K 用库熔断丝COAX 同轴电缆A C VpCbl (口dbCRYSTAL 晶体整荡器GenerWfCddbDIODE 二极管M D s ODE ane OTTK ddb 稳压二极管DIODE V ARACTOR 变容二极管其他元S 件库段LEDDPY_7-SEG 7 段 LEDDPY_7-SEG_DP 7 段 LED (带小数点) PrOte C DOS SCh lffi atic 4000 Cmos 丄 ib FUSE 熔断器INDUCTOR 电感40NDU CT OB 器NINDUCTOR^可调电感402E JK N 触道器效应管JFET P P 沟道场效应管 P LA MP D 灯泡Schematic An alog Digita l.L ib DPY _7!SEG 数字式集码成块元件库LAMP NEDN 起辉器SW-PB 开关A D E 系祷光二极管系列HD 系列MC 系列METER 仪表BVC 同轴电缆接插件MICROPHONE 麦克风亠一P MiOSFETMiOS chematic Comparator.Lib 比较放大器元件库Protel Dos Shcematic Intel.Lib INTEL公司生产的80系列CPU集成块元件库Protel Dos Schematic Lin ear.lib 线性元件库Protel Dos Schemattic Memory Devices.Lib 内存存储器元件库Protel Dos Schematic SYnertek.Lib SY 系列集成块元件库Protes Dos Schematic Motorlla.Lib 摩托罗拉公司生产的元件库Protes Dos Schematic NEC.lib NEC 公司生产的集成块元件库Protes Dos Schematic Operatio nel Amplifers.lib 运算放大器元件库Protes Dos Schematic TTL.Lib 晶体管集成块元件库74系列Protel Dos Schematic Voltage Regulator.lib 电压调整集成块元件库Protes Dos Schematic乙log.Lib 齐格格公司生产的Z80系列CPU集成块元件库PCB 的连接器符号PROTEUS 原理图元器件库详细说明Device.lib包括电阻、电容、二极管、三极管和ACTIVE.LIB 包括虚拟仪器和有源器件DIODE.LIB 包括二极管和整流桥DISPLAY.LIB 包括 LCD LEDBIPOLAR.LIB 包括三极管FET.LIB 包括场效应管ASIMMDLS.LIB 包括模拟元器件VALVES 丄IB 包括电子管ANALOG.LIB 包括电源调节器、运放和数据采样 ICCAPACITORS.LIB 包 括电容COMS.LIB 包括4000系列ECL.LIB 包括 ECL10000系列MICRO.LIB 包括 通用微处理器OPAMP.LIB 包括 运算放大器RESISTORS.LIB 包括电阻FAIRCHLD .LIB包括FAIRCHLD半导体公司的分立器件LINTEC.LIB包括LINTEC公司的运算放大器NATDAC.LIB包括国家半导体公司的数字采样器件NATOA.LIB包括国家半导体公司的运算放大器TECOOR.LIB包括TECOO公司的SCR 和TRIAC TEXOAC.LIB包括德州仪器公司的运算放大器和比较器ZETEX .LIB包括ZETEX公司的分立器件分立元件库元件名称及中英对照RESPACK 排阻lm016l Icd1602 液晶7SEG CC共阴,CA共阳数码管RESPACK-8排阻(9 脚)以此类推天线直流整流桥整流桥缓蜂电容有极性电容可 熔断丝同 AND 与门ANTENNABATTERY 电源 BELL 铃,钟BVC同轴电缆接插件 BRIDEG 1 (二极管) BRIDEG 2 (集成块) BUFFER 冲器 BUZZER 鸣器 CAP 电容CAPACITORCAPACITOR POLCAPVAR 调电容CIRCUIT BREAKER COAX 轴电缆 CON 插口CRYSTAL 整荡器稳压二极管 变容二极管3 段 LED 7 段 LED7 段LED 带小数电解电感带铁芯电感可调电N 沟P 沟起辉器DIODE极管DIODE SCHOTTKY DIODE VARACTOR DPY_3-SEG DPY_7-SEGDPY_7-SEG_DP 点) ELECTRO 电容 FUSE 熔断器INDUCTOR INDUCTOR IRON INDUCTOR3 感JFET N 道场效应管JFET P 道场效应管LAMP 灯泡LAMP NEDN LED 发光二极管METERDB 并行插口 MICROPHONE麦克风MOSAC伺服电机与感光三MOSFET MOTOR 交流电机MOTOR SERVO NAND 非门 NOR 或非门NOT 非门 NPN NPNE 极管NPN-PHOTO 极管OPAMP 放OR 或门 PHOTO 光二极管PNP 三极管 NPNDAR 极管 PNFDAR 极管 POT 滑线变阻器PELAY-DPDT 继电器RES1.2RES3.4电阻RESISTOR BRIDGERESPACK?SCR晶闸管PLUG ?PLUG AC FEMALESOCKET ?SOURCE CURRENTSOURCE VOLTAGESPEAKER器SW ?关SW-DPDY ?开关SW-SPST ?开关BUTTON钮THERMISTORTRANS1压器TRANS2调变压器TRIAC ?双向可控硅TRIODE ? 空管VARISTOR可变桥式电阻电阻插头三相交流插头插座电流源电压源扬声开双刀双掷单刀单掷按电热调节器变可-——*亠山三端三极真变阻器齐纳 数码管 开ZENER?二极管DPY_7-SEG_DPSW-PB关 重要元件中文名称及说明7407驱动门1N914二极管74LS00与非门74LS04非门74LS08与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9对应于4根线的BCD 码7SEG 3-8译码器电路BCD-7SEG 转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA 安培计AND与门BATTERY电池/电池组BUS总线CAP电容CAPACITOR电容器CLOCK时钟信号源CRYSTAL 晶振D-FLIPFLOP D 触发器FUSE保险丝GROUND 地LAMP 灯LED-RED红色发光二极管LOGIC ANALYSER 逻辑分析器LOGICPROBE逻辑探针LOGICPROBE[BIG]逻辑探针用来显示连接位置的逻辑状态LOGICSTATE逻辑状态用鼠标点击,可改变该方框连接位置的逻辑状态LOGICTOGGLE逻辑触发MASTERSWITCH按钮手动闭合,立即自动打开MOTOR马达OR或门POT-LIN三引线可变电阻器POWER电源RES电阻RESISTOR电阻器SWITCH按钮手动按一下一个状态SWITCH-SPDT 二选通一按钮VOLTMETER伏特计VOLTMETER-MILLI mV 伏特计VTERM串行口终端LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN 个控制端口(共14线),工作电压为5V。

74act373mt说明书

1/11April 2001s HIGH SPEED: t PD = 6ns (TYP .) at V CC = 5V sLOW POWER DISSIPATION:I CC = 4µA(MAX.) at T A =25°CsCOMPATIBLE WITH TTL OUTPUTS V IH = 2V (MIN.), V IL = 0.8V (MAX.)s50Ω TRANSMISSION LINE DRIVING CAPABILITYsSYMMETRICAL OUTPUT IMPEDANCE:|I OH | = I OL = 24mA (MIN)sBALANCED PROPAGATION DELAYS:t PLH ≅ t PHLsOPERATING VOLTAGE RANGE:V CC (OPR) = 4.5V to 5.5VsPIN AND FUNCTION COMPATIBLE WITH 74 SERIES 373sIMPROVED LATCH-UP IMMUNITYDESCRIPTIONThe 74ACT373 is a high-speed CMOS OCTAL D-TYPE LATCH with 3 STATE OUTPUT NON INVERTING fabricated with sub-micron silicon gate and double-layer metal wiring C 2MOS technology.These 8 bit D-Type latch are controlled by a latch enable input (LE) and an output enable input (OE).When the (LE) input is high , the Q outputs follow the data (D) inputs . When the (LE) is taken low,the Q outputs will be latched at the logic levels set up at the D inputs. When the (OE) input is low, the8 outputs will be in a normal logic state (high or low logic level); when the (OE) input is high, the outputs will be in a high impedance state.This device is designed to interface directly High Speed CMOS systems with TTL and NMOS components.All inputs and outputs are equipped with protection circuits against static discharge, giving them 2KV ESD immunity and transient excess voltage.74ACT373OCTAL D-TYPE LATCHWITH 3 STATE OUTPUTS (NON INVERTED)PIN CONNECTION AND IEC LOGIC SYMBOLSORDER CODESPACKAGE TUBE T & R DIP 74ACT373B SOP 74ACT373M74ACT373MTRTSSOP74ACT373TTRs l c )Ob sc t () -O bs o e t eP r od u t (s)O b ss 74ACT3732/11INPUT AND OUTPUT EQUIVALENT CIRCUIT PIN DESCRIPTIONTRUTH TABLEZ : High ImpedanceNOTE: Outputs are latched at the time when the input is taken LOW logic levelLOGIC DIAGRAMThis logic diagram has not be used to estimate propagation delaysl slc)O b s oe t eP ro du ct()-O bs oe t eP ro dut(s74ACT3733/11 ABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions isnot implied.RECOMMENDED OPERATING CONDITIONS1) V IN from 0.8V to 2.0VSymbol Parameter Value UnitV CC Supply Voltage-0.5 to +7VV I DC Input Voltage-0.5 to V CC + 0.5VV O DC Output Voltage-0.5 to V CC + 0.5VI IK DC Input Diode Current± 20mAI OK DC Output Diode Current± 20mAI O DC Output Current± 50mAI CC or I GND DC V CC or Ground Current± 400mAT stg Storage T emperature-65 to +150°CT L Lead Temperature (10 sec)300°CSymbol Parameter Value UnitV CC Supply Voltage 4.5 to 5.5VV I Input Voltage0 to V CC VV O Output Voltage0 to V CC VT op Operating T emperature-55 to 125°Cdt/dv Input Rise and Fall Time V CC = 4.5 to 5.5V (note 1)8ns/Vl slc)O b s oe t eP ro du ct()-O bs oe t eP ro dut(s 74ACT3734/11DC SPECIFICATIONS1) Maximum test duration 2ms, one output loaded at time2) Incident wave switching is guaranteed on trasmission lines with impedances as low as 50ΩAC ELECTRICAL CHARACTERISTICS (C L = 50 pF, R L = 500 Ω, Input t r = t f = 3ns)(*) Voltage range is 5.0V ±0.5VSymbol ParameterTest Condition ValueUnitV CC(V)T A = 25°C-40 to 85°C-55 to 125°CMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage4.5V O = 0.1 V orV CC-0.1V2.0 1.5 2.0 2.0V5.5 2.0 1.5 2.0 2.0V IL Low Level InputVoltage4.5V O = 0.1 V orV CC-0.1V1.50.80.80.85.5 1.50.80.80.8V V OH High Level OutputVoltage4.5I O=-50 µA 4.4 4.49 4.4 4.45.5I O=-50 µA 5.4 5.49 5.4 5.44.5I O=-24 mA 3.86 3.76 3.7V5.5I O=-24 mA 4.86 4.76 4.7V OL Low Level OutputVoltage4.5I O=50 µA0.0010.10.10.15.5I O=50 µA0.0010.10.10.14.5I O=24 mA0.360.440.55.5I O=24 mA0.360.440.5I I Input Leakage Cur-rent5.5V I = V CC or GND± 0.1± 1± 1µAI OZ High ImpedanceOutput LeakegeCurrent5.5V I = V IH or V ILV O = V CC or GND± 0.5± 5± 5µAI CCT Max I CC/Input 5.5V I = V CC - 2.1V0.6 1.5 1.6mAI CC Quiescent SupplyCurrent5.5V I = V CC or GND44080µAI OLD Dynamic OutputCurrent (note 1, 2)5.5V OLD = 1.65 V max7550mAI OHD V OHD = 3.85 V min-75-50mASymbol ParameterTest Condition ValueUnitV CC(V)T A = 25°C-40 to 85°C-55 to 125°CMin.Typ.Max.Min.Max.Min.Max.t PLH t PHL Propagation DelayTime LE to Q 5.0(*) 5.510.011.511.5ns t PLH t PHL Propagation DelayTime D to Q 5.0(*) 6.010.011.511.5ns t PZL t PZH Output EnableTime 5.0(*) 6.09.510.510.5ns t PLZ t PHZ Output DisableTime 5.0(*)7.011.012.512.5ns t W LE Minimum PulseWidth, HIGH 5.0(*) 1.37.08.08.0ns t s Setup Time D toLE, HIGH or LOW 5.0(*)-0.57.08.08.0ns t h Hold Time D to LE,HIGH or LOW 5.0(*)0.50.0 1.0 1.0nsl t)O b s oe t eP ro du c(s)-Obs74ACT3735/11 CAPACITIVE CHARACTERISTICS1) C PD is defined as the value of the IC’s internal equivalent capacitance which is calculated from the operating current consumption withoutload. (Refer to Test Circuit). Average operating current can be obtained by the following equation. I CC(opr) = C PD x V CC x f IN + I CC/n (per circuit)TEST CIRCUITC L = 50pF or equivalent (includes jig and probe capacitance)R L = R1 = 500Ω or equivalentR T = Z OUT of pulse generator (typically 50Ω)Symbol ParameterTest Condition ValueUnitV CC(V)T A = 25°C-40 to 85°C-55 to 125°CMin.Typ.Max.Min.Max.Min.Max.C IN Input Capacitance 5.04pFC OUT OutputCapacitance5.08pFC PD Power DissipationCapacitance (note1)5.0f IN = 10MHz25pFTEST SWITCH t PLH, t PHL Opent PZL, t PLZ2V CCt PZH, t PHZ Open) O bss 74ACT373WAVEFORM 1: PROPAGATION DELAYS, LE MINIMUN PULSE WIDTH, Dn TO LE SETUP ANDHOLD TIMES (f=1MHz; 50% duty cycle)WAVEFORM 2: OUTPUT ENABLE AND DISABLE TIMES (f=1MHz; 50% duty cycle)l sl)O b s oe t eP ro du ct()-O bs oe t ePs74ACT3737/11 WAVEFORM 3: PROPAGATION DELAYS TIME (f=1MHz; 50% duty cycle)O bO bO bl slc)O b s oe t eP ro du ct()-O bs oe t eP ro dut(s74ACT373Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for theconsequences of use of such information nor for any infringement of patents or other rights of third parties which may result fromits use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specificationsmentioned in this publication are subject to change without notice. This publication supersedes and replaces all informationpreviously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices orsystems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 11/11。

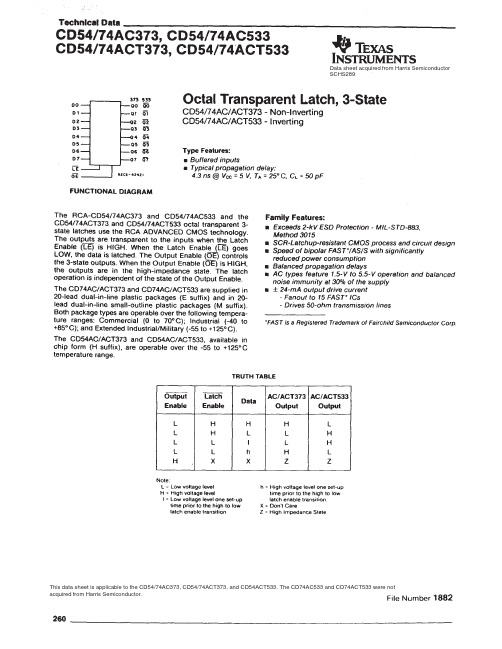

CD74ACT373中文资料

Data sheet acquired from Harris SemiconductorSCHS289This data sheet is applicable to the CD54/74AC373, CD54/74ACT373, and CD54ACT533. The CD74AC533 and CD74ACT533 were notacquired from Harris Semiconductor.IMPORTANT NOTICETexas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE (“CRITICAL APPLICATIONS”). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER’S RISK.In order to minimize risks associated with the customer’s applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI’s publication of information regarding any third party’s products or services does not constitute TI’s approval, warranty or endorsement thereof.Copyright © 1999, Texas Instruments Incorporated。

74系列数字集成电路功能表大全word精品文档9页

74系列数字集成电路功能表大全74LS系列通用逻辑电路功能表74LS00 TTL 2输入端四与非门74LS01 TTL 集电极开路2输入端四与非门74LS02 TTL 2输入端四或非门74LS03 TTL 集电极开路2输入端四与非门74LS122 TTL 可再触发单稳态多谐振荡器74LS123 TTL 双可再触发单稳态多谐振荡器74LS125 TTL 三态输出高有效四总线缓冲门74LS126 TTL 三态输出低有效四总线缓冲门74LS13 TTL 4输入端双与非施密特触发器74LS132 TTL 2输入端四与非施密特触发器74LS133 TTL 13输入端与非门74LS136 TTL 四异或门74LS138 TTL 3-8线译码器/复工器74LS139 TTL 双2-4线译码器/复工器74LS14 TTL 六反相施密特触发器74LS145 TTL BCD—十进制译码/驱动器74LS15 TTL 开路输出3输入端三与门74LS150 TTL 16选1数据选择/多路开关74LS151 TTL 8选1数据选择器74LS153 TTL 双4选1数据选择器74LS154 TTL 4线—16线译码器74LS155 TTL 图腾柱输出译码器/分配器74LS156 TTL 开路输出译码器/分配器74LS157 TTL 同相输出四2选1数据选择器74LS158 TTL 反相输出四2选1数据选择器74LS16 TTL 开路输出六反相缓冲/驱动器74LS160 TTL 可预置BCD异步清除计数器74LS161 TTL 可予制四位二进制异步清除计数器74LS162 TTL 可预置BCD同步清除计数器74LS163 TTL 可予制四位二进制同步清除计数器74LS164 TTL 八位串行入/并行输出移位寄存器74LS165 TTL 八位并行入/串行输出移位寄存器74LS166 TTL 八位并入/串出移位寄存器74LS169 TTL 二进制四位加/减同步计数器74LS17 TTL 开路输出六同相缓冲/驱动器74LS170 TTL 开路输出4×4寄存器堆74LS173 TTL 三态输出四位D型寄存器74LS174 TTL 带公共时钟和复位六D触发器74LS175 TTL 带公共时钟和复位四D触发器74LS180 TTL 9位奇数/偶数发生器/校验器74LS181 TTL 算术逻辑单元/函数发生器74LS185 TTL 二进制—BCD代码转换器74LS190 TTL BCD同步加/减计数器74LS191 TTL 二进制同步可逆计数器74LS192 TTL 可预置BCD双时钟可逆计数器74LS193 TTL 可预置四位二进制双时钟可逆计数器74LS194 TTL 四位双向通用移位寄存器74LS195 TTL 四位并行通道移位寄存器74LS196 TTL 十进制/二-十进制可预置计数锁存器74LS197 TTL 二进制可预置锁存器/计数器74LS20 TTL 4输入端双与非门74LS21 TTL 4输入端双与门74LS22 TTL 开路输出4输入端双与非门74LS221 TTL 双/单稳态多谐振荡器74LS240 TTL 八反相三态缓冲器/线驱动器74LS241 TTL 八同相三态缓冲器/线驱动器74LS243 TTL 四同相三态总线收发器74LS244 TTL 八同相三态缓冲器/线驱动器74LS245 TTL 八同相三态总线收发器74LS247 TTL BCD—7段15V输出译码/驱动器74LS248 TTL BCD—7段译码/升压输出驱动器74LS249 TTL BCD—7段译码/开路输出驱动器74LS251 TTL 三态输出8选1数据选择器/复工器74LS253 TTL 三态输出双4选1数据选择器/复工器74LS256 TTL 双四位可寻址锁存器74LS257 TTL 三态原码四2选1数据选择器/复工器74LS258 TTL 三态反码四2选1数据选择器/复工器74LS259 TTL 八位可寻址锁存器/3-8线译码器74LS26 TTL 2输入端高压接口四与非门74LS260 TTL 5输入端双或非门74LS266 TTL 2输入端四异或非门74LS27 TTL 3输入端三或非门74LS273 TTL 带公共时钟复位八D触发器74LS279 TTL 四图腾柱输出S-R锁存器74LS28 TTL 2输入端四或非门缓冲器74LS283 TTL 4位二进制全加器74LS290 TTL 二/五分频十进制计数器74LS293 TTL 二/八分频四位二进制计数器74LS295 TTL 四位双向通用移位寄存器74LS298 TTL 四2输入多路带存贮开关74LS299 TTL 三态输出八位通用移位寄存器74LS30 TTL 8输入端与非门74LS32 TTL 2输入端四或门74LS322 TTL 带符号扩展端八位移位寄存器74LS323 TTL 三态输出八位双向移位/存贮寄存器74LS33 TTL 开路输出2输入端四或非缓冲器74LS347 TTL BCD—7段译码器/驱动器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS352 TTL 双4选1数据选择器/复工器74LS353 TTL 三态输出双4选1数据选择器/复工器74LS365 TTL 门使能输入三态输出六同相线驱动器74LS366 TTL 门使能输入三态输出六反相线驱动器74LS367 TTL 4/2线使能输入三态六同相线驱动器74LS368 TTL 4/2线使能输入三态六反相线驱动器74LS37 TTL 开路输出2输入端四与非缓冲器74LS373 TTL 三态同相八D锁存器74LS374 TTL 三态反相八D锁存器74LS375 TTL 4位双稳态锁存器74LS377 TTL 单边输出公共使能八D锁存器74LS378 TTL 单边输出公共使能六D锁存器74LS379 TTL 双边输出公共使能四D锁存器74LS38 TTL 开路输出2输入端四与非缓冲器74LS380 TTL 多功能八进制寄存器74LS39 TTL 开路输出2输入端四与非缓冲器74LS390 TTL 双十进制计数器74LS393 TTL 双四位二进制计数器74LS40 TTL 4输入端双与非缓冲器74LS42 TTL BCD—十进制代码转换器74LS447 TTL BCD—7段译码器/驱动器74LS45 TTL BCD—十进制代码转换/驱动器74LS450 TTL 16:1多路转接复用器多工器74LS451 TTL 双8:1多路转接复用器多工器74LS453 TTL 四4:1多路转接复用器多工器74LS46 TTL BCD—7段低有效译码/驱动器74LS460 TTL 十位比较器74LS461 TTL 八进制计数器74LS465 TTL 三态同相2与使能端八总线缓冲器74LS466 TTL 三态反相2与使能八总线缓冲器74LS467 TTL 三态同相2使能端八总线缓冲器74LS468 TTL 三态反相2使能端八总线缓冲器74LS469 TTL 八位双向计数器74LS47 TTL BCD—7段高有效译码/驱动器74LS48 TTL BCD—7段译码器/内部上拉输出驱动74LS490 TTL 双十进制计数器74LS491 TTL 十位计数器74LS498 TTL 八进制移位寄存器74LS50 TTL 2-3/2-2输入端双与或非门74LS502 TTL 八位逐次逼近寄存器74LS503 TTL 八位逐次逼近寄存器74LS51 TTL 2-3/2-2输入端双与或非门74LS533 TTL 三态反相八D锁存器74LS534 TTL 三态反相八D锁存器74LS54 TTL 四路输入与或非门74LS540 TTL 八位三态反相输出总线缓冲器74LS55 TTL 4输入端二路输入与或非门74LS563 TTL 八位三态反相输出触发器74LS564 TTL 八位三态反相输出D触发器74LS573 TTL 八位三态输出触发器74LS574 TTL 八位三态输出D触发器74LS645 TTL 三态输出八同相总线传送接收器74LS670 TTL 三态输出4×4寄存器堆74LS73 TTL 带清除负触发双J-K触发器74LS74 TTL 带置位复位正触发双D触发器74LS76 TTL 带预置清除双J-K触发器74LS83 TTL 四位数字比较器74。

MC74LCX16373中文资料

nLE

Inputs LE1 X H H L OE1 H L L L D0:7 X L H X

Outputs O0:7 Z L H O0 LE2 X H H L

Inputs OE2 H L L L D8:15 X L H X

Outputs O8:15 Z L H O0

H = High Voltage Level; L = Low Voltage Level; Z = High Impedance State; X = High or Low Voltage Level and Transitions Are Acceptable, for ICC reasons, DO NOT FLOAT Inputsபைடு நூலகம்

MOTOROLA

2

LCX DATA BR1339 — REV 3

元器件交易网

MC74LCX16373

ABSOLUTE MAXIMUM RATINGS*

Symbol VCC VI VO Parameter DC Supply Voltage DC Input Voltage DC Output Voltage Value –0.5 to +7.0 –0.5 ≤ VI ≤ +7.0 –0.5 ≤ VO ≤ +7.0 –0.5 ≤ VO ≤ VCC + 0.5 IIK IOK DC Input Diode Current DC Output Diode Current –50 –50 +50 IO ICC IGND TSTG DC Output Source/Sink Current DC Supply Current Per Supply Pin DC Ground Current Per Ground Pin Storage Temperature Range ±50 ±100 ±100 –65 to +150 Output in 3–State Note 1. VI < GND VO < GND VO > VCC Condition Unit V V V V mA mA mA mA mA mA °C

74系列 数字集成电路 型号功能表

7434 六缓冲器

7436 四4输入或非门

7437 四输入端与非缓冲器

7438 双2输入与非缓冲器(OC)

7440 双四输入端与非缓冲器

74126 四3态总线缓冲器

74128 双2输入端或非线驱动器

74131 3-8线译码器

74132 二输入与非触发器

74133 13输入与非门

74134 12输入与非门

74165 8位移位寄存器

74166 8位移位寄存器

74167 BCD同步系数乘法器

74168 4位可逆同步计数器

74169 4位可逆同步计数器

74170 4×4位寄存器堆

7483 4位全加器

7485 4位幅度比较器

7486 四2输入异或门

7490 4位十进制波动计数器

7491 8位移位寄存器

7492 12分频计数器

7493 二进制计数器

7419 六反相器(施密特)

7420 双4输入与非门

7421 双4输入与门

7422 双4输入与非门(OC)

7423 可扩展双4输入与非门

7424 四2输入与非门

74109 正沿触发双J-K触发器

74110 与输入双J-K主从触发器

74112 双J-K负边沿触发器

74113 双J-K负边沿触发器

74114 双J-K负边沿触发器

74116 双4位锁存器

7455 四4输入与或非门

7458 2/3输入双与或非门

7460 双4输入与扩展器

7461 三3输入与扩展器

7462 4输入与扩展器

74hc573完整中文资料

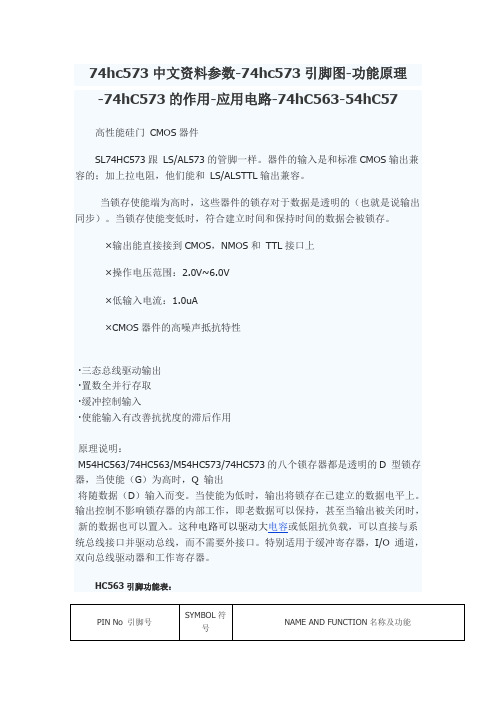

74hc573中文资料参数-74hc573引脚图-功能原理-74hC573的作用-应用电路-74hC563-54hC57高性能硅门CMOS器件SL74HC573跟LS/AL573的管脚一样。

器件的输入是和标准CMOS输出兼容的;加上拉电阻,他们能和LS/ALSTTL输出兼容。

当锁存使能端为高时,这些器件的锁存对于数据是透明的(也就是说输出同步)。

当锁存使能变低时,符合建立时间和保持时间的数据会被锁存。

×输出能直接接到CMOS,NMOS和TTL接口上×操作电压范围:2.0V~6.0V×低输入电流:1.0uA×CMOS器件的高噪声抵抗特性·三态总线驱动输出·置数全并行存取·缓冲控制输入·使能输入有改善抗扰度的滞后作用原理说明:M54HC563/74HC563/M54HC573/74HC573的八个锁存器都是透明的D 型锁存器,当使能(G)为高时,Q 输出将随数据(D)输入而变。

当使能为低时,输出将锁存在已建立的数据电平上。

输出控制不影响锁存器的内部工作,即老数据可以保持,甚至当输出被关闭时,新的数据也可以置入。

这种电路可以驱动大电容或低阻抗负载,可以直接与系统总线接口并驱动总线,而不需要外接口。

特别适用于缓冲寄存器,I/O 通道,双向总线驱动器和工作寄存器。

HC563引脚功能表:HC573引脚功能表:图1 HC573引脚图图2 HC573 国际电工委员会逻辑符号图3 HC563引脚图图4 HC563 国际电工委员会逻辑符号图5 HC563 逻辑图图6 HC573 逻辑图图7 输入输出等效电路真值表:ABSOLUTE MAXIMUM RATINGS绝对最大额定值:Top Operating Temperature: M54HC Series M74HC Series 操作温度:M54HC系列M74HC系列-55 to +125 -40 to +85℃tr,tf Input Rise and Fall Time输入上升和下降时间VCC =2V0 to 1000ns VCC=4.5V0 to 500VCC =6V0 to 400VOHHigh Level Output Voltage输出高电平电压2.0 VI = VIH or VILIO=-20 μA1.92.0-1.9 -1.9 -V4.54.44.54.44.4---6.05.96.05.95.9-4.5IO=-6.0mA4.184.314.134.10-6.0IO=-7.8 mA5.685.85.635.60-VOLLow Level Output Voltage输出低电平电压2.0 VI = VIH or VILIO=20μA-0.0 0.1 -0.1-0.1V4.5-0.00.1 0.10.16.0-0.00.10.10.14.5IO=6.0mA-0.170.260.330.406.0IO=7.8mA-0.180.260.330.40IIInput Leakage Current输入漏电流6.0VI =VCC or GND--±0.1-±1±1μA IOZState Output Off State Current关断状态3态输出电流6.0VI =VIH or VIL VO =VCC or GND--±0.5-±5.0-±10μAICCQuiescent Supply Current静态电源电流6.0VI =VCC or GND--4-40-80μA应用电路图:点击图片查看大图图8。

74LCX16373G中文资料

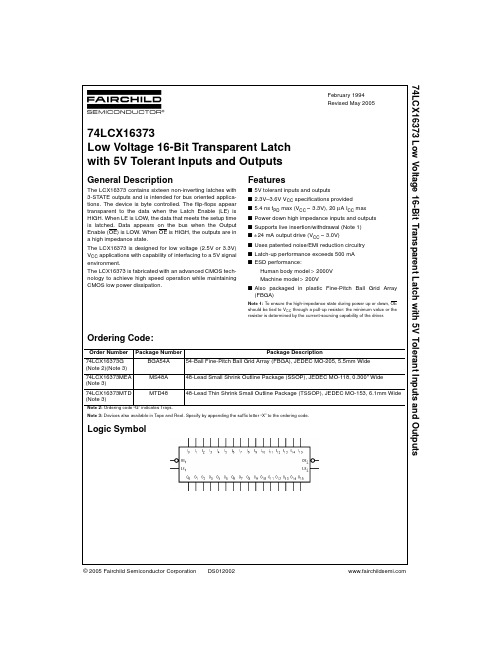

© 2005 Fairchild Semiconductor Corporation DS012002February 1994Revised May 200574LCX16373 Low Voltage 16-Bit Transparent Latch with 5V Tolerant Inputs and Outputs74LCX16373Low Voltage 16-Bit Transparent Latch with 5V Tolerant Inputs and OutputsGeneral DescriptionThe LCX16373 contains sixteen non-inverting latches with 3-STATE outputs and is intended for bus oriented applica-tions. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is LOW, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in a high impedance state.The LCX16373 is designed for low voltage (2.5V or 3.3V)V CC applications with capability of interfacing to a 5V signal environment.The LCX16373 is fabricated with an advanced CMOS tech-nology to achieve high speed operation while maintaining CMOS low power dissipation.Featuress 5V tolerant inputs and outputs s 2.3V–3.6V V CC specifications provided s 5.4 ns t PD max (V CC 3.3V), 20 P A I CC max s Power down high impedance inputs and outputs s Supports live insertion/withdrawal (Note 1)s r 24 mA output drive (V CC 3.0V)s Uses patented noise/EMI reduction circuitry s Latch-up performance exceeds 500 mA s ESD performance:Human body model ! 2000V Machine model ! 200Vs Also packaged in plastic Fine-Pitch Ball Grid Array (FBGA)Note 1: To ensure the high-impedance state during power up or down, OE should be tied to V CC through a pull-up resistor: the minimum value or the resistor is determined by the current-sourcing capability of the driver.Ordering Code:Note 2: Ordering code “G ” indicates Trays.Note 3: Devices also available in Tape and Reel. Specify by appending the suffix letter “X ” to the ordering code.Logic SymbolOrder Number Package NumberPackage Description74LCX16373G (Note 2)(Note 3)BGA54A 54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm Wide 74LCX16373MEA (Note 3)MS48A 48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" Wide 74LCX16373MTD (Note 3)MTD4848-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm Wide 274L C X 16373Connection DiagramsPin Assignment for SSOP and TSSOPPin Assignment for FBGA(Top Thru View)Pin DescriptionsFBGA Pin AssignmentsTruth TablesH HIGH Voltage Level L LOW Voltage Level X ImmaterialZ High ImpedanceO 0 Previous O 0 before HIGH-to-LOW transition of Latch EnablePin Names DescriptionOE n Output Enable Input (Active LOW)LE n Latch Enable Input I 0–I 15Inputs O 0–O 15Outputs NCNo Connect123456A O 0NC OE 1LE 1NC I 0B O 2O 1NC NC I 1I 2C O 4O 3V CC V CC I 3I 4D O 6O 5GND GND I 5I 6E O 8O 7GND GND I 7I 8F O 10O 9GND GND I 9I 10G O 12O 11V CC V CC I 11I 12H O 14O 13NC NC I 13I 14JO 15NCOE 2LE 2NCI 15InputsOutputs LE 1OE 1I 0–I 7O 0–O 7XH X Z H L L L H L H H LL XO 0InputsOutputs LE 2OE 2I 8–I 15O 8–O 15X H X Z H L L L H L H H LLX O 074LCX16373Functional DescriptionThe LCX16373 contains sixteen D-type latches with 3-STATE standard outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LE n ) input is HIGH, data on the I n enters the latches. In this condition the latches are transparent, i.e. a latch output will change state each timeits I input changes. When LE n is LOW, the latches store information that was present on the I inputs a setup time preceding the HIGH-to-LOW transition of LE n . The 3-STATE standard outputs are controlled by the Output Enable (OE n ) input. When OE n is LOW, the standard out-puts are in the 2-state mode. When OE n is HIGH, the stan-dard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.Logic DiagramsPlease note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays. 474L C X 16373Absolute Maximum Ratings (Note 4)Recommended Operating Conditions (Note 6)Note 4: The Absolute Maximum Ratings are those values beyond which the safety of the device cannot be guaranteed. The device should not be operated at these limits. The parametric values defined in the Electrical Characteristics tables are not guaranteed at the Absolute Maximum Ratings. The “Recom-mended Operating Conditions ” table will define the conditions for actual device operation.Note 5: I O Absolute Maximum Rating must be observed.Note 6: Unused inputs must be held HIGH or LOW. They may not float.DC Electrical CharacteristicsSymbol ParameterValueConditionsUnits V CC Supply Voltage 0.5 to 7.0V V I DC Input Voltage 0.5 to 7.0VV O DC Output Voltage 0.5 to 7.0Output in 3-STATEV 0.5 to V CC 0.5Output in HIGH or LOW State (Note 5)I IK DC Input Diode Current 50V I GND mA I OK DC Output Diode Current 50V O GND mA 50V O ! V CCI O DC Output Source/Sink Current r 50mA I CC DC Supply Current per Supply Pin r 100mA I GND DC Ground Current per Ground Pin r 100mAT STGStorage Temperature65 to 150q CSymbol ParameterMin Max Units V CC Supply Voltage Operating 2.0 3.6V Data Retention1.5 3.6V I Input Voltage 0 5.5V V O Output Voltage HIGH or LOW State0V CC V3-STATE5.5I OH /I OLOutput CurrentV CC 3.0V 3.6V r 24mAV CC 2.7V 3.0V r 12V CC 2.3V 2.7Vr 8T AFree-Air Operating Temperature4085q C 't/'VInput Edge Rate, V IN 0.8V –2.0V, V CC 3.0V10ns/VSymbol ParameterConditionsV CC T A 40q C to 85q C Units (V)Min MaxV IH HIGH Level Input Voltage 2.3 2.7 1.7V 2.7 3.6 2.0V IL LOW Level Input Voltage 2.3 2.70.7V2.73.60.8V OHHIGH Level Output VoltageI OH 100 P A 2.3 3.6V CC 0.2VI OH 8 mA 2.3 1.8I OH 12 mA 2.7 2.2I OH 18 mA 3.0 2.4I OH 24 mA3.0 2.2V OLLOW Level Output VoltageI OL 100 P A 2.3 3.60.2V I OL 8 mA 2.30.6I OL 12 mA 2.70.4I OL 16 mA 3.00.4I OL 24 mA3.00.55I I Input Leakage Current 0 d V I d 5.5V 2.3 3.6r 5.0P A I OZ 3-STATE Output Leakage 0 d V O d 5.5V 2.3 3.6r 5.0P A V I V IH or V IL I OFFPower-Off Leakage CurrentV I or V O 5.5V10P A74LCX16373DC Electrical Characteristics (Continued)Note 7: Outputs disabled or 3-STATE only.AC Electrical CharacteristicsNote 8: Skew is defined as the absolute value of the difference between the actual propagation delay for any two separate outputs of the same device. The specification applies to any outputs switching in the same direction, either HIGH-to-LOW (t OSHL ) or LOW-to-HIGH (t OSLH ). Parameter guaranteed by design.Dynamic Switching CharacteristicsCapacitanceSymbol ParameterConditionsV CC T A 40q C to 85q C Units (V)MinMax I CC Quiescent Supply Current V I V CC or GND2.33.620P A 3.6V d V I , V O d 5.5V (Note 7) 2.3 3.6r 20'I CCIncrease in I CC per InputV IH V CC 0.6V2.33.6500P ASymbolParameterT A 40q C to 85q C, R L 500:UnitsV CC 3.3V r 0.3VV CC 2.7V V CC 2.5V r 0.2VC L 50 pF C L 50 pF C L 30 pF MinMax Min Max Min Max t PHL Propagation Delay 1.5 5.4 1.5 5.9 1.5 6.5ns t PLH I n to O n1.5 5.4 1.5 5.9 1.5 6.5t PHL Propagation Delay 1.5 5.5 1.5 6.4 1.5 6.6ns t PLH LE to O n1.5 5.5 1.5 6.4 1.5 6.6t PZL Output Enable Time1.5 6.1 1.5 6.5 1.57.9ns t PZH 1.5 6.1 1.5 6.5 1.57.9t PLZ Output Disable Time 1.5 6.0 1.5 6.3 1.57.2ns t PHZ 1.5 6.01.5 6.31.57.2t S Setup Time, I n to LE 2.5 2.5 3.0ns t H Hold Time, I n to LE 1.5 1.5 2.0ns t W LE Pulse Width3.03.03.5ns t OSHL Output to Output Skew (Note 8) 1.0ns t OSLH1.0Symbol ParameterConditionsV CC T A 25q C Units (V)Typical V OLP Quiet Output Dynamic Peak V OL C L 50 pF, V IH 3.3V, V IL 0V 3.30.8V C L 30 pF, V IH 2.5V, V IL 0V 2.50.6V OLVQuiet Output Dynamic Valley V OLC L 50 pF, V IH 3.3V, V IL 0V 3.3 0.8VC L 30 pF, V IH 2.5V, V IL 0V2.50.6Symbol ParameterConditionsTypical Units C IN Input Capacitance V CC Open, V I 0V or V CC 7pF C OUT Output CapacitanceV CC 3.3V, V I 0V or V CC8pF C PDPower Dissipation CapacitanceV CC 3.3V, V I 0V or V CC , f 10 MHz20pF 674L C X 16373AC LOADING and WAVEFORMS Generic for LCX FamilyFIGURE 1. AC Test Circuit (C L includes probe and jig capacitance)Waveform for Inverting and Non-Inverting FunctionsPropagation Delay. Pulse Width and t rec Waveforms3-STATE Output Low Enable andDisable Times for Logic3-STATE Output High Enable andDisable Times for LogicSetup Time, Hold Time and Recovery Time for Logict rise and t fallFIGURE 2. Waveforms(Input Characteristics; f =1MHz, t r = t f = 3ns)Test Switch t PLH , t PHL Opent PZL , t PLZ 6V at V CC 3.3 r 0.3V, and 2.7V V CC x 2 at V CC 2.5 r 0.2Vt PZH , t PHZGNDSymbol V CC3.3V r 0.3V2.7V 2.5V r 0.2V V mi 1.5V 1.5V V CC /2V mo 1.5V 1.5V V CC /2V x V OL 0.3V V OL 0.3V V OL 0.15V V yV OH 0.3VV OH 0.3VV OH 0.15V74LCX16373 Schematic DiagramGeneric for LCX Family 874L C X 16373Physical Dimensionsinches (millimeters) unless otherwise noted54-Ball Fine-Pitch Ball Grid Array (FBGA), JEDEC MO-205, 5.5mm WidePackage Number BGA54A74LCX16373 Physical Dimensions inches (millimeters) unless otherwise noted (Continued)48-Lead Small Shrink Outline Package (SSOP), JEDEC MO-118, 0.300" WidePackage Number MS48A1074L C X 16373 L o w V o l t a g e 16-B i t T r a n s p a r e n t L a t c h w i t h 5V T o l e r a n t I n p u t s a n d O u t p u t sPhysical Dimensions inches (millimeters) unless otherwise noted (Continued)48-Lead Thin Shrink Small Outline Package (TSSOP), JEDEC MO-153, 6.1mm WidePackage Number MTD48Fairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to the user. 2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.。

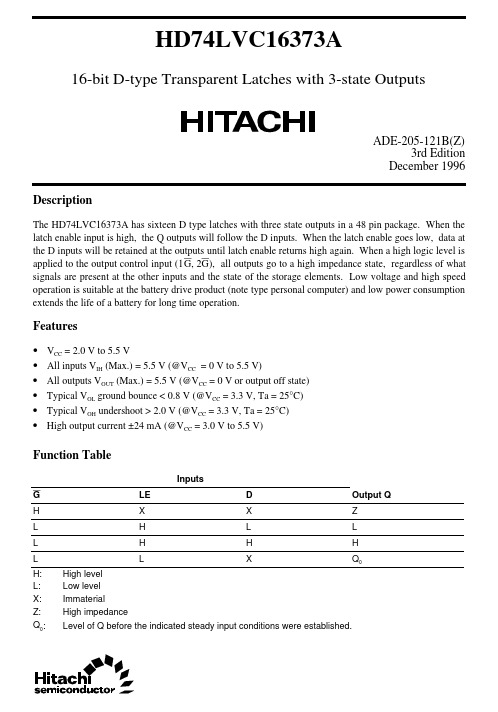

HD74LVC16373A中文资料

HD74LVC16373A16-bit D-type Transparent Latches with 3-state OutputsADE-205-121B(Z)3rd EditionDecember 1996 DescriptionThe HD74LVC16373A has sixteen D type latches with three state outputs in a 48 pin package. When the latch enable input is high, the Q outputs will follow the D inputs. When the latch enable goes low, data at the D inputs will be retained at the outputs until latch enable returns high again. When a high logic level is applied to the output control input (1G, 2G), all outputs go to a high impedance state, regardless of what signals are present at the other inputs and the state of the storage elements. Low voltage and high speed operation is suitable at the battery drive product (note type personal computer) and low power consumption extends the life of a battery for long time operation.Features• V CC = 2.0 V to 5.5 V• All inputs V IH (Max.) = 5.5 V (@V CC = 0 V to 5.5 V)• All outputs V OUT (Max.) = 5.5 V (@V CC = 0 V or output off state)• Typical V OL ground bounce < 0.8 V (@V CC = 3.3 V, Ta = 25°C)• Typical V OH undershoot > 2.0 V (@V CC = 3.3 V, Ta = 25°C)• High output current ±24 mA (@V CC = 3.0 V to 5.5 V)Function TableInputsG LE D Output QH X X ZL H L LL H H HL L X QlevelH: HighL:Low levelX:ImmaterialZ:High impedanceQ:Level of Q before the indicated steady input conditions were established.HD74LVC16373A Pin Arrangement2HD74LVC16373A3Absolute Maximum RatingsItemSymbol Ratings Unit ConditionsSupply voltage V CC –0.5 to 6.0V Input diode current I IK –50mA V I = –0.5 V Input voltage V I –0.5 to 6.0V Output diode current I OK –50mA V O = –0.5 V 50mA V O = V CC +0.5 V Output voltage V O –0.5 to V CC +0.5V Output "H" or "L"–0.5 to 6.0V Output "Z" or V CC :OFF Output current I O±50mA V CC , GND current / pin I CC or I GND 100mA Storage temperatureTstg–65 to +150°CNote:The absolute maximum ratings are values which must not individually be exceeded, and furthermore,no two of which may be realized at the same time.Recommended Operating ConditonsItemSymbol Ratings Unit Conditions Supply voltage V CC 1.5 to 5.5V Data hold 2.0 to 5.5V At operation Input / output voltageV I 0 to 5.5V G , LE, D V O0 to V CC V Output "H" or "L"0 to 5.5V Output "Z" or V CC :OFFOperating temperature Ta –40 to 85°C Output currentI OH –12mA V CC = 2.7 V –24*2mA V CC = 3.0 V to 5.5 V I OL12mA V CC = 2.7 V 24*2mA V CC = 3.0 V to 5.5 V Input rise / fall time *1t r , t f10ns/VNotes: 1.This item guarantees maximum limit when one input switches.Waveform : Refer to test circuit of switching characteristics.2.duty cycle ≤ 50%HD74LVC16373A4Electrical CharacteristicsTa = –40 to 85°CItem Symbol V CC (V)Min Max Unit Test Conditions Input voltageV IH 2.7 to 3.6 2.0—V 4.5 to 5.5V CC ×0.7—V V IL2.7 to3.6—0.8V4.5 to5.5—V CC ×0.3V Output voltageV OH2.7 to 5.5V CC –0.2—V I OH = –100 µA 2.7 2.2—V I OH = –12 mA3.0 2.4—V 3.0 2.2—V I OH = –24 mA4.53.8—V V OL2.7 to 5.5—0.2V I OL = 100 µA 2.7—0.4V I OL = 12 mA3.0—0.55V I OL = 24 mA4.5—0.55V Input currentI IN 0 to 5.5—±5.0µA V IN = 5.5 V or GND Off state output current I OZ 2.7 to 5.5—±5.0µA V IN = V CC , GNDV OUT = 5.5 V or GND Output leak currentI OFF0—20µA V IN / V OUT = 5.5 V Quiescent supply current I CC2.7 to3.6—±20µA V IN / V OUT = 3.6 to 5.5 V 2.7 to 5.5—20µA V IN = V CC or GND∆I CC3.0 to 3.6—500µAV IN = one input at(V CC –0.6)V,other inputs at V CC or GNDHD74LVC16373A5Switching CharacteristicsTa = –40 to 85°CItemSymbol V CC (V)Min Typ Max Unit From (Input)To (Output)Propagation delay timet PLH 2.7——7.7ns DQt PHL 3.3±0.3 1.5—7.0ns 5.0±0.5—— 5.5ns t PLH 2.7——8.0ns LEQt PHL3.3±0.3 2.0—7.0ns 5.0±0.5—— 5.5ns Output enable timet ZH 2.7——8.0ns GQt ZL3.3±0.3 1.5—7.0ns 5.0±0.5—— 6.0ns Output disable timet HZ 2.7——8.0ns GQt LZ3.3±0.3 1.5—7.0ns 5.0±0.5—— 6.0ns Setup timet su2.7 2.0——ns3.3±0.3 2.0——ns 5.0±0.52.0——ns Hold timet h2.7 1.5——ns3.3±0.3 1.5——ns 5.0±0.51.5——ns Pulse widtht w2.73.0——ns 3.3±0.3 3.0——ns 5.0±0.53.0——ns Between output pins skew *1t OSLH 2.7———ns t OSHL3.3±0.3—— 1.0ns 5.0±0.5—— 1.0ns Input capacitance C IN 2.7— 3.0—pF Output capacitance C O2.7—15.0—pFNote:1.This parameter is characterized but not tested.tos LH = | t PLHm – t PLHn |, tos HL = | t PHLm – t PHLn |HD74LVC16373A Test CircuitWaveforms – 16HD74LVC16373A Waveforms – 2Waveforms – 37HD74LVC16373A Waveforms – 48Hitachi CodeJEDECEIAJWeight (reference value)TTP-48DB——0.20 gUnit: mm*Dimension including the plating thickness Base material dimensionCautions1.Hitachi neither warrants nor grants licenses of any rights of Hitachi’s or any third party’s patent,copyright, trademark, or other intellectual property rights for information contained in this document.Hitachi bears no responsibility for problems that may arise with third party’s rights, includingintellectual property rights, in connection with use of the information contained in this document.2.Products and product specifications may be subject to change without notice. Confirm that you have received the latest product standards or specifications before final design, purchase or use.3.Hitachi makes every attempt to ensure that its products are of high quality and reliability. However,contact Hitachi’s sales office before using the product in an application that demands especially high quality and reliability or where its failure or malfunction may directly threaten human life or cause risk of bodily injury, such as aerospace, aeronautics, nuclear power, combustion control, transportation,traffic, safety equipment or medical equipment for life support.4.Design your application so that the product is used within the ranges guaranteed by Hitachi particularly for maximum rating, operating supply voltage range, heat radiation characteristics, installationconditions and other characteristics. Hitachi bears no responsibility for failure or damage when used beyond the guaranteed ranges. Even within the guaranteed ranges, consider normally foreseeable failure rates or failure modes in semiconductor devices and employ systemic measures such as fail-safes, so that the equipment incorporating Hitachi product does not cause bodily injury, fire or other consequential damage due to operation of the Hitachi product.5.This product is not designed to be radiation resistant.6.No one is permitted to reproduce or duplicate, in any form, the whole or part of this document without written approval from Hitachi.7.Contact Hitachi’s sales office for any questions regarding this document or Hitachi semiconductor products.Hitachi, Ltd.Semiconductor & Integrated Circuits.Nippon Bldg., 2-6-2, Ohte-machi, Chiyoda-ku, Tokyo 100-0004, Japan Tel: Tokyo (03) 3270-2111 Fax: (03) 3270-5109Copyright ' Hitachi, Ltd., 1999. All rights reserved. Printed in Japan.Hitachi Asia Pte. Ltd.16 Collyer Quay #20-00Hitachi TowerSingapore 049318Tel: 535-2100Fax: 535-1533URLNorthAmerica : http:/Europe : /hel/ecg Asia (Singapore): .sg/grp3/sicd/index.htm Asia (Taiwan): /E/Product/SICD_Frame.htm Asia (HongKong): /eng/bo/grp3/index.htm Japan : http://www.hitachi.co.jp/Sicd/indx.htmHitachi Asia Ltd.Taipei Branch Office3F, Hung Kuo Building. No.167, Tun-Hwa North Road, Taipei (105)Tel: <886> (2) 2718-3666Fax: <886> (2) 2718-8180Hitachi Asia (Hong Kong) Ltd.Group III (Electronic Components)7/F., North Tower, World Finance Centre,Harbour City, Canton Road, Tsim Sha Tsui,Kowloon, Hong Kong Tel: <852> (2) 735 9218Fax: <852> (2) 730 0281 Telex: 40815 HITEC HXHitachi Europe Ltd.Electronic Components Group.Whitebrook ParkLower Cookham Road MaidenheadBerkshire SL6 8YA, United Kingdom Tel: <44> (1628) 585000Fax: <44> (1628) 778322Hitachi Europe GmbHElectronic components Group Dornacher Stra§e 3D-85622 Feldkirchen, Munich GermanyTel: <49> (89) 9 9180-0Fax: <49> (89) 9 29 30 00Hitachi Semiconductor (America) Inc.179 East Tasman Drive,San Jose,CA 95134 Tel: <1> (408) 433-1990Fax: <1>(408) 433-0223For further information write to:。

SN74ALVCH16373DGGR中文资料

IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third–party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.Mailing Address:Texas InstrumentsPost Office Box 655303Dallas, Texas 75265Copyright 2002, Texas Instruments Incorporated。

TM1637四段数码管模块驱动

TM1637四段数码管模块驱动:轻松上手,点亮你的数字生活一、模块简介1. 支持共阴极或共阳极数码管;2. 内置键扫描电路,可驱动8个按键;3. 通过两个IO口与单片机通信,节省IO资源;4. 可调节显示亮度,满足不同环境需求。

二、模块接口及引脚功能TM1637四段数码管模块共有6个引脚,分别为VCC、GND、DIO、CLK、KEY1和KEY2。

各引脚功能如下:1. VCC:电源正极,接3.3V或5V电源;2. GND:电源负极,接GND;3. DIO:数据输入/输出引脚,与单片机IO口相连;4. CLK:时钟引脚,与单片机IO口相连;5. KEY1、KEY2:按键引脚,可接至单片机IO口,实现按键功能。

三、驱动原理TM1637四段数码管模块的驱动原理如下:1. 初始化:上电后,对TM1637进行初始化,设置显示亮度、扫描频率等参数;2. 数据写入:通过DIO和CLK引脚,将显示数据写入TM1637内部寄存器;3. 显示更新:TM1637内部自动扫描数码管,根据寄存器中的数据更新显示内容;4. 按键扫描:TM1637内置键扫描电路,可实时检测按键状态,并将结果输出至单片机。

四、编程控制1. 引入TM1637库文件;2. 初始化TM1637对象,并设置CLK和DIO引脚;3. 编写显示函数,将数据写入数码管;4. 编写按键扫描函数,检测按键状态。

include <TM1637.h>// 定义CLK和DIO引脚define CLK 2define DIO 3TM1637 tm1637(CLK, DIO);void setup() {// 初始化TM1637tm1637.init();// 设置显示亮度(07)tm1637.setBrightness(5);}void loop() {// 显示数字09for (int i = 0; i < 10; i++) {tm1637.display(i);delay(1000);}}五、模块应用场景1. 时间显示:制作时钟、计时器等,实时展示时间信息;2. 温度显示:配合温度传感器,实时监测环境温度;3. 电压/电流显示:用于电子秤、电源等设备,显示电压或电流值;4. 计数器:用于运动会、比赛等场合,记录选手成绩或得分;5. 智能家居:作为家居设备的一部分,显示各种传感器数据。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

The ACTQ16373 contains sixteen non-inverting latches with 3-STATE outputs and is intended for bus oriented applications. The device is byte controlled. The flip-flops appear transparent to the data when the Latch Enable (LE) is HIGH. When LE is low, the data that meets the setup time is latched. Data appears on the bus when the Output Enable (OE) is LOW. When OE is HIGH, the outputs are in high Z state. The ACTQ16373 utilizes Fairchild’s Quiet Series technology to guarantee quiet output switching and improved dynamic threshold performance. FACT Quiet Series features GTO output control for superior performance.

Device also available in Tape and Reel. Specify by appending suffix letter “X” to the ordering code.

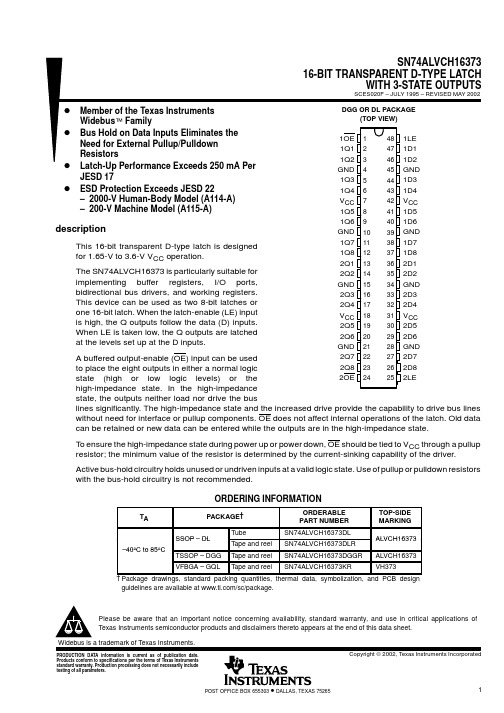

Logic Symbol

Connection Diagram

Pin Descriptions

Pin Names OEn LEn I0–I15 O0–O15 Description Output Enable Input (Active LOW) Latch Enable Input Inpuirchild FACT Quiet Series technology s Guaranteed simultaneous switching noise level and dynamic threshold performance s Guaranteed pin-to-pin output skew s Separate control logic for each byte s 16-bit version of the ACTQ373 s Outputs source/sink 24 mA s Additional specs for Multiple Output Switching s Output Loading specs for both 50 pF and 250 pF loads

Note 1: Absolute maximum ratings are those values beyond which damage to the device may occur. The databook specifications should be met, without exception to ensure that the system design is reliable over its power supply, temperature, and output/input loading variables. Fairchild does not recommend operation of FACT circuits outside databook specifications.

H = HIGH Voltage Level L = LOW Voltage Level X = Immaterial Z = High Impedance Previous = previous output prior to HIGH-to-LOW transition of LE

Logic Diagrams

元器件交易网

74ACTQ16373

Functional Description

The ACTQ16373 contains sixteen D-type latches with 3STATE standard outputs. The device is byte controlled with each byte functioning identically, but independent of the other. Control pins can be shorted together to obtain full 16-bit operation. The following description applies to each byte. When the Latch Enable (LEn) input is HIGH, data on the Dn enters the latches. In this condition the latches are transparent, i.e., a latch output will change states each time its D input changes. When LEn is LOW, the latches store information that was present on the D inputs a setup time preceding the HIGH-to-LOW transition of LEn. The 3STATE standard outputs are controlled by the Output Enable (OEn) input. When OEn is LOW, the standard outputs are in the 2-state mode. When OEn is HIGH, the standard outputs are in the high impedance mode but this does not interfere with entering new data into the latches.

4.5V to 5.5V 0V to VCC 0V to VCC −40°C to +85°C 125 mV/ns

DC Electrical Characteristics