HCF4538M013TR中文资料

HCPL-M453中文资料

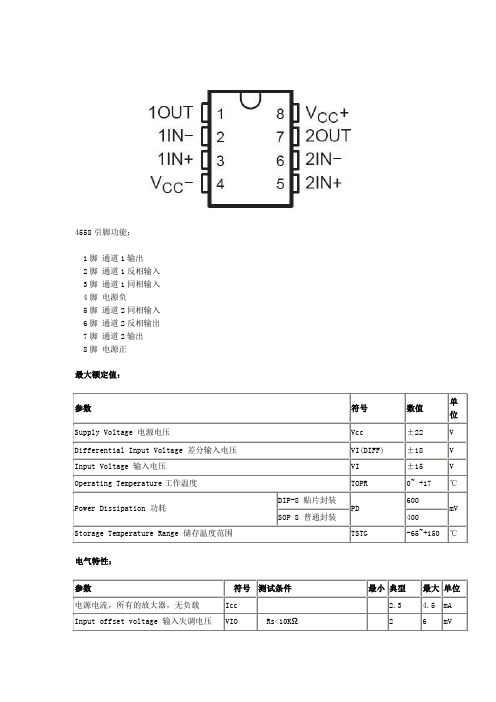

Small Outline, 5 Lead, High Speed Optocouplers Technical DataHCPL-M452HCPL-M453Features• Surface Mountable• Very Small, Low Profile JEDEC Registered Package Outline• Compatible with Infrared Vapor Phase Reflow and Wave Soldering Processes • Very High Common Mode Transient Immunity:15000 V/µs at V CM = 1500 V Guaranteed (HCPL-M453)• High Speed: 1 Mb/s • TTL Compatible• Guaranteed AC and DC Performance overTemperature: 0°C to 70°C • Open Collector Output • Recognized Under the Component Program of U.L. (File No. E55361) for Dielectric Withstand Proof Test Voltage of 3750 Vac, 1Minute• Lead Free OptionCAUTION: The small device geometries inherent to the design of this bipolar component increase the component's susceptibility to damage from electrostatic discharge (ESD). It is advised that normal static precautions be taken in handling and assembly of this component to prevent damage and/or degradation which may be induced by ESD.The SO-5 JEDEC registered (MO-155) package outline does not require “through holes” in a PCB. This package occupies approximately one-fourth the footprint area of the standard dual-in-line package. The lead profile is designed to be compatible with standard surface mount processes.These diode-transistoroptocouplers use an insulating layer between the light emitting diode and an integrated photon detector to provide electrical insulation between input and output. Separate connections for the photodiode bias and output transistor collector increase the speed up to a hundred timesSO-5 Package Standard DIP SO-8 Package HCPL-M452HCPL-4502HCPL-0452HCPL-M453HCPL-4503HCPL-0453(Note: These devices equivalent to 6N135/6N136 devices but without the base lead.)DescriptionThese small outline high CMR,high speed, diode-transistor opto-couplers are single channel devices in a five lead miniature footprint. They are electrically equivalent to the following Agilent optocouplers:tions. A standard 16 mA TTL sink current through the input LED will provide enough output current for 1 TTL load and a 5.6 k Ω pull-up resistor. CTR of the HCPL-M452 is 19%minimum at I F = 16 mA.over that of a conventional photo-transistor coupler by reducing the base-collector capacitance.The HCPL-M452 is designed for high speed TTL/TTL applica-The HCPL-M453 is an HCPL-M452 with increased common mode transient immunity of 15,000 V/µs minimum at V CM =1500 V guaranteed.Applications• Line Receivers -High common mode transient immunity (>1000V/µs) and low input-output capacitance (0.6 pF).• High Speed Logic Ground Isolation - TTL/TTL, TTL/LTTL, TTL/CMOS, TTL/LSTTL.• Replace Slow Phototran-sistor Optocouplers • Replace PulseTransformers - Save board space and weight• Analog Signal Ground Isolation -Integrated photon detector provides improved linearity over phototransistor type.Land Pattern RecommendationDIMENSIONS IN MILLIMETERS AND (INCHES)Outline Drawing (JEDEC MO-155)SchematicGNDV CCV OANODECATHODEDIMENSIONS IN MILLIMETERS (INCHES)* MAXIMUM MOLD FLASH ON EACH SIDE IS 0.15 mm (0.006)NOTE: FLOATING LEAD PROTRUSION IS 0.15 mm (6 mils) MAX.MAX.= 0.102 (0.004)Absolute Maximum Ratings(No Derating Required up to 85°C)Storage Temperature .................................................-55°C to +125°C Operating Temperature .............................................-55°C to +100°C Average Input Current - I F .....................................................25 mA [1]Peak Input Current - I F ...........................................................50 mA [2](50% duty cycle, 1 ms pulse width)Peak Transient Input Current - I F ..............................................1.0 A(≤1 µs pulse width, 300 pps)Reverse Input Voltage - V R (Pin3-1)...............................................5 V Input Power Dissipation ........................................................45 mW [3]Average Output Current - I O (Pin 5)...........................................8 mA Peak Output Current .................................................................16 mA Output Voltage - V O (Pin 5-4)........................................-0.5 V to 20 V Supply Voltage - V CC (Pin 6-4).......................................-0.5 V to 30 V Output Power Dissipation....................................................100 mW [4]Infrared and Vapor Phase Reflow Temperature..................see belowSolder Reflow Thermal ProfileRecommended Pb-Free IR ProfileTIME (SECONDS)T E M P E R A T U R E (°C )ROOM°C of ACTUAL NOTES:THE TIME FROM 25 °C to PEAK TEMPERATURE = 8 MINUTES MAX.T smax = 200 °C, T smin = 150 °CInsulation Related SpecificationsParameter Symbol Value Units ConditionsMin External Air Gap L(IO1)≥ 5mm Measured from input terminals (Clearance)to output terminalsMin. External Tracking Path L(IO2)≥ 5mm Measured from input terminals (Creepage)to output terminalsMin. Internal Plastic Gap0.08mm Through insulation distance (Clearance)conductor to conductor Tracking Resistance CTI175V DIN IEC 112/VDE 0303 Part 1 Isolation Group (per DIN VDE 0109)IIIa Material Group DIN VDE 0109Electrical SpecificationsOver recommended temperature (T A = 0°C to 70°C) unless otherwise specified. (See note 11.)*All typicals at T A = 25°C.Switching SpecificationsOver recommended temperature (T A = 0°C to 70°C) V CC = 5 V, I F = 16 mA unless otherwise specified.All typicals at T A = 25°C.Notes:1. Derate linearly above 85°C free-air temperature at a rate of 0.5 mA/°C.2. Derate linearly above 85°C free-air temperature at a rate of 1.0 mA/°C.3. Derate linearly above 85°C free-air temperature at a rate of 1.1 mW/°C.4. Derate linearly above 85°C free-air temperature at a rate of 2.3 mW/°C.5. CURRENT TRANSFER RATIO in percent is defined as the ratio of output collector current, I O, to the forward LED inputcurrent, I F, times 100.6. Device considered a two terminal device: pins 1 and 3 shorted together, and pins 4, 5 and 6 shorted together.7. In accordance with UL 1577, each optocoupler is proof tested by applying an insulation test voltage ≥4500 V RMS for 1 second(leakage detection current limit, I I-O≤ 5 µA).8. Common transient immunity in a Logic High level is the maximum tolerable (positive) dV CM/dt on the rising edge of thecommon mode pulse, V CM, to assure that the output will remain in a Logic High state (i.e., V O > 2.0 V). Common mode transient immunity in a Logic Low level is the maximum tolerable (negative) dV CM/dt on the falling edge of the common mode pulse signal, V CM to assure that the output will remain in a Logic Low state (i.e., V O < 0.8 V).9. The 1.9 kΩ load represents 1 TTL unit load of 1.6 mA and the 5.6 kΩ pull-up resistor.10. The frequency at which the ac output voltage is 3 dB below its mid-frequency value.11. Use of a 0.1 µF bypass capacitor connected between pins 4 and 6 is recommended.Figure 7. Logic High Output Current vs. Temperature.Figure 8. Small-Signal CurrentTransfer Ratio vs. Quiescent Input Current.Figure 4. Current Transfer Ratio vs.Temperature.Figure 5. Propagation Delay vs.Temperature.Figure 6. Propagation Delay Time vs. Load Resistance.Figure 1. dc and Pulsed Transfer Characteristics.Figure 2. Current Transfer Ratio vs.Input Current.Figure 3. Input Current vs. Forward Voltage.105V O – OUTPUT VOLTAGE – VI O – O U T P U T C U R R E N T – m A1.51.00.50.1N O R M A L I Z E D C U R R E N T T R A N S F E R R A T I OI F – INPUT CURRENT – mA V F – FORWARD VOLTAGE – VOLTSI F – F O R W A R D C U R R E N T – m A1.11.00.90.80.70.6N O R M A L I Z E D C U R R E N T T R A N S F E R R A T I OT A – TEMPERATURE – °C200015001000500T A – TEMPERATURE – °C t P – P R O P A G A T I O N D E L A Y – n s3.02.01.00.60.40.20.8R L – LOAD RESISTANCE – k Ωt P – P R O P A G A T I O N D E L A Y – µsT A – TEMPERATURE – °C101010100101010I O H – L O G I C H I G H O U T P U T C U R R E N T – n A∆I F ∆I O – S M A L L S I G N A L C U R R E N T T R A N S F E R R A T I O0.100.200.30I F – QUIESCENT INPUT CURRENT – mAFigure 11. Test Circuit for Transient Immunity and Typical Waveforms.Figure 10. Switching Test Circuit.Figure 9. Frequency Response.f – FREQUENCY – MHzN O R M A L I Z E D R E S P O N S E –d BAC INPUTOOI F = 15 pFt V I FOV V 0 VSWITCH AT B: I = 1.6 mA FV CMCCt r , t f = 16 ns/semiconductors For product information and a complete list of distributors, please go to our web site.For technical assistance call:Americas/Canada: +1 (800) 235-0312 or (916) 788-6763Europe: +49 (0) 6441 92460China: 10800 650 0017Hong Kong: (+65) 6756 2394India, Australia, New Zealand: (+65) 6755 1939 Japan: (+81 3) 3335-8152 (Domestic/Interna-tional), or 0120-61-1280 (Domestic Only) Korea: (+65) 6755 1989Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (+65) 6755 2044 Taiwan: (+65) 6755 1843Data subject to change.Copyright © 2004 Agilent Technologies, Inc. Obsoletes 5989-0792ENDecember 28, 20045989-2117EN。

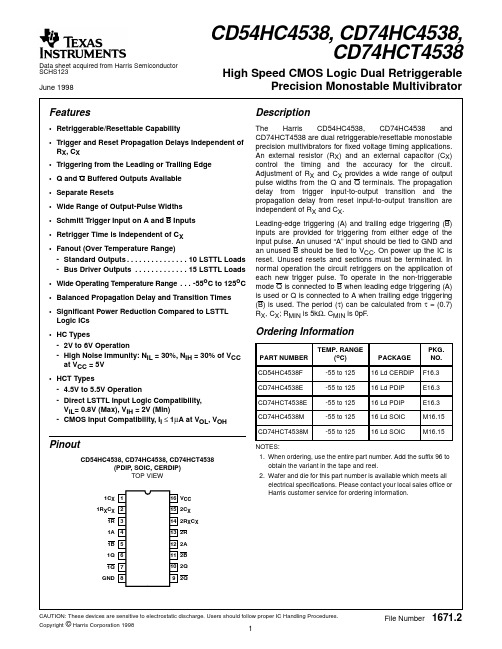

CD74HC4538中文资料

TEMP. RANGE

PART NUMBER

(oC)

PACKAGE

PKG. NO.

CD54HC4538F

-55 to 125 16 Ld CERDIP F16.3

CD74HC4538E

-55 to 125 16 Ld PDIP

E16.3

CD74HCT4538E

VCC

VCC

RX 2(14)

CX

1(15)

8

VCC

3(13) R

4(12) A

5(11) B

16 VCC

HIGH Z

VCC

D R1 R2 Q

CL FF CL

Q

VCC

R1

+ COMP II

-

R2

VCC

6(10) Q

7(9) Q

FIGURE 2. LOGIC DIAGRAM (1 MONO)

FUNCTIONAL TERMINAL CONNECTIONS

1

File Number 1671.2

元器件交易网 CD54HC4538, CD74HC4538, CD74HCT4538

Functional Diagram

1Cx 1Rx

1

2

VCC

1Cx 4 1A

1RxCx 6

1Q

5 1B

MONO 1

7 1Q

3 1R

13 2R

12 2A

元器件交易网

Data sheet acquired from Harris Semiconductor SCHS123 June 1998

CD54HC4538, CD74HC4538, CD74HCT4538

4538芯片

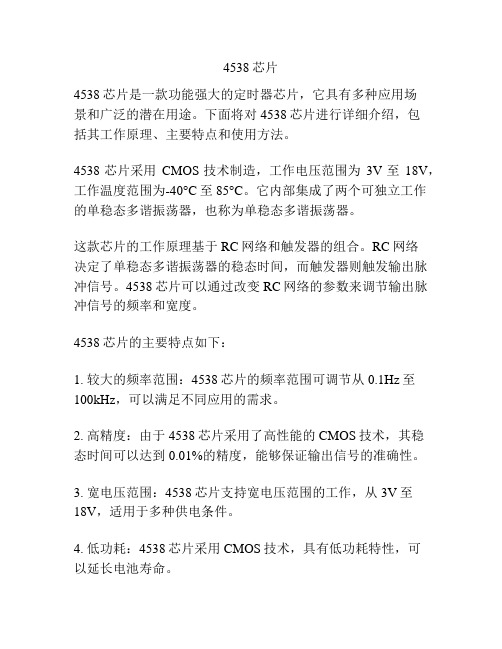

4538芯片4538芯片是一款功能强大的定时器芯片,它具有多种应用场景和广泛的潜在用途。

下面将对4538芯片进行详细介绍,包括其工作原理、主要特点和使用方法。

4538芯片采用CMOS技术制造,工作电压范围为3V至18V,工作温度范围为-40°C至85°C。

它内部集成了两个可独立工作的单稳态多谐振荡器,也称为单稳态多谐振荡器。

这款芯片的工作原理基于RC网络和触发器的组合。

RC网络决定了单稳态多谐振荡器的稳态时间,而触发器则触发输出脉冲信号。

4538芯片可以通过改变RC网络的参数来调节输出脉冲信号的频率和宽度。

4538芯片的主要特点如下:1. 较大的频率范围:4538芯片的频率范围可调节从0.1Hz至100kHz,可以满足不同应用的需求。

2. 高精度:由于4538芯片采用了高性能的CMOS技术,其稳态时间可以达到0.01%的精度,能够保证输出信号的准确性。

3. 宽电压范围:4538芯片支持宽电压范围的工作,从3V至18V,适用于多种供电条件。

4. 低功耗:4538芯片采用CMOS技术,具有低功耗特性,可以延长电池寿命。

5. 可编程输出:4538芯片的输出脉冲信号可以通过改变RC网络的参数进行编程,实现不同的输出频率和宽度。

4538芯片的使用方法相对简单,下面是一些基本的步骤:1. 连接电源:将4538芯片的VCC引脚连接到正电源,将GND引脚连接到地。

2. 设置参数:通过改变RC网络的参数来设置输出信号的频率和宽度。

可以通过改变电阻和电容的数值来实现。

3. 连接触发器:将4538芯片的触发器引脚连接到外部触发器,外部触发器可以是按钮、传感器或其他设备。

4. 获得输出:当触发器引脚接收到触发信号时,4538芯片会根据设置的参数生成相应的输出脉冲信号。

总之,4538芯片是一款功能强大且易于使用的定时器芯片,适用于多种应用场景。

它具有广泛的潜在用途,如电子钟、计时器、脉冲产生器等。

无论是在消费电子产品还是工业控制系统中,4538芯片都有着重要的作用。

cd4538芯片资料,中文

终止输出脉冲;不用的 RD 应接 VDD。但整个触发器不用时,器

RD 应接 Vss。

CC4538 提供了 16 引线多层陶瓷双列直插(D)、熔封陶瓷双列

直插(J)、塑料双列直插(P)和陶瓷片状载体(C)4 种封装形式。

推荐工作条件

引出端排列(俯视)

电源电压范围……………….3V~15V

输入电压范围………………..0V~VDD

工作温度范围

M 类……………….-55℃~125℃

E 类……………….-40℃~85℃

极限值 电源电压…...-0.5V~18V 输入电压……-0.5V~VDD+0.5V 输入电流…………….±10mA 储存稳定…………….-65℃~150℃

引出端功能符号

1Cext、2Cext 外接电容端

1Q、2Q

每个触发器具有上升沿触发输入(TR+)和下降沿( TR -),

TR+和 TR -带有施密特触发器,使上升和下降时间不受限制,不

用的 TR+应接 Vss;不用的 TR -应接 VDD。对于非可重触发方式

工作,当采用上升沿触发时(TR+), TR -应接至 Q ;当采用下

降沿触发时( TR -),TR+应接至 Q。直接复位 RD 处于低电平时,

mA µA µA

动态工作条件(TA=25℃) 参数

tw

TR+、 TR -、RD

VDD=5V 最小 最大 170 -

规范值 VDD=10V 最小 最大

90

-

VDD=15V 最小 最大

80

-

脉冲宽度 tr、tf 上升或下 RD

降时间

-

15

-

5

-

4

TR+

无限制

单位 ns µs µs

4538集成电路IC

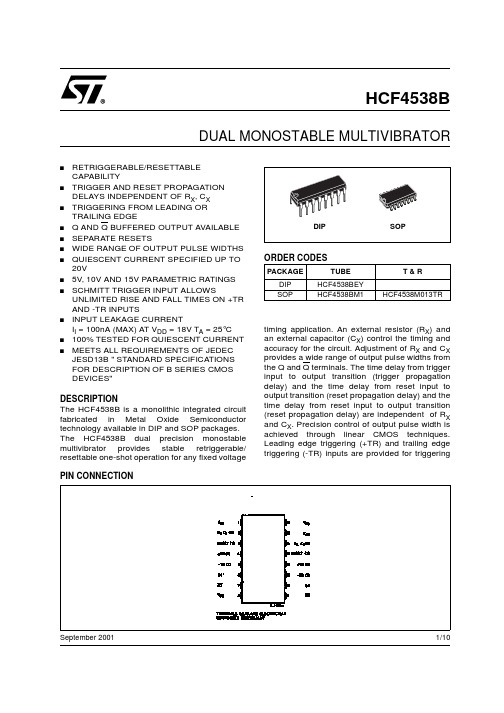

1/10September 2001sRETRIGGERABLE/RESETTABLE CAPABILITY s TRIGGER AND RESET PROPAGATION DELAYS INDEPENDENT OF R X , C X s TRIGGERING FROM LEADING OR TRAILING EDGE s Q AND Q BUFFERED OUTPUT AVAILABLE s SEPARATE RESETS s WIDE RANGE OF OUTPUT PULSE WIDTHS s QUIESCENT CURRENT SPECIFIED UP TO 20V s 5V, 10V AND 15V PARAMETRIC RATINGS s SCHMITT TRIGGER INPUT ALLOWSUNLIMITED RISE AND FALL TIMES ON +TR AND -TR INPUTS s INPUT LEAKAGE CURRENTI I = 100nA (MAX) AT V DD = 18V T A = 25°C s 100% TESTED FOR QUIESCENT CURRENT s MEETS ALL REQUIREMENTS OF JEDEC JESD13B " STANDARD SPECIFICATIONS FOR DESCRIPTION OF B SERIES CMOS DEVICES"DESCRIPTIONThe HCF4538B is a monolithic integrated circuit fabricated in Metal Oxide Semiconductor technology available in DIP and SOP packages. The HCF4538B dual precision monostable multivibrator provides stable retriggerable/resettable one-shot operation for any fixed voltage timing application. An external resistor (R X ) and an external capacitor (C X ) control the timing and accuracy for the circuit. Adjustment of R X and C X provides a wide range of output pulse widths from the Q and Q terminals. The time delay from trigger input to output transition (trigger propagation delay) and the time delay from reset input to output transition (reset propagation delay) and the time delay from reset input to output transition (reset propagation delay) are independent of R X and C X . Precision control of output pulse width is achieved through linear CMOS techniques.Leading edge triggering (+TR) and trailing edge triggering (-TR) inputs are provided for triggeringHCF4538BDUAL MONOSTABLE MULTIVIBRATORPIN CONNECTIONORDER CODESPACKAGE TUBE T & R DIP HCF4538BEY SOPHCF4538BM1HCF4538M013TRHCF4538B2/10from either edge of an input pulse. An unused +TR input should be tied to V SS . An unused -TR input should be tied to V DD . A RESET (on low level) is provided for immediate termination of the output pulse or to prevent output pulses when power is turned on. An unused RESET input should be tied to V DD . However, if an entire section of the HCF4538B is not used, its inputs must be tied to either V DD or V SS (see table 1). In normal operation the circuit triggers (extends the output pulse one period) on the application of each new trigger pulse. For operation in the non-retiggerable mode, Q is connected to -TR when leading edge triggering (+TR) is used or Q is connected to +TR when trailing edge triggering (-TR) is used. The time period (T) for this multivibrator can be calculated by : T = R X C X . The min. value of external resistance, R X , is 4K Ω. The max. and min. values of external capacitance, C X , are 100µF and 5nF, respectively. IINPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTerminals 1, 8, 15 are electrically connected internallyFUNCTIONAL DIAGRAMPIN No SYMBOL NAME AND FUNCTION 4, 12+TR Trigger Inputs (Low to High, Edge-Triggered)5, 11-TR Trigger Inputs (High to Low, Edge-Triggered)3, 13RESET Direct Reset Inputs (Active Low)1, 15C X 1, C X 2External Capacitor Con-nections2, 14R X C X 1R X C X 2External Resistor/Capaci-tor Connections 6, 10Q1, Q2Pulse Outputs7, 9Q1, Q2Complementary Pulse Outputs8V SS Negative Supply Voltage 16V DDPositive Supply VoltageHCF4538B3/10TABLE 1 : Functional Terminal ConnectionsA Retriggerable one-shot multivibrator has an output pulse width which is extended on full time period (T) after application of the last trigger pulse.A Non-Retriggerable one-shot multivibrator has a time period (T) referenced from the application of the firs trigger pulse.LOGIC DIAGRAMFUNCTIONV DD to Term. N °V SS to Term. N °Input Pulse to Term. N °Other ConnectionsMono (1)Mono (2)Mono (1)Mono (2)Mono (1)Mono (2)Mono (1)Mono (2)Leading Edge Trigger/Retriggerable3, 511, 13412Leading Edge Trigger/NonRetriggerable 3134125, 711, 9Trailing Edge Trigger/Retriggerable313412511Trailing Edge Trigger/NonRetriggerable3135114, 612, 10HCF4538B4/10LOGIC DIAGRAMABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied.All voltage values are referred to V SS pin voltage.RECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V DD Supply Voltage-0.5 to +22V V I DC Input Voltage -0.5 to V DD + 0.5V I I DC Input Current± 10mA P D Power Dissipation per Package200mW Power Dissipation per Output Transistor 100mW T op Operating Temperature -55 to +125°C T stgStorage Temperature-65 to +150°CSymbol ParameterValue Unit V DD Supply Voltage 3 to 20V V I Input Voltage0 to V DD V T opOperating Temperature-55 to 125°CHCF4538B5/10DC SPECIFICATIONSThe Noise Margin for both "1" and "0" level is: 1V min. with V DD =5V, 2V min. with V DD =10V, 2.5V min. with V DD =15VSymbolParameterTest ConditionValue UnitV I (V)V O (V)|I O |(µA)V DD (V)T A = 25°C -40 to 85°C -55 to 125°C Min.Typ.Max.Min.Max.Min.Max.I LQuiescent Current0/550.045150150µA0/10100.0410*******/15150.04206006000/20200.0810030003000V OHHigh Level Output Voltage0/5<15 4.95 4.95 4.95V0/10<1109.959.959.950/15<11514.9514.9514.95V OLLow Level Output Voltage5/0<150.050.050.05V10/0<1100.050.050.0515/0<1150.050.050.05V IHHigh Level Input Voltage 0.5/4.5<15 3.5 3.5 3.5V1/9<1107771.5/13.5<115111111V ILLow Level Input Voltage 4.5/0.5<15 1.5 1.5 1.5V9/1<11033313.5/1.5<115444I OHOutput Drive Current0/5 2.5<15-1.6-3.2-1.3-1.3mA0/5 4.6<15-0.51-1-0.42-0.420/109.5<110-1.3-2.6-1.1-1.10/1513.5<115-3.4-6.8-2.8-2.8I OLOutput Sink Current0/50.4<15-0.511-0.42-0.42mA 0/100.5<110-1.3 2.6-1.1-1.10/15 1.5<115-3.46.8-2.8-2.8I I Input Leakage Current0/18Any Input 18±10-5±0.1±1±1µA C IInput CapacitanceAny Input57.5pFHCF4538B6/10DYNAMIC ELECTRICAL CHARACTERISTICS (T amb = 25°C, C L = 50pF, R L = 200K Ω, t r = t f = 20 ns)(*) Typical temperature coefficient for all V DD value is 0.3 %/°C.(1) Minimum R X value = 4K Ω , minimum C X value = 5000 pFSymbolParameterTest ConditionValue (*)UnitV DD (V)Min.Typ.Max.t TLH t THL Transition Time5100200ns 1050100154080t PLH t PHL Propagation Delay Time+TR or -TR to Q or Q 5300600ns1015030015100200t PLH t PHL Propagation Delay TimeReset to Q or Q 5R L = 1K Ω250500ns101252501595190t WH t WLMinimum Input Pulse Width +TR, -TR or Reset 5R L = 1K Ω80140ns104080153060t WTOutput Pulse Width - Q or Q (C X = 0.005 µF, R X = 10K Ω (1))55760.664.5µs105558.963.0155559.163.5t WTOutput Pulse Width - Q or Q (C X = 0.1µF, R X = 100K Ω)59.49.9710.5ms109.49.9510.6159.510.010.6t WTOutput Pulse Width - Q or Q (C X = 10µF, R X = 100K Ω)50.95 1.0 1.06s100.95 1.0 1.06150.961.0 1.07t WPulse Width MatchBetween Circuits in Same Package : (100(T 1 - T 2)/T 1) (C X = 0.1µF, R X = 100K Ω) 5± 1%10± 115± 1t rrMinimum Retrigger Time50ns 100150C INInput CapacitanceAny Input57.5pFHCF4538B7/10TEST CIRCUITLR L = 200K ΩR T = Z OUT of pulse generator (typically 50Ω)WAVEFORM : PROPAGATION DELAY TIMES (f=1MHz; 50% duty cycle)HCF4538BInformation furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.© The ST logo is a registered trademark of STMicroelectronics© 2001 STMicroelectronics - Printed in Italy - All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia - Brazil - China - Finland - France - Germany - Hong Kong - India - Italy - Japan - Malaysia - Malta - MoroccoSingapore - Spain - Sweden - Switzerland - United Kingdom© 10/10。

74HC4538中文资料

GENERAL DESCRIPTION

The 74HC/HCT4538 are high-speed Si-gate CMOS devices and are pin compatible with “4538” of the “4000B” series. They are specified in compliance with JEDEC standard no. 7A.

Product specification

74HC/HCT4538

Fig.1 Pin configuration.

Fig.2 Logic symbol.

Fig.3 IEC logic symbol.

September 1993

3

元器件交易网

Philips Semiconductors

Philips Semiconductors

Dual retriggerable precision monostable multivibrator

Product specification

74HC/HCT4538

FEATURES

• Separate reset inputs • Triggering from leading or trailing edge • Output capability: standard • ICC category: MSI • Power-on reset on-chip

CH453手册

CH453 中文手册

3

5.3. 键盘扫描

CH453 的键盘扫描功能支持 8×8 矩阵的 64 键键盘。在键盘扫描期间,DIG7~DIG0 引脚用于列 扫描输出,SEG7~SEG0 引脚都带有内部下拉电阻,用于行扫描输入。

CH453 定期在显示驱动扫描过程中插入键盘扫描。在键盘扫描期间,DIG7~DIG0 引脚按照 DIG0 至 DIG7 的顺序依次输出高电平,其余引脚输出低电平;SEG7~SEG0 引脚的输出被禁止,当没有键被 按下时,SEG7~SEG0 都被下拉为低电平;当有键被按下时,例如连接 DIG3 与 SEG4 的键被按下,则 当 DIG3 输出高电平时 SEG4 检测到高电平;为了防止因为按键抖动或者外界干扰而产生误码,CH453 实行两次扫描,只有当两次键盘扫描的结果相同时,按键才会被确认有效。如果 CH453 检测到有效的 按键,则记录下该按键代码,并通过 INT#引脚产生低电平有效的键盘中断,此时单片机可以通过串 行接口读取按键代码;在没有检测到新的有效按键之前,CH453 不再产生任何键盘中断。CH453 不支 持组合键,也就是说,同一时刻,不能有两个或者更多的键被按下;如果多个键同时按下,那么按键 代码较小的按键优先。

CH453 所提供的按键代码为 7 位,位 2~位 0 是列扫描码,位 5~位 3 是行扫描码,位 6 是状态 码(键按下为 1,键释放为 0)。例如,连接 DIG3 与 SEG4 的键被按下,则按键代码是 1100011B 或者 63H,键被释放后,按键代码通常是 0100011B 或者 23H(也可能是其它值,但是肯定小于 40H),其中, 对应 DIG3 的列扫描码为 011B,对应 SEG4 的行扫描码为 100B。单片机可以在任何时候读取按键代码, 但一般在 CH453 检测到有效按键而产生键盘中断时读取按键代码,此时按键代码的位 6 总是 1,另外, 如果需要了解按键何时释放,单片机可以通过查询方式定期读取按键代码,直到按键代码的位 6 为 0。

ioThinx 4530 Series硬件用户手册说明书

ioThinx 4530 Series HardwareUser’s ManualVersion 1.1, August 2019/product© 2019 Moxa Inc. All rights reserved.ioThinx 4530 Series HardwareUser’s ManualThe software described in this manual is furnished under a license agreement and may be used only in accordance withthe terms of that agreement.Copyright Notice© 2019 Moxa Inc. All rights reserved.TrademarksThe MOXA logo is a registered trademark of Moxa Inc.All other trademarks or registered marks in this manual belong to their respective manufacturers.DisclaimerInformation in this document is subject to change without notice and does not represent a commitment on the part of Moxa.Moxa provides this document as is, without warranty of any kind, either expressed or implied, including, but not limited to, its particular purpose. Moxa reserves the right to make improvements and/or changes to this manual, or to the products and/or the programs described in this manual, at any time.Information provided in this manual is intended to be accurate and reliable. However, Moxa assumes no responsibility for its use, or for any infringements on the rights of third parties that may result from its use.This product might include unintentional technical or typographical errors. Changes are periodically made to the information herein to correct such errors, and these changes are incorporated into new editions of the publication.Technical Support Contact Information/supportMoxa AmericasToll-free: 1-888-669-2872 Tel: +1-714-528-6777 Fax: +1-714-528-6778Moxa China (Shanghai office) Toll-free: 800-820-5036Tel: +86-21-5258-9955 Fax: +86-21-5258-5505Moxa EuropeTel: +49-89-3 70 03 99-0 Fax: +49-89-3 70 03 99-99Moxa Asia-PacificTel: +886-2-8919-1230 Fax: +886-2-8919-1231Moxa IndiaTel: +91-80-4172-9088 Fax: +91-80-4132-1045Safety SymbolsNOTE Indicates a potential malfunction which, if not avoided, will not result in damage to property. INFORMATION This information is important for preventing errors.Table of Contents1.Preface .............................................................................................................................................. 1-1Revision History ................................................................................................................................. 1-2 Relevant Models ................................................................................................................................. 1-2 Package Contents ............................................................................................................................... 1-2 Usage Scenarios ................................................................................................................................. 1-2 Hardware and Software Requirements ................................................................................................... 1-3 Safety Precautions .............................................................................................................................. 1-3 Additional Resources ........................................................................................................................... 1-4 2.Product Overview .............................................................................................................................. 2-1Specifications ..................................................................................................................................... 2-2 Appearance ........................................................................................................................................ 2-2 Front View .................................................................................................................................. 2-2Physical Dimensions .................................................................................................................... 2-2 LED Indicators .................................................................................................................................... 2-3 3.Hardware Installation ....................................................................................................................... 3-1Wiring System and Field Power ............................................................................................................. 3-2 System Power ............................................................................................................................. 3-2Field Power ................................................................................................................................. 3-3 Wiring Ethernet Ports .......................................................................................................................... 3-3 Wiring Serial Port(s) ............................................................................................................................ 3-4 Serial Console (Debug Port) ................................................................................................................. 3-5 Grounding the Unit ............................................................................................................................. 3-8 Connecting the System Power Ground ........................................................................................... 3-8Connecting the Field Power Ground ............................................................................................... 3-8 Mounting the Unit ............................................................................................................................... 3-9 Installing the Unit on a DIN Rail .................................................................................................... 3-9Removing the Unit from a DIN Rail .............................................................................................. 3-10Installing Covers on the Device and the Right-Most I/O Module ....................................................... 3-11Removing a Cover from the Right-Most Module ............................................................................. 3-11Horizontal Installation ................................................................................................................ 3-12 Powering on the Unit ......................................................................................................................... 3-12 Reset Button: Factory Reset Process ................................................................................................... 3-121PrefaceIn this chapter, we explain the scope of and how to use this document.The following topics are covered in this chapter:❒Revision History❒Relevant Models❒Package Contents❒Usage Scenarios❒Hardware and Software Requirements❒Safety Precautions❒Additional ResourcesRevision HistoryVersion Change DateV1.0 First Release 2019-01-25Relevant ModelsThis document is only applicable to the models listed below.Model Name DescriptionioThinx 4533-LX Controller with Cortex-A7 1 GHz dual-core CPU, 512 MB RAM, 3-in-1 serial ports, LinuxOS, -20 to 60°C operating temperatureioThinx 4533-LX-T Controller with Cortex-A7 1 GHz dual-core CPU, 512 MB RAM, 3-in-1 serial ports, LinuxOS, -40 to 75°C operating temperaturePackage ContentsThe following items are included in the product package.•The ioThinx 4530 Series device•Quick installation guide (Printed)•Warranty cardUsage ScenariosThe ioThinx 4530 Series advanced controllers have the high computing power required to easily and securely upload field site data to the cloud. For cloud connectivity, the ioThinx 4530 comes with Azure, AWS, and Alibaba Cloud SDKs pre-installed.Users can take advantage of the built-in cloud examples, removing dependency on the libraries and toolchain configurations. For better control precision, the Moxa Industrial Linux operating system gives the ioThinx 4530 Series the capability to handle computations and control actions at the same time. In addition, the ioThinx 4530 Series helps manage data privacy, and supports both hardware privacy features, such as TPM (TrustedPlatform Module, which is optional), and software privacy features, such as secure boot, to help usersimplement cybersecurity protections. For users who are not proficient at using typical PLC programminglanguages, the ioThinx 4530 series supports C/C++ and Python, both of which provide more advancedprogramming options, to help users easily build their own applications.Hardware and Software Requirements You will need the following hardware and software to use the ioThinx 4530 Series.• A power source that provides 12 to 48 VDC, and power wires• A PC running Linux OS (we recommend Debian 9, Kernel 4.4) and an Ethernet cable•45MR/ML modules, if availableSafety PrecautionsPlease observe the following safety precautions when installing and using the ioThinx 4510 Series:Additional ResourcesRefer to the following documents for additional information.•Datasheets for the following products:ioThinx 4530 SeriesioThinx 4500 Series (45MR/ML) Modules•User’s Manual for the following products:ioThinx 4500 (45M) Module Series2Product OverviewIn this chapter, we give an overview of each ioThinx 4530 Series product.The following topics are covered in this chapter:❒Technical DataCommon Specifications❒AppearanceFront ViewPhysical Dimensions❒LED IndicatorsioThinx 4530 Series Hardware Product Overview SpecificationsNOTE The latest specifications for Moxa’s products can be found at https://. AppearanceFront ViewPhysical DimensionsioThinx 4530 Series Hardware Product Overview LED IndicatorsLabel Usage Qty Color ActionSP System Power 1 Green On: Power onOff: Power offFP Field Power 1 Green On: Power onOff: Power offRDY System (kernel) 1 Green/Red Green: System readyGreen (blinking): System is booting upRed: System error, or executing factorydefaultRed (blinking): Triggering factory default,or upgrading the firmware U1/U2 User defined 1 of each Green/Red User-definedSD microSD card 1 Green Green: SD card is insertedOFF: SD card is being accessedL1/L2 Ethernet 1 of each Green/Amber Green: 100MbAmber: 10MbBlinking: Data is being transmitted Off: InactiveP1/P2 Serial 1 of each Green/Amber Green: TxAmber: RxBlinking: Data is being transmitted Off: InactiveNOTE DO NOT DISCONNECT THE POWER OR NETWORK CABLE when the RDY LED is blinking.3Hardware InstallationIn this chapter, we describe how to install ioThinx 4530 Series products.The following topics are covered in this chapter:❒Wiring System and Field PowerSystem PowerField Power❒Wiring Ethernet Ports❒Wiring Serial Port(s)❒Serial Console (Debug Port)❒Grounding the UnitConnecting the System Power GroundConnecting the Field Power Ground❒Mounting the UnitInstalling the Unit on a DIN RailRemoving the Unit from a DIN RailInstalling Covers on the Device and the Right-Most I/O ModuleRemoving a Cover from the Right-Most ModuleHorizontal Installation❒Powering on the Unit❒Reset Button: Factory Reset ProcessWiring System and Field PowerWire range: 12 to 26 AWG (Ferrule diameter: 2.0 to 0.4 mm) Wire strip length: 10 mm Unit: mm (in.)NOTEPowering the unit requires connecting both the system and field power to the power supply. If only one of the power sources is connected, the device may not work properly.NOTEWe recommended using different power supplies to ensure that the system power and field power are isolated from each other. If using the same power supply for system power and field power, 3 KV or above isolation between them is recommended.System PowerThis device requires a 12 to 48 VDC system power input. The system power powers this device and the expansion modules via an internal bus, which is galvanically connected to the system power supply.The amount of system current required to support an expansion module is 1 A. If more modules and more power consumption is needed, an additional power module (45MR-7210) is required. Below is an example: • 10 x 45MR-1600 (59.4 mA) = 594 mA • 5 x 45MR-3810 (187 mA) = 935 mAThe total system current is 1.594 A, which is greater than 1 A. Therefore, an additional 45MR-7210 is needed.NOTE Install the 45MR-7210 to the left hand side of the module where the power consumption would be exceeded.NOTEWhen booting up the device in a low temperature environment, it may take up to two minutes until the device is up and running.NOTETo avoid damaging your devices, reset all power supplies connected to this device and 45MR-7210 modules at the same time.NOTEClick the following link to see how many 45MR-7210 power modules you will need to support your ioThinx 4500 Series project: Field PowerThis device provides 12/24 VDC field power input, which is a passive power supply without protection and the maximum current output is 2 A.NOTEThe 12/24 VDC field power supply can be connected directly to 45MR modules. If more connection points are needed, purchase 45MR-7820 (8 x FP+ and 8 x FP-) modules.Wiring Ethernet PortsThe maximum cable length of a 10/100BaseT connection is usually stated as 100 m (350 feet), but the actual limit for your application could be longer or shorter depending on the amount of electrical noise in the environment. To minimize the amount of noise, Ethernet cables should not run parallel to power cables or other types of cables that generate electrical noise. The following diagram and table shows the pin assignments for the RJ45 Ethernet ports:PinMedia Direct Interface Signal 1 Tx+ (transmit) 2 Tx- (transmit) 3 Rx+ (receive) 4 Not used 5 Not used 6 Rx- (receive) 7 Not used 8Not usedWiring Serial Port(s)Wire range: 16 to 28 AWG (Ferrule diameter: 1.2 to 0.3 mm) Wire strip length: 9.0 mm Unit: mm (in.)Pin RS-232 RS-422 RS-485 (P1/P2) 1 TXD TXD+ DATA1+ 2 RXDTXD- DATA1- 3 RTS RXD+ DATA2+ 4 CTS RXD- DATA2- 5GNDGNDGNDNOTEConnect the signal common pin (e.g. GND pin on the serial port pin assignment) between each of the serial device units. For insulated wire (shielding cable) that is used to reduce electrical noise, connect the cable shield drain wire to the chassis ground.NOTETo ensure that wires are securely connected to terminal block connectors, strip 7 to 9 mm of insulation off the ends of the wires before connecting them to the terminal block.Serial Console (Debug Port)The serial console gives users a convenient way of connecting to the programmable controllers. This method is particularly useful when using the computer for the first time. The serial console is also effective for connecting to the Moxa programmable controllers when you do not know target network settings and IP addresses.Step 1:Open the card coverConsole port for the ioThinx SeriesStep 2:Attach the 4-pin serial console cable to the console port. The following diagram shows the 4-pin serial connector and pin connections.Pin Assignment for the Serial Console PortSerial Console Default SettingsPin Definition 1 TxD 2RxD 3NC 4GNDParameter Value Baudrate 115200 bps Parity None Data bits 8 Stop bits 1 Flow Control None TerminalVT100We recommend using Moxa PComm Terminal Emulator to connect to the serial console. The following steps describe how to connect the console.1. Download Moxa PComm Lite from the Moxa website ( ).2. Install Moxa PComm Lite to the host Windows PC.3. Run PComm Lite Terminal Emulator from Start → Programs → PComm Lite Ver 1.x → TerminalEmulator .4.Click Profile Open.5.Specify which COM port is connecting to the Moxa controller, and then use the following configurationsettings: 115200, 8, none, 1.6.Click on the Terminal tab and configure the Terminal Type to VT100. Click OK to proceed.7.The serial console will be displayed on the terminal screen.Grounding the UnitThis device has two ground pins. One pin is for system power and the other pin is for field power. Connecting the System Power GroundThe system power ground connector is at the back of the unit. Once the device has been installed on a DIN rail, the system power ground connector will connect to the DIN rail.Connecting the Field Power GroundConnect the field power ground pin () to your field power ground.Mounting the UnitIn this section, we describe how to mount the device on a DIN rail and how to unmount the device from a DINrail.Installing the Unit on a DIN RailTake the following steps to install the unit on a DIN rail.Step 1: Hook the mounting clip of the unit onto the DIN rail, and then lower the clip onto the DIN rail. At least 55 mm of space above the DIN rail should be kept free to ensure that the installation can be done correctly.Step 2: Push the unit towards the DIN rail until the end of the mounting clip snaps into place.INFORMATION When the I/O module is inserted into the correct position, the connection between the internal bus and the previous module is established.Removing the Unit from a DIN RailTake the following steps to remove the unit from a DIN rail.Step 1: Use your finger to pull the release tab on the lower part of the module.Step 2: Press the release tab (item 1 in the figure) and then remove the CPU module from the DIN rail (item2 in the figure).NOTE Disconnect all connections, including Ethernet, serial, and power cables, from the device before removing the device from the DIN rail.Installing Covers on the Device and the Right-Most I/O ModuleInsert the covers on the left side of the device and on the right side of the I/O module that is installed furthest to the right. Make sure the covers cover the internal bus of the module.NOTE The covers provide protection against electrostatic discharge.Removing a Cover from the Right-Most ModuleBefore adding a new module to the right-most module, remove the cover first. Place your hand on the cover and slide it up as indicated in the diagram below.Horizontal InstallationBefore installing the device, ensure there is enough Array space around the device so that it can dissipate heat. Inorder to ensure the device works properly, we suggestreserving the space shown in the figure below.Powering on the UnitAfter turning on the power supply, it will take 5 to 10 seconds for the operating system to boot up. The greenReady LED will illuminate continuously until the operating system is ready.Reset Button: Factory Reset ProcessUse the following procedure to reset the ioThinx to the factory defaults. Note that when you reset the ioThinx,all of your tag definitions, software programs, and files will be deleted, and the service and runtime engine willbe restarted.1.Power off the device.2.Press and hold the reset button; while holding the reset button:a.Power on the device; the RDY LED will blink green while the device is booting up.b.After the device has booted up, the RDY LED will blink red; continue holding the reset button until theRDY LED stops blinking.3.Release the reset button to load the factory default settings.NOTE Do NOT power off, operate, or connect any devices when the RDY LED is a solid red. The factory reset functionis only activated when the system is booting up.NOTE It should take about 20 seconds from the time the RDY LED starts blinking green until it stops blinking red.。

HCF4538B

s RETRIGGERABLE/RESETT ABLECAPABILITYs TRIGGER AND RESET PROPAGATION DELAYS INDEPENDENT OF R X,C Xs TRIGGERING FROM LEADING ORTRAILING EDGEs Q AND Q BUFFERED OUTPUT AVAILABLE s SEPARATE RESETSs WIDE RANGE OF OUTPUT PULSE WIDTHS s QUIESCENT CURRENT SPECIFIED UP TO 20Vs5V,10V AND15V PARAMETRIC RATINGSs SCHMITT TRIGGER INPUT ALLOWS UNLIMITED RISE AND FALL TIMES ON+TR AND-TR INPUTSs INPUT LEAKAGE CURRENTI I=100nA(MAX)AT V DD=18V T A=25°Cs100%TESTED FOR QUIESCENT CURRENT s MEETS ALL REQUIREMENTS OF JEDEC JESD13B”STANDARD SPECIFICATIONSFOR DESCRIPTION OF B SERIES CMOSDEVICES”DESCRIPTIONThe HCF4538B is a monolithic integrated circuit fabricated in Metal Oxide Semiconductor technology available in DIP and SOP packages. The HCF4538B dual precision monostable multivibrator provides stable retriggerable/ resettable one-shot operation for any fixed voltage timing application.An external resistor(R X)and an external capacitor(C X)control the timing and accuracy for the circuit.Adjustment of R X and C X provides a wide range of output pulse widths from the Q and Q terminals.The time delay from trigger input to output transition(trigger propagation delay)and the time delay from reset input to output transition(reset propagation delay)and the time delay from reset input to output transition (reset propagation delay)are independent of R X and C X.Precision control of output pulse width is achieved through linear CMOS techniques. Leading edge triggering(+TR)and trailing edge triggering(-TR)inputs are provided for triggeringHCF4538BDUAL MONOSTABLE MULTIVIBRATORPIN CONNECTION ORDER CODESPACKAGE TUBE T&R DIP HCF4538BEYSOP HCF4538BM1HCF4538M013TRDIP SOP1/10September2001HCF4538B2/10from either edge of an input pulse.An unused +TR input should be tied to V SS .An unused -TR input should be tied to V DD .A RESET (on low level)is provided for immediate termination of the output pulse or to prevent output pulses when power is turned on.An unused RESET input should be tied to V DD .However,if an entire section of the HCF4538B is not used,its inputs must be tied to either V DD or V SS (see table 1).In normal operation the circuit triggers (extends the output pulse one period)on the application of each new trigger pulse.For operation in the non-retiggerable mode,Q is connected to -TR when leading edge triggering (+TR)is used or Q is connected to +TR when trailing edge triggering (-TR)is used.The time period (T)for this multivibrator can be calculated by :T =R X C X .The min.value of external resistance,R X ,is 4K Ω.The max.and min.values of external capacitance,C X ,are 100µF and 5nF,respectively.IINPUT EQUIVALENT CIRCUITPIN DESCRIPTIONTerminals 1,8,15are electrically connected internallyFUNCTIONAL DIAGRAMPIN No SYMBOL NAME AND FUNCTION 4,12+TR Trigger Inputs (Low to High,Edge-Triggered)5,11-TR Trigger Inputs (High to Low,Edge-Triggered)3,13RESET Direct Reset Inputs (Active Low)1,15C X 1,C X 2External Capacitor Con-nections2,14R X C X 1R X C X 2External Resistor/Capaci-tor Connections 6,10Q1,Q2Pulse Outputs7,9Q1,Q2Complementary Pulse Outputs8V SS Negative Supply Voltage 16V DDPositive Supply VoltageHCF4538B3/10TABLE 1:Functional Terminal ConnectionsA Retriggerable one-shot multivibrator has an output pulse width which is extended on full time period (T)after application of the last trigger pulse.A Non-Retriggerable one-shot multivibrator has a time period (T)referenced from the application of the firs trigger pulse.LOGIC DIAGRAMFUNCTIONV DD to Term.N °V SS to Term.N °Input Pulse to Term.N °Other ConnectionsMono (1)Mono (2)Mono (1)Mono (2)Mono (1)Mono (2)Mono (1)Mono (2)Leading Edge Trigger/Retriggerable3,511,13412Leading Edge Trigger/NonRetriggerable 3134125,711,9Trailing Edge Trigger/Retriggerable313412511Trailing Edge Trigger/NonRetriggerable3135114,612,10HCF4538B4/10LOGIC DIAGRAMABSOLUTE MAXIMUM RATINGSAbsolute Maximum Ratings are those values beyond which damage to the device may occur.Functional operation under these conditions is not implied.All voltage values are referred to V SS pin voltage.RECOMMENDED OPERATING CONDITIONSSymbol ParameterValue Unit V DD Supply Voltage -0.5to +22V V I DC Input Voltage -0.5to V DD +0.5V I I DC Input Current±10mA P D Power Dissipation per Package200mW Power Dissipation per Output Transistor 100mW T op Operating Temperature -55to +125°C T stgStorage Temperature-65to +150°CSymbol ParameterValue Unit V DD Supply Voltage 3to 20V V I Input Voltage0to V DD V T opOperating Temperature-55to 125°CHCF4538B5/10DC SPECIFICATIONSThe Noise Margin for both ”1”and ”0”level is:1V min.with V DD =5V,2V min.with V DD =10V,2.5V min.with V DD =15VSymbolParameterTest ConditionValue UnitV I (V)V O (V)|I O |(µA)V DD (V)T A =25°C -40to 85°C -55to 125°C Min.Typ.Max.Min.Max.Min.Max.I LQuiescent Current0/550.045150150µA0/10100.0410*******/15150.04206006000/20200.0810030003000V OHHigh Level Output Voltage0/5<15 4.95 4.95 4.95V0/10<1109.959.959.950/15<11514.9514.9514.95V OLLow Level Output Voltage 5/0<150.050.050.05V10/0<1100.050.050.0515/0<1150.050.050.05V IHHigh Level Input Voltage 0.5/4.5<15 3.5 3.5 3.5V1/9<1107771.5/13.5<115111111V ILLow Level Input Voltage 4.5/0.5<15 1.5 1.5 1.5V9/1<11033313.5/1.5<115444I OHOutput Drive Current0/5 2.5<15-1.6-3.2-1.3-1.3mA0/5 4.6<15-0.51-1-0.42-0.420/109.5<110-1.3-2.6-1.1-1.10/1513.5<115-3.4-6.8-2.8-2.8I OLOutput Sink Current0/50.4<15-0.511-0.42-0.42mA 0/100.5<110-1.3 2.6-1.1-1.10/15 1.5<115-3.46.8-2.8-2.8I I Input Leakage Current0/18Any Input 18±10-5±0.1±1±1µA C IInput CapacitanceAny Input57.5pFHCF4538B6/10DYNAMIC ELECTRICAL CHARACTERISTICS (T amb =25°C,C L =50pF,R L =200K Ω,t r =t f =20ns)(*)Typical temperature coefficient for all V DD value is 0.3%/°C.(1)Minimum R X value =4K Ω,minimum C X value =5000pFSymbolParameterTest ConditionValue (*)UnitV DD (V)Min.Typ.Max.t TLH t THL Transition Time5100200ns 1050100154080t PLH t PHL Propagation Delay Time+TR or -TR to Q or Q 5300600ns1015030015100200t PLH t PHL Propagation Delay TimeReset to Q or Q 5R L =1K Ω250500ns101252501595190t WH t WLMinimum Input Pulse Width +TR,-TR or Reset 5R L =1K Ω80140ns104080153060t WTOutput Pulse Width -Q or Q (C X =0.005µF,R X =10K Ω(1))55760.664.5µs105558.963.0155559.163.5t WTOutput Pulse Width -Q or Q (C X =0.1µF,R X =100K Ω)59.49.9710.5ms109.49.9510.6159.510.010.6t WTOutput Pulse Width -Q or Q (C X =10µF,R X =100K Ω)50.95 1.0 1.06s100.95 1.0 1.06150.961.0 1.07t WPulse Width MatchBetween Circuits in Same Package :(100(T 1-T 2)/T 1)(C X =0.1µF,R X =100K Ω) 5±1%10±115±1t rrMinimum Retrigger Time50ns 100150C INInput CapacitanceAny Input57.5pFHCF4538B7/10TEST CIRCUITC L =50pF or equivalent (includes jig and probe capacitance)R L =200K ΩR T =Z OUT of pulse generator (typically 50Ω)WAVEFORM :PROPAGATION DELAY TIMES (f=1MHz;50%duty cycle)HCF4538B8/10DIM.mm.inchMIN.TYP MAX.MIN.TYP.MAX. a10.510.020B0.77 1.650.0300.065 b0.50.020b10.250.010D200.787 E8.50.335e 2.540.100e317.780.700F7.10.280 I 5.10.201 L 3.30.130Z 1.270.050Plastic DIP-16(0.25)MECHANICAL DATAP001CHCF4538B9/10DIM.mm.inch MIN.TYPMAX.MIN.TYP.MAX.A 1.750.068a10.10.20.0030.007a2 1.650.064b 0.350.460.0130.018b10.190.250.0070.010C 0.50.019c145°(typ.)D 9.8100.3850.393E 5.86.20.2280.244e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208L 0.5 1.270.0190.050M 0.620.024S8°(max.)SO-16MECHANICAL DATAPO13HHCF4538BInformation furnished is believed to be accurate and reliable.However,STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringe ment of patents or other rights of third parties which may result from its use.No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics.Specifications mentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.©The ST logo is a registered trademark of STMicroelectronics©2001STMicroelectronics-Printed in Italy-All Rights ReservedSTMicroelectronics GROUP OF COMPANIESAustralia-Brazil-China-Finland-France-Germany-Hong Kong-India-Italy-Japan-Malaysia-Malta-MoroccoSingapore-Spain-Sweden-Switzerland-United Kingdom©http://w 10/10。

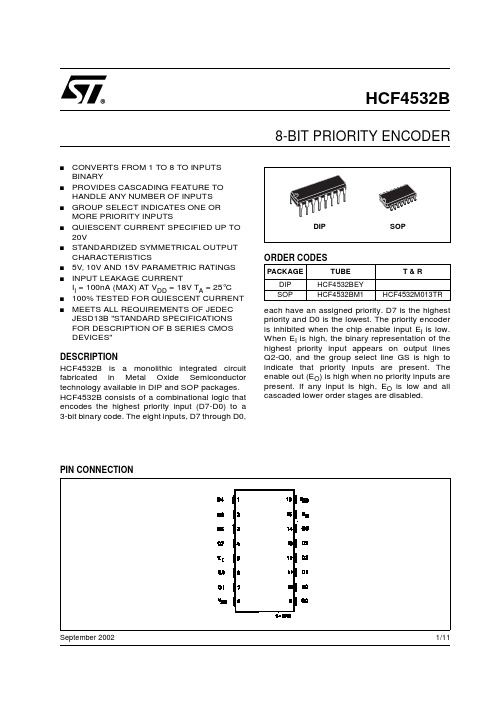

4532集成电路IC

8-BIT PRIORITY ENCODER

s CONVERTS FROM 1 TO 8 TO INPUTS BINARY

s PROVIDES CASCADING FEATURE TO HANDLE ANY NUMBER OF INPUTS

s GROUP SELECT INDICATES ONE OR MORE PRIORITY INPUTS

±10-5 ±0.1

±1

±1 µA

CI Input Capacitance

Any Input

5 7.5

pF

The Noise Margin for both "1" and "0" level is: 1V min. with VDD=5V, 2V min. with VDD=10V, 2.5V min. with VDD=15V

H

L

H

L

L

L

L

L

H

X

X

H

L

H

L

L

H

L

L

L

L

L

L

H

X

H

L

L

H

L

H

L

L

L

L

L

L

L

H

H

L

L

L

L

X : Don’t Care

2/11

LOGIC DIAGRAM

HCF4532B

ABSOLUTE MAXIMUM RATINGS

Symbol

Parameter

Value

Unit

VDD Supply Voltage

X : Don’t Care

M54HC4538中文资料

M54HC4538M74HC4538October 1993DUAL RETRIGGERABLE MONOSTABLE MULTIVIBRATORB1R(Plastic Package)ORDER CODES :M54HC4538F1R M74HC4538M1R M74HC4538B1R M74HC4538C1RF1R(Ceramic Package)M1R(Micro Package)C1R (Chip Carrier)PIN CONNECTIONS (top view)NC =No Internal Connecti o n.HIGH SPEEDt PD =25ns (TYP.)AT V CC =5V .LOW POWER DISSIPATIONSTANDBY STATEI CC =4µA (MAX.)AT T A =25°C ACTIVE STATE I CC =200µA (TYP.)AT V CC =5V .HIGH NOISE IMMUNITYV NIH =V NIL =28%V CC (MIN.).OUTPUT DRIVE CAPABILITY 10LSTTL LOADS.BALANCED PROPAGATION DELAYS t PLH =t PHL.WIDE OUTPUT PULSE WIDTH RANGE t WOUT =120ns ~60s OVER AT V CC =4.5V .OUTPUT PULSE WIDTH INDEPENDENT FROM TRIGGER INPUT PULSE WIDTH .PIN AND FUNCTION COMPATIBLE WITH 4538BThe M54/74HC4538is a high speed CMOS DUAL MONOSTABLEMULTIVIBRATOR fabricated in sili-con gate C 2MOS technology.It has the same high speed performance of LSTTL combined with true CMOS low power consumption.Each multivibrator features both a negative,A,and a positive,B,edge triggered input,either of which can be used as an in-hibit input.Also included is a clear input that when taken low resets the one shot.The monostable multivibrators are retriggerable.That is,they may be triggered reapeatedly while their outputs are gener-ating a pulse and the pulse will be extended.Pulse width stability over a wide range of temperature and supply is achieved using linear CMOS techniques.The output pulse equation is simply :PW =0.7(R)(C)where PW is in seconds,R in Ohms,and C is in Farads.All inputs are equipp ed with protection circuits against static discharge and transient excess volt-age.DESCRIPTION1/14M54/M74HC4538 SYSTEM DIAGRAMTIMING CHART2/14BLOCK DIAGRAMNotes:1.Cx,Rx,Dx are extern al comp onen ts.2.Dx is a clamp ing diode.3.The external capaci t or is charg ed to V CC in the stand-by state,i.e.no trigger.When the supp ly voltage is turned off Cx is discharge dmainlythroug h aninternal parasitic diode(see figures).IfCx is sufficiently largeandV CC dec rease s rapidy,there willbesome possibility of damag ing the I.C.with a surge current or latch-up.If the voltage supply filter capacit or is large enoug h and V CC decreas e slowly, the surge curren t is automatically limited and damag e the I.C.is avoided.The maximum forward current of the para sitic diode is ap-proxima tely20mA.In cases where Cx is large the time taken for the suppl y voltage to fall to0.4V CC can be calculated as follows: t f≥(V CC–0.7)⋅Cx/20mAIn cases where t f is too short an external champ ing diode is required to protect the I.C.from the surge curren t. FUNCTIONAL DESCRIPTIONSTAND-BY STATEThe external capacitor,Cx,is fully charged to V CC in the stand-by state.Hence,before triggering,tran-sistor Qp and Qn(connected to the Rx/Cx node)are both turned off.The two comparators that control the timing and the two reference voltage sources stop operating.The total supply current is therefore only leakage current.TRIGGER OPERATIONTriggering occurs when:1st)A is”low”and B has a falling edge;2nd)B is”high”and A has a rising edge;After the multivibrator has been retrigger ed com-parator C1and C2start operating and Qn is turned on.Cx then discharges through Qn.The voltage at the node Rx/Cx external falls.When it reaches V REFL the output of comparator C1 becomes low.This in turn resets the flip-flop and Qn is turned off.At this point C1stops functioning but C2continues to operate.The voltage at R/Cexternal begins to rise with a time constant set by the external components Rx,Cx.Triggering the multivibrator causes Q to go high after internal delay due to the flip-flop and the gate.Q re-mains high until the voltage at R/C external rises again to V REFH.At this point C2output goes low and G goes low.C2stops operatin g.That means that after triggering when the voltage at R/C external re-turns to V REFH the multivibrator has returned to its MONOSTABLE STATE.In the case where Rx•Cx are large enough and the discharge time of the ca-pacitor and the delay time in the I.C.can be ignored, the width of the output pulse tw(out)is as follows:t W(OUT)=0.72Cx•RxRE-TRIGGER OPERATIONWhen a second trigger pulse follows the first its ef-fect will depend on the state of the multivibrator.If the capacitor Cx is being charged the voltage level of Rx/Cx external falls to V REFL again and Q remains high i.e.the retrigger pulse arrives in a time shorter than the period Rx•Cx seconds,the capacitor charging time constant.If the second trigger pulse is very close to the initial trigger pulse it is ineffective ;i.e.,the second trigger must arrive in the capacitor discharge cycle to be ineffective.Hence the minimum time for a second trigger to be effective,trr(Min.)depend s on V CC and Cx.M54/M74HC45383/14RESET OPERATIONCD is normally high.If CD is low,the trigger is not effective because Q output goes low and trigger control flip-flop is reset.Also transistor Op is turned on and Cx is charged quicky to V CC.This means if CD input goes low,the IC becomes waiting state both in operating and non operatin g state.FUNCTIONAL DESCRIPTION(continued)TRUTH TABLEINPUTS OUTPUTSNOTEA B CD Q QH H OUTPUT ENABLEX L H L H INHIBITH X H L H INHIBITL H OUTPUT ENABLE X X L L H INHIBITINPUT AND OUTPUT EQUIVALENT CIRCUITPIN DESCRIPTIONPIN No SYMBOL NAME AND FUNCTION1,151T1,2T1External CapacitorConnections2,141T2,2T2External Resistor/CapacitorConnections3,131CD,2CD Direct Reset Inputs(ActiveLOW)4,121A,2A Trigger Inputs(LOW toHIGH,Edge-Triggered) 5,111B,2B Trigger Inputs(HIGH toLOW,Edge-Triggered) 6,10Q1,Q2Pulse Outputs7,9Q1,Q2Complementary Pulse Outputs 8GND Ground(0V)16V CC Positive Supply Voltage IEC LOGIC SYMBOLM54/M74HC4538 4/14ABSOLUTE MAXIMUM RATINGSSymbol Parameter Value Unit V CC Supply Voltage-0.5to+7V V I DC Input Voltage-0.5to V CC+0.5V V O DC Output Voltage-0.5to V CC+0.5VI IK DC Input Diode Current±20mAI OK DC Output Diode Current±20mAI O DC Output Source Sink Current Per Output Pin±25mAI CC or I GND DC V CC or Ground Current±50mAP D Power Dissipation500(*)mW T stg Storage Temperature-65to+150o C T L Lead Temperature(10sec)300o C Absolute Maximum Ratings are those values beyond whichdamage to the device may occu r.Functiona l ope ration und er these cond ition isnotimplied. (*)500mW:≅65o C derate to300mW by10mW/o C:65o C to85o CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Value Unit V CC Supply Voltage2to6V V I Input Voltage0to V CC V V O Output Voltage0to V CC VT op Operating Temperature:M54HC SeriesM74HC Series -55to+125-40to+85o Co Ct r,t f Input Rise and Fall Time(CLR only)V CC=2V0to1000nsV CC=4.5V0to500V CC=6V0to400C X External Capacitor NO LIMITATION(*)R X External Resistor V CC≤3V5K to1M(*)ΩV CC>3V1K to1M(*)(*)The maximum allowable values of Cx and Rx are a function of leakage of capa citor Cx,the leakage of device and leakage due to the board layout and surface resistance.Susce ptibility to externally induced noise may occur for Rx>1MΩM54/M74HC45385/14DC SPECIFICATIONSSymbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.V IH High Level InputVoltage 2.0 1.5 1.5 1.5V 4.5 3.15 3.15 3.156.0 4.2 4.2 4.2V IL Low Level InputVoltage 2.00.50.50.5V 4.5 1.35 1.35 1.356.0 1.8 1.8 1.8V OH High LevelOutput Voltage 2.0V I=V IHorV ILI O=-20µA1.92.0 1.9 1.9V 4.5 4.4 4.5 4.4 4.46.0 5.9 6.0 5.9 5.94.5I O=-4.0mA 4.18 4.31 4.13 4.106.0I O=-5.2mA 5.68 5.8 5.63 5.60V OL Low Level OutputVoltage 2.0V I=V IHorV ILI O=20µA0.00.10.10.1V 4.50.00.10.10.16.00.00.10.10.14.5I O=4.0mA0.170.260.370.406.0I O=5.2mA0.180.260.370.40I I Input LeakageCurrent 6.0V I=V CC or GND±0.1±1±1µAI I Input LeakageCurrent 6.0V I=V CC or GNDRext/Cext±0.1±1±1µAI CC Quiescent SupplyCurrent6.0V I=V CC or GND44080µAI CC Quiescent SupplyCurrent 2.0V I=V CC or GNDpins2,14V I=V CC/240120160µA 4.50.20.30.4mA 6.00.30.60.8mAM54/M74HC4538 6/14AC ELECTRICAL CHARACTERISTICS(C L=50pF,Input t r=t f=6ns)Symbol ParameterTest Conditions ValueUnit V CC(V)T A=25o C54HC and74HC-40to85o C74HC-55to125o C54HCMin.Typ.Max.Min.Max.Min.Max.t TLH t THL Output TransitionTime2.0307595110ns4.581519226.07131619t PLH t PHL PropagationDelay Time(A,B-Q,Q)2.0120250315375ns4.5305063756.025435464t PLH t PHL PropagationDelay Time(CD-Q,Q)2.0100195245295ns4.5253949596.020334250t WOUT Output PulseWidth 2.0C X=0R X=5KΩ540120015001800ns 4.5R X=1KΩ1802503203756.0R X=1KΩ1502002603202.0C X=0.01µFR X=10KΩ70839670967096µs 4.5697785698569856.0697785698569852.0C X=0.1µFR X=10KΩ0.670.750.830.670.830.670.9ms 4.50.670.730.770.670.770.670.86.00.670.730.770.670.770.670.8∆t WOUT Output PulseWidth ErrorBetween Circuits(In same pack)±1%t W(H) t W(L)Minimum PulseWidth(CLOCK)2.0307595110ns4.581519226.07131619t W(L)Minimum PulseWidth(CLEAR)2.0307595110ns 4.581519226.07131619t REM Minimum ClearRemoval Time 2.00151520ns 4.505576.0055t s MinimumRetrigger Time 2.0C X=0.1µFR X=1KΩ3806ns 4.5926.0722.0C X=0.01µFR X=1KΩ6µs 4.5 1.46.0 1.2C IN Input Capacitance5101010pFC PD(*)Power DissipationCapacitance 70pF(*)C PD is defined as the value of the IC’s internal equivalent capac itanc e which is calculated from the operating current con sump tion without load. (Refer toTest Circuit).Average operting current can be obtained by the followingequation.I CC(opr)=C PD•V CC•f IN+I CC‘•Duty/100+I CC/2(per circuit) (I CC‘=Active Supp ly Current)(Duty=%))M54/M74HC45387/14M54/M74HC4538TEST CIRCUIT I CC(Opr.)Output Pulse Width Constant K=Supply Voltage.INPUT WAVEFORM IS THE SAME AS THAT IN CASE OFSWITCHING CHARACTERISTICS TEST.t WOUT-Cx Characteristics(Typ).t rr-V CC Characteristics(Typ).8/14M54/M74HC4538 SWITCHING CHARACTERISTICS TEST WAVEFORM9/14M54/M74HC4538Plastic DIP16(0.25)MECHANICAL DATAmm inch DIM.MIN.TYP.MAX.MIN.TYP.MAX.a10.510.020B0.77 1.650.0300.065 b0.50.020b10.250.010D200.787 E8.50.335e 2.540.100e317.780.700F7.10.280I 5.10.201L 3.30.130Z 1.270.050P001C 10/14Ceramic DIP16/1MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX. A200.787 B70.276 D 3.30.130E0.380.015e317.780.700F 2.29 2.790.0900.110 G0.40.550.0160.022 H 1.17 1.520.0460.060 L0.220.310.0090.012 M0.51 1.270.0200.050 N10.30.406 P7.88.050.3070.317 Q 5.080.200P053DSO16(Narrow)MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX.A 1.750.068 a10.10.20.0040.007 a2 1.650.064 b0.350.460.0130.018 b10.190.250.0070.010 C0.50.019c145°(typ.)D9.8100.3850.393 E 5.8 6.20.2280.244 e 1.270.050e38.890.350F 3.8 4.00.1490.157G 4.6 5.30.1810.208 L0.5 1.270.0190.050 M0.620.024 S8°(max.)P013HPLCC20MECHANICAL DATAmm inchDIM.MIN.TYP.MAX.MIN.TYP.MAX. A9.7810.030.3850.395 B8.899.040.3500.356 D 4.2 4.570.1650.180 d1 2.540.100d20.560.022E7.378.380.2900.330 e 1.270.050e3 5.080.200F0.380.015G0.1010.004 M 1.270.050M1 1.140.045P027AInformation furnished is believed to be accurate and reliable.However,SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may results from its use.No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics.Specificationsmentioned in this publication are subject to change without notice.This publication supersedes and replaces all information previously supplied.SGS-THOMSON Microelectronics products are not authorized for use ascritical components in life support devices or systems without express written approval of SGS-THOMSON Microelectonics.©1994SGS-THOMSON Microelectronics-All Rights ReservedSGS-THOMSON Microelectronics GROUP OF COMPANIESAustralia-Brazil-France-Germany-Hong Kong-Italy-Japan-Korea-Malaysia-Malta-Morocco-The Netherlands-Singapore-Spain-Sweden-Switzerland-Taiwan-Thailand-United Kingdom-U.S.A。

74HCT4538中文资料

September 1993

5

元器件交易网

Philips Semiconductors

Dual retriggerable precision monostable multivibrator

Product specification

74HC/HCT4538

DC CHARACTERISTICS FOR 74HC

(1) Connect CTC (pins 1 and 15) to GND (pin 8).

Fig.5 Connection of the external timing components Rt and Ct.

(1) Positive edge triggering. (2) Positive edge retriggering (pulse

A LOW level at nRD terminates the output pulse immediately.

Schmitt-trigger action in the trigger inputs makes the circuit highly tolerant to slower rise and fall times.

74HC/HCT4538 Dual retriggerable precision monostable multivibrator

Product specification File under Integrated Circuits, IC06

September 1993

元器件交易网

nQ

H

↑

H

X

X

L

L

H

Notes

1. H = HIGH voltage level L = LOW voltage level X = don’t care ↑ = LOW-to-HIGH transition ↓ = HIGH-to-LOW transition = one HIGH level output pulse = one LOW level output pulse

CD4538BCM_NL中文资料

© 2002 Fairchild Semiconductor Corporation DS006000October 1987Revised April 2002CD4538BC Dual Precision MonostableCD4538BCDual Precision MonostableGeneral DescriptionThe CD4538BC is a dual, precision monostable multivibra-tor with independent trigger and reset controls. The device is retriggerable and resettable, and the control inputs are internally latched. Two trigger inputs are provided to allow either rising or falling edge triggering. The reset inputs are active LOW and prevent triggering while active. Precise control of output pulse-width has been achieved using lin-ear CMOS techniques. The pulse duration and accuracy are determined by external components R X and C X . The device does not allow the timing capacitor to discharge through the timing pin on power-down condition. For this reason, no external protection resistor is required in series with the timing pin. Input protection from static discharge is provided on all pins.Featuress Wide supply voltage range: 3.0V to 15V s High noise immunity:0.45 V CC (typ.)s Low power TTL compatibility:Fan out of 2 driving 74L or 1 driving 74LSs New formula:PW OUT = RC (PW in seconds, R in Ohms, C in Farads)s ±1.0% pulse-width variation from part to part (typ.)s Wide pulse-width range:1 µs to ∞s Separate latched reset inputss Symmetrical output sink and source capability s Low standby current: 5 nA (typ.) @ 5 V DC s Pin compatible to CD4528BCOrdering Code:Devices also available in T ape and Reel. Specify by appending the suffix letter “X” to the ordering code.Connection Diagram Top ViewTruth TableH = HIGH Level L = LOW Level↑ = Transition from LOW-to-HIGH ↓ = Transition from HIGH-to-LOW = One HIGH Level Pulse = One LOW Level Pulse X = IrrelevantOrder Number Package NumberPackage DescriptionCD4538BCM M16A 16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" Narrow CD4538BCWM M16B 16-Lead Small Outline Intergrated Circuit (SOIC), JEDEC MS-013, 0.300" Wide CD4538BCNN16E16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WideInputsOutputs Clear A B Q Q L X X L H X H X L H X X LLHH L↓ H↑H 2C D 4538B CBlock DiagramR X and C X are External Components V DD = Pin 16V SS = Pin 8Logic DiagramFIGURE 1.CD4538BC Theory of OperationFIGURE 2.Trigger OperationThe block diagram of the CD4538BC is shown in Figure 1, with circuit operation following.As shown in Figure 1 and Figure 2, before an input trigger occurs, the monostable is in the quiescent state with the Q output low, and the timing capacitor C X completely charged to V DD. When the trigger input A goes from V SS to V DD (while inputs B and C D are held to V DD) a valid trigger is recognized, which turns on comparator C1 and N-Channel transistor N1(1). At the same time the output latch is set. With transistor N1 on, the capacitor C X rapidly discharges toward V SS until V REF1 is reached. At this point the output of comparator C1 changes state and transistor N1 turns off. Comparator C1 then turns off while at the same time com-parator C2 turns on. With transistor N1 off, the capacitor C X begins to charge through the timing resistor, R X, toward V DD. When the voltage across C X equals V REF2, compara-tor C2 changes state causing the output latch to reset (Q goes low) while at the same time disabling comparator C2. This ends the timing cycle with the monostable in the qui-escent state, waiting for the next trigger.A valid trigger is also recognized when trigger inputB goes from V DD to V SS (while input A is at V SS and inputCD is at V DD)(2).It should be noted that in the quiescent state C X is fully charged to V DD, causing the current through resistor R X to be zero. Both comparators are “off” with the total device current due only to reverse junction leakages. An added feature of the CD4538BC is that the output latch is set via the input trigger without regard to the capacitor voltage. Thus, propagation delay from trigger to Q is independent of the value of C X, R X, or the duty cycle of the input wave-form.Retrigger OperationThe CD4538BC is retriggered if a valid trigger occurs(3) fol-lowed by another valid trigger(4) before the Q output has returned to the quiescent (zero) state. Any retrigger, after the timing node voltage at pin 2 or 14 has begun to rise from V REF1, but has not yet reached V REF2, will cause an increase in output pulse width T. When a valid retrigger is initiated(4), the voltage at T2 will again drop to V REF1 before progressing along the RC charging curve toward V DD. TheQ output will remain high until time T, after the last valid retrigger.Reset OperationThe CD4538BC may be reset during the generation of the output pulse. In the reset mode of operation, an input pulseon C D sets the reset latch and causes the capacitor to be fast charged to V DD by turning on transistor Q1(5). When the voltage on the capacitor reaches V REF2, the reset latch will clear and then be ready to accept another pulse. If theC D input is held low, any trigger inputs that occur will be inhibited and the Q and Q outputs of the output latch will not change. Since the Q output is reset when an input low level is detected on the C D input, the output pulse T can be made significantly shorter than the minimum pulse width specification. 4C D 4538B CFIGURE 3. Retriggerable Monostables CircuitryFIGURE 4. Non-Retriggerable Monostables CircuitryFIGURE 5. Connection of Unused SectionsCD4538BCAbsolute Maximum Ratings (Note 1)(Note 2)Recommended Operating Conditions (Note 2)Note 1: “Absolute Maximum Ratings ” are those values beyond which the safety of the device cannot be guaranteed, they are not meant to imply that the devices should be operated at these limits. The tables of “Recom-mended Operating Conditions ” and “Electrical Characteristics ” provide con-ditions for actual device operation.Note 2: V SS = 0V unless otherwise specified.DC Electrical Characteristics (Note 2)Note 3: I OH and I OL are tested one output at a time.DC Supply Voltage (V DD )−0.5 to +18 V DCInput Voltage (V IN )−0.5V to V DD + 0.5 V DCStorage Temperature Range (T S )−65°C to +150°CPower Dissipation (P D )Dual-In-Line 700 mW Small Outline 500 mWLead Temperature (T L )(Soldering, 10 seconds)260°C DC Supply Voltage (V DD ) 3 to 15 V DC Input Voltage (V IN )0 to V DD V DCOperating Temperature Range (T A )−55°C to +125°CSymbol ParameterConditions −55°C +25°C +125°C UnitsMinMax MinTyp Max MinMax I DDQuiescent V DD = 5V V IH = V DD 200.0055150µADevice CurrentV DD = 10V V IL = V SS400.01010300V DD = 15V All Outputs Open 800.01520600V OLLOW Level V DD = 5V |I O | < 1 µA0.0500.050.05VOutput VoltageV DD = 10V V IH = V DD , V IL = V SS 0.0500.050.05V DD = 15V 0.0500.050.05V OHHIGH Level V DD = 5V |I O | < 1 µA4.95 4.955 4.95VOutput VoltageV DD = 10V V IH = V DD , V IL = V SS9.959.95109.95V DD = 15V 14.9514.951514.95V ILLOW Level |I O | < 1 µAInput VoltageV DD = 5V, V O = 0.5V or 4.5V 1.5 2.25 1.5 1.5VV DD = 10V, V O = 1.0V or 9.0V 3.0 4.50 3.0 3.0V DD = 15V, V O = 1.5V or 13.5V4.06.75 4.0 4.0V IHHIGH Level |I O | < 1 µAInput VoltageV DD = 5V, V O = 0.5V or 4.5V 3.5 3.5 2.75 3.5VV DD = 10V, V O = 1.0V or 9.0V 7.07.0 5.507.0V DD = 15V, V O = 1.5V or 13.5V11.011.08.2511.0I OLLOW Level V DD = 5V, V O = 0.4V V IH = V DD 0.640.510.880.36mAOutput Current V DD = 10V, V O = 0.5V V IL = V SS1.6 1.32.250.9(Note 3)V D = 15V, V O = 1.5V 4.2 3.48.8 2.4I OHHIGH Level V DD = 5V, V O = 4.6V −0.6−0.51−0.88−0.36mA Output Current V DD = 10V, V O = 9.5V V IL = V SS−1.6−1.3−2.25−0.9(Note 3)V D = 15V, V O = 13.5V−4.2−3.4−8.8−2.4I IN Input Current,V DD = 15V, V IN = 0V or 15V ±0.02±10−5±0.05±0.5µA Pin 2 or 14I INInput Current V DD = 15V, V IN = 0V or 15V±0.1±10−5±0.1±1.0µAOther Inputs 6C D 4538B CAC Electrical Characteristics (Note 4)T A = 25°C, C L = 50 pF, and t r = t f = 20 ns unless otherwise specifiedNote 4: AC parameters are guaranteed by DC correlated testing.Note 5: The maximum usable resistance R X is a function of the leakage of the Capacitor C X , leakage of the CD4538BC, and leakage due to board layout,surface resistance, etc.Symbol ParameterConditionsMinTyp Max Unitst TLH , t THLOutput Transition TimeV DD = 5V 100200ns V DD = 10V 50100V DD = 15V4080t PLH , t PHLPropagation Delay TimeTrigger Operation —A or B to Q or Q V DD = 5V 300600nsV DD = 10V 150300V DD = 15V 100220Reset Operation —C D to Q or Q V DD = 5V 250500nsV DD = 10V 125250V DD = 15V95190t WL , t WHMinimum Input Pulse Width V DD = 5V 3570ns A, B, or C DV DD = 10V 3060V DD = 15V 2550t RRMinimum Retrigger TimeV DD = 5V 0ns V DD = 10V 00V DD = 15VC IN Input CapacitancePin 2 or 1410pF Other Inputs57.5PW OUTOutput Pulse Width (Q or Q)R X = 100 k ΩV DD = 5V 208226244µs(Note: For Typical Distribution,C X = 0.002 µFV DD = 10V 211230248see Figure 6)V DD = 15V 216235254R X = 100 k ΩV DD = 5V 8.839.6010.37ms C X = 0.1 µF V DD = 10V 9.029.8010.59V DD = 15V 9.2010.0010.80R X = 100 k ΩV DD = 5V 0.870.95 1.03s C X = 10.0 µFV DD = 10V 0.890.97 1.05V DD = 15V 0.910.99 1.07Pulse Width Match between R X = 100 k ΩV DD = 5V ±1%Circuits in the Same Package C X = 0.1 µF V DD = 10V ±1C X = 0.1 µF, R X = 100 k ΩV DD = 15V±1Operating Conditions R X External Timing Resistance 5.0(Note 5)k ΩC XExternal Timing CapacitanceNo LimitpFCD4538BCTypical ApplicationsFIGURE 6. Typical Normalized Distribution of Unitsfor Output Pulse WidthFIGURE 7. Typical Pulse Width Variation as aFunction of Supply Voltage V DDFIGURE 8. Typical Total Supply Current Versus Output Duty Cycle, R X = 100 k Ω, C L = 50 pF,C X = 100 pF, One Monostable Switching OnlyFIGURE 9. Typical Pulse Width ErrorVersus TemperatureFIGURE 10. Typical Pulse Width ErrorVersus TemperatureFIGURE 11. Typical Pulse Width VersusTiming RC Product 8C D 4538B CTest Circuits and WaveformsFIGURE 12. Switching Test Waveforms*C L = 50 pFInput Connections*Includes capacitance of probes, wiring, and fixture parasiticNote : Switching test waveforms for PG1, PG2, PG3 are shown in Figure 12.FIGURE 13. Switching Test CircuitCharacteristics CD A B t PLH , t PHL , t TLH , t THL V DDPG1V DDPW OUT , t WH , t WL t PLH , t PHL , t TLH , t THL V DDV SSPG2PW OUT , t WH , t WL t PLH(R), t PHL(R),PG3PG1PG2t WH , t WLCD4538BCTest Circuits and Waveforms (Continued)R X = R X ′ = 100 k ΩC X = C X ′ = 100 pF C 1 = C 2 = 0.1 µFDuty Cycle = 50%FIGURE 14. Power Dissipation TestCircuit and Waveforms 10C D 4538B CPhysical Dimensions inches (millimeters) unless otherwise noted16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150" NarrowPackage Number M16A16-Lead Small Outline Intergrated Circuit (SOIC), JEDEC MS-013, 0.300" WidePackage Number M16B CD4538BC Dual Precision MonostablePhysical Dimensions inches (millimeters) unless otherwise noted (Continued)16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300" WidePackage Number N16EFairchild does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and Fairchild reserves the right at any time without notice to change said circuitry and specifications.LIFE SUPPORT POLICYFAIRCHILD ’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:1.Life support devices or systems are devices or systemswhich, (a) are intended for surgical implant into thebody, or (b) support or sustain life, and (c) whose failureto perform when properly used in accordance withinstructions for use provided in the labeling, can be rea-sonably expected to result in a significant injury to theuser.2. A critical component in any component of a life support device or system whose failure to perform can be rea-sonably expected to cause the failure of the life support device or system, or to affect its safety or 元器件交易网。

74HC4538双通道可触发器

74HC/HCT4538- -双通道可再触发精确单稳态多频振荡器

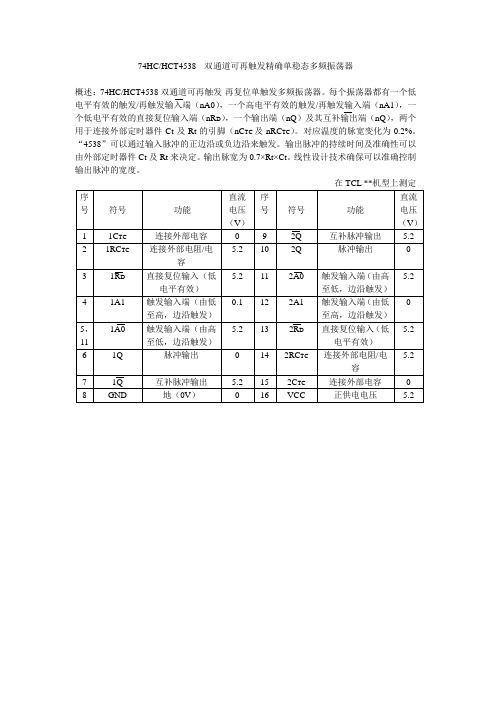

概述:74HC/HCT4538双通道可再触发-再复位单触发多频振荡器。

每个振荡器都有一个低电平有效的触发/再触发输入端(nA0),一个高电平有效的触发/再触发输入端(nA1),一个低电平有效的直接复位输入端(nR D),一个输出端(nQ)及其互补输出端(nQ),两个用于连接外部定时器件Ct及Rt的引脚(nC TC及nRC TC)。

对应温度的脉宽变化为0.2%。

“4538”可以通过输入脉冲的正边沿或负边沿来触发。

输出脉冲的持续时间及准确性可以由外部定时器件Ct及Rt来决定。

输出脉宽为0.7×Rt×Ct。

线性设计技术确保可以准确控制输出脉冲的宽度。

HC32L130_HC32L136系列用户手册Rev1.4

HC32L130系列/ HC32L136系列32位ARM® Cortex®-M0+ 微控制器用户手册前言非常感谢大家对华大半导体产品的支持和信赖。

使用本系列产品前,请系统阅读本手册和“数据手册”。

➢本手册的目的和对象读者本手册主要介绍本系列的功能、操作事项和使用方法。

对象读者为使用本系列实际开发产品的工程师。

※本手册介绍外设功能的构成和操作说明,但不包括该系列的规格说明。

关于芯片规格,详情参见其对应的“数据手册”。

➢样本程序和开发环境华大半导体提供外设功能运行用的样本程序和本系列所需的开发环境说明。

关于华大微控制器的运行规格和使用方法,请联系本公司。