微处理器的外部特性

微机原理 复习8086

地址 数据

CLK DEN VCC 8284 RES 外部复位信号 RESET RDY MN/MX CLK RESET READY 8086 BHE A19~A16 AD15~AD0 INTR S0 S1 S2

பைடு நூலகம்

INTA AMWC DT/R AIOWC ALE MRDC MWTC IORC 8288 IOWC BHE AB 存储器 8286 T OE DB I/O接口

• 8086指令队列的作用是什么? 答:作用是:在执行指令的同时从内存 中取了一条指令或下几条指令,取来的指 令放在指令队列中这样它就不需要象以往 的计算机那样让CPU轮番进行取指和执行的 工作,从而提高CPU的利用率。

EU

指令队列

BIU

8086CPU内部寄存器有哪几种?各自的特点 和作用是什么? 8086CPU有14个16位寄存器和8个8位寄 存器,可分为: 数据寄存器;指针和变址寄存器;段寄 存器;指令指针寄存器;标志寄存器。

• 为了实现寻址1MB存储器空间,8086CPU将 1MB的存储空间分成若干个逻辑段进行管理, 4个16位的段寄存器来存放每一个逻辑段的 段起始地址。

• 已知堆栈段寄存器(SS)=2400H,堆栈指 针(SP)=1200H,计算该堆栈栈顶的实际 地址,并画出堆栈示意图。 • (SS)=2400H,(SP)=1200H ;PA=(SS)×10H+(SP)= 2400H×10H +1200H = 25200H。

8086CPU 重新启动后,从何处开始执行指 令? • 答:重新启动后,CS=FFFFH,IP=0000H,故 从物理地址为FFFF0H 的位置开始执行指令 。

8086 系统中存储器采用什么结构?用 什么信号来选中存储体?

• 答:8086 系统中,存储器采用分体结构,1MB 的 存储空间分成两个存储体:偶地址存储体和奇地 址存储体,各为512KB。 • 使用A0 和BHE 来区分两个存储体。当A0=0 时,选 中偶地址存储体,与数据总线低8位相连,从低8 位数据总线读/写一个字节。当BHE =0 时,选中奇 地址存储体,与数据总线高8 位相连,从高8 位数 据总线读/写一个字节。 • 当A0=0,BHE =0 时,同时选中两个存储体,读/写 一个字。

微电子器件的噪声特性研究与降噪方法

微电子器件的噪声特性研究与降噪方法噪声是微电子器件中一个不可避免的问题,它对电路的性能和可靠性有着重要的影响。

因此,研究和降噪方法成为微电子器件设计和制造过程中的重要课题。

本文将探讨微电子器件的噪声特性研究以及常见的降噪方法。

一、噪声特性研究微电子器件的噪声可大致分为两类:内部噪声和外部噪声。

内部噪声是由于器件自身的结构和工作原理引起的,例如热噪声和亚米粒子噪声。

外部噪声则是来自于环境和其他电路的干扰。

1. 热噪声热噪声是由于器件内部电子的热运动引起的。

它与温度成正比,温度越高,热噪声越大。

热噪声是一种宽谱噪声,其功率密度与频率成正比。

研究热噪声的特性可以通过测量和分析器件的功率谱密度来实现。

2. 亚米粒子噪声亚米粒子噪声是由于电子,特别是载流子的随机撞击产生的。

它与电流的大小成正比。

亚米粒子噪声对于微电子器件来说是很重要的,特别是在低电流和小面积器件中。

它的功率谱密度与频率成反比关系。

3. 环境噪声环境噪声包括来自电源、通信系统和其他电子设备的干扰。

这些干扰信号往往具有特定的频谱特性,可以通过滤波器和屏蔽来减小其对微电子器件的影响。

二、降噪方法为了降低噪声对微电子器件性能的影响,人们开发了各种降噪方法。

以下是一些常见的降噪方法:1. 降低温度由于热噪声与温度成正比,因此降低器件的工作温度可以减小热噪声的影响。

这可以通过使用低温材料和制冷技术来实现。

例如,超导电路在低温下可以实现零电阻,从而降低热噪声的影响。

2. 优化器件结构优化器件的结构可以降低亚米粒子噪声的影响。

例如,通过调整器件的结构参数和优化接触电阻和载流子迁移率等因素,可以减小亚米粒子噪声引起的电流涨落。

3. 布局和屏蔽合理的布局设计和良好的屏蔽设计可以减小外部环境噪声对器件的影响。

通过将敏感部分和噪声源分离,并采用合适的屏蔽材料和技术,可以有效地降低外部噪声的干扰。

4. 信号处理技术信号处理技术可以对噪声信号进行滤波和去噪,从而减小噪声对微电子器件的影响。

stm32 外部晶振波形

stm32 外部晶振波形外部晶振是一种用于为微处理器系统提供时钟信号的重要元件。

在STM32系列芯片中,外部晶振可以提供更稳定和准确的时钟信号,从而确保芯片的正常运行。

本文将详细介绍STM32外部晶振的波形特性以及其在系统中的作用。

外部晶振通过其振荡电路产生一个固定频率的振荡信号,这个频率通常是非常精确的,并且可以通过更换晶振元件来实现不同的频率选择。

在STM32系列芯片中,常见的频率选择包括4MHz、8MHz、16MHz 等。

外部晶振在STM32系统中扮演着重要的角色,它提供了处理器的主时钟信号,控制着芯片内部各个模块的工作时序。

外部晶振的波形特性对系统的稳定性和可靠性有着至关重要的影响。

首先,让我们来看一下外部晶振的典型波形。

通常,外部晶振的波形是一个类似于正弦波的振荡信号,其频率由晶振元件的特性以及外部电路的参数来决定。

在STM32系统中,外部晶振的输入波形会经过芯片内部的时钟分频电路,最终形成供处理器使用的主时钟信号。

其次,外部晶振的波形特性对系统的稳定性和可靠性有着直接影响。

一个好的外部晶振应该具备以下几个方面的特点:稳定性高、频率准确、抗干扰能力强等。

当外部晶振频率不稳定或者受到干扰时,会直接影响到系统的时钟精度和运行稳定性,甚至导致系统无法正常工作。

为了确保外部晶振的稳定性和准确性,STM32系统内部通常会采用一定的电路设计和措施。

例如,可以在晶振引脚周围设置合适的滤波电路,以阻塞外部噪声干扰;或者采用多个晶振脚同时连接,以提高信号的冗余性和抗干扰能力。

此外,外部晶振还需要与处理器内部的其它模块进行时序同步,以确保数据的正确传输和处理。

在STM32系统中,通常会通过时钟树来实现各个模块的时钟分配和同步,从而实现整个系统的正常运行。

值得一提的是,外部晶振在系统中不仅仅是作为时钟信号源使用,还可以通过系统的时钟分频电路来生成其他的频率信号,例如用于串口通信的波特率时钟、用于定时中断的计数器时钟等。

片机基础知识:8051特点、结构与扩展

-8051特点、结构与扩展

1

1.1 8051单片机的特点 1.2 8051的内部结构 1.3 8051的系统扩展

1.1 8051单片机的特点

一、单机的概念

将组成微型计算机的各功能部件: 中央处理器、存储器、I/O接口电路及定时/计数器 等制作在一块集成电路芯片中从而构成完整的微型 计算机-故称作单晶片微型计算机, 简称单片机(Single chip microcomputer)。 或称微控制器(MCU:Microcontroller)

并行端口

串行端口

中断系统

P0 P1 P2 P3 TXD RXD

INT0 INT1

1、中央处理器CPU

CPU(Central Processing Unit)是计算机的核心部件, 它由运算器和控制器组成, 完成计算机的运算和控制功能。

运 算 器 又 称 算 术 逻 辑 部 件 ( ALU, Aithmctieal Logic Unit), 主要完成对数据的算术运算和逻辑运算。

INTEL公司将MCS51的核心技术授权给了很多其它 公司,所以有很多公司在做以8051为核心的单片机,当 然,功能或多或少有些改变,以满足不同的需求。

80C51系列单片机兼容的主要产品

* ATMEL公司带Flash存储器技术的AT89系列 * Philips公司的80C51、80C552系列 * 华邦公司的W78C51、W77C51高速低价系列 * ADI公司的ADμC8xx高精度ADC系列 * LG公司的GMS90/97低压高速系列 * Maxim公司的DS89C420高速(50MIPS)系列 * Cygnal公司的C8051F系列高速SOC单片机

(3)主流与多品种共存

DSP概述

号的处理。

5. 具有特殊的DSP指令

为了满足数字信号处理的需要,在DSP的指令系统 中,设计了一些完成特殊功能的指令。 如:TMS320C54x中的FIRS和LMS指令,专门用于 完成系数对称的FIR滤波器和LMS算法。

6.快速的指令周期

由于采用哈佛结构、流水线操作、专用的硬件乘 法器、特殊的指令以及集成电路的优化设计,使指令 周期可在6.6ns以下。如:TMS320F2812的运算速度 为150MIPS,即150百万条指令/秒。

7.硬件配置强

丰富的片上存储器类型:片内集成RAM、ROM、Flash 及双口RAM等存储空间; 丰富的片上外部设备:定时器、比较器、捕捉器、PWM 、异步串口、同步串口、DMA控制器、A/D和通用I/O口、 看门狗等; JTAG(Joint Test Action Group)标准测试接口(IEEE 1149标准接口):便于对DSP作片上的在线仿真。

外部存储 器接口

冯· 诺伊曼结构

(b)哈佛(Harvard)结构

该结构采用双存储空间,程序存储器和数据存储器分 开,有各自独立的程序总线和数据总线,可独立编址和独

立访问,可对程序和数据进行独立传输,使取指令操作、

指令执行操作、数据吞吐并行完成,大大地提高了数据处 理能力和指令的执行速度,非常适合于实时的数字信号处 理。微处理器的哈佛结构如下图所示。

数字信号处理的实现是用硬件、软件或软硬结合的 方法来实现各种算法。数字信号处理的实现一般有以下 几种方法:

专用DSP芯片

用基于通用DSP核的ASIC芯片实现。随着专用集成电 路ASIC(Application Specific Integrated Circuit)的广泛使用, 可以将DSP的功能集成到ASIC中。一般说来,DSP核是通 用DSP器件中的CPU部分,再配上用户所需的存储器(包括 Cache、RAM、ROM、FLASH、EPROM)和外设(包括串口、 并口、主机接口、DMA、定时器等),组成用户的ASIC。

2018年北京邮电大学电子与通信工程专硕招生专业目录、研究方向、考试科目、考试大纲、考研经验-新祥旭考研

2018年北京邮电大学电子与通信工程专硕考研招生专业目录、研究方向、考试科目、考试大纲、考研经验一、招生信息招生院系:电子工程学院招生人数:191招生专业:085208 电子与通信工程备注:此专业为专业学位二、研究方向01 (全日制)无线通信与电磁兼容、物联网与移动互联网02 (全日制)移动电子商务、无线通信与物联网、数据挖掘03 (全日制)移动互联网、未来通信、数据服务与网络应用04 (全日制)通信电子、卫星导航及多媒体05 (全日制)移动/卫星通信及电路设计、物联网与服务06 (全日制)射频天线、太赫兹通信07 (全日制)宽带融合网,智慧光子互联,空天地一体网络08 (全日制)射频技术、天线与电磁兼容、微波毫米波09 (全日制)电磁兼容与信息安全、认知网络与宽带通信10 (全日制)光电检测与光通信11 (全日制)认知无线电、智能信息处理12 (全日制)天线与电波传播13 (全日制)物联网与大数据14 (全日制)无线通信15 (全日制)微纳电子技术、智能通信、物联网与大数据16 (全日制)卫星移动通信、多媒体与物联网17 (全日制)宽带接入与网络融合技术18 (全日制)无线通信理论研究与应用19 (全日制)多媒体通信与集成电路技术20 (全日制)传感器网络技术21 (全日制)信息物理融合、智能人机交互、移动云计算22 (全日制)大气激光通信23 (全日制)无线通信、光纤通信、卫星与空间通信24 (全日制)移动互联网、通信网络及安全25 (全日制)电磁兼容、超宽带无线通信、移动互联网26 (全日制)宽带通信器件和系统、电磁兼容27 (全日制)生物信息学28 (全日制)电子信息处理与智能服务29 (全日制)纳米材料及器件30 (非全日制)授课地点:广东三、考试科目①101思想政治理论②201英语一③301数学一④801通信原理⑤802电子电路⑥804信号与系统⑦809微机原理与应用四、专业课考试大纲(1)801通信原理1、预备知识希尔伯特变换、解析信号、频带信号与带通系统、随机信号的功率谱密度、高斯白噪声、窄带平稳高斯过程、匹配滤波器。

第六章 存储器系统 微机原理 第2版 课后答案

第六章存储器系统本章主要讨论内存储器系统,在介绍三类典型的半导体存储器芯片的结构原理与工作特性的基础上,着重讲述半导体存储器芯片与微处理器的接口技术。

6.1 重点与难点本章的学习重点是8088的存储器组织;存储芯片的片选方法(全译码、部分译码、线选);存储器的扩展方法(位扩展、字节容量扩展)。

主要掌握的知识要点如下:6.1.1 半导体存储器的基本知识1.SRAM、DRAM、EPROM和ROM的区别RAM的特点是存储器中信息能读能写,且对存储器中任一存储单元进行读写操作所需时间基本上是一样的,RAM中信息在关机后立即消失。

根据是否采用刷新技术,又可分为静态RAM(SRAM)和动态RAM(DRAM)两种。

SRAM是利用半导体触发器的两个稳定状态表示“1”和“0”;DRAM是利用MOS管的栅极对其衬间的分布电容来保存信息,以存储电荷的多少,即电容端电压的高低来表示“1”和“0”;ROM的特点是用户在使用时只能读出其中信息,不能修改和写入新的信息;EPROM可由用户自行写入程序和数据,写入后的内容可由紫外线照射擦除,然后再重新写入新的内容,EPROM可多次擦除,多次写入。

一般工作条件下,EPROM 是只读的。

2.导体存储器芯片的主要性能指标(1)存储容量:存储容量是指存储器可以容纳的二进制信息量,以存储单元的总位数表示,通常也用存储器的地址寄存器的编址数与存储字位数的乘积来表示。

(2)存储速度:有关存储器的存储速度主要有两个时间参数:TA:访问时间(Access Time),从启动一次存储器操作,到完成该操作所经历的时间。

TMC:存储周期(Memory Cycle),启动两次独立的存储器操作之间所需的最小时间间隔。

(3)存储器的可靠性:用MTBF—平均故障间隔时间(Mean Time Between Failures)来衡量。

MTBF越长,可靠性越高。

(4)性能/价格比:是一个综合性指标,性能主要包括存储容量、存储速度和可靠性。

计算机组成原理 教学大纲

计算机组成原理教学大纲一、说明(一)课程性质学院平台必修课程,学习者需先修数字电路类课程,具备数字电路的基础知识。

该课程是后续操作系统、编译原理、接口技术等许多计算机专业课程的基础课。

(二)教学目的《计算机组成原理》是计算机科学与工程学院所有专业的专业必修主干课程,通过本课程的学习,使学生理解单处理机系统的组成结构以及各功能部件的组成和工作原理,让学生建立计算机的整机概念,初步具备设计简单计算机系统的能力,并对一些新技术、新产品以及计算机硬件的发展方向有一定的了解,为进一步学习本专业后继课程和进行有关的技术工作打下基础。

(三)教学内容计算机的主要组成部分、各部分的功能以及工作原理,主要内容包括运算方法和运算器、多层次存储体系、指令系统、中央处理器、总线系统、外围设备与输入输出系统等(四)教学时数72学时(五)教学方式课堂教学二、本文第一章计算机系统概论教学要点:本章是学习本门课程的基础。

目的是让学生对计算机的组成有一个全面的概括的了解。

了解硬件和软件的概念、计算机组成和计算机体系结构的不同。

掌握计算机系统的层次结构;准确画出计算机的硬件框图,并能解释其工作的过程;能深刻理解硬件的主要技术指标,并用这些技术指标描述常见硬件的性能。

教学时数:4学时教学内容:第一节计算机的分类(0.5学时)模拟计算机和电子计算机以及它们各自的特点。

第二节计算机的发展简史(1学时)计算机的五代变化、半导体存储器的发展、微处理器的发展、计算机的性能指标。

第三节计算机的硬件(1学时)硬件组成要素、运算器、存储器、控制器、适配器与输入输出设备。

第四节计算机的软件(1学时)软件的组成与分类、软件的发展演变。

第五节计算机系统的层次结构(0.5学时)多级组成的计算机系统、软件与硬件的逻辑等价性。

第二章运算方法和运算器教学要点:讲述数据和文字的表示、数据格式以及不同格式数据的基本运算方法、ALU电路的设计。

目的在于使学生了解计算机的基本运算过程。

微处理器系统结构与嵌入式系统设计教学大纲教案

《微处理器系统结构与嵌入式系统设计》教学大纲教案课程英文名称:Microcomputer System Theory and Embedded System Design课程代码:E0130340 学时数:64 学分数:4课程类型:学科基础课程适用学科专业:工学,仪器仪表类、电气类、电子信息类、自动化类、计算机类各专业以及机械类、测绘类、航空航天类、能源动力类、交通运输类、生物医疗工程类各相关专业先修课程:数字逻辑设计及应用,高级语言程序设计,软件技术基础执笔者:编写日期:审核人:一、课程简介本课程是工学电子电气信息工程及相关专业的学科基础课程,与实践类课程《微处理器系统与嵌入式系统综合设计》(课程代码:K0175010)互为配套课程。

本课程在阐述通用微处理器系统的架构、组成及工作原理的基础上,介绍了基于ARM CPU的、现代嵌入式微系统的设计与实现技术。

课程全面涵盖了微处理器、存储器、总线及接口等计算机子系统,重点体现了嵌入式系统/片上系统中硬件电路和软件程序的协同工作原理与设计方法,具体讲述了微处理器中数据通路、控制部件及指令的实现技术、分层存储器设计技术、输入/输出接口控制技术,以及ARM微处理器程序设计技术、异常处理技术,嵌入式系统引导程序设计、接口驱动程序设计及操作系统移植等内容。

This course is a basic subject-centered course in electrical and electronic information engineering and other related specialties. It will be helpful to understand the knowledge of the co-requisite experimental course K0175010 - Microprocessor and Embedded System Laboratory.The architecture, organization and operation principles of general-purpose microprocessor systems will be elaborated, as well as the design and implementation technology for current embedded microsystems based on ARM CPU. The subsystems in a computer, including microprocessor, memories, buses, input/output interfaces and others, will be completely involved. The primary goal of this course is to studying the cooperated relationship between the hardware and software in an embedded system or a System-on-Chip, by discussing in detail on the design method for data path and the controller inside CPU, the implementation technology for hierarchy storage system, the control mode for peripherals, and the program skill for APPs, exception handlers, boot codes, drivers and operating system transplantation, and so on.二、课程目标本课程旨在培养学生深入理解微处理器芯片与嵌入式系统的架构、组成及工作原理,熟练掌握现代嵌入式微系统中硬件电路和软件程序的基本分析、设计与实现方法。

名词解释微处理器

微处理器

微处理器是一种集成电路芯片,用于执行计算机程序中的指令和数据处理任务。

它是现代计算机系统中的核心组件之一。

微处理器通常由一个或多个中央处理单元(CPU)核心、内部高速缓存、控制单元和输入/输出接口等组成。

微处理器负责解码和执行计算机程序中的指令,这些指令包括算术、逻辑、数据移动和控制操作。

它通过与主存储器和其他外部设备进行交互,实现数据的读取、写入和传输。

微处理器还具有时钟系统,用于同步各个组件的操作,并确保指令按照正确的顺序执行。

微处理器的性能通常通过其时钟频率、指令集架构和核心数量等参数来衡量。

随着技术的不断进步,微处理器的速度和功能也得到了显著提升,使得计算机能够更快地执行复杂的任务,如图形渲染、视频编码和科学计算等。

微处理器广泛应用于各种计算设备,包括个人电脑、服务器、移动设备和嵌入式系统等。

它们在计算机领域扮演着至关重要的角色,推动了信息技术的发展和计算能力的提升。

1。

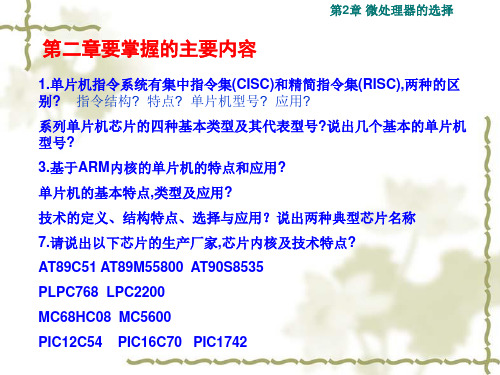

智能仪器第2章微处理器的选择

主要生产厂家? 代表性芯片?

第2章 微处理器的选择

AT89系列的主 要特点

第2章 微处理器的选择

1. 基本型单片机(Atmel公司的AT89系列)

3.精简增强型单片机(Philips公司的P87LPC900系列)

特点是无三总线构架,内部增加了许多功能部件,如 LCD段驱动器、模拟比较器、12C通信端口和看门狗定时 器等,其内部 Flash同时可作E2PROM使用,且内含RTC 日历时钟功能等。

P89LPC900系列基于6倍速的80C51兼容内核,内嵌 Flash程序存储器,可实现在应用编程(ClAP)/在系统编程 (ISP)和快速的2 ms页编程/擦除周期;包括512字节片内 E2PROM和768字节SRAM数据存储器;包括了16位捕获/ 比较/PWM、3 Mb/s的SPI和400 Kb/s的FC总线、增强型 DART、看门狗定时器和用户可选择的电源管理功能;带 有精度为±2.5%的内部振荡器。

第2章 微处理器的选择

3.高档型单片机(Silicon Lab公司的C8051F000系列)

Silicon Lab公司的C8051F系列单片机具有与 MCS 51单片机内核指令集完全兼容的微控制器。

C8051F系列单片机采用具有专利的CIP-51内 核,而Silicon Lab专利与MCS-5l单片机指令系统完 全兼容,运行速度高达25MIPS,除具有标准8051 的数字外设部件之外,片内还集成数据采集和控制 系统中常用的模拟部件和其他数字外设及功能部件。

MIPS (计算机) - 即Million Instructions Per Second(每秒百万条指令)

DSP技术与应用习题库 2

一、填空题第一章1.数字信号处理特点大量的实时计算(FIR、IIR、FFT),数据具有高度重复(乘积和操作在滤波、卷积和FFT中等常见)。

2.信号处理的作用信号改善、信号检测、估计等。

3.信号处理的方法信号波形分析/变换、滤波、现代谱估计/分析、自适应滤波等。

4.信息系统包括采集、传输、处理等。

5.数字信号处理常用算法有FIR滤波、IIR滤波、离散傅里叶变换、卷积等。

6.处理器速度的提高得益于器件水平、处理器结构、并行技术等。

7.DSP结构特点包括哈弗结构、流水线技术、硬件乘法器、多处理单元、特殊的DSP指令。

8.DSP芯片按用途分为通用型DSP 、专用型DSP 。

9.DSP芯片按数据格式分为浮点型、定点型。

第二章1.C28x芯片具有C27x目标-兼容模式、C28x 模式、C2xLP源-兼容模式。

2.C28x芯片模式选择由ST1 中的OBJMODE 和AMODE 位组合来选定模式。

3.CPU内核由CPU 、仿真逻辑、接口组成。

4.CPU主要特性是、、、、。

5.CPU信号包括存储器接口信号、时钟和控制信号、复位和中断信号仿真信号。

6.TMS320F2812组成特点是32位、定点、改进哈佛结构、循环的寻址方式。

7.存储器接口有 3 组地址总线。

8.存储器接口有 3 组数据总线。

9.存储器接口地址总线有PAB 、DRAB 、DWAB 。

9.存储器接口数据总线有PRDB 、DRDB 、DWDB 。

10.CPU中断控制寄存器有IFR 、IER 、DBGIER 。

11.ACC累加器是32 位的,可表示为ACC 、AH 、AL 。

12.被乘数寄存器是32 位的,可表示为XT 、T 、TL 。

13.乘数结果寄存器是32 位的,可表示为P 、PH 、PL 。

14.数据页指针寄存器16 位的,有65536页,每页有64 存储单元。

数据存储空间容量是4M字。

15.堆栈指针复位后SP指向地址是0x000400h 。

第三章1.DSP芯片内部包含存储器类型有、、、、。

MA86E L104 的单芯片微处理器 说明书

Version: 1.30This document information is the intellectual property of Megawin Technology.笙泉科技股份有限公司Megawin Technology Co., Ltd.MA86E/L104 说明书目录目录 (2)1.概叙 (5)2.功能 (6)3.方框图 (8)4.特殊功能寄存器 (9)4.1.SFR 图 (9)4.2.SFR 位分配 (10)4.3.辅助SFR 图(Page P) (11)4.4.辅助SFR 位分配(Page P) (12)5.引脚结构 (13)5.1.封装指南 (13)5.2.引脚定义 (14)6.8051 CPU 功能描叙 (15)6.1.CPU 寄存器 (15)6.2.CPU 时序 (16)6.3.CPU 寻址模式 (16)7.存储器组织 (18)7.1.程序存储器 (18)7.2.数据存储器 (19)7.3.关于C51编译器的声明标识符 (21)8.数据指针寄存器(DPTR) (22)9.系统时钟 (23)9.1.时钟结构 (23)9.2.时钟寄存器 (24)10.看门狗定时器(WDT) (26)10.1.WDT 结构 (26)10.2.WDT 在掉电模式和空闲模式期间 (26)10.3.WDT 寄存器 (27)10.4.WDT硬件选项 (28)11.系统复位 (29)11.1.复位源 (29)11.2.上电复位 (29)11.3.外部复位 (30)11.4.软件复位 (30)11.5.非法地址复位 (31)11.6.掉电检测器(Brown-Out)复位 (31)11.7.WDT 复位 (31)12.电源管理 (32)12.1.电源监控模块 (32)This document information is the intellectual property of Megawin Technology.12.2.1.慢频模式 (32)12.2.2.副频模式 (32)12.2.3.Watch 模式 (33)12.2.4.Monitor 模式(仅仅使用于L-系列) (33)12.2.5.空闲模式 (33)12.2.6.掉电模式 (33)12.2.7.中断唤醒掉电模式 (34)12.2.8.复位唤醒掉电模式 (34)12.2.9.KBI 键盘唤醒掉电模式 (35)12.3.电源控制寄存器 (36)13.输入输出口配置 (38)13.1.输入输出口结构 (38)13.1.1.端口3准双向口 (38)13.1.2.端口3推挽输出 (39)13.1.3.端口3仅是输入(高阻抗输入)模式 (39)13.1.4.端口3开漏输出 (40)13.1.5.通用端口集电极开漏输出结构 (40)13.1.6.通用端口推挽输出结构 (40)13.1.7.通用端口输入结构 (41)13.2.输入输出口寄存器 (42)13.2.1.端口1寄存器 (42)13.2.2.端口3寄存器 (43)13.2.3.端口4寄存器 (43)13.2.4.上拉控制寄存器 (44)14.中断 (45)14.1.中断结构 (45)14.2.中断源 (46)14.3.中断使能 (47)14.4.中断优先级 (47)14.5.中断处理 (48)14.6.TI的特别中断向量 (48)14.7.中断寄存器 (49)15.定时器/计数器 (53)15.1.定时器0 和定时器1 (53)15.1.1.模式0结构 (53)15.1.2.模式1 结构 (54)15.1.3.模式2 结构 (54)15.1.4.模式3 结构 (55)15.1.5.定时器0/1可编程时钟输出 (55)15.1.6.定时器0/1寄存器 (57)16.串行口(UART) (59)16.1.串行口模式0 (60)16.2.串行口模式1 (62)16.3.串行口模式2和模式3 (63)16.4.错误帧检测 (63)This document information is the intellectual property of Megawin Technology.16.6.自动地址识别 (64)16.7.波特率设置 (66)16.7.1.波特率模式0 (66)16.7.2.波特率模式2 (66)16.7.3.波特率模式1 和3 (66)16.8.串行口重复模式 (70)16.9.串行口寄存器 (71)17.键盘中断(KBI) (75)17.1.键盘中断结构图 (75)17.2.键盘中断寄存器 (75)18.ISP and IAP (77)18.1.闪存存储配置 (77)18.2.在系统可编程(ISP) (78)18.2.1.ISP/IAP 寄存器 (78)18.2.2.ISP操作描述 (80)18.2.3.ISP示例代码 (81)18.3.在应用编程(IAP) (82)18.3.1.IAP存储边界/范围 (82)18.3.2.更新IAP存储的数据 (82)19.P页特殊功能寄存器访问 (83)20.辅助特殊功能寄存器 (86)21.硬件选项 (88)22.应用说明 (90)22.1.电源电路 (90)22.2.复位电路 (90)22.3.XTAL 振荡电路 (91)22.4.ICP 接口电路 (92)22.5.在芯片编程功能 (93)23.电气特性 (94)23.1.最大绝对额定值 (94)23.2.直流特性 (95)23.3.外部时钟特性 (99)23.4.IHRCO 特性 (100)23.5.ILRCO 特性 (100)23.6.Flash 特性 (101)23.7.串行口时序特性 (101)24.指令集 (102)25.封装尺寸 (107)26.修订历史 (110)This document information is the intellectual property of Megawin Technology.1. 概叙MA86E/L104是基于80C51的高效1-T结构的单芯片微处理器,每条指令需要1~6 时钟信号 (比标准的8051快 6~7 倍), 与标准8051指令集兼容。

引脚与总线

8、CLK(Clock) 系统时钟,输入 系统通过该引脚给CPU提供内部定时信号

➢8086/8088的标准工作时钟为5MHz ➢IBM PC/XT机的8088采用了4.77MHz的时钟,

9

32

10

31

11

30

12

29

13

28

14

27

15

26

16

25

17

24

18

23

19

22

20

21

VCC AD15 A16 / S3 A17 / S4 A18 / S5 A19 / S6 BHE*/S7 MN / MX* RD* HOLD (RQ*/ GT0*) HLDA(RQ* /GT1*) WR* (LOCK*) M / IO* (S2*) DT / R* (S1*) DEN * (S0) ALE* (QS0) INTA* (QS1) TEST* READY RESET

最小模式下24~31引脚的信号定义如下:

1. 中断响应引脚

INTA(Interrupt Acknowledge)

CPU对可屏蔽中断进行响应,输出、低电平有效 CPU进入中断响应周期,发出的2个负脉冲,以通

知外设接口来自INTR引脚的中断请求已被CPU响 应,并作为中断向量号的读选通信号。

读写控制引脚

时钟周期:微机系统中统一的时钟信号CLK 的周期---由CPU的主频决定。时钟 周期是CPU处理动作的最小定时单 位

三者关系: 一个指令周期包含若干个总线周期; 一个基本总线周期需4个时钟周期, 称为4个“T状态”,T1、T2、T3、T4。

stm32 外部晶振波形

stm32 外部晶振波形一、简介外部晶振是嵌入式系统中常用的时钟源之一,它能够提供高精度的时钟信号,用于驱动处理器和其他外设。

stm32系列微控制器也支持外部晶振,本文将详细探讨stm32外部晶振的波形特性。

二、stm32外部晶振的接口stm32微控制器通常提供多个外部晶振接口,常见的有HSE(High Speed External)和LSE(Low Speed External)接口。

HSE接口适用于高速晶振,频率范围通常在4MHz到26MHz之间;LSE接口适用于低速晶振,频率范围通常在32.768kHz到100kHz之间。

三、stm32外部晶振的波形特性stm32外部晶振的波形特性对系统的时钟稳定性和性能有重要影响,下面将分别介绍HSE和LSE接口的波形特性。

3.1 HSE接口的波形特性HSE接口使用的是振荡电路,其波形特性如下:1.稳定性:HSE振荡器的稳定性决定了时钟信号的精度和准确性。

stm32微控制器通常采用外部负反馈电路来提高稳定性。

2.频率精度:HSE振荡器的频率精度取决于晶体的精度和振荡电路的设计。

一般来说,晶体的精度越高,振荡电路的设计越优秀,频率精度就越高。

3.启动时间:HSE振荡器的启动时间是指从电源施加到稳定输出的时间。

启动时间较长可能导致系统启动延迟,因此需要合理选择晶体和振荡电路设计。

3.2 LSE接口的波形特性LSE接口通常使用晶体振荡器,其波形特性如下:1.稳定性:LSE晶体振荡器的稳定性对于低速时钟信号的精度和准确性至关重要。

与HSE接口相比,LSE晶体振荡器的稳定性要求更高。

2.频率精度:LSE晶体振荡器的频率精度也取决于晶体的精度,但由于频率较低,振荡电路的设计对频率精度的影响较小。

3.启动时间:LSE晶体振荡器的启动时间相对较短,一般在几十毫秒到几百毫秒之间。

在系统上电时,需要等待LSE振荡器输出稳定的时钟信号后再使用。

四、stm32外部晶振的使用方法stm32微控制器使用外部晶振的方法如下:1.配置引脚:根据所选的外部晶振接口,将对应的引脚配置为晶振输入。

8086和825574LS373控制LED流水灯课设.

专 业

自动化

班 级

**

姓 名

**

设 计 起 止 日 期

2013.12.16~2013.12.20

设计题目:多路流水灯控制程序的设计

设计任务(主要技术参数):

按要求设计出模拟多路流水灯控制系统。通过8086系统总线单元和输入输出并行接口8255单元、74LS373以及LED显示单元进行连接,并应用所设计的程序使连接好的线路工作正常。

沈 阳 大 学

课程设计说明书NO.4

(1)8086的主要特性

Intel8086/8088CPU是Intel公司推出的高性能的微处理器,具体如下主要特性:

(a)8086CPU数据总线为16位,8088CUP数据总线为8位。

(b)地址总线都是20位,低16位用于数据总线复用,可直接寻址为1MB的存储空间。

LOOP $

DEC AH

CMP AH,02H

JZ START

ROR AL,1

JMP OBA2

沈 阳 大 学

课程设计说明书NO.11

OBA4:

MOV DX,00H

MOV AL,00FFH

OUT DX,AL

MOV CX,9FF0H

LOOP $

MOV CX,9FF0H

LOOP $

MOV DX,02H

OUT DX,AL

表2方式0下8255的16种输入输出组合a组b组a口pa0pa7c口pc4pc7b口pb0pb7c口pc0pc3入入入入入入入出入入出入入入出出入出入入入出入出入出出入入出出出出入入入出入入出出入出入出入出出出出入入出出入出出出出入出出出出74ls373主要功能74ls373是常用的地址锁存器芯片它实质是一个是带三态缓冲输出的8d触发器在单片机系统中为了扩展外部存储器通常需要一块74ls373芯片沈阳大学课程设计说明书图4内部结构和引脚介绍制造led的材料不同可以产生具有不同能量的光子借此可以控制led所发出光的波长也就是光谱或颜色

LTM4644四通道DC-DCμModule稳压器特性和典型应用

L TM4644四通道DC/DCμModule稳压器特性和典型应用文章来源:ictry样片申请网简介4输出降压型微型模块(µModule) 稳压器LTM4644,该器件可配置为单输出(16A)、双输出(12A、4A 或8A、8A)、三输出(8A、4A、4A) 或四输出(每输出4A) 的稳压器。

这种灵活性使系统设计师能够依靠一个简单和紧凑的微型模块稳压器满足FPGA、ASIC 和微处理器以及其他电路板电路的多种电压和负载电流要求。

LTM4644 稳压器包括DC/DC 控制器、电源开关、电感器和补偿组件,采用9mm x 15mm x 5.01mm BGA 封装。

仅需8 个外部陶瓷电容器(1206 或更小的外壳尺寸) 和 4 个反馈电阻器(0603 外壳尺寸) 就能调节 4 个可独立地调整并介于0.6V 至 5.5V 的输出。

单独的输入引脚使 4 个通道能够由4V 至14V 的不同电源轨或一个公共电源轨供电。

LTM4644 非常适用于通信、数据存储、工业、交通运输和医疗系统中的应用。

在55°C 的环境温度时,LTM4644 从12V 输入提供高达13A 电流和1.5V 输出,或在200LFM 气流时提供高达14A 电流。

4 个通道以90°的相位差工作,以在1MHz 缺省开关频率或同步至一个700kHz 至 1.3MHz 的外部时钟时,最大限度地降低输入纹波。

通过增加一个高于4V 的外部偏置电源,LTM4644 可在输入电源电压低至 2.375V 时调节输出。

该稳压器还包括输出过压和过流故障保护。

重点特性∙每路输出可提供4A 电流的四通道输出降压型μModule® 稳压器∙宽输入电压范围:4V 至14V2.375V 至14V (采用外部偏置)∙0.6V 至5.5V 输出电压∙每个通道可提供4A DC、5A 峰值输出电流∙高达5.5W 功率耗散(TA = 60ºC,200 LFM,无散热器)∙±1.5% 的总输出电压调节∙电流模式控制、快速瞬态响应∙可通过并联提供较高的输出电流∙输出电压跟踪∙内部温度检测二极管输出∙外部频率同步∙过压、过流和过热保护∙9mm x 15mm x 5.01mm BGA 封装典型应用LTM4644 是一款每路输出可提供4A 电流的四通道DC/DC 降压型μModule (微型模块) 稳压器。

ADC0808功能及简介

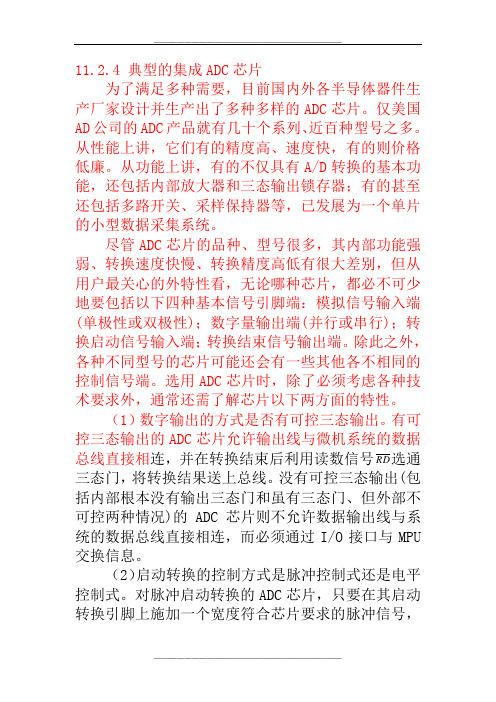

11.2.4 典型的集成ADC芯片为了满足多种需要,目前国内外各半导体器件生产厂家设计并生产出了多种多样的ADC芯片。

仅美国AD公司的ADC产品就有几十个系列、近百种型号之多。

从性能上讲,它们有的精度高、速度快,有的则价格低廉。

从功能上讲,有的不仅具有A/D转换的基本功能,还包括内部放大器和三态输出锁存器;有的甚至还包括多路开关、采样保持器等,已发展为一个单片的小型数据采集系统。

尽管ADC芯片的品种、型号很多,其内部功能强弱、转换速度快慢、转换精度高低有很大差别,但从用户最关心的外特性看,无论哪种芯片,都必不可少地要包括以下四种基本信号引脚端:模拟信号输入端(单极性或双极性);数字量输出端(并行或串行);转换启动信号输入端;转换结束信号输出端。

除此之外,各种不同型号的芯片可能还会有一些其他各不相同的控制信号端。

选用ADC芯片时,除了必须考虑各种技术要求外,通常还需了解芯片以下两方面的特性。

(1)数字输出的方式是否有可控三态输出。

有可控三态输出的ADC芯片允许输出线与微机系统的数据总线直接相连,并在转换结束后利用读数信号RD选通三态门,将转换结果送上总线。

没有可控三态输出(包括内部根本没有输出三态门和虽有三态门、但外部不可控两种情况)的ADC芯片则不允许数据输出线与系统的数据总线直接相连,而必须通过I/O接口与MPU 交换信息。

(2)启动转换的控制方式是脉冲控制式还是电平控制式。

对脉冲启动转换的ADC芯片,只要在其启动转换引脚上施加一个宽度符合芯片要求的脉冲信号,就能启动转换并自动完成。

一般能和MPU 配套使用的芯片,MPU 的I/O 写脉冲都能满足ADC 芯片对启动脉冲的要求。

对电平启动转换的ADC 芯片,在转换过程中启动信号必须保持规定的电平不变,否则,如中途撤消规定的电平,就会停止转换而可能得到错误的结果。

为此,必须用D 触发器或可编程并行I/O 接口芯片的某一位来锁存这个电平,或用单稳等电路来对启动信号进行定时变换。

DSP优势

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。

随着数字信号处理技术的日益推进,DSP领域的科技成果越来越普遍的应用于音频领域并大大的推动了音频科技的进步。

一、DSP的优势数字化的音频产品必将涉及将类比信号转换成数字信号后加以传输的问题。

而在这种转换的过程中需要做大量的数学运算,因此必须选择运算快速的微处理器才能完成实时的字信号处理。

而市面上的微处理有成百上千种,各有其特色及对应的应用场合,DSP以其特有的优势更适合音频领域。

DSP具有两条内部总线,一个是数据总线,一个是程序总线;而传统的微处理器内部只有一条总线供数据传输与程序执行使用;从上面我们已经看到ModifiedHarvard架构在大量数学运算方面有着强大的优势,在DSP内部具有硬件乘法器,大量的寄存器,目前最快的可在一个指令周期内完成32bit乘32bit的指令,而传统的微处理器运算系以微代码来执行,碰到乘法运算指令时就得消耗掉好几个指令周期,加上传统的微处理器中的寄存器较少,不得不经常从外部储存器传输数据来进行运算,而DSP指令具备重新执行功能,因此在数学运算速度超越一般传统的微处理器。

归纳起来DSP具备有以下的特点:内建乘法累加器;指令管线化;多总线与存储空间;循环寻址与位重新寻址;零负荷循环运算;晶片内含存储体与存储体介面。

总地说来与通用微处理器相比,DSP微处理器(芯片)有以下优缺点DSP优点:对元件值的容限不敏感,受温度、环境等外部参与影响小;容易实现集成;VLSI;可以分时复用,共享处理器;方论文联盟便调整处理器的系数实现自适应滤波;可实现模拟处理不能实现的功能:线性相位、多抽样率处理、级联、易于存储等;可用于频率非常低的信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

分类学习这40个引脚(总线)信号 1. 数据和地址引脚(20个) 2. 读写控制引脚(8个) 3. 中断请求和响应引脚(3个) 4. 总线请求和响应引脚(2个) 5. 其它引脚(7个)

第1.3章:1.3.1.2 最小组态的引脚信号

分类学习这40个引脚(总线)信号 1. 数据和地址引脚(20个)

8088

第1.3章:3. 中断请求和响应引脚

INTR(Interrupt Request)

可屏蔽中断请求,输入、高电平有效 有效时,表示请求设备向CPU申请可屏蔽 中断 该中断请求是否响应受控于标志寄存器中 的IF标志位(中断允许标志)、可以被屏 蔽掉

第1.3章:3. 中断请求和响应引脚(续1)

第1.3章:1.3.1.2 最小组态的引脚信号

分类学习这40个引脚(总线)信号 2. 读写控制引脚(8个)

ALE IO/M* WR* RD* READY DEN* DT/R* SS0*

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC AD15 AD16 / S3 AD17 / S4 AD18 / S5 AD19 / S6 SS0* (HIGH) MN / MX* RD* HOLD (RQ)*/ GT0*) HLDA (RQ1* /GT1*) WR* (LOCK*) M / IO ( S2* ) DT / R* ( S1* ) DEN ( S0 ) ALE INTA TEST* READY RESET

两种组态利用MN/MX*引脚区别

MN/MX*接高电平为最小组态模式 MN/MX*接低电平为最大组态模式

两种组态下的内部操作并没有区别

IBM PC/XT采用最大组态 本书以最小组态展开基本原理

通常在信号名称加 上划线(如:MX)或星号(如:MX*) 表示低电平有效

第1.3章:8088的引脚图

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC AD15 AD16 / S3 AD17 / S4 AD18 / S5 AD19 / S6 SS0* (HIGH) MN / MX* RD* HOLD (RQ)*/ GT0*) HLDA (RQ1* /GT1*) WR* (LOCK*) M / IO ( S2* ) DT / R* ( S1* ) DEN ( S0 ) ALE INTA TEST* READY RESET

8088

40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21

VCC AD15 AD16 / S3 AD17 / S4 AD18 / S5 AD19 / S6 SS0* (HIGH) MN / MX* RD* HOLD (RQ)*/ GT0*) HLDA (RQ1* /GT1*) WR* (LOCK*) M / IO ( S2* ) DT / R* ( S1* ) DEN ( S0 ) ALE INTA TEST* READY RESET

第1章

第1.3章:微处理器外部特性

教学重点

最小组态下的基本引脚 最小组态下的总线形成 最小组态下的总线时序

第1.3章:1.3.1 8088的引脚信号和总线形成

外部特性表现在其引脚信号上,学习 时请特别关注以下几个方面: ⑴ 引脚的功能 ⑵ 信号的流向 ⑶ 有效电平 ⑷ 三态能力

输出正常的低电平、高 电平外,还可以输出高 阻的第三态

8088

第1.3章:2. 读写控制引脚

ALE(Address Latch Enable)

地址锁存允许,输出、三态、高电平有效 ALE引脚高有效时,表示复用引脚:AD7 ~ AD0和A19/S6 ~ A16/S3正在传送地址信息 由于地址信息在这些复用引脚上出现的时 间很短暂,所以系统可以利用ALE引脚将 地址锁存到锁存器中,锁存器后面我们会 讲到

8088

第1.3章:1.3. 总线请求和响应引脚

HOLD

总线保持(即总线请求),输入、高电平 有效 有效时,表示总线请求设备向CPU申请占 有总线 该信号从有效回到无效时,表示总线请求 设备对总线的使用已经结束,通知CPU收 回对总线的控制权

第1.3章:1.3. 总线请求和响应引脚(续1)

HLDA(HOLD Acknowledge)

第1.3章:1.3.1.2 最小组态的引脚信号

分类学习这40个引脚(总线)信号 3. 中断请求和响应引脚(3个)

INTR INTA* NMI

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC AD15 AD16 / S3 AD17 / S4 AD18 / S5 AD19 / S6 SS0* (HIGH) MN / MX* RD* HOLD (RQ)*/ GT0*) HLDA (RQ1* /GT1*) WR* (LOCK*) M / IO ( S2* ) DT / R* ( S1* ) DEN ( S0 ) ALE INTA TEST* READY RESET

AD7 ~ AD0

A15 ~ A8

A19/S6 ~ A16/S3

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20

第1.3章:1. 数据和地址引脚

AD7 ~ AD0(Address/Data)

地址/数据分时复用引脚,双向、三态 在访问存储器或外设的总线操作周期中, 这些引脚在第一个时钟周期输出存储器或 I/O端口的低8位地址A7 ~ A0 其他时间用于传送8位数据D7 ~ D0

第1.3章:1. 数据和地址引脚(续1)

主机与外设进行数据交换通常采用可屏蔽中断

不可屏蔽中断通常用于处理掉电等系统故障

第1.3章:1.3.1.2 最小组态的引脚信号

分类学习这40个引脚(总线)信号 4. 总线请求和响应引脚(2个)

HOLD HLDA

GND A14 A13 A12 A11 A10 A9 A8 AD7 AD6 AD5 AD4 AD3 AD2 AD1 AD0 NMI INTR CLK GND 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 40 39 38 37 36 35 34 33 32 31 30 29 28 27 26 25 24 23 22 21 VCC AD15 AD16 / S3 AD17 / S4 AD18 / S5 AD19 / S6 SS0* (HIGH) MN / MX* RD* HOLD (RQ)*/ GT0*) HLDA (RQ1* /GT1*) WR* (LOCK*) M / IO ( S2* ) DT / R* ( S1* ) DEN ( S0 ) ALE INTA TEST* READY RESET

总线周期 存储器读

存储器写 I/O读

IO/M* 0

0 1

WR* 1

0 1

RD* 0

1 0

I/O写

1

0

1

第1.3章:2. 读写控制引脚(续4)

READY

存储器或I/O口就绪,输入、高电平有效 总线操作周期中,CPU会测试该引脚

如果测到高有效,CPU直接进入下一步 如果测到无效,CPU将插入等待周期

等待周期中仍然要监测READY信号,确定 是否继续插入等待周期

第1.3章:2. 读写控制引脚(续1)

IO/M*(Input and Output/Memory)

I/O或存储器访问,输出、三态 该引脚输出高电平时,表示CPU将访问I/O 端口,这时地址总线A15 ~ A0提供16位I/O 口地址 该引脚输出低电平时,表示CPU将访问存 储器,这时地址总线A19 ~ A0提供20位存储 器地址

INTA*(Interrupt Acknowledge)

可屏蔽中断响应,输出、低电平有效 有效时,表示来自INTR引脚的中断请求已 被CPU响应,CPU进入中断响应周期

第1.3章:3. 中断请求和响应引脚(续2)

NMI(Non-Maskable Interrupt)

不可屏蔽中断请求,输入、上升沿有效 有效表示外界向CPU申请不可屏蔽中断 该中断请求不能被CPU屏蔽,所以优先级 别高于INTR(可屏蔽中断)

第4章:什么是三态(Tristate)?

指引脚信号的定义、作用; 通常采用英文单词或其缩 写表示

信号从芯片向外输出, 还是从外部输入芯片 , 或者是双向的

起作用的逻辑电平 高、低电平有效上 升、下降边沿有效

三态是针对输出引脚的状态而言的 就是输出引脚可以处于以下三种状态中的任意一 种: 高电平(对应逻辑1)、 低电平(对应逻辑0)、 高阻态 高阻态相当于断路或悬空 芯片对这些引脚相当于放弃控制,让其他器件接 管