数据选择器 ppt课件

合集下载

《数据选择器》PPT课件

6

74LS151的真值表(功能表)

S=1时,选择器被封锁。 S为低电平使能端, 即S=0时,选择器正常工作。

2n -1

Y m i Di i0

Y = m0 D0 + m1 D1 + m2 D2 + m3 D3

+ m4 D4 + m5 D5 + m6 D6 + m7 D7

输入

D A2 A1 A0 S

A B C D A B C D A B C 1A B0 C A B C D

A B C D AC B 1AB 0C

与八选一数据选择器输出Y的表达式比较

15

F 2A B C D A B C D A B C 1A B0 C A B C D

A B C D AC B 1AB 0 C比较两式

YA 2A 1A 0D 0A 2A 1A 0D 1A 2A AA1A BB0 CCD 2 DD67A 2A 1A 100D 3

函数 ∑m(0, 3, 5, 6, 7) 也可以用四选一芯片来实现。

可见, 当逻辑函数的变量个数和数据选择器的地址 输入变量个数相同时,直接将逻辑函数输入变量有序 地与数据选择器的地址输入端连接即可。

若函数的变量数小于地址变量数, 应如何处理多余的数据选择器的地址输 入端 ?

13

对于一个组合逻辑函数, 可以根据它的最小项表达 式借助于MUX来实现它,当函数变量数等于地址输入 变量数时,方法如下: (1) 将给定函数化为最小项与或表达式。

量或反变量。

14

例 3-14 实现函数:

F 2 B C A B C D A B C D A B C A B D C D

解:首先将要实现的函数化成最小项表达式。即:

74LS151的真值表(功能表)

S=1时,选择器被封锁。 S为低电平使能端, 即S=0时,选择器正常工作。

2n -1

Y m i Di i0

Y = m0 D0 + m1 D1 + m2 D2 + m3 D3

+ m4 D4 + m5 D5 + m6 D6 + m7 D7

输入

D A2 A1 A0 S

A B C D A B C D A B C 1A B0 C A B C D

A B C D AC B 1AB 0C

与八选一数据选择器输出Y的表达式比较

15

F 2A B C D A B C D A B C 1A B0 C A B C D

A B C D AC B 1AB 0 C比较两式

YA 2A 1A 0D 0A 2A 1A 0D 1A 2A AA1A BB0 CCD 2 DD67A 2A 1A 100D 3

函数 ∑m(0, 3, 5, 6, 7) 也可以用四选一芯片来实现。

可见, 当逻辑函数的变量个数和数据选择器的地址 输入变量个数相同时,直接将逻辑函数输入变量有序 地与数据选择器的地址输入端连接即可。

若函数的变量数小于地址变量数, 应如何处理多余的数据选择器的地址输 入端 ?

13

对于一个组合逻辑函数, 可以根据它的最小项表达 式借助于MUX来实现它,当函数变量数等于地址输入 变量数时,方法如下: (1) 将给定函数化为最小项与或表达式。

量或反变量。

14

例 3-14 实现函数:

F 2 B C A B C D A B C D A B C A B D C D

解:首先将要实现的函数化成最小项表达式。即:

数电综合课件-数据选择器(MUX)

F = ABC+ABC+ABD+ABD+ACD。 解:這是一個四變數函數,對其一次降維後可 用74151實現,兩次降維後可用 ½ 74153實現。

CD AB 00 01 11 10

00 1 1

01

11

11 1

1

10 1 1 1

(a) 圖 4.2.28

C AB 0 1 降維D 00 1

01 1

11 D D 10 D 1

D5

D6 D7

A2~A0:地址輸入端; D7~D0 :數據輸入端; EN:使能端; Y:輸出端;

圖 4.2.22 ( b )簡化符號

EN 1 D0 D1 D2 D3

D4 D5 D6 D7

A0

1

1

A1

1

1

A2

1

1

& ≥1

Y 1Y

Vcc D4 D5 D6 D7 A0 A1 A2

16 15 14 13 12 11 10 9

0

(A<B) i

B0

B0

B4

B1

B1

F A<B

B5

B2

B2

B6

B3

B3

B7

圖 4.2.30

A0

A 1 7 48 5

A2

F A>B

A3

(A>B) i

(A=B) i F A=B

Байду номын сангаас

(A<B) i

B0

B1

F A<B

B2

B3

F A>B F A=B F A<B

(2) 並聯方式

A 15---12 B 15---12

CD AB 00 01 11 10

00 1 1

01

11

11 1

1

10 1 1 1

(a) 圖 4.2.28

C AB 0 1 降維D 00 1

01 1

11 D D 10 D 1

D5

D6 D7

A2~A0:地址輸入端; D7~D0 :數據輸入端; EN:使能端; Y:輸出端;

圖 4.2.22 ( b )簡化符號

EN 1 D0 D1 D2 D3

D4 D5 D6 D7

A0

1

1

A1

1

1

A2

1

1

& ≥1

Y 1Y

Vcc D4 D5 D6 D7 A0 A1 A2

16 15 14 13 12 11 10 9

0

(A<B) i

B0

B0

B4

B1

B1

F A<B

B5

B2

B2

B6

B3

B3

B7

圖 4.2.30

A0

A 1 7 48 5

A2

F A>B

A3

(A>B) i

(A=B) i F A=B

Байду номын сангаас

(A<B) i

B0

B1

F A<B

B2

B3

F A>B F A=B F A<B

(2) 並聯方式

A 15---12 B 15---12

数据选择器(MUX) 数电课件

端(低电平D有2效n )1,L。,D;1,D个0选择控制n 端

E

; 个输入 Y 2n

;A此n外1,L,还,有A一1,个A使0能端

二、4选1数据选择器(4—1MUX) 1. 逻辑功能

4—1MUX的逻辑功能是在两位选择控制信号的作用下,从4个输入信号中选择1个,送 至输出端。

2. 框图

A2

A1

A0

D6

A2 A1 A0D7

(公式4.3.2)

四、中规模集成数据选择器

8—1MUX 74LS151 的引脚图如图4.3.4—1所示。

图4.3.4—1

双4—1MUX 74LS153的引脚图如图4.3.4—2所示。 图4.3.4—2

五、数据选择器的应用 1. 数据选择器的级联

表4.3.2—1

5. 逻辑函数表达式

4—1MUX的逻辑函数表达式为

Y E A1 A0D0 E A1 A0D1 EA1 A0D2 EA1 A0D3

E A1 A0D0 A1A0D1 A1 A0D2 A1A0D3

6. 功能表(简化的真值表)

4—1MUX的功能表如表4.3.2—2所示。

图4.3.3—1

3. 功能表

8—1MUX的功能表如表4.3.3—1所示。

表4.3.3—1

4. 逻辑函数表达A2

A1

A0 D0

A2

A1A0 D1

Y

E

A2

A1

A0

D2

A2 A1A0D3

A2 A1 A0D4 A2 A1A0D5

4. 画出连线图如下图所示。 返回

E

; 个输入 Y 2n

;A此n外1,L,还,有A一1,个A使0能端

二、4选1数据选择器(4—1MUX) 1. 逻辑功能

4—1MUX的逻辑功能是在两位选择控制信号的作用下,从4个输入信号中选择1个,送 至输出端。

2. 框图

A2

A1

A0

D6

A2 A1 A0D7

(公式4.3.2)

四、中规模集成数据选择器

8—1MUX 74LS151 的引脚图如图4.3.4—1所示。

图4.3.4—1

双4—1MUX 74LS153的引脚图如图4.3.4—2所示。 图4.3.4—2

五、数据选择器的应用 1. 数据选择器的级联

表4.3.2—1

5. 逻辑函数表达式

4—1MUX的逻辑函数表达式为

Y E A1 A0D0 E A1 A0D1 EA1 A0D2 EA1 A0D3

E A1 A0D0 A1A0D1 A1 A0D2 A1A0D3

6. 功能表(简化的真值表)

4—1MUX的功能表如表4.3.2—2所示。

图4.3.3—1

3. 功能表

8—1MUX的功能表如表4.3.3—1所示。

表4.3.3—1

4. 逻辑函数表达A2

A1

A0 D0

A2

A1A0 D1

Y

E

A2

A1

A0

D2

A2 A1A0D3

A2 A1 A0D4 A2 A1A0D5

4. 画出连线图如下图所示。 返回

第10讲 数据选择器

1) 4选1数据选择器 选 数据选择器 (1) 基本设计思想。 基本设计思想。 4选1数据选择器的基本设计思想是将 MUX等效为一个单刀多掷开关 , 并通过开关 等效为一个单刀多掷开关, 等效为一个单刀多掷开关 的转换,将多路数据的输入有选择地传输出去。 的转换,将多路数据的输入有选择地传输出去。

Y0 数 据 D 输 入 Y1 Y2 Y3 数 据 输 出

A1

A0

图4.5.1 4路数据分配器的功能图 路数据分配器的功能图

4.5.2 数据选择器(Multiplexer) 数据选择器 1.数据选择器 数据选择器 从多路数据中选择某一路数据输出的逻辑电 路称为“ 数据选择器” 简称MUX, 或称 “ 多 路称为 “ 数据选择器 ” , 简称 , 或称“ 路调制器” 、 “ 多路开关” 。 同样, MUX也相 路调制器 ” 多路开关 ” 同样 , 也相 当于一个单刀多掷开关, 当于一个单刀多掷开关,但其逻辑功能正好与数 据分配器相反。常用的MUX有2选1、4选1、8选 据分配器相反。常用的 有 选 、 选 、 选 1、 16选 1等 。 如对 、 选 等 如对MUX的功能进行扩展 , 还可 的功能进行扩展, 的功能进行扩展 得到32选 、 选 等选择器 下面以4选 为例 等选择器。 为例, 得到 选1、64选1等选择器。下面以 选1为例, 来说明MUX的功能。 的功能。 来说明 的功能

如果令8选 的地址变量为逻辑变量, 如果令 选 1MUX的地址变量为逻辑变量 , 的地址变量为逻辑变量 则可列出F和 的真值表如表 即 A2A1A0=ABC,则可列出 和 Y的真值表如表 则可列出 4.5.3所示。 所示。 所示 由真值表可知: 由真值表可知:只要令 D3=D5=D6=D7=1 D0=D1=D2=D4=0 就可用8选 来产生上述函数了, 就可用 选 1MUX来产生上述函数了 , 其 来产生上述函数了 逻辑图如图4.5.6所示。 所示。 逻辑图如图 所示

《数据选择器》课件

VS

详细描述

分布式数据选择器由多个数据选择器组成 ,每个数据选择器具有独立的选择信号和 数据输入/输出端口。通过将各个数据选 择器的数据输出端口连接起来,可以实现 数据的分布式处理和传输。分布式数据选 择器具有灵活性和可扩展性,适用于大规 模数据处理和复杂系统。

可编程数据选择器

总结词

可编程数据选择器是一种可以通过编程配置 其选择逻辑和数据输入端口的自定义选择器 。

数字信号。

多路复用

数据选择器可以用于实现多路复用技术,如频分复用和时分复用等。通过选择不同的输 入通道,数据选择器可以实现多路信号的同时传输,从而提高通信系统的传输效率和可

靠性。

04

数据选择器的扩展

多路数据选择器

总结词

多路数据选择器是一种能够同时处理多个数据输入的选择器,具有多个数据输入端口和多个数据输出端口。

个对应的输出信号。

高速性能

数据选择器通常具有高速性能,能 够快速地完成数据的传输和处理。

灵活性

数据选择器的选择输入信号和数据 输入信号可以有多种组合方式,因 此具有很高的灵活性,可以适用于 各种不同的应用场景。

03

数据选择器的应用

数据选择器在数字系统中的应用

实现多路数据分时传输

数据选择器在数字系统中常被用于实现多路数据的分时传输。通过选择不同的输 入端口,数据选择器可以在同一时间选择并传输一路数据,从而实现多路数据的 并行处理。

06

数据选择器的优缺点

数据选择器的优点

并行处理能力强

灵活性高

数据选择器能够同时处理多个输入数据, 提高了并行处理能力,使得数据处理速度 更快。

数据选择器可以根据需要选择不同的输入 数据,使得系统更加灵活,能够适应不同 的数据处理需求。

《数据选择器的应用》课件

数据选择器还可以用于实现组合逻辑函数,例如实现AND 、OR、XOR等逻辑操作。

02

数据选择器的分类

2选1数据选择器

总结词

一种简单的数据选择器,有两个数据输入端和两个数据输出端。

详细描述

2选1数据选择器也称为2-to-1多路复用器,它有两个数据输入端D0和D1,以及 一个数据输出端Y。通过一个2位二进制地址信号A0和A1来选择输入数据D0或 D1,并将选中的数据输出到Y端。

《数据选择器的应用》ppt课件

• 数据选择器概述 • 数据选择器的分类 • 数据选择器的使用方法 • 数据选择器的应用实例 • 数据选择器的优势与局限性 • 数据选择器的发展趋势与展望

01

数据选择器概述

数据选择器的定义

数据选择器(也称为多路选择器或 MUX)是一种组合逻辑电路,它可 以从多个数据输入中选择一个数据输 出。

04

数据选择器的应用实例

数据选择器在信号分离中的应用

总结词:信号分离

详细描述:数据选择器在信号分离中起到关键作用,它可以根据输入信号的特征,将多个信号源的输出信号进行选择和分离 ,从而实现信号的筛选和传输。

数据选择器在信号分离中的应用

总结词:信号合成

详细描述:数据选择器还可以用于信号合成,将多个信号源的信号进行组合,生成一个新的复合信号 。这种应用在音频处理、图像处理等领域中非常常见。

需求。

多功能化趋势

为了满足复杂应用的需求,数据选择器正 朝着多功能化的方向发展,集成更多的输

入和输出通道以及更丰富的功能模块。

高集成度趋势

随着半导体工艺的进步,数据选择器正朝 着高集成度的方向发展,以实现更小体积 、更低成本和更高效能。

智能化趋势

随着人工智能和物联网技术的快速发展, 数据选择器正朝着智能化的方向发展,能 够实现自适应选择、自学习等功能。

02

数据选择器的分类

2选1数据选择器

总结词

一种简单的数据选择器,有两个数据输入端和两个数据输出端。

详细描述

2选1数据选择器也称为2-to-1多路复用器,它有两个数据输入端D0和D1,以及 一个数据输出端Y。通过一个2位二进制地址信号A0和A1来选择输入数据D0或 D1,并将选中的数据输出到Y端。

《数据选择器的应用》ppt课件

• 数据选择器概述 • 数据选择器的分类 • 数据选择器的使用方法 • 数据选择器的应用实例 • 数据选择器的优势与局限性 • 数据选择器的发展趋势与展望

01

数据选择器概述

数据选择器的定义

数据选择器(也称为多路选择器或 MUX)是一种组合逻辑电路,它可 以从多个数据输入中选择一个数据输 出。

04

数据选择器的应用实例

数据选择器在信号分离中的应用

总结词:信号分离

详细描述:数据选择器在信号分离中起到关键作用,它可以根据输入信号的特征,将多个信号源的输出信号进行选择和分离 ,从而实现信号的筛选和传输。

数据选择器在信号分离中的应用

总结词:信号合成

详细描述:数据选择器还可以用于信号合成,将多个信号源的信号进行组合,生成一个新的复合信号 。这种应用在音频处理、图像处理等领域中非常常见。

需求。

多功能化趋势

为了满足复杂应用的需求,数据选择器正 朝着多功能化的方向发展,集成更多的输

入和输出通道以及更丰富的功能模块。

高集成度趋势

随着半导体工艺的进步,数据选择器正朝 着高集成度的方向发展,以实现更小体积 、更低成本和更高效能。

智能化趋势

随着人工智能和物联网技术的快速发展, 数据选择器正朝着智能化的方向发展,能 够实现自适应选择、自学习等功能。

《实验四数据选择器》课件

结束数据采集后,关闭数据 选择器并断开连接

数据选择器的使用注意事项

● 确保数据选择器已正确安装并连接到计算机 ● 确保数据选择器的电源已接通并正常工作 ● 确保数据选择器的输入和输出端口已正确连接 ● 确保数据选择器的设置已正确配置,包括数据格式、采样频率等 ● 确保数据选择器的通信协议已正确设置,包括波特率、数据位、停止位等 ● 确保数据选择器的输入和输出信号已正确连接,包括模拟信号、数字信号等 ● 确保数据选择器的接地已正确处理,避免干扰和损坏 ● 确保数据选择器的使用环境已满足要求,包括温度、湿度、电磁干扰等 ● 确保数据选择器的操作已正确执行,包括启动、停止、数据采集等 ● 确保数据选择器的维护已正确进行,包括清洁、检查、更换等

数据选择器的逻辑功能:实现数据的选择和输出 数据选择器的应用:广泛应用于数字电路、计算机等领域

数据选择器的工作原理

数据选择器是一种 用于选择数据的设 备,通常用于计算 机系统中。

数据选择器的工作原 理是通过控制信号来 选择输入数据中的某 一位或几位,并将其 输出到输出端。

数据选择器的输入 端可以有多个,输 出端只有一个。

技术进步:随着 科技的发展,数 据选择器的性能 将不断提高,如 速度更快、功耗 更低、可靠性更 高等。

应用领域:数据 选择器的应用领 域将不断扩大, 如物联网、大数 据、人工智能等。

未来展望:数据 选择器在未来将 更加智能化、集 成化,成为通信、 计算机等领域的 重要部件。

感谢您的耐心观看

汇报人:

数据选择器的信号处理过程中的输出信号:输出信号可以是数字信号,也可以是模拟信号,取决 于输入信号的类型和选择信号的类型

实验四数据选择器的使 用方法

数据选择器的使用步骤

设置数据选择器的参数,如 选择模式、数据格式等 打开数据选择器的软件界面

《数据选择器》课件

越好。

影响因素

可靠性受到多种因素的影响,包括 数据选择器的内部电路设计、制造 工艺、工作环境等。

测试方法

通过在长时间内进行高低温循环、 振动、湿度等环境试验,可以评估 数据选择器的可靠性。

06

数据选择器的发展趋势

高性能数据选择器的发展趋势

高速数据传输

随着数据传输速率的不断提高,高性能数据选择器需要具备更高 的工作频率和更低的延迟,以满足高速数据传输的需求。

选择信号

数据选择器的选择信号由二进制编码组成,通过这些信号可以选择一个相应的数据输入。

输出信号

数据选择器的输出信号是经过选择的输入信号,这些信号通过译码输出端输出。

数据选择器的信号传输方式

并行传输

数据选择器的数据输入端可以同 时接收多个数据信号,实现数据 的并行传输。

串行传输

数据选择器的译码输出端只能输 出一个信号,实现数据的串行传 输。

基于FPGA的数据选择器实现方式

FPGA实现方式

通过现场可编程门阵列(FPGA)来实现数据选择器的功能。 这种实现方式结合了硬件和软件的优点,具有速度快、灵活 性高、易于扩展和修改的优点,同时也有功耗低、可靠性高 等优点。

FPGA实现方式的优缺点

优点是速度快、灵活性高、易于扩展和修改,功耗低、可靠 性高,适用于对速度、稳定性、功耗和灵活性要求较高的应 用场景;缺点是需要专业的开发工具和经验,且相对于硬件 和软件实现方式来说成本较高。

05

数据选择器的性能指标

传输延迟时间

传输延迟时间

指数据选择器在接收到选择信号 后,将数据从输入端传输到输出 端所需要的时间。传输延迟时间 越短,数据选择器的速度越快。

影响因素

传输延迟时间受到多种因素的影 响,包括数据选择器的内部电路

影响因素

可靠性受到多种因素的影响,包括 数据选择器的内部电路设计、制造 工艺、工作环境等。

测试方法

通过在长时间内进行高低温循环、 振动、湿度等环境试验,可以评估 数据选择器的可靠性。

06

数据选择器的发展趋势

高性能数据选择器的发展趋势

高速数据传输

随着数据传输速率的不断提高,高性能数据选择器需要具备更高 的工作频率和更低的延迟,以满足高速数据传输的需求。

选择信号

数据选择器的选择信号由二进制编码组成,通过这些信号可以选择一个相应的数据输入。

输出信号

数据选择器的输出信号是经过选择的输入信号,这些信号通过译码输出端输出。

数据选择器的信号传输方式

并行传输

数据选择器的数据输入端可以同 时接收多个数据信号,实现数据 的并行传输。

串行传输

数据选择器的译码输出端只能输 出一个信号,实现数据的串行传 输。

基于FPGA的数据选择器实现方式

FPGA实现方式

通过现场可编程门阵列(FPGA)来实现数据选择器的功能。 这种实现方式结合了硬件和软件的优点,具有速度快、灵活 性高、易于扩展和修改的优点,同时也有功耗低、可靠性高 等优点。

FPGA实现方式的优缺点

优点是速度快、灵活性高、易于扩展和修改,功耗低、可靠 性高,适用于对速度、稳定性、功耗和灵活性要求较高的应 用场景;缺点是需要专业的开发工具和经验,且相对于硬件 和软件实现方式来说成本较高。

05

数据选择器的性能指标

传输延迟时间

传输延迟时间

指数据选择器在接收到选择信号 后,将数据从输入端传输到输出 端所需要的时间。传输延迟时间 越短,数据选择器的速度越快。

影响因素

传输延迟时间受到多种因素的影 响,包括数据选择器的内部电路

数据选择器

工作方式

工作原理是:给A1A0一组信号比如1 0那么就相当于给了他一个2进制数字2也就相当于选通了D2这个输入端, 这个时候输出Y输出的就是D2的信号;D2是什么,Y就输出什么 。

输出表如下:

逻辑功能

数据选择器(MUX)的逻辑功能是在选择信号的控制下,从多路数据中选择一路数据作为输出信号 。

数据选择器

组合逻辑电路

01 基本定义

03 逻辑功能

目录

02 工作方式 04 4选1原理图

数据选择器(data selector)根据给定的输入代码,从一组输入信号中选出指定的一个送至输出端的组合逻 辑电路。有时也把它叫做多路选择器或多路调制器(multiplexer)。

基本定义

数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电 路称为数据选择器。在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,示的是四选一数据选择器的原理图。图1中的D0、D1、D2、D3是四个数据输入端,Y为输出端,A1、 A0是输入端。从表中可见,利用指定A1A0的代码,能够从D0、D1、D2、D3这四个输入数据中选出任何一个并送到 输出端。因此,用数据选择器可以实现数据的多路分时传送。

此外,数据选择器还广泛用于产生任意一种组合逻辑函数。在图1电路中,若将Y看成是A0、A1及D0、D1、D2、 D3的函数,则可写成

如果把A1、A0视为两个输入逻辑变量,同时把D0、D1、D2和D3取为第三个输入逻辑变量A2的不同状态(即A2、 /A2、1或0),便可产生所需要的任何一种三变量A2、A1、A0的组合逻辑函数。可见,利用具有n位输入的数据选 择器可以产生任何一种输入变量数不大于n +1的组合逻辑函数 。

谢谢观看

组合逻辑电路—数据选择器(电子技术课件)

DDDDDSSDDSD0120241356774H(IC) 1YY51

&Y

E

S2 S1 S0

74LS151功能框图

任务五:数据选择器

1个使能输入端 8 路数据输入端

3 个地址输 入端

E D0

D1

D2

D3 D4

D5

D6

D7

S0 1

1

S1 1

1

S2 1

1

&

& &

&

2个互补输 出端

&

≥≥

Y

&

1 11 Y

&

& &

&

74LS151的逻辑图

任务五:数据选择器

3、74LS151的功能表

任务五:数据选择器

1、数据选择器的定义与功能

数据选择器:能实现数据选择功能的逻辑电路。它的作用相当于多个输入的单 刀多掷开关,又称“多路开关” 。

数据选择的功能:在通道选择信号 的作用下,将多个通道的数据分时 传送到公共的数据通道上去的。

I0 I1

I 2n1

数据输出 通道选择

信号

任务五:数据选择器

0

1

0

0

1

1

Y S1 S0 I0 S1S0 I1 S1 S0 I2 S1S0 I3 Y I0m0 I0 I1 I2 I3

任务五:数据选择器

2、集成电路数据选择器

8选1数据选择器74HC151

D7

D6

D5

D4

Y

D3

74HC151

D2

Y

D1

D0

任务五:数据选择器

5、 数据选择器的扩展位的扩展

数字电子技术-数据选择器PPT28页

END

39、没有不老的誓言,没有不变的承 诺,踏 上旅途 ,义无 反顾。 40、对时间的价值没有没有深切认识 的人, 决不会 坚韧勤 勉。

16、业余生活要有意义,不要越轨。——华盛顿 17、一个人即使已登上顶峰,也仍要自强不息。——罗素·贝克 18、最大的挑战和突破在于用人,而用人最大的突破在于信任人。——马云 19、自己活着,就是为了使别人过得更美好。——雷锋 20、要掌握书,莫被书掌握;要为生而读,莫为读而生。——布尔沃

数字电子技术-数据选择器

36、“不可能”这个字(法语是一个字 ),只 在愚人 的字典 中找得 到。--拿 破仑。 37、不要生气要争气,不要看破要 破,不 要嫉妒 要欣赏 ,不要 托延要 积极, 不要心 动要行 动。 38、勤奋,机会,乐观是成功的三要 素。(注 意:传 统观念 认为勤 奋和机 会是成 功的要 素,但 是经过 统计学 和成功 人士的 分析得 出,乐 观是成 功的第 三要素 。

02-15.2 数据选择器工作原理-课件

end

endmodule

《数字电子技术基础》

█ 数据选择器的Verilog-HDL设计

//8选1数据选择器设计

always @(in0 or in1 or in2 or in3 or in4 or in5 or in6 or in7

module mux_81

or sel)

(out,in0,in1,in2,in3,in4,in5,in6,in7, begin

数字电子技术基础第十五讲若干常用中规模组合逻辑电路数据分配器和数据选择器数据选择器工作原理数据选择器工作原理lecture数字电子技术基础第十五讲若干常用中规模组合逻辑电路数据分配器和数据选择器数据选择器工作原理数据选择器与数据分配器的功能正好相反它完成从一组输入数据中选出某一个的功能是一种称为数据选择器dataselector或多路开关multiplexer的逻辑电路

out=in2; else if(sel==3'b011)

out=in3; else if(sel==3'b100)

out=in4;

《数字电子技术基础》

第十五讲 若干常用中规模组合逻辑电路-数据分配器和数据选择器

█ 数据选择器的Verilog-HDL设计

//…… else if(sel==3'b101) out=in5; else if(sel==3'b110) out=in6; else out=in7;

D0

逻辑函数表达式:

D1

D2

Y Y D0A1A0 D1A1A0 D2 A1A0 D3A1A0

D3

A1 A0 图1 数据选择器原理框图

《数字电子技术基础》

第十五讲 若干常用中规模组合逻辑电路-数据分配器和数据选择器

endmodule

《数字电子技术基础》

█ 数据选择器的Verilog-HDL设计

//8选1数据选择器设计

always @(in0 or in1 or in2 or in3 or in4 or in5 or in6 or in7

module mux_81

or sel)

(out,in0,in1,in2,in3,in4,in5,in6,in7, begin

数字电子技术基础第十五讲若干常用中规模组合逻辑电路数据分配器和数据选择器数据选择器工作原理数据选择器工作原理lecture数字电子技术基础第十五讲若干常用中规模组合逻辑电路数据分配器和数据选择器数据选择器工作原理数据选择器与数据分配器的功能正好相反它完成从一组输入数据中选出某一个的功能是一种称为数据选择器dataselector或多路开关multiplexer的逻辑电路

out=in2; else if(sel==3'b011)

out=in3; else if(sel==3'b100)

out=in4;

《数字电子技术基础》

第十五讲 若干常用中规模组合逻辑电路-数据分配器和数据选择器

█ 数据选择器的Verilog-HDL设计

//…… else if(sel==3'b101) out=in5; else if(sel==3'b110) out=in6; else out=in7;

D0

逻辑函数表达式:

D1

D2

Y Y D0A1A0 D1A1A0 D2 A1A0 D3A1A0

D3

A1 A0 图1 数据选择器原理框图

《数字电子技术基础》

第十五讲 若干常用中规模组合逻辑电路-数据分配器和数据选择器

数字译码器和数据选择器PPT文档共16页

数字译码器和数据选择器

56、死去何所道,托体同山阿。 57、春秋多佳日,登高赋新诗。 58、种豆南山下,草盛豆苗稀。晨兴 理荒秽 ,带月 荷锄归 。道狭 草木长 ,夕露 沾我衣 。衣沾 不足惜 ,但使 愿无违 。 59、相见无杂言,但道桑麻长。 60、迢迢新秋夕,亭亭月将圆。过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

56、死去何所道,托体同山阿。 57、春秋多佳日,登高赋新诗。 58、种豆南山下,草盛豆苗稀。晨兴 理荒秽 ,带月 荷锄归 。道狭 草木长 ,夕露 沾我衣 。衣沾 不足惜 ,但使 愿无违 。 59、相见无杂言,但道桑麻长。 60、迢迢新秋夕,亭亭月将圆。过得舒适、愉快,这是不可能的,因为人类必须具备一种能应付逆境的态度。——卢梭

▪

27、只有把抱怨环境的心情,化为上进的力量,才是成功的保证。——罗曼·罗兰

▪

28、知之者不如好之者,好之者不如乐之者。——孔子

▪

29、勇猛、大胆和坚定的决心能够抵得上武器的精良。——达·芬奇

▪

30、意志是一个强壮的盲人,倚靠在明眼的跛子肩上。——叔本华

数据选择器PPT优秀版

例 用数据选择器实现三变量多数表决器。

这个问题可以用八选一实现,也可以用四选一来实现,不

管是八选一还是四选一都可以用以上三种方法来做。

1、用八选一实现

(1)真值表对照法 三变量多数表决器真值表 及八选一数据选择器功能 表如表 2所示,两表合一 对照则

D0 D1 D2 D4 0

D3 D5 D6 D7 1

-

L

L L L D0

D0

-

L

L L H D1

D1

-

L

L H L D2

D2

-

L

L H H D3

D3

-

L

H L L D4

D4

-

L

H L H D5

D5

-

L

H H L D6

D6

-

L

H H H D7

D7

①3个地址输入端

②D0~D7 8个数据源 ③同相输出Y和反相输出W

D3

1

D2

2

D13ຫໍສະໝຸດ D04Y5

W

6

G

7

GND 8

表 2 真值表

A2 A 1 A0

F

Di

0 0 00

D0

0 0 10

D1

0 1 00

D2

0 1 11

D3

1 0 00

D4

1 0 11

D5

1 1 01

D6

1 1 11

D7

(2)表达式对照法

由公式确定Di,三变量多数表决器的表达式为:

_ _

此法比较直观且简便,其方法F 是: 首先A 选定2 A 地址1 A 变0 量; A 2 A 1 A 0 A 2 A 1A 0 A 2 A 1 A 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

与八选一方程对比

F ' A2 A1 A0D0 A2 A1A0D1 A2 A1 A0D2 A2 A1A0D3 A2 A1 A0D4 A2 A1A0D5 A2 A1 A0D6 A2 A1A0D7 为使F′=F则令

D0 D1 D2 D4 0 D3 D5 D6 D7 1

ppt课件

D5 D6 D7

W

&

1 D08 D09 DDD111102 D13 DD1145

G

C

B

Y

A

D0

D1

D2 74LS151

DD34

D5

D6

W

D7

ppt课件

Y

-

Y

10

3、 数据选择器的典型应用

数据选择器的应用就是用数据选择器实现逻辑函 数,具体方法有三种:

(1)真值表对照法 由数据选择器的功能表和逻辑函数真值表对照,分别对照 出输入、数据输入和输出。 (2)表达式对照法 由数据选择器的输出表达式和逻辑函数表达式对照,分别 对照出输入、数据输入和输出。 (3)卡诺图对照法 由数据选择器的降维卡诺图和逻辑函数卡诺图对照,分别 对照出输入、数据输入和输出。

ppt课件

D3

1

D2

2

D1

3

D0

4

Y

5

W

6

G

7

GND 8

16 VCC

74LS151 15 D4

14 D5 13 D6 12 D7 11 A 10 B 9C

输入使能G为低电平有效

Y = m0D0 m1D1 m2D2 m3D3 m4D4

7

m5D5 m6D6 m7D7 miDi i=0

式中mi为C、B、A最小项。例如 CBA=010时,根据最小项的性质,

D1

数

D1

D2

据

D2

… …

选

F

F

择

器 Dm

…

A1 A2 An

(a)

(b)

(a) 数据选择器逻辑符号;ppt(课b件) 单刀多路开关比拟数据选择器 1

1. 数据选择器功能介绍

A1 A0

D0 D1 D2 D3

D0 D1 D2 D3

D3

A1

D2

A0 F

F

E

D1

(a)

D0

1 A0

F

1

A0A1

A1

E

(c)

图 4 – 50 四选一MUX ppt课件

1

& ≥1

(b)

1 F F

2

功能表

输 入 数

输

入

D

A1

A0

D0

0

0

地

输出

址

Y

D0

变

据

D1

0

1

D1

量

D2

1

0

D2 由地址码决定从

D3

1

1

逻辑表达式

D3 四路输入中选择 哪一路输出。

Y D0 A1A0 D1A1pApt0课件 D2 A1A 0 D3 A1A0

3

74LS151八选一数据选择器的功能表

解 (1)使能端扩展 用二片四选一和一个反相器、 一个或门即可。如图4-51所示,第三个地址端A2直接接 到Ⅰ的使能端,通过反相器接到Ⅱ的使能端。当A2=0 时,Ⅰ选中,Ⅱ禁止。 F输出F1,即从D0~D3中选一路 输出;当A2=1时,Ⅰ禁止, Ⅱ选中。F输出F2, 即从 D4~D7 中选一路输出。这一过程可由下表列出:

ppt课件

6

D0 D1 D2 D3 A2

A1

E A1

D0

D1 D2 Ⅰ

D3

A0

A0

F1

D4 D5 D6 D7 1

A1 A0

E A1

D0

D1 D2 Ⅱ

D3

A0

F2

≥1

F

图 4 – 51 四选一扩展为八选一

ppt课件

7

D7

(2) 树型扩展。

D6

不用使能端而采用两级级联

D5

树型扩展数据选择器

D4

D3 D2 D1 D0

0 0 00

D0

0 0 10

D1

0100

D2

D0 D1 D2 D4 0

0 1 11

D3

1 0 00

D4

1 0 11

D3 D5 D6 D7 1

1 1 01

ppt课件 1 1 1 1

D5

D6

D7

12

(2)表达式对照法

由公式确定Di,三变量多数表决器的表达式为:

__

F A2 A1 A0 A2 A1A0 A2 A1 A0 A2 A1A0

只有m2为1,其余各项为0,故 Y=D2,即只有D2传送到输出端。

4

(1) 四位二选一数据选择器 74LS157; (2) 二位四选一数据选择器 74LS153; (3) 八选一数据选择器 74LS151 (4) 十六选一数据选择器 74LS150。

ppt课件

5

2. 数据选择器的扩展 将四选一数据选择器扩为八选一数据选择器。

输入

输出

使能端 选择地址码

G CBA Y

H ××× L

L

L L L D0

L

L L H D1

L

L H L D2

L

L H H D3

L

H L L D4

L

H L H D5

L

H H L D6

L

H H H D7

①3个地址输入端

②D0~D7 8个数据源 ③同相输出Y和反相输出W

W H - D0 - D1 - D2 - D3 - D4 - D5 - D6 - D7

D3

D2 D1 Ⅱ

F1

D0A1 A0Biblioteka D3D2D1 Ⅰ

F0

D0A1 A0

D1 Ⅲ

F

D0

A2

A1 A0

ppt课件

8

将两片74LS151连接成一个两位8选1数据选择

器 EN

C B A

G

C

B A

Y

Y0

D00

D0

DDD000123 D04

D1

D2 DD34

74LS151

D05 DD0067

D5 D6 D7

-

W

Y0

G

C

B A

Y

Y1

D10

D0

D11 D12

D1 D2 74LS151

DD1134

DD34

D15 D16 D17

D5 D6 D7

-

W

Y1

ppt课件

9

将两片74LS151连接成一个16选1数据选择

器D

G

C

C

B A

B

Y

A

D00

D0

≥1

DD0012 D03 D04

D1 D2 74LS151 DD34

D05 DD0067

ppt课件

11

例 用数据选择器实现三变量多数表决器。

这个问题可以用八选一实现,也可以用四选一来实现,不

管是八选一还是四选一都可以用以上三种方法来做。

1、用八选一实现

(1)真值表对照法

表 2 真值表

三变量多数表决器真值表

A2 A 1 A0 F

Di

及八选一数据选择器功能 表如表 2所示,两表合一 对照则

4.4.3数据选择器

数据选择器是指经过选择,把多个通道上的数据传 送到唯一的公共通道上去。

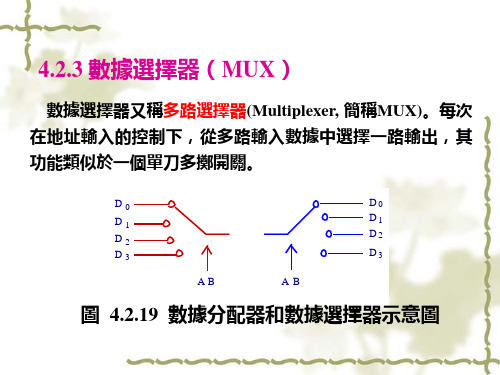

数据选择器又称多路选择器(Multiplexer, 简称MUX),其 框图如图1(a)所示。它有n位地址输入、2n位数据输入、1位输 出。每次在地址输入的控制下,从多路输入数据中选择一路输 出,其功能类似于一个单刀多掷开关,见图1(b)。

13

(3) 卡诺图对照法。此法比较直观且简便,其方法是:首 先选定地址变量;然后在卡诺图上确定地址变量控制范围, 即输入数据区;最后由数据区确定每一数据输入端的连接。

ppt课件

14

“ 1”

A2

A2D7 D6 D5 D4 D3 D2 D1 D0

F ' A2 A1 A0D0 A2 A1A0D1 A2 A1 A0D2 A2 A1A0D3 A2 A1 A0D4 A2 A1A0D5 A2 A1 A0D6 A2 A1A0D7 为使F′=F则令

D0 D1 D2 D4 0 D3 D5 D6 D7 1

ppt课件

D5 D6 D7

W

&

1 D08 D09 DDD111102 D13 DD1145

G

C

B

Y

A

D0

D1

D2 74LS151

DD34

D5

D6

W

D7

ppt课件

Y

-

Y

10

3、 数据选择器的典型应用

数据选择器的应用就是用数据选择器实现逻辑函 数,具体方法有三种:

(1)真值表对照法 由数据选择器的功能表和逻辑函数真值表对照,分别对照 出输入、数据输入和输出。 (2)表达式对照法 由数据选择器的输出表达式和逻辑函数表达式对照,分别 对照出输入、数据输入和输出。 (3)卡诺图对照法 由数据选择器的降维卡诺图和逻辑函数卡诺图对照,分别 对照出输入、数据输入和输出。

ppt课件

D3

1

D2

2

D1

3

D0

4

Y

5

W

6

G

7

GND 8

16 VCC

74LS151 15 D4

14 D5 13 D6 12 D7 11 A 10 B 9C

输入使能G为低电平有效

Y = m0D0 m1D1 m2D2 m3D3 m4D4

7

m5D5 m6D6 m7D7 miDi i=0

式中mi为C、B、A最小项。例如 CBA=010时,根据最小项的性质,

D1

数

D1

D2

据

D2

… …

选

F

F

择

器 Dm

…

A1 A2 An

(a)

(b)

(a) 数据选择器逻辑符号;ppt(课b件) 单刀多路开关比拟数据选择器 1

1. 数据选择器功能介绍

A1 A0

D0 D1 D2 D3

D0 D1 D2 D3

D3

A1

D2

A0 F

F

E

D1

(a)

D0

1 A0

F

1

A0A1

A1

E

(c)

图 4 – 50 四选一MUX ppt课件

1

& ≥1

(b)

1 F F

2

功能表

输 入 数

输

入

D

A1

A0

D0

0

0

地

输出

址

Y

D0

变

据

D1

0

1

D1

量

D2

1

0

D2 由地址码决定从

D3

1

1

逻辑表达式

D3 四路输入中选择 哪一路输出。

Y D0 A1A0 D1A1pApt0课件 D2 A1A 0 D3 A1A0

3

74LS151八选一数据选择器的功能表

解 (1)使能端扩展 用二片四选一和一个反相器、 一个或门即可。如图4-51所示,第三个地址端A2直接接 到Ⅰ的使能端,通过反相器接到Ⅱ的使能端。当A2=0 时,Ⅰ选中,Ⅱ禁止。 F输出F1,即从D0~D3中选一路 输出;当A2=1时,Ⅰ禁止, Ⅱ选中。F输出F2, 即从 D4~D7 中选一路输出。这一过程可由下表列出:

ppt课件

6

D0 D1 D2 D3 A2

A1

E A1

D0

D1 D2 Ⅰ

D3

A0

A0

F1

D4 D5 D6 D7 1

A1 A0

E A1

D0

D1 D2 Ⅱ

D3

A0

F2

≥1

F

图 4 – 51 四选一扩展为八选一

ppt课件

7

D7

(2) 树型扩展。

D6

不用使能端而采用两级级联

D5

树型扩展数据选择器

D4

D3 D2 D1 D0

0 0 00

D0

0 0 10

D1

0100

D2

D0 D1 D2 D4 0

0 1 11

D3

1 0 00

D4

1 0 11

D3 D5 D6 D7 1

1 1 01

ppt课件 1 1 1 1

D5

D6

D7

12

(2)表达式对照法

由公式确定Di,三变量多数表决器的表达式为:

__

F A2 A1 A0 A2 A1A0 A2 A1 A0 A2 A1A0

只有m2为1,其余各项为0,故 Y=D2,即只有D2传送到输出端。

4

(1) 四位二选一数据选择器 74LS157; (2) 二位四选一数据选择器 74LS153; (3) 八选一数据选择器 74LS151 (4) 十六选一数据选择器 74LS150。

ppt课件

5

2. 数据选择器的扩展 将四选一数据选择器扩为八选一数据选择器。

输入

输出

使能端 选择地址码

G CBA Y

H ××× L

L

L L L D0

L

L L H D1

L

L H L D2

L

L H H D3

L

H L L D4

L

H L H D5

L

H H L D6

L

H H H D7

①3个地址输入端

②D0~D7 8个数据源 ③同相输出Y和反相输出W

W H - D0 - D1 - D2 - D3 - D4 - D5 - D6 - D7

D3

D2 D1 Ⅱ

F1

D0A1 A0Biblioteka D3D2D1 Ⅰ

F0

D0A1 A0

D1 Ⅲ

F

D0

A2

A1 A0

ppt课件

8

将两片74LS151连接成一个两位8选1数据选择

器 EN

C B A

G

C

B A

Y

Y0

D00

D0

DDD000123 D04

D1

D2 DD34

74LS151

D05 DD0067

D5 D6 D7

-

W

Y0

G

C

B A

Y

Y1

D10

D0

D11 D12

D1 D2 74LS151

DD1134

DD34

D15 D16 D17

D5 D6 D7

-

W

Y1

ppt课件

9

将两片74LS151连接成一个16选1数据选择

器D

G

C

C

B A

B

Y

A

D00

D0

≥1

DD0012 D03 D04

D1 D2 74LS151 DD34

D05 DD0067

ppt课件

11

例 用数据选择器实现三变量多数表决器。

这个问题可以用八选一实现,也可以用四选一来实现,不

管是八选一还是四选一都可以用以上三种方法来做。

1、用八选一实现

(1)真值表对照法

表 2 真值表

三变量多数表决器真值表

A2 A 1 A0 F

Di

及八选一数据选择器功能 表如表 2所示,两表合一 对照则

4.4.3数据选择器

数据选择器是指经过选择,把多个通道上的数据传 送到唯一的公共通道上去。

数据选择器又称多路选择器(Multiplexer, 简称MUX),其 框图如图1(a)所示。它有n位地址输入、2n位数据输入、1位输 出。每次在地址输入的控制下,从多路输入数据中选择一路输 出,其功能类似于一个单刀多掷开关,见图1(b)。

13

(3) 卡诺图对照法。此法比较直观且简便,其方法是:首 先选定地址变量;然后在卡诺图上确定地址变量控制范围, 即输入数据区;最后由数据区确定每一数据输入端的连接。

ppt课件

14

“ 1”

A2

A2D7 D6 D5 D4 D3 D2 D1 D0