LM4863_IcpdfCom_1318331

LM4863低电压AB类2.2W立体声音频功放IC应用原理及设计

LM4863低电压AB类2.2W立体声音频功放IC应用原理及设计注意事项LM4863典型应用图应用信息裸露DAP封装PCB装置考虑事项裸露DAP封装必须连接到地。

LM4863裸露DAP封装需要特别注意它的散热设计。

如果没有适当的处理散热设计问题,LM4863在驱动4Ω阻值时将进入热关断。

在LM4863底部的裸露DAP封装必须焊接到电路板的铜衬垫上。

裸露DAP封装的热量通过一个铜面传开。

如果铜面不在电路板的顶层表面上,需要使用8-10个直径小于或等于0.013英寸的通孔来把裸露DAP封装热耦合到铜平面上。

由于铜面是用来把裸露DAP封装中的热量散发出去,所以它应当尽可能的大一些。

如果散热片和放大器共用同一层PCB板,5V电压下驱动4Ω的负载,至少需要使用2.5in2面积的散热片。

不放在同一PCB层的LM4863在相同负载和工作电压下则需要5in2。

如果周围环境温度大于25℃,需要增大散热片的面积或使用风扇来确保LM4863的结温低于150℃的关断温度。

在功率特征曲线中有更多的说明。

当LM4863驱动3Ω负载情况时需要另加风扇。

当环境温度很高时,需要更大风力的风扇或更大面积的散热片以避免器件进入热关断。

驱动3Ω和4Ω负载时PCB布局及注意事项由于使用了低阻抗的负载,LM4863输出管脚连线电阻的大小会对输出功率有非常大的影响。

从LM4863的输出端到负载或负载连接器的连线必须尽可能宽。

输出连线的任何电阻都会降低输出功率。

举例来说,在输出使用一个4Ω的负载以及0.1Ω的连线电阻,那么负载的输出功率会从2.2W降低到2.0W。

输出功率的大小还取决于基准电源。

为了在大输出功率的情况下避免电源电压降低,电源连线也应当尽可能宽。

桥式配置说明如上图所示,LM4863内部有两对运放。

第一个放大器的增益是外部配置结构决定的,而第二个放大器是内部固定增益为单位增益,构成倒相装置。

第一个放大器的闭环增益是通过调节R f 与R i之间的比率来确定的,而第二个放大器的增益是通过两个20KΩ的内连电阻来固定的。

lm4863芯片工作原理

lm4863芯片工作原理

LM4863是一款双声道音频功率放大器芯片,适用于低压供应

电源应用。

以下为其工作原理:

1. 输入信号:LM4863中包含两个独立的音频放大器通道,每

个通道都有一个差分输入阶段。

输入信号经过输入电容耦合进入差动放大器,同时通过调整输入电阻来控制输入信号的增益。

2. 差分放大器:输入信号经过差分放大器,将差模信号(即信号的正负号之差)放大,并且抑制共模信号(即信号的正负号之和)。

这有助于提高信号的动态范围和抑制对地的共模噪声。

3. 功率驱动器:放大的信号经过一个功率输出级别的引脚,通常为一个电容和电感组成的滤波网络。

这个网络用于减小输出的直流偏置,并限制短路电流。

这可以保护芯片和外部连接设备。

4. 输出级:放大后的信号通过输出级提供给连接的扬声器或耳机。

这个级别通常包含一个功率输出晶体管和一个负反馈网络,用于提高放大器的稳定性和线性度。

5. 供电电源:LM4863通过一个电源引脚从供电电源获取所需

的电源电压。

芯片内部包含一个负压电源调整电路和一个正压电源调整电路,将输入电源电压稳定为所需的工作电压。

综上所述,LM4863芯片通过差动放大器和输出级来放大输入

信号,并通过电源引脚提供所需的供电电压。

它适用于低压供应电源应用,如便携式音频设备和汽车音频系统。

LN4863功放

LN4863内置了低功耗待机电路和过热保护电路,同时内置了杂音消除电路,可以消除芯片启动 和关断过程中的咔嗒声或噼噗声。

■ 关键指标

功率输出@1% THD+N & VDD=5V LN4863LQ ,RL=3Ω,4Ω LN4863MTE,RL= 3Ω,4Ω LN4863MTE,RL=8Ω LN4863,RL=8Ω

单端耳机模式 THD+N@75mW into 32 Ω 关断电流 供电电压

■ 产品特点

立体声耳机放大器模式 “咔嗒声和噼噗声”抑制电路 稳定的固定增益 热关断功能 超小型封装:SOP,SOIC,TSSOP,LLP等

■ 用途

多媒体监听器 笔记本和台式电脑 便携电视

2.2 W双声道立体声集成耳机模式BTL音频功率放大器 LN4863系列

上海南麟电子有限公司

- 11 -

2.2W BTL音频功率放大器 双声道立体声 & 耳机模式

2.2 W双声道立体声集成耳机模式BTL音频功率放大器 LN4863系列

LN4863 系列

■ 产品概述

LN4863为双声道桥接音频功率放大电路,在5V输入电压条件下,能够为4Ω负载提供2.2W功率 的稳定输出,为3Ω负载提供2.5W功率的稳定输出,总谐波失真和噪声不超过1%。耳机输入端允许在驱 动立体声耳机时采用单端模式。

■ 功能框图

2.2 W双声道立体声集成耳机模式BTL音频功率放大器 LN4863系列

图 1 LN4863 功能框图

■ 绝对最大额定值

L4863L-S18-T中文资料

UNISONIC TECHNOLOGIES CO., LTDL4863 CMOS ICDUAL 2.2W AUDIO AMPLIFIER PLUS STEREO HEADPHONE FUNCTIONDESCRIPTIONThe UTC L4863 is a dual bridge-connected audio power amplifier. It combines dual bridge speaker amplifiers and stereo headphone amplifiers on one chip to simplify audio system design.In addition, the headphone input pin allows the amplifiers to operate in single-ended mode when driving stereo headphones. The IC could deliver different power by packages as below (when connected to a 5V supply with less than 1.0% THD+N.): - HTSSOP-20, 4Ω load: 2.2W - HTSSOP-20, 3Ω load: 2.5W(with forced-air cooled) - SOP/DIP , 8Ω load: 1.1W.The UTC L4863 features an externally controlled, low-power consumption shutdown mode, a stereo headphone amplifier mode, and thermal shutdown protection. It also utilizes circuitry to reduce “clicks and pops” during device turn-on.FEATURES* “Click and pop” suppression * Thermal shutdown protection * Unity-gain stable* Stereo headphone amplifier mode*Pb-free plating product number: L4863LORDERING INFORMATIONOrder NumberNormal Lead Free PlatingPackage PackingL4863-D16-T L4863L-D16-T DIP-16 Tube L4863-S16-R L4863L-S16-R SOP-16 Tape Reel L4863-S16-T L4863L-S16-T SOP-16 TubeL4863-S18-R L4863L-S18-R SOP-18 Tape Reel L4863-S18-T L4863L-S18-T SOP-18 Tube L4863-N20-R L4863L-N20-R HTSSOP-20Tape Reel L4863-N20-T L4863L-N20-T HTSSOP-20TubePIN CONFIGURATIONTHERMAL DATAPARAMETER SYMBOL RATINGS UNITSOP-16 80 ℃/WSOP-18 90 ℃/WDIP-16 63 ℃/W Thermal resistance (Junction to Ambient)HTSSOP-20θJA90 ℃/WSOP-16 20 ℃/WSOP-18 2 ℃/WDIP-16 20 ℃/W Thermal resistance (Junction to Case)HTSSOP-20θJC2 ℃/WABSOLUTE MAXIMUM RATINGPARAMETER SYMBOL RATINGS UNITSupply Voltage V DD 6.0 V Recommended Supply Voltage Range V DD 2.0 ~ 5.5 V Input Voltage V IN -0.3 ~ V DD +0.3 VPower Dissipation P D Internally limitedJunction Temperature T J +125 ℃Operating Temperature T OPR -40 ~ +85 ℃Storage Temperature T STG -65 ~ +150 ℃Note Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.ELECTRICAL CHARACTERISTICS (Notes 1)(V DD =5V, Ta =25, ℃unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITFOR ENTIRE ICSupply Voltage V DD 2 5.5V V IN =0V, I OUT =0A, HP-IN=0V6 11.5 20Quiescent Power Supply Current (Note 2) I DDV IN =0V, I OUT =0A, HP-IN=4V 5.8 mA Shutdown Current I SD V DD applied to the SHUTDOWN pin2 0.7 μA High V IH4 V Headphone Input VoltageLow V IL0.8VFOR BRIDGED-MODE OPERATION Output Offset VoltageV O(OFF)V IN =0V 5 50mVR L =3Ω 2.5THD=1%, f=1kHzR L =4Ω 2.2R L =3Ω 3.2 HTSSOP-20 THD+N=10%, f=1kHzR L =4Ω 2.7 WTHD=1%, f=1kHz R L =8Ω 1.0 1.1THD+N=10%, f=1kHz R L =8Ω 1.5WOutput Power(measured at the device terminals) SOP/DIP P OUT THD+N=1%, f=1kHz, RL=32Ω 0.34 W HTSSOP-20 R L =4Ω, P OUT =2W0.3 Total Harmonic Distortion + Noise SOP/DIP THD+N 20Hz ≤f ≤20kHz, A VD =2 R L =8Ω, P OUT =1W 0.3 %Power Supply Rejection Ratio PSRRV DD =5V, V RIPPLE =200mV RMS , R L =8Ω,C B =1.0μF67 dB Channel Separation X TALK f =1kHz, C B =1.0μF 90 dB Signal To Noise Ratio SNR V DD =5V, P OUT =1.1W, R L =8Ω 98 dB FOR SINGLE-ENDED OPERATION Output Offset Voltage V O(OFF)V IN =0V 5 50mVTHD=0.5%, f=1kHz, R L =32Ω 75 85THD+N=1%, f=1kHz, R L =8Ω 340Output Power P OUT THD+N=10%, f=1kHz, R L =8Ω 440 mW Total Harmonic Distortion + Noise THD+N A V =-1, P OUT =75mW,20Hz ≤f ≤20kHz, R L =32Ω0.2%Power Supply Rejection Ratio PSRR C B =1.0μF, V RIPPLE =200mV RMS, f =1kHz 52 dB Channel Separation X TALK f =1kHz, C B =1.0μF 60 dB Signal To Noise Ratio SNR V DD =5V, P OUT =340mW, R L =8Ω 95 dB Note:1. All voltages are measured with respect to the ground (GND) pins, unless otherwise specified.2. Depends on the offset voltage when a practical load is connected to the amplifier.3. When driving 3Ω or 4Ω and operating on a 5V supply, the HTSSOP-20 package must be mounted to the circuit board that has a minimum of 2.5 in 2 of exposed, uninterrupted copper area connected to the exposed-DAP.TYPICAL APPLICATION CIRCUITAudioInputAudioInputNote: Pin out shown for DIP-16 and SOP-16 packages. Refer to the PIN CONFIGURATION for the pin out of other packages.Figure 1.Typical Audio Amplifier Application CircuitEXTERNAL COMPONENTS DESCRIPTIONComponents FunctionalDescriptionR I The inverting input resistance, along with R F, set the closed-loop gain. R I, along with C I form a high pass filter with fc=1/(2πR I C I)C I The input coupling capacitor blocks DC voltage at the amplifier’s input terminals. C I, along with R I, create a high pass filter with fc=1/(2πR I C I). Refer to the section. Selecting Proper External Components, for an explanation of determine the value of C I.R F The feedback resistance, along with R I, set the closed-Ioop gain.C S The supply bypass capacitor. Refer to the Power Supply Bypassing section for information about properly placing and selecting the value of, this capacitor.C B The capacitor, C B, filters the half-supply voltage present on the Bypass pin. Refer to the Selecting Proper External Components section for information concerning proper placement and selecting C B’S value.TYPICAL CHARACTERISTICS(For HTSSOP-20)THD+N(%)THD+N(%)THD+N vs Output PowerTHD+N(%)10m0.01100.1Level (W)THD+N vs FrequencyTHD+N(%)200.011100.11001k10k20k BW<80kHz P OUT=2.0W, BW<80kHzFrequency (Hz) PowerDissipation(W)TYPICAL CHARACTERISTICS(Cont.)(For DIP-16, SOP-16 and SOP-18)T H D +N (%)T H D +N (%)T H D +N (%)T H D +N (%)T H D +N (%)T H D +N (%)TYPICAL CHARACTERISTICS(Cont.)THD+N vs Output PowerTHD+N(%)10m1100.112Level (W)THD+N vs FrequencyTHD+N(%)201100.11001k10k20kFrequency (Hz) THD+N(%)THD+N(%)Output Power vs Load ResistanceLoad Resistance (Power Dissipation vs Supply VoltagePower Out (mW) f=1kHz, BW<80kHzTYPICAL CHARACTERISTICS(Cont.)O u t p u t P o w e r (W )O u t p u t P o w e r (W )O u t p u tPow er (W)O u t p u t P o w e r (W )10140Output Power vs Load resistance700.80.60.40.21% THD+N 10% THD+N20305060Load Resistance (Ω)22.500.70.75Output Power vs Supply Voltage1.25Output Power (W)0.60.50.40.30.2R L =160.51V DD =5V f=1kHzTHD+N Bridged Load BW<80kHzL =32ΩR L =8TYPICAL CHARACTERISTICS(Cont.)P o w e r D i s s i p a t i o n (W )O u t p u t N o i s e V o l t a g e (μv )O u t p u t L e v e l (d B )O u t p u t L e v e l (d B )P S R R (d B )G A I N (d B )P h a s e ( )oTYPICAL CHARACTERISTICS(Cont.)15Supply Current vs Supply VoltageSupply Voltage (V)SupplyCurrent(mA)12963DropoutVoltage(V)UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where。

LM4863中文说明书完整

第五页 共六页

封装外形图三:(LM4863F)TSSOP 20

LM4863

第六页 共六页

第二页 共六页

LM4863

最大额定值 (TA=25℃)

参数名称

符号

数值

单位

工作电压

Vdd

6.0

V

存储温度

Tstg

-65 to +150

℃

输入电压 功率消耗

-0.3 to +(0.3+Vdd)

V

PD

见附注 1

W

结温度

150

℃

蒸发状态(60 秒)

215

℃

红外线 (15 秒)

220

℃

附注 1:最大功耗取决于三个因素:TJMAX,TA,θJA 它的计算公式 PDMAX=(TJMAX-TA)/θJA ,CSC4863 的 TJMAX=150℃. TA 为外部 环境的温度,θJA 取决于不同的封装形式。(TSSOP 封装形式的为 20℃/W)

0.3

%

RL=8Ω

0.3

%

Vdd=4.9V to 5.1V

52

dB

最小谐波失真 电源抑制比

THD

PSR R

f=1kHz,CB=1uF Vdd=5V, Po=1.1W

CB=1.0uF, VPIPPLE=200mVRMS,f=1khz

60

dB

95

dB

52

dB

通道隔离度

XTAL

K

f=1khz, CB=1.0uF

电特性

(除非特别说明,VCC=5V,RL=8Ω,f=1kHz,Tamb=25℃)

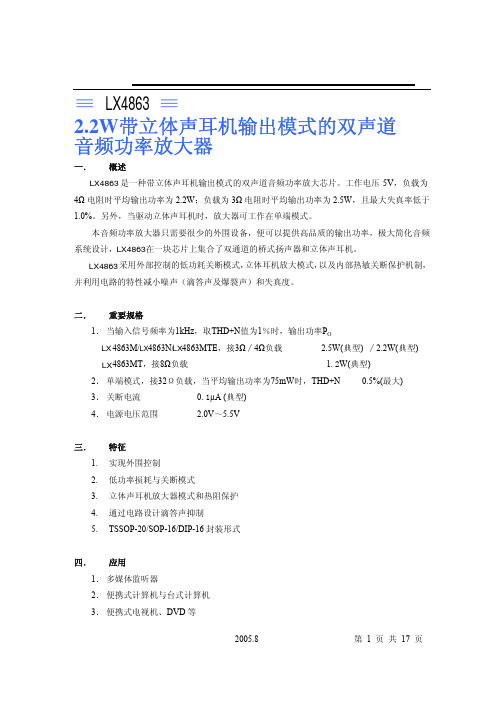

LX4863产品说明书

2005.8 第 1 页 共 17 页≡LX≡ 2.2W 带立体声耳机输出模式的双声道 音频功率放大器一.概述LX 是一种带立体声耳机输出模式的双声道音频功率放大芯片。

工作电压 5V ,负载为4Ω电阻时平均输出功率为2.2W ;负载为3Ω电阻时平均输出功率为2.5W ,且最大失真率低于1.0%。

另外,当驱动立体声耳机时,放大器可工作在单端模式。

本音频功率放大器只需要很少的外围设备,便可以提供高品质的输出功率,极大简化音频系统设计,在一块芯片上集合了双通道的桥式扬声器和立体声耳机。

采用外部控制的低功耗关断模式,立体耳机放大模式,以及内部热敏关断保护机制,并利用电路的特性减小噪声(滴答声及爆裂声)和失真度。

二. 重要规格1. 当输入信号频率为1kHz ,取THD+N 值为1%时,输出功率P O4863M/4863N/4863MTE ,接3Ω∕4Ω负载 2.5W(典型) ∕2.2W(典型) 4863MT ,接8Ω负载 1.2W(典型)2. 单端模式,接32Ω负载,当平均输出功率为75mW 时,THD+N 0.5%(最大) 3. 关断电流 0.1µA (典型) 4. 电源电压范围 2.0V ~5.5V 三.特征1. 实现外围控制2. 低功率损耗与关断模式3. 立体声耳机放大器模式和热阻保护4. 通过电路设计滴答声抑制5. TSSOP-20/SOP-16/DIP-16封装形式 四.应用1. 多媒体监听器2. 便携式计算机与台式计算机 3. 便携式电视机、DVD 等LX4863LX4863LX4863LX4863LX LX LX LX2005.8 第 2 页 共 17 页五. 芯片封装引脚分布图1 、SOP16和DIP 封装 图2 、TSSOP20封装说明:4863M (SOP16封装),4863N (DIP 封装),4863MT (TSSOP20封装), 4863MTE (TSSOP20带散热片封装)。

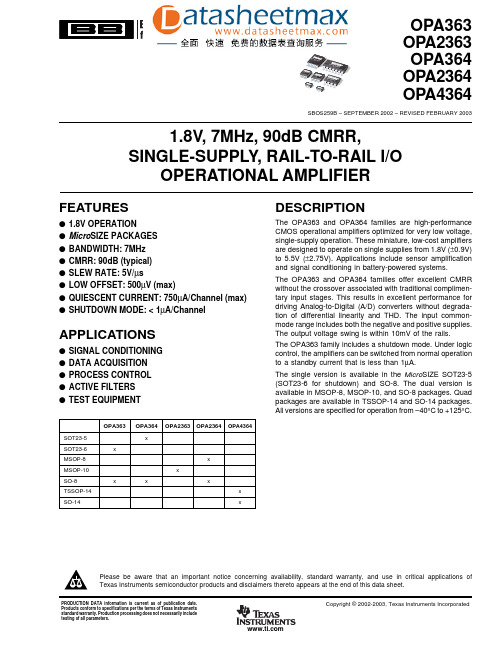

IC datasheet pdf-OPA363,OPA2363,OPA364,OPA2364,OPA4364,pdf(1.8V, 7MHz, 90dB CMRR, Single-Supply Rail

DESCRIPTION

The OPA363 and OPA364 families are high-performance CMOS operational amplifiers optimized for very low voltage, single-supply operation. These miniature, low-cost amplifiers are designed to operate on single supplies from 1.8V (±0.9V) to 5.5V (±2.75V). Applications include sensor amplification and signal conditioning in battery-powered systems. The OPA363 and OPA364 families offer excellent CMRR without the crossover associated with traditional complimentary input stages. This results in excellent performance for driving Analog-to-Digital (A/D) converters without degradation of differential linearity and THD. The input commonmode range includes both the negative and positive supplies. The output voltage swing is within 10mV of the rails. The OPA363 family includes a shutdown mode. Under logic control, the amplifiers can be switched from normal operation to a standby current that is less than 1µA. The single version is available in the MicroSIZE SOT23-5 (SOT23-6 for shutdown) and SO-8. The dual version is available in MSOP-8, MSOP-10, and SO-8 packages. Quad packages are available in TSSOP-14 and SO-14 packages. All versions are specified for operation from –40°C to +125°C.

A7533 Datasheet v0[1].7(Preliminary)

![A7533 Datasheet v0[1].7(Preliminary)](https://img.taocdn.com/s3/m/19c95f775acfa1c7aa00cc8a.png)

A7533A/B <Preliminary> 4X2 Switch Matrix with Tone/Polarity ControllerDocument TitleData sheet of A7533.Revision HistoryRev. No.History Issue Date Remark0.1Initial issue.Jun. 25th, 2007Preliminary0.2Logo changed.Oct. 18th, 20070.3Change DC spec, truth table Dec. 7th , 20070.4Add B type Jan. 16th, 20080.5Modify ordering information, add top marking info., reflow profile Apr. 17th, 20080.6Change pin definition Jul, 15, 20080.7Modify typo of Pin 14 and Pin 16, add remark of application ckt. Jul, 08, 2009Important Notice:AMICCOM reserves the right to make changes to its products or to discontinue any integrated circuit product or service without notice. AMICCOM integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life-support applications, devices or systems or other critical applications. Use of AMICCOM products in such applications is understood to be fully at the risk of the customer.A7533A/BTable of Contents1 Typical Applications (1)2 General Description (1)3 Pin Assignments (1)4 Block Diagram (2)5 Pin Configurations (3)6 Electrical Specifications (4)7 Absolute Maximum Ratings (4)8 Applications Circuit (5)9 Truth Table (6)10 Ordering Information (8)11 Package Information (9)12 Top Marking Information (10)13 Reflow Profile (12)14 Tape Reel Information (13)15 Product Status (16)A7533A/B<Preliminary> 4X2 Switch Matrix with Tone/Polarity Controller1 Typical Applications4*2 Switch Matrix for 0.2 -3.0 GHz Applications:n LNB n CATVn Cellular Systems n DBS2 General DescriptionA7533 is a low-cost 4 x 2 switch matrix with tone detector in a 20-lead QFN package for use in RF multiplexing applications from 200 to 3000 MHz. A positive voltage controlled 4 bit decoder and tone/polarity detector are both integrated on the switch with DiSEqC control signals rejection. A7533 is ok to be used in 50/75 ohm systems.Switch outputs (OP1 & OP2) can be independentlyselected from any of the four inputs (HH, HL, VH, VL) or simultaneously select the same inputs. Note that the switch is bi-directional and input/output functionality may be interchanged.3 Pin AssignmentsHLN.C.V2T2A75331234567891015141312112019181716N.C.T1VLN.C.V1N.C.OP2DC2OP1DC1VDDN.C.N.C.VHVHMHHA7533 QFN Package Top View4 Block Diagram1645 Tone/Polarity Controll CircuitV HV LO P 11O P 2V 2T 2DC1DC2H HH L2205 Pin ConfigurationsPin No.Pin NameFunction1112T1V1Tone and Polarity detector input.54V2T2Tone and Polarity detector input.1416202VL VH HH HL RF input pin106OP1OP2RF output pin9VDDPower pin, Connect to 3.6V power.1313151719N.C.No connection, Connect to PCB ground.18VHM Vertical-Horizontal Mirror.Connect to ground à Normal Leave open à Mirror.79DC2DC1By-pass , Connect to by-pass capacitor Back side paddleGNDConnect to ground.6 Electrical SpecificationsTypical condition: T A = +25°C, VDD= +3.3V, 50 ohm System. All RF port are terminated to 50 ohm .Parameter Condition Min.Typ.Max.Units SwitchInsertion Loss200 - 950 MHz950 - 1450 MHz1450 - 2150 MHz2150 - 3000 MHz666.576.56.57.598.57.5811dBIsolation200 - 950 MHz950 - 1450 MHz1450 - 2150 MHz2150 - 3000 MHz3531292337333125dBReturn Loss (Input; VL, HL, VH, HH)200 - 3000 MHz1215dB Return Loss (Output; OP1, OP2)200 - 3000 MHz1015dB Output IP3200 - 3000 MHz20dBm Input Power for 1 dB Compression200 - 3000 MHz15dBm Switching On/Off Speedt RISE / t FALL (10/90% RF)200 - 3000 MHz10ms Polarity and Tone DetectorPolarity Threshold With external 62KΩ1414.7515.5V Tone Signal Frequency-40~85℃, 650mVpp72278KHz Tone Signal Duty Cycle-40~85℃405060% Tone Signal Amplitude Threshold With external 62KΩand 500pF0.10.17Vpp Power supplySupply Voltage-40~85℃3 3.3 4.2V Current Consumption-40~85℃ 1.5 2.2 3.2mA Note:Tone/Polarization threshold could be tuned by change the value of external R,C. Please contact AMICCOM FAE for specified application.7 Absolute Maximum RatingsParameter RatingBias Voltage Range (VDD)+5 VDCStorage Temperature-65 to +150°COperating Temperature-40 to +85°CMaximum Input Power+17 dBm (200 - 3000 MHz)8 Applications CircuitNote 162K ohm resistors shall be kept in 1% tolerance.Note 2If 500 pF is not available, 470 pF is also acceptable.Note 3All capacitors shall be within 10 % tolerance. But, 5 % tolerance is preferred.9 Truth TableAbove figure show the function of VHM. (Vertical/Horizontal mirror)Above figure show the different between 7533A and 7533B (High/Low band upside down) V1,V2 = 0 means DC voltage =9.5~14V, V1, V2=1 means DC voltage =15.5~19VT1, T2=0 means 22KHz tone disappeared. T1, T2=1 means 22KHz tone appeared.A7533A When pin 18 “VHM” connected to GNDControl Input Outputto Input StateState V1T1V2T2OP1OP210000HH HH20001HH HL30010HH VH40011HH VL50100HL HH60101HL HL70110HL VH80111HL VL91000VH HH101001VH HL111010VH VH121011VH VL131100VL HH141101VL HL151110VL VH161111VL VLA7533A When pin 18 “VHM” open. Vertical and Horizontal will be mirror.Control Input Outputto Input StateState V1T1V2T2OP1OP210000VH VH20001VH VL30010VH HH40011VH HL50100VL VH60101VL VL70110VL HH80111VL HL91000HH VH101001HH VL111010HH HH121011HH HL131100HL VH141101HL VL151110HL HH161111HL HLA7533B When pin 18 “VHM” connected to GNDControl Input Outputto Input StateState V1T1V2T2OP1OP210000HL HL20001HL HH30010HL VL40011HL VH50100HH HL60101HH HH70110HH VL80111HH VH91000VL HL101001VL HH111010VL VL121011VL VH131100VH HL141101VH HH151110VH VL161111VH VHA7533A/B A7533B When pin 18 “VHM” open. Vertical and Horizontal will be mirror.Control Input Outputto Input StateState V1T1V2T2OP1OP210000VL VL20001VL VH30010VL HL40011VL HH50100VH VL60101VH VH70110VH HL80111VH HH91000HL VL101001HL VH111010HL HL121011HL HH131100HH VL141101HH VH151110HH HL161111HH HH10 Ordering InformationPart No.Package Units Per Reel / TrayA75X33AQF/Q QFN20L, Pb Free, Tape & Reel, -40℃〜85℃3KA75X33AQF QFN20L, Pb Free, Tray, -40℃〜85℃490EAA75X33BQF/Q QFN20L, Pb Free, Tape & Reel, -40℃〜85℃3KA75X33BQF QFN20L, Pb Free, Tray, -40℃〜85℃490EA11 Package InformationQFN 20L (4 X 4 X 0.8mm) Outline Dimensionsunit: inches/mm10615E 2e162051e bC 0.10M A B106L TOP VIEWBOTTOM VIEWCA 3A0.10//Cy CSeating PlaneDimensions in inches Dimensions in mm SymbolMin Nom Max Min Nom Max A 0.0280.0300.0320.700.750.80A 10.0000.0010.0020.000.020.05A 30.008 REF 0.203 REF b 0.0070.0100.0120.180.250.30D 0.1540.1580.161 3.90 4.00 4.10D 20.0750.0790.083 1.90 2.00 2.10E 0.1540.1580.161 3.90 4.00 4.10E 20.0750.0790.083 1.90 2.00 2.1012 Top Marking Information A75X33AQF¡Part No. :A75X33AQF ¡Pin Count :20¡Package Type :QFN¡Dimension :4*4 mm¡Mark Method :Laser Mark ¡Character Type :ArialA75X33BQF¡Part No. :A75X33BQF ¡Pin Count :20¡Package Type :QFN¡Dimension :4*4 mm¡Mark Method :Laser Mark ¡Character Type :Arial13 Reflow ProfileActual Measurement Graph14 Tape Reel InformationCover / Carrier Tape Dimension11 EA IC60cm ±4cmTYPE P A0B0P0P1D0D1E F W 20 QFN 4*48 4.35 4.35 4.0 2.0 1.5 1.5 1.75 5.51224 QFN 4*48 4.4 4.4 4.0 2.0 1.5 1.5 1.75 5.51232 QFN 5*58 5.25 5.25 4.0 2.0 1.5 1.5 1.75 5.51248 QFN 7*7127.257.25 4.0 2.0 1.5 1.5 1.757.516DFN-104 3.2 3.2 4.0 2.0 1.5- 1.75 1.9820 SSOP 128.27.5 4.0 2.0 1.5 1.5 1.757.51624 SSOP 128.28.8 4.0 2.0 1.5 1.5 1.757.51628 SSOP (150mil)86104.0 2.0 1.5 1.5 1.757.516TYPE K0K1t COVER TAPE WIDTH20 QFN (4X4) 1.1-0.39.224 QFN (4X4) 1.4-0.39.232 QFN (5X5) 1.1-0.39.248 QFN (7X7) 1.1-0.313.3DFN-100.75-0.25820 SSOP 2.5-0.313.324 SSOP 2.1-0.313.328 SSOP (150mil) 2.5-0.312.5A 040mil.NO COMPONENT LEADER LENGTH500minPP 1P 0D 0FWD 1Unit : mmREEL DIMENSIONSUNIT IN mmTYPE G N T M D K L R20 QFN(4X4)24 QFN(4X4) 32 QFN(5X5)DFN-1012.8+0.6/-0.4100 REF18.2(MAX)1.75±0.2513.0+0.5/-0.22.0±0.5330+0.00/-1.020.248 QFN(7X7)16.8+0.6/-0.4100 REF22.2(MAX)1.75±0.2513.0+0.5/-0.22.0±0.5330+0.00/-1.020.228 SSOP (150mil)20.4+0.6/-0.4100 REF25(MAX) 1.75±0.2513.0+0.5/-0.22.0±0.5330+0.00/-1.020.220 SSOP24 SSOP16.4+2.0/-0.0100 REF22.4(MAX)1.75±0.2513.0+0.2/-0.21.9±0.4330+0.00/-1.020.2MDTKUSE OF THE REEL FOR ‘/Q’ TYPEIC IC20 QFN(4X4); 32 QFN(5X5); 48QFN(7X7);SSOP28(150mil)RF ICs AMICCOM15 Product StatusData Sheet Identification Product StatusDefinitionObjectivePlanned or Under DevelopmentThis data sheet contains the design specifications for product development. Specifications may change in any manner without notice.PreliminaryEngineering Samples and First ProductionThis data sheet contains preliminary data, and supplementary data will be published at a later date.AMICCOM reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.No Identification Noted Full ProductionThis data sheet contains the final specifications.AMICCOM reserves the right to make changes at any time without notice in order to improve design and supply the best possible product.Obsolete Not In ProductionThis data sheet contains specifications on aproduct that has been discontinued by AMICCOM.The data sheet is printed for reference information only.Headquarter5F, No.2, Li-Hsin Rd. 6, Hsinchu Science Park ,Taiwan 30078Tel: 886-3-5785818Taipei Office7F, No.407, Rueiguang Rd., Nei-Hu, Taipei,Taiwan 11492。

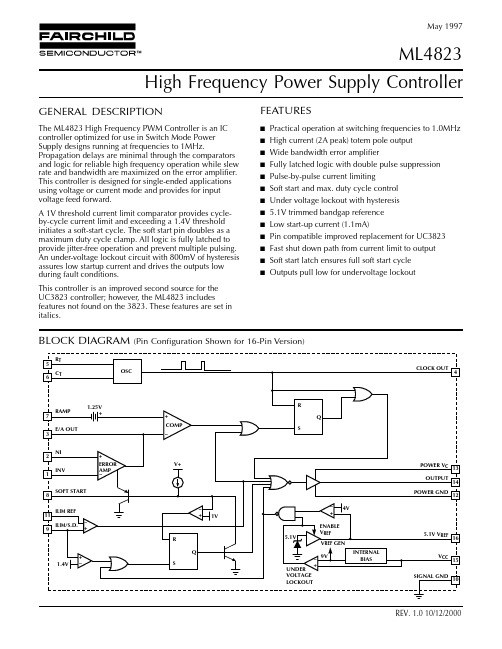

ML4823中文资料

May 1997ML4823High Frequency Power Supply ControllerFEATURESs Practical operation at switching frequencies to 1.0MHz s High current (2A peak) totem pole output s Wide bandwidth error amplifiers Fully latched logic with double pulse suppression s Pulse-by-pulse current limitings Soft start and max. duty cycle control s Under voltage lockout with hysteresis s 5.1V trimmed bandgap references Low start-up current (1.1mA)s Pin compatible improved replacement for UC3823s Fast shut down path from current limit to output s Soft start latch ensures full soft start cycle sOutputs pull low for undervoltage lockoutGENERAL DESCRIPTIONThe ML4823 High Frequency PWM Controller is an IC controller optimized for use in Switch Mode Power Supply designs running at frequencies to 1MHz.Propagation delays are minimal through the comparators and logic for reliable high frequency operation while slew rate and bandwidth are maximized on the error amplifier.This controller is designed for single-ended applications using voltage or current mode and provides for input voltage feed forward.A 1V threshold current limit comparator provides cycle-by-cycle current limit and exceeding a 1.4V threshold initiates a soft-start cycle. The soft start pin doubles as a maximum duty cycle clamp. All logic is fully latched to provide jitter-free operation and prevent multiple pulsing.An under-voltage lockout circuit with 800mV of hysteresis assures low startup current and drives the outputs low during fault conditions.This controller is an improved second source for the UC3823 controller; however, the ML4823 includesfeatures not found on the 3823. These features are set in italics.BLOCK DIAGRAM (Pin Configuration Shown for 16-Pin Version)ML4823 ABSOLUTE MAXIMUM RATINGSAbsolute maximum ratings are those values beyond whichthe device could be permanently damaged. Absolutemaximum ratings are stress ratings only and functionaldevice operation is not implied.Supply Voltage (V C, V CC) (30V)OUTPUT Current, Source or Sink DC.......................................................................0.5APulse (0.5µs).........................................................2.0AAnalog Inputs(INV, NI, RAMP, SS, I LIM)..................GND –0.3V to 6V CLOCK OUTPUT Current......................................–5mA F/A OUT Current......................................................5mA SOFT START Sink Current.......................................20mA R T Charging Current...............................................–5mA OPERATING CONDITIONSTemperature RangeML4823C..................................................0°C to 70°C ML4823I................................................–40°C to 85°C Junction Temperature............................................125°C Storage Temperature Range.....................–65°C to 150°C Lead Temperature (Soldering 10 sec.)....................260°C Thermal Resistance (θJA)Plastic DIP.......................................................80°C/W Plastic SOIC...................................................105°C/W Plastic Chip Carrier (PLCC)..............................78°C/WELECTRICAL CHARACTERISTICSUnless otherwise specified, R T = 3.65kΩ, C T = 1000pF, T A = Operating Temperature Range, V CC = 15V. (Note 1) PARAMETER CONDITIONS MIN TYP MAX UNITS OSCILLATORInitial Accuracy T J = 25°C,360400440kHz Voltage Stability10V ≤ V CC≤ 30V,0.22% Temperature Stability5% Total Variation Line, temp.340460kHz Clock Out High 3.9 4.5V Clock Out Low 2.3 2.9V Ramp Peak 2.6 2.8 3.0V Ramp Valley0.7 1.0 1.25V Ramp Valley to Peak 1.6 1.8 2.0V REFERENCEOutput Voltage T J = 25°C, I O = 1mA 5.025 5.10 5.175V Line Regulation10V ≤ V CC≤ 30V220mV Load Regulation1mA ≤ I O≤ 10mA520mV Temperature Stability–40°C ≤ T J≤ 150°C,0.20.4% Total Variation Line, load, temp. 4.975 5.225V Output Noise Voltage10Hz to 10kHz50µV Long Term Stability T J = 125°C, 1000 hrs,525mV Short Circuit Current V REF = 0V–15–50–100mA ERROR AMPLIFIERInput Offset Voltage±30mV Input Bias Current0.63µA Input Offset Current0.11µA Open Loop Gain 1 ≤ V O≤ 4V5095dBML4823ELECTRICAL CHARACTERISTICS (Continued)PARAMETER CONDITIONS MIN TYP MAX UNITS ERROR AMPLIFIER (Continued)CMRR 1.5 ≤ V CC≤ 5.5V5080dB PSRR10 ≤ V CC≤ 30V70100dB Output Sink Current V E/A OUT = 1V1 2.5mA Output Source Current V E/A OUT = 4V–0.5–1.3mA Output High Voltage I E/A OUT = –0.5mA 4.0 4.7 5.0V Output Low Voltage I E/A OUT = 1mA00.5 1.0V Unity Gain Bandwidth3 5.5MHz Slew Rate612V/µs PWM COMPARATORRAMP Bias Current V RAMP = 0V–1–5µA Duty Cycle Range080% E/A OUT Zero DC Threshold V RAMP = 0V 1.1 1.25V Delay to Output5080ns SOFT STARTCharge Current V SOFT START = 0.5V3920µA Discharge Current V SOFT START = 1V1mA CURRENT LIMIT/SHUTDOWNI LIM Bias Current0V ≤ I LIM≤ 4V±10µA Current Limit Offset I LIM REF = 1.1V015mV I LIM REF Common Mode Range 1.0 1.25V Shutdown Threshold 1.25 1.40 1.55V Delay to Output5080ns OUTPUTOutput Low Level I OUT = 20mA0.250.40VI OUT = 200mA 1.2 2.2V Output High Level I OUT = –20mA12.813.5VI OUT = –200mA12.013.0V Collector Leakage V C = 30V100500µA Rise/Fall Time C L = 1000pF3060ns UNDER VOLTAGE LOCKOUTStart Threshold8.89.29.7V UVLO Hysteresis0.40.8 1.2V SUPPLYStart Up Current V CC = 8V 1.1 2.5mA I CC INV, RANP, I LIM = 0V2233mANI = 1VNote 1:Limits are guaranteed by 100% testing, sampling, or correlation with worst-case test conditions.ML4823 SOFT START AND CURRENT LIMITThe ML4823 employs two current limits. When thevoltage at I LIM/SD exceeds the I LIM REF threshold on I LIMREF, the outputs are immediately shut off and the cycle isterminated for the remainder of the oscillator period byresetting the RS flip flop.If the output current is rising quickly (usually due totransformer saturation) such that the voltage on pin 9reaches 1.4V before the outputs have turned off, a softstart cycle is initiated. The soft start capacitor is dischargedand outputs are held “off” until the voltage at SS reaches1V, ensuring a complete soft start cycle. The duty cycle onstart up is limited by limiting the output voltage of theerror amplifier voltage to the voltage at the SS pin.。

仕芯LM4863中文说明

0.3

%

RL=8Ω

0.3

%

Vdd=4.9V to 5.1V

52

dB

最小谐波失真 电源抑制比

THD

PSR R

f=1kHz,CB=1uF Vdd=5V, Po=1.1W

CB=1.0uF, VPIPPLE=200mVRMS,f=1khz

60

dB

95

dB

52

dB

通道隔离度

XTAL

K

f=1khz, CB=1.0uF

-0.3 to +(0.3+Vdd)

V

PD

见附注 1

W

结温度

150

℃

蒸发状态(60 秒)

215

℃

红外线 (15 秒)

220

℃

附注 1:最大功耗取决于三个因素:TJMAX,TA,θJA 它的计算公式 PDMAX=(TJMAX-TA)/θJA ,CSC4863 的 TJMAX=150℃. TA 为外部 环境的温度,θJA 取决于不同的封装形式。(TSSOP 封装形式的为 20℃/W)

封装外形图三:(LM4863F)TSSOP 20

LM4863

深圳仕芯半导体有限公司

TEL:13480743050 QQ254343262

第六页 共六页

/04863

双通道立体声音频功率放大器

LM4863

概述与特点

LM4863 是一个双路音频功率放大器.它能够在 5V 电源电压下给一个 4Ω负载提供 THD 小于 10%、最 大平均值为 2.46W 的输出功率。另外,在驱动立体声耳机时耳机输入引脚可以使放大器工作在单边模式。

LM4863 是为提供高保真音频输出而专门设计的.它仅仅需要少量的外围元件,为了简化音频系统设计, LM4863 集双路桥式扬声器放大器和立体声耳机放大器与一体。LM4863 还有外部控制的关闭模式,立体声 耳机放大器模式和热保护关闭模式,还有减少开机噪声功能。

CS4863中文说明书

编号:CS4863-AX-BJ-39

1、概 述

CS4863 是双桥接的音频功率放大器。当电源电压为 5V 时,在保证总谐波失真、噪声失真之 和小于 1.0%的情况下,可向 4Ω负载提供 2.2W 的输出功率或者可向 3Ω负载提供 2.5W 的输出功 率。另外,当驱动立体声耳机时,耳机输入端允许放大器工作在单端模式。

201201b1电气参数电路工作在桥接模式vdd5vta25cs4863符号参数条件典型极限单位极限os输出偏移电压50mvmax输出功率thdn1f1khzcs4863mtethdn10f1khzcs4863mter322525222211323227271503410thdn总谐波失真和噪20hzf20khzavd2wcs4863lq2wcs48631w030303psrr电源纹波抑制比dd5vripple200mvrms67dbtalk通道隔离度f1khzc10f90dbsnr信噪比dd5vr11w98db电气参数电路工作在单端模式vdd5vta25cs4863符号参数条件典型极限单位极限os输出偏移电压50mvmax输出功率thdn05f1khz32thdn1f1khzthdn10f1khz8534044075mwminmwmwthdn总谐波失真和噪75mw02psrr电源纹波抑制比ripple200mvrmsf1khzc10f52dbtalk通道隔离度f1khzc10f60dbsnr信噪比dd5vr340mw95dbtstab上电稳定时间033ufvdd5v240ms无锡中微爱芯电子有限公司wuxiicoreelectronicsco

应用信息

1.桥式配置说明

如图(1)所示,CS4863 内部有两对运算放大器,形成两个通道(通道 A 和通道 B)的立体声放大器。 (以下为 A 通道的论述,同时也适合于 B 通道。)放大器 Amp1A 的增益是外部配置结构决定,闭环 增益通过配置 Rf 和 Ri 的来决定,而放大器 Amp2A 被两个 20kΩ的内部电阻固定增益为-1,构成倒相

LM4863中文资料

LM4863Dual 2.2W Audio Amplifier Plus Stereo Headphone FunctionGeneral DescriptionThe LM4863is a dual bridge-connected audio power ampli-fier which,when connected to a 5V supply,will deliver 2.2W to a 4Ωload (Note 1)or 2.5W to a 3Ωload (Note 2)with less than 1.0%THD+N.In addition,the headphone input pin al-lows the amplifiers to operate in single-ended mode to drive stereo headphones.Boomer audio power amplifiers were designed specifically to provide high quality output power from a surface mount package while requiring few external components.To sim-plify audio system design,the LM4863combines dual bridge speaker amplifiers and stereo headphone amplifiers on one chip.The LM4863features an externally controlled,low-power consumption shutdown mode,a stereo headphone amplifier mode,and thermal shutdown protection.It also utilizes cir-cuitry to reduce “clicks and pops”during device turn-on.Note 1:An LM4863MTE which has been properly mounted to the circuit board will deliver 2.2W into 4Ω.The other package options for the LM4863will deliver 1.1W into 8Ω.See the Application Information section for LM4863MTE usage information.Note 2:An LM4863MTE which has been properly mounted to the circuit board and forced-air cooled will deliver 2.5W into 3Ω.Key Specificationsn P O at 1%THD+Ninto 3Ω(LM4863MTE) 2.5W(typ)into 4Ω(LM4863MTE) 2.2W(typ)into 8Ω(LM4863)1.1W(typ)n Single-ended mode -THD+N at 75mW into 32Ω0.5%(max)n Shutdown current0.7µA(typ)Featuresn Stereo headphone amplifier mode n “Click and pop”suppression circuitry n Unity-gain stablen Thermal shutdown protection circuitrynExposed-DAP TSSOP ,TSSOP ,SOIC and DIP packaging availableApplicationsn Multimedia monitorsn Portable and desktop computers n Portable televisionsTypical ApplicationBoomer ®is a registered trademark of National Semiconductor Corporation.DS012881-1*Refer to the section Proper Selection of External Components,for a detailed discussion of C B size.FIGURE 1.Typical Audio Amplifier Application CircuitOctober 1999LM4863Dual 2.2W Audio Amplifier Plus Stereo Headphone Function©1999National Semiconductor Corporation Connection DiagramsDS012881-28Top ViewOrder Number LM4863M,LM4863N See NS Package Number M16B for SO See NS Package Number N16A for DIPDS012881-2Top ViewOrder Number LM4863MTESee NS Package Number MXA20A for Exposed-DAP TSSOPL M 4863 2Absolute Maximum Ratings(Note4)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage 6.0V Storage Temperature−65˚C to+150˚C Input Voltage−0.3V to V DD+0.3V Power Dissipation(Note10)Internally limited ESD Susceptibility(Note11)2000V ESD Susceptibility(Note12)200V Junction Temperature150˚C Solder InformationSmall Outline PackageVapor Phase(60sec.)215˚C Infrared(15sec.)220˚C See AN-450“Surface Mounting and their Effects onProduct Reliablilty”for other methods of soldering surfacemount devices.Thermal ResistanceθJC(typ)—M16B20˚C/W θJA(typ)—M16B80˚C/W θJC(typ)—N16A20˚C/W θJA(typ)—N16A63˚C/W θJC(typ)—MTC2020˚C/W θJA(typ)—MTC2080˚C/W θJC(typ)—MXA20A2˚C/W θJA(typ)—MXA20A41˚C/W(Note7)θJA(typ)—MXA20A51˚C/W(Note5)θJA(typ)—MXA20A90˚C/W(Note6) Operating RatingsTemperature RangeT MIN≤T A≤T MAX−40˚C≤T A≤85˚C Supply Voltage 2.0V≤V DD≤5.5VElectrical Characteristics for Entire IC(Notes3,4)The following specifications apply for V DD=5V unless otherwise noted.Limits apply for T A=25˚C.Symbol Parameter Conditions LM4863Units(Limits)Typical Limit(Note13)(Note14)V DD Supply Voltage2V(min)5.5V(max)I DD Quiescent Power Supply Current V IN=0V,I O=0A(Note15),HP-IN=0V11.520mA(max)6mA(min)V IN=0V,I O=0A(Note15),HP-IN=4V 5.8mAI SD Shutdown Current V PIN1=V DD0.72µA(min) V IH Headphone High Input Voltage4V(min) V IL Headphone Low Input Voltage0.8V(max)Electrical Characteristics for Bridged-Mode Operation(Notes3,4)The following specifications apply for V DD=5V unless otherwise specified.Limits apply for T A=25˚C.Symbol Parameter Conditions LM4863Units(Limits)Typical Limit(Note 13)(Note 14)V OS Output Offset Voltage V IN=0V550mV(max) P O Output Power(Note9)THD=1%,f=1kHzLM4863MTE,R L=3Ω(Note7)2.5WLM4863MTE,R L=4Ω(Note8) 2.2WLM4863,R L=8Ω 1.1 1.0W(min)THD+N=10%,f=1kHzLM4863MTE,R L=3Ω(Note7) 3.2WLM4863MTE,R L=4Ω(Note8) 2.7LM4863,R L=8Ω 1.5WTHD+N=1%,f=1kHz,R L=32Ω0.34W THD+N Total Harmonic Distortion+Noise20Hz≤f≤20kHz,A VD=2LM4863MTE,R L=4Ω,P O=2W0.3LM4863,R L=8Ω,P O=1W0.3%PSRR Power Supply Rejection Ratio V DD=5V,V RIPPLE=200mV RMS,R L=8Ω,C B=1.0µF 67dBLM48633Electrical Characteristics for Bridged-Mode Operation (Notes 3,4)(Continued)The following specifications apply for V DD =5V unless otherwise specified.Limits apply for T A =25˚C.SymbolParameterConditionsLM4863Units (Limits)Typical Limit (Note 13)(Note 14)X TALK Channel Separation f =1kHz,C B =1.0µF90dB SNRSignal To Noise Ratio V DD =5V,P O =1.1W,R L =8Ω98dBElectrical Characteristics for Single-Ended Operation (Notes 3,4)The following specifications apply for V DD =5V unless otherwise specified.Limits apply for T A =25˚C.SymbolParameterConditionsLM4863Units (Limits)Typical Limit (Note 13)(Note 14)V OS Output Offset Voltage V IN =0V550mV (max)P OOutput PowerTHD =0.5%,f =1kHz,R L =32Ω8575mW (min)THD+N =1%,f =1kHz,R L =8Ω340mW THD+N =10%,f =1kHz,R L =8Ω440mW THD+N Total Harmonic Distortion+Noise A V =−1,P O =75mW,20Hz ≤f ≤20kHz,R L =32Ω0.2%PSRR Power Supply Rejection Ratio C B =1.0µF,V RIPPLE =200mV RMS ,f =1kHz52dB X TALK Channel Separation f =1kHz,C B =1.0µF60dB SNRSignal To Noise RatioV DD =5V,P O =340mW,R L =8Ω95dB Note 3:All voltages are measured with respect to the ground pins,2,7,and 15,unless otherwise specified.Note 4:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is func-tional,but do not guarantee specific performance limits.Electrical Characteristics state DC and AC electrical specifications under particular test conditions which guar-antee specific performance limits.This assumes that the device is within the Operating Ratings.Specifications are not guaranteed for parameters where no limit is given,however,the typical value is a good indication of device performance.Note 5:The θJA given is for an MXA20A package whose exposed-DAP is soldered to an exposed 2in 2piece of 1ounce printed circuit board copper.Note 6:The θJA given is for an MXA20A package whose exposed-DAP is not soldered to any copper.Note 7:When driving 3Ωloads from a 5V supply,the LM4863MTE must be mounted to the circuit board and forced-air cooled (450linear-feet per minute).Note 8:When driving 4Ωloads from a 5V supply,the LM4863MTE must be mounted to the circuit board.Note 9:Output power is measured at the device terminals.Note 10:The maximum power dissipation must be derated at elevated temperatures and is dictated by T JMAX ,θJA ,and the ambient temperature T A .The maximum allowable power dissipation is P DMAX =(T JMAX −T A )/θJA .For the LM4863,T JMAX =150˚C.For the θJA s for different packages,please see the Application Informa-tion section or the Absolute Maximum Ratings section.Note 11:Human body model,100pF discharged through a 1.5k Ωresistor.Note 12:Machine model,220pF–240pF discharged through all pins.Note 13:Typicals are measured at 25˚C and represent the parametric norm.Note 14:Limits are guaranteed to National’s AOQL (Average Outgoing Quality Level).Note 15:The quiescent power supply current depends on the offset voltage when a practical load is connected to the amplifier.Truth Table for Logic InputsSHUTDOWNHP-IN LM4863MODELow Low Bridged Low High Single-Ended High Low LM4863Shutdown HighHighLM4863ShutdownL M 4863 4External Components Description(Figure 1)Components Functional Description1.R i Inverting input resistance which sets the closed-loop gain in conjunction with R f .This resistor also forms a high pass filter with C i at f c =1/(2πR i C i ).2.C iInput coupling capacitor which blocks the DC voltage at the amplifier’s input terminals.Also creates ahighpass filter with R i at f c =1/(2πR i C i ).Refer to the section,Proper Selection of External Components ,for an explanation of how to determine the value of C i .3.R f Feedback resistance which sets the closed-loop gain in conjunction with R i .4.C s Supply bypass capacitor which provides power supply filtering.Refer to the Power Supply Bypassing section for information concerning proper placement and selection of the supply bypass capacitor.5.C BBypass pin capacitor which provides half-supply filtering.Refer to the section,Proper Selection of External Components ,for information concerning proper placement and selection of C B .Typical Performance Characteristics MTE Specific CharacteristicsNote 16:These curves show the thermal dissipation ability of the LM4863MTE at different ambient temperatures given these conditions:500LFPM +JEDEC board:The part is soldered to a 1S2P 20-lead exposed-DAP TSSOP test board with 500linear feet per minute of forced-air flow across it.Board information -copper dimensions:74x74mm,copper coverage:100%(buried layer)and 12%(top/bottom layers),16vias under the exposed-DAP .500LFPM +2.5in 2:The part is soldered to a 2.5in 2,1oz.copper plane with 500linear feet per minute of forced-air flow across it.2.5in 2:The part is soldered to a 2.5in 2,1oz.copper plane.Not Attached:The part is not soldered down and is not forced-air cooled.LM4863MTETHD+N vs Output PowerDS012881-97LM4863MTETHD+N vs FrequencyDS012881-99LM4863MTETHD+N vs Output PowerDS012881-96LM4863MTETHD+N vs FrequencyDS012881-98LM4863MTEPower Dissipation vs Power OutputDS012881-90LM4863MTE (Note 16)Power Derating CurveDS012881-95LM48635Non-MTE Specific CharacteristicsTHD+N vs FrequencyDS012881-3THD+N vs FrequencyDS012881-4THD+N vs FrequencyDS012881-5THD+N vs Output Power DS012881-6THD+N vs Output Power DS012881-7THD+N vs Output PowerDS012881-8THD+N vs Output Power DS012881-87THD+N vs Frequency DS012881-89THD+N vs Output PowerDS012881-88Output Power vs Load ResistanceDS012881-84Power Dissipation vs Supply VoltageDS012881-85L M 4863 6Non-MTE Specific Characteristics(Continued)Output Power vs Supply VoltageDS012881-9Output Power vs Supply VoltageDS012881-10Output Power vs Supply VoltageDS012881-11Output Power vs Load Resistance DS012881-12Output Power vs Load Resistance DS012881-13Power Dissipation vs Output PowerDS012881-14Dropout Voltage vs Supply VoltageDS012881-15Power Derating CurveDS012881-16Power Dissipation vs Output PowerDS012881-17Noise Floor DS012881-18Channel Separation DS012881-19Channel SeparationDS012881-20LM48637Non-MTE Specific Characteristics(Continued)Application InformationEXPOSED-DAP MOUNTING CONSIDERATIONSThe exposed-DAP must be connected to ground.The exposed-DAP package of the LM4863MTE requires special attention to thermal design.If thermal design issues are not properly addressed,an LM4863MTE driving 4Ωwill go into thermal shutdown.The exposed-DAP on the bottom of the LM4863MTE should be soldered down to a copper pad on the circuit board.Heat is conducted away from the exposed-DAP by a copper plane.If the copper plane is not on the top surface of the cir-cuit board,8to 10vias of 0.013inches or smaller in diameter should be used to thermally couple the exposed-DAP to the plane.For good thermal conduction,the vias must be plated-through and solder-filled.The copper plane used to conduct heat away from the exposed-DAP should be as large as pratical.If the plane is on the same side of the circuit board as the exposed-DAP ,2.5in 2is the minimum for 5V operation into 4Ω.If the heat sink plane is buried or not on the same side as the exposed-DAP ,5in 2is the minimum for 5V operation into 4Ω.If the am-bient temperature is higher than 25˚C,a larger copper plane or forced-air cooling will be required to keep the LM4863MTE junction temperature below the thermal shut-down temperature (150˚C).See the power derating curve for the LM4863MTE for derating information.The LM4863MTE requires forced-air cooling when operating into 3Ω.With the part attached to 2.5in 2of exposed copper,with a 3Ωload,and with an ambient temperature of 25˚C,450linear-feet per minute kept the part out of thermal shut-down.In higher ambient temperatures,higher airflow rates and/or larger copper areas will be required to keep the part out of thermal shutdown.See DEMOBOARD CIRCUIT LAYOUT for an example of an exposed-DAP TSSOP circuit board layout.3Ω&4ΩLAYOUT CONSIDERATIONSWith low impedance loads,the output power at the loads is heavily dependent on trace resistance from the output pins of the LM4863.Traces from the output of the LM4863MTE to the load or load connectors should be as wide as practical.Any resistance in the output traces will reduce the power de-livered to the load.For example,with a 4Ωload and 0.1Ωof trace resistance in each output,output power at the load drops from 2.2W to 2.0WOutput power is also dependent on supply regulation.To keep the supply voltage from sagging under full output power conditions,the supply traces should be as wide as practical.BRIDGE CONFIGURATION EXPLANATIONAs shown in Figure 1,the LM4863has two pairs of opera-tional amplifiers internally,allowing for a few different ampli-fier configurations.The first amplifier’s gain is externally con-figurable,while the second amplifier is internally fixed in a unity-gain,inverting configuration.The closed-loop gain of the first amplifier is set by selecting the ratio of R f to R i while the second amplifier’s gain is fixed by the two internal 20k Ωresistors.Figure 1shows that the output of amplifier one serves as the input to amplifier two which results in both am-plifiers producing signals identical in magnitude,but out of phase 180˚.Consequently,the differential gain for each channel of the IC isA VD =2*(R f /R i )By driving the load differentially through outputs +OutA and −OutA or +OutB and −OutB,an amplifier configuration com-monly referred to as “bridged mode”is established.Bridged mode operation is different from the classical single-ended amplifier configuration where one side of its load is con-nected to ground.A bridge amplifier design has a few distinct advantages over the single-ended configuration,as it provides differential drive to the load,thus doubling the output swing for a speci-fied supply voltage.Four times the output power is possible as compared to a single-ended amplifier under the same conditions.This increase in attainable output power as-sumes that the amplifier is not current limited or clipped.In order to choose an amplifier’s closed-loop gain without caus-ing excessive clipping,please refer to the Audio Power Am-plifier Design section.A bridge configuration,such as the one used in LM4863,also creates a second advantage over single-ended amplifi-ers.Since the differential outputs,+OutA,−OutA,+OutB,and −OutB,are biased at half-supply,no net DC voltage ex-ists across the load.This eliminates the need for an output coupling capacitor which is required in a single supply,single-ended amplifier configuration.If an output coupling capacitor is not used in a single-ended configuration,the half-supply bias across the load would result in both in-creased internal IC power dissipation as well as permanent loudspeaker damage.Power Supply Rejection RatioDS012881-21Open LoopFrequency ResponseDS012881-22Supply Current vs Supply Voltage 8Application Information(Continued)POWER DISSIPATIONWhether the power amplifier is bridged or single-ended, power dissipation is a major concern when designing the amplifier.Equation1states the maximum power dissipation point for a single-ended amplifier operating at a given supply voltage and driving a specified load.P DMAX=(V DD)2/(2π2R L):Single-Ended(1) However,a direct consequence of the increased power de-livered to the load by a bridge amplifier is an increase in in-ternal power dissipation.Equation2states the maximum power dissipation point for a bridge amplifier operating at the same given conditions.P DMAX=4*(V DD)2/(2π2R L):Bridge Mode(2) Since the LM4863is a dual channel power amplifier,the maximum internal power dissipation is2times that of Equa-tion1or Equation2depending on the mode of operation. Even with this substantial increase in power dissipation,the LM4863does not require heatsinking.The power dissipation from Equation2,assuming a5V power supply and an8Ωload,must not be greater than the power dissipation that re-sults from Equation3:P DMAX=(T JMAX−T A)/θJA(3) For packages M16A and MTA20,θJA=80˚C/W,and for package N16A,θJA=63˚C/W.T JMAX=150˚C for the LM4863.Depending on the ambient temperature,T A,of the system surroundings,Equation3can be used to find the maximum internal power dissipation supported by the IC packaging.If the result of Equation2is greater than that of Equation3,then either the supply voltage must be de-creased,the load impedance increased,or the ambient tem-perature reduced.For the typical application of a5V power supply,with an8Ωbridged load,the maximum ambient tem-perature possible without violating the maximum junction temperature is approximately48˚C provided that device op-eration is around the maximum power dissipation point and assuming surface mount packaging.Internal power dissipa-tion is a function of output power.If typical operation is not around the maximum power dissipation point,the ambient temperature can be increased.Refer to the Typical Perfor-mance Characteristics curves for power dissipation infor-mation for different output powers.POWER SUPPLY BYPASSINGAs with any power amplifier,proper supply bypassing is criti-cal for low noise performance and high power supply rejec-tion.The capacitor location on both the bypass and power supply pins should be as close to the device as possible.The effect of a larger half supply bypass capacitor is improved PSRR due to increased half-supply stability.Typical applica-tions employ a5V regulator with10µF and a0.1µF bypass capacitors which aid in supply filtering.This does not elimi-nate the need for bypassing the supply nodes of the LM4863.The selection of bypass capacitors,especially C B, is thus dependent upon desired PSRR requirements,click and pop performance as explained in the section,Proper Selection of External Components,system cost,and size constraints.SHUTDOWN FUNCTIONIn order to reduce power consumption while not in use,the LM4863contains a shutdown pin to externally turn off the amplifier’s bias circuitry.This shutdown feature turns the am-plifier off when a logic high is placed on the shutdown pin.The trigger point between a logic low and logic high level istypically half supply.It is best to switch between ground andthe supply V DD to provide maximum device performance.Byswitching the shutdown pin to V DD,the LM4863supply cur-rent draw will be minimized in idle mode.While the devicewill be disabled with shutdown pin voltages less than V DD,the idle current may be greater than the typical value of0.7µA.In either case,the shutdown pin should be tied to adefinite voltage to avoid unwanted state changes.In many applications,a microcontroller or microprocessoroutput is used to control the shutdown circuitry which pro-vides a quick,smooth transition into shutdown.Another solu-tion is to use a single-pole,single-throw switch in conjunctionwith an external pull-up resistor.When the switch is closed,the shutdown pin is connected to ground and enables theamplifier.If the switch is open,then the external pull-up re-sistor will disable the LM4863.This scheme guarantees thatthe shutdown pin will not float,thus preventing unwantedstate changes.HP-IN FUNCTIONThe LM4863possesses a headphone control pin that turnsoff the amplifiers which drive+OutA and+OutB so thatsingle-ended operation can occur and a bridged connectedload is muted.Quiescent current consumption is reducedwhen the IC is in this single-ended mode.Figure2shows the implementation of the LM4863’s head-phone control function using a single-supply headphone am-plifier.The voltage divider of R1and R2sets the voltage atthe HP-IN pin(pin16)to be approximately50mV when thereare no headphones plugged into the system.This logic-lowvoltage at the HP-IN pin enables the LM4863and places it inbridged mode operation.Resistor R4limits the amount ofcurrent flowing out of the HP-IN pin when the voltage at thatpin goes below ground resulting from the music coming fromthe headphone amplifier.The output coupling capacitors pro-tect the headphones by blocking the amplifier’s half supplyDC voltage.When there are no headphones plugged into the system andthe IC is in bridged mode configuration,both loads are es-sentially at a0V DC potential.Since the HP-IN threshold isset at4V,even in an ideal situation,the output swing cannotcause a false single-ended trigger.When a set of headphones are plugged into the system,thecontact pin of the headphone jack is disconnected from thesignal pin,interrupting the voltage divider set up by resistorsR1and R2.Resistor R1then pulls up the HP-IN pin,en-abling the headphone function.This disables the secondside of the amplifier thus muting the bridged speakers.Theamplifier then drives the headphones,whose impedance isin parallel with resistors R2and R3.Resistors R2and R3have negligible effect on output drive capability since thetypical impedance of headphones are32Ω.Also shown inFigure2are the electrical connections for the headphonejack and plug.A3-wire plug consists of a Tip,Ring andSleave,where the Tip and Ring are signal carrying conduc-tors and the Sleave is the common ground return.One con-trol pin contact for each headphone jack is sufficient to indi-cate to control inputs that the user has inserted a plug into ajack and that another mode of operation is desired.The LM4863can be used to drive both a pair of bridged8Ωspeakers and a pair of32Ωheadphones without using theHP-IN pin.In this case the HP-IN would not be connected tothe headphone jack but to a microprocessor or a switch.Byenabling the HP-IN pin,the8Ωspeakers can be muted.LM48639Application Information(Continued)PROPER SELECTION OF EXTERNAL COMPONENTS Proper selection of external components in applications us-ing integrated power amplifiers is critical to optimize device and system performance.While the LM4863is tolerant to avariety of external component combinations,consideration to component values must be used to maximize overall sys-tem quality.The LM4863is unity-gain stable,giving the designer maxi-mum system performance.The LM4863should be used in low gain configurations to minimize THD+N values,and maximize the signal to noise ratio.Low gain configurations require large input signals to obtain a given output power.In-put signals equal to or greater than 1Vrms are available from sources such as audio codecs.Please refer to the sec-tion,Audio Power Amplifier Design ,for a more complete explanation of proper gain selection.Besides gain,one of the major considerations is the closed-loop bandwidth of the amplifier.To a large extent,the bandwidth is dictated by the choice of external components shown in Figure 1.The input coupling capacitor,C i ,forms a first order high pass filter which limits low frequency re-sponse.This value should be chosen based on needed fre-quency response for a few distinct reasons.CLICK AND POP CIRCUITRYThe LM4863contains circuitry to minimize turn-on transients or “clicks and pops”.In this case,turn-on refers to either power supply turn-on or the device coming out of shutdown mode.When the device is turning on,the amplifiers are inter-nally configured as unity gain buffers.An internal current source ramps up the voltage of the bypass pin.Both the in-puts and outputs ideally track the voltage at the bypass pin.The device will remain in buffer mode until the bypass pin has reached its half supply voltage,1/2V DD .As soon as the bypass node is stable,the device will become fully opera-tional,where the gain is set by the external resistors.Although the bypass pin current source cannot be modified,the size of C B can be changed to alter the device turn-on time and the amount of “clicks and pops”.By increasing amount of turn-on pop can be reduced.However,the tradeoff for using a larger bypass capacitor is an increase in turn-on time for this device.There is a linear relationship be-tween the size of C B and the turn-on time.Here are some typical turn-on times for a given C B :C B T ON 0.01µF 20ms 0.1µF 200ms 0.22µF 420ms 0.47µF 840ms 1.0µF2SecIn order eliminate “clicks and pops”,all capacitors must be discharged before turn-on.Rapid on/off switching of the de-vice or the shutdown function may cause the “click and pop”circuitry to not operate fully,resulting in increased “click and pop”noise.In a single-ended configuration,the output cou-pling capacitor,C O ,is of particular concern.This capacitor discharges through the internal 20k Ωresistors.Depending on the size of C O ,the time constant can be relatively large.To reduce transients in single-ended mode,an external 1k Ω–5k Ωresistor can be placed in parallel with the internal 20k Ωresistor.The tradeoff for using this resistor is an in-crease in quiescent current.The value of C I will also reflect turn-on pops.Clearly,a cer-tain size for C I is needed to couple in low frequencies without excessive attenuation.But in many cases,the speakers used in portable systems,whether integral or external,have little ability to reproduce signals below 100Hz to 150Hz.In this case,using a large input and output capacitor may not increase system performance.In most cases,choosing a small value of C I in the range of 0.1µF to 0.33µF),along with C B equal to 1.0µF should produce a virtually clickless and popless turn-on.In cases where C I is larger than 0.33µF,it may be advantageous to increase the value of C B .Again,it should be understood that increasing the value of C B will reduce the “clicks and pops”at the expense of a longer device turn-on time.DS012881-24FIGURE 2.Headphone CircuitL M 486310Application Information(Continued)NO-LOAD DESIGN CONSIDERATIONSIf the outputs of the LM4863have a load higher than10kΩ,the LM4863may show a small oscillation at high output lev-els.To prevent this oscillation,place5kΩresistors from thepower outputs to ground.AUDIO POWER AMPLIFIER DESIGNDesign a1W/8ΩBridged Audio AmplifierGiven:Power Output:1WrmsLoad Impedance:8ΩInput Level:1VrmsInput Impedance:20kΩBandwidth:100Hz−20kHz±0.25dBA designer must first determine the minimum supply rail toobtain the specified output power.By extrapolating from theOutput Power vs Supply Voltage graphs in the Typical Per-formance Characteristics section,the supply rail can beeasily found.A second way to determine the minimum sup-ply rail is to calculate the required V opeak using Equation3and add the dropout ing this method,the mini-mum supply voltage would be(V opeak+(2*V od)),where V odis extrapolated from the Dropout Voltage vs Supply Voltagecurve in the Typical Performance Characteristics section.(4)Using the Output Power vs Supply Voltage graph for an8Ωload,the minimum supply rail is3.9V.But since5V is a stan-dard supply voltage in most applications,it is chosen for thesupply rail.Extra supply voltage creates headroom that al-lows the LM4863to reproduce peaks in excess of1W with-out producing audible distortion.At this time,the designermust make sure that the power supply choice along with theoutput impedance does not violate the conditions explainedin the Power Dissipation section.Once the power dissipation equations have been addressed,the required differential gain can be determined from Equa-tion4.(5)R f/R i=A VD/2(6)From equation4,the minimum A VD is2.83;use A VD=3Since the desired input impedance was20kΩ,and with aA VD of3,a ratio of1.5:1of R f to R i results in an allocation ofR i=20kΩand R f=30kΩ.The final design step is to ad-dress the bandwidth requirements which must be stated as apair of−3dB frequency points.Five times away from a polegives0.17dB down from passband response,which is betterthan the required±0.25dB specified.f L=100Hz/5=20Hzf H=20kHz x5=100kHzAs stated in the External Components section,R i in con-junction with C i create a highpass filter.C i≥1/(2π*20kΩ*20Hz)=0.397µF;use0.33µFThe high frequency pole is determined by the product of thedesired high frequency pole,f H,and the differential gain,AVD.With a A VD=3and f H=100kHz,the resulting GBWP=150kHz which is much smaller than the LM4863GBWP of3.5MHz.This figure displays that if a designer has a need todesign an amplifier with a higher differential gain,theLM4863can still be used without running into bandwidthproblems.DEMOBOARD CIRCUIT LAYOUTThe demoboard circuit layout is provided here as an ex-ample of a circuit using the LM4863.If an LM4863MTE isused with this layout,the exposed-DAP is soldered down tothe copper pad beneath the part.Heat is conducted awayfrom the part by the two large copper pads in the upper cor-ners of the demoboard.This demoboard provides enough heat dissipation ability toallow an LM4863MTE to output2.2W into4Ωat25˚C.DS012881-94All LayersDS012881-93Silk Screen LayerLM486311。

A43L2616AV-6中文资料