实验二:+0-9999的计数器电路的设计

基于单片机的00-99计数器的设计

郑州科技学院单片机课程设计题目基于单片机的00-99计数器的设计学生姓名xxxxxxxxxx专业班级11级自动化3班学号xxxxxxxxxxx 院(系)电气工程学院指导教师xxxxxxx完成时间2014年12月26日郑州科技学院单片机应用技术课程设计任务书专业11自动化班级3班学号xxxxx 姓名xxxxx一、设计题目基于单片机的00~99计数器的设计二、设计任务与要求1. 把单片机系统中的P0.0/AD0~P0.7/AD7端口与LED数码显示器a1~h1相连;要求:P0.0/AD0对应着a1,P0.1/AD1对应着b1,P0.7/AD7对应着h1。

2. 把单片机系统中的P2.0/A8~P2.7/A15端口与LED数码显示器a2~h2连。

3. 把单片机系统中的P1.7端口与独立式键盘SP1相连。

三、参考文献[1] 李学龙.使用单片机控制的智能遥控电风扇控制器[J].电子电路制作, 2003,9.[2] 耿长清.单片机应用技术[M].北京,化学工业出版社,2001,8.[3] 杨西明.单片机编程与应用技术入门[M].北京:机械工业出版,2004,9.[4] 公茂法.单片机人机接口实例集[M].北京:北京航天航空大学出版社,1998,10.[5] 李全力.单片机原理及应用技术[M].北京:高等教育出版社,2001,7.四、设计时间2014 年12 月15日至2014 年12 月26 日指导教师签名:年月日目录1 课程设计的目的 (1)2 设计思路 (1)3 方案设计 (1)3.1 方案分析 (1)3.2 最小控制系统的设计 (2)4 电路的设计 (4)4.1 数码管显示电路 (4)4.2 键盘输入 (4)4.3 复位电路 (5)4.4 晶振电路 (5)4.4 总原理图 (7)5 程序设计 (8)6 系统调试与结果 (10)7 结论 (11)8 心得体会 (11)参考文献 (13)附录1:总体电路原理图 (14)附录2:实物图 (16)附录3:元器件清单 (17)1课程设计的目的(1) 利用单片机定时器/计数器中断设计秒表,从而实现秒、十分之一秒的计时。

单片机课程设计00-99加计数器(完结版qq)

课程设计课程名称51单片机原理及应用单片机“0~99”加法计数器题目名称程序设计专业班级12级计算机科学与技术2班学生姓名郑伟、刘刚、纪强、岳向阳学号51202012032、5120201200751202012021、51202012018 指导教师刘粉二○一四年十二月蚌埠学院计算机科学与技术系课程设计任务书目录一.前言 (4)二.单片机介绍 (4)(一).AT89C51简介编辑 (4)(二).主要特性编辑 (5)(三).特性概述编辑 (5)(四).管脚说明编辑 (5)(五).芯片擦除编辑 (7)(六).串口通讯 (7)三.课程设计的目的和要求 (11)(一).设计目的 (11)(二).课程设计题目 (11)(三).设计任务及要求 (11)四.总体设计思路 (11)(一).硬件设计思路及系统框图 (11)1.硬件设计思路: (11)2.原器件清单 (12)3.系统框图 (12)(二).软件设计思路: (12)(三).对照表 (12)(四).程序流程图 (13)五.硬件设计 (15)(一).芯片主要特性 (15)(二)管脚说明: (15)(三).排阻的作用 (16)(四).电路图说明 (17)1.添加晶振和复位 (17)2.添加P0和P2两个按键 (17)3. 数码管动态显示 (17)六.软件设计说明 (17)七.使用Keil、preoteus软件调试仿真说明 (19)八.结束语 (20)九.参考文献 (21)附录: (22)(一).汇编源程序 (22)(二).原理图 (24)前言单片机全称叫单片微型计算机(Single Chip Microcomputer),是一种集成在电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的计算机系统。

如何设计简单的计数器电路

如何设计简单的计数器电路在数字电子电路中,计数器是一种常见而重要的电路元件,它能够实现对输入脉冲信号进行计数和展示。

本文将介绍如何设计一个简单的计数器电路。

设计简单的计数器电路可以分为两个步骤:选择适当的计数器类型和设计逻辑电路。

一、选择适当的计数器类型在选择计数器类型时,需要考虑计数器的位数和计数模式。

根据计数器的位数,可以选择4位、8位或更多位的计数器。

根据计数模式,可以选择二进制计数,BCD(二进制编码十进制)计数,或其他计数方式。

以4位二进制计数器为例,设计一个可以从0到15计数的计数器。

二、设计逻辑电路为了实现从0到15的计数,我们可以使用四个JK触发器和适当的逻辑门来构建计数器电路。

首先,将四个JK触发器连接成一个级联结构,即将一个触发器的输出引脚连接到下一个触发器的时钟输入引脚,以此类推。

同时,将第一个触发器的时钟输入引脚连接到输入脉冲信号源。

接下来,需要设置逻辑门来控制计数器的复位和使能。

当计数器达到15时,需要将其复位为0,即重新开始计数。

我们可以使用与门来实现这一功能,将四个触发器的输出引脚连接到与门的输入引脚,当四个引脚全部为高电平时,输出高电平信号,将其作为复位信号。

另外,为了使计数器能够正常工作,还需要设置使能信号。

我们可以使用使能控制器来实现这一功能,将输入脉冲信号和复位信号分别连接到使能控制器的输入引脚,使能控制器的输出引脚连接到四个JK 触发器的使能输入引脚。

通过上述设计,我们就可以获得一个简单的4位计数器电路。

当输入脉冲信号源提供脉冲时,计数器将递增一个单位;当计数器达到15时,将被复位为0,并重新开始计数。

设计计数器电路时,需要注意以下几点:1. 选用适当的计数器类型和位数,根据实际需求确定。

2. 熟悉JK触发器的工作原理和真值表,确保触发器的连线正确。

3. 理解逻辑门的功能,如与门、或门等。

4. 考虑计数器的复位和使能功能,确保计数器能够正常工作。

总结:设计一个简单的计数器电路需要选择适当的计数器类型和设计逻辑电路。

单片机计数器设计

单片机计数器的设计可以根据具体的需求进行灵活的选择。

以下是一个简单的单片机计数器的设计:

确定计数范围:根据需求确定计数器的范围,例如0-99或0-999。

选择计数器类型:根据计数范围选择合适的计数器类型,可以是二进制计数器、十进制计数器或BCD码计数器等。

确定计数方式:确定计数的方式,可以是递增计数、递减计数或双向计数等。

确定计数信号源:确定计数信号的来源,可以是外部信号源或内部时钟信号源。

连接计数器到外设:根据需求将计数器的输出连接到外设,例如LED显示器、数码管或继电器等。

编写计数器程序:使用适当的单片机编程语言编写计数器程序,包括计数器的初始化、计数操作和显示操作等。

测试和调试:在硬件连接完成后,对计数器进行测试和调试,确保计数器功能正常。

以上是一个简单的单片机计数器的设计流程,具体的实施可以根据具体的需求和单片机型号进行调整。

加法计数器电路设计

加法计数器电路设计需要考虑多个因素,包括输入信号、计数器状态、计数规则等。

以下是一个简单的加法计数器电路设计的步骤:

1. 确定计数器的位数:根据需要计数的最大值和最小值,确定计数器的位数。

例如,如果要计数的范围是0到99,则可以选择一个3位的二进制计数器。

2. 确定计数器的状态:根据确定的位数,确定计数器的所有可能状态。

例如,对于一个3位的二进制计数器,有8个可能的状态:000、001、010、011、100、101、110、111。

3. 确定计数规则:根据计数器的状态和输入信号,确定计数器的计数规则。

例如,对于一个3位的二进制加法计数器,可以采用逢十进一的规则,即当计数器的值达到最大值(111)时,下一个输入信号会使计数器的值回绕到最小值(000)。

4. 设计电路:根据上述步骤,设计加法计数器电路。

可以采用门电路、触发器等电子元件来构成加法计数器。

在设计过程中,需要考虑电路的稳定性和可靠性,以及尽量减小功耗和减小体积等问题。

5. 仿真和测试:使用仿真软件对设计的加法计数器电路进行仿真和测试,以确保其功能正确性和性能可靠性。

总之,加法计数器电路设计需要综合考虑多个因素,并采用合适的电子元件和设计方法来实现。

0~9999的计数器电路的设计

EDA实验报告实验二:0~9999的计数器电路的设计1.实验目的(1)进一步熟悉和掌握Quartus II软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验容设计并调试好一个技术围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统(可选用的芯片为ispLSI 1032E-PLCC84或EPM7128S-PL84或XCS05/XCS10-PLCC84芯片)进行硬件验证。

3.实验条件(1)开发软件:Quartus II8.0。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

4.实验设计(1)系统原理框图为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图所示的原理框图构成顶层电路CNT9999。

CNT9999电路原理框图(2)VHDL程序计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL 程序如下。

1)CNT10的VHDL源程序:--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO:OUT STD_LOGIC);END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)ISBEGINIF CLR='1'THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1'THENIF ENA='1'THENIF CQI="1001"THENCQI<="0000";ELSECQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CLK,CQI) ISBEGINIF CLK'EVENT AND CLK='1'THEN IF CQI<"1001"THENCO<='0';ELSECO<='1';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;2)CNT9999的VHDL源程序:--CNT9999.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CNT9999 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));END ENTITY CNT9999;ARCHITECTURE ART OF CNT9999 ISCOMPONENT CNT10 ISPORT(CLK,CLR,ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO:OUT STD_LOGIC);END COMPONENT CNT10;SIGNAL S0,S1,S2,S3:STD_LOGIC;BEGINU0:CNT10 PORT MAP(CLK,CLR,ENA,DOUT(3 DOWNTO 0),S0);U1:CNT10 PORT MAP(S0,CLR,ENA,DOUT(7 DOWNTO 4),S1);U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(11 DOWNTO 8),S2);U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(15 DOWNTO 12),S3);END ARCHITECTURE ART;(3)仿真波形设置本设计包括两个层次,因此先进行底层的十进制计数器CNT10的仿真,再进行顶层CNT9999的仿真。

数字积分器实验报告

北京工业大学课程设计报告数电课设题目数字积分器 班级: 1302421 学号: 13024219 姓 名: 吕迪__________组 号: 7 _________2015年4 月一、 设计题目数字积分器二、 设计技术指标及设计要求 1.模拟输入信号0~10V ,积分时间1~10秒,步距1秒。

2.积分值为0000~9999。

3.误差小于1%± 1LSB 。

4. 应具有微调措施,以便校正精度。

三、 设计框架分10次,输出为1000。

输入模拟量的范围为 0~10V ,通过10次积分,输出积分值为0000~9999。

误差要求小于1%± 1LSB 。

数字积分器应具有微调措施, 对于由元件参数引起的误差, 可以通过微调进行调节, 使其达到误差精度。

微调的设置应尽可能使电路简单,并使测量时便于调节,能提供微小调节,尽快达到要求,完成微调的 任务。

四、设计方案按照设计框架的要求可以将整个电路分为五个部分,分别为: 路、计数器电路,数字显示部分。

1 V/F 压频转换V/F 压频转换器由两部分组成,一部分把电压转换成三角波,另一部分把三角波转换成方波。

本实验 设计电路的目的是将输入的 1至10V 电压转换成相应的100Hz 至1000Hz 的频率。

经过查阅资料,有两种方案可供选择。

方案一是由卩A741+NE555组成,方案二是由两片 ^741组成。

100,积分时间为1S ,积V/F 压频转换器、时间积分电路、门电我们选择了方案一。

2时间积分电路(单稳电路)时间积分电路采用LM556CM ,利用LM556CM 以及适当阻值的电阻、电位器接成典型的单稳触发器,之后将NE555 的2 号管脚接上按键脉冲开关,以便控制积分时间,其积分时间公式为1.1RC=1(S) 。

3、与门电路与门电路是整个电路中最简单的部分,用一片74LS08 就可以。

它是把时间积分电路的输出端口和V/F 压频转换的LM556CM 的输出端口进行相与,从而得到时间为1 秒相应频率的方波。

数字电子技术课程设计报告(数字积分器)

题目二:数字积分器一、设计任务与要求:(一)、设计要求:1、模拟输入信号0-10V,积分时间1—10秒,步距1秒。

2、积分值为0000-9999。

3、误差小于1%±1LSB。

4、应具有微调措施,以便校正精度。

(二)、设计方案:1、通过数字积分器,对输入模拟量进行积分,并将积分值转化为数字量并显示。

输入与输出的对应关系为:输入1V,转化为频率100HZ,计数器计数为100,积分时间为1S,积分10次,输出为1000。

输入模拟量的范围为0—10V,通过10次积分,输出积分值为0000—9999。

误差要求<1%±1LSB。

数字积分器应具有微调措施,对于由元件参数引起的误差,可以通过微调进行调节,使其达到误差精度。

微调的设置应尽可能使电路简单,并使测量时易于调节,能通过微小调节,尽快达到要求,完成微调的任务。

2、方案选择(三)、所用元器件:组件:74LSl61 74LS00 741LS08uA741 74LS20555 3DK7电容、电阻若干电位器:10K(调零)二、方案选择与论证三、方案说明(一)V/F转换器最终确定的电压-频率转换器电路的原理图如下图所示(R1为可调电阻):在该电路中,通用运算放大器uA741被接成了积分器的形式。

输入电压经R3、R4分压后送入uA741的3脚作为参考电压。

假设Q1管截止,那么就有I R1R2=I C1,Vi给C1充电,uA741的6脚的电压不断下降。

当uA741的6脚的电压下降到NE555的5脚的电压的一半也就是2.5V时NE555状态翻转,3脚输出高电平15V,Q1导通,C1放电,uA741的6脚的电压上升。

当该电压上升至NE555的5脚的电压5V时NE555的状态再次翻转,Q1截止,电容C1再次被充电。

电路输出一个周期的脉冲方波振荡信号。

NE555的7脚是集电极开路输出,R6为上拉电阻,其上端接至+5V从而使得电压-频率转换器的输出与TTL电平相匹配。

EDA实验报告-cnt9999

EDA实验报告CNT9999计数器的设计指导老师:***班级:电技1503学号:***********姓名:***交通工程学院2017.10.15实验一0~9999的计数器电路的设计1.实验目的(1)进一步熟悉和掌握Quartus II软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好一个计数范围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统进行硬件验证。

3实验条件(1)开发软件:Quartus II 13.0。

(2)实验设备:GW48-CK EDA 实验开发系统。

(3)拟用芯片:EP3C55F484C7。

4.实验设计1)系统原理框图为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图1.1所示的原理图构成顶层电路CNT9999.图1.1 CNT9999电路原理图2)VHDL程序计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

CNT10的VHDL源程序:--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA: IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC );END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA) ISBEGINIF CLR='1' THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1' THENIF ENA='1' THENIF CQI="1001" THEN CQI<="0000";ELSE CQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CQI) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CQI<"1001" THEN CO<='0';ELSE CO<='1';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;CNT9999的VHDL源程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;--使用IEEE.STD_LOGIC_1164程序包PORT(CLR: IN STD_LOGIC;CLK: IN STD_LOGIC;CLK2:IN STD_LOGIC;ENA: IN STD_LOGIC;COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY DCNT9999;ARCHITECTURE ART OF DCNT9999 ISCOMPONENT CNT10 IS --CNT10元件定义语句PORT(CLK, CLR, ENA: IN STD_LOGIC;CQ: OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO: OUT STD_LOGIC);END COMPONENT CNT10;COMPONENT CTRLS IS --元件定义语句PORT(CLK: IN STD_LOGIC;--端口说明语句(端口名:端口模式数据类型)SEL: OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END COMPONENT CTRLS;COMPONENT DISPLAY IS --元件定义语句PORT(SEL: IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN: IN STD_LOGIC_VECTOR(15 DOWNTO 0);COM: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);SEG: OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END COMPONENT DISPLAY;SIGNAL S0,S1,S2: STD_LOGIC; --信号的定义,定义了3个标准位的单值信号SIGNAL SEL: STD_LOGIC_VECTOR(2 DOWNTO 0);--定义1个标准位矢量的位矢量信号SEL,含有3个元素SIGNAL DOUT:STD_LOGIC_VECTOR(15 DOWNTO 0);--定义1个标准位矢量的位矢量信号DOUT,有16个数组元素BEGINU0: CNT10 PORT MAP(CLK,CLR, ENA, DOUT(3 DOWNTO 0), S0); --元件例化语句,位置关联的方式U1: CNT10 PORT MAP(S0, CLR, ENA, DOUT(7 DOWNTO 4), S1);U2: CNT10 PORT MAP(S1, CLR, ENA, DOUT(11 DOWNTO 8), S2);U3: CNT10 PORT MAP(S2, CLR, ENA, DOUT(15 DOWNTO 12));U4: CTRLS PORT MAP(CLK2,SEL);U5: DISPLAY PORT MAP(SEL(2 DOWNTO 0),DOUT(15 DOWNTO 0),COM(7 DOWNTO 0),SEG(7 DOWNTO 0));--位置关联方式END ARCHITECTURE ART;3)仿真波形设置本设计包括两个层次,因此先进行底层的十进制计数器CNT10的仿真,再进行顶层CNT9999的仿真。

0-99手动计数器的设计

┊┊┊┊┊┊┊┊┊┊┊┊┊装┊┊┊┊┊订┊┊┊┊┊线┊┊┊┊┊┊┊┊┊┊┊┊┊第1章绪论1.1 计数器介绍本设计是根据我们所学习的单片机课程,按照课程要求进行的课程设计。

单片机技术是一个不可或缺的技术,尤其是对于我们电气专业来说它是我们必须要掌握的技能之一,使我们未来工作和生活的根本。

现在的社会是一个信息科技高速发展的社会,也是一个电子技术和微机计算机迅速发展的时代,单片机的档次和水平在不断的提高,其应用的领域和范围也越来越广,成为现代电子系统中最重要的智能化核心部分。

随着计数器技术的不断发展与进步,计数器的种类越来越多,应用的范围越来越广,随之而来的竞争也越来越激烈。

过硬的技术也成为众多生产厂商竞争的焦点之一。

厂商为了在竞争中处于不败之地,从而不断地改进技术,增加产品的种类。

现计数器的种类以增加到:电磁计数器、电子计数器、机械计数器(拉动机械计数器、转动机械计数器、按动机械计数器、测长机械计数器)、液晶计数器等。

计数器的应用范围也遍布印刷、纺织、印染、针织、电缆、电讯、军工、轻工、机械、开关、断路器、矿山、实行多班制的纺织行业的织布机、织带机、制线、制带、造纸、制革、薄膜、高压开关电器产品、试验设备,印刷设备、短路器、医疗、纺织、机械、仓库和码头的货运、行人及车辆过往的数量计数、冶金、食品、国防、包装、配料、石油、化工、发电、机床、仪表、自动化控制等行业。

1.2 本次设计的要求1) 上电时,数码管显示为00。

2) 利用单片机来制作一个手动计数器,在单片机的管脚上接一个轻触开关,作为手动计数的按钮,用单片机的I/O口接数码管,作为计数器,进行加计数显示。

3) 计数器计数到99后,再按计数按钮,则数码管从00重新开始计数。

1.3 本次设计的目的1) 学习基本理论在实践中综合运用的初步经验,掌握电路设计的基本方法、设计步骤,培养综合设计与调试能力。

2) 掌握汇编语言程序设计方法。

3) 培养实践技能,提高分析和解决实际问题的能力。

0-99手动计数器的设计要点

┊┊┊┊┊┊┊┊┊┊┊┊┊装┊┊┊┊┊订┊┊┊┊┊线┊┊┊┊┊┊┊┊┊┊┊┊┊第1章绪论1.1 计数器介绍本设计是根据我们所学习的单片机课程,按照课程要求进行的课程设计。

单片机技术是一个不可或缺的技术,尤其是对于我们电气专业来说它是我们必须要掌握的技能之一,使我们未来工作和生活的根本。

现在的社会是一个信息科技高速发展的社会,也是一个电子技术和微机计算机迅速发展的时代,单片机的档次和水平在不断的提高,其应用的领域和范围也越来越广,成为现代电子系统中最重要的智能化核心部分。

随着计数器技术的不断发展与进步,计数器的种类越来越多,应用的范围越来越广,随之而来的竞争也越来越激烈。

过硬的技术也成为众多生产厂商竞争的焦点之一。

厂商为了在竞争中处于不败之地,从而不断地改进技术,增加产品的种类。

现计数器的种类以增加到:电磁计数器、电子计数器、机械计数器(拉动机械计数器、转动机械计数器、按动机械计数器、测长机械计数器)、液晶计数器等。

计数器的应用范围也遍布印刷、纺织、印染、针织、电缆、电讯、军工、轻工、机械、开关、断路器、矿山、实行多班制的纺织行业的织布机、织带机、制线、制带、造纸、制革、薄膜、高压开关电器产品、试验设备,印刷设备、短路器、医疗、纺织、机械、仓库和码头的货运、行人及车辆过往的数量计数、冶金、食品、国防、包装、配料、石油、化工、发电、机床、仪表、自动化控制等行业。

1.2 本次设计的要求1) 上电时,数码管显示为00。

2) 利用单片机来制作一个手动计数器,在单片机的管脚上接一个轻触开关,作为手动计数的按钮,用单片机的I/O口接数码管,作为计数器,进行加计数显示。

3) 计数器计数到99后,再按计数按钮,则数码管从00重新开始计数。

1.3 本次设计的目的1) 学习基本理论在实践中综合运用的初步经验,掌握电路设计的基本方法、设计步骤,培养综合设计与调试能力。

2) 掌握汇编语言程序设计方法。

3) 培养实践技能,提高分析和解决实际问题的能力。

单片机00-99计数器实验总结

单片机00-99计数器实验总结

经过这次单片机00-99计数器实验,我对单片机的使用以及数

字电路的基础知识有了更深入的理解。

以下是我的实验总结:

一、实验原理

1. 十进制计数器:通过编号为0~9的数码管显示数字0~9;

2. 二进制计数器:通过10个LED灯表示二进制数字0~9,实

现0~99的计数;

3. 基础知识:单片机端口的输入输出、计数器的基本原理等。

二、实验过程

1. 搭建电路:根据电路图搭建电路,通过开关完成输入控制,让LED灯一次代表1个二进制数,完成计数器的计数功能;

2. 程序设计:通过C语言完成单片机的程序设计,实现计数

器的功能,将计数器的输出显示在LED灯和数码管上;

3. 调试测试:连接单片机和电脑,通过Keil软件进行程序的

编译、下载和调试测试,保证计数器能够正常工作。

三、实验结果

经过多次测试,00-99计数器实验的结果良好,可以顺利计数,LED灯和数码管能够显示出正确的结果。

四、实验心得

1. 理论知识的重要性:在实验中,掌握了数字电路的基本操作,熟悉了单片机的应用,并理解了计数器的工作原理,这对提高理论知识的理解和使用能力有很大的帮助。

2. 注意电路的接线:在实际搭建电路的过程中,注意各个部分的连接,保证电路的正常运行,避免出现因接线不良等问题而导致的错误结果。

3. 合理的编写程序:在程序的编写过程中,需要考虑到各个部分的功能,保证程序的稳定运行,避免出现因程序逻辑错误而导致的计数显示错误等问题。

总之,通过这次实验,我收获了很多,培养了自己的动手实践能力和编程思维能力,同时也提高了自己的专业知识水平。

0~99计数器的设计

成绩课程论文题目:基于Proteus的0-99计数器的设计与仿真课程名称:基于Proteus的51系列单片机设计与仿真电子工程学院制2015年5月目录一、设计目的 (1)二、设计内容 (2)三、设计步骤 (3)1.硬件电路设计 (3)1.2.工作原理 (1)1.3.原理图 (2)1.4.元件的作用 (2)1.5.元件清单 (3)2.程序设计 (3)2.1程序流程图 (3)2.2汇编程序 (4)四、调试与仿真 (5)五、心得体会 (6)基于Proteus的51系列单片机设计与仿真一、设计目的通过课程设计,培养学生运用已学知识解决实际问题的能力、查阅资料的能力、自学能力和独立分析问题、解决问题的能力和能通过独立思考。

二、设计内容一个完整00~99手动计数器想当于一个简单的单片机系统,该系统设置电路、单片机、显示电路等构成。

单片机是集成IC芯片,只需根据实际设计要求选型。

其他部分都需要根据应用要求和性能指标自行设计。

在AT89C51单片机的p12,p13管脚接一个轻触开关,作为手动计数的按钮,用单片机的P2.0--P2.7接一个共阳数码管,作为00-99计数的个位数显示,用单片机的P0.0-P0.7接一个共阳数码管,作为00-99计数的十位数显示。

三、设计步骤1.1硬件电路设计晶振电路:单片机晶振的作用是为系统提供基本的时钟信号。

通常一个系统共用一个晶振,便于各部分保持同步。

有些通讯系统的基频和射频使用不同的晶振,而通过电子调整频率的方法保持同步。

也就是说晶振是给单片机提供工作信号脉冲的。

这个脉冲就是单片机的工作速度。

1.2 工作原理晶振与单片机XTAL0和XTAL1引脚构成的振荡电路中会产生偕波,这个波对电路的影响不大,但会降低电路的时钟振荡器的稳定性。

为了提高电路的稳定性在晶振的两引脚处接入两个10pf-50pf的瓷片电容接地来削减偕波对电路的稳定性的影响。

晶振电路中两个电容的取值都是相同的,或者说相差不大,如果相差太大,容易造成谐振的不平衡,容易造成停振或者干脆不起振。

EDA设计999计数器

计算机与信息技术学院设计性实验报告一、实验目的1.掌握计数器的工作方式2.掌握计数器程序设计方法3.设计一个999计数器,使波形图从0计数到999。

二、实验仪器或设备装Quartue II 5.0软件的微机一台三、总体设计(设计原理、设计方案及流程等)(一)设计原理1.对于一个矩形信号脉冲序列,如果在其上升沿计一次数,就可以设计一个十进制计数器,当计数够10次后,进位端就有一个输出。

2.可以用三个十进制计数器设计一个电路,使其可以计数从0到999,即可以设计出一个999计数器。

3.在Quartue II 5.0的编译环境中,可以根据Verilog HDL的文件生成一个与源程序对应的结构功能框图。

(二)设计方案及流程1.设计方案:(1)在Verilog HDL的编译环境里,编写代码,设计一个十进制计数器即count10,使其在输入信号clk的上升沿进行计数,并在输出端q把计数结果输出。

当计数到9时,进位端cout为1,并使输出端q为0 ,其他时候进位端cout为0。

(2)根据count10.v生成一个与其相对应的功能结构框图,第一个框图的进位输出作为第二个的输入,第二个框图的进位输出作为第三个框图的输入。

则第一个框图的输出即为个位,第二个框图的输出即为十位,第三个框图的输出即为百位。

三者组合即可从0计数到999。

2.流程图图1 流程图四、实验步骤(包括主要步骤、代码分析等)(一)主要步骤1.打开Quartue II 5.0集成调试软件2.单击“File”-“New”-“Verilog HDL File”,新建一个Verilog HDL 文件,命名为“count10.v”。

3.新建工程,命名为“count10”,进行“编译”。

4.单击“File”—“Create/Update”生成一个十进制计数器的结构功能框图。

5.单击“File”-“New”-“Other Files”-“Block Symbol File”,在此环境下将生成的十进制计数器的结构功能框图找出来,并找出所需要的输入输出引脚,按照电路原理图连接电路。

9999计数器

电工电子实验报告学生姓名:马雷学生学号:2011112030558系别班级:物电1105班课程名称:现代电子技术实验(EDA)报告性质:(基础、综合、设计)报告实验地点:现代电子技术实验室开课学期:2013年10月成绩评定:教师签名:9999计数器设计报告一、实验目的利用CEET-EDA实验箱上的八位数码管设计一9999计数器,能够自己加一计数,并且高位要能在没有计数时是灭的。

二、基本思想做9999计数器就是把以前的99计数器加上8位,数码管的段选,位选也有一定的单片机的基础,也不是问题,这里最主要的的是解决高位不用时对应的数码管熄灭的问题。

三、设计步骤.1、分频模块always @ (posedge clk0)beginq=q+1;a=q[16:16];enda=q[16:16]是数码管的扫描和计数器的加一分频当a的上升沿到来时数码管就扫描一次。

2、数码管的扫描模块always @ (posedge a)beginsel=sel+1;end每当a的上升沿来到是数码管就加一让下一个数码管亮,由于sel是两位的所以当sel 加到11时后再加一时溢出清零,一直循环,数码管就一直工作,且扫描时间是人眼不可见的。

3、计数器模块always @ (posedge a)beginif(c[11:8]==9)begin c[15:12]=c[15:12]+1;c[11:8]=0;endelse if(c[15:12]==10) begin c[19:16]=c[19:16]+1;c[15:12]=0;endelse if(c[19:16]==10) begin c[23:20]=c[23:20]+1;c[19:16]=0;endelse if(c[23:20]==10) c[23:20]=0;else c=c+1;end这里之所以从第九位开始计数是因为分频太快,数码管的扫描是适合的,但计数不适合,所以在这里前八位也想当与分频的作用。

0-9999手动计数器

NANCHANG UNIVERSITY毕业设计GRADUATION DESIGN(2008—2011年)题目: 0-9999计数器英文题目: 0-9999 COUNTER学院: 共青学院系别: 信息工程系专业: 电子信息工程技术班级: 08电信(1)学生姓名: XXX学号: 8051308009 指导老师: XXX起讫日期:2010年5月1日-2011年5月30日二○一一年六月目录摘要 (Ⅰ)Abstract (II)第一章绪论 (1)1.1前言 (1)1.2选题背景 (1)1.3设计要求 (2)第二章方案论证与电路设计 (2)2.1方案论证与选择 (2)2.2系统总体框图和原理 (3)2.3电源供电部分 (3)2.4AT89C51单片机 (4)2.5单片复位电路 (5)2.6按键部分 (5)2.7显示部分 (6)2.8电路原理图 (8)第三章软件设计与仿真调试 (9)3.1 PROTEUS仿真图 (10)3.2程序流程图 (11)第四章总结与体会 (11)总结 (12)参考文献(References) (12)致谢 (13)附录 (14)0-9999计数器摘要本文所设计的计数器是采用手动计数的方式,能手动实现加一,减一,清零功能,该设计抗干扰性好,可靠性高.应用灵活,该产品应用广泛,可用于测量流水线上的产品的数量,也可以用于测量宾馆、饭店、商场、展览观、车站、码头、银行等场所的人员数量及人员流通数量.采用数码管静态显示方式。

通过人眼的观察,进行手动计数,经单片机识别按键端口的电平,来进行计数显示,得到想要的数据。

关键词:体积小、功耗低、单片机、廉价、8位数码管.0-9999 COUNTERAbstractThis article designs the counter is uses the manual counting the way, the anti-jamming is good, the reliability is high. Applies nimbly, this product application is widespread, whether there is available as well as can inspect the product damage in survey assembly line product quantity; Also may use in surveying place and so on guesthouse, hotel, market, display view, station, wharf, bank personnel quantities and the personnel circulates quantity. The road causes the nixietube demonstration value.Through the human eye observation, carries on the manual counting, after the monolithic integrated circuit recognition pressed key port level, carries on the counting, again passes through the nixietube to demonstrate, obtains the wish data. Key words: automatic counting, infrared detection, SCM, decoding.第一章绪论1.1引言近年来,电子技术和计算机技术应用领域不断扩大,单片机技术已经成为电子技术应用领域中的一个新亮点,使单片机技术成为电子类及计算机类工作者必须掌握的专业技术之一。

基于单片机的0-99计数器设计

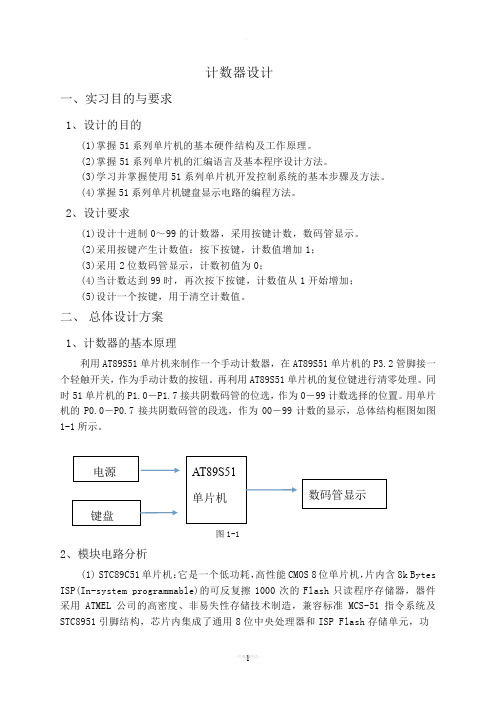

计数器设计 一、实习目的与要求1、设计的目的(1)掌握51系列单片机的基本硬件结构及工作原理。

(2)掌握51系列单片机的汇编语言及基本程序设计方法。

(3)学习并掌握使用51系列单片机开发控制系统的基本步骤及方法。

(4)掌握51系列单片机键盘显示电路的编程方法。

2、设计要求(1)设计十进制0~99的计数器,采用按键计数,数码管显示。

(2)采用按键产生计数值:按下按键,计数值增加1; (3)采用2位数码管显示,计数初值为0;(4)当计数达到99时,再次按下按键,计数值从1开始增加; (5)设计一个按键,用于清空计数值。

二、 总体设计方案1、计数器的基本原理利用AT89S51单片机来制作一个手动计数器,在AT89S51单片机的P3.2管脚接一个轻触开关,作为手动计数的按钮。

再利用AT89S51单片机的复位键进行清零处理。

同时51单片机的P1.0-P1.7接共阴数码管的位选,作为0-99计数选择的位置。

用单片机的P0.0-P0.7接共阴数码管的段选,作为00-99计数的显示,总体结构框图如图1-1所示。

图1-12、模块电路分析(1) STC89C51单片机:它是一个低功耗,高性能CMOS 8位单片机,片内含8k Bytes ISP(In-system programmable)的可反复擦1000次的Flash 只读程序存储器,器件采用ATMEL 公司的高密度、非易失性存储技术制造,兼容标准MCS-51指令系统及STC8951引脚结构,芯片内集成了通用8位中央处理器和ISP Flash 存储单元,功电源 键盘AT89S51 单片机数码管显示能强大的微型计算机的STC8951可为许多嵌入式控制应用系统提供高性价比的解方案。

STC8951具有如下特点:40个引脚,8k Bytes Flash片内程序存储器,128bytes 的随机存取数据存储器(RAM),32个外部双向输入输出(I/O)口,5个中断优先级,2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信,片内时钟振荡器。

单片机课程设计+00-99计数器

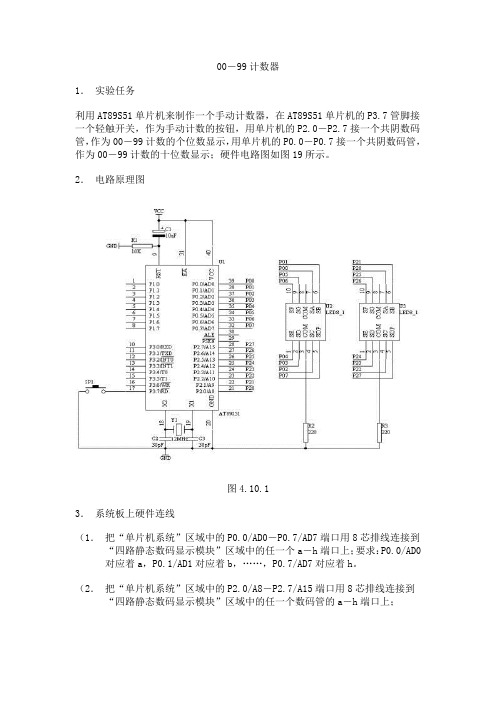

00-99计数器1.实验任务利用AT89S51单片机来制作一个手动计数器,在AT89S51单片机的P3.7管脚接一个轻触开关,作为手动计数的按钮,用单片机的P2.0-P2.7接一个共阴数码管,作为00-99计数的个位数显示,用单片机的P0.0-P0.7接一个共阴数码管,作为00-99计数的十位数显示;硬件电路图如图19所示。

2.电路原理图图4.10.13.系统板上硬件连线(1.把“单片机系统”区域中的P0.0/AD0-P0.7/AD7端口用8芯排线连接到“四路静态数码显示模块”区域中的任一个a-h端口上;要求:P0.0/AD0对应着a,P0.1/AD1对应着b,……,P0.7/AD7对应着h。

(2.把“单片机系统”区域中的P2.0/A8-P2.7/A15端口用8芯排线连接到“四路静态数码显示模块”区域中的任一个数码管的a-h端口上;(3.把“单片机系统”区域中的P3.7/RD端口用导线连接到“独立式键盘”区域中的SP1端口上;4.程序设计内容(1.单片机对按键的识别的过程处理(2.单片机对正确识别的按键进行计数,计数满时,又从零开始计数;(3.单片机对计的数值要进行数码显示,计得的数是十进数,含有十位和个位,我们要把十位和个位拆开分别送出这样的十位和个位数值到对应的数码管上显示。

如何拆开十位和个位我们可以把所计得的数值对10求余,即可得个位数字,对10整除,即可得到十位数字了。

(4.通过查表方式,分别显示出个位和十位数字。

5.程序框图图4.10.26.汇编源程序Count EQU 30HSP1 BIT P3.7ORG 0START: MOV Count,#00HNEXT: MOV A,CountMOV B,#10DIV ABMOV DPTR,#TABLEMOVC A,@A+DPTRMOV P0,AMOV A,BMOVC A,@A+DPTRMOV P2,AWT: JNB SP1,WT ||可能有问题WAIT: JB SP1,WAITLCALL DELY10MSJB SP1,WAITINC CountMOV A,CountCJNE A,#100,NEXTLJMP STARTDELY10MS: MOV R6,#20D1: MOV R7,#248DJNZ R7,$DJNZ R6,D1RETTABLE: DB 3FH,06H,5BH,4FH,66H,6DH,7DH,07H,7FH,6FH END7. C语言源程序#include <AT89X51.H>unsigned char code table[]={0x3f,0x06,0x5b,0x4f,0x66, 0x6d,0x7d,0x07,0x7f,0x6f};unsigned char Count;void delay10ms(void){unsigned char i,j;for(i=20;i>0;i--)for(j=248;j>0;j--);}void main(void){Count=0;P0=table[Count/10];P2=table[Count%10];while(1){if(P3_7==0){delay10ms();if(P3_7==0){Count++;if(Count==100){Count=0;}P0=table[Count/10]; P2=table[Count%10]; while(P3_7==0);}}}}。

按键实现0~9999计数器 单片机

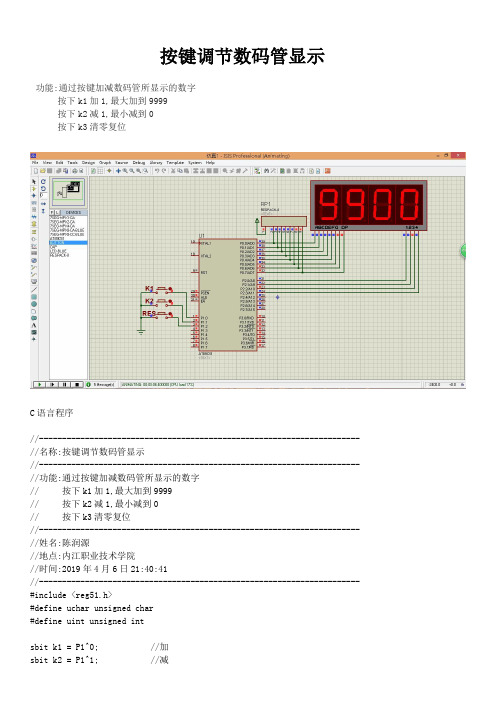

按键调节数码管显示功能:通过按键加减数码管所显示的数字按下k1加1,最大加到9999按下k2减1,最小减到0按下k3清零复位C语言程序//---------------------------------------------------------------------- //名称:按键调节数码管显示//---------------------------------------------------------------------- //功能:通过按键加减数码管所显示的数字// 按下k1加1,最大加到9999// 按下k2减1,最小减到0// 按下k3清零复位//---------------------------------------------------------------------- //姓名:陈润源//地点:内江职业技术学院//时间:2019年4月6日21:40:41//---------------------------------------------------------------------- #include <reg51.h>#define uchar unsigned char#define uint unsigned intsbit k1 = P1^0; //加sbit k2 = P1^1; //减sbit k3 = P1^2; //复位void key(void);void display(void);uchar code table[]={0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0x80,0x90}; //数组char m=99,n=98; //显示初值,m,n的值决定开机显示数值//****************************************//延时程序//****************************************void delayms(uint xms){uint i,j;for(i=xms;i>0;i--)for(j=110;j>0;j--);}//***********************************************//显示程序//***********************************************void display(void){P2=0X08;P0=table[m%10]; //显示个位delayms(5);P2=0X04;P0=table[m/10]; //显示十位delayms(5);P2=0X02;P0=table[n%10]; //显示百位delayms(5);P2=0X01;P0=table[n/10]; //显示千位delayms(5);}//***************************************************//按键处理//***************************************************void key(){if(k1==0) //检测按键是否被按下{ //延时消抖delayms(10);if(k1==0) //再次检测是否真正按下按键{m++; //m自加一if(m>=100) //如果m加到100则n加一 (限制m的取值范围) 个位、十位最大显示99 {n++; //n自加一m=0; //使m又从0开始计数if(n>=100) //如果n加到100则m=n=99 (限制n的取值范围) 百位、千位最大显示99 {m=99; //最大显示9999n=99;}}}while(!k1); //按键松开}if(k2==0) //检测按键是否被按下{ //延时消抖delayms(10); //再次检测是否真正按下按键if(k2==0){ //m自减一m--;if(m<=0) //如果m减到0则n减一 (限制n的取值范围) 个位、十位最小显示00 {m=99; //重新给m装初值n--; //n自减一if(n==-1) //如果n减到-1,则m=n=0 (限制n的取值范围) 百位、千位最小显示00{n=0; //最小显示0000m=0;}}}while(!k2); //按键松开}if(k3==0) //检测按键是否被按下{delayms(10); //延时消抖if(k3==0) //再次检测是否真正按下按键{m=0; //复位,显示0000n=0;}while(!k3); //按键松开}}void main(){while(1){ //调用按键检测key(); //数码管显示display(); }}。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验二:+0-9999的计数器电路的设计EDA实验报告学院电气与信息工程学院(部):专电子信息工程业:学生姓刘玉文名:班电子信息工程1101 级:学11401700430 号:指导教师姓谭会生名:实验二:0~9999的计数器电路的设计1.实验目的(1)进一步熟悉和掌握Quartus II软件的使用。

(2)进一步熟悉和掌握GW48-CK或其他EDA实验开发系统的使用。

(3)学习和掌握VHDL进程语句和元件例化语句的使用。

2.实验内容设计并调试好一个技术范围为0~9999的4位十进制计数器电路CNT9999,并用GW48-CK或其他EDA实验开发系统(可选用的芯片为ispLSI 1032E-PLCC84或EPM7128S-PL84或XCS05/XCS10-PLCC84芯片)进行硬件验证。

3.实验条件(1)开发软件:Quartus II8.0。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

4.实验设计(1)系统原理框图为了简化设计并便于显示,本计数器电路CNT9999的设计分为两个层次,其中底层电路包括四个十进制计数器模块CNT10,再由这四个模块按照图所示的原理框图构成顶层电路CNT9999。

CNT9999电路原理框图(2)VHDL程序计数器CNT9999的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。

1)CNT10的VHDL源程序:--CNT10.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO:OUT STD_LOGIC);END ENTITY CNT10;ARCHITECTURE ART OF CNT10 ISSIGNAL CQI:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,CLR,ENA)ISBEGINIF CLR='1'THEN CQI<="0000";ELSIF CLK'EVENT AND CLK='1'THENIF ENA='1'THENIF CQI="1001"THENCQI<="0000";ELSECQI<=CQI+'1';END IF;END IF;END IF;END PROCESS;PROCESS(CLK,CQI) ISBEGINIF CLK'EVENT AND CLK='1'THENIF CQI<"1001"THENCO<='0';ELSECO<='1';END IF;END IF;END PROCESS;CQ<=CQI;END ARCHITECTURE ART;2)CNT9999的VHDL源程序:--CNT9999.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY CNT9999 ISPORT(CLK:IN STD_LOGIC;CLR:IN STD_LOGIC;ENA:IN STD_LOGIC;DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0));END ENTITY CNT9999;ARCHITECTURE ART OF CNT9999 ISCOMPONENT CNT10 ISPORT(CLK,CLR,ENA:IN STD_LOGIC;CQ:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO:OUT STD_LOGIC);END COMPONENT CNT10;SIGNAL S0,S1,S2,S3:STD_LOGIC;BEGINU0:CNT10 PORT MAP(CLK,CLR,ENA,DOUT(3 DOWNTO 0),S0);U1:CNT10 PORT MAP(S0,CLR,ENA,DOUT(7 DOWNTO 4),S1);U2:CNT10 PORT MAP(S1,CLR,ENA,DOUT(11 DOWNTO 8),S2);U3:CNT10 PORT MAP(S2,CLR,ENA,DOUT(15 DOWNTO 12),S3);END ARCHITECTURE ART;(3)仿真波形设置本设计包括两个层次,因此先进行底层的十进制计数器CNT10的仿真,再进行顶层CNT9999的仿真。

如图是CNT10仿真输入设置及可能结果估计图。

同理可进行CNT9999仿真输入设置及可能结果估计。

CNT10的时序仿真结果CNT9999的时序仿真结果5.实验总结通过本次实验,对Quartus II软件的基本操作有了更深层次的认识,并能初步熟练和掌握他的运用。

文件名与实体名要相对应,输入源程序时要仔细,时序仿真时,要先保存仿真文件,最后才能对其进行相应地仿真操作。

计数动态扫描显示电路1.实验目的(1)学习Quartus II 8.0 软件的基本使用方法。

(2)学习GW48-CK EDA实验开发系统的基本使用方法。

(3)了解VHDL程序中数据对象、数据类型、顺序语句和并行语句的综合应用。

2.实验内容设计并调试一个由两个4位二进制并行加法器级联而成的8位二进制并行加法器。

3.实验内容(1)开发软件:Quartus II 8.0。

(2)实验设备:GW48-CK EDA实验开发系统。

(3)拟用芯片:EPM7128S-PL84。

4.实验设计(1)系统原理框图为了简化设计并便于显示,该计数动态扫描显示电路分为两个层次,底层电路包括四个十进制计数器模块CNT10、动态显示控制信号产生模块CTRLS、数据动态显示控制模块DISPLAY等六个模块,再由这六个模块按照图所示的原理图构成顶层电路DTCNT9999。

(2)VHDL程序十进制计数器模块CNT10的VHDL程序见0~9999的计数器电路,其余两个模块的VHDL程序如下:1)CTRLS的VHDL源程序--CTRLS.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CTRLS ISPORT(CLK:IN STD_LOGIC;SEL:OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); END ENTITY CTRLS;ARCHITECTURE ART OF CTRLS ISSIGNAL CNT:STD_LOGIC_VECTOR(2 DOWNTO 0);BEGINPROCESS(CLK) ISBEGINIF CLK'EVENT AND CLK='1' THENIF CNT="111" THENCNT<="000";ELSECNT<=CNT+'1';END IF;END IF;END PROCESS;SEL<=CNT;END ARCHITECTURE;2)DISPLAY的VHDL源程序:--DISPLAY.VHDLIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DISPLAY ISPORT(SEL:IN STD_LOGIC_VECTOR(2 DOWNTO 0);DATAIN:IN STD_LOGIC_VECTOR(15 DOWNTO 0);COM:OUT STD_LOGIC_VECTOR(7 DOWNTO 0);--LEDW:OUT STD_LOGIC_VECTOR(2 DOWNTO 0);SEG:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END ENTITY;ARCHITECTURE ART OF DISPLAY ISSIGNAL DATA:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINP1:PROCESS(SEL) ISBEGINCASE SEL ISWHEN "000"=>COM<="11111110";WHEN "001"=>COM<="11111101";WHEN "010"=>COM<="11111011";WHEN "011"=>COM<="11110111";WHEN "100"=>COM<="11101111";WHEN "101"=>COM<="11011111";WHEN "110"=>COM<="10111111";WHEN "111"=>COM<="01111111";WHEN OTHERS =>COM<="11111111";END CASE;END PROCESS P1;--LEDW<=SEL;P2:PROCESS(SEL,DATAIN)BEGINCASE SEL ISWHEN "000"=>DATA<=DATAIN(3 DOWNTO 0);WHEN "001"=>DATA<=DATAIN(7 DOWNTO 4);WHEN "010"=>DATA<=DATAIN(11 DOWNTO 8);WHEN "011"=>DATA<=DATAIN(15 DOWNTO 12);WHEN OTHERS=>DATA<="0000";END CASE;CASE DATA ISWHEN "0000"=>SEG<="00111111";WHEN "0001"=>SEG<="00000110";WHEN "0010"=>SEG<="01011011";WHEN "0011"=>SEG<="01001111";WHEN "0100"=>SEG<="01100110";WHEN "0101"=>SEG<="01101101";WHEN "0110"=>SEG<="01111101";WHEN "0111"=>SEG<="00000111";WHEN "1000"=>SEG<="01111111";WHEN "1001"=>SEG<="01101111";WHEN OTHERS=>SEG<="00000000";END CASE;END PROCESS P2;END ARCHITECTURE;(3)仿真波形设置0~9999计数的时序仿真结果5.实验总结经过本次实验,对Quartus II有了更深入的了解,以及学会了更多操作。