M93C46-BN3中文资料

93C46-93c06-93c56-93c66-93c86的驱动程序(C51)

93C46/93c06/93c56/93c66/93c86的驱动程序(C51)/*————————————————————〖说明〗SPI总线驱动程序包括的普通封装标准模式,特殊封装标准模式默认的晶振。

〖文件〗﹫2003/5/12—————————————————————*//*通用93c06-93c86系列使用说明93c06=93c4693c56=93c6693c76=93c86dipx 可以自行定义*/#include ““#include ““/*-----------------------------------------------------SPI 93cXX系列时序函数调用(普通封装)调用方式:自行定义﹫2001/05/12函数说明:私有函数,封装各接口定义-----------------------------------------------------*/#define di_93 dip3#define sk_93 dip2#define cs_93 dip1#define do_93 dip4#define gnd_93 dip5#define org_93 dip6sbit cs_93=P1 ;sbit sk_93=P1;sbit di_93=P1;sbit do_93=P1;sbit org_93=P0;/*-----------------------------------------------------SPI93cXX系列时序函数调用(普通封装)调用方式:void high46(void) ---高8位函数调用void low46(void) ---低8位函数调用﹫2001/05/12函数说明:私有函数,SPI专用93c46普通封装驱动程序-----------------------------------------------------*/void high46(void){di_93=1;sk_93=1; _nop_();sk_93=0;_nop_();}void low46(void){di_93=0;sk_93=1;_nop_();sk_93=0;_nop_();}void wd46(unsigned char dd) {unsigned char i;for (i=0;i=0x80) high46(); else low46();dd=dd=0x80) high46a(); else low46a();dd=dd>1;address=address|0x80; address=address|0x80;high46();wd46(address);dat1=rd46();dat0=rd46();cs_93=0;dat=dat1*256 dat0;return(dat);}bit write93c46_word(unsigned char address,unsigned int dat) {unsigned char e,temp=address;e=0;while (e>=1;//??address|=0x40;wd46(address);wd46(dat/256);wd46(dat%6);cs_93=0;_nop_();cs_93=1;time=0;do_93=1;while (1){if (do_93==1) break;if (time>20) break;}cs_93=0;if (read93c46_word(temp)==dat)return(0);}e ;}return(1);}/*-----------------------------------------------------SPI93c57系列函数调用(举例)调用方式:bit write93c57_word(unsigned int address,unsigned int dat) ﹫2001/05/12函数说明:私有函数,SPI专用-----------------------------------------------------*/void ewen57(void){_nop_();cs_93=1;dip7=0;high46();low46();wd46(0x60);cs_93=0;unsigned int read93c57_word(unsigned int address){unsigned int dat;unsigned char dat0,dat1;gnd_93=0;cs_93=sk_93=0;org_93=1;cs_93=1;address=address>>1;high46();high46();wd46(address);dat1=rd46();dat0=rd46();cs_93=0;dat=dat1*256 dat0;return(dat);}bit write93c57_word(unsigned int address,unsigned int dat) {unsigned char e;unsigned int temp=address;e=0;while (e>=1;address|=0x80;wd46(address);wd46(dat/256);wd46(dat%6);cs_93=0;_nop_();cs_93=1;time=0;do_93=1;while (1){if (do_93==1) break;if (time>20) break;}cs_93=0;if (read93c57_word(temp)==dat) {return(0);}e ;}return(1);}/*-----------------------------------------------------SPI93c56系列函数调用(举例)调用方式:bit write93c56_word(unsigned int address,unsigned int dat) ﹫2001/05/12函数说明:私有函数,SPI专用-----------------------------------------------------*/void ewen56(void){_nop_();cs_93=1;high46();low46();low46();wd46(0xc0);cs_93=0;}unsigned int read93c56_word(unsigned char address){unsigned int dat;unsigned char dat0,dat1;gnd_93=0;cs_93=sk_93=0;org_93=1;cs_93=1;address=address>>1;high46();high46();low46();wd46(address);dat1=rd46();dat0=rd46();cs_93=0;dat=dat1*256 dat0;return(dat);}bit write93c56_word(unsigned char address,unsigned int dat) {unsigned char e;unsigned int temp=address;e=0;while (e>=1;wd46(address);wd46(dat/256);wd46(dat%6);cs_93=0;_nop_();cs_93=1;TH0=0;time=0;do_93=1;while (1){if (do_93==1) break;if (time) break;}cs_93=0;if (read93c56_word(temp)==dat) {return(0);}e ;}return(1);}/*-----------------------------------------------------SPI93c76与SPI93c86系列函数调用(举例)调用方式:bit write93c76_word(unsigned int address,unsigned int dat) ﹫2001/05/12函数说明:私有函数,SPI专用-----------------------------------------------------*/void ewen76(void){_nop_();cs_93=1;dip7=1;high46();low46();low46();high46();high46();wd46(0xff);cs_93=0;}unsigned int read93c76_word(unsigned int address){unsigned char dat0,dat1;gnd_93=0;cs_93=sk_93=0;org_93=1;cs_93=1;address>>=1;high46();high46();low46();if((address&0x200)==0x200) high46();else low46();if ((address&0x100)==0x100) high46();else low46();wd46(address);dat1=rd46();dat0=rd46();cs_93=0;return(dat1*256|dat0);}bit write93c76_word(unsigned int address,unsigned int dat) {unsigned char e;unsigned int temp=address;e=0;address>>=1;while (e10) break;}cs_93=0;e ;}return(1);}/*----------------------------------------------------- 主函数调用(举例)调用方式:main() ﹫2001/05/12函数说明:私有函数,SPI专用-----------------------------------------------------*/ main(){ bit b;unsigned int i;unsigned int j[32],k;for(i=0;i<32;i )j[i]=read93c56_word(i);for(i=0;i<32;i )write93c56_word(i,0x0909);i=0;b=write93c56_word(i,0x0909); j[i]=read93c56_word(i);i=1;b=write93c56_word(i,0x1111); j[i]=read93c56_word(i);i=2;b=write93c56_word(i,0x2222); j[i]=read93c56_word(i);}。

AT93C46中文资料详解

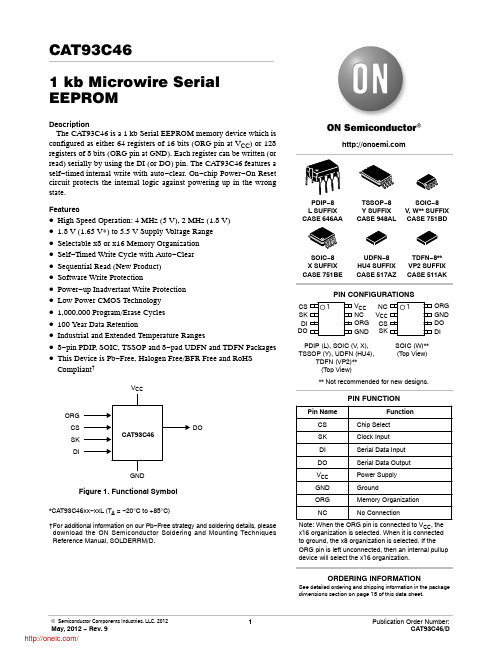

AT93C46中文资料详解AT93C46 是1K的串行EEPROM存储器器件,它们可配置为16位(ORG 管脚接Vcc)或者8位(ORG管脚接GND)的寄存器。

每个寄存器都可通过DI(或DO管脚)串行写入(或读出)。

AT93C46 内部有一个指令缓存器储存传输进来的串行数据,再由指令译码控制逻辑与内部频率产生器,在指定的地址将数据作读取或写入的动作。

AT93C46采用Catalyst公司先进的CMOS EEPROM浮动闸(floating gate)技术制造而成。

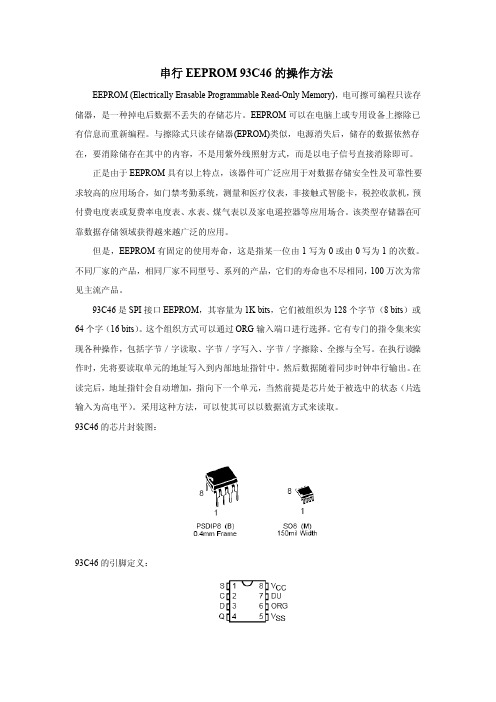

器件可采用8脚DIP,8脚SOIC或8脚TSSOP 的封装形式。

AT93C46 集成电路AT93C46 功能介绍AT93C46 是一片串行数据存储器芯片,其接脚说明如表1 及内部结构如图3。

不论写入或读取数据,皆采用串行传输的模式作动,虽然没有比并列传输来的快速,但是在传递远距离的数据,却可以大量减少使用传输线的需求,也缩小了系统整体的占有面积。

因此,非常适合用于微控制器或是微处理器,表2是对AT93C 系列作容量上的比较。

AT93C46 内部有一个指令缓存器储存传输进来的串行数据,再由指令译码控制逻辑与内部频率产生器,在指定的地址将数据作读取或写入的动作。

AT93C46 共有7 个功能指令,我们用表3来说明之;另外,也将其控制动作用表4说明,而AT93C46 特性说明概要如下:保存的资料约40 年之久。

● 可以重复写入超过1 百万次。

● 可以记录64 组16bit 的数字。

● 采用微金属丝接口(Microwire Interface)。

● 有4 条串行金属线总线。

● 1024bit 的串行数据存储器。

● 内部是采用CMOS EEPROM 的方式。

READ:允许数据从指定的地址读出,当接受到有效的输入讯号时,数据将会被放在输出缓存器内,随着频率讯号上升同步输出,在DO 输出数据前会先输出一个“ 假的位”,如同起始位的功能一样,再由D15 一直到D0 输出为止。

93c46

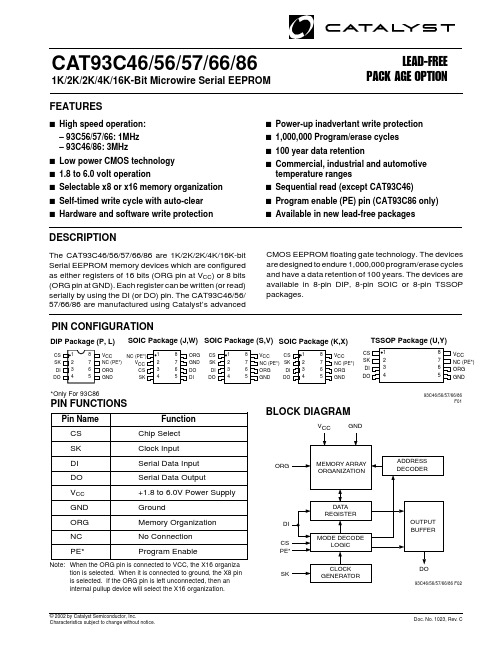

1 概述CSI93c46是一种存储器可以定义为16 位ORG 引脚接Vcc 或者定义为8 位ORG 引脚接GND 的1K/2K/2K/4K/16K 位的串行E2PROM 每一个的存储器都可以通过DI 引脚或DO 引脚进行写入或读出每一片CSI93c46/56/57/66/86 都是采用CSIalyst 公司先进的CMOS E2PROM 浮动门工艺加工器件可以经受1000000 次的写入/擦除操作片内数据保存寿命达到100 年器件可提供的封装有DIP-8 SOIC-8 TSSOP-82 器件特性高速度操作1MHz低功耗工艺电源电压宽1.8 伏到6.0 伏存储器可选择8 位或者16 位结构写入时自动清除存储器内容硬件和软件写保护1000000 次写入/擦除周期100 年数据保存寿命商业级工业级和汽车级温度范围连续读操作除93c46外写入允许引脚PE 只有93C86 有3 管脚配置及其方框图3 1 管脚3 2 管脚说明说明当ORG 接Vcc 时存储器为16 位结构当ORG 接GND 是存储器为8 位结构当ORG引脚悬空时内部的上拉电阻把存储器选择为16 位结构管脚名称功能CS 片选信号SK 时钟输入DI 串行数据输入DO 串行数据输出Vcc 电源+1.8 伏到6 伏GND 接地ORG 存储器结构选择NC 不用连接PE* 写入保护4 器件操作简介CSI93c46/56 57 /66/86 是一个有1024/2048/4096/16384 位内含工业标准微处理器的非易失的存储器CSI93c46/56/57/66/86 可以选择为16 位或8 位结构当选择16 位结构时93c46有7 条9 位的指令93C57 有7 条10 位的指令93C56 和93C66 有7 条11 位的指令93C86 有7 条13 位的指令用来控制对器件进行读写和擦除操作当选择8 位结构时93c46有7 条10 位的指令93C57 有7 条11 位的指令93C56 和93C66 有7 条12 位的指令93C86 有7 条14 位的指令来控制对器件进行读写和擦除操作CSI93c46/56/57/66/86 的所有操作都在单电源上进行当执行任何的写操作时内部的升压电路将提供高压给芯片指令地址和写入的数据在时钟信号SK 的上升沿时由DI 引脚输入DO 引脚除了从器件读取数据或在进行了写操作后查询准备/繁忙ready/busy 的器件工作状态外平常是高阻态的准备/繁忙ready/busy 是开始了一个写操作后选择器件CS 为高电平后从DO 引脚读得用来测定期间工作状态的信号DO 为低电平则表示写操作还没有完成当DO 为高电平时则表示器件可以输入下一条指令此时如果有需要可以在DI 引脚移入一个高电平DO 会进入高阻态DO 引脚会在时钟SK的下降沿时进入高阻态将DO 引脚恢复高阻态是值得推荐在DI 和DO 合用一个I/O 口来读/写的应用中所有送往器件的指令格式为一个高电平1 的开始位一个2 位或4 位的操作码6 位93c46/7 位93C57 /8 位(93C56 或93C66)/10 位(93C86)(当选择8 位结构时加一位)及写入数据时的16 位数据选择8 位结构时为8 位注当器件为93C86 时执行写入擦除写全部和擦全部操作时写允许引脚PE 必须为1 如果PE 引脚悬空93C86 为允许写入模式当执行写允许和写禁止指令后PE 可以不必理会93c46是1k位串行EEPROM储存器。

HDLTEK ht49 mcu控制ht93lc46的读写 说明书

HT49 MCU 控制 HT93LC46 的讀寫

文件編碼:HA0044T

簡介

HT93LC46 EEPROM 是 Holtek 製造的 1K 位元系列的 EEPROM(電子可擦除式唯讀記憶體), 一般它用於微控制器的固定資料的儲存。在本文中,我們將以 Holtek 公司八位元微控制器 HT49 系列爲例,介紹該晶片常用的操作功能代碼。用戶只需把代碼加到程式中,並且在使 用 HT93LC46 之前將引腳 CS/SK/DI/DO 連接即可。

功能說明

在本文中將用到一個插入文件 HT93LC46S.ASM 和一彙編原始檔案 OP16_93LC46S.ASM。在 HT-IDE3000 開發環境下,在使用所提供的介面函數前按下述的操作步驟: 步驟 1:把 OP16_93LC46S.ASM 加到專案下(用[Project/Edit]指令)。 步驟 2:根據你的電路,修改 HT93LC46S.INC 文件連接 CS/SK/DI/DO 引腳。 步驟 3:包括 HT93LC46.ASM 在內的原始檔案呼叫介面函數。 註:在使用這些函數前要適當地設置輸入/輸出口的模式。

mov a, 04bh

mov data2, a

mov a, 0c3h

mov data3, a

call ht93lc46_wral

;ht93lc46 寫全部空間

nop

mov a,3fh

;ORG 腳接 VCC,64x16

mov temp,a

read_2:

clr data2

clr data3

mov a, temp

data3 db ?

porta equ

[70h]

sk

NM93C66TLVN中文资料

TL D 10045NM93C06L C46L C56L C66L256- 1024- 2048- 4096-Bit SerialEEPROMwithExtendedVoltage(2 7Vto5 5V)(MICROWIREBusInterface)November1996 NM93C06L C46L C56L C66L256- 1024- 2048- 4096-Bit Serial EEPROMwith Extended Voltage(2 7V to5 5V)(MICROWIRE TM Bus Interface)General DescriptionThe NM93C06L C46L C56L C66L devices are256 1024 2048 4096bits respectively of non-volatileelectrically erasable memory divided into16 64 128 256x16-bit registers(addresses) The NM93CxxL Family func-tions in an extended voltage operating range requires onlya single power supply and is fabricated using National Semi-conductor’s floating gate CMOS technology for high reliabili-ty high endurance and low power consumption These de-vices are available in both SO and TSSOP packages forsmall space considerationsThe EEPROM Interfacing is MICROWIRE compatible forsimple interface to standard microcontrollers and micro-processors There are7instructions that control these de-vices Read Erase Write Enable Erase Erase All WriteWrite All and Erase Write Disable The ready busy statusis available on the DO pin during programmingFeaturesY2 7V to5 5V operation in all modesY Typical active current of100m A Typical standbycurrent of1m AY No erase required before writeY Reliable CMOS floating gate technologyY MICROWIRE compatible serial I OY Self-timed programming cycleY Device status during programming modeY40years data retentionY Endurance 106data changesY Packages available 8-pin SO 8-pin DIP and8-pinTSSOPBlock DiagramTL D 10045–1TRI-STATE is a registered trademark of National Semiconductor CorporationMICROWIRE TM is a trademark of National Semiconductor CorporationC1996National Semiconductor Corporation RRD-B30M126 Printed in U S A http www national comConnection DiagramsDual-In-Line Package(N)8-Pin SO(M8)and8-Pin TSSOP(MT8)TL D 10045–2Top ViewNS Package Number N08E M08A or MTC08Pin NamesCS Chip SelectSK Serial Data Clock DI Serial Data Input DO Serial Data Output GND GroundV CC Power SupplyOrdering InformationCommercial Temp Range(0 C to a70 C)Order NumberNM93C06LN NM93C46LNNM93C56LN NM93C66LNNM93C06LM8 NM93C46LM8NM93C56LM8 NM93C66LM8NM93C06LMT8 NM93C46LMT8NM93C56LMT8 NM93C66LMT8Extended Temp Range(b40 C to a85 C)Order NumberNM93C06LEN NM93C46LENNM93C56LEN NM93C66LENNM93C06LEM8 NM93C46LEM8NM93C56LEM8 NM93C66LEM8NM93C06LEMT8 NM93C46LEMT8NM93C56LEMT8 NM93C66LEMT8Automotive Temp Range(b40 C to a125 C)Order NumberNM93C06LVN NM93C46LVNNM93C56LVN NM93C66TLVNNM93C06LVM8 NM93C46LVM8NM93C56LVM8 NM93C66LVM8NM93C06LVMT8 NM93C46LVMT8NM93C56LVMT8 NM93C66LVMT8http www national com2Absolute Maximum Ratings(Note1)If Military Aerospace specified devices are required please contact the National Semiconductor Sales Office Distributors for availability and specifications Ambient Storage Temperature b65 C to a150 C All Input or Output Voltages a6 5V to b0 3V with Respect to GroundLead Temp (Soldering 10sec )a300 C ESD Rating2000V Operating ConditionsAmbient Operating TemperatureNM93C06L–NM93C66L0 C to a70 C NM93C06LE–NM93C66LE b40 C to a85 C NM93C06LV–NM93C66LV b40 C to a125 C Power Supply(V CC)Range2 7V to5 5VDC and AC Electrical Characteristics 2 7V k V CC k4 5VSymbol Parameter Part Number Conditions Min Max UnitsI CCA Operating Current CS e V IH SK e250kHz1mAI CCS Standby Current CS e V IL10m AI IL Input Leakage V IN e0V to V CCg1m AI OL Output LeakageV IL Input Low Voltage b0 10 15V CCVV IH Input High Voltage0 8V CC V CC a1V OL Output Low Voltage I OL e10m A0 1V CCVV OH Output High Voltage I OH e b10m A0 9V CCf SK SK Clock Frequency0250kHzt SKH SK High Time1m st SKL SK Low Time1m st SKS SK Setup Time SK Must Be at V IL for0 2m st SKS before CS goes hight CS Minimum CS(Note2)1m s Low Timet CSS CS Setup Time0 2m st DH DO Hold Time70nst DIS DI Setup Time0 4m st CSH CS Hold Time0m st DIH DI Hold Time0 4m st PD1Output Delay to‘‘1’’2m st PD0Output Delay to‘‘0’’2m st SV CS to Status Valid1m st DF CS to DO in CS e V IL0 4m sTRI-STATEt WP Write Cycle Time15mshttp www national com3DC and AC Electrical Characteristics 4 5V k V CC k5 5VSymbol Parameter Part Number Conditions Min Max UnitsI CCA Operating Current CS e V IH SK e1MHz1mAI CCS Standby Current CS e V IL50m AI IL Input Leakage V IN e0V to V CCg1m AI OL Output Leakage(Note4)V IL Input Low Voltage b0 10 8V V IH Input High Voltage2V CC a1V OL1Output Low Voltage I OL e2 1mA0 4V V OH1Output High Voltage I OH e b400m A2 4V OL2Output Low Voltage I OL e10m A0 2V V OH2Output High Voltage I OL e b10m A V CC b0 2f SK SK Clock Frequency(Note5)01MHzt SKH SK High Time NM93C06L-NM93C66L250nsNM93C06LE-NM93C66LE300t SKL SK Low Time250nst SKS SK Setup TIme SK Must Be at V IL for50nst SKS before CS goes hight CS Minimum CS(Note2)250ns Low Timet CSS CS Setup Time50nst DH DO Hold Time70nst DIS DI Setup Time NM93C06L-NM93C66L100nsNM93C06LE-NM93C66LE200t CSH CS Hold Time0nst DIH DI Hold Time20nst PD1Output Delay to‘‘1’’500nst PD0Output Delay to‘‘0’’500nst SV CS to Status Valid500nst DF CS to DO in100ns TRI-STATE CS e V ILt WP Write Cycle Time10ms http www national com4Capacitance(Note3)T A e25 C f e1MHzSymbol Test Typ Max UnitsC OUT Output Capacitance5pFC IN Input Capacitance5pFNote1 Stress above those listed under‘‘Absolute Maximum Ratings’’may cause permanent damage to the device This is a stress rating only and operation of the device at these or any other conditions above those indicated in the operational sections of the specification is not implied Exposure to absolute maximum rating conditions for extended periods may affect device reliabilityNote2 CS(Chip Select)must be brought low(to V IL)for an interval of t CS in order to reset all internal device registers(device reset)prior to beginning another opcode cycle(this is shown in the opcode diagrams in the following pages)Note3 This parameter is periodically sampled and not100%testedNote4 Typical leakage values are in the20nA rangeNote5 The shortest allowable SK clock period e1 f SK(as shown under the f SK parameter) Maximum SK clock speed(minimum SK period)is determined by the interaction of several AC parameters stated in the datasheet Within this SK period both t SKH and t SKL limits must be observed Therefore it is not allowable to set 1 t SK e t SKH(minimum)a t SKL(minimum)for shorter SK cycle time operationAC Test ConditionsV CC RangeV IL V IH V IL V IH V OL V OHI OL I OH Input Levels Timing Levels Timing Levels2 7V s V CC k4 5V0 3V 1 8V1 0V0 8V 1 5V g10m A (Extended Voltage Levels)4 5V s V CC s5 5V0 4V 2 4V1 0V 2 0V0 4V 2 4V b2 1mA 0 4mA(TTL Levels)Output Load 1TTL Gate(C L e100pF)Functional DescriptionThe NM93C06L C46L C56L C66L device have7instruc-tions as described below Note that the MSB of any instruc-tion is a‘‘1’’and is viewed as a start bit in the interface sequence For the C06and C46the next8bits carry the op code and the6-bit address for register selection For the C56and C66the next10-bits carry the op code and the8-bit address for register selectionRead(READ)The READ instruction outputs serial data on the DO pin After a READ instruction is received the instruction and ad-dress are decoded followed by data transfer from the se-lected memory register into a16-bit serial-out shift register A dummy bit(logical0)precedes the16-bit data output string Output data changes are initiated by a low to high transition of the SK clockErase Write Enable(WEN)When V CC is applied to the part it powers up in the Erase Write Disable(WDS)state Therefore all programming modes must be preceded by an Erase Write Enable WENinstruction Once an Erase Write Enable instruction is exe-cuted programming remains enabled until an Erase WriteDisable(WDS)instruction is executed or V CC is completelyremoved from the partErase(ERASE)The ERASE instruction will program all bits in the selectedregister to the logical‘‘1’’state CS is brought low followingthe loading of the last address bit This falling edge of theCS pin initiates the self-timed programming cycleThe DO pin indicates the READY BUSY status of the chip ifCS is brought high after the t CS interval DO e logical‘‘0’’indicates that programming is still in progress DO e logical‘‘1’’indicates that the register at the address specified inthe instruction has been erased and the part is ready foranother instructionhttp www national com 5Functional Description(Continued)Write(WRITE)The WRITE instruction is followed by16bits of data to be written into the specificed address After the last bit of data is put on the data-in(DI)pin CS must be brought low before the next rising edge of the SK clock This falling edge of CS initiates the self-timed programming cycle The DO pin indi-cates the READY BUSY status of the chip if CS is brought high after the t CS interval DO e logical0indicates that programming is still in progress DO e logical1indicates that the register at the address specified in the instruction has been written with the data pattern specified in the in-struction and the part is ready for another instruction Erase All(ERAL)The ERAL instruction will simultaneously program all regis-ters in the memory array and set each bit to the logical‘‘1’’state The Erase All cycle is identical to the ERASE cycle except for the different op-code As in the ERASE mode the DO pin indicates the READY BUSY status of the chip if CS is brought high after the t CS intervalWrite All(WRALL)The WRALL instruction will simultaneously program all reg-isters with the data pattern specified in the instruction As in the WRITE mode the DO pin indicates the READY BUSY status of the chip if CS is brought high after the t CS interval Write Disable(WDS)To protect against accidental data distrub the WDS instruc-tion disables all programming modes and should follow all programming operations Execution of a READ instruction is independent of both the WEN and WDS instructionsNote NSC CMOS EEPROMs do not require an‘‘ERASE’’or‘‘ERASE ALL’’operation prior to the‘‘WRITE’’and‘‘WRITE ALL’’instructions The‘‘ERASE’’and ‘‘ERASE ALL’’instructions are included to maintain compatibility with earlier technology EEPROMsInstruction Set for the NM93C06L and NM93C46LInstruction SB Op Code Address Data CommentsREAD110A5–A0Reads data stored in memory at specified address WEN10011XXXX Enable all programming modesERASE111A5–A0Erase selected registerWRITE101A5–A0D15–D0Writes selected registerERAL10010XXXX Erases all registersWRALL10001XXXX D15–D0Writes all registersWDS10000XXXX Disables all programming modesNote Address bits A5and A4become‘‘Don’t Care’’for the NM93C06LInstruction Set for the NM93C56L and NM93C66LInstruction SB Op Code Address Data CommentsREAD110A7–A0Reads data stored in memory at specified address WEN10011XXXXXX Enable all programming modesERASE111A7–A0Erase selected registerWRITE101A7–A0D15–D0Writes selected registerERAL10010XXXXXX Erases all registersWRALL10001XXXXXX D15–D0Writes all registersWDS10000XXXXXX Disables all programming modesNote Address bit A7is‘‘Don’t Care’’for the NM93C56Lhttp www national com6Timing DiagramsSynchronous Data TimingTL D 10045–13READTL D 10045–5WENTL D 10045–67http www national comTiming Diagrams(Continued)WDSTL D 10045–7WRITETL D 10045–8WRALLTL D 10045–9 http www national com8Timing Diagrams(Continued)ERASETL D 10045–10ERALTL D 10045–119http www national comPhysical Dimensions inches(millimeters)unless otherwise notedMolded Small Out-Line Package(M8)NS Package Number M08Ahttp www national com10Physical Dimensions inches(millimeters)unless otherwise noted(Continued)Notes Unless otherwise specified1 Reference JEDEC Registration M0-153 Variation AA Dated7 938-Pin Molded TSSOP JEDEC(MT8)NS Package Number MTC0811http www national comN M 93C 06L C 46L C 56L C 66L 256- 1024- 2048- 4096-B i tS e r i a l E E P R O M w i t h E x t e n d e d V o l t a g e (2 7V t o 5 5V )(M I C R O W I R E B u s I n t e r f a c e )Physical Dimensions inches (millimeters)unless otherwise noted (Continued)Molded Dual-In-Line Package (N)NS Package Number N08E LIFE SUPPORT POLICY NATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION As used herein 1 Life support devices or systems are devices or 2 A critical component is any component of a life systems which (a)are intended for surgical implantsupport device or system whose failure to perform can into the body or (b)support or sustain life and whose be reasonably expected to cause the failure of the life failure to perform when properly used in accordance support device or system or to affect its safety or with instructions for use provided in the labeling can effectiveness be reasonably expected to result in a significant injury to the userNational SemiconductorNational Semiconductor National Semiconductor National Semiconductor Corporation EuropeSoutheast Asia Japan Ltd Fax a 49(0)180-5308586Fax (852)23763901Tel 81-3-5620-7561。

93c46使用方法(中文)

Rev.3.2_01应用手册 No.M103CMOS串行E2PROMS-2900A/29xxxA/93CxxA系列的使用方法目录1. 关于输入端子的连接 (2)2. 输入、输出端子等效电路 (2)2-1.输入端子 (2)2-2.输出端子 (3)3. 程序禁止指令 (4)4. 电源接通清除电路 (4)4-1.电源电压的上升方法 (4)4-2.初始化时间 (6)5. 关于往E2PROM传送16位写入数据的途中、CS下降时的写入工作 (7)6. 关于E2PROM的奇偶校验工作 (8)7. 关于输入端子噪声抑制时间 (9)8. 注意事项 (9)CMOS串行E2PROMS-2900A/29xxxA/93CxxA系列的使用方法Rev.3.2_01注意 不仅限于本公司的产品,由于E2PROM「在电源ON/OFF时工作于低电压领域内」以及「输入噪声信号而导致的指令的误识别」,具有引起误工作(误写入)的危险性。

特别是,负责传送指令给E2PROM的微机的电压,处于低于最低工作电压的电压范围内时,有可能发生这些故障。

在此所记载的内容是关于使用本E2PROM的重要内容,请务必认真阅读。

1.关于输入端子的连接S-2900A/29xxxA/93CxxA系列产品的输入端子全部为CMOS构造,所以在E2PROM工作时请设计为不能输入高阻抗。

特别是「电源ON/OFF时」和「工作待机时」,请设置CS输入为非选择状态。

数据的误写入在CS端子为非选择状态时(CS为Low、CS为High)不会发生。

因此,当CS极性为High 动态的情况下,推荐连接10 kΩ ~ 100 kΩ的下拉电阻。

为了更确实地防止误工作,虽然CS端子连接下拉/上拉电阻是最重要的,但也推荐除此以外的其他端子也连接同样的下拉/上拉电阻。

表1CS端子 High动态 Low动态CS端子的处理下拉电阻:10 kΩ ~ 100 kΩ上拉电阻:10 kΩ ~ 100 kΩ代表产品S-93C46A, S-29130A S-29194A2.输入、输出端子等效电路表示E2PROM输入端子的等效电路。

汽车电子常用芯片型号代换资料

汽车电子常用芯片型号代换资料汽车电子常用芯片型号代换资料汽车电子, 存储器标志印字芯片功能代换型号BOSCH3003930061 ADC0809B22AN 存储器 93C06B34AB 存储器 24C02B43AB 存储器 24C02B46AJ 存储器 24C02B49AJ 存储器 24C02B52AP 存储器 24C02B54AH 存储器 24C02B57120 存储器 27C64B57324 存储器 2732AB57347 存储器 27C64B57423 存储器 27C256B57449 74HC74B57477 存储器 27C64B57519 存储器 27C64B57581 74HC573B57604 存储器 27C256B57605 存储器 27256B57607 存储器 27C128B57610 存储器 27C128B57618 存储器 87C257B57618 存储器 87C64B57625 存储器 2764AB57654 存储器 27C256B57701 存储器 27C256B57733 4x位开关 TLE4211, TLE6220 B57764 存储器 87C257 B57764 存储器 87C64B57771 存储器 27C256B57922 存储器 87C257B57960 存储器 27C256B57995 存储器 TMS27C256B58014 存储器 27C256B58038 存储器 27C256B58094 存储器 27C510B58126 存储器 27C010B58127 存储器 27C512B58150 存储器 87C257B58157 存储器 27C512B58185 存储器 87C257B58196 存储器 NS93C46B58234 存储器 27C256B58235 存储器 87C257B58239 存储器 27C512B58240 6 x位开关 TLE4216G, TLE4226GB58241 4 x位开关 TLE4214G, TLE6225B58243 存储器 CJ87BC6QGB58244 I87M12B58258 存储器 24C02B58265 控制器 CAN控制器??B58275 存储器 27C1024B58286 控制器 SAB80C166B58293 存储器 27C512B58331 存储器 28F010B58380 存储器 24C02B58381 存储器 AM28F512B58399 存储器 AM29F010B58400 存储器 87C510B58424 存储器 27C512B58502 ABS,ASR系统IC TLE5200G, TLE6210G B58504 ABS,ASR系统IC TLE5201G, TLE6211G B58505 2 x位开关TLE5225G, TLE6215GB58517 存储器 28F020B58533 存储器 27C4096B58539 存储器 27C256B58541 存储器 27C512B58542 存储器 27C512B58543 存储器 27C512B58544 存储器 27C1001B58545 存储器 87C257B58546 存储器 87C510B58547 存储器 27C1001B58548 存储器 TMS27PC210 = 27C1024B58550 存储器 27C512B58590 AS87C196ENB58637 4 x位开关 TLE5226G, TLE6216GB58639 存储器 87PC110B58732 4 x位开关 TLE5216G, TLE6220B58755 存储器 AM29F200B58768 存储器 AM29F400ABB58791 存储器 AM29F200ABB58813 存储器 93C56B58911 存储器 TMS27C010AB58335 存储器 AT28C64BB58601 存储器 AM29F200BB9411 存储器 AM27C256DELCO08393 功放 TDA7372A96405 功放 TDA7376B9355092 存储器 24C049355093 存储器 24C0816124342 功放 TDA736016175974 RDS解调器SAA6579 16219796 功放TDA7454 100% , not TDA7384 16233541 存储器 M27C256BPIONEERPA2024A 电源 TA8244HPA3002 功放 HA1397PA3005 功放 HA1384PA3027A 功放 HA13150APA3029A 功放 HA13151PA3029B 功放 HA13151PAL001A 功放 TDA7394PAL002A 功放 TDA7394PAL003A 功放 TDA7384APAL005A 功放 TDA7385PAL006A 功放 TDA7560PAL007A 功放 TDA7560PAU001A 功放 HA13151VISTEON0022FBCAC 电源 TL751M100040FBCAC 电源 TL751M1077002 I2C存储器 24C167008FB 电源 78L0570001BB RDS解调器 TDA733070001SE RDS解调器 TDA733070001RR RDS解调器 TDA7330 ??70002FE 音频处理器 TDA731170003AB 功放 TDA200370003SC FREQ. SYNTH.70003SE RDS解调器 TDA733070005EB PLL立体声译码器 TDA159170005EH 音频处理器 TDA7340P70006SE 音频处理器 TDA734070008AB 功放 TDA736070009AB 功放 11 pins70010AB 功放 TDA735070010BB 双运放 TDA342070010FB 电源 TL751M1070011AB 功放 TDA7350with some modifications 70011SB 音频处理器 TDA152470014BB 控制放大器 LM83770016SE 音频处理器 TDA7460N70017AB 驱动放大 TDA723770017FB 电源 TA1483270019SB 音频处理器70023AB 功放 TDA739170024AB 功放 TDA737570024SB 杜比电路 TEA065570025SB AMS LA201070026SB FRONT END70027SB70028SB IF/DET70029SB 音频处理器 TDA730670032AB 前置放大 TDA1523 ??70033BB 控制放大器 LM83770034AB 功放 TDA1519B70039AB 功放 TDA8566Q70042FB 电源 L084, L495370043AB TEA0675 or TDA8586Q70045SB 杜比电路 TEA067570047SB 杜比电路 TEA0675T70052AB 功放 TDA8586Q70082FB 电源70530FB 电源70670FS 前置放大 TEA0676T71005DC LCD显示驱动 PCF857771005TB 多频调制 DS36277N7100130 PCF8576TN700700CFFB000 电源 PHIL, HSOP-20 F2DF-14A652-EA 电源TL751M10SONY159-00 功放 HA13151160-00 功放 HA13151180-00 功放 HA13152260-41 功放 HA13151260-77 功放 HA13150A279-82 功放 HA13151279-87 功放 HA13151279-89 功放 HA13152360-47 功放 HA13153365-41 功放 HA13155368-11 电子音量 LC75372E 369-41 功放 HA13155369-42 功放 HA13153426-49 功放 HA13155448-48 功放 HA13157448-61 功放 HA13156490-48 功放 HA13158PICKUPSOPTIMA-150S JVC OPTIMA-6S KSP-1H KENWOOD KSS-213F RAE0142Z MATSUSHITA RAE0144 1121 SONY KSS-210A KSS-168A SONY KSS-320BKSS-412A SONY KSS-401AKSS-401A SONY KSS-412AKSS-313A SONY KSS-313CKSS-240 SONY KSS-390KSS-314A SONY KSS-313A SOH-AAU SAMSUNG KSS-213KSS-540A SONY KSS-541AKSS-520A SONY KSS-521AMOTOROLAMC13304T3 功放 TA8215MC13306T3S 功放 TA8205MC13309T3 功放 TA8215MC13320T3 功放CHRYSLER 4632512 音频处理器TDA7314S 4651311 功放TDA1553Q4391943 74HC004392073 27C2564392075 74HC144517571 74HC3734517572 74HC74 ??4632511 TDA1591T4632858 TDA3601AQ4632990 M28F1024651350 L9222AOTHERSM851G OKI , 存储器 93C4616811G OKI , 存储器 93C4616911 OKI , 存储器 59C11 ADxxxx YAZAKI, 存储器 93C46 8-bit ABxxxx YAZAKI, 存储器 ER59C11标志印字芯片功能代换型号BOSCH3003930061 ADC0809B22AN 存储器 93C06B34AB 存储器 24C02B43AB 存储器 24C02B46AJ 存储器 24C02B49AJ 存储器 24C02B52AP 存储器 24C02B54AH 存储器 24C02B57120 存储器 27C64B57324 存储器 2732AB57347 存储器 27C64B57423 存储器 27C256B57449 74HC74B57477 存储器 27C64B57519 存储器 27C64B57581 74HC573B57604 存储器 27C256B57605 存储器 27256B57607 存储器 27C128B57610 存储器 27C128B57618 存储器 87C64B57625 存储器 2764AB57654 存储器 27C256B57696 存储器 27C256B57701 存储器 27C256B57733 4x位开关 TLE4211, TLE6220B57764 存储器 87C257B57764 存储器 87C64B57771 存储器 27C256B57808 存储器 27C256B57922 存储器 87C257B57960 存储器 27C256B57995 存储器 TMS27C256B58014 存储器 27C256B58038 存储器 27C256B58094 存储器 27C510B58126 存储器 27C010B58127 存储器 27C512B58150 存储器 87C257B58157 存储器 27C512B58185 存储器 87C257B58196 存储器 NS93C46B58234 存储器 27C256B58235 存储器 87C257B58239 存储器 27C512B58240 6 x位开关TLE4216G, TLE4226G B58241 4 x位开关TLE4214G, TLE6225 B58243 存储器 CJ87BC6QGB58244 I87M12B58258 存储器 24C02B58265 控制器 CAN控制器??B58275 存储器 27C1024B58286 控制器 SAB80C166B58293 存储器 27C512B58331 存储器 28F010B58380 存储器 24C02B58381 存储器 AM28F512B58399 存储器 AM29F010B58400 存储器 87C510B58424 存储器 27C512B58502 ABS,ASR系统IC TLE5200G, TLE6210G B58504 ABS,ASR系统IC TLE5201G, TLE6211G B58505 2 x位开关TLE5225G, TLE6215GB58517 存储器 28F020B58530 存储器 AM29F010B58533 存储器 27C4096B58539 存储器 27C256B58541 存储器 27C512B58542 存储器 27C512B58543 存储器 27C512B58544 存储器 27C1001B58545 存储器 87C257B58546 存储器 87C510B58547 存储器 27C1001B58548 存储器 TMS27PC210 = 27C1024B58550 存储器 27C512B58590 AS87C196ENB58637 4 x位开关 TLE5226G, TLE6216GB58639 存储器 87PC110B58732 4 x位开关 TLE5216G, TLE6220B58755 存储器 AM29F200B58768 存储器 AM29F400ABB58791 存储器 AM29F200ABB58813 存储器 93C56B58911 存储器 TMS27C010AB58335 存储器 AT28C64BB58601 存储器 AM29F200BB9411 存储器 AM27C256DELCO08393 功放 TDA7372A9355092 存储器 24C049355093 存储器 24C0816124342 功放 TDA736016175974 RDS解调器SAA6579 16219796 功放TDA7454 100% , not TDA7384 16233541 存储器 M27C256BPIONEERPA2024A 电源 TA8244HPA3002 功放 HA1397PA3005 功放 HA1384PA3027A 功放 HA13150APA3029A 功放 HA13151PA3029B 功放 HA13151PAL001A 功放 TDA7394PAL002A 功放 TDA7394PAL003A 功放 TDA7384APAL005A 功放 TDA7385PAL006A 功放 TDA7560PAL007A 功放 TDA7560PAU001A 功放 HA13151VISTEON0022FBCAC 电源 TL751M100040FBCAC 电源 TL751M1077002 I2C存储器 24C167008FB 电源 78L0570001BB RDS解调器 TDA733070001SE RDS解调器 TDA733070001RR RDS解调器 TDA7330 ??70002FE 音频处理器 TDA731170003AB 功放 TDA200370003SC FREQ. SYNTH.70003SE RDS解调器 TDA733070005EB PLL立体声译码器 TDA159170005EH 音频处理器 TDA7340P70006SE 音频处理器 TDA734070009AB 功放 11 pins70010AB 功放 TDA735070010BB 双运放 TDA342070010FB 电源 TL751M1070011AB 功放 TDA7350with some modifications 70011SB 音频处理器 TDA152470014BB 控制放大器 LM83770016SE 音频处理器 TDA7460N70017AB 驱动放大 TDA723770017FB 电源 TA1483270019SB 音频处理器70023AB 功放 TDA739170024AB 功放 TDA737570024SB 杜比电路 TEA065570025SB AMS LA201070026SB FRONT END70027SB70028SB IF/DET70029SB 音频处理器 TDA730670032AB 前置放大 TDA1523 ??70033BB 控制放大器 LM83770034AB 功放 TDA1519B70039AB 功放 TDA8566Q70042FB 电源 L084, L495370043AB TEA0675 or TDA8586Q70045SB 杜比电路 TEA067570047SB 杜比电路 TEA0675T70052AB 功放 TDA8586Q70082FB 电源70530FB 电源70670FS 前置放大 TEA0676T71005DC LCD显示驱动 PCF857771005TB 多频调制 DS36277N7100130 PCF8576TN700700CFFB000 电源 PHIL, HSOP-20F2DF-14A652-EA 电源 TL751M10SONY159-00 功放 HA13151160-00 功放 HA13151180-00 功放 HA13152260-41 功放 HA13151260-77 功放 HA13150A279-82 功放 HA13151279-87 功放 HA13151279-89 功放 HA13152360-47 功放 HA13153365-41 功放 HA13155368-11 电子音量 LC75372E 369-41 功放 HA13155369-42 功放 HA13153426-49 功放 HA13155448-48 功放 HA13157448-61 功放 HA13156490-48 功放 HA13158PICKUPSOPTIMA-150S JVC OPTIMA-6SKSP-1H KENWOOD KSS-213F RAE0142Z MATSUSHITA RAE0144 1121 SONY KSS-210AKSS-168A SONY KSS-320BKSS-412A SONY KSS-401AKSS-401A SONY KSS-412AKSS-313A SONY KSS-313CKSS-240 SONY KSS-390KSS-314A SONY KSS-313ASOH-AAU SAMSUNG KSS-213KSS-540A SONY KSS-541AKSS-520A SONY KSS-521AMOTOROLAMC13304T3 功放 TA8215MC13306T3S 功放 TA8205MC13309T3 功放 TA8215MC13320T3 功放CHRYSLER4632512 音频处理器 TDA7314S4651311 功放 TDA1553Q4391943 74HC004392073 27C2564392075 74HC144517571 74HC3734517572 74HC74 ??4632511 TDA1591T4632858 TDA3601AQ4632990 M28F1024651350 L9222AOTHERSM851G OKI , 存储器 93C4616811G OKI , 存储器 93C4616911 OKI , 存储器 59C11 ADxxxx YAZAKI, 存储器 93C46 8-bit ABxxxx YAZAKI, 存储器 ER59C11第1部分汽车音响常用集成电路1.1 收音系统电路1.1.1 AN7222 AM调谐,AM/FM中频放大电路1.1.2 AN7254 FM前端电路1.1.3 AN7463S 带消噪的FM立体声解码器 1.1.4 BA403 FM中频放大器1.1.5 BA1310 锁相环式FM立体声解码器1.1.6 BA1332/BA1332L 锁相环式FM立体声解码器1.1.7 BA1350 带噪声抑制的FM立体声解码器 1.1.8 BA1405/BA1405F FM立体声调制器1.1.9 CX20029 AM/FM立体声收音机电路 1.1.10 CXA1101P/CXA1101M 双通道杜比B型降噪电路1.1.11 CXA1102P/CXA1102M 双通道杜比B型降噪电路1.1.12 CXA1238M/CXA1238S AM/FM立体声收音电路1.1.13 HA11219 FM噪声抑制电路1.1.14 HA12134A 双通道杜比B型降噪电路 1.1.15 KA2244 FM 中频放大器1.1.16 KA2261 锁相环式FM立体声解码器1.1.17 KB4409 锁相环式FM立体声解码器1.1.18 KIA6010SN FM噪声抑制电路1.1.19 LA1130 AM调谐电路1.1.20 LA1132 AM调谐电路1.1.21 LA1135 AM调谐电路1.1.22 LA1140 FM中频放大器1.1.23 LA1175 FM调谐电路1.1.24 LA1862M FM立体声解码器1.1.25 LA2110 FM消噪电路1.1.26 LA3365 锁相环式FM立体声解码器 1.1.27 LA3370 锁相环式FM立体声解码器1.1.28 LA3375 锁相环式FM立体声解码器1.1.29 LA3430 带消噪功能的锁相环式FM立体声解码器1.1.30 LB3500 FM本振频率1/8分频器1.1.31 LC7218/LC7218M/LC7218JM 电子调谐PLL频率合成器1.1.32 LC7219/LC7219M/LC7219JM 电子调谐PLL频率合成器1.1.33 LC72131/LC72131M AM/FM PLL频率合成器1.1.34 LC72146/LC72146M/LC72146V 电子调谐PLL频率合成器1.1.35 LC72191/LC72191M/LC72191JM 立体声电子调谐PLL频率合成器1.1.36 LC72722/LC72722M/LC72722PM 单片RDS信号处理系统1.1.37 LM7001/LM7001M 电子调谐辅助微处理器1.1.38 TA7343AP/TA7343AF 锁相环式FM立体声解码器1.1.39 TA7358P/AP FM调谐电路1.1.40 TA7640AP AM调谐,AM/FM中频放大器 1.1.41 TA8122N/TA8122F 3V AM/FM调谐电路1.1.42 TA8127N/TA8127F 3V AM/FM调谐电路1.1.43 TA8132N/TA8132F AM/FM中放及立体声解码器1.1.44 TA8164P 3V AM/FM收音机电路1.1.45 TC9246F/TC9246P 数字音响锁相环电路1.1.46 TD7104P/TD7104F 数字合成调谐器用ECL预引比例器1.1.47 TDA1579/TDA1579T 交通告警无线传输解码器1.1.48 TEA0652 杜比B/C型降噪电路1.1.49 TEA5560 FM中频放大器1.1.50 μPB553AC 150M Hz低功耗分频电路1.1.51 μPC1167C2 FM中频放大器1.1.52 μPC1171C AM调谐电路1.1.53 μPC1191V AM调谐电路1.1.54 μPC1200V FM中频放大器1.1.55 μPC1215V AM电子调谐电路1.2 磁带放音系统电路1.2.1 AN6263N 磁带暂停检测电路1.2.2 BA338/BA338L 自动选曲电路1.2.3 BA3430S/BA3430F/BA3430FS 带静噪检测的立体声前置放大器1.2.4 BA6219B/BA6219BFP Y 双向电机驱动器1.2.5 BA6285FP/BA6285FS 双向电机驱动器 1.2.6 CXA2509AQ 带选曲功能的均衡放大器 1.2.7 D7784P 双声道磁头选择开关、自动翻转及放大器1.2.8 LA2000/LA2000S 单曲自动选曲电路1.2.9 LB1641 双向电机驱动器1.2.10 LB1649 双桥式电机驱动器1.2.11 LB1836M 桥式电机驱动器1.2.12 MM1322XFBE 电机驱动控制电路1.2.13 TA7291P/TA7291S/TA7291F 电机驱动控制电路1.2.14 μPC1470H 电机速度控制器1.3 音频处理电路1.3.1 AN214 4.4W音频功率放大器1.3.2 AN7168 5.8W×2双通道音频功率放大器1.3.3 AN7178 5.7W×2双通道音频功率放大器1.3.4 AN7310N 立体声双通道音频前置放大器1.3.5 AN7311 立体声双通道音频前置放大器1.3.6 BA328双通道音频前置放大器1.3.7 BA5406 5W×2音频功率放大器1.3.8 CXA1646Q 电子音量控制电路1.3.9 CXA1946AQ 电子音量控制电路1.3.10 HA13001 5.5W×2(BTL 17.5W)音频功率放大器1.3.11 HA13119 5.5W×2音频功率放大器1.3.12 HA13150A 21W×4 BTL音频功率放大器1.3.13 HA13151/HA13151A 14W×4 BTL音频功率放大器1.3.14 HA 13153 15W×4 BTL音频功率放大器 1.3.15 HA 13155 33W×4 B TL音频功率放大器1.3.16 LA2900M 双通道高电平线路放大器1.3.17 LA3160 双通道音频前置放大器1.3.18 LA4440 6W×2(BTL 19W)音频功率放大器1.3.19 LA4445 5.5W×2音频功率放大器1.3.20 LA4743B 45W×4(BTL 19W)音频功率放大器1.3.21 LA47501 50W×4(BTL 19W)音频功率放大器1.3.22 LC7538NM 电子音色控制电路1.3.23 LC75373ED 电子音量控制电路1.3.24 LC75383ED 电子音量控制电路1.3.25 M51522AL 双通道音频前置放大器1.3.26 TA7227P 5.5W×2音频功率放大器 1.3.28 TA7240P/TA7240AP 5.8W×2音频功率放大器1.3.29 TA7270P 5.8W×2音频功率放大器 1.3.30 TA7325P 双通道音频前置放大器。

串行EEPROM 93C46的操作方法

写入一个字(16 位): // Writes memory location An A0. void Write(unsigned char address,unsigned int InData) { unsigned char temp; Ewen(); SK=0; DI=1; // 101 A5A0 CS=0; CS=1; SK=1; SK=0; // 1 address=address&0x3f|0x40; for(temp=8;temp!=0;temp) // 8 { DI=address&0x80; SK=1; SK=0; address<<=1; } for(temp=16;temp!=0;temp) // 16 { DI=InData&0x8000; SK=1; SK=0; InData<<=1; } CS=0; DO=1; CS=1; SK=1; while(DO==0) // busy test { SK=0; SK=1; } SK=0; CS=0; Ewds(); }

数据读取:

数据写入:

93C46 共有七种操作,如下列所示:

指令

功能描述

操作码 ORG=0 字节 数据 ORG=1 字 数据

READ

读取数据

10

AQ0

WRITE

写入数据

01

A6~A0

D7~D0 A5~A0 D15~D0

EWEN

擦/写使能

00

11XXXXX

11XXXX

程序流程: 1、先将要写入的字节所在的字读出。 2、根据原始地址的最后一位决定把要写入的字节放到高八位还是低八位。如果为1 高八位, 0 为低八位。 3、把合成的字写入到相应地址上。

AV93LC46资料

1024-BITS SERIAL ELECTRICALLY ERASABLE PROMFeaturesState-of-the-art architecture-Non-volatile data storage-Operating voltage Vcc : 2.7-5.5V-Full TTL compatible inputs and outputs -Auto increment read efficient data dump Hardware and software write protection-Defaults to write-disabled state at power up -Software instructions for write-enable/disable -Vcc level verification before self-timed programming cycleAdvanced low voltage CMOS EEPROM technologyGeneral DescriptionThe AV93LC46 is a 1024-bit, non-volatile, serial EEPROM. It is manufactured by using advanced CMOS EEPROM technology. The AV93C46 provides efficient non-volatile read/write memory arranged as 64registers of 16 bits each. Seven 9-bit instructions control the operation of the device, which includes read,write and write enable/disable functions. The data out pin (DO) indicates the status of the device during the self-timed non-volatile programming cycle.The self-timed write cycle includes an automatic erase-before write capability. Only when the chip is in the WRITE ENABLE state and proper Vcc operation range is the WRITE instruction accepted and thus to protect Against inadvertent writes, Data is written in 16 bits per write instruction into the selected register. If chip select (CS) is brought HIGH after initiation of the write cycle, the data output (DO) pin will indicate the READY/BUSY status of the chip.The AV93C46 is available in space-saving 8-lead PDIP, 8-lead SOP and rotated 8-lead SOP package.CONNECTION DIAGRAMPIN ASSIGNMENTCSChip Select SK Serial Data Clock DI Serial Data Input DO Serial Data OutputGND Ground VCC Power Supply NCNo ConnectionORDERING INFORMATIONAV93LC46 XXAV ----------AVIC Electronics CO.,LTDLC ----------Operating Voltage : 2.7~5.5V, CMOS46 ----------Type : 1KXX --------- SC/PC/SI/PI/TC/TI(S----SOP8; P----DIP8; T----TSSOP; C----0℃~+70℃; I---- -45℃~+80℃)Block DiagramAbsolute Maximum RatingsStorage Temperature…………………. –65℃ to +125℃Voltage with Respect to Ground………-0.3 to +6.5 VNOTE:These are STRESS rating only. Appropriate conditions for operating these devices given elsewhere may permanently damage the part. Prolonged exposure to maximum ratings may affect device reliability. Operating ConditionsTemperature under bias AV93LC46……………0℃ to +70℃DC Electrical Characteristics (Vcc=2.7V-5.5V,Ta=25℃, unless otherwise noted)symbolParameterconditionsMinMaxUnitsIcc1 Operating Current (Program)SCL=10KHz CMOS Input Leavels - 3 mAIcc2 Operating Current (Read)SCL=10KHz CMOS Input Leavels - 200 uAI SB1 Stabdby Current SCL =SDA =0V,Vcc =5V - 10 uA I SB2 Stabdby Current SCL =SDA =0V,Vcc =3V - 1 uA I IL Input Leakage V IN =0V to Vcc -1 +1 uA I OL Output Leakage Vout=0V to Vcc -1 +1 uA V IL Input Low Voltage**-0.1 Vcc X 0.3 VV IH Input High Voltage** Vcc X 0.7Vcc+0.2 VV OL1 Output Low Voltage I OL =2.1mA TTL - 0.4 V V OL2 Output Low Voltage I OL =10uA CMOS - 0.2 V V LK Vcc Lockout Voltage Programming Command Can Be ExecutedDefault - VNote. ** V IL min and V IH max are reference only and are not testedAC Electrical Characteristics (Vcc=2.7V – 5.5V, Ta=25℃ unless otherwise noted ) Symbol Parameter Conditions Min Max Units F SK SK Clock Frequency 0 1 MHzT SKH SK High Time 250 ns T SKL SK Low Time 250 ns T CS Minimum CS Low Time 250 nsT CSS CS Setup Time Relative to SK 50 ns T DIS DI Setup Time Relative to SK 100 ns T CSH CS Hold Time Relative to SK 0 ns T DIH DI Hold Time Relative to SK 100 ns T PD1 Output Delay to “1” AC Test 500 ns T PD0 Output Delay to “0” AC Test 500 ns T SVCS to Status Valid AC Test CL=100pF500 nsT DF CS to DO in 3-state CS=VIL 100 ns T WP Write Cycle Time 10 ms Endurance** 5V,25℃,Page Mode1M Write cycles Note. ** The Parameter is characterized and isn’t 100% tested.Instruction SetInstruction Start Bit OP Code Address Input Data10A5-A0READ 1WEN(Write Enable) 1 00 11XXXXD15-D0*A5-A0WRITE 101WRALL (Write all Registers) 1 00 01XXXX D15-D0* WDS (Write Disable) 1 00 00XXXXA5-A011ERASE 1ERAL (Erase All Registers) 1 00 10XXXX* If input Data is not 16 bits exactly, the last 16 bits will be taken as input data ( a word )Pin Capacitance ** (Ta=25℃, f=1MHz)Symbol Parameter Max UnitsCapacitance 5 pF Cout OutputCapacitance 5 pFC IN InputFunctional DescriptionsApplicationsThe AV93LC46 is ideal for high volume applications requiring low power and low density storage. This device uses a low cost, space saving 8-pin package. Typical applications include robotics, alarm devices, electronic locks, meters and instrumentation settings such as LAN cards, monitors and MODEM. Endurance and Data RetentionThe AV93LC46 is designed for applications requiring up to 1000K programming cycles (WRITE, WRALL, EARSE and ERAll). It provides 40 years of secure data retention without power after the execution of 1000K programming cycles.Device OperationThe AV93LC46 is controlled by seven 9-bit instructions. Instructions are clocked in (serially) on the DI pin.Each instruction begins with a logical “1” (the start bit). This is followed by the opcode (2 bits), the address field (6 bits), and data, if appropriate. The clock signal (SK) may be halted at any time and theAV93LC46 will remain in its last state. This allows full static flexibility and maximum power conservation.Read (READ)The READ instruction is the only instruction that outputs serial data on the DO pin. After the read instruction and address have been decoded, data is transferred from the selected memory register into a 16-bit serial shift register. (Please note that one logical “0” bit precedes the actual 16-bit output data string.) the output on DO changes during the rising edge transitions of SK. (Shown in Figure 3 )Auto Increment Read OperationsSequential read is possible, since the AV93LC46 has been designed to output a continuous stream of memory content in response to a single read operation instruction. To utilize this function, the system asserts a read instruction specifying a start location address. Once the 16 bits of the addressed word have been clocked out, the data in consecutively higher address locations (the address “0000” is assumed as the higher address of “111111”) is output. The address will wrap around continuously with CS high until the chip select (CS) control pin is brought low. This allows for single instruction data dumps to executed with a minimum of firmware overhead.Write Enable (WEN)Before any device programming (WRITE, WRAll, ERASE, and ERAl) can be done, the WRITE ENABLE (WEN) instruction must be executed first. When Vcc is applied, this device powers up in the WRITE DISABLE state. The device then remains in a WRITE DISABle state until a WEN instruction is executed. Thereafter the device remains enabled until a WDS instruction is executed or until Vcc is removed. (NOTE: Neither the Wen nor the WDS instruction has any effect on the READ instruction.) (Shown in Figure 4.)Write Disable (WDS)The WRITE DISABLE (WDS) instruction disables all programming capabilities. This protects the entire part against accidental modification of data until a WEN instruction is executed. (When Vcc is applied, this part powers up in the WRITE DISABLE state.) To protect data, a WDS instruction should be executed upon completion of each programming operation. (NOTE: Neither the WEN nor the WDS instruction has any effect on the READ instruction.) (Shown in Figure 5.)Functional Description (Continued)Write (WRITE)The WRITE instruction includes 16 bits of data to be written into the specified register . After the last bit has been applied to DI, and before the next rising edge of SK, CS must be brought LOW. The falling edge of CS initiates the selftimed programming cycle.After a minimum wait of 250ns (5V operation) from the falling edge of CS (tcs), DO will indicate the READY/BUSY status of the chip if CS is brought HIGH. This means that logical “0” implies the programming is still in progress while logical “1” indicates the selected register has been written, and the part is ready for another instruction.(See Figure 6.)Note: The combination of CS HIGH, DI HIGH and the rising edge of the SK clock, resets theREADY/BUSY flag. Therefore, it is important if you want to access the READY/BUSY flag,not to reset it through this combination of control signals.Before a WRITE instruction can be executed, the device must be in the WRITE ENABLE (WEN) state. Write All (WRALL)The write All (WRALL) instruction programs all registers with the data pattern specified in the instruction. While the WRALL instruction is being loaded, the address field becomes a sequence of DON’T-CARE bits. (Shown in Figure 7.)As with the WRITE instruction, if CS is brought HIGH after a minimum wait of of 250ns (tcs), the DO pin indicates the READY/BUSY status of the chip. (Shown Figure 7.)ERASE (ERASE)After the erase instruction is entered, CS must be brought LOW. The falling edge of CS initiates the self-timed internal programming cycle. Bringing CS HIGH after minimum of tcs, will cause DO to indicate the READY/BUSY status of the chip. To explain this, a logical “0” indicates the programming is still in progress while a logical “1” indicates the erase cycle is complete and the part is ready for another instruction. (Shown in Figure 8.)Erase All (ERALL)Full chip erase is provided for ease of programming. Erasing the entire chip involves setting all the entire memory array a logical “1”. (Shown in Figure 9.)Security ConsiderationTo protect the entire part against accidental modification of data, each programming instruction (WRITE, WRALL, ERASE, and ERALL) must satisfy two conditions before user initiate self-timed programming cycle (the falling edge of CS). One is that the AV93LC46 is at WEN status. The other is that Vcc value must exceed a lock-out value which can be adjusted by AVIC.Timing Diagram (1)Organization KeyI/OAV93LC46 (1K) AV93LC56 (2K)X 8 X 16 X 8 X 16A N A6A5A8(1)A7(2)D N D7D15D7D15 Note : (1). A8 is a DON’T CARE value, but the extra clock is required.(2). A7 is a DON’T CARE value, but the extra clock is required.Timing Diagram (2)Timing Diagram (3)。

93LC46B中文资料

FEATURES•Single supply with operation down to 2.5V •Low power CMOS technology - 1 mA active current (typical)- 1 µ A standby current (maximum)•128 x 8 bit organization (93LC46A)•64 x 16 bit organization (93LC46B)•Self-timed ERASE and WRITE cycles (including auto-erase)•Automatic ERAL before WRAL•Power on/off data protection circuitry •Industry standard 3-wire serial interface•Device status signal during ERASE/WRITE cycles •Sequential READ function•1,000,000 E/W cycles guaranteed •Data retention > 200 years•8-pin PDIP/SOIC and 8-pin TSSOP packages •Available for the following temperature ranges: DESCRIPTIONThe Microchip T echnology Inc. 93LC46AX/BX are 1K-bit, low voltage serial Electrically Erasable PROMs. The device memory is configured as x8 (93LC46A) or x16 bits (93LC46B). Advanced CMOS technology makes these devices ideal for low power nonvolatile memory applications. The 93LC46AX/BX is available in standard 8-pin DIP , 8-pin surface mount SOIC, and TSSOP packages. The 93LC46AX/BX are offered only in a 150-mil SOIC package.-Commercial (C):0 ° C to +70 ° C -Industrial (I): -40 ° C to +85 °C元器件交易网93LC46A/B1.0ELECTRICALCHARACTERISTICS1.1Maximum Ratings* Vcc...................................................................................7.0V All inputs and outputs w.r.t. Vss ................-0.6V to Vcc +1.0V Storage temperature.....................................-65°C to +150°C Ambient temp. with power applied.................-65°C to +125°C Soldering temperature of leads (10 seconds).............+300°C ESD protection on all pins................................................4 kV*Notice: Stresses above those listed under “Maximum ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended peri-ods may affect device reliability.TABLE 1-1PIN FUNCTION TABLE Name FunctionCS Chip SelectCLK Serial Data ClockDI Serial Data InputDO Serial Data OutputV SS GroundNC No ConnectV CC Power SupplyTABLE 1-2DC AND AC ELECTRICAL CHARACTERISTICSAll parameters apply over the specified operating ranges unless otherwise noted Commercial (C): V CC = +2.5V to +6.0V Tamb = 0°C to +70°C Industrial (I):V CC = +2.5V to +6.0V Tamb = -40°C to +85°CParameter Symbol Min.Max.Units ConditionsHigh level input voltage V IH1 2.0Vcc +1V 2.7V < V CC≤ 5.5V (Note 2) V IH20.7 V CC Vcc +1V V CC < 2.7VLow level input voltage V IL1-0.30.8V V CC > 2.7V (Note 2) V IL2-0.30.2 Vcc V V CC < 2.7VLow level output voltage V OL1—0.4V I OL = 2.1 mA; Vcc = 4.5VV OL2—0.2V I OL =100 µA; Vcc = Vcc Min.High level output voltage V OH1 2.4—V I OH = -400 µA; Vcc = 4.5VV OH2V CC-0.2—V I OH = -100 µA; Vcc = Vcc Min.Input leakage current I LI-1010µA V IN = V SS to Vcc Output leakage current I LO-1010µA V OUT = V SS to VccPin capacitance (all inputs/outputs)C IN, C OUT—7pFV IN/V OUT = 0 V (Notes 1 & 2)Tamb = +25°C, F CLK = 1 MHzOperating current I CC write— 1.5mAI CC read— 1500mAµAF CLK = 2 MHz; Vcc = 6.0VF CLK = 1 MHz; Vcc = 3.0VStandby current I CCS—1µA CS = VssClock frequency F CLK—21MHzMHzV CC > 4.5VV CC < 4.5VClock high time T CKH250—nsClock low time T CKL250—nsChip select setup time T CSS50—ns Relative to CLK Chip select hold time T CSH0—ns Relative to CLK Chip select low time T CSL250—nsData input setup time T DIS100—ns Relative to CLK Data input hold time T DIH100—ns Relative to CLK Data output delay time T PD—400ns C L = 100 pFData output disable time T CZ—100ns C L = 100 pF (Note 2) Status valid time T SV—500ns C L = 100 pFProgram cycle time T WC—6ms ERASE/WRITE mode T EC—6ms ERAL modeT WL—15ms WRAL modeEndurance—1M—cycles25°C, V CC = 5.0V, Block Mode (Note 3)Note 1:This parameter is tested at T amb = 25°C and Fclk = 1 MHz.2:This parameter is periodically sampled and not 100% tested.3:This application is not tested but guaranteed by characterization. For endurance estimates in a specific application, please consult the Total Endurance Model which may be obtained on Microchip’s BBS or website.元器件交易网93LC46A/B2.0PIN DESCRIPTION2.1Chip Select (CS)A high level selects the device; a low level deselects the device and forces it into standby mode. However, a pro-gramming cycle which is already in progress will be completed, regardless of the Chip Select (CS) input signal. If CS is brought low during a program cycle, the device will go into standby mode as soon as the pro-gramming cycle is completed.CS must be low for 250 ns minimum (T CSL) between consecutive instructions. If CS is low, the internal con-trol logic is held in a RESET status.2.2Serial Clock (CLK)The Serial Clock is used to synchronize the communi-cation between a master device and the 93LC46AX/ BX. Opcodes, address, and data bits are clocked in on the positive edge of CLK. Data bits are also clocked out on the positive edge of CLK.CLK can be stopped anywhere in the transmission sequence (at high or low level) and can be continued anytime with respect to clock high time (T CKH) and clock low time (T CKL). This gives the controlling master freedom in preparing opcode, address, and data.CLK is a “Don't Care” if CS is low (device deselected). If CS is high, but the START condition has not been detected, any number of clock cycles can be received by the device without changing its status (i.e., waiting for a ST ART condition).CLK cycles are not required during the self-timed WRITE (i.e., auto ERASE/WRITE) cycle.After detection of a ST ART condition the specified num-ber of clock cycles (respectively low to high transitions of CLK) must be provided. These clock cycles are required to clock in all required opcode, address, and data bits before an instruction is executed (T able 2-1 and T able 2-2). CLK and DI then become don't care inputs waiting for a new ST ART condition to be detected.2.3Data In (DI)Data In (DI) is used to clock in a ST ART bit, opcode, address, and data synchronously with the CLK input.2.4Data Out (DO)Data Out (DO) is used in the READ mode to output data synchronously with the CLK input (T PD after the posi-tive edge of CLK).This pin also provides READY/BUSY status information during ERASE and WRITE cycles. READY/BUSY sta-tus information is available on the DO pin if CS is brought high after being low for minimum chip select low time (T CSL) and an ERASE or WRITE operation has been initiated.The status signal is not available on DO, if CS is held low during the entire ERASE or WRITE cycle. In this case, DO is in the HIGH-Z mode. If status is checked after the ERASE/WRITE cycle, the data line will be high to indicate the device is ready.TABLE 2-1INSTRUCTION SET FOR 93LC46AInstruction SB Opcode Address Data In Data Out Req. CLK CyclesERASE111A6A5A4A3A2A1A0—(RDY/BSY)10ERAL10010X X X X X—(RDY/BSY)10EWDS10000X X X X X—HIGH-Z10EWEN10011X X X X X—HIGH-Z10READ110A6A5A4A3A2A1A0—D7 - D018WRITE101A6A5A4A3A2A1A0D7 - D0(RDY/BSY)18WRAL10001X X X X X D7 - D0(RDY/BSY)18 TABLE 2-2INSTRUCTION SET FOR 93LC46BInstruction SB Opcode Address Data In Data Out Req. CLK CyclesERASE111A5A4A3A2A1A0—(RDY/BSY)9ERAL10010X X X X—(RDY/BSY)9EWDS10000X X X X—HIGH-Z9EWEN10011X X X X—HIGH-Z9READ110A5A4A3A2A1A0—D15 - D025WRITE101A5A4A3A2A1A0D15 - D0(RDY/BSY)25WRAL10001X X X X D15 - D0(RDY/BSY)25元器件交易网93LC46A/B3.0FUNCTIONAL DESCRIPTION Instructions, addresses, and write data are clocked into the DI pin on the rising edge of the clock (CLK). The DO pin is normally held in a HIGH-Z state except when reading data from the device, or when checking the READY/BUSY status during a programming operation. The READY/BUSY status can be verified during an ERASE/WRITE operation by polling the DO pin; DO low indicates that programming is still in progress, while DO high indicates the device is ready. The DO will enter the HIGH-Z state on the falling edge of the CS.3.1START ConditionThe ST ART bit is detected by the device if CS and DI are both high with respect to the positive edge of CLK for the first time.Before a ST ART condition is detected, CS, CLK, and DI may change in any combination (except to that of a ST ART condition), without resulting in any device oper-ation (ERASE, ERAL, EWDS, EWEN, READ, WRITE, and WRAL). As soon as CS is high, the device is no longer in the standby mode.An instruction following a START condition will only be executed if the required amount of opcodes, addresses, and data bits for any particular instruction is clocked in.After execution of an instruction (i.e., clock in or out of the last required address or data bit) CLK and DI become don't care bits until a new ST ART condition is detected.3.2Data In (DI) and Data Out (DO)It is possible to connect the Data In (DI) and Data Out (DO) pins together. However, with this configuration, if A0 is a logic-high level, it is possible for a “bus conflict”to occur during the “dummy zero” that precedes the READ operation. Under such a condition the voltage level seen at DO is undefined and will depend upon the relative impedances of DO and the signal source driv-ing A0. The higher the current sourcing capability of A0, the higher the voltage at the DO pin.3.3Data ProtectionDuring power-up, all programming modes of operation are inhibited until Vcc has reached a level greater than 2.2V. During power-down, the source data protection circuitry acts to inhibit all programming modes when Vcc has fallen below 2.2V at nominal conditions.The ERASE/WRITE Disable (EWDS) and ERASE/ WRITE Enable (EWDS) commands give additional pro-tection against accidentally programming during nor-mal operation.After power-up, the device is automatically in the EWDS mode. Therefore, an EWEN instruction must be performed before any ERASE or WRITE instruction can be executed.元器件交易网93LC46A/B3.4ERASEThe ERASE instruction forces all data bits of the spec-ified address to the logical “1” state. CS is brought low following the loading of the last address bit. This falling edge of the CS pin initiates the self-timed programming cycle.The DO pin indicates the READY/BUSY status of the device if CS is brought high after a minimum of 250 ns low (T CSL). DO at logical “0” indicates that program-ming is still in progress. DO at logical “1” indicates that the register at the specified address has been erased and the device is ready for another instruction.3.5Erase All (ERAL)The Erase All (ERAL) instruction will erase the entire memory array to the logical “1” state. The ERAL cycle is identical to the ERASE cycle, except for the different opcode. The ERAL cycle is completely self-timed and commences at the falling edge of the CS. Clocking of the CLK pin is not necessary after the device has entered the ERAL cycle.The DO pin indicates the READY/BUSY status of the device, if CS is brought high after a minimum of 250 ns low (T CSL) and before the entire ERAL cycle is com-plete.元器件交易网93LC46A/B3.6ERASE/WRITE Disable and Enable(EWDS/EWEN)The 93LC46A/B powers up in the ERASE/WRITE Dis-able (EWDS) state. All programming modes must be preceded by an ERASE/WRITE Enable (EWEN) instruction. Once the EWEN instruction is executed, programming remains enabled until an EWDS instruc-tion is executed or Vcc is removed from the device. T o protect against accidental data disturbance, the EWDS instruction can be used to disable all ERASE/WRITE functions and should follow all programming opera-tions. Execution of a READ instruction is independent of both the EWEN and EWDS instructions.3.7READThe READ instruction outputs the serial data of the addressed memory location on the DO pin. A dummy zero bit precedes the 8-bit (93LC46A) or 16-bit (93LC46B) output string. The output data bits will toggle on the rising edge of the CLK and are stable after the specified time delay (T PD). Sequential read is possible when CS is held high. The memory data will automati-cally cycle to the next register and output sequentially.FIGURE 3-6:READ TIMING CSCLKDI DO110An•••A0HIGH-Z0Dx•••D0Dx•••D0•••Dx D0元器件交易网93LC46A/B3.8WRITEThe WRITE instruction is followed by 8 bits (93LC46A) or 16 bits (93LC46B) of data which are written into the specified address. After the last data bit is put on the DI pin, the falling edge of CS initiates the self-timed auto-erase and programming cycle.The DO pin indicates the READY/BUSY status of the device, if CS is brought high after a minimum of 250 ns low (T CSL) and before the entire write cycle is complete. DO at logical “0” indicates that programming is still in progress. DO at logical “1” indicates that the register at the specified address has been written with the data specified and the device is ready for another instruc-tion.3.9Write All (WRAL)The Write All (WRAL) instruction will write the entire memory array with the data specified in the command. The WRAL cycle is completely self-timed and com-mences at the falling edge of the CS. Clocking of the CLK pin is not necessary after the device has entered the WRAL cycle. The WRAL command does include an automatic ERAL cycle for the device. Therefore, the WRAL instruction does not require an ERAL instruction but the chip must be in the EWEN status.The DO pin indicates the READY/BUSY status of the device if CS is brought high after a minimum of 250 ns low (T CSL).元器件交易网元器件交易网93LC46A/B Array NOTES:元器件交易网93LC46A/B Array NOTES:元器件交易网93LC46A/B Array NOTES:93LC46A/B93LC46A/B PRODUCT IDENTIFICATION SYSTEMSales and SupportData SheetsProducts supported by a preliminary Data Sheet may have an errata sheet describing minor operational differences and recom-mended workarounds. To determine if an errata sheet exists for a particular device, please contact one of the following:1. Y our local Microchip sales office.2. The Microchip Corporate Literature Center U.S. FAX: (602) 786-7277.3. The Microchip’s Bulletin Board, via your local CompuServe number (CompuServe membership NOT required).元器件交易网AMERICASCorporate OfficeMicrochip Technology Inc.2355 West Chandler Blvd.Chandler, AZ 85224-6199Tel: 602-786-7200 Fax: 602-786-7277 Technical Support: 602 786-7627 Web: AtlantaMicrochip T echnology Inc.500 Sugar Mill Road, Suite 200B Atlanta, GA 30350Tel: 770-640-0034 Fax: 770-640-0307 BostonMicrochip Technology Inc.5 Mount Royal AvenueMarlborough, MA 01752T el: 508-480-9990 Fax: 508-480-8575 ChicagoMicrochip Technology Inc.333 Pierce Road, Suite 180Itasca, IL 60143Tel: 630-285-0071 Fax: 630-285-0075 DallasMicrochip T echnology Inc.14651 Dallas Parkway, Suite 816 Dallas, TX 75240-8809Tel: 972-991-7177 Fax: 972-991-8588 DaytonMicrochip T echnology Inc.Two Prestige Place, Suite 150 Miamisburg, OH 45342Tel: 937-291-1654 Fax: 937-291-9175 Los AngelesMicrochip Technology Inc.18201 Von Karman, Suite 1090Irvine, CA 92612Tel: 714-263-1888 Fax: 714-263-1338 New YorkMicrochip T echnology Inc.150 Motor Parkway, Suite 416 Hauppauge, NY 11788T el: 516-273-5305 Fax: 516-273-5335 San JoseMicrochip Technology Inc.2107 North First Street, Suite 590San Jose, CA 95131T el: 408-436-7950 Fax: 408-436-7955 TorontoMicrochip Technology Inc.5925 Airport Road, Suite 200 Mississauga, Ontario L4V 1W1, Canada Tel: 905-405-6279 Fax: 905-405-6253ASIA/PACIFICHong KongMicrochip Asia PacificRM 3801B, Tower T woMetroplaza223 Hing Fong RoadKwai Fong, N.T., Hong KongTel: 852-2-401-1200 Fax: 852-2-401-3431IndiaMicrochip Technology IndiaNo. 6, Legacy, Convent RoadBangalore 560 025, IndiaT el: 91-80-229-0061 Fax: 91-80-229-0062KoreaMicrochip Technology Korea168-1, Y oungbo Bldg. 3 FloorSamsung-Dong, Kangnam-KuSeoul, KoreaTel: 82-2-554-7200 Fax: 82-2-558-5934ShanghaiMicrochip TechnologyRM 406 Shanghai Golden Bridge Bldg.2077 Y an’an Road West, Hongiao DistrictShanghai, PRC 200335T el: 86-21-6275-5700Fax: 86 21-6275-5060SingaporeMicrochip T echnology TaiwanSingapore Branch200 Middle Road#10-03 Prime CentreSingapore 188980T el: 65-334-8870 Fax: 65-334-8850Taiwan, R.O.CMicrochip Technology Taiwan10F-1C 207Tung Hua North RoadTaipei, Taiwan, ROCT el: 886 2-717-7175 Fax: 886-2-545-0139EUROPEUnited KingdomArizona Microchip Technology Ltd.Unit 6, The CourtyardMeadow Bank, Furlong RoadBourne End, Buckinghamshire SL8 5AJTel: 44-1628-851077 Fax: 44-1628-850259FranceArizona Microchip Technology SARLZone Industrielle de la Bonde2 Rue du Buisson aux Fraises91300 Massy, FranceTel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79GermanyArizona Microchip Technology GmbHGustav-Heinemann-Ring 125D-81739 Müchen, GermanyTel: 49-89-627-144 0 Fax: 49-89-627-144-44ItalyArizona Microchip Technology SRLCentro Direzionale ColleonePalazzo Taurus 1 V. Le Colleoni 120041 Agrate BrianzaMilan, ItalyTel: 39-39-6899939 Fax: 39-39-6899883JAPANMicrochip Technology Intl. Inc.Benex S-1 6F3-18-20, Shin Y okohamaKohoku-Ku, Y okohamaKanagawa 222 JapanTel: 81-4-5471- 6166 Fax: 81-4-5471-61225/8/97 Printed on recycled paper.元器件交易网。

DataSheet - EEprom 93C46

DESCRIPTION (cont’d) The M93Cx6 specified at 5V±10%, the M93Cx6-W specified at 2.5V to 5.5V and the M93Cx6-R specified at 1.8V to 5.5V. The M93Cx6 memory array organization may be divided into either bytes (x8) or words (x16) which may be selected by a signal applied on the ORG input. The M93C86/C76/C66/C56/C46/C06 is divided into either 2048/1024/512/256/128/32x8 bit bytes or 1024/512/256/128/64/16 x16 bit words respectively. These memory devices are available in both PSDIP8 and SO8 package. The M93Cx6 memory is accessed by a set of instructions which includes Read a Byte/Word, Write a Byte/Word, Erase a Byte/Word, Erase All and Write All. A Read instruction loads the address of the first byte/word to be read into an internal

S D Q C ORG VCC VSS July 1997 Chip Select Input Serial Data Input Serial Data Output Serial Clock Organisation Select Supply Voltage Ground

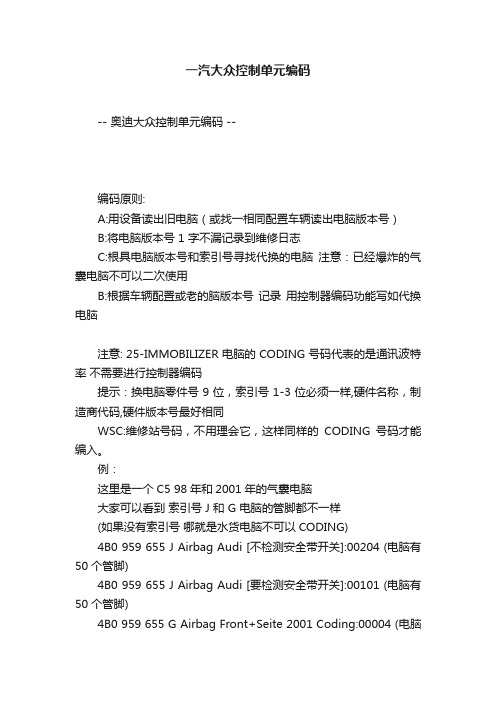

一汽大众控制单元编码

一汽大众控制单元编码-- 奥迪大众控制单元编码 --编码原则:A:用设备读出旧电脑(或找一相同配置车辆读出电脑版本号)B:将电脑版本号 1 字不漏记录到维修日志C:根具电脑版本号和索引号寻找代换的电脑注意:已经爆炸的气囊电脑不可以二次使用B:根据车辆配置或老的脑版本号记录用控制器编码功能写如代换电脑注意: 25-IMMOBILIZER 电脑的 CODING 号码代表的是通讯波特率不需要进行控制器编码提示:换电脑零件号9位,索引号1-3位必须一样,硬件名称,制造商代码,硬件版本号最好相同WSC:维修站号码,不用理会它,这样同样的CODING号码才能编入。

例:这里是一个C5 98年和2001年的气囊电脑大家可以看到索引号 J 和 G 电脑的管脚都不一样(如果没有索引号哪就是水货电脑不可以CODING)4B0 959 655 J Airbag Audi [不检测安全带开关]:00204 (电脑有50个管脚)4B0 959 655 J Airbag Audi [要检测安全带开关]:00101 (电脑有50个管脚)4B0 959 655 G Airbag Front+Seite 2001 Coding:00004 (电脑有84个管脚)4B0 959 655 G Airbag Front+Seite 2001 Coding:00104 (电脑有84个管脚)4B0 959 655 G Airbag Front+Seite 2001 Coding:00106 (电脑有84个管脚)4B0 959 655 G Airbag Front+Seite 2001 Coding:00204 (电脑有84个管脚)4B0 959 655 G Airbag Front+Seite 2001 Coding:00206 (电脑有84个管脚)*************************************************************** *****************************上海大众 B51CD 909 601 AOL AIRBAG VW51 123646Q0 909 601 AXG AIRBAG VW5:0004 225993A0 907 389 ABS ITTAE 20 [上海大众] 045053A0 907 389 ABS ITTAE 20 [一汽大众] 036043A0 907 389 ABS ITTAE 20 [奇瑞ABS+] 036046Q0 909 601 E AIRBAG 123436Q0 907 397 E ABS 00010974B0 959 655 G Airbag Fron+Seite 2001 000044B0 959 655 G Airbag Fron+Seite 2001 00104************************************************************** 发动机电脑电脑内进汽负压传感器AUDI part no. 4A0 907 473 D Maade in GermanyII 04.05.1995MOTORSTEUERGERAT MMPFI V6-ZYLHELLA...Part NO.5DA 007 193-024A0 953 234 IMMO AUZ9Z0 S3 32 95 28 D76 000004D0 907 379 D ABS BOSCH 5 7402 00024--8A0 959 655 B Airbag V AUDI D00 007664A0 820 043 H Klima-Vollautomat D05 000604A1 919 033 HD C4-kombiinstrument d20 1995-04 00062*************************************************************** **发动机电脑电脑内进汽负压传感器手动变速器 1994年IMMO 与众不同 ST93c46x16 在PCB背面 IMMO 数据定义4A0 953 234 IMM AUZ9Z0R6601234 D69 Coding: 00000 WSC 000004A0907473D 2,6L MPFI HS D01 CODING:000604D0907379D ABS BOSCH 5 7402 CODING:061698A0959655A AirBag IV AUDI D00 CODING:010224A0820043G Klima-Vollautomat D05 CODING:00060*************************************************************** **1G0 953 257 IMMO VWZ3Z0A1235467 10400 (用01配钥匙) 4A0 953 234 IMMO AUZ9Z0 S3 32 95 28 D76 00000 (用01配钥匙)330 953 253 IMMO VWZ9Z0W1234567 00000 (用21配钥匙) 3BD 920 820 A B5-KOMBIINSTR VDO-V26 (仪表) 05145 (用21配钥匙)3BD 920 806 B KOMBI+WEGFAHR SP VDO VOL 05125 (用21配钥匙)4609188DA C5-Kombininstr Un4 D-9280AC5 02042 (用21配钥匙)4B0 962 258 E Zentrdverrie.1 DWA D34 [中文显示仪表]04683用21配钥匙*************************************************************** ****2001 C501-01 ENGINE3B0 909 552 AD 2.4L V6/5VCODING:04552VIN:VBA24 B2130 17825 IMMAUZ720Y167561202-01 AT4B0 927 156 AL AE5 01V 2.4L 5V ROWCODING:0001317-01 仪表&IMMO4B0 962 258 E Zentrdverrie.1 DWA D34 (中文显示仪表) CODING:04683VIN:VBA24 B2130 17825 IMMAUZ720Y167561217-10-09 -Adaotoution 1270 改公里数可用17-10-04 语言选择不可用 ,可见是固定语言显示03-01 ABS/ASR3B0 614 111 ABS/ASR 5.3 FrontCODING:0003108-空调 4B0 820 043 AF A6-Klimavoll automatn D65 CODING:001602002 款 GOLF 全车电脑版本号17-仪表与IMMO1J0 920 826 A KOMBI+WEGFAHRS. BPV V09 CODING:01112 WSC:00000VIN: WVWZZ Z1JZ2 D1910 77IMMO SN: VWZ6Z 0A378 861101-发动机I06A 906 033 AF SIMOS33 1.6l 2V 00AT4083 CODING:00033 WSC:31414VIN: WVWZZ Z1JZ2 D1910 77IMMO SN: VWZ6Z 0A378 861102-自动波01M 927 733 JH AG4 Getriebe 01M 4830 CODING:00000 WSC:0000046-中控与舒适系统1C0 959 799 B 1C Komfortgerβ HL0 0003 CODING:00259 WSC:314141C1959801A 1C Tsteuer.FS KL0 00021C1959802A 1C Tsteuer.BF1C0959811A 1C Tsteuer.HL HL0 00021C0959812A 1C tsteuer.HR03-ABS系统1C0 907 379 J ABS FRONT MK60 0103 CODING:0001025 WSC:3141415-气囊系统1C0 909 605 A 27 AIRBAG VW51 01 02 CODING:12855 WSC:31414*****************************************************气囊电脑 6QO-909-605A零件号索引号控制器编码VEHICLE EQUIPMENT PART # INDEX CODE# Driver"s,Pass. A/B 1J0 909 603 AN 16718 Driver"s,Pass. A/B 6Q0 909 601 0C 12355Only Driver"s A/B 1J0 909 603AP 16720Only Driver"s A/B 6Q0 909 601 OB 12354 Dr"s,Pass.+Side A/B 1J0 909 608 AR 16722 Driver"ss+Side A/B 1J0 909 608 AS 16723C 00067J 00074Dr"s,Pass.+Side A/B+ 1J0 909 609 A 00065 Elec. Belt TensionerDr"s,Pass.+Side A/B+ 6Q0 909 605A 02 12338 Elec. Belt TensionerDr"s,Pass.+Side+Head 6Q0 909 605F 02 12338 A/B+Elec. Belt Tens.Dr,s+Side A/B+Elec. 1J0 909 609 B 00066Belt TensionerDr"s+Side A/B+Elec. 6Q0 909 605A 01 12337 Belt TensionerDr"s,Side,Head A/B+ 6Q0 909 605F X1 12337 Elec. Belt TensionerDr"s,Pass.,A/B with 6Q0 909 605A 03 12339 Kneebar,Side A/B+Elec. Belt TensionerDr"s,Pass.,A/B with 6Q0 909 605F 03 12339 Kneebar,Side+Head A/BElec. Belt Tensioner 6Q0 909 601 OM 12365 Dr"s,Pass. A/B withKneebarDr"s,Pass. A/B with 6Q0 909 605A OM 12345 Kneebar,Side A/B+Elec. Belt TensionerDr"s,Pass. A/B with 6Q0 909 605F X4 22580 Kneebar,Side+Head A/B+Elec. Belt Tensioner***************************************************** 上海大众菠萝全车电脑版本号15 6Q0909601E 07 AIRBAG VW5 0007CODING:1234317 6Q0 920 800 & ........... VDO V13CODING:0014119 6N0 909 901 14 CE CANcoding:0001409 6Q1 937 049C 00.BN -SG 1S32coding:2561201 036 906 034DM m......4MZ 4449coding:0007101 06A 906 032 JCME7.5.104686coding:0007103 6Q0 907 379 E 0103 ABS MK60coding:00010972002上海大众 B5 V6 2.8L 自动波全车电脑版本号底盘型号: 3B - B5 VW Passat可测试系统地址码: 01,02,03,08,15,17,19,36,46,55,56地址码:01 - 发动机零件号码: 3B0 907 551 CP 2.8L V6/5V G 0001Coding 号: 08051 维修站号码: 00000底盘号码: LSVCE 29F42 12345 67 IMMO SN: VWZ7Z 0A412 3456地址码:02 - 自动波零件号码: 8D0 927 156 DJ AG5 01V 2.8l5V RdW 1111Coding 号: 00113 维修站号码: 66187地址码:03 - ABS /ESP零件号码: 1J0 907 379 Q ABS/EDS 20 IE CAN 0001Coding 号: 13604 维修站号码: 00000地址码:08 - 空调系统冷气/暖气零件号码: 3B1 907 044 J CLIMATRONIC B5GP 0003Coding 号: 17000 维修站号码: 66187TDC: 00603 - Footwell/defroster Flap Positioning Motor (V85) 37-10 - Faulty - IntermittentTDC: 01271 - Positioning Motor for Temperature Flap (V68) 37-10 - Faulty - IntermittentTDC: 01272 - Positioning Motor for Central Flap (V70)37-10 - Faulty - IntermittentTDC: 01274 - Air Flow Flap Positioning Motor (V71)37-10 - Faulty - IntermittentTDC: 01341 - Control Module in Instrument Panel On Comfort CAN (J285)27-10 - Implausible Signal - Intermittent地址码:15-Airbags 气囊系统零件号码: 1C0 909 605 B XJ AIRBAG VW51 04 02 * XJ为软件索引号Coding 号: 22602 维修站号码: 66187地址码:17-仪表与IMMO零件号码: 3BD 920 806 C KOMBI+WEGFAHRSP VDO V01Coding 号: 07125 维修站号码: 11111底盘号码: LSVCE 29F42 12345 67IMMO SN: VWZ7Z 0A412 3456TDC: 01316 - ABS Control Module49-00 - 没有通讯地址码:19-网关零件号码: 6N0 909 901 Gateway K<->CAN 0001Coding 号: 00004 维修站号码: 01313 /ENGINE+AT+AIRBAG0 - IMMO2 仪表啥也不管理 /IMMO3 仪表为默认只管理发动机和自动波+1 - Automatic Transmission 自动变速器+2 - ABS Brakes 防报死系统+4 - Airbags 气囊+7 - Steering 方向助力 (所以啊上海大众菠萝的网关CODING 是00014)ABS Brakes, and Airbags, (1+2+4 = 7) = 00007.如果把这车的CODING号码改为00006 就会多出TDC:01316如果把这车的CODING号码改为00014 就会多出TDC:01316 和TDC:01309TDC: 01316 - ABS Control Module49-00 - 没有通讯TDC: 01309 - Power Steering Control Module (J500)49-00 - 没有通讯地址码:36- 司机侧座椅调节零件号码: 3B1 959 760 D Sitzverstellung 0101Coding 号: 0000000 维修站号码: 00000TDC:01008 - Note: Emergency OFF Switch is Active!000 - - - Intermittent地址码:55-射灯控制零件号码: 4B0 907 357 LEUCHTWEITEREGLER D004Coding 号: 00015 维修站号码: 66187*************************************************************** ***上海大众时代娇子ABS控制单元coding为02802,普通奇瑞的ABS为01901宝来汽车电脑器件型号01- 发动机:06A906032EQ 1.6L 5V MQ2004680CODING:00031 WSC:00000VIN:LFVBA 11JX2 30499 94 IMMO_SN:VWZ7Z 0B642 230915-安全气囊:1C0909601 2K AIRBAG VW 510006 //怪不的你在例外1贴讲K81不可编码少了2K啊!CODING:12875 WSC:1031503 -ABS电脑:1C0907379L 0101ABS FRON 7MK60CODING:0001025 WSC:00000 //注意:CODING号码为7位的是KWP2000通讯协议25-IMMOBILZER 电子防盗:Bitte Adresse 17 engeben (这句话的意思是:转到地址17诊断)1998年以后的车辆一般已经没有单独的25系统,整合到17-仪表&IMMO46-中控与适系统:1C0959799 2M Komfortgerat HLO 00001 CODING:00259 WSC: 000001C1959801A 1M TJrsteuer FS KLO 000917-组合仪表(防盗)电脑版本:1J5920806b komb1+wegfarlrsp vdo v02coding: 01102 wsc: 00000VIN:LFVBA 11JX2 30499 94 IMMO_SN:VWZ7Z 0B642 230919 - 网关: 6N0909901 Gateway k<-> can 0001coding:00006 wsc:00000AUDI A4 1.808 -空调系统4A0 820 043DCODING 000400006000061polo 波罗 1.4L MT 全车电脑版本号01-ENGINE //01-10-d 188 (含 EPC 电子油门控制)036 906 034 DM MARELLI 4MV 4837Coding: 00071 WSC 12345VIN: LSVFA49J732012842 IMMO ID:VWZ7Z0C683158503 - ABS 6Q0 907 379 L ABS FRONT MK60 0101Coding: 0001097 WSC 1234508 - 空调 6Q0 820 045 Klimaanlage X0840该空调是没有CODING 和WSC 的我去维修站多次用VAS5051+VAS5052验证过的2 Faults Found:01596 - Motor for Outside/Recirculated Air Flap (V154)30-10 - Open or Short to B+ - Intermittent01596 - Motor for Outside/Recirculated Air Flap (V154)41-10 - Blocked or No Voltage - Intermittent15 - AIRBAG 6Q0 909 601 E 07 AIRBAG VW5 0007Coding: 12343 WSC 1234517 - 仪表/IMMO 6Q0 920 800 KOMBI+WEGFAHRSP VDO V16Coding: 00141 WSC 57952LSVFA49J732012842 VWZ7Z0C683158519 - 网关 6N0 909 901 14 GATEWAY CAN 1S33Coding: 00014 WSC 1234525 - IMMOBILIZER(因为该车无电子防盗实际上这是17仪表抢答的)Controller: Bitte AdressComponent: e 17 eingeben46-J393(T23+T12C)舒适系统 6Q0 959 433 G 4W Komfortgera 0002Coding: 00064 WSC 12345 (coding 为00264 可多控制后面2个门)J386(T12d+T8h+t12e)左前门: 6Q2959802A 4W Tusteuer.FS KLO 0001J387(T8i +T6p+T12f)右前门: 6Q2959801A 4W Tusteuer.BF KLO 000156 - 收放机6QD 035 152 Radio 5GD 0001Coding: 00001 WSC 1234509 - 电源与继电器管理 6Q1 937 049 C 00 BN-SG. 1S33Coding: 25612 Code: WSC 1234544 - 转向助力 6Q0 423 156 Q LenkhilfeTRW V250Coding: 10140 Code: WSC 1234503 - ABS 6Q0 907 379 L ABS FRONT MK60 0101Coding: 0001097 WSC 12345--------------------------------------------------------------------------------桑塔纳2000时代骄子安全气囊1C0 909 601 2N AIRBAG VW51 0008CODING:12878 WSC:01234同 2003 年4月以后的捷达春天等是同一个只是CODING:01901 号码不同奇瑞的 ABS+ 也是这个东东:CODING:01901看ABS 泵标签有 330 614 111 字样C5 发动机 4D0 907 551 AH CODING 号码01 - ENGINE 发动机系统4D0 907 551 AH 2.8L V6/5V MOTR HS D04Coding: 06201 WSC 06335TDC 16825 - EVAP Emission Control Sys: Incorrect Flow宝来汽车电脑版本号01- 发动机:06A 906 032JB 1.6L 5V AT AG4 4629 CODING:00033 WSC:0000002-自动变速箱零件号码01M 927 733 KK 组件AG4 GETRIEBE 01M 4989 Coding 号00000 维修站号码0000017-组合仪表(防盗)电脑版本:1J5920806C komb1+wegfaHrsp vdo v02 coding: 01102 wsc: 0000046-舒适系统零件号码 1C0 959 799 组件1M KOMFORTGER atHLO 0002 Coding 号00259 维修站号码00000斯科达法比亚气囊电脑VAG NUMBER Index CODING=========== ===== =====1J0 909 603 AS AIRBAG 167231J0 909 603 AT AIRBAG 167242002 Jetta 1.8T 电脑版本号2002 Jetta 1.8T金德 k81/PC2000 for Windows XP 双模式01 --发动机 : 06A 906 032 HF 1.8L R4/5VT G 0004 Coding: 07550 WSC 13622VIN:3VWSE69M62M112530IMMO SN:VWZ7Z0A418528402 -- 自动波09A 927 750 T AG5 Getriebe 09A 019303 -- ABS: 1C0 907 379 K ASR FRONT MK60 0103Coding: 0018945 WSC 0002817 -- 仪表/IMMO : 1J5 920 926 AX KOMBI+WEGFAHRSP VDO V11Coding: 07204 WSC 225853VWSE69M62M112530 VWZ7Z0A418528419 -- 网关 6N0 909 901 Gateway K<->CAN 0001Coding: 00006 WSC 2258546 -- 中控与舒适系统 1C0 959 799 C 1H Komfortger醫 HLO 0003Coding: 00257 WSC 0002856 -- 收放机 3B7 035 180 Radio NP2 0055Coding: 00031 WSC 00028美规原装奥迪A6.2.8L 手动自动两用波箱电脑型号发动机电脑:4D0907551AH 2.8L V6/5V MOTRAT D02CODING:06252波箱电脑:4B09271156G AG501V 2.8L5V USA 8509CODING:00001ABS电脑 :8E0614111M ABS/EDS5.3 OUATTRO D31CODING:06169仪表电脑:4B0919930RX C5-KOMBIINSTR VDO D15CODING:07262空调电脑:4B0820043G A6-KLIMAVOLL AUTOMAT:D61CODING:00160中央控制门锁:4B0962258C CENTRALLOCK/ALARM D30CODING:15885宝来1.6L A/T发动机的CODING:00033 ABS:0001025 A/T:00000 仪表:01102 音响:00001 舒适性系统:00259 捷达:1.6l A/T发动机的CODING:04030 A/T:03604 SRS:00065 防盗:09600 捷达都市先锋发动机:04003 A/T:00000 ABS:03604一汽新A6address 01Protocol: KW1281Controller: 3B0907 551 CKComponent: 2.8L V6/5V 0002Coding: 08502Shop #: WSC 00000Address 03Protocol: KW1281Controller: 3B0 614 111Component: ABS/ASR 5.3 FRONT D00Coding: 00032Shop #: WSC 00000Skipping Address 15-AirbagsAddress 17Protocol: KW1281Controller: 4C0 920 930 BComponent: C5-KOMBIINSTR. VDO D12Coding: 00162Shop #: WSC 000002001.5 VW Passat 1.8T w/ engine code AWM.CODING:12878 WSC:01234同 2003 年4月以后的捷达春天等是同一个只是CODING:01901 号码不同奇瑞的 ABS+ 也是这个东东:CODING:01901看ABS 泵标签有 330 614 111 字样C5 发动机 4D0 907 551 AH CODING 号码01 - ENGINE 发动机系统4D0 907 551 AH 2.8L V6/5V MOTR HS D04Coding: 06201 WSC 06335TDC 16825 - EVAP Emission Control Sys: Incorrect Flow宝来汽车电脑版本号01- 发动机:06A 906 032JB 1.6L 5V AT AG4 4629CODING:00033 WSC:0000002-自动变速箱零件号码01M 927 733 KK 组件AG4 GETRIEBE 01M 4989Coding 号00000 维修站号码0000017-组合仪表(防盗)电脑版本:1J5920806C komb1+wegfaHrsp vdo v02coding: 01102 wsc: 0000046-舒适系统零件号码 1C0 959 799 组件1M KOMFORTGER atHLO 0002 Coding 号00259 维修站号码00000斯科达法比亚气囊电脑VAG NUMBER Index CODING=========== ===== =====1J0 909 603 AS AIRBAG 167231J0 909 603 AT AIRBAG 167242002 Jetta 1.8T 电脑版本号2002 Jetta 1.8T金德 k81/PC2000 for Windows XP 双模式01 --发动机 : 06A 906 032 HF 1.8L R4/5VT G 0004Coding: 07550 WSC 13622VIN:3VWSE69M62M112530IMMO SN:VWZ7Z0A418528402 -- 自动波09A 927 750 T AG5 Getriebe 09A 019303 -- ABS: 1C0 907 379 K ASR FRONT MK60 0103Coding: 0018945 WSC 0002817 -- 仪表/IMMO : 1J5 920 926 AX KOMBI+WEGFAHRSP VDO V11Coding: 07204 WSC 225853VWSE69M62M112530 VWZ7Z0A418528419 -- 网关 6N0 909 901 Gateway K<->CAN 0001Coding: 00006 WSC 2258546 -- 中控与舒适系统 1C0 959 799 C 1H Komfortger醫 HLO 0003Coding: 00257 WSC 0002856 -- 收放机 3B7 035 180 Radio NP2 0055Coding: 00031 WSC 00028美规原装奥迪A6.2.8L 手动自动两用波箱电脑型号发动机电脑:4D0907551AH 2.8L V6/5V MOTRAT D02CODING:06252波箱电脑:4B09271156G AG501V 2.8L5V USA 8509CODING:00001ABS电脑 :8E0614111M ABS/EDS5.3 OUATTRO D31CODING:06169仪表电脑:4B0919930RX C5-KOMBIINSTR VDO D15CODING:07262空调电脑:4B0820043G A6-KLIMAVOLL AUTOMAT:D61CODING:00160中央控制门锁:4B0962258C CENTRALLOCK/ALARM D30CODING:15885宝来1.6L A/T发动机的CODING:00033 ABS:0001025 A/T:00000 仪表:01102 音响:00001 舒适性系统:00259 捷达:1.6l A/T发动机的CODING:04030 A/T:03604 SRS:00065 防盗:09600 捷达都市先锋发动机:04003 A/T:00000 ABS:03604一汽新A6address 01Protocol: KW1281Controller: 3B0 907 551 CKComponent: 2.8L V6/5V 0002Coding: 08502Shop #: WSC 00000Address 03Protocol: KW1281Controller: 3B0 614 111Component: ABS/ASR 5.3 FRONT D00Coding: 00032Shop #: WSC 00000Skipping Address 15-AirbagsAddress 17Protocol: KW1281Controller: 4C0 920 930 BComponent: C5-KOMBIINSTR. VDO D12Coding: 00162Shop #: WSC 000002001.5 VW Passat 1.8T w/ engine code AWM.4B0-906-018-CL using a 2001.5 VW Passat 1.8T w/ engine code AWM.Audi DTC Table - General4B0-906-018-CL数据流 Diagnostic Trouble Code (DTC) table VW TECHNICAL LIBRARY【01-发动机】 4B0 906 018 CL 1.8L R4/5VT G 0001Coding: 16551 WSC 00008WVWPD63B61P269969 VWZ7Z0A35518632 Faults Found:17524 - Oxygen (Lambda) Sensor Heating: B1 S1: Open CircuitP1116 - 35-00 - -18034 - Powertrain Data Bus: Missing Message from TCUP1626 - 35-10 - - - IntermittentReadiness: 0110 1101【02 - 自动波】 4B0 927 156 DA AG5 01V 1.8l5VT RdW 1313 Coding: 00013 WSC 000082 Faults Found:18158 - Supply Voltage too LowP1750 - 35-10 - - - Intermittent18249 - Engine Control Module / Transmission Control Module IncompatibleP1841 - 35-00 - -【03 -ABS 】3B0 614 111 ABS/ASR 5.3 FRONT D00Coding: 00021 WSC 000281 Faults Found:18257 - Please check DTC Memory of Transmission Controller P1849 - 35-00 - -Skipping Address 15-Airbags【17 -仪表&IMMO】3B0 920 925 B KOMBI+WEGFAHRSPVDO V13Coding: 07235 WSC 00008WVWPD63B61P269969 VWZ7Z0A35518633 Faults Found:00779 - Outside Air Temp Sensor (G17)30-10 - Open or Short to B+ - Intermittent01316 - ABS Control Module49-10 - No Communications - Intermittent01315 - Transmission Control Module49-10 - No Communications - Intermittent【25 - IMMOBILIZER】Controller: Bitte Adress e 17 eingeben 请转到地址17-仪表与防盗No Faults Foundor DTCs not supported by controlleror a communication error ocurred【46 - 中控与舒适系统】1C0 959 799 C 08 Komfortger醫HLO 0001Coding: 00257 WSC 00008谁来区分不同处?奥迪A6 2.8L VIN:LFVBA24BX2300155201)3B0 907 551 BF 2.8L V6/5V G01 001CODING:04552 WSC:0000002)4B0 927 156 AJ AG5 01V 2.8L5V USA 3132CODING:00004 WSC:0000003)3B0 614 111 ABS/ASR 5.3 FRONT D00CODING:00031 WSC:0000015)4B0 959 655 G Airbag Fronttseite 2001CODING:00004 WSC:0000035)4B0 962 258 J Central Lock/Alarm D35 CODING:06731 WSC:0000045?)4B0 907 357 LEDCHTWETTEREGLER D004 CODING:00005 WSC:0000036)4B0 959 608 Sitzmamnory R1 F 000 CODING:00000 WSC:0000056)4C0 035 186 Radio D02CODING:0020766)4B0 919 283 ParkingSystem A6 Row D18 CODING:0110617)4C0 920 930 A Ch-kOMRIINSTR VDO D12 CODING:00162-------- --------08)4B0 820 043 AF A6-Klimavnllautomat D65 coding:00160奥迪A6 2.4L VIN:VBA24B013014521 ?15?? 01)3B0 907 552 AD 2.4L V6/5V G 0000 CODING:04552------------ -------------02)4B0 927 156 AL AG5 01V 2.4L5V RHW 2526 CODING:0001303)3B0 614 111 ABS/ASR 5.3 FRONT D00 CODING:0003115)4B0 959 655G Airbag Fronttseite 2000 CODING:0000435)4B0 962 258 E Zentralverrieg.DWA D34 CODING:0468345)4B0 951 178 A (?Unnenmumueberw) D04 CODING: 0000136)4B0 959 760 A Sitzmemnry D0556)4C0 035 186 Radio D02CODING:0020766)4B0 919 283 Parkingsystem A6 ROW D18 CODING:0010617)4C0 920 930 A C5-KOMHI INSTR VDO D09 CODING:00062--------- ---------08)4B0 820 043 AF A6-Klimavcllautomat D65 CIDING:00160大众奥迪1.8L奥迪 A6 1.8L VIN:VBA14B22301545501)4R0 906 018 CA 1.8L R4/5VT 0003 CODING:04502--------- -----------03)3B0 614 111 ABS/ASR 5.3 FRONT D00 CODING:0002215)4B0 959 655G Airbag Frongt+Seite 2001 CODING:0000435)4B0 962 258J Central lock/Alarm D35 CODING:0000156)4C0 035 186 RadioCODING:0020117)4C0 920 900A C5-KOMRI INSTR VDO D12 CODING:00144---------- -----------08)4B0 820 043H A6-Klimauollautomat D64 CODING:00140宝来 1.8L VIN:LFVBA21J22302392801)06A 906 032 LD 1.8L R4/5VT 0001 CODING:04530-------- ---------02)01M 927 733 LL AG4 Getribe 01M 4956 coding:0000003)1c0 907 379K ASR PRONT MK60 0103 CODING:002150515)1C0 909 601 2K Airbag VW51 0004 CODING:1287546)1C0 959 799C 18 Komfortger BF HLO 0003 CODING:0025956)3BD 035 186 Radio 5GD 0001 CODING:0040317)1J5 920 826A KO MRITWEGFAHRSP VDO V04CODING:0512208)3B1 907 044C CLIMATRONIC C 2.0.0 CODING:0110019)6N0 909 901 Gateway k<->CAN 0000 CODING:00006又一个1.8L VIN:VBA14B22301545501)06A 906 032 LF 1.8L R4/5VS MOTR 0001 CODING:04530-------- --------02)01M 927 733 KJ AG4 Getriehe 01M 4952 CODING:0000003)1C0 907 379 K ASR FRONT MK60 0103 CODING:001331315)1C0 909 601 2k Airbag VW51 0006 CODING:1287536)3R1 959 760 Sitzverstellung 0101 CODING:000000046)1C0 959 799 C 1H Komfortger gt hlw 0003 coding:002591c1 959 801a 1C1 959 802A1C0 959 811A 1C0 959 812A56)3BD 035 186 RADIO 5GD 0001 CODING:0040317)1JD 920 826 KOMRI+MEGAHRSP VDO V02 CODING:0510208)3B1 907 044C CLJMATRONIC C2.0.019)6N0 909 901 Gateway k<->CAN 0001 CODING:00006。

93C46串行EEPROM数据读写实验

93C46串行EEPROM 数据读写实验一、实验目的1.学会93C46的操作指令,掌握93C46读/写程序的编写2.掌握93C46与单片机的接口方式 二、实验说明93C46/56/66是1K/2K/4K 位的串行电可擦写的EPROM 。

93C46的1K 位EPROM ,可以按128字节排列,也可以64字节排列。

93C46芯片有8脚,当ORG 接VCC 时作64字使用。

当ORG 接地时作128字节使用。

本实验使用单片机P1口的低4位对93C46进行控制,当然也可以使用其他I/O 口。

CS 是片选端,高电平有效,CLK 是移位脉冲输入端,DI 是数据输入端,D0是数据位输出端。

ORG 接5V ,93C46作64个字使用。

如图:93C46指令表 本实验提供93C46的读写操作软件,有5条主要的命令:READ 、WRITE 、WRAL 、ERASE 和ERAL 。

其中EWEN (写允许)和EWDS (写禁止)操作命令已经包含在写入命令和擦除命令当中了。

程序中寄存器R7用来指定93C46的地址,R6、R5分别用来存放待操作数据的高低字节。

对主程序操作只要在调用子程序之前把相应的内容写进R7、R6、R5中就可以了。

三、实验内容及步骤本实验需要用到单片机最小应用系统CPU 模块(F1区)、串行EEPROM 模块(E1区)。

1.用单片机最小应用系统和93C46串行接口模块,用导线连接P1.0到CS ,P1.1到CLK ,P1.2到DIN ,P1.3到D0UT ,ORG 与+5V 电源相接。

2.用串行数据通信线连接计算机与仿真器,把仿真器插到模块的锁紧插座中,请注意仿真器的方向:缺口朝上。