基于Libero SoC v11.4开发环境的中断产生器设计与仿真

嵌入式中断按键实验报告

嵌入式中断按键实验报告本实验的目的是学习如何在嵌入式系统中使用中断来处理按键输入。

通过该实验,我们可以掌握如何配置和使用中断,以及如何编写中断服务程序来处理按键输入。

实验材料:1. 嵌入式开发板2. 按键模块3. 电源适配器实验步骤:1. 将按键模块连接到嵌入式开发板的GPIO引脚上,确保连接正确。

2. 打开开发板的开关,给开发板供电。

3. 在开发板上配置GPIO引脚作为中断输入,并使能中断。

4. 编写中断服务程序来处理按键输入。

当按键被按下时,中断服务程序将被调用,并执行相应的操作。

5. 在主程序中初始化中断服务程序,并进入一个无限循环。

在该循环中,可以进行其他的操作,并等待按键中断的发生。

实验结果:在实验中,我们成功地配置并使用了中断来处理按键输入。

当按键被按下时,中断服务程序被调用,并执行了相应的操作。

讨论与分析:通过该实验,我们学习到了中断的基本原理和使用方法。

中断是一种非常重要的机制,可以使嵌入式系统更高效地响应外部事件。

在实际的嵌入式应用中,按键输入是非常常见的操作,使用中断可以很好地处理按键输入,提高系统的响应速度和可靠性。

然而,中断也存在一些问题。

首先,中断处理需要一定的时间,在高速的系统中,中断的处理时间可能会影响到系统的性能。

另外,当系统存在多个中断源时,中断处理的优先级和调度也需要仔细设计,以确保系统的正常运行。

总结:通过本实验,我们成功地学习了嵌入式系统中使用中断处理按键输入的方法。

中断是一种重要的机制,可以使系统更高效地响应外部事件。

通过合理地设计和使用中断,可以提高系统的性能和可靠性。

在实际的嵌入式应用中,我们应该根据具体的需求和系统条件来选择最合适的中断处理方法,并进行适当的优化和调试。

Libero开发流程基础_063009

Actel FPGA Libero开发流程(基础)关于Actel成立于1985年非易失性FPGA领导企业反熔丝和闪存技术2007年收益达到1.97亿美元拥有1.45亿现金和投资无债务连续72季实现预计(pro-forma)利润率 拥有550多名员工全球开发和支持中心在世界各地拥有3500多家客户100%符合RoHS标准要求需要的软件Actel 提供全套FPGA 开发软件Libero,包含Viewdraw图形输入Verilog HDL /VHDL 输入Synplify/Synplify pro 综合Designer 布局布线ModelSim AE 仿真全套软件免费下载软件License 免费使用期限一年,满一年Actel 自动发送新的License 到你的注册邮箱需要的软件(续)to: 需要的软件(续)点击客户入门,new User需要的软件(续) 给出你的信箱--Submit需要的软件(续) 完成该表格--Submit需要的软件(续)这样你就可以进行免费License 申请需要的软件(续) 申请免费License需要的软件(续) 选择一年免费Gold 。

需要的软件(续)需要的软件(续)给出你的硬盘ID ---Submit到C: dir..C868-6CBA…几分钟后你会收到license需要的软件(续)需要的软件(续)按照邮件内容设置License 即可 下载软件,顺序点击指示位置需要的软件(续)下载两个文件,安装LiberoIDE , 选择Gold,…, 再安装SP2需要的软件(续)需要的软件(续) 安装后的计算机桌面需要的软件(续)启动Libero8.5—help—license detail需要的软件(续)若license 设置不正确,软件会提示。

至此,软件已具备。

Actel FPGA 结构简介Actel的技的术优势出色的真正基于闪存的技术全面的低功耗特性较任何其它解决方案更为安全卓越的可靠性上电即用高集成度实现更低的总体成本可重编程和易失性Actel FPGAActel FPGA 技术:Flash: Flash 开关Antifuse: 反熔丝 目前产品系列FusionIGLOO\e\plusProASIC3\EProASIC PLUSAxceleratorA54SXAeXA54SXFPGA ChipRAM/FIFOCharge Pumps Pro I/OVersaTileFROM NVM JTAG ISPISP AES DecryptionPLL/CCC VersaNets设计Libero开发流程(基础)Libero Demo 设计该设计包含下列模块/单元: •1 PLL锁相环•2 两个计数器count1,count2 •1 个或门产生异步复位 •Clock 和Reset 输入•3 LED 驱动输出Libero开发流程(基础)-创建新项目-创建Count1/PLL 模块-创建Count2模块-创建顶层模块-功能仿真-使用Synplify综合-布局布线-编程设计框图Step 1 –创建新项目Libero_demo 选择Project—New Project创建新项目Libero_demo(续)键入项目名,项目位置,选择使用的语言,所有设计存储于所选位置,以项目名字为目录的子目录下,--选择下一步创建新项目Libero_demo(续)选择系列,门数和封装,并选择完成,得到右边创建锁相环PLL 分频或倍频选择右边Catalog—clock & management—PLL static-双击鼠标右健,如下图,选择相应项创建锁相环PLL 分频或倍频创建锁相环PLL 分频或倍频红色下划线数字是你真正得到的频率和相位,我们得到0.75Mhz 的时钟,选择产生,得到如下,输入pll1,--OK创建锁相环PLL 分频或倍频可以看到已产生pll1 和使用的资源报告产生计数器count1如同锁相环产生分频,选择Catalog—Basic blocks—counter—双击鼠标右健接着产生计数器如图选择实现方式,宽度,清零等,最后产生接着产生计数器可以看到有两个模块产生Count2 的产生下面我们通过HDL 编辑器产生第二个计数器,点击HDL Editer, 如下图Count2 的产生我们给文件名count2, 注意文件名和模块名可以不一致,一个文件可以包含多个模块Count2 的产生在文本编辑器里完成如图输入,击鼠标右健给予语法检查顶层模块top到目前,我们已建立了两个计数器,一个PLL 分频模块,我们需要在顶层用这些建立设计用建立计数器count2同样的方法建立top文件内容如下:module top(input CLOCK, input RESET,output[2:0] q);wire tb_clka;wire tb_aclr;wire tb_lock,tb_gla;wire [17:0]tb_q;assign tb_aclr=(~tb_lock)| RESET;/*********** pll1, counter1, counter2 instantiations *********/pll1 p1(.POWERDOWN(1),.CLKA(CLOCK),.LOCK(tb_lock),.GLA(tb_gla));count1 c1(.Aclr(tb_aclr),.Clock(tb_gla),.Q(tb_q));count2 c2(.aclr(tb_aclr),.clock(tb_q[17]),.Q(q));endmodule问题:我怎么知道PLL1和count1 模块的信号名?答案:打开相应生成的HDL 文件,Copy 模块端口即可顶层模块Libero并不知道顶层是那个模块,你需要如下设置仿真设计需要输入,这些输入在testbench模块里生成。

美高森美发布LiberoSoCv11.8软件

性能传感器技 术的最新典 范 , 可为物 联 网( 1 o T) 用 途 提 供

高 质 量 的数 据 , 支 持 从 网络 边 缘 进 行 智 能检 测 。 模 拟 输 出 ADXI 3 5 6和数 字输 出 ADXL 3 5 7这 两 款 三

胳

A DI ME M S加 速 度 计 开 启

省去混频器 , 通 过 内部 时钟 分 频 器 和 可 选 RF时 钟 输 出 简 化 系 统 设 计 。 同期 推 出 的 2 8纳 米 数 模 转 换 器 ( D/ A 转 换

器) AD9 1 7 2是 与 其 对应 的 RF DAC。

轴加速度计提供可选 测量范 围 : ±l O g 、 ±2 0 g和 ± 4 0 g , 灵

活度更 高 ; 噪 声 密度 为 8 0 g / r o o t Hz , 处 于 业 界 领 先 水 平, 在温度范 围内的 O g失 调 漂 移 保 证 上 限 为 0 . 7 5 mg / C, 只需 极 少量 的校 准 工作 即 可 实 现 精 密测 量 。此 外 , 产 品 采 用密封封装 , 可 以确 保 最 终 产 品 出 厂后 重 复性 与稳 定 性 始

无线 状 态 监控 新 时代

ADI 公 司宣布 , 广受 用 户欢 迎 的 低 噪 声 、 低漂移 、 低 功 耗 三轴 MEMS加 速 度 计 系 列 新 增 ADXL 3 5 6和 ADXL 3 5 7 两 款 器 件 。新 款 加 速 度 计 可实 现 高频 低 噪声 性 能 , 提 供 高 分辨率振动测量 , 可 在 状 态 监 控 应 用 中尽 早 检 测 出机 器 故 障 。ADXI 3 5 6和 ADXI 3 5 7不 仅 性 能 出 色 , 功 耗也极 低 , 因而 是 无 线 传 感 器 网络 的理 想 之 选 。此 外 , 这 两 款 加 速 度 计 还 可 在 高 冲击 和 高 振 动 的 环 境 下 提 供 精 确 可 靠 的倾 斜 测量 , 不 会 造 成 传 感 器 饱 和 。对 于 重 型 设 备 或 无 人 驾 驶 飞

美高森美最新发布 FPGA 可编程工具 Libero系统级芯片(SoC)软件

美高森美最新发布FPGA 可编程工具Libero系统

级芯片(SoC)软件

致力于在功耗、安全、可靠性和性能方面提供差异化半导体技术方案的领先供应商美高森美公司发布Libero系统级芯片(SoC)软件的v11.8最新版本。

这是一款综合性可编程逻辑器件(FPGA)设计工具,具有混合语言仿真等重要性能改进,还有同级最佳调试功能,以及一个全新网表视图。

除此以外,美高森美还提供免费的License,让用户评估美高森美基于Flash的FPGA和SoC FPGA器件。

美高森美Libero SoC设计工具包的内容包括Mentor Graphics ModelSim Simulator,可以逐行验证硬件描述语言(HDL)代码。

可以在任何级别进行仿真:行为级(预综合)、结构级(后综合),以及反标的动态仿真。

易于使用的图形用户界面可让用户快速识别和调试问题。

Libero SoC v11.8现在还包括ModelSim Microsemi Pro,可让用户在混合语言环境下进行仿真,而且,相比以前的版本可以提升20%的仿真时间。

高森美公司软件工程副总裁Jim Davis说道:新版本Libero SoC v11.8具有显着的改进,其中集成的ModelSim ME Pro可以针对VHSIC硬件描述语言(VHDL)、Verilog和SystemVerilog提供混合语言的仿真支持,使得客户能够瞄准各式各样的IP设计,而且毋须担心混合多种语言会出现问题。

新版本还包括最新的SmartDebug增强功能,比如美高森美FPGA独有的FPGA硬件断点(FHB)功能。

FHB功能可让用户在设计中设置断点,并按照时钟周期。

基于Libero SoC v11.4开发环境的中断产生器设计与仿真

基于Libero SoC v11.4开发环境的中断产生器设计与仿真作者:黄显高黄伟王超来源:《电子技术与软件工程》2015年第02期本文利用2014年7月21日发布的Libero SoC V11.4最新版本的开发工具来创建一个中断产生器的设计。

通过配置一个SmartFusion的微控制子系统、在微控制子系统中配置计时器,生成一个中断产生器的设计。

最后执行综合仿真验证了中断产生器设计的正确性。

【关键词】Libero 中断产生器合成仿真随着单芯片容量增大、体积减小,芯片的功能也逐步增加,因此芯片的开发环境工具Libero版本也要逐步升级。

Actel公司2014年7月21日发布了新的Libero SoC V11.4版本[1]后,从Actel公司网站上下载的中断产生器实例工程不能在Libero SoC V11.4版本上运行,本文在新的Libero SoC V11.4版本上一步一步地修改演示了该中断产生器实例设计和仿真的全过程。

1 中断产生器的框图描述中断产生器是有一个嵌入式微控制子系统(MSS)模块和两个定时器模块组成。

两个定时器Timer1和Timer2是内部中断源,其定时不同,由同一10MHz的时钟源控制。

外部中断由外部的Switch信号控制。

Timer1连接到MSS的FABINT端,而Timer2连接到MSS的GPIO_0端。

无论哪一个中断源(Timer1,Timer2或Switch),处理器将执行相应的中断服务程序,并且中断源的信息在超级终端器打印出来。

2 中断产生器的设计点击桌面上双击Libero SoC V11.4快捷键,来建立一个新的项目。

然后配置一个SmartFusion的微控制子系统。

双击Interrupt_MSS_GPIO_MSS_0,打开SmartDesign MSS配置器,对MSS的外设进行配置。

禁用如下外设有External Memory Controller、ACE、MAC、UART_1、SPI_0、SPI_1、I2C_0、 I2C_1、Fabric Interface、WATCHDOG。

Libero_SoC集成开发环境使用教程

© 2013 Microsemi Corporation.

Power Matters

5

Libero SoC 概述2

Libero SoC 概览

Libero SoC 设计流程

Libero SoC 工程样例 Libero SoC License 管理

© 2013 Microsemi Corporation.

Power Matters

14

Libero SoC 设计流程

Create design有3种方法创建你的设计: 1、system builder. 2、smart design . 3、verilog 或 VHDL

• • • • • •

指定要求的最小时钟周期. 设置输入输出端口时序信息. 定义指定路径的最大延迟. False路径分析. 多周期路径分析. 指定端口的外部附载.

© 2013 Microsemi Corporation.

Power Matters

28

Implement Design : Synthesize

如果你想使用系统默认的设置进行综合, 只需要双击就可以了,如果你要自己定 制相应的设置,则右键选择open interactively, 打开Synplify综合工具。

选择导入文件,可以将时序约束文件导入近来,用于指导综合.

可以手动添加源文件到关联文件框中,也可以由系统自动添加!

© 2013 Microsemi Corporation.

Power Matters

基于SoC的非对称数字系统算法设计与实现

基于SoC的非对称数字系统算法设计与实现姜智;肖昊【期刊名称】《合肥工业大学学报(自然科学版)》【年(卷),期】2024(47)5【摘要】文章提出一种在片上系统(System on Chip,SoC)实现高吞吐率的有限状态熵编码(finite state entropy,FSE)算法。

通过压缩率、速度、资源消耗、功耗4个方面对所提出的编码器和解码器与典型的硬件哈夫曼编码(Huffman coding,HC)进行性能比较,结果表明,所提出的硬件FSE编码器和解码器具有显著优势。

硬件FSE(hFSE)架构实现在SoC的处理系统和可编程逻辑块(programmable logic,PL)上,通过高级可扩展接口(Advanced eXtensible Interface 4,AXI4)总线连接SoC 的处理系统和可编程逻辑块。

算法测试显示,FSE算法在非均匀数据分布和大数据量情况下,具有更好的压缩率。

该文设计的编码器和解码器已在可编程逻辑块上实现,其中包括1个可配置的缓冲模块,将比特流作为单字节或双字节配置输出到8 bit 位宽4096深度或16 bit位宽2048深度的块随机访问存储器(block random access memory,BRAM)中。

所提出的FSE硬件架构为实时压缩应用提供了高吞吐率、低功耗和低资源消耗的硬件实现。

【总页数】6页(P655-659)【作者】姜智;肖昊【作者单位】合肥工业大学微电子学院【正文语种】中文【中图分类】TN762;TN764【相关文献】1.基于IEEE 1500的数字SOC测试系统的设计与实现2.基于片上系统SoC的孤立词语音识别算法设计3.OMA DRM 2数字版权保护终端系统的SoC设计方案及其VLSI实现4.无线通信系统数字变频算法设计与实现因版权原因,仅展示原文概要,查看原文内容请购买。

NIOSII SOPC实例1

一.关于SOPC1)SOPC英文全名为:System-On-a-Programmable-Chip,即可编程片上系统。

SOPC 用可编程逻辑技术把整个系统放到一块硅片上,来用于嵌入式系统研究和电子信息处理。

SOPC是一种特殊的嵌入式系统,它是片上系统(System-On-a -Chip,SOC),即由单个芯片完成整个系统的主要逻辑功能但它不是简单的SOC,它也是可编程系统,具有灵活的设计方式,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

SOPC设计包括以32位NIOSII软核处理器为核心的嵌入式系统的硬件配置、硬件设计、硬件仿真、软件设计以及软件调试等。

SOPC系统设计的基本软件工具有:1)QuartusII:用于完成NIOSII系统的综合、硬件优化、适配、编程下载以及硬件系统调试等;2)SOPC Builder:Altera NiosII嵌入式处理器开发软件包,用于实现NiosII 系统的配置、生成,内嵌于QuartusII软件中;3)ModelSim: 用于对SOPC生成的NiosII系统的HDL描述进行系统的功能仿真;4)NiosII IDE:用于进行软件的开发、调试,以及向目标开发板进行Flash下载;二.关于NIOSII处理器NIOSII 是一个可配置的软核处理器。

“可配置”的意思是设计者可以根据性能和成本的要求来增加或删减处理器的功能。

ALTERA公司并不销售NIOSII处理器芯片,而是销售空的FPGA,并提供NIOSII 系统相应的IP核来组成NIOSII系统,然后将这个系统下载到FPGA中实现。

1)关于AVALONAvalon总线是SOPC硬件系统的重要组成部分,Avalon总线规范是为了开发SOPC 环境下外设而设计的。

图1-1 一个SOPC的示例二. SOPC简单实例:软核控制LCD液晶字母显示器1.系统构成规划1)系统功能:在character LCD上显示”Hello LCD from NiosII!”2)本系统中需要的外围器件:(1)L CD:输出显示(2)S RAM存储器:程序运行时将其导入SRAM3)SOPC中建立系统需要添加的模块包括:(1)N ios II 32bit CPU(2)L CD display(3)外部RAM总线(4)外部RAM接口(5)J TAG UART Interface(6)定时器2.硬件系统的建立1)首先打开Quartus II 建立工程文件:将工程文件命名为hello_lcd,顶层文件与工程文件同名。

Libero开发流程基础_063009

Actel FPGA Libero开发流程(基础)关于Actel成立于1985年非易失性FPGA领导企业反熔丝和闪存技术2007年收益达到1.97亿美元拥有1.45亿现金和投资无债务连续72季实现预计(pro-forma)利润率 拥有550多名员工全球开发和支持中心在世界各地拥有3500多家客户100%符合RoHS标准要求需要的软件Actel 提供全套FPGA 开发软件Libero,包含Viewdraw图形输入Verilog HDL /VHDL 输入Synplify/Synplify pro 综合Designer 布局布线ModelSim AE 仿真全套软件免费下载软件License 免费使用期限一年,满一年Actel 自动发送新的License 到你的注册邮箱需要的软件(续)to: 需要的软件(续)点击客户入门,new User需要的软件(续) 给出你的信箱--Submit需要的软件(续) 完成该表格--Submit需要的软件(续)这样你就可以进行免费License 申请需要的软件(续) 申请免费License需要的软件(续) 选择一年免费Gold 。

需要的软件(续)需要的软件(续)给出你的硬盘ID ---Submit到C: dir..C868-6CBA…几分钟后你会收到license需要的软件(续)需要的软件(续)按照邮件内容设置License 即可 下载软件,顺序点击指示位置需要的软件(续)下载两个文件,安装LiberoIDE , 选择Gold,…, 再安装SP2需要的软件(续)需要的软件(续) 安装后的计算机桌面需要的软件(续)启动Libero8.5—help—license detail需要的软件(续)若license 设置不正确,软件会提示。

至此,软件已具备。

Actel FPGA 结构简介Actel的技的术优势出色的真正基于闪存的技术全面的低功耗特性较任何其它解决方案更为安全卓越的可靠性上电即用高集成度实现更低的总体成本可重编程和易失性Actel FPGAActel FPGA 技术:Flash: Flash 开关Antifuse: 反熔丝 目前产品系列FusionIGLOO\e\plusProASIC3\EProASIC PLUSAxceleratorA54SXAeXA54SXFPGA ChipRAM/FIFOCharge Pumps Pro I/OVersaTileFROM NVM JTAG ISPISP AES DecryptionPLL/CCC VersaNets设计Libero开发流程(基础)Libero Demo 设计该设计包含下列模块/单元: •1 PLL锁相环•2 两个计数器count1,count2 •1 个或门产生异步复位 •Clock 和Reset 输入•3 LED 驱动输出Libero开发流程(基础)-创建新项目-创建Count1/PLL 模块-创建Count2模块-创建顶层模块-功能仿真-使用Synplify综合-布局布线-编程设计框图Step 1 –创建新项目Libero_demo 选择Project—New Project创建新项目Libero_demo(续)键入项目名,项目位置,选择使用的语言,所有设计存储于所选位置,以项目名字为目录的子目录下,--选择下一步创建新项目Libero_demo(续)选择系列,门数和封装,并选择完成,得到右边创建锁相环PLL 分频或倍频选择右边Catalog—clock & management—PLL static-双击鼠标右健,如下图,选择相应项创建锁相环PLL 分频或倍频创建锁相环PLL 分频或倍频红色下划线数字是你真正得到的频率和相位,我们得到0.75Mhz 的时钟,选择产生,得到如下,输入pll1,--OK创建锁相环PLL 分频或倍频可以看到已产生pll1 和使用的资源报告产生计数器count1如同锁相环产生分频,选择Catalog—Basic blocks—counter—双击鼠标右健接着产生计数器如图选择实现方式,宽度,清零等,最后产生接着产生计数器可以看到有两个模块产生Count2 的产生下面我们通过HDL 编辑器产生第二个计数器,点击HDL Editer, 如下图Count2 的产生我们给文件名count2, 注意文件名和模块名可以不一致,一个文件可以包含多个模块Count2 的产生在文本编辑器里完成如图输入,击鼠标右健给予语法检查顶层模块top到目前,我们已建立了两个计数器,一个PLL 分频模块,我们需要在顶层用这些建立设计用建立计数器count2同样的方法建立top文件内容如下:module top(input CLOCK, input RESET,output[2:0] q);wire tb_clka;wire tb_aclr;wire tb_lock,tb_gla;wire [17:0]tb_q;assign tb_aclr=(~tb_lock)| RESET;/*********** pll1, counter1, counter2 instantiations *********/pll1 p1(.POWERDOWN(1),.CLKA(CLOCK),.LOCK(tb_lock),.GLA(tb_gla));count1 c1(.Aclr(tb_aclr),.Clock(tb_gla),.Q(tb_q));count2 c2(.aclr(tb_aclr),.clock(tb_q[17]),.Q(q));endmodule问题:我怎么知道PLL1和count1 模块的信号名?答案:打开相应生成的HDL 文件,Copy 模块端口即可顶层模块Libero并不知道顶层是那个模块,你需要如下设置仿真设计需要输入,这些输入在testbench模块里生成。

中断过程的模拟与仿真

电子技术• Electronic Technology94 •电子技术与软件工程 Electronic Technology & Software Engineering【关键词】中断请求 中断响应 中断类型码 中断服务程序1 实验内容与任务因CPU 响应中断是瞬间完成的,在学习中断响应的课程中,同学们无法掌握CPU 响应中断的全过程。

为此,本文设计了一套中断中断过程的模拟与仿真文/张文远1 宋苏阳2 茹国宝1过程的实验电路。

具体内容和要求如下:(1)利用8259A 中断控制器和8255A 并行口,结合实验装置,设计一个模拟中断申请和响应过程的实验电路;(2)设计者应分析如何确定中断的触发方式?如何模拟外围申请和CPU 响应中断的整个过程?如何模拟CPU 获取中断类型码和中断向量的?如何模拟CPU 执行中断服务程序?为什么要这样设计?(3)如何完成对82设计者应分析中断控制器和8255A 并行口的初始化操作?分析其原因;(4)实验分三个层次:1)、8259A 中断控制器单片方式的工作原理与时序;2)、8259A 中断控制器级联方式主片、从片的工作原理与时序;3)、创新实验,设计一个实时时钟。

设计要求:① 采用8253A 对系统提供的标准时钟1MHz 进行分频,得到10Hz 时钟信号,作为中断请求信号,通过ISA 总线的IR7插孔向主机发出中断请求 ② 编写程序实现实时时钟显示。

2 实验原理及方案2.1 实验的基本原理8259A 在微机系统中用于管理外部多个中断源。

单片8259A 可以管理8个中断请求,级联方式可以扩展8片8259A ,最多可以管理64个中断源;8259A 采用向量中断方式,能够根据不同的中断请求向CPU 提供相应的中断类型码;8259A 具有优先权裁决和中断嵌套管理功能。

2.2 实现方案CPU 响应中断是瞬间完成的,为了了解CPU 响应中断的过程,拟采用手工模拟的方法,2.2.5 烟雾模块主要是作为公交车内的安全监测预警的装置,公交车在行驶途中监测到烟雾时说明有乘客吸烟或者车辆发生故障着火,驾驶员应该及时处理。

soc芯片的中断处理流程

soc芯片的中断处理流程下载温馨提示:该文档是我店铺精心编制而成,希望大家下载以后,能够帮助大家解决实际的问题。

文档下载后可定制随意修改,请根据实际需要进行相应的调整和使用,谢谢!并且,本店铺为大家提供各种各样类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,如想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by theeditor. I hope that after you download them,they can help yousolve practical problems. The document can be customized andmodified after downloading,please adjust and use it according toactual needs, thank you!In addition, our shop provides you with various types ofpractical materials,such as educational essays, diaryappreciation,sentence excerpts,ancient poems,classic articles,topic composition,work summary,word parsing,copy excerpts,other materials and so on,want to know different data formats andwriting methods,please pay attention!SOC 芯片的中断处理流程一般包括以下几个步骤:1. 中断触发外部设备或事件产生中断请求,发送给 SOC 芯片。

arm soc开发流程

ARM SOC开发流程是一个复杂的过程,涉及到多个阶段。

首先,使用Verilog对SOC 进行描述。

然后,利用Vivado等工具进行编译、综合和实现,以完成硬件层面的SOC功能实现。

此外,还需要将编写的C或汇编代码转换为机器码,并在仿真过程中将此机器码作为Verilog描述的RAM的初始化内容,以便进行仿真。

接下来是软件开发阶段,这包括U-BOOT编译、Linux内核编译、安装QT库、配置内核、驱动模块编译、Preloader的生成、DTB文件生成、DTS转换为DTB文件命令、修改FLASH分区、Jfss2文件系统镜像生成、启动代码与内核烧写以及Linux Demo测试等步骤。

这一阶段的目标是在芯片上运行一个可以稳定工作的系统。

最后,我们需要考虑到一些实际操作问题。

例如,一段C代码要在SOC上运行起来,除了需要PC机上的编译流程外,还需要考虑到实际硬件环境的因素。

例如,芯片需要有电源、FLASH存储器来存储程序、晶振提供时钟等。

同时,也需要有一定的输出信息的方式,如UART,这样我们才能知道程序是否正常运行。

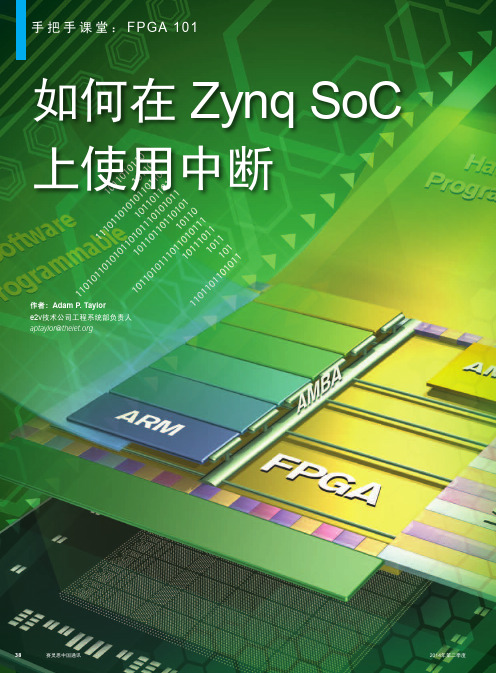

如何在Zynq SoC 上使用“中断”

端口

DMA 通道

12 13 14 15 8 9 10 11 4 56 7 0 12 3

配置

AES/ SHA

IRQ 高性能

AXI 32b/64b 从系统端口

处理系统 (PS)

XADC

图1 – 红圈显示的是通用中断控制器。

可编程逻辑 (PL)

使用通用中断控制器(GIC)来处理中断。GIC 可处理源 自以下方面的中断 :

printf(“****button pressed****\n\r”); toggle = !toggle;

XGpioPs_WritePin(Gpioint, ledpin, toggle); for( delay = 0; delay < LED_DELAY; delay++)

无论中断的来源在何处,都可将中 断的类别归为可屏蔽和不可屏蔽两种。 您可通过在中断掩码寄存器中设置相应 的位来安全地忽略可屏蔽中断。但不能 忽略不可屏蔽中断,因为这类中断通常 用于定时器和看门狗监控器。

中断的触发既可以是边缘触发也 可以是水平触发。我们将在后面部分看 到,赛灵思 Zynq®-7000 All Programmable SoC 支持中断的这两种配置方式。

2014年第二季度

在嵌入式处理中,中断表示暂时 停止处理器的当前活动。处理 器会保存当前的状态并执行中 断服务例程,以便对引起中断的原因进 行寻址。中断可能来自下列三个地方之 一:

• 硬件 – 直接连接处理器的电子信号 • 软件 – 处理器加载的软件说明 • 异常情况 – 发生错误或异常事件时

处理器出现的异常情况

//connect to the hardware Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_ INT,(Xil_ExceptionHandler)XScuGic_InterruptHandler,

广工基于Libero的数字逻辑设计仿真及验证实验实验报告(6)

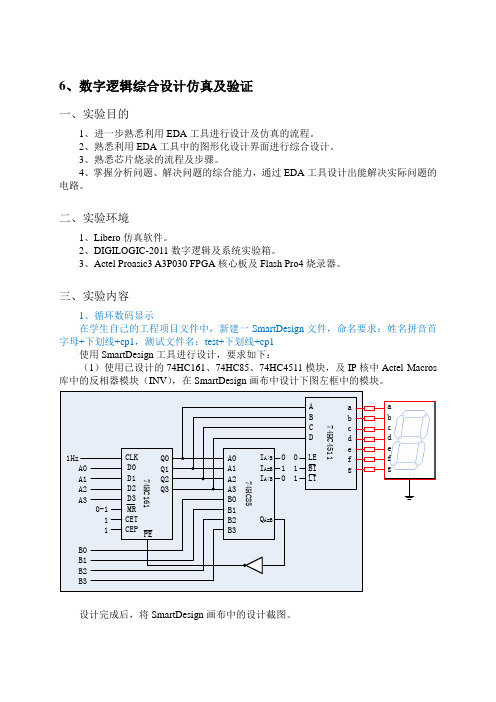

6、数字逻辑综合设计仿真及验证一、实验目的1、进一步熟悉利用EDA工具进行设计及仿真的流程。

2、熟悉利用EDA工具中的图形化设计界面进行综合设计。

3、熟悉芯片烧录的流程及步骤。

4、掌握分析问题、解决问题的综合能力,通过EDA工具设计出能解决实际问题的电路。

二、实验环境1、Libero仿真软件。

2、DIGILOGIC-2011数字逻辑及系统实验箱。

3、Actel Proasic3 A3P030 FPGA核心板及Flash Pro4烧录器。

三、实验内容1、循环数码显示在学生自己的工程项目文件中,新建一SmartDesign文件,命名要求:姓名拼音首字母+下划线+cp1,测试文件名:test+下划线+cp1使用SmartDesign工具进行设计,要求如下:(1)使用已设计的74HC161、74HC85、74HC4511模块,及IP核中Actel Macros 库中的反相器模块(INV),在SmartDesign画布中设计下图左框中的模块。

abcdefg 设计完成后,将SmartDesign画布中的设计截图。

(截图)(2)设计相应的测试平台。

测试平台中的数据要求所输入的A3A2A1A0及B3B2B1B0分别为学生学号末四位的最小数及最大数所对应的二进制数。

//测试平台代码(3)第一次仿真结果(4)综合结果(5)布局布线(引脚分配截图)。

注意,布局布线时输入引脚应避开FPGA板中上(6)第三次仿真结果(布局布线后)(7)烧录。

完成后给老师检查。

2、4位学号显示设计要求:4位数码管依次显示本人学号末4位。

SmartDesign文件命名要求:姓名拼音首字母+下划线+cp2,测试文件名:test+下划线+cp23、交通灯控制器设计要求:交通路口东西向和南北向各有红、黄、绿三种交通灯,按“东西向红灯亮,南北向绿灯亮→东西向红灯亮,南北向黄灯亮→东西向绿灯亮,南北向红灯亮→东西向黄灯亮,南北向红灯亮”顺序循环变化,试设计状态机实现此功能。

IAR串口Simulator仿真中断的调试实现

宏文件中首先定义了一个宏函数 exeUserSetup(),它将在启动 C-SPY 并完成应用程序下载到目标系统之 后自动运行,用来创建仿真环境。然后定义一个 Access()宏函数,它将从 InputData.txt 文件中读取 Fibonacci 数列,并将这些数值分配给接收寄存器地址。用户需要将 Access()宏函数连接到一个‘立即读 取断点’。

UARTRBRTHR 接收缓冲器的值后将恢复仿真进程。

► 三、运行仿真中断 单步运行程序到 While()循环处暂停,等待输入。在 Interrupt.c 源代码窗口中找到 irqHandler()函数, 并在“++callCount;”语句行设置一个断点。全速运行程序,到达断点时程序将暂停,Terminal I/O 对话框 将显示 Fibonacci 数列,如图 5。

C-SPY 提供了 2 个系统宏函数__setSimBreak 和__orderInterrupt,可在设置宏函数 execUserSetup()中 调用, 用于自动设置断点和中断定义, 避免用户进行手动配置。 为此可以采用宏文件 SetupAdvanced.mac 取代前面的 SetupSimple.mac.这样在 C-SPY 启动时将自动设置断点,完成中断定义,用户还不必手动 在 Interrupts 和 Breakpoints 对话框中进行输入。注意,在加载 SetupAdvanced.mac 宏文件之前,应该 先去除以前定义的断点和中断。 SetupAdvanced.mac 宏文件源程序见后。

access用于链接到断点的宏在执行过程中当cspy在uartrbrthr地址上检测到一个读取访问时会暂时挂起仿真进程而执行access宏函数从inputdatatxt文件中读取数值并将其写入uartrbrthrcspy在读取uartrbrthr接收缓冲器的值后将恢复仿真进程

Libero Soc 11.2使用手册_ProASIC3系列

(2) MSS(Microcontroller Subsystem单元)

ARM Cortex-M3硬核,主频高达166MHz; 64 KB嵌入SRAM(eSRAM); 多达512 KB嵌入eNVM(Flash); 10/100/1000Mbps以太网MAC; USB 2.0 OTG(高达480Mbps); CAN控制器; SPI、I2C、多功能UARTs(MMUART)等外设; 看门狗定时器; 两个32Bit定时器(可配置为1个64Bit定时器); 两个DMA控制器:8通道PDMA(peripheral DMA),传输MSS与外设数据;高速

备注............................................................... 24

艾懋电子科技有限公司

1、SmartFusion2 概述

1.1 简介

基于Flash架构的SmartFusion2是Microsemi的第四代65nm工艺的片上系统 产品,是满足工业、军事、航空、通信和医疗领域所亟需的高安全性、高可靠性 和极低功耗的SoC系统的唯一选择。

SmartFusion2基于Microsemi前三代Flash架构FPGA发展而来,保留了Flash 架构FPGA的所有优点,并提供用户超高安全性、超高可靠性、超低功耗、超高性 能。内部集成166 MHz的ARM®Cortex™-M3的硬核处理器;配合先进的安全处理加 速器,保护您的知识产权;在SRAM、PLL等片内外设基础上,集成了高速乘法器、 DDR2/3、CAN、USB、SerDes以及千兆以太网等高级外设,满足更高性能场合SoC 需求。

HPDMA(High-performance DMA),传输eSRAM与DDR数据。

掌握用CCSsimulator模拟中断的方法

main.c isr.c vectors.asm linker.cmd

使能并打开中断 中断服务函数 中断向量表 链接器命令文件

实验环境建立

#include <stdio.h> #define #define #define #define IMR IFR ST1 PMST *(unsigned *(unsigned *(unsigned *(unsigned int int int int *)0x0000 *)0x0001 *)0x0007 *)0x001D

PAGE 1: REVS: o=0x1000, STACK: o=0x1400, IDRAM: o=0x1800, } SECTIONS { .vectors: .text: .cinit: .stack: .bss: .const: .cio: .sysmem }

> > > > > > > >

VECT SRAM SRAM STACK IDRAM IDRAM IDRAM IDRAM

摘要

复习C54x中断操作 模拟中断的方法 实验内容及步骤

Simulator 下模拟中断

编写引脚文件,指示出中断产生的时间! 将引脚文件和相应的中断引脚进行“连接”! 装载并运行程序后,CCS会根据引脚文件中设置 的时间来产生模拟的中断信号!

引脚文件(.txt)

文件内容 100 120 300 含义 分别在第 100、120、300 个CPU clock时 产生中断

软件中断,是由指令 (INTR、TRAP、RESET) 产生的。 硬件中断:

外部中断——通过DSP外部中断引脚接收到的片外设备产生的中断 (例如ADC/DAC向DSP发出的中断) 片上外设中断——DSP片上外设 (如定时器、串口、DMA等) 向CPU 发出的中断

Libero11.2使用简易教程

Libero Soc 11.2 使用手册

---- SOC 系列使用手册

作者:李达

艾懋电子科技有限公司

目录

1、参考例程 .........................................................

3

1.1 概述 ........................................................

1.3 FPGA 系列(包含硬 ARM 系列)

1.3.1 新建项目

1、点击工具栏上的 Project -> New Project (或者下图红色箭头所指) 会出

现下面所示的对话框:

艾懋电子科技有限公司

2、Project

Enable Block Creation :可以把你自己写的代码封装成一个 IPcore ,可以用在

3

1.3.1 新建项目 ...............................................

3

1.3.2 新建一个 HDL文件 : ......................................

5

1.3.3 生成 HDL文件名字 .......................................

1.3.4 编译

鼠标 左键 选中 Synthesize ,右键 点击一下,在弹出的对话框中点击 RUN;当 你看到他的前面出现了 绿色 的对号,就证明已经编译成功啦 !

如果编译错误了,鼠标 左键 选中 Synthesize ,右键 点击下“ Open Interactively ”打开 Synthesize 的窗口,进行调试。

一种基于Arduino的智能掌机设计

一种基于Arduino的智能掌机设计发布时间:2021-05-17T06:48:45.851Z 来源:《电力设备》2021年第1期作者:张朝栋程海玉唐佳锦丁一弘[导读] 物联网是新一代信息技术的重要组成部分,也是信息化时代的重要发展阶段。

(嘉兴学院南湖学院浙江嘉兴 314001)摘要:物联网是新一代信息技术的重要组成部分,也是信息化时代的重要发展阶段。

Aduino是一个方便快捷的开源电子原型平台,包括硬件(各种型号的Aduino板)和软件(aduino_ide)。

它是基于开源的软硬件平台,构建在开源simple I/O接口版上,具有类似于Java、C语言的Processing/Wiring开发环境。

我国目前对控制系统的发展比较成熟,但对控制系统的多样性还有待开发。

本文主要阐述了基于Arduino编程对智能掌机控制的实现,在过程中如何有序地实现对虚拟人物的控制并通过LDE显示屏实时进行反馈。

关键词:物联网,控制,Arduino,智能掌机与其他发达国家相比,我国在这一行业起步较晚。

在近几年,国家也开始有政策去积极鼓励该行业的稳定进步和相关产业的发展创新。

时至今日,手持掌机在现场生产、现场调试、远程抄表、物流快递等场景中发挥着非常重要的作用。

并且对象广泛,在各年龄层中流行,不仅促进相关产业技术的发展和进步,也带动了相关产业的经济发展。

Arduino包含两个主要部分。

硬件部分是可以连接电路的Arduino电路板。

另一个是Arduino?IDE,计算机中的程序开发环境。

在IDE中编写程序代码,把程序上传到Arduino电路板上,程序会告诉Arduino电路板需要做些什么。

一、基于Arduino的智能掌机的主要技术特点Arduino软件是一种让微处理器系统得到预想地开发和控制的软件平台,它能够使硬件系统和软件系统拥有高度的模块化,且其软件系统是完全开放的。

由于它具有高度模块化的硬件系统,因此,在主要的控制器主板的外部模块是各种开关量的输入/输出信号模块,以及各种使用模拟量传感器的输入信号模块和总线类型的传感器输入信号模块、通讯模块。