SIR838DP-T1-GE3;中文规格书,Datasheet资料

SIC762CD-T1-GE3;中文规格书,Datasheet资料

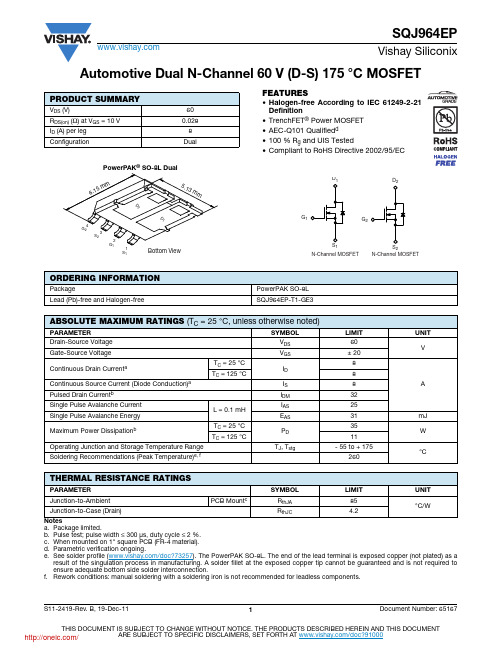

Integrated DrMOS Power StageDESCRIPTIONThe SiC762CD is an integrated solution that contains PWM optimized n-channel MOSFETs (high side and low side) and a full featured MOSFET driver IC. The device complies with the Intel DrMOS standard for desktop and server V core power stages. The SiC762CD delivers up to 35 A continuous output current and operates from an input voltage range of 3 V to 27 V. The integrated MOSFETs are optimized for output voltages in the ranges of 0.8 V to 2.0 V with a nominal input voltage of 24 V. The device can also deliver very high power at 5 V output for ASIC applications.The SiC762CD incorporates an advanced MOSFET gate driver IC. This IC accepts a single PWM input from the V R controller and converts it into the high side and low side MOSFET gate drive signals. The driver IC is designed to implement the skip mode (SMOD) function for light load efficiency improvement. Adaptive dead time control also works to improve efficiency at all load points. The SiC762CD has a thermal warning (THDN) that alerts the system of excessive junction temperature. The driver IC includes an enable pin, UVLO and shoot through protection.The SiC762CD is optimized for high frequency buck applications. Operating frequencies in excess of 1 MHz can easily be achieved.The SiC762CD is packaged in Vishay Siliconix high performance PowerP AK MLP6 x 6 package. Compact co-packaging of components helps to reduce stray inductance, and hence increases efficiency. •FEATURES•Integrated Gen III MOSFETs and DrMOScompliant gate driver IC•Enables V core switching at 1 MHz•Easily achieve > 90 % efficiency in multi-phase, low output voltage solutions•Low ringing on the VSWH pin reduces EMI•Pin compatible with DrMOS 6 x 6 version 3.0•Tri-state PWM input function prevents negative output voltage swing• 5 V logic levels on PWM•MOSFET threshold voltage optimized for 5 V driver bias supply•Automatic skip mode operation (SMOD) for light load efficiency•Under-voltage lockout•Built-in bootstrap schottky diode•Adaptive deadtime and shoot through protection •Thermal shutdown warning flag•Low profile, thermally enhanced PowerPAK® MLP 6 x 640 pin package•Halogen-free according to IEC 61249-2-21 definition •Compliant to RoHS directive 2002/95/ECAPPLICATIONS•CPU and GPU core voltage regulation•Server, computer, workstation, game console, graphics boards, PCSIC762CD APPLICATION DIAGRAMMa.T A = 25 °C and all voltages referenced to P GND = C GND unless otherwise noted.Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.Note:a.Recommended operating conditions are specified over the entire temperature range, and all voltages referenced to P GND = C GND unless otherwise noted.ORDERING INFORMATIONPart Number Package SiC762CD-T1-GE3PowerPAK MLP66-40SiC762DBReference boardRECOMMENDED OPERATING CONDITIONSParameter Symbol Min.Typ.Max.UnitInput Voltage V IN 3.01224VControl Input Voltage V CIN 4.5 5.5Drive Input Voltage V DRV 4.55.5Switch NodeV SW_DC1224THERMAL RESISTANCE RATINGSParameterSymbol Typ.Max.Unit Maximum Power Dissipation at T PCB = 25 °C P D_25C 25W Maximum Power Dissipation at T PCB = 100 °C P D_100C 10Thermal Resistance from Junction to T op R th_J_TOP 15°C/WThermal Resistance from Junction to PCBR th_J_PCB5Notes:a.Typical limits are established by characterization and are not production tested.b.Guaranteed by design.ELECTRICAL SPECIFICATIONSParameter Symbol Test Conditions Unless SpecifiedV DSBL# = V SMOD = 5 V ,V IN = 12 V , V VDRV = V VCIN = 5 V ,T A = 25 °C Min.Typ.a Max.UnitPower SuppliesV CIN Control Input Current I VCIN V DSBL# = 0 V , no switching21µAV DSBL# = 5 V , no switching 350V DSBL# = 5 V , f s = 300 kHz, D = 0.1500Drive Input Current (Dynamic)I VDRV f s = 300 kHz, D = 0.11418mAf s = 1000 kHz, D = 0.14054Bootstrap SupplyBootstrap Switch Forward Voltage V BS Diode V VCIN = 5 V, forward bias current 2 mA0.600.75VControl Inputs (PWM, DSBL#, SMOD)PWM Rising Threshold V th_pwm_r 3.5 3.9 4.2VPWM Falling Threshold V th_pwm_f 0.8 1.0 1.2PWM T ristate Rising Threshold V th_tri_r 0.9 1.3 1.8PWM T ristate Falling ThresholdV th_tri_f 3.43.74.0PWM T ristate Rising Threshold Hysteresis V hys_tri_r 280mV PWM T ristate Falling Threshold Hysteresis V hys_tri_f 180T ristate Hold-Off Time b t TSHO 150ns PWM Input CurrentI PWM V PWM = 5 V 250µA V PWM = 0 V - 250SMOD, DSBL# Logic Input Voltage V LOGIC_LH Rising (low to high) 2.0V V LOGIC_LH Falling (high to low)0.8Pull Down Impedance R THDN 5 k Ω resistor pull-up to V CIN40ΩTHDN Output Low V THDNL0.04V ProtectionThermal Warning Flag Set 150°CThermal Warning Flag Clear 135Thermal Warning Flag Hysteresis 15Under Voltage Lockout V CIN V UVLO Rising, on threshold 3.3 3.9V Under Voltage Lockout V CINFalling, off threshold 2.32.95Under Voltage Lockout Hysteresis V CIN V UVLO_HYST 400mV High Side Gate Discharge ResistorbR HS_DSCRGV VDRV = V VCIN = 0 V; V IN = 12 V20.2k ΩNote:a. Min. and Max. are not 100 % production tested.TIMING DEFINITIONSNote:GH is referenced to the high side source. GL is referenced to the low side source.TIMING SPECIFICATIONSParameter Symbol Test Conditions Unless Specified V VDRV = V VCIN = V DSBL# = 5 V ,V VIN = 12 V , T A = 25 °C Min. Typ.Max.UnitTurn Off Propagation DelayHigh Side at d_off_HS 25 % of PWM to 90 % of GH102035nsRise Time High Side t r_HS 10 % to 90 % of GH 10Fall Time High Side t f_HS 90 % to 10 % of GH 8Turn Off Propagation Delay Low Side at d_off_LS 75 % of PWM to 90 % of GL103745Rise Time Low Side t r_LS 10 % to 90 % of GL 6Fall Time Low Side t f_LS 90 % to 10 % of GL 5Dead Time Rising t dead_on 10 % of GL to 10 % of GH 27Dead Time Fallingt dead_off10 % of GH to 10 % of GL19Region DefinitionSymbol 1T urn off propagation delay LSt d_off_LS 2Fall time LS t f_LS 3Dead time rising t dead_on 4Rise time HSt r_HS 5T urn off propagation delay HSt d_off_HS 6Fall time HS t f_HS 7Dead time falling t dead_off 8Rise time LSt r_LSP W MGHGLS W1234 567810%90%10%90%75%25%SIC762CD BLOCK DIAGRAMDETAILED OPERATIONAL DESCRIPTIONPWM Input with Tristate FunctionThe PWM input receives the PWM control signal from the V R controller IC. The PWM input is designed to be compatible with standard controllers using two state logic (H and L) and advanced controllers that incorporate Tristate logic (H, L and Tristate) on the PWM output. For two state logic, the PWM input operates as follows. When PWM is driven above V th_pwm_r the low side is turned off and the high side is turned on. When PWM input is driven below V th_pwm_f the high side turns off and the Low side turns on. For Tristate logic, the PWM input operates as above for driving the MOSFETs.However, there is an third state that is entered into as the PWM output of Tristate compatible controller enters its high impedance state during shut-down. The high impedance state of the controller's PWM output allows the SiC762CD to pull the PWM input into the Tristate region (see the Tristate Voltage Threshold Diagram below). If the PWM input stays in this region for the Tristate Hold-Off Period, t TSHO , both high side and low side MOSFETs are turned off. This function allows the V R phase to be disabled without negative output voltage swing caused by inductor ringing and saves a Schottky diode clamp. The PWM and Tristate regions are separated by hysteresis to prevent false triggering. The SiC762CD incorporates PWM voltage thresholds that are compatible with 5 V logic.Disable (DSBL#)In the low state, the DSBL# pin shuts down the driver IC and disables both high-side and low-side MOSFET. In this state,the standby current is minimized. If DSBL# is left unconnected an internal pull-down resistor will pull the pin Diode Emulation Mode (SMOD) Skip ModeWhen SMOD pin is low the diode emulation mode is enabled.This is a non-synchronous conversion mode that improves light load efficiency by reducing switching losses. Conducted losses that occur in synchronous buck regulators when inductor current is negative are also reduced. Circuitry in the gate drive IC detects when inductor current crosses zero and automatically stops switching the low side MOSFET. See SMOD Operation Diagram for additional details. This function can also be used for a pre-biased output voltage. If SMOD is left unconnected, an internal pull up resistor will pull the pin up to V CIN (Logic High) to disable the diode emulation function.Thermal Shutdown Warning (THDN)The THDN pin is an open drain signal that flags the presence of excessive junction temperature. Connect a maximum of 20 k Ω to pull this pin up to V CIN . An internal temperature sensor detects the junction temperature. The temperature threshold is 150 °C. When this junction temperature is exceeded the THDN flag is set. When the junction temperature drops below 135 °C the device will clear the THDN signal. The SiC762CD does not stop operation when the flag is set. The decision to shutdown must be made by an external thermal control function.Voltage Input (V IN )This is the power input to the drain of the high-side Power MOSFET. This pin is connected to the high power intermediate BUS rail.Switch Node (V SWH and PHASE)The Switch node V SWH is the circuit PWM regulated output.Figure 2U V LOV DR VGHGLC G N DP G N DV S W HBOOTV I N V CI NP W MDSBL#THD NSMOD Thermal W arningT ristate P W MAST C N TL DCM DETECTPHASEregulated high output for the buck converter. The PHASE pin is internally connected to the switch node V SWH . This pin is to be used exclusively as the return pin for the BOOT capacitor. A 20.2 k Ω resistor is connected between GH and PHASE to provide a discharge path for the HS MOSFET in the event that V CIN goes to zero while V IN is still applied.Ground connections (C GND and P GND )P GND (power ground) should be externally connected to C GND (control signal ground). The layout of the Printed Circuit Board should be such that the inductance separating the C GND and P GND should be a minimum. Transient differences due to inductance effects between these two pins should not exceed 0.5 V.Control and Drive Supply Voltage Input (V DRV ,V CIN )V CIN is the bias supply for the gate drive control IC. V DRV is the bias supply for the gate drivers. It is recommended to separate these pins through a resistor. This creates a low pass filtering effect to avoid coupling of high frequency gate drive noise into the IC.Bootstrap Circuit (BOOT)The internal bootstrap switch and an external bootstrap capacitor form a charge pump that supplies voltage to the BOOT pin. An integrated bootstrap diode is incorporated so that only an external capacitor is necessary to complete the bootstrap circuit. Connect a boot strap capacitor with one leg tied to BOOT pin and the other tied to PHASE pin.Shoot-Through Protection and Adaptive Dead Time (AST)The SiC762CD has an internal adaptive logic to avoid shoot through and optimize dead time. The shoot through protection ensures that both high-side and low-side MOSFET are not turned on the same time. The adaptive dead time control operates as follows. When PWM input goes high the LS gate starts to go low after a few ns. When this signal crosses through 1.7 V the logic to switch the HS gate on is activated. When PWM goes low the HS gate goes low. When the HS gate-to-source drive signal crosses through 1.7 V the logic to turn on the LS gate is activated.This feature helps to adjust dead time as gate transitions change with respect to output current and temperature.Under Voltage Lockout (UVLO)During the start up cycle, the UVLO disables the gate drive holding high-side and low-side MOSFET gate low until the input voltage rail has reached a point at which the logic circuitry can be safely activated. The SiC762CD also incorporates logic to clamp the gate drive signals to zero when the UVLO falling edge triggers the shutdown of the device. As an added precaution, a 20.2 k Ω resistor is connected between GH and PHASE to provide a discharge path for the HS MOSFET.TRISTATE PWM VOLTAGE THRESHOLD DIAGRAMDEVICE TRUTH TABLEDSBL#SMOD PWM GH GL Open X X L L L X X L L H L L L H (I L > 0), L (I L ≤ 0)H L H H L H H H H L HHLLHFigure 3V th_tri_f V th_p w m_r V th_tri_rV th_p w m_fP W MGHGL t TSHOt TSHOSMOD OPERATION DIAGRAMPIN CONFIGURATIONFigure 4DSBLSMODP W MGHGLV S WI L > 0I L = 0t d(O N)t d(OFF)Figure 5 - PowerPAK MLP 6 x 6 40P Pin Out - Top ViewV I NP2A G N DP1V S W HP330V S W H29V S W H28 P G N D27 P G N D26 P G N D25 P G N D24 P G N D23 P G N D22 P G N D21 P G N D4PWM39DSBL#38THDN37CGND36GL35VSWH34VSWH33VSWH32VSWH31VSWHSMOD 1V CI N 2V DR V 3BOOT 4C G ND 5GH 6PHASE 7V I N8V I N 9V I N 1020 PGND19 PGND18PGND17 PGND16 PGND15VSWH14VIN13VIN12VIN11VINPIN DESCRIPTIONPin Number Symbol Description1SMOD Disable low side gate operation. Active low.2V CIN This will be the bias supply input for control IC (5 V).3V DRV IC bias supply and gate drive supply voltage (5 V).4BOOT High side driver bootstrap voltage pin for external bootstrap capacitor.5, 37, PAD1C GND Control signal ground. It should be connected to P GND externally. All pins internally connected.6GH Gate signal output pin for high side MOSFET. Pin for monitoring.7PHASE Return pin for the HS bootstrap capacitor. Connect a 0.1 µF ceramic capacitor from this pin to the boot pin (4).8 to 14, PAD2V IN Input voltage for power stage. It is the drain of the high-side MOSFET.15, 29 to 35,PAD3VSWHIt is the phase node between high side MOSFET source and low side MOSFET drain. It should be connected to an output inductor. All pins internally connected.16 to 28P GND Power ground.36GL Gate signal output pin for low side MOSFET. Pin for monitoring.38THDN Thermal shutdown open drain output. Use a 10K pull up resistor to V CIN.39DSBL#Disable pin. Active low.ELECTRICAL CHARACTERISTICSI CIN (mA) vs. Temperature at Frequency = 300 kHzD = 10 %, V CIN = V DRV = 5 VPWM Falling Threshold (V) vs. Temperature (°C)V CIN = V DRV = 5 VDSBL Falling Threshold (V) vs. Temperature (°C)I DRV (mA) vs. Temperature at Frequency = 300 kHzD = 10 %, V CIN = V DRV = 5 VPWM Rising Threshold (V) vs. Temperature (°C)V CIN = V DRV = 5 VDSBL Rising Threshold (V) vs. Temperature (°C)ELECTRICAL CHARACTERISTICSSMOD Falling Threshold (V) vs. Temperature (°C)V CIN = V DRV = 5 VI CIN + I DRV (mA) vs. Temperature at Frequency = 1 MHzD = 10 %, V CIN = V DRV = 5 VPWM Falling Tristate (V) vs. Temperature (°C)SMOD Rising Threshold (V) vs. Temperature (°C)V CIN = V DRV = 5 VI DRV (mA) vs. Temperature at Frequency = 1 MHzD = 10 %, V CIN = V DRV = 5 VPWM Rising Tristate Threshold (V) vs. Temperature (°C)ELECTRICAL CHARACTERISTICSCINSMOD Falling Threshold vs. V CINPWM Falling Threshold vs. VCINSMOD Rising Threshold vs. V CINPWM Rising Threshold vs. V分销商库存信息: VISHAYSIC762CD-T1-GE3。

RHRG30120;中文规格书,Datasheet资料

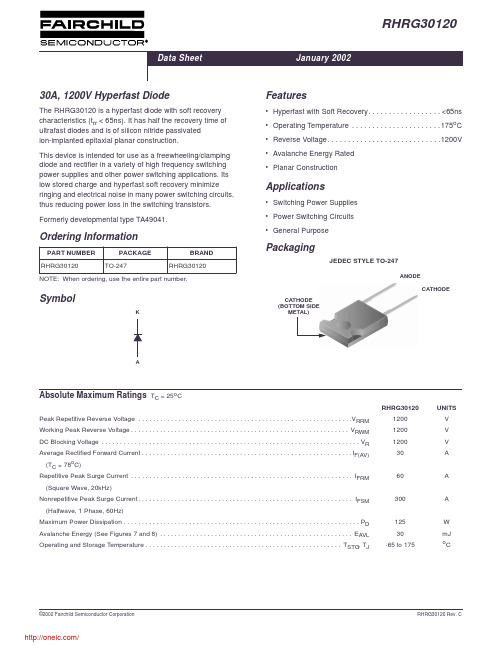

RHRG3012030A,1200V Hyperfast DiodeThe RHRG30120is a hyperfast diode with soft recovery characteristics (t rr <65ns).It has half the recovery time of ultrafast diodes and is of silicon nitride passivated ion-implanted epitaxial planar construction.This device is intended for use as a freewheeling/clamping diode and rectifier in a variety of high frequency switching power supplies and other power switching applications.Its low stored charge and hyperfast soft recovery minimizeringing and electrical noise in many power switching circuits,thus reducing power loss in the switching transistors.Formerly developmental type TA49041.SymbolFeatures•Hyperfast with Soft Recovery..................<65ns •Operating Temperature ......................175o C •Reverse Voltage............................1200V •Avalanche Energy Rated •Planar ConstructionApplications•Switching Power Supplies •Power Switching Circuits •General PurposePackagingJEDEC STYLE TO-247Ordering InformationNOTE:When ordering,use the entire partnumber.KACATHODE CATHODEANODEMETAL)(BOTTOM SIDEAbsolute Maximum Ratings T C =25o CRHRG30120UNITS Peak Repetitive Reverse Voltage ...........................................................V RRM 1200V Working Peak Reverse Voltage............................................................V RWM 1200V DC Blocking Voltage .......................................................................V R 1200V Average Rectified Forward Current..........................................................I F(AV)30A (T C =78o C)Repetitive Peak Surge Current .............................................................I FRM 60A (Square Wave,20kHz)Nonrepetitive Peak Surge Current...........................................................I FSM 300A(Halfwave,1Phase,60Hz)Maximum Power Dissipation .................................................................P D 125W Avalanche Energy (See Figures 7and 8).....................................................E AVL 30mJOperating and Storage Temperature ......................................................T STG ,T J-65to 175o CData SheetJanuary 2002Electrical SpecificationsT C =25o C,Unless Otherwise SpecifiedDEFINITIONSV F =Instantaneous forward voltage (pw =300µs,D =2%).I R =Instantaneous reverse current.t rr =Reverse recovery time (See Figure 6),summation of t a +t b .t a =Time to reach peak reverse current (See Figure 6).t b =Time from peak I RM to projected zero crossing of I RM based on a straight line from peak I RM through 25%of I RM (See Figure 6).R θJC =Thermal resistance junction to case.pw =pulse width.D =duty cycle.Typical Performance CurvesFIGURE 1.FORWARD CURRENT vs FORWARD VOLTAGE FIGURE 2.REVERSE CURRENT vs REVERSE VOLTAGE200100101I F ,F O R W A R D C U R R E N T (A )V F ,FORWARD VOLTAGE (V)0.51.01.52.02.53.03.54.04.5175o C100o C25o C500100101.00.10.010.001020040060080010001200V R ,REVERSE VOLTAGE (V)I R ,R E V E R S E C U R R E N T (µA )175o C100o C 25o CFIGURE 3.t rr ,t a AND t b CURVES vs FORWARD CURRENTFIGURE 4.CURRENT DERATING CURVETypical Performance Curves(Continued)1007550251t ,T I M E (n s )I F ,FORWARD CURRENT (A)1030t rrt at b40302010255075100125150175T C ,CASE TEMPERATURE (o C)I F (A V ),A V E R A G E F O R W A R D C U R R E N T (A )SQ.WAVEDCTest Circuits and WaveformsFIGURE 5.t rr TEST CIRCUITFIGURE 6.t rr WAVEFORMS AND DEFINITIONSFIGURE 7.AVALANCHE ENERGY TEST CIRCUITFIGURE 8.AVALANCHE CURRENT AND VOLTAGEWAVEFORMSV DDV GEV t 1R GDUTCURRENT SENSE+LRV DDR <0.1ΩE AVL =1/2LI 2[V R(AVL)/(V R(AVL)-V DD )]Q 1=IGBT (BV CES >DUT V R(AVL))-V DDQ 1I MAX =1.225A L =40mH I V012分销商库存信息: FAIRCHILD RHRG30120。

FDS9933A;中文规格书,Datasheet资料

D2D2D1D1TRADEMARKSACEx™CoolFET™CROSSVOLT™E 2CMOS TM FACT™FACT Quiet Series™FAST ®FASTr™GTO™HiSeC™The following are registered and unregistered trademarks Fairchild Semiconductor owns or is authorized to use and is not intended to be an exhaustive list of all such trademarks.LIFE SUPPORT POLICYFAIRCHILD’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORTDEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROV AL OF FAIRCHILD SEMICONDUCTOR CORPORATION.As used herein:1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant intothe body, or (b) support or sustain life, or (c) whosefailure to perform when properly used in accordancewith instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.2. A critical component is any component of a lifesupport device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.PRODUCT STATUS DEFINITIONS Definition of Terms Datasheet Identification Product Status DefinitionAdvance InformationPreliminary No Identification Needed Obsolete This datasheet contains the design specifications for product development. Specifications may change in any manner without notice.This datasheet contains preliminary data, andsupplementary data will be published at a later date.Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice in order to improve design.This datasheet contains specifications on a product that has been discontinued by Fairchild semiconductor.The datasheet is printed for reference information only.Formative or In DesignFirst ProductionFull ProductionNot In ProductionDISCLAIMERFAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY , FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.SyncFET™TinyLogic™UHC™VCX™ISOPLANAR™MICROWIRE™POP™PowerTrench QFET™QS™Quiet Series™SuperSOT™-3SuperSOT™-6SuperSOT™-8分销商库存信息: FAIRCHILDFDS9933A。

MC74HCT138ADTR2G,MC74HCT138ADR2G,MC74HCT138ADG,MC74HCT138AN,MC74HCT138AD, 规格书,Datasheet 资料

MC74HCT138A1-of-8 Decoder/ Demultiplexer with LSTTL Compatible InputsHigh−Performance Silicon−Gate CMOSThe MC74HCT138A is identical in pinout to the LS138. The HCT138A may be used as a level converter for interfacing TTL or NMOS outputs to High Speed CMOS inputs.The HCT138A decodes a three−bit Address to one−of−eight active−lot outputs. This device features three Chip Select inputs, two active−low and one active−high to facilitate the demultiplexing, cascading, and chip−selecting functions. The demultiplexing function is accomplished by using the Address inputs to select the desired device output; one of the Chip Selects is used as a data input while the other Chip Selects are held in their active states.Features•Output Drive Capability: 10 LSTTL Loads•TTL/NMOS Compatible Input Levels•Outputs Directly Interface to CMOS, NMOS, and TTL •Operating V oltage Range: 4.5 to 5.5 V•Low Input Current: 1.0 m A•In Compliance with the Requirements Defined by JEDEC Standard No. 7A•Chip Complexity: 122 FETs or 30.5 Equivalent Gates•Pb−Free Packages are Available**For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting TechniquesReference Manual, SOLDERRM/D.MARKINGDIAGRAMSSOIC−16D SUFFIXCASE 751BTSSOP−16DT SUFFIXCASE 948FPDIP−16N SUFFIXCASE 648116MC74HCT138ANAWLYYWWG116HCT138AGAWLYWWA=Assembly LocationWL, L=Wafer LotYY, Y=YearWW, W=Work WeekG or G=Pb−Free Package(Note: Microdot may be in either location)See detailed ordering and shipping information in the package dimensions section on page 2 of this data sheet.ORDERING INFORMATIONHCT138AALYW GG116InputsOutputs CS1CS2CS3A2A1A0Y0Y1Y2Y3Y4Y5Y6Y7X X H X X X H H H H H H H H X HX X X X H H H H H H H H L X X X X X H H H H H H H H H L L L L L L H H H H H H H H L L L LH H L H H H H H H H L L L H L H HL H H H H H H L L L H H H H H L H H H H H L L H L L H H H H L H H H H L L H L H H H H H H LH H H L L H H L H H H H H H L H HLLHHHHHHHHHHLFUNCTION TABLEH = high level (steady state)L = low level (steady state)X = don’t careLOGIC DIAGRAMY6Y5Y4Y3Y2Y1Y0Y7CS1CS2ACTIVE-LOW OUTPUTSADDRESS INPUTSCS3CHIP-SELECT INPUTSCC PIN ASSIGNMENTA0CS2A2A1Y7CS1CS3GNDY3Y2Y1Y0V CC Y5Y4Y6Design Criteria Value Units Internal Gate Count*30.5ea.Internal Gate Propagation Delay 1.5nsInternal Gate Power Dissipation 5.0m W Speed Power Product.0075pJ*Equivalent to a two −input NAND gate.ORDERING INFORMATIONDevicePackage Shipping †MC74HCT138ANG PDIP −16(Pb −Free)500 Units / Box MC74HCT138ADG SOIC −16(Pb −Free)48 Units / Rail MC74HCT138ADR2G SOIC −16(Pb −Free)2500 Units / Tape & Reel MC74HCT138ADTR2TSSOP −16*2500 Units / Tape & Reel†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.*This package is inherently Pb −Free.MAXIMUM RATINGSSymbol Parameter Value Unit V CC DC Supply Voltage (Referenced to GND)– 0.5 to + 7.0V V in DC Input Voltage (Referenced to GND)– 0.5 to V CC + 0.5V V out DC Output Voltage (Referenced to GND)– 0.5 to V CC + 0.5VI in DC Input Current, per Pin±20mAI out DC Output Current, per Pin±25mAI CC DC Supply Current, V CC and GND Pins±50mAP D Power Dissipation in Still Air Plastic DIP†SOIC Package†TSSOP Package†750500450mWT stg Storage Temperature– 65 to + 150_C T L Lead Temperature, 1 mm from Case for 10 Seconds(Plastic DIP, TSSOP or SOIC Package)260_CStresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.†Derating—Plastic DIP: – 10 mW/_C from 65_ to 125_CSOIC Package: – 7 mW/_C from 65_ to 125_CTSSOP Package: − 6.1 mW/_C from 65_ to 125_CRECOMMENDED OPERATING CONDITIONSSymbol Parameter Min Max Unit V CC DC Supply Voltage (Referenced to GND) 4.5 5.5VV in, V out DC Input Voltage, Output Voltage (Referenced to GND)0V CC V T A Operating Temperature, All Package Types– 55+ 125_C t r, t f Input Rise and Fall Time (Figure 1)0500ns DC ELECTRICAL CHARACTERISTICS (Voltages Referenced to GND)Symbol Parameter Test Conditions V CCVGuaranteed LimitUnit – 55 to25_C v85_C v 125_CV IH Minimum High−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.52.02.02.02.02.02.0VV IL Maximum Low−Level Input Voltage V out = 0.1 V or V CC – 0.1 V|I out| v 20 m A4.55.50.80.80.80.80.80.8VV OH Minimum High−Level Output Voltage V in = V IH or V IL|I out| v 20 m A4.55.54.45.44.45.44.45.4VV in = V IH or V IL|I out| v 4.0 mA 4.5 3.98 3.84 3.7V OL Maximum Low−Level Output Voltage V in = V IH or V IL|I out| v 20 m A4.55.50.10.10.10.10.10.1VV in = V IH or V IL|I out| v 4.0 mA 4.50.260.330.4I in Maximum Input Leakage Current V in = V CC or GND 6.0±0.1±1.0±1.0m AI CC Maximum Quiescent SupplyCurrent (per Package)V in = V CC or GNDI out = 0 m A5.5 4.040160m AD I CC Additional Quiescent SupplyCurrentV in = 2.4 V, Any One InputV in = V CC or GND, Other Inputsl out = 0 m A 5.5≥ − 55_C25_C to 125_CmA2.9 2.4This device contains protectioncircuitry to guard against damagedue to high static voltages or electricfields. However, precautions mustbe taken to avoid applications of anyvoltage higher than maximum ratedvoltages to this high−impedance cir-cuit. For proper operation, V in andV out should be constrained to therange GND v (V in or V out) v V CC.Unused inputs must always betied to an appropriate logic voltagelevel (e.g., either GND or V CC).Unused outputs must be left open.AC ELECTRICAL CHARACTERISTICS (V CC = 5.0 V ± 10%, C L = 50 pF, Input t r = t f = 6.0 ns)Symbol ParameterGuaranteed LimitUnit – 55 to 25_C v 85_C v 125_Ct PLH ,t PHL Maximum Propagation Delay, Input A to Output Y (Figures 1 and 4)303845ns t PLH ,t PHL Maximum Propagation Delay, CS1 to Output Y (Figures 2 and 4)273441ns t PLH ,t PHL Maximum Output Transition Time, CS2 or CS3 to Output Y (Figures 3 and 4)303845ns t TLH ,t THL Maximum Output Transition Time, Any Output (Figures 2 and 4)151922ns t r , t f Maximum Input Rise and Fall Time 500500500ns C inMaximum Input Capacitance101010pFC PDPower Dissipation Capacitance (Per Enabled Output)*Typical @ 25°C, V CC = 5.0 VpF51*Used to determine the no −load dynamic power consumption: P D = C PD V CC f + I CC V CC .EXPANDED LOGIC DIAGRAMA0A1A2CS3CS2CS1SWITCHING WAVEFORMSFigure 1.3 VGNDFigure 2.3 V GND t OUTPUT YINPUT CS2, CS33 V GNDFigure 3.*Includes all probe and jig capacitanceFigure 4.C L *TEST POINT TEST CIRCUITPDIP −16N SUFFIX CASE 648−08ISSUE TSOIC −16D SUFFIX CASE 751B −05ISSUE JNOTES:1.DIMENSIONING AND TOLERANCING PERANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: INCH.3.DIMENSION L TO CENTER OF LEADSWHEN FORMED PARALLEL.4.DIMENSION B DOES NOT INCLUDEMOLD FLASH.5.ROUNDED CORNERS OPTIONAL.MSEATING PLANEMAM0.25 (0.010)T DIM MIN MAX MIN MAX MILLIMETERS INCHES A 0.7400.77018.8019.55B 0.2500.270 6.35 6.85C 0.1450.175 3.69 4.44D 0.0150.0210.390.53F 0.0400.70 1.02 1.77G 0.100 BSC 2.54 BSC H 0.050 BSC 1.27 BSC J 0.0080.0150.210.38K 0.1100.130 2.80 3.30L 0.2950.3057.507.74M 0 10 0 10 S0.0200.0400.51 1.01____NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSIONS A AND B DO NOT INCLUDE MOLD PROTRUSION.4.MAXIMUM MOLD PROTRUSION 0.15 (0.006)PER SIDE.5.DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBARPROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION ATMAXIMUM MATERIAL CONDITION.SBM0.25 (0.010)AST DIM MIN MAX MIN MAX INCHESMILLIMETERS A 9.8010.000.3860.393B 3.80 4.000.1500.157C 1.35 1.750.0540.068D 0.350.490.0140.019F 0.40 1.250.0160.049G 1.27 BSC 0.050 BSC J 0.190.250.0080.009K 0.100.250.0040.009M 0 7 0 7 P 5.80 6.200.2290.244R0.250.500.0100.019____TSSOP −16DT SUFFIX CASE 948F −01ISSUE ADIM MIN MAX MIN MAX INCHESMILLIMETERS A 4.90 5.100.1930.200B 4.30 4.500.1690.177C −−− 1.20−−−0.047D 0.050.150.0020.006F 0.500.750.0200.030G 0.65 BSC 0.026 BSC H 0.180.280.0070.011J 0.090.200.0040.008J10.090.160.0040.006K 0.190.300.0070.012K10.190.250.0070.010L 6.40 BSC 0.252 BSC M0 8 0 8 NOTES:1.DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.2.CONTROLLING DIMENSION: MILLIMETER.3.DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS.MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.4.DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.5.DIMENSION K DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08(0.003) TOTAL IN EXCESS OF THE K DIMENSION AT MAXIMUM MATERIAL CONDITION.6.TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY .7.DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE −W −.____ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages.“Typical” parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including “Typicals” must be validated for each customer application by customer’s technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates,and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.PUBLICATION ORDERING INFORMATION。

SI7116DN-T1-GE3;中文规格书,Datasheet资料

Vishay SiliconixSi7116DNN-Channel 40-V (D-S) Fast Switching MOSFETFEATURES•Halogen-free Option Available •TrenchFET ® Power MOSFET•New Low Thermal Resistance PowerPAK ®Package with Low 1.07 mm Profile •PWM Optimized •100 % R g TestedAPPLICATIONS•Synchronous Rectification •Intermediate Switch •Synchronous BuckPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)Q g (Typ.)400.0078 at V GS = 10 V 16.415 nC0.010 at V GS = 4.5 V14.5Notes:a.Surface Mounted on 1" x 1" FR4 board.b.See Solder Profile (/ppg?73257). The PowerPAK 1212-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.c.Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components. ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameterSymbol 10 sSteady StateUnit Drain-Source Voltage V DS 40VGate-Source VoltageV GS ± 20Continuous Drain Current (T J = 150 °C)a T A = 25 °C I D16.410.5AT A = 70 °C13.18.4Pulsed Drain CurrentI DM 60Continuous Source Current (Diode Conduction)a I S 3.21.3Avalanche Current L = 0 1 mH I AS 15Avalanche EnergyE AS 11mJ Maximum Power Dissipation aT A = 25 °C P D 3.8 1.5W T A = 70 °C 2.00.8Operating Junction and Storage T emperature Range T J , T stg- 55 to 150°CSoldering Recommendations (Peak Temperature)b, c260THERMAL RESISTANCE RATINGSParameter Symbol T ypical Maximum UnitMaximum Junction-to-Ambient a t ≤ 10 s R thJA 2433°C/WSteady State 6581Maximum Junction-to-Case (Drain)Steady StateR thJC1.92.4Vishay SiliconixSi7116DNNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.MOSFET SPECIFICATIONS T J = 25 °C, unless otherwise notedParameter Symbol T est Conditions Min.T yp.Max.UnitStaticGate Threshold Voltage V GS(th) V DS = V GS , I D = 250 µA 1.52.5VGate-Body LeakageI GSS V DS = 0 V , V GS = ± 20 V ± 100 nAZero Gate Voltage Drain Current I DSS V DS = 40 V , V GS = 0 V 1µA V DS = 40 V, V GS = 0 V , T J = 55 °C5On-State Drain Current aI D(on) V DS ≥ 5 V , V GS = 10 V 40A Drain-Source On-State Resistance a R DS(on) V GS = 10 V , I D = 16.4 A 0.00650.0078ΩV GS = 4.5 V, I D = 14.5 A 0.00830.010Forward T ransconductance a g fs V DS = 15 V , I D = 16.4 A 68S Diode Forward Voltage a V SDI S = 3.2 A, V GS = 0 V0.81.2VDynamic bTotal Gate Charge Q g V DS = 20 V , V GS = 4.5 V , I D = 16.4 A1523nCGate-Source Charge Q gs 6.7Gate-Drain Charge Q gd 5.1Gate Resistance R g f = 1 MHz0.71.42.1ΩTurn-On Delay Time t d(on) V DD = 20 V , R L = 20 ΩI D ≅ 1 A, V GEN = 10 V , R g = 6 Ω1015ns Rise Timet r 1015Turn-Off Delay Time t d(off) 3655Fall Timet f 1015Source-Drain Reverse Recovery Time t rr I F = 3.2 A, di/dt = 100 A/µs 3060Body Diode Reverse Recovery ChargeQ rrI F = 3.2 A, di/dt = 100 A/µs 2652nc Output Characteristics Transfer CharacteristicsVishay SiliconixSi7116DNTYPICAL CHARACTERISTICS 25°C, unless otherwise notedGate ChargeSource-Drain Diode Forward VoltageCapacitanceOn-Resistance vs. Gate-to-Source VoltageSafe Operating AreaVishay SiliconixSi7116DNTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Sil iconix maintains worl dwide manufacturing capabil ity. Products may be manufactured at one of several qual ified l ocations. Rel iabil ity data for Sil icon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?73139.Normalized Thermal Transient Impedance, Junction-to-CaseVishay SiliconixAN822PowerPAK ® 1212 Mounting and Thermal ConsiderationsJohnson ZhaoMOSFETs for switching applications are now available with die on resistances around 1 m Ω and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvi-ous that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. The PowerPAK 1212-8 provides ultra-low thermal impedance in a small package that is ideal for space-constrained applications. In this application note, the PowerPAK 1212-8’s construction is described. Following this,mounting information is presented. Finally, thermal and electrical performance is discussed.THE PowerPAK PACKAGEThe PowerPAK 1212-8 package (Figure 1) is a deriva-tive of PowerPAK SO-8. It utilizes the same packaging technology, maximizing the die area. The bottom of the die attach pad is exposed to provide a direct, low resis-tance thermal path to the substrate the device is mounted on. The PowerPAK 1212-8 thus translates the benefits of the PowerPAK SO-8 into a smaller package, with the same level of thermal performance.(Please refer to application note “PowerPAK SO-8Mounting and Thermal Considerations.”)The PowerPAK 1212-8 has a footprint area compara-ble to TSOP-6. It is over 40 % smaller than standard TSSOP-8. Its die capacity is more than twice the size of the standard TSOP-6’s. It has thermal performance an order of magnitude better than the SO-8, and 20times better than TSSOP-8. Its thermal performance is better than all current SMT packages in the market. It will take the advantage of any PC board heat sink capability. Bringing the junction temperature down also increases the die efficiency by around 20 % compared with TSSOP-8. For applications where bigger pack-ages are typically required solely for thermal consider-ation, the PowerPAK 1212-8 is a good option.Both the single and dual PowerPAK 1212-8 utilize the same pin-outs as the single and dual PowerPAK SO-8.The low 1.05 mm PowerPAK height profile makes both versions an excellent choice for applications with space constraints.PowerPAK 1212 SINGLE MOUNTINGTo take the advantage of the single PowerPAK 1212-8’s thermal performance see Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs. Click on the PowerPAK 1212-8 single in the index of this document.In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack,experiments have found that adding copper beyond an area of about 0.3 to 0.5 in 2 of will yield little improve-ment in thermal performance.Figure 1.PowerPAK 1212 DevicesVishay SiliconixAN822PowerPAK 1212 DUALTo take the advantage of the dual PowerPAK 1212-8’s thermal performance, the minimum recommended land pattern can be found in Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs . Click on the PowerPAK 1212-8 dual in the index of this doc-ument.The gap between the two drain pads is 10 mils. This matches the spacing of the two drain pads on the Pow-erPAK 1212-8 dual package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight, and layer stack,experiments have found that adding copper beyond an area of about 0.3 to 0.5 in 2 of will yield little improve-ment in thermal performance.REFLOW SOLDERINGVishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a preconditioning test and are then reliability-tested using temperature cycle, bias humid-ity, HAST, or pressure pot. The solder reflow tempera-ture profile used, and the temperatures and time duration, are shown in Figures 2 and 3. For the lead (Pb)-free solder profile, see /doc?73257.Ramp-Up Rate+ 6°C /Second Maximum Temperature at 155 ± 15 °C 120 Seconds Maximum Temperature Above 180 °C 70 - 180 Seconds Maximum T emperature240 + 5/- 0 °CTime at Maximum T emperature 20 - 40 Seconds Ramp-Down Rate+ 6 °C/Second MaximumFigure 2. Solder Reflow Temperature ProfileFigure 3.Solder Reflow Temperatures and Time DurationsVishay SiliconixAN822THERMAL PERFORMANCE IntroductionA basic measure of a device’s thermal performance is the junction-to-case thermal resistance, R θjc, or the junction to- foot thermal resistance, R θjf. This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the PowerPAK 1212-8, PowerPAK SO-8,standard TSSOP-8 and SO-8 equivalent steady state performance.By minimizing the junction-to-foot thermal resistance, the MOSFET die temperature is very close to the tempera-ture of the PC board. Consider four devices mounted on a PC board with a board temperature of 45 °C (Figure 4). Suppose each device is dissipating 2 W. Using the junc-tion-to-foot thermal resistance characteristics of the PowerPAK 1212-8 and the other SMT packages, die temperatures are determined to be 49.8 °C for the Pow-erPAK 1212-8, 85 °C for the standard SO-8, 149 °C for standard TSSOP-8, and 125 °C for TSOP-6. This is a 4.8 °C rise above the board temperature for the Power-PAK 1212-8, and over 40 °C for other SMT packages. A 4.8 °C rise has minimal effect on r DS(ON) whereas a rise of over 40 °C will cause an increase in r DS(ON) as high as 20 %.Spreading CopperDesigners add additional copper, spreading copper, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading copper.Figure 5 and Figure 6 show the thermal resistance of a PowerPAK 1212-8 single and dual devices mounted on a 2-in. x 2-in., four-layer FR-4 PC boards. The two inter-nal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many appli-cations. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken. The results indicate that an area above 0.2 to 0.3 square inches of spreading copper gives no additional thermal performance improvement.A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces, and then totally removed. No signif-icant effect was observed.TABLE 1: EQIVALENT STEADY STATE PERFORMANCEPackage SO-8TSSOP-8TSOP-8PPAK 1212PPAK SO-8ConfigurationSingleDual Single Dual Single Dual Single Dual Single Dual Thermal Resiatance R thJC (C/W)2040528340902.45.51.85.5Figure 4. Temperature of Devices on a PC BoardVishay SiliconixAN822CONCLUSIONSAs a derivative of the PowerPAK SO-8, the PowerPAK 1212-8 uses the same packaging technology and has been shown to have the same level of thermal perfor-mance while having a footprint that is more than 40 %smaller than the standard TSSOP-8.Recommended PowerPAK 1212-8 land patterns are provided to aid in PC board layout for designs using this new package.The PowerPAK 1212-8 combines small size with attrac-tive thermal characteristics. By minimizing the thermal rise above the board temperature, PowerPAK simplifies thermal design considerations, allows the device to run cooler, keeps r DS(ON) low, and permits the device to handle more current than a same- or larger-size MOS-FET die in the standard TSSOP-8 or SO-8 packages.Figure 5. Spreading Copper - Si7401DNFigure 6. Spreading Copper - Junction-to-Ambient Performance分销商库存信息: VISHAYSI7116DN-T1-GE3。

SI4459ADY-T1-GE3;中文规格书,Datasheet资料

3600

1800 Crss

Coss

0.003 0 14 28 42 ID - Drain Current (A) 56 70

0 0 6 12 18 24 VDS - Drain-to-Source Voltage (V) 30

A

mJ

Maximum Power Dissipation

PD

W

Operating Junction and Storage Temperature Range

TJ, Tstg

°C

THERMAL RESISTANCE RATINGS

Parameter Maximum Junction-to-Ambienta, c Maximum Junction-to-Foot Notes: a. Surface mounted on 1" x 1" FR4 board. b. t = 10 s. c. Maximum under steady state conditions is 80 °C/W. d. Based on TC = 25 °C. Document Number: 69979 S11-1813-Rev. B, 12-Sep-11 This document is subject to change without notice. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT /doc?91000 / 1 t 10 s Steady State Symbol RthJA RthJF Typical 29 13 Maximum 35 16 Unit °C/W

DP83848H-MAU-EK;中文规格书,Datasheet资料

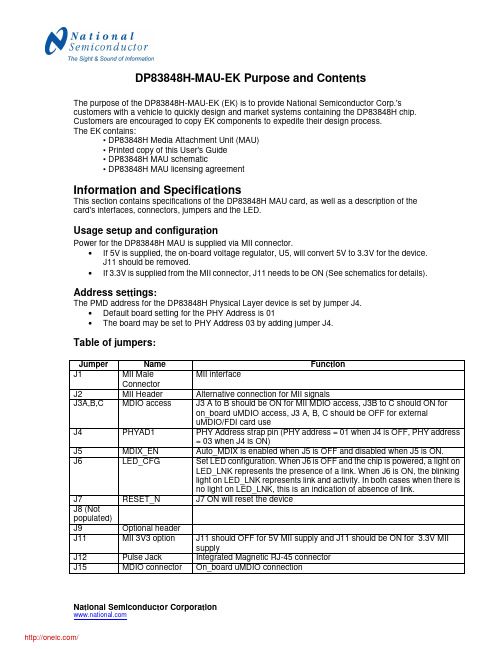

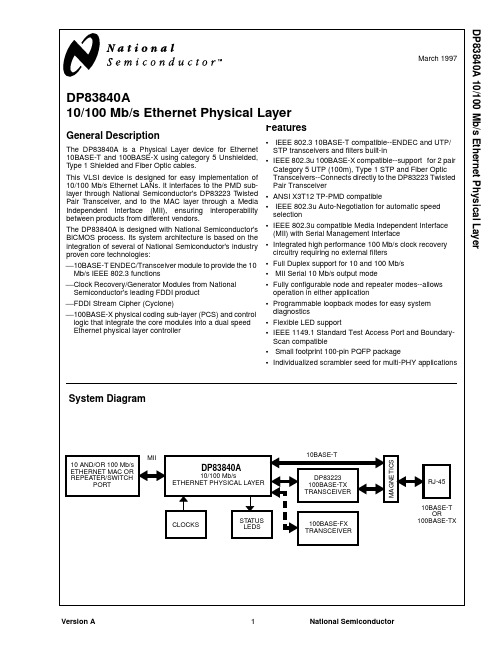

DP83848H-MAU-EK Purpose and ContentsThe purpose of the DP83848H-MAU-EK (EK) is to provide National Semiconductor Corp.'scustomers with a vehicle to quickly design and market systems containing the DP83848H chip. Customers are encouraged to copy EK components to expedite their design process.The EK contains:• DP83848H Media Attachment Unit (MAU)• Printed copy of this User's Guide• DP83848H MAU schematic• DP83848H MAU licensing agreementInformation and SpecificationsThis section contains specifications of the DP83848H MAU card, as well as a description of thecard's interfaces, connectors, jumpers and the LED.Usage setup and configurationPower for the DP83848H MAU is supplied via MII connector.•If 5V is supplied, the on-board voltage regulator, U5, will convert 5V to 3.3V for the device.J11 should be removed.•If 3.3V is supplied from the MII connector, J11 needs to be ON (See schematics for details). Address settings:The PMD address for the DP83848H Physical Layer device is set by jumper J4.•Default board setting for the PHY Address is 01•The board may be set to PHY Address 03 by adding jumper J4.Table of jumpers:Jumper Name FunctionJ1 MII MaleMII interfaceConnectorJ2 MII Header Alternative connection for MII signalsJ3A,B,C MDIO access J3 A to B should be ON for MII MDIO access, J3B to C should ON foron_board uMDIO access, J3 A, B, C should be OFF for externaluMDIO/FDI card useJ4 PHYAD1 PHY Address strap pin (PHY address = 01 when J4 is OFF, PHY address= 03 when J4 is ON)J5 MDIX_EN Auto_MDIX is enabled when J5 is OFF and disabled when J5 is ON.J6 LED_CFG Set LED configuration. When J6 is OFF and the chip is powered, a light onLED_LNK represents the presence of a link. When J6 is ON, the blinkinglight on LED_LNK represents link and activity. In both cases when there isno light on LED_LNK, this is an indication of absence of link.J7 RESET_N J7 ON will reset the deviceJ8 (Notpopulated)J9 Optional headerJ11 MII 3V3 option J11 should OFF for 5V MII supply and J11 should be ON for 3.3V MIIsupplyJ12 Pulse Jack Integrated Magnetic RJ-45 connectorJ15 MDIO connector On_board uMDIO connectionDP83848H MAU SpecificationOverviewThe DP83848H MAU is an NSC demo platform to allow customer evaluation of our device.While the DP83848H has many advanced and enticing features, this specific board is designed to demonstrate only a subset of those. The features chosen are the ones that the mainstream customers will use. Thus we have created an affordable, aesthetic platform to demonstrate the simplicity of designing in a National Semiconductor DP83848H.Target EnvironmentAny customer equipment that provides a standard IEEE 802.3, Clause 22 MII DTE interface; e.g. SmartBits/Netcom box.Features/GoalsThe DP83848H MAU features:•Intergrated magnetics•Minimum configuration requirements:o 2 PHY Addresses - 01h (default) or 03ho 2 LEDs – 1 power, 1 LED for LINKo Strap Options – MDIX_EN, LED_CFGo RESET_N jumper•Connections for the following interfaces:o MIl Interfaceo Integrated transformer RJ-45o Header for “ribbon cable” connection to MII•Standard PCB layout considerations with regards to clock, MII, and TD/RD•Single sided component placement•On-board clock – Crystal•On-board power supplied by MII connector only, jumper to configure 5v or 3.3v•On-board MDIO circuit•Low costMAU Block DiagramPCB Physical Layout requirements / Considerations•FR4 material•Trace impedance will be ensured by design:o Trace symmetry within differential pair (+/- 0.5”)o Differential impedance 100 ohms, +/- 5%o Adjacent differential pairs spacing > 2X distance within a differential pair, to minimize cross-talk and EMI•Trace length matching between differential pairs not required•Trace space will be 0.007”/0.008” minimum•Uniform supply & ground plane•Combination of through-hole and surface mount technology•Target size 2.0” (height), 3.0” (length)• 4 layers•Silk screen on two sidesMAU Interface requirements•System interface will be via the MII connector, and MII header•RJ-45 for network connection•On Board Serial Management circuitSoftware•No device specific software is required for this boardNational does provide the integrity utility; a diagnostic and configuration package at/appinfo/networks/ethernet_utility.htmlAdditional informationUpdated versions of the included material, related material can be found by going to or directly to design resources at/appinfo/networks/webench/dp83848.htmlNational Semiconductor Corporation2900 Semiconductor DriveSanta Clara, CA 95051, U.S.A.Tel: 1-800-272-9959Fax: 1-800-737-7018Email: support@WWW: National Semiconductor EuropeFax: (+49) 0-180-530 85 86Email: europe.support@Deutsch Tel: (+49) 0-180-530 85 85English Tel: (+49) 0-180-532 78 32National Semiconductor Asia PacificCustomer Response GroupTel: 65-254-4466Fax: 65-250-4466Email: sea.support@National Semiconductor Japan Ltd.Tel: 81-3-5620-6175Fax: 81-3-5620-6179Copyright © 2005 National Semiconductor Corporation.National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names are trademarks of their respective holders.分销商库存信息: NATIONAL-SEMICONDUCTOR DP83848H-MAU-EK。

产品规格书-模板.pdf

广州博冠光电科技股份有限公司

自研摇头机规格说明书

产品经理 王继升 日期

项目经理 骆爱群 日期

确认签字

销售经理 刘涌辉 日期

研发总监 刘广 日期

版本控制

版本 REV1.0

日期 2018-05-09

撰写 王继升

页数

更新说明 首次发布

第 页 1共 4 页

规格说明书

广州博冠光电科技股份有限公司

产品参数 Product specification

配件 Accessories

电源适配器 USB 数据线 USB-cable 用户手册 User Manual /Instruction

数量*1 数据线 1m*1

数量*1

其他 Other

包装 The Package

第 页 4共 4 页

麦克风

支持语音

音箱

WIFI 音箱

供电方式 Mode of power supply

Micro USB-cable DC 5V±10%,最大功耗 3W,防雷击 防静电,支持过压保护

使用环境温度

-10°~50°

技术规格

存储类型 视频编码 支持模式 语音 告警

TF 卡,最高支持 128GB(需单独购买) 云存(客户可选) H.265 日夜模式 星光模式 高品质双向语音 移动侦测告警 声音告警

第 页 3共 5 页

规格说明书

广州博冠光电科技股份有限公司

APP 功能

国际认证 配件清单

区域设置

告警区域设置

剪辑

10、20、30、60 秒等长度视频剪辑 保存至手机 直播

分享

分享至社交软件(短视频) 分享视频源至亲友(管理者可以删除权限)

SIB433EDK-T1-GE3;中文规格书,Datasheet资料

Min. - 20

Typ.

Max.

Unit V

- 13 2.5 - 0.4 -1 ±6 ± 0.5 -1 - 10 - 15 0.047 0.064 0.085 12 0.058 0.077 0.105

mV/°C V

µA

A S

Drain-Source On-State Resistance Forward Transconductancea Dynamic

°C

THERMAL RESISTANCE RATINGS

Parameter Maximum Junction-to-Ambientb, f Maximum Junction-to-Case (Drain) t5s Steady State Symbol RthJA RthJC Typical 41 7.5 Maximum 51 9.5 Unit °C/W

G R

1.60 mm

D

Ordering Information: SiB433EDK-T1-GE3 (Lead (Pb)-free and Halogen-free)

P-Channel MOSFET

ABSOLUTE MAXIMUM RATINGS (TA = 25 °C, unless otherwise noted)

SiB433EDK

Vishay Siliconix

P-Channel 20-V (D-S) MOSFET

FEATURES PRODUCT SUMMARY

VDS (V) - 20 RDS(on) () 0.058 at VGS = - 4.5 V 0.077 at VGS = - 2.5 V 0.105 at VGS = - 1.8 V ID (A) - 9a - 9a -5 7.6 nC Qg (Typ.)

SIP32411DNP-T1-GE4;SIP32411DR-T1-GE3;中文规格书,Datasheet资料

Notes: x = Lot code GE3 and GE4 denote halogen-free and RoHS compliant

ABSOLUTE MAXIMUM RATINGS

Parameter Supply Input Voltage (VIN) Enable Input Voltage (VEN) Output Voltage (VOUT) Maximum Continuous Switch Current (Imax.) Maximum Pulsed Current (IDM) VIN (Pulsed at 1 ms, 10 % Duty Cycle) ESD Rating (HBM) Junction Temperature (TJ) Thermal Resistance (JA)a Power Dissipation (PD)a 6 pin SC70-6b 4 pin TDFN4 1.2 mm x 1.6 mmc 6 pin SC70-6b 4 pin TDFN4 1.2 mm x 1.6 mmc SC70-6 package TDFN4 1.2 mm x 1.6 mm SC70-6 package TDFN4 1.2 mm x 1.6 mm Limit - 0.3 to 6 - 0.3 to 6 - 0.3 to VIN + 0.3 1.8 2.4 2.2 3 4000 - 40 to 125 240 170 230 324 V °C °C/W mW A V Unit

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

SL838

Infrared Receiver Head 红外线接收头

1.特性

●小型设计;●内置专用IC;

●宽角度及长距离接收;●抗干扰能力强;

●能抵于环境光线影响;●低电压工作;

2.应用:

■视听器材(音响,电视,录影机,碟机、机顶盒、DVB)■家庭电器(冷气机,电风扇,电灯)■其他无线遥控器产品;

外型尺寸及引脚排列图

3.

应用电路图:

4.

原理图:

型号:SL838

5.

6.测试波型:

7.极限参数:

8.接收角度图:

9.推荐使用条件

10.使用注意

1)在无任何外加压力及影响品质的环境下储存及使用;

2)在无污染性气体或海风(含盐分)的环境下储存及使用;

3)请勿清洗本产品,在低湿度环境下储存及使用;

4)在规定的条件下焊接引线管脚,请勿施加外力;

5)使用前,请先用静电带将作业员及电烙铁连接到静电地线;

6)请注意保护红外线接收头的接收面,勿触碰,玷污或磨损后会影响接收效果。

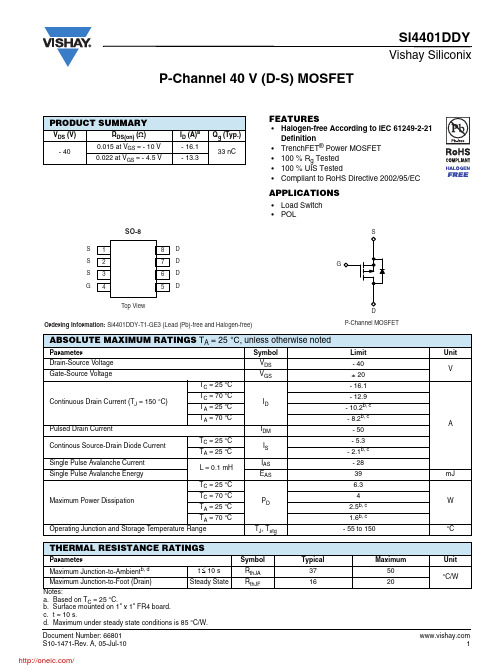

SI4401DDY-T1-GE3;中文规格书,Datasheet资料

0.024 V GS = 4.5 V 0.018 V GS = 10 V 0.012

C - Capacitance (pF)

3600 Ciss 2700

1800

0.006

900

Coss Crss

0 0 10 20 30 40 50

0 0 8 16 24 32 40

ID - Drain Current (A)

0.5

1.0

1.5

2.0

VDS - Drain-to-Source Voltage (V)

VGS - Gate-to-Source Voltage (V)

Output Characteristics

0.030 4500

Transfer Characteristics

RDS(on) - On-Resistance (Ω)

50 V GS = 10 V thru 5 V 40

ID - Drain Current (A)

10

V GS = 4 V

ID - Drain Current (A)

8

30

6

20

4 T C = 25 °C 2

10 V GS = 3 V 0 0.0

T C = 125 °C 0 T C = - 55 °C 0 1 2 3 4

• Halogen-free According to IEC 61249-2-21 Definition • TrenchFET® Power MOSFET • 100 % Rg Tested • 100 % UIS Tested • Compliant to RoHS Directive 2002/95/EC

Si4401DDY

Vishay Siliconix

产品规格承认书

产品规格承认书热释电红外传感器系列产品规格承认书SIR301B特点* 高灵敏度和优越的信噪比* 对温度变化的高稳定性* 抗干扰能力强(例如振动,射频干扰等.) * 优越的性价比应用1.安全2.照明器具3.家庭和其他领域1.使用范围本文书使用于被动式热释电红外传感器输出装置2.传感器输出形式平衡差动型3.品名及品号3.1品名热释电红外传感器3.2品号SIR301B4. 外形及尺寸4.1 外观表面光洁,无划伤,污渍,生锈等现象。

4.2外形及尺寸TO-5 : 具体尺寸详见图15. 电性能参数(环境温度 25ºC )6. 光学性能参数 7.环境性能参数8.检验项目8.1 制程检验全检:项目5电性能参数,包括5.1~5.3,5.5项。

8.2 发货检验发货前按照发货抽检标准对项目5的5.1~5.3,5.5项和项目4的4.1,4.2项进行抽检。

9.包装货物包装牢固,无破损现象。

10.不合格品处理在收货,过程检验中,发现不合格产品,双方对此进行协商处理。

11. 协议事项本协议内容的变更必须经过双方协商,并出具文字文件确认。

图1 尺寸规格图热释电红外传感器测试方法测量条件♦环境温度 25ºC♦黑体温度 420K♦调制频率 1赫兹, 0.3~3.5赫兹△f,♦放大倍数 72.5 dB图2 热释电测试方法图3 平衡度测试方法双元传感器的灵敏平衡度是通过测量每个单元的灵敏度(即单个输出峰值电压),并采用下列公式计算得出。

平衡度 = |VA-VB|/(VA+VB) ×100%VA = A面的灵敏度 ( mVp-p )VB = B面的灵敏度 ( mVp-p )基本测试电路图4 基本测试电路入射视角图图5 入射视角窗口材料的可接收通过波长图6 滤光片光谱特性包装方式:元件包装图纸(单位:mm)卡纸内装传感器100只包装盒外纸箱包装图纸(单位:mm)小包装箱390*260*145,包装传感器30*100=3000只。

SIR426DP-T1-GE3;中文规格书,Datasheet资料

Vishay SiliconixSiR426DPN-Channel 40-V (D-S) MOSFETFEATURES•Halogen-free According to IEC 61249-2-21Definition•TrenchFET ® Power MOSFET •100 % R g Tested •100 % UIS Tested•Compliant to RoHS Directive 2002/95/ECAPPLICATIONS•DC/DC Converters- Synchronous Buck - Synchronous RectifierPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)Q g (Typ.)400.0105 at V GS = 10 V 30a 9.3 nC0.0125 at V GS = 4.5 V30aNotes:a.Based on T C = 25 °C. Package limited.b.Surface Mounted on 1" x 1" FR4 board.c.t = 10 s.d. See Solder Profile (/ppg?73257). The PowerPAK SO-8 is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.e.Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components.f.Maximum under Steady State conditions is 70 °C/W.ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameter Symbol Limit Unit Drain-Source Voltage V DS 40VGate-Source Voltage V GS ± 20Continuous Drain Current (T J = 150 °C)T C = 25 °C I D 30a AT C = 70 °C 30aT A = 25 °C 15.9b, cT A = 70 °C 12.8b, cPulsed Drain Current I DM 70Avalanche Current L = 0.1 mHI AS 20Avalanche Energy E AS 20mJ Continuous Source-Drain Diode Current T C = 25 °C I S30a A T A = 25 °C 4b, c Maximum Power DissipationT C = 25 °C P D 41.7W T C = 70 °C 26.7T A = 25 °C 4.8b, c T A = 70 °C 3.1b, cOperating Junction and Storage T emperature Range T J , T stg - 55 to 150°C Soldering Recommendations (Peak Temperature)d, e 260THERMAL RESISTANCE RATINGSParameter Symbol Typical MaximumUnitMaximum Junction-to-Ambient b, f t ≤ 10 s R thJA2126°C/WMaximum Junction-to-Case (Drain)Steady StateR thJC 2.4 3.0Vishay SiliconixSiR426DPNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS T J = 25 °C, unless otherwise notedParameter Symbol Test Conditions Min. Typ.Max.UnitStaticDrain-Source Breakdown Voltage V DS V GS = 0 V , I D = 250 µA40V V DS Temperature Coefficient ΔV DS /T J I D = 250 µA47mV/°C V GS(th) T emperature Coefficient ΔV GS(th)/T J - 5.4Gate-Source Threshold Voltage V GS(th)V DS = V GS , I D = 250 µA 1.2 2.5V Gate-Source LeakageI GSS V DS = 0 V , V GS = ± 20 V ± 100nA Zero Gate Voltage Drain Current I DSS V DS = 40 V , V GS = 0 V 1µA V DS = 40 V , V GS = 0 V , T J = 55 °C5On-State Drain Current aI D(on) V DS ≥ 5 V, V GS = 10 V 30A Drain-Source On-State Resistance a R DS(on)V GS = 10 V , I D = 15 A 0.00850.0105ΩV GS = 4.5 V, I D = 10 A 0.01040.0125Forward T ransconductance a g fsV DS = 15 V , I D = 15 A43SDynamic bInput Capacitance C iss V DS = 20 V , V GS = 0 V, f = 1 MHz1160pFOutput CapacitanceC oss 185Reverse Transfer Capacitance C rss 70Total Gate Charge Q g V DS = 20 V , V GS = 10 V , ID = 10 A 20.531nC V DS = 20 V , V GS = 4.5 V , I D = 10 A 9.314Gate-Source Charge Q gs 3.1Gate-Drain Charge Q gd 2.5Gate Resistance R g f = 1 MHz0.20.8 1.6ΩTurn-On Delay Time t d(on) V DD = 20 V , R L = 2 ΩI D ≅ 10 A, V GEN = 4.5 V , R g = 1 Ω1835ns Rise Timet r 1530Turn-Off Delay Time t d(off) 1835Fall Timet f 1020Turn-On Delay Time t d(on) V DD = 20 V , R L = 2 ΩI D ≅ 10 A, V GEN = 10 V , R g = 1 Ω918Rise Timet r 918Turn-Off Delay Time t d(off) 1835Fall Timet f816Drain-Source Body Diode Characteristics Continuous Source-Drain Diode Current I S T C = 25 °C30A Pulse Diode Forward Current I SM 70Body Diode VoltageV SD I S = 4.0 A, V GS = 0 V0.77 1.2V Body Diode Reverse Recovery Time t rr I F = 10 A, dI/dt = 100 A/µs, T J = 25 °C2345ns Body Diode Reverse Recovery Charge Q rr 1938nC Reverse Recovery Fall Time t a 14nsReverse Recovery Rise Timet b9Vishay Siliconix SiR426DPOn-Resistance vs. Drain Current and Gate VoltageGate ChargeThreshold VoltageSingle Pulse Power (Junction-to-Ambient)Vishay SiliconixSiR426DPTYPICAL CHARACTERISTICS 25 °C, unless otherwise noted* The power dissipation P D is based on T J(max) = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.Power, Junction-to-CasePower, Junction-to-AmbientSiR426DPVishay SiliconixTYPICAL CHARACTERISTICS 25 °C, unless otherwise notedVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?65162.Package InformationVishay Siliconix PowerPAK® SO-8, (SINGLE/DUAL)MILLIMETERS INCHES DIM.MIN.NOM.MAX.MIN.NOM.MAX.A0.97 1.04 1.120.0380.0410.044A10.00-0.050.000-0.002b0.330.410.510.0130.0160.020c0.230.280.330.0090.0110.013D 5.05 5.15 5.260.1990.2030.207D1 4.80 4.90 5.000.1890.1930.197D2 3.56 3.76 3.910.1400.1480.154D3 1.32 1.50 1.680.0520.0590.066D40.57 TYP.0.0225 TYP.D5 3.98 TYP.0.157 TYP.E 6.05 6.15 6.250.2380.2420.246E1 5.79 5.89 5.990.2280.2320.236E2 3.48 3.66 3.840.1370.1440.151E3 3.68 3.78 3.910.1450.1490.154E40.75 TYP.0.030 TYP.e 1.27 BSC0.050 BSCK 1.27 TYP.0.050 TYP.K10.56--0.022--H0.510.610.710.0200.0240.028L0.510.610.710.0200.0240.028L10.060.130.200.0020.0050.008θ0°-12°0°-12°W0.150.250.360.0060.0100.014M0.125 TYP.0.005 TYP.ECN: T10-0055-Rev. J, 15-Feb-10DWG: 5881Vishay SiliconixAN821PowerPAK ® SO-8 Mounting and Thermal ConsiderationsWharton McDanielMOSFETs for switching applications are now available with die on resistances around 1 m Ω and with the capability to handle 85 A. While these die capabilities represent a major advance over what was available just a few years ago, it is important for power MOSFET packaging technology to keep pace. It should be obvi-ous that degradation of a high performance die by the package is undesirable. PowerPAK is a new package technology that addresses these issues. In this appli-cation note, PowerPAK’s construction is described.Following this mounting information is presented including land patterns and soldering profiles for max-imum reliability. Finally, thermal and electrical perfor-mance is discussed.THE PowerPAK PACKAGEThe PowerPAK package was developed around the SO-8 package (Figure 1). The PowerPAK SO-8 uti-lizes the same footprint and the same pin-outs as the standard SO-8. This allows PowerPAK to be substi-tuted directly for a standard SO-8 package. Being a leadless package, PowerPAK SO-8 utilizes the entire SO-8 footprint, freeing space normally occupied by the leads, and thus allowing it to hold a larger die than a standard SO-8. In fact, this larger die is slightly larger than a full sized DPAK die. The bottom of the die attach pad is exposed for the purpose of providing a direct,low resistance thermal path to the substrate the device is mounted on. Finally, the package height is lower than the standard SO-8, making it an excellent choice for applications with space constraints.PowerPAK SO-8 SINGLE MOUNTINGThe PowerPAK single is simple to use. The pin arrangement (drain, source, gate pins) and the pin dimensions are the same as standard SO-8 devices (see Figure 2). Therefore, the PowerPAK connection pads match directly to those of the SO-8. The only dif-ference is the extended drain connection area. To take immediate advantage of the PowerPAK SO-8 single devices, they can be mounted to existing SO-8 land patterns.The minimum land pattern recommended to take full advantage of the PowerPAK thermal performance see Application Note 826, Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Sili-conix MOSFETs . Click on the PowerPAK SO-8 single in the index of this document.In this figure, the drain land pattern is given to make full contact to the drain pad on the PowerPAK package.This land pattern can be extended to the left, right, and top of the drawn pattern. This extension will serve to increase the heat dissipation by decreasing the ther-mal resistance from the foot of the PowerPAK to the PC board and therefore to the ambient. Note that increasing the drain land area beyond a certain point will yield little decrease in foot-to-board and foot-to-ambient thermal resistance. Under specific conditions of board configuration, copper weight and layer stack,experiments have found that more than about 0.25 to 0.5 in 2 of additional copper (in addition to the drain land) will yield little improvement in thermal perfor-mance.Figure 1.PowerPAK 1212 DevicesFigure 2.Standard SO-8Pow erPAK SO-8Vishay SiliconixAN821PowerPAK SO-8 DUALThe pin arrangement (drain, source, gate pins) and the pin dimensions of the PowerPAK SO-8 dual are the same as standard SO-8 dual devices. Therefore, the PowerPAK device connection pads match directly to those of the SO-8. As in the single-channel package,the only exception is the extended drain connection area. Manufacturers can likewise take immediate advantage of the PowerPAK SO-8 dual devices by mounting them to existing SO-8 dual land patterns.To take the advantage of the dual PowerPAK SO-8’s thermal performance, the minimum recommended land pattern can be found in Application Note 826,Recommended Minimum Pad Patterns With Outline Drawing Access for Vishay Siliconix MOSFETs . Click on the PowerPAK 1212-8 dual in the index of this doc-ument.The gap between the two drain pads is 24 mils. This matches the spacing of the two drain pads on the Pow-erPAK SO-8 dual package.REFLOW SOLDERINGVishay Siliconix surface-mount packages meet solder reflow reliability requirements. Devices are subjected to solder reflow as a test preconditioning and are then reliability-tested using temperature cycle, bias humid-ity, HAST, or pressure pot. The solder reflow tempera-ture profile used, and the temperatures and time duration, are shown in Figures 3 and 4.For the lead (Pb)-free solder profile, see /doc?73257.Ramp-Up Rate+ 6 °C /Second Maximum Temperature at 155 ± 15 °C 120 Seconds Maximum Temperature Above 180 °C 70 - 180 Seconds Maximum T emperature 240 + 5/- 0 °CTime at Maximum T emperature 20 - 40 SecondsRamp-Down Rate+ 6 °C/Second MaximumFigure 3. Solder Reflow Temperature ProfileFigure 3.Solder Reflow Temperatures and Time DurationsVishay SiliconixAN821THERMAL PERFORMANCE IntroductionA basic measure of a device’s thermal performance is the junction-to-case thermal resistance, R θjc , or the junction-to-foot thermal resistance, R θjf . This parameter is measured for the device mounted to an infinite heat sink and is therefore a characterization of the device only, in other words, independent of the properties of the object to which the device is mounted. Table 1 shows a comparison of the DPAK, PowerPAK SO-8, and stan-dard SO-8. The PowerPAK has thermal performance equivalent to the DPAK, while having an order of magni-tude better thermal performance over the SO-8. Thermal Performance on Standard SO-8 Pad Pattern Because of the common footprint, a PowerPAK SO-8can be mounted on an existing standard SO-8 pad pat-tern. The question then arises as to the thermal perfor-mance of the PowerPAK device under these conditions.A characterization was made comparing a standard SO-8and a PowerPAK device on a board with a trough cut out underneath the PowerPAK drain pad. This configuration restricted the heat flow to the SO-8 land pads. The results are shown in Figure 5.Because of the presence of the trough, this result sug-gests a minimum performance improvement of 10 °C/W by using a PowerPAK SO-8 in a standard SO-8 PC board mount.The only concern when mounting a PowerPAK on a standard SO-8 pad pattern is that there should be no traces running between the body of the MOSFET.Where the standard SO-8 body is spaced away from the pc board, allowing traces to run underneath, the Power-PAK sits directly on the pc board.Thermal Performance - Spreading CopperDesigners may add additional copper, spreading cop-per, to the drain pad to aid in conducting heat from a device. It is helpful to have some information about the thermal performance for a given area of spreading cop-per.Figure 6 shows the thermal resistance of a PowerPAK SO-8 device mounted on a 2-in. 2-in., four-layer FR-4PC board. The two internal layers and the backside layer are solid copper. The internal layers were chosen as solid copper to model the large power and ground planes common in many applications. The top layer was cut back to a smaller area and at each step junction-to-ambient thermal resistance measurements were taken.The results indicate that an area above 0.3 to 0.4 square inches of spreading copper gives no additional thermal performance improvement. A subsequent experiment was run where the copper on the back-side was reduced, first to 50 % in stripes to mimic circuit traces,and then totally removed. No significant effect was observed.TABLE 1.DPAK and PowerPAK SO-8Equivalent Steady State PerformanceDPAKPowerPAKSO-8 Standard SO-8 Thermal Resistance R θjc1.2 °C/W1.0 °C/W16 °C/WFigure 5. PowerPAK SO-8 and Standard SO-0 Land Pad Thermal PathFigure 6. Spreading Copper Junction-to-Ambient PerformanceR th v s. Spreading Copper (0 %, 50 %, 100 % Back Copper))s t t a w /C ( e c n a d e p m I 0.0056514641360.250.500.751.001.251.501.752.000 %50 %100 %分销商库存信息: VISHAYSIR426DP-T1-GE3。

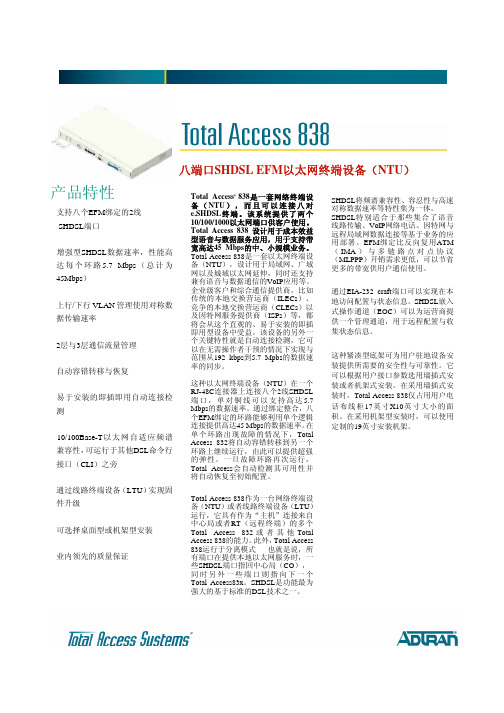

TA838中文

产品特性■支持八个EFM 绑定的2线SHDSL 端口■增强型SHDSL 数据速率,性能高达每个环路5.7 Mbps (总计为45Mbps )■上行/下行VLAN 管理使用对称数据传输速率■2层与3层通信流量管理■自动容错转移与恢复■易于安装的即插即用自动连接检测■10/100Base-T 以太网自适应频谱兼容性,可运行于其他DSL 命令行接口(CLI )之旁■通过线路终端设备(LTU )实现固件升级■可选择桌面型或机架型安装■业内领先的质量保证Total Access ®838是一套网络终端设备(NTU ),而且可以连接八对e.SHDSL 终端。

该系统提供了两个10/100/1000以太网端口供客户使用。

Total Access 838 设计用于成本效益型语音与数据服务应用,用于支持带宽高达45 Mbps 的中、小规模业务。

Total Access 838是一套以太网终端设备(NTU ),设计用于局域网、广域网以及城域以太网延伸,同时还支持兼有语音与数据通信的VoIP 应用等。

企业级客户和综合通信提供商,比如传统的本地交换营运商(ILECs )、竞争的本地交换营运商(CLECs )以及因特网服务提供商(ISPs )等,都将会从这个直观的、易于安装的即插即用型设备中受益。

该设备的另外一个关键特性就是自动连接检测,它可以在无需操作者干预的情况下实现与范围从192 kbps 到5.7 Mpbs 的数据速率的同步。

这种以太网终端设备(NTU )在一个 RJ-48C 连接器上连接八个2线SHDSL 端口,单对铜线可以支持高达5.7 Mbps 的数据速率。

通过绑定整合,八个EFM 绑定的环路能够利用单个逻辑连接提供高达45 Mbps 的数据速率。

在单个环路出现故障的情况下,Total Access 832将自动容错转移到另一个环路上继续运行,由此可以提供超强 的弹性。

一旦故障环路再次运行,Total Access 会自动检测其可用性并将自动恢复至初始配置。

SI2343DS-T1-GE3;中文规格书,Datasheet资料