TIM7785-35SL中文资料

LM2578AM资料

LM2578A/LM3578A Switching RegulatorGeneral DescriptionThe LM2578A is a switching regulator which can easily be set up for such DC-to-DC voltage conversion circuits as the buck,boost,and inverting configurations.The LM2578A fea-tures a unique comparator input stage which not only has separate pins for both the inverting and non-inverting inputs, but also provides an internal1.0V reference to each input, thereby simplifying circuit design and p.c.board layout.The output can switch up to750mA and has output pins for its collector and emitter to promote design flexibility.An external current limit terminal may be referenced to either the ground or the V in terminal,depending upon the application.In addi-tion,the LM2578A has an on board oscillator,which sets the switching frequency with a single external capacitor from<1 Hz to100kHz(typical).The LM2578A is an improved version of the LM2578,offer-ing higher maximum ratings for the total supply voltage and output transistor emitter and collector voltages.Featuresn Inverting and non-inverting feedback inputsn 1.0V reference at inputsn Operates from supply voltages of2V to40Vn Output current up to750mA,saturation less than0.9V n Current limit and thermal shut downn Duty cycle up to90%Applicationsn Switching regulators in buck,boost,inverting,and single-ended transformer configurationsn Motor speed controln Lamp flasherConnection Diagram and Ordering InformationDual-In-Line Package00871129Order Number LM3578AM,LM2578AN or LM3578ANSee NS Package Number M08A or N08E February2005LM2578A/LM3578A Switching Regulator©2005National Semiconductor Corporation Functional Diagram00871101L M 2578A /L M 3578A 2Absolute Maximum Ratings(Note1) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Total Supply Voltage50V Collector Output to Ground−0.3V to+50V Emitter Output to Ground(Note2)−1V to+50V Power Dissipation(Note3)Internally limited Output Current750mA Storage Temperature−65˚C to+150˚C Lead Temperature(soldering,10seconds)260˚C Maximum Junction Temperature150˚CESD Tolerance(Note4)2kVOperating RatingsAmbient Temperature RangeLM2578A−40˚C≤T A≤+85˚C LM3578A0˚C≤T A≤+70˚C Junction Temperature RangeLM2578A−40˚C≤T J≤+125˚C LM3578A0˚C≤T J≤+125˚CElectrical CharacteristicsThese specifications apply for2V≤V IN≤40V(2.2V≤V IN≤40V for T J≤−25˚C),timing capacitor C T=3900pF,and25%≤duty cycle≤75%,unless otherwise specified.Values in standard typeface are for T J=25˚C;values in boldface type apply for operation over the specified operating junction temperature range.LM2578A/Symbol Parameter Conditions Typical LM3578A Units(Note5)Limit(Note6) OSCILLATORf OSC Frequency20kHz24kHz(max)16kHz(min)∆f OSC/∆T Frequency Drift with Temperature−0.13%/˚C Amplitude550mV p-p REFERENCE/COMPARATOR(Note7)V R Input Reference I1=I2=0mA and 1.0V Voltage I1=I2=1mA±1%(Note8) 1.050/1.070V(max)0.950/0.930V(min)∆V R/∆V IN Input Reference Voltage LineRegulationI1=I2=0mA and0.003%/VI1=I2=1mA±1%(Note8)0.01/0.02%/V(max) I INV Inverting Input Current I1=I2=0mA,duty cycle=25%0.5µALevel Shift Accuracy Level Shift Current=1mA 1.0%10/13%(max)∆V R/∆t Input Reference Voltage Long TermStability100ppm/1000h OUTPUTV C(sat)Collector Saturation Voltage I C=750mA pulsed,Emittergrounded 0.7V0.90/1.2V(max)V E(sat)Emitter Saturation Voltage I O=80mA pulsed, 1.4VV IN=V C=40V 1.7/2.0V(max)I CES Collector Leakage Current V IN=V CE=40V,Emitter grounded,Output OFF 0.1µA200/250µA(max)BV CEO(SUS)Collector-Emitter Sustaining Voltage I SUST=0.2A(pulsed),V IN=060V50V(min) CURRENT LIMITV CL Sense Voltage Shutdown Level Referred to V IN or Ground110mV(Note9)80mV(min)160mV(max)LM2578A/LM3578A3Electrical Characteristics(Continued)These specifications apply for 2V ≤V IN ≤40V (2.2V ≤V IN ≤40V for T J ≤−25˚C),timing capacitor C T =3900pF,and 25%≤duty cycle ≤75%,unless otherwise specified.Values in standard typeface are for T J =25˚C;values in boldface type apply for operation over the specified operating junction temperature range.LM2578A/Symbol ParameterConditionsTypical LM3578A Units(Note 5)Limit (Note 6)CURRENT LIMIT ∆V CL /∆T Sense Voltage Temperature Drift 0.3%/˚C I CLSense Bias CurrentReferred to V IN 4.0µA Referred to ground0.4µA DEVICE POWER CONSUMPTION I SSupply CurrentOutput OFF,V E =0V2.0mA3.5/4.0mA (max)Output ON,I C =750mA pulsed,14mAV E =0VNote 1:Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.Note 2:For T J ≥100˚C,the Emitter pin voltage should not be driven more than 0.6V below ground (see Application Information).Note 3:At elevated temperatures,devices must be derated based on package thermal resistance.The device in the 8-pin DIP must be derated at 95˚C/W,junction to ambient.The device in the surface-mount package must be derated at 150˚C/W,junction-to-ambient.Note 4:Human body model,1.5k Ωin series with 100pF.Note 5:Typical values are for T J =25˚C and represent the most likely parametric norm.Note 6:All limits guaranteed at room temperature (standard type face)and at temperature extremes (bold type face).Room temperature limits are 100%production tested.Limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC)methods.All limits are used to calculate AOQL.Note 7:Input terminals are protected from accidental shorts to ground but if external voltages higher than the reference voltage are applied,excessive current will flow and should be limited to less than 5mA.Note 8:I 1and I 2are the external sink currents at the inputs (refer to Test Circuit).Note 9:Connection of a 10k Ωresistor from pin 1to pin 4will drive the duty cycle to its maximum,typically 90%.Applying the minimum Current Limit Sense Voltage to pin 7will not reduce the duty cycle to less than 50%.Applying the maximum Current Limit Sense Voltage to pin 7is certain to reduce the duty cycle below 50%.Increasing this voltage by 15mV may be required to reduce the duty cycle to 0%,when the Collector output swing is 40V or greater (see Ground-Referred Current Limit Sense Voltage typical curve).Typical Performance CharacteristicsOscillator Frequency Changewith TemperatureOscillator Voltage Swing0087113200871133L M 2578A /L M 3578A 4Typical Performance Characteristics(Continued)Input Reference Voltage Drift with TemperatureCollector Saturation Voltage(Sinking Current,Emitter Grounded)0087113400871135Emitter Saturation Voltage(Sourcing Current,Collector at V in )Ground ReferredCurrent Limit Sense Voltage0087113600871137Current Limit Sense Voltage Drift with Temperature Current Limit Response Time for Various Over Drives0087113800871139LM2578A/LM3578A5Typical Performance Characteristics(Continued)Current Limit Sense Voltagevs Supply VoltageSupply Current0087114000871141Supply CurrentCollector Current with Emitter Output Below Ground0087114200871143Test Circuit*Parameter tests can be made using the test circuit shown.Select the desired V in ,collector voltage and duty cycle with adjustable power supplies.A digital volt meter with an input resistance greater than 100M Ωshould be used to measure the following:Input Reference Voltage to Ground;S1in either position.Level Shift Accuracy (%)=(T P3(V)/1V)x 100%;S1at I 1=I 2=1mAInput Current (mA)=(1V −T p3(V))/1M Ω:S1at I 1=I 2=0mA.Oscillator parameters can be measured at T p4using a fre-quency counter or an oscilloscope.The Current Limit Sense Voltage is measured by connecting an adjustable 0-to-1V floating power supply in series with the current limit terminal and referring it to either the ground or the V in terminal.Set the duty cycle to 90%and monitor test point T P5while adjusting the floating power supply voltage until the LM2578A’s duty cycle just reaches 0%.This voltage is the Current Limit Sense Voltage.The Supply Current should be measured with the duty cycle at 0%and S1in the I 1=I 2=0mA position.*LM2578A specifications are measured using automated test equipment.This circuit is provided for the customer’s convenience when checking parameters.Due to possible variations in testing conditions,the measured values from these testing procedures may not match those of the factory.L M 2578A /L M 3578A 6Test Circuit*(Continued)00871103 Op amp supplies are±15VDVM input resistance>100MΩ*LM2578max duty cycle is90%Definition of TermsInput Reference Voltage:The voltage(referred to ground) that must be applied to either the inverting or non-inverting input to cause the regulator switch to change state(ON or OFF).Input Reference Current:The current that must be drawn from either the inverting or non-inverting input to cause the regulator switch to change state(ON or OFF).Input Level Shift Accuracy:This specification determines the output voltage tolerance of a regulator whose output control depends on drawing equal currents from the inverting and non-inverting inputs(see the Inverting Regulator of Fig-ure21,and the RS-232Line Driver Power Supply of Figure 23).Level Shift Accuracy is tested by using two equal-value resistors to draw current from the inverting and non-inverting input terminals,then measuring the percentage difference in the voltages across the resistors that produces a controlled duty cycle at the switch output.Collector Saturation Voltage:With the inverting input ter-minal grounded thru a10kΩresistor and the output transis-tor’s emitter connected to ground,the Collector Saturation-Voltage is the collector-to-emitter voltage for a given collector current.Emitter Saturation Voltage:With the inverting input termi-nal grounded thru a10kΩresistor and the output transistor’s collector connected to V in,the Emitter Saturation Voltage is the collector-to-emitter voltage for a given emitter current. Collector Emitter Sustaining Voltage:The collector-emitter breakdown voltage of the output transistor,mea-sured at a specified current.Current Limit Sense Voltage:The voltage at the CurrentLimit pin,referred to either the supply or the ground terminal,which(via logic circuitry)will cause the output transistor toturn OFF and resets cycle-by-cycle at the oscillator fre-quency.Current Limit Sense Current:The bias current for theCurrent Limit terminal with the applied voltage equal to theCurrent Limit Sense Voltage.Supply Current:The IC power supply current,excluding thecurrent drawn through the output transistor,with the oscilla-tor operating.Functional DescriptionThe LM2578A is a pulse-width modulator designed for useas a switching regulator controller.It may also be used inother applications which require controlled pulse-width volt-age drive.A control signal,usually representing output voltage,fed intothe LM2578A’s comparator is compared with an internally-generated reference.The resulting error signal and the os-cillator’s output are fed to a logic network which determineswhen the output transistor will be turned ON or OFF.Thefollowing is a brief description of the subsections of theLM2578A.COMPARATOR INPUT STAGEThe LM2578A’s comparator input stage is unique in that boththe inverting and non-inverting inputs are available to theuser,and both contain a1.0V reference.This is accom-plished as follows:A1.0V reference is fed into a modifiedvoltage follower circuit(see FUNCTIONAL DIAGRAM).When both input pins are open,no current flows through R1LM2578A/LM3578A7Functional Description(Continued)and R2.Thus,both inputs to the comparator will have the potential of the 1.0V reference,V A .When one input,for example the non-inverting input,is pulled ∆V away from V A ,a current of ∆V/R1will flow through R1.This same current flows through R2,and the comparator sees a total voltage of 2∆V between its inputs.The high gain of the system,through feedback,will correct for this imbalance and return both inputs to the 1.0V level.This unusual comparator input stage increases circuit flex-ibility,while minimizing the total number of external compo-nents required for a voltage regulator system.The inverting switching regulator configuration,for example,can be set up without having to use an external op amp for feedback polarity reversal (see TYPICAL APPLICATIONS).OSCILLATORThe LM2578A provides an on-board oscillator which can be adjusted up to 100kHz.Its frequency is set by a single external capacitor,C 1,as shown in Figure 1,and follows the equationf OSC =8x10−5/C 1The oscillator provides a blanking pulse to limit maximum duty cycle to 90%,and a reset pulse to the internal circuitry.OUTPUT TRANSISTORThe output transistor is capable of delivering up to 750mA with a saturation voltage of less than 0.9V.(see Collector Saturation Voltage and Emitter Saturation Voltage curves).The emitter must not be pulled more than 1V below ground (this limit is 0.6V for T J ≥100˚C).Because of this limit,an external transistor must be used to develop negative output voltages (see the Inverting Regulator Typical Application).Other configurations may need protection against violation of this limit (see the Emitter Output section of the Applica-tions Information).CURRENT LIMITThe LM2578A’s current limit may be referenced to either the ground or the V in pins,and operates on a cycle-by-cycle basis.The current limit section consists of two comparators:one with its non-inverting input referenced to a voltage 110mV below V in ,the other with its inverting input referenced110mV above ground (see FUNCTIONAL DIAGRAM).The current limit is activated whenever the current limit terminal is pulled 110mV away from either V in or ground.Applications InformationCURRENT LIMITAs mentioned in the functional description,the current limit terminal may be referenced to either the V in or the ground terminal.Resistor R3converts the current to be sensed into a voltage for current limit detection.CURRENT LIMIT TRANSIENT SUPPRESSIONWhen noise spikes and switching transients interfere with proper current limit operation,R1and C1act together as a low pass filter to control the current limit circuitry’s response time.Because the sense current of the current limit terminal varies according to where it is referenced,R1should be less than 2k Ωwhen referenced to ground,and less than 100Ωwhen referenced to V in .00871104FIGURE 1.Value of Timing Capacitor vsOscillator Frequency00871115FIGURE 2.Current Limit,Ground Referred00871116FIGURE 3.Current Limit,V in ReferredL M 2578A /L M 3578A 8Applications Information(Continued)C.L.SENSE VOLTAGE MULTIPLICATIONWhen a larger sense resistor value is desired,the voltage divider network,consisting of R1and R2,may be used.This effectively multiplies the sense voltage by(1+R1/R2).Also, R1can be replaced by a diode to increase current limit sense voltage to about800mV(diode V f+110mV).UNDER-VOLTAGE LOCKOUTUnder-voltage lockout is accomplished with few external components.When V in becomes lower than the zener breakdown voltage,the output transistor is turned off.This occurs because diode D1will then become forward biased, allowing resistor R3to sink a greater current from the non-inverting input than is sunk by the parallel combination of R1 and R2at the inverting terminal.R3should be one-fifth of the value of R1and R2in parallel.MAXIMUM DUTY CYCLE LIMITINGThe maximum duty cycle can be externally limited by adjust-ing the charge to discharge ratio of the oscillator capacitor with a single external resistor.Typical values are50µA for the charge current,450µA for the discharge current,and a voltage swing from200mV to750mV.Therefore,R1is selected for the desired charging and discharging slopes and C1is readjusted to set the oscillator frequency.00871117 FIGURE4.Current Limit Transient Suppressor,Ground Referred00871118 FIGURE5.Current Limit Transient Suppressor,V in Referred00871119 FIGURE6.Current Limit Sense Voltage Multiplication,Ground Referred00871120FIGURE7.Current Limit Sense Voltage Multiplication,V in Referred00871122FIGURE8.Under-Voltage LockoutLM2578A/LM3578A9Applications Information(Continued)DUTY CYCLE ADJUSTMENTWhen manual or mechanical selection of the output transis-tor’s duty cycle is needed,the cirucit shown below may be used.The output will turn on with the beginning of each oscillator cycle and turn off when the current sunk by R2and R3from the non-inverting terminal becomes greater than the current sunk from the inverting terminal.With the resistor values as shown,R3can be used to adjust the duty cycle from 0%to 90%.When the sum of R2and R3is twice the value of R1,the duty cycle will be about 50%.C1may be a large electrolytic capacitor to lower the oscillator frequency below 1Hz.REMOTE SHUTDOWNThe LM2578A may be remotely shutdown by sinking a greater current from the non-inverting input than from the inverting input.This may be accomplished by selecting re-sistor R3to be approximately one-half the value of R1and R2in parallel.EMITTER OUTPUTWhen the LM2578A output transistor is in the OFF state,if the Emitter output swings below the ground pin voltage,the output transistor will turn ON because its base is clamped near ground.The Collector Current with Emitter Output Be-low Ground curve shows the amount of Collector current drawn in this mode,vs temperature and Emitter voltage.When the Collector-Emitter voltage is high,this current will cause high power dissipation in the output transistor and should be avoided.This situation can occur in the high-current high-voltage buck application if the Emitter output is used and the catch diode’s forward voltage drop is greater than 0.6V.A fast-recovery diode can be added in series with the Emitter output to counter the forward voltage drop of the catch diode (see Figure 2).For better efficiency of a high output current buck regulator,an external PNP transistor should be used as shown in Figure 16.SYNCHRONIZING DEVICESWhen several devices are to be operated at once,their oscillators may be synchronized by the application of an external signal.This drive signal should be a pulse waveform with a minimum pulse width of 2µs.and an amplitude from00871121FIGURE 9.Maximum Duty Cycle Limiting00871123FIGURE 10.Duty Cycle Adjustment00871124FIGURE 11.Shutdown Occurs when V L is High00871130FIGURE 12.D1Prevents Output Transistor from Improperly Turning ON due to D2’s Forward Voltage L M 2578A /L M 3578A 10Applications Information(Continued)1.5V to2.0V.The signal source must be capable of 1.)driving capacitive loads and 2.)delivering up to 500µA for each LM2578A.Capacitors C1thru CN are to be selected for a 20%slower frequency than the synchronization frequency.Typical ApplicationsThe LM2578A may be operated in either the continuous or the discontinuous conduction mode.The following applica-tions (except for the Buck-Boost Regulator)are designed for continuous conduction operation.That is,the inductor cur-rent is not allowed to fall to zero.This mode of operation has higher efficiency and lower EMI characteristics than the dis-continuous mode.BUCK REGULATORThe buck configuration is used to step an input voltage down to a lower level.Transistor Q1in Figure 14chops the input DC voltage into a squarewave.This squarewave is then converted back into a DC voltage of lower magnitude by the low pass filter consisting of L1and C1.The duty cycle,D,of the squarewave relates the output voltage to the input volt-age by the following equation:V out =D x V in =V in x (t on )/(t on +t off ).Figure 15is a 15V to 5V buck regulator with an output current,I o ,of 350mA.The circuit becomes discontinuous at 20%of I o(max),has 10mV of output voltage ripple,an effi-ciency of 75%,a load regulation of 30mV (70mA to 350mA)and a line regulation of 10mV (12≤V in ≤18V).Component values are selected as follows:R1=(V o −1)x R2where R2=10k ΩR3=V/I sw(max)R3=0.15Ωwhere:V is the current limit sense voltage,0.11VI sw(max)is the maximum allowable current thru the output transistor.L1is the inductor and may be found from the inductance calculation chart (Figure 16)as follows:Given V in =15VV o =5VI o(max)=350mA f OSC =50kHzDiscontinuous at 20%of I o(max).Note that since the circuit will become discontinuous at 20%of I o(max),the load current must not be allowed to fall below 70mA.00871125FIGURE 13.Synchronizing Devices00871105FIGURE 14.Basic Buck RegulatorLM2578A/LM3578A11Typical Applications(Continued)00871106V in =15V R3=0.15ΩV o =5V C1=1820pF V ripple =10mV C2=220µF I o =350mA C3=20pF f osc =50kHz L1=470µH R1=40k ΩD1=1N5818R2=10k ΩFIGURE 15.Buck or Step-Down RegulatorL M 2578A /L M 3578A 12LM2578A/LM3578A Typical Applications(Continued)00871131FIGURE16.DC/DC Inductance Calculator13Typical Applications(Continued)Step 1:Calculate the maximum DC current through the inductor,I L(max).The necessary equations are indicated at the top of the chart and show that I L(max)=I o(max)for the buck configuration.Thus,I L(max)=350mA.Step 2:Calculate the inductor Volts-sec product,E-T op ,according to the equations given from the chart.For the Buck:E-T op =(V in −V o )(V o /V in )(1000/f osc )=(15−5)(5/15)(1000/50)=66V-µs.with the oscillator frequency,f osc ,expressed in kHz.Step 3:Using the graph with axis labeled “Discontinuous At %I OUT ”and “I L(max,DC)”find the point where the desired maximum inductor current,I L(max,DC)intercepts the desired discontinuity percentage.In this example,the point of interest is where the 0.35A line intersects with the 20%line.This is nearly the midpoint of the horizontal axis.Step 4:This last step is merely the translation of the point found in Step 3to the graph directly below it.This is accom-plished by moving straight down the page to the point which intercepts the desired E-T op .For this example,E-T op is 66V-µs and the desired inductor value is 470µH.Since this example was for 20%discontinuity,the bottom chart could have been used directly,as noted in step 3of the chart instructions.For a full line of standard inductor values,contact Pulse Engineering (San Diego,Calif.)regarding their PE526XX series,or A.I.E.Magnetics (Nashville,Tenn.).A more precise inductance value may be calculated for the Buck,Boost and Inverting Regulators as follows:BUCKL =V o (V in −V o )/(∆I L V in f osc )BOOSTL =V in (V o −V in )/(∆I L f osc V o )INVERTL =V in |V o |/[∆I L (V in +|V o |)f osc ]where ∆I L is the current ripple through the inductor.∆I L is usually chosen based on the minimum load current expected of the circuit.For the buck regulator,since the inductor current I L equals the load current I O ,∆I L =2•I O(min)∆I L =140mA for this circuit.∆I L can also be interpreted as ∆I L =2•(Discontinuity Factor)•I Lwhere the Discontinuity Factor is the ratio of the minimum load current to the maximum load current.For this example,the Discontinuity Factor is 0.2.The remainder of the components of Figure 15are chosen as follows:C1is the timing capacitor found in Figure 1.C2≥V o (V in −V o )/(8f osc 2V in V ripple L1)where V ripple is the peak-to-peak output voltage ripple.C3is necessary for continuous operation and is generally in the 10pF to 30pF range.D1should be a Schottky type diode,such as the 1N5818or 1N5819.BUCK WITH BOOSTED OUTPUT CURRENTFor applications requiring a large output current,an external transistor may be used as shown in Figure 17.This circuit steps a 15V supply down to 5V with 1.5A of output current.The output ripple is 50mV,with an efficiency of 80%,a load regulation of 40mV (150mA to 1.5A),and a line regulation of 20mV (12V ≤V in ≤18V).Component values are selected as outlined for the buck regulator with a discontinuity factor of 10%,with the addition of R4and R5:R4=10V BE1B f /I pR5=(V in −V −V BE1−V sat )B f /(I L(max,DC)+I R4)where:V BE1is the V BE of transistor Q1.V sat is the saturation voltage of the LM2578A output transis-tor.V is the current limit sense voltage.B f is the forced current gain of transistor Q1(B f =30for Figure 17).I R4=V BE1/R4I p =I L(max,DC)+0.5∆I LL M 2578A /L M 3578A 14Typical Applications(Continued)BOOST REGULATORThe boost regulator converts a low input voltage into a higher output voltage.The basic configuration is shown in Figure 18.Energy is stored in the inductor while the transis-tor is on and then transferred with the input voltage to the output capacitor for filtering when the transistor is off.Thus,V o =V in +V in (t on /t off ).The circuit of Figure 19converts a 5V supply into a 15V supply with 150mA of output current,a load regulation of 14mV (30mA to 140mA),and a line regulation of 35mV (4.5V ≤V in ≤8.5V).R1=(V o −1)R2where R2=10k Ω.R3=V/(I L(max,DC)+0.5∆I L )where:∆I L =2(I LOAD(min))(V o /V in )∆I L is 200mA in this example.R4,C3and C4are necessary for continuous operation and are typically 220k Ω,20pF,and 0.0022µF respectively.C1is the timing capacitor found in Figure 1.C2≥I o (V o −V in )/(f osc V o V ripple ).00871108V in =15V R4=200ΩV o =5V R5=330ΩV ripple =50mV C1=1820pF I o =1.5AC2=330µFf osc =50kHz C3=20pF R1=40k ΩL1=220µH R2=10k ΩD1=1N5819R3=0.05ΩQ1=D45FIGURE 17.Buck Converter with Boosted Output Current00871109FIGURE 18.Basic Boost Regulator00871111V in =5V R4=200k ΩV o =15V C1=1820pF V ripple =10mV C2=470µF I o =140mA C3=20pF f osc =50kHz C4=0.0022µF R1=140k ΩL1=330µH R2=10k ΩD1=1N5818R3=0.15ΩFIGURE 19.Boost or Step-Up RegulatorLM2578A/LM3578A15Typical Applications(Continued)D1is a Schottky type diode such as a 1N5818or 1N5819.L1is found as described in the buck converter section,using the inductance chart for Figure 16for the boost configuration and 20%discontinuity.INVERTING REGULATORFigure 20shows the basic configuration for an inverting regulator.The input voltage is of a positive polarity,but the output is negative.The output may be less than,equal to,or greater in magnitude than the input.The relationship be-tween the magnitude of the input voltage and the output voltage is V o =V in x (t on /t off ).Figure 21shows an LM2578A configured as a 5V to −15V polarity inverter with an output current of 300mA,a load regulation of 44mV (60mA to 300mA)and a line regulation of 50mV (4.5V ≤V in ≤8.5V).R1=(|V o |+1)R2where R2=10k Ω.R3=V/(I L(max,DC)+0.5∆I L ).R4=10V BE1B f /(I L (max,DC)+0.5∆I L )where:V,V BE1,V sat ,and B f are defined in the “Buck Converter with Boosted Output Current”section.∆I L =2(I LOAD(min))(V in +|V o |)/V INR5is defined in the “Buck with Boosted Output Current”section.R6serves the same purpose as R4in the Boost Regulator circuit and is typically 220k Ω.C1,C3and C4are defined in the “Boost Regulator”section.C2≥I o |V o |/[f osc (|V o |+V in )V ripple ]L1is found as outlined in the section on buck converters,using the inductance chart of Figure 16for the invert con-figuration and 20%discontinuity.BUCK-BOOST REGULATORThe Buck-Boost Regulator,shown in Figure 22,may step a voltage up or down,depending upon whether or not the desired output voltage is greater or less than the input voltage.In this case,the output voltage is 12V with an input voltage from 9V to 15V.The circuit exhibits an efficiency of 75%,with a load regulation of 60mV (10mA to 100mA)and a line regulation of 52mV.R1=(V o −1)R2where R2=10k ΩR3=V/0.75AR4,C1,C3and C4are defined in the “Boost Regulator”section.D1and D2are Schottky type diodes such as the 1N5818or 1N5819.where:V d is the forward voltage drop of the diodes.V sat is the saturation voltage of the LM2578A output transis-tor.V sat1is the saturation voltage of transistor Q1.L1≥(V in −V sat −V sat1)(t on /I p )00871110FIGURE 20.Basic Inverting Regulator00871112V in =5V R4=190ΩV o =−15V R5=82ΩV ripple =5mV R6=220k ΩI o =300mA C1=1820pF I min =60mAC2=1000µFf osc =50kHz C3=20pF R1=160k ΩC4=0.0022µF R2=10k ΩL1=150µH R3=0.01ΩD1=1N5818FIGURE 21.Inverting RegulatorL M 2578A /L M 3578A16。

富士通 FLM7785-4F 说明书

Fujitsu recommends the following conditions for the reliable operation of GaAs FETs:1. The drain-source operating voltage (V DS ) should not exceed 10 volts.2. The forward and reverse gate currents should not exceed 16.0 and -2.2 mA respectively with gate resistance of 100Ω.G.C.P.: Gain Compression Point, S.C.L.: Single Carrier LevelDESCRIPTIONThe FLM7785-4F is a power GaAs FET that is internally matched for standard communication bands to provide optimum power and gain in a 50 ohm system.Eudyna’s stringent Quality Assurance Program assures the highest reliability and consistent performance.FEATURES• High Output Power:P 1dB = 36.5dBm (Typ.)• High Gain:G 1dB = 8.5dB (Typ.)• High PAE:ηadd = 35% (Typ.)• Low IM 3= -46dBc@Po = 25.5dBm • Broad Band:7.7 ~ 8.5GHz• Impedance Matched Zin/Zout = 50Ω• Hermetically SealedPOWER DERATING CURVE122430186050100150200Case Temperature (°C)T o t a l P o w e r D i s s i p a t i o n (W)OUTPUT POWER & IM 3 vs. INPUT POWERV DS =10V f 1= 8.5 GHz f 2 = 8.51 GHz 2-tone test121416182022Input Power (S.C.L.) (dBm)S.C.L.: Single Carrier Level21232527293133-50-40-30-20-10O u t p u t P o w e r (S .C .L .) (d B m )IM 3P outI M 3 (d B c )OUTPUT POWER vs. FREQUENCYPin=28.5dBm26.5dBm24.5dBm22.5dBm7.97.78.18.38.5Frequency (GHz)343536373833O u t p u t P o w e r (d B m )V DS =10V P1dBV DS =10V f = 8.1 GHzOUTPUT POWER vs. INPUT POWER18202224262830Input Power (dBm)343638323028304515O u t p u t P o w e r (d B m )ηaddP outηa d d (%)S-PARAMETERSV DS = 10V , I DS = 1100mAFREQUENCY S11S21S12S22(MHZ)MAG ANG MAG ANG MAG ANG MAG ANG 7500.711120.0 3.482-74.8.025-92.7.478147.97600.694109.7 3.441-86.9.031-113.4.490133.67700.67299.8 3.396-98.7.037-131.2.507120.77800.64890.0 3.354-110.3.043-143.4.525109.97900.62180.2 3.331-121.7.049-157.1.53599.88000.59170.2 3.319-133.1.055-170.0.54190.78100.55759.3 3.344-144.8.061178.8.54282.68200.51647.3 3.377-156.5.067166.5.53974.98300.47033.5 3.444-168.7.074154.9.52567.58400.41416.0 3.540178.2.080141.7.49659.78500.356-7.7 3.625163.9.089128.6.44952.98600.308-40.8 3.704148.3.097113.5.38046.98700.307-83.13.723131.3.10197.4.28243.10-j50S 0°S 21S 12Eudyna Devices Inc. products contain gallium arsenide(GaAs) which can be hazardous to the human body and the environment. For safety, observe the following procedures:CAUTION• Do not put this product into the mouth.• Do not alter the form of this product into a gas, powder, or liquidthrough burning, crushing, or chemical processing as these by-products are dangerous to the human body if inhaled, ingested, or swallowed.• Observe government laws and company regulations when discarding this product. This product must be discarded in accordance with methods specified by applicable hazardous waste procedures.For further information please contact:Eudyna Devices USA Inc.2355 Zanker Rd.San Jose, CA 95131-1138, U.S.A.TEL:(408) 232-9500FAX:(408) 428-9111Eudyna Devices Europe Ltd.Network House Norreys DriveMaidenhead, Berkshire SL6 4FJ United KingdomTEL:+44 (0) 1628 504800FAX:+44 (0) 1628 504888Eudyna Devices Asia Pte Ltd.Hong Kong BranchRm.1101, Ocean Centre, 5 Canton Rd.Tsim Sha Tsui, Kowloon, Hong Kong TEL:+852-2377-0227FAX:+852-2377-3921Eudyna Devices Inc.Sales Division1, Kanai-cho, Sakae-kuY okohama, 244-0845, Japan TEL:+81-45-853-8156FAX:+81-45-853-8170Eudyna Devices Inc.reserves the right to change products and specifications without notice.The information does not convey any license under rights of Eudyna Devices Inc.or others.©2004 Eudyna Devices USA Inc.Printed in U.S.A.。

TMS320C6655 57产品预览信息说明书

TMS320C6655/57Fixed and Floating-Point Digital Signal Processor Data ManualPRODUCT PREVIEW information applies to products in theformative or design phase of development. Characteristic dataand other specifications are design goals. Texas Instrumentsreserves the right to change or discontinue these productswithout notice.Literature Number:SPRS814March 2012SPRS814—March 2012Data Manual TMS320C6655/57Release HistoryFor detailed revision information, see ‘‘Revision History’’ on page A-226.RevisionDate Description/Comments SPRS841 March 2012Initial releaseFixed and Floating-Point Digital Signal ProcessorSPRS814—March 2012TMS320C6655/ Contents1Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .131.1KeyStone Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.2Device Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .141.3Functional Block Diagram. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .162Device Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.1Device Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .172.2DSP Core Description. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .182.3Memory Map Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .212.4Boot Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252.5Boot Modes Supported and PLL Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .252.5.1Boot Device Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262.5.2Device Configuration Field . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .262.5.3PLL Boot Configuration Settings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332.6Second-Level Bootloaders . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .332.7Terminals . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.7.1Package Terminals. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.7.2Pin Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .342.8Terminal Functions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .392.9Development and Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.9.1Development Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.9.2Device Support . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .632.10Related Documentation from Texas Instruments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .653Device Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .663.1Device Configuration at Device Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .663.2Peripheral Selection After Device Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .673.3Device State Control Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .673.3.1Device Status Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .703.3.2Device Configuration Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .713.3.3JTAG ID (JTAGID) Register Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.4Kicker Mechanism (KICK0 and KICK1) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.5LRESETNMI PIN Status (LRSTNMIPINSTAT) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .723.3.6LRESETNMI PIN Status Clear (LRSTNMIPINSTAT_CLR) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .733.3.7Reset Status (RESET_STAT) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .743.3.8Reset Status Clear (RESET_STAT_CLR) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .753.3.9Boot Complete (BOOTCOMPLETE) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .753.3.10Power State Control (PWRSTATECTL) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .763.3.11NMI Event Generation to CorePac (NMIGRx) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .763.3.12IPC Generation (IPCGRx) Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .773.3.13IPC Acknowledgement (IPCARx) Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .783.3.14IPC Generation Host (IPCGRH) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .783.3.15IPC Acknowledgement Host (IPCARH) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .793.3.16Timer Input Selection Register (TINPSEL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .803.3.17Timer Output Selection Register (TOUTPSEL) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .823.3.18Reset Mux (RSTMUXx) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .833.3.19Device Speed (DEVSPEED) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .843.3.20Pin Control 0 (PIN_CONTROL_0) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .843.3.21Pin Control 1 (PIN_CONTROL_1) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .863.3.22UPP Clock Source (UPP_CLOCK) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .863.4Pullup/Pulldown Resistors . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .874System Interconnect. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .884.1Internal Buses and Switch Fabrics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .884.2Switch Fabric Connections Matrix. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .894.3TeraNet Switch Fabric Connections . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .914.4Bus Priorities . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .954.4.1Packet DMA Priority Allocation (PKTDMA_PRI_ALLOC) Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .954.4.2EMAC / UPP Priority Allocation (EMAC_UPP_PRI_ALLOC) Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .95SPRS814—March 2012Fixed and Floating-Point Digital Signal Processor TMS320C6655/57 5C66x CorePac . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .975.1Memory Architecture. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .985.1.1L1P Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .985.1.2L1D Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .995.1.3L2 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .995.1.4MSM SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.1.5L3 Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.2Memory Protection. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1015.3Bandwidth Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1025.4Power-Down Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1025.5C66x CorePac Revision. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1035.6C66x CorePac Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1036Device Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1046.1Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1046.2Recommended Operating Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1056.3Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1066.4Power Supply to Peripheral I/O Mapping. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1077Peripheral Information and Electrical Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.1Recommended Clock and Control Signal Transition Behavior . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.2Power Supplies. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1087.2.1Power-Supply Sequencing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1097.2.2Power-Down Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.2.3Power Supply Decoupling and Bulk Capacitors. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.2.4SmartReflex. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1147.3Power Sleep Controller (PSC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1167.3.1Power Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1167.3.2Clock Domains. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1177.3.3PSC Register Memory Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1187.4Reset Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1207.4.1Power-on Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1217.4.2Hard Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1227.4.3Soft Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1237.4.4Local Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1247.4.5Reset Priority . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1247.4.6Reset Controller Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1257.4.7Reset Electrical Data / Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1257.5Main PLL and PLL Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1277.5.1Main PLL Controller Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1287.5.2PLL Controller Memory Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1307.5.3Main PLL Control Register. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1367.5.4Main PLL and PLL Controller Initialization Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1377.5.5Main PLL Controller/SRIO/HyperLink/PCIe Clock Input Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1377.6DD3 PLL. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1407.6.1DDR3 PLL Control Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1407.6.2DDR3 PLL Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1417.6.3DDR3 PLL Initialization Sequence. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1417.6.4DDR3 PLL Input Clock Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1427.7Enhanced Direct Memory Access (EDMA3) Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1437.7.1EDMA3 Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.2EDMA3 Channel Controller Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.3EDMA3 Transfer Controller Configuration. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1447.7.4EDMA3 Channel Synchronization Events. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1457.8Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1477.8.1Interrupt Sources and Interrupt Controller . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1477.8.2CIC Registers. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1627.8.3Inter-Processor Register Map. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1687.8.4NMI and LRESET . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1697.8.5External Interrupts Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 169Fixed and Floating-Point Digital Signal ProcessorSPRS814—March 2012TMS320C6655/57 7.9Memory Protection Unit (MPU) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1717.9.1MPU Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1747.9.2MPU Programmable Range Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1817.10DDR3 Memory Controller. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1867.10.1DDR3 Memory Controller Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1867.10.2DDR3 Memory Controller Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11I 2C Peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11.1I 2C Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1877.11.2I 2C Peripheral Register Description(s). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1887.11.3I 2C Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1897.12SPI Peripheral . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1927.12.1SPI Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1927.13HyperLink Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1957.13.1HyperLink Device-Specific Interrupt Event. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1957.13.2HyperLink Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1977.14UART Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1997.15PCIe Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2007.16EMIF16 Peripheral. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2017.16.1EMIF16 Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2017.17Ethernet Media Access Controller (EMAC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2047.17.1EMAC Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2047.17.2EMAC Peripheral Register Description(s). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2057.17.3EMAC Electrical Data/Timing (SGMII) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2097.18Management Data Input/Output (MDIO). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2097.18.1MDIO Peripheral Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2107.18.2MDIO Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2107.19Timers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.19.1Timers Device-Specific Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.19.2Timers Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2127.20Serial RapidIO (SRIO) Port. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2137.21General-Purpose Input/Output (GPIO) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.21.1GPIO Device-Specific Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.21.2GPIO Electrical Data/Timing. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.22Semaphore2 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2147.23Emulation Features and Capability. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.1Advanced Event Triggering (AET) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.2Trace. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2157.23.3IEEE 1149.1 JTAG . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2167.24Enhanced Viterbi-Decoder Coprocessor (VCP2). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2177.25Turbo Decoder Coprocessor (TCP3d). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2177.26Multichannel Buffered Serial Port (McBSP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2187.26.1McBSP Peripheral Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2187.26.2McBSP Electrical Data/Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2197.27Universal Parallel Port (UPP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2227.27.1UPP Register Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 222A Revision History. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 226B Mechanical Data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227B.1Thermal Data. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227B.2Packaging Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 227。

东芝功放管资料

38

TIM1414-5-252

5

TIM1414-5L TIM1414-4UL NEW TIM1414-4LA TIM1414-4-252

TIM8596-4 TIM0910-4

NEW

TIM1213-4L TIM1011-4L TIM1011-4UL

NEW

36

TIM1213-4UL

TIM1011-2UL TIM8596-2 TIM0910-2 TIM1011-2L TIM1112-2

7

8

9

4

Output Power at 1dB Gain Compression (dBm)

40 Output Power at 1dB Gain Compression (W)

46

X-, Ku-band Internally Matched Power GaAs FETs/GaN HEMTs Pout vs. Frequency Map

5

■ GaN HEMTs

C-band Internally Matched Power GaN HEMT

BIAS CONDITIONS FREQUENCY BAND (GHz) 7.7-8.5

NEW 7-AA06A 7-AA04A

(Ta = 25 °C)

RF PERFORMANCE SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS ELECTRICAL CHARACTERISTICS (TYP.) Tch (°C) 250 VGSoff (V) – 4.0 PACKAGE CODE IDS (@Pin = 44.0 dBm) (A) TYP. 10.0 MAX. 12.0 G✽✽ (dB) MAX. ±0.8 Tch✽ (°C) MAX. 140 50 – 10 18.0

TIM7785-16SL中文资料

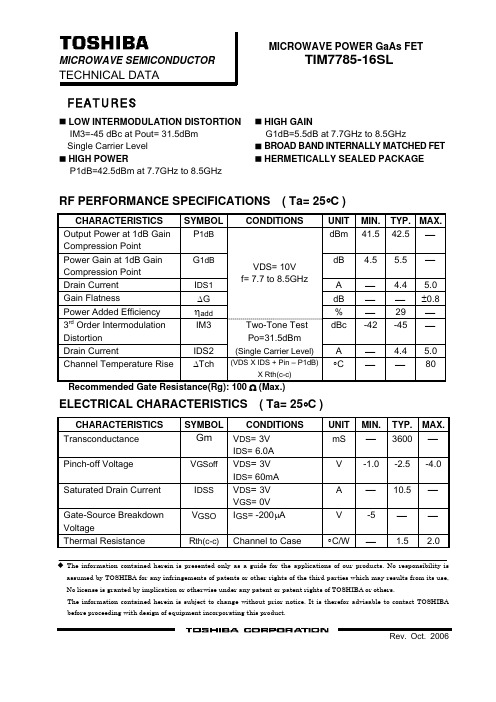

MICROWAVE POWER GaAs FETMICROWAVE SEMICONDUCTOR TIM7785-16SLTECHNICAL DATAFEATURESLOW INTERMODULATION DISTORTION HIGH GAINIM3=-45 dBc at Pout= 31.5dBm G1dB=5.5dB at 7.7GHz to 8.5GHz Single Carrier Level BROAD BAND INTERNALLY MATCHED FET HIGH POWERHERMETICALLY SEALED PACKAGEP1dB=42.5dBm at 7.7GHz to 8.5GHzRF PERFORMANCE SPECIFICATIONS ( Ta= 25°C )CHARACTERISTICS SYMBOL CONDITIONS UNITMIN. TYP.MAX. Output Power at 1dB Gain Compression PointP 1dB dBm 41.5 42.5⎯Power Gain at 1dB Gain Compression Point G 1dB dB 4.5 5.5 ⎯ Drain Current I DS1 A⎯4.45.0 Gain Flatness ΔGdB ⎯ ⎯±0.8 Power Added Efficiency ηadd VDS= 10V f= 7.7 to 8.5GHz% ⎯ 29 ⎯3rd Order Intermodulation Distortion IM3 dBc -42 -45 ⎯ Drain Current IDS2 Two-Tone Test Po=31.5dBm(Single Carrier Level) A ⎯4.45.0 Channel Temperature Rise ΔTch (VDS X IDS + Pin – P1dB)X Rth(c-c)°C ⎯ ⎯80 Recommended Gate Resistance(Rg): 100 Ω (Max.)ELECTRICAL CHARACTERISTICS ( Ta= 25°C )CHARACTERISTICS SYMBOL CONDITIONSUNITMIN. TYP.MAX.TransconductanceGm V DS = 3V I DS = 6.0AmS ⎯ 3600⎯ Pinch-off Voltage V GSoff V DS = 3VI DS = 60mAV -1.0 -2.5-4.0 Saturated Drain Current I DSS V DS = 3VV GS = 0VA⎯10.5⎯ Gate-Source Breakdown Voltage V GSO I GS = -200μA V -5 ⎯ ⎯Thermal Resistance R th(c-c) Channel to Case°C/W⎯1.52.0The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may results from its use, No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.The information contained herein is subject to change without prior notice. It is therefor advisable to contact TOSHIBA before proceeding with design of equipment incorporating this product.ABSOLUTE MAXIMUM RATINGS ( Ta= 25°C )CHARACTERISTICS SYMBOL UNITRATINGDrain-Source Voltage V DS V 15 Gate-Source Voltage V GS V -5 Drain CurrentI DS A 14.0 Total Power Dissipation (Tc= 25 °C) P T W 75 Channel Temperature T ch °C 175 Storage TemperatureT stg°C-65 to +175PACKAGE OUTLINE (2-16G1B)Unit in mm (1) Gate (2) Source (3) DrainHANDLING PRECAUTIONS FOR PACKAGE MODELSoldering iron should be grounded and the operating time should not exceed 10 seconds at 260°C.RF PERFORMANCEOutput Power (Pout) vs. Frequency43 42 41 P o u t (d B m )407.77.98.18.38.5Frequency (GHz)Output Power(Pout) vs. Input Power(Pin)4544 43 PoutηaddPin(dBm)4241 40 39 38 37 36P o u t (d B m )80 70 ηa d d (%)60 50 40 30 201029 31 33 35 37 39POWER DISSIPATION vs. CASE TEMPERATURE906030 0 0 40 80 120 160 200Tc (°C)P T (W )IM3 vs. Output Power Characteristicsf=5MHz27-10-20 -30-40 -50 -60 I M 3(d B c )29 31 33 35 37 Pout(dBm) @Single carrier level。

AD7715资料

1. The AD7715 consumes less than 450␣ µA in total supply current at 3 V supplies and 1␣ MHz master clock, making it ideal for use in low-power systems. Standby current is less than 10␣ µA. 2. The programmable gain input allows the AD7715 to accept input signals directly from a strain gage or transducer removing a considerable amount of signal conditioning. 3. The AD7715 is ideal for microcontroller or DSP processor applications with a three-wire serial interface reducing the number of interconnect lines and reducing the number of opto-couplers required in isolated systems. The part contains on-chip registers which allow software control over output update rate, input gain, signal polarity and calibration modes. 4. The part features excellent static performance specifications with 16-bits no missing codes, ± 0.0015% accuracy and low rms noise (<550␣ nV). Endpoint errors and the effects of temperature drift are eliminated by on-chip calibration options, which remove zero-scale and full-scale errors.

LM7815详细中文资料

LM7815中文资料目录1.lm7815介绍2.实际应用3.引脚序号、引脚功能4.lm7815应用电路5.7815电参数三端稳压集成电路lm7815。

电子产品中,常见的三端稳压集成电路有正电压输出的lm78 ×× 系列和负电压输出的lm79××系列。

顾名思义,三端IC是指这种稳压用的集成电路,只有三条引脚输出,分别是输入端、接地端和输出端。

它的样子象是普通的三极管,TO- 220 的标准封装,也有lm9013样子的TO-92封装。

1.lm7815介绍用lm78/lm79系列三端稳压IC来组成稳压电源所需的外围元件极少,电路内部还有过流、过热及调整管的保护电路,使用起来可靠、方便,而且价格便宜。

该系列集成稳压IC型号中的lm78或lm79后面的数字代表该三端集成稳压电路的输出电压,如lm7806表示输出电压为正6V,lm7909表示输出电压为负9V。

因为三端固定集成稳压电路的使用方便,电子制作中经常采用。

最大输出电流1.5A,LM78XX系列输出电压分别为5V;6V;8V;9V;10V;12V;15V;18V;24V。

2.实际应用在实际应用中,应在三端集成稳压电路上安装足够大的散热器(当然小功率7815IC内部电路图.的条件下不用)。

当稳压管温度过高时,稳压性能将变差,甚至损坏。

当制作中需要一个能输出1.5A以上电流的稳压电源,通常采用几块三端稳压电路并联起来,使其最大输出电流为N个1.5A,但应用时需注意:并联使用的集成稳压电路应采用同一厂家、同一批号的产品,以保证参数的一致。

另外在输出电流上留有一定的余量,以避免个别集成稳压电路失效时导致其他电路的连锁烧毁。

在lm78 ** 、lm79 ** 系列三端稳压器中最常应用的是TO-220 和TO-202 两种封装。

这两种封装的图形以及引脚序号、引脚功能如附图所示。

图中的引脚号标注方法是按照引脚电位从高到底的顺序标注的。

塞弗朗 7885 电视信号表计 使用手册说明书

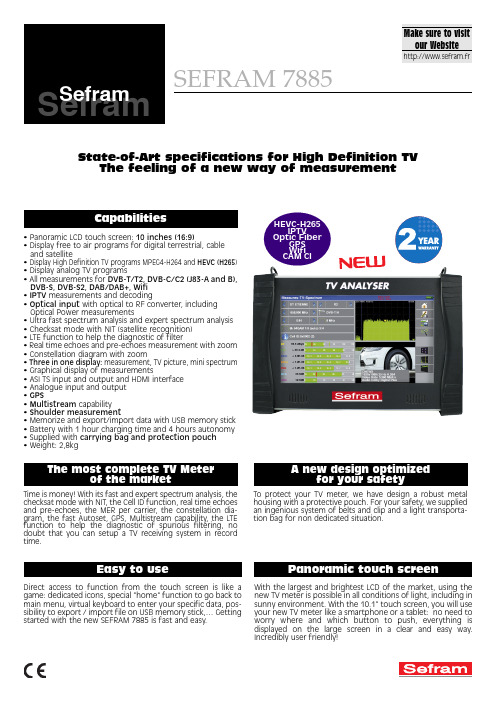

SEFRAM 7885 SeframTime is money! With its fast and expert spectrum analysis, the checksat mode with NIT, the Cell ID function, real time echoes and pre-echoes, the MER per carrier, the constellation dia-gram, the fast Autoset, GPS, Multistream capability, the LTE function to help the diagnostic of spurious filtering, no doubt that you can setup a TV receiving system in record time.To protect your TV meter, we have design a robust metal housing with a protective pouch. For your safety, we supplied an ingenious system of belts and clip and a light transporta-tion bag for non dedicated situation.A new design optimizedfor your safetyDirect access to function from the touch screen is like a game: dedicated icons, special "home" function to go back to main menu, virtual keyboard to enter your specific data, pos-sibility to export / import file on USB memory stick,… Getting started with the new SEFRAM 7885 is fast and easy.With the largest and brightest LCD of the market, using the new TV meter is possible in all conditions of light, including in sunny environment. With the 10.1" touch screen, you will use your new TV meter like a smartphone or a tablet: no need to worry where and which button to push, everything is displayed on the large screen in a clear and easy way. Incredibly user friendly!Panoramic touch screen• Panoramic LCD touch screen: 10 inches (16:9)• Display free to air programs for digital terrestrial, cable and satellite• Display High Definition TV programs MPEG4-H264 and HEVC (H265)• Display analog TV programs• All measurements for DVB-T/T2, DVB-C/C2 (J83-A and B), DVB-S, DVB-S2, DAB/DAB+, Wifi•IPTV measurements and decoding• Optical input with optical to RF converter, including Optical Power measurements• Ultra fast spectrum analysis and expert spectrum analysis • Checksat mode with NIT (satellite recognition)• LTE function to help the diagnostic of filter• Real time echoes and pre-echoes measurement with zoom • Constellation diagram with zoom• Three in one display:measurement, TV picture, mini spectrum • Graphical display of measurements• ASI TS input and output and HDMI interface• Analogue input and output• GPS• Multistream capability• Shoulder measurement• Memorize and export/import data with USB memory stick • Battery with 1 hour charging time and 4 hours autonomy • Supplied with carrying bag and protection pouch• Weight: 2,8kgState-of-Art specifications for High Definition TVThe feeling of a new way of measurementFT7885 A01 - Specifications can be updated without notice32, rue Edouard Martel - B.P. 55 - 42009 - St Etienne cedex 2Tel.+33 (0).4.77.59 36 81Supplied with:main adaptor (90-245V with European plug), user's manual on CD ROM, F/F and F/BNC adaptor, carrying protective pouch,belt clip, transportation pouch.(*): the display of digital encrypted programs is possible, if user has a valid subsciption card and if the encryption type is supported bythe TV Meter. Please check with our sales department when ordering. Dolby is a trade mark of Dolby Laboratories.978852000Transportation handcase978361000Car cigar lighter adapter978853000Audio/video cableOptional accessories: Car cigar lighterP/N 978361000Transportation hardcase P/N 978852000A/V cableP/N 978852000。

三端稳压器的参数介绍

∙如何正确理解三端稳压器数据手册中各个参数的含义∙发布时间:2010-8-9 10:22:07 | 来源: 第一价值网| 查看: 1554次| 收藏 | 打印TAG:三端稳压器7805、7809、7812数据参数|输出电压|线性调整率|负载调整率|静态电流|静态电流变化量|输出噪声电压78系列三端稳压器是最常见的电子元件,很多初学者最先接触到的就是这类器件,但是,能够系统全面的介绍三端稳压器知识的书籍甚少,很多朋友都是一知半解,本想系统总结一下线性稳压器的各种参数及其意义,想了好久,还是没有头绪,就先从7805的数据手册上写的一些参数入手,来讨论一下各参数的意义吧。

LM7805是国家半导体开发出来比较成熟,较早的一种线性稳压半导体器件,现在仍然还有很多公司在使用,个人也用得比较多,因为很便宜且性能比较稳定。

常提到的三端稳压块7805就是指它了。

拿它作为例子很有代表性。

参数一:输出电压最简单的一个参数,就是稳压器的输出电压,能稳定在多少V,7805输出电压稳定在5V参数二:线性调整率稳压器的输入电压一般都比较宽,在该范围内,输入如果变化输出电压的变化有多大呢?该参数就是描述这种变化的一个参数。

很显然输出电压的变化是越小越好了,一般都是几毫伏。

拿7805作为例子来说吧,参考Data Sheet就可以知道,在常温,输出500mA电流的情况下,输入电压在7~25V之间变化的时候,输出电压的变化典型值为3mV,最大值为50mV参数三:负载调整率负载发生变化时,输出电压也会相应的发生变化,一般是负载越重,输出电压会有所下降,负载越轻输出电压会有所上升。

负载调整率就是反应这种变化的一个量。

看7805的Data Sheet可知,在负载变化在5mA~1.5A时,输出电压的变化范围在10~50mV参数四:静态电流对于线性稳压器来说是一个非常重要的参数。

该电流为驱动大功率调整管所必须的,它不流向负载,而是直接流向地,因此该电流是越小越好。

QS7785中文资料

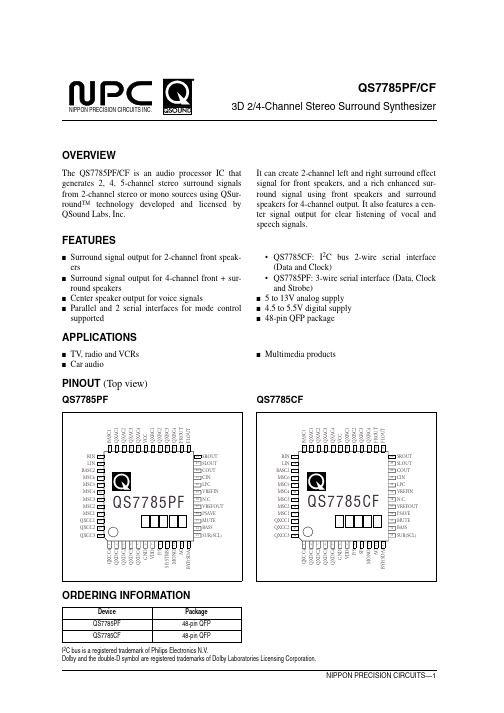

BYP(SDA) 12

ORDERING INFORMATION

Device QS7785PF QS7785CF

Package 48-pin QFP 48-pin QFP

I2C bus is a registered trademark of Philips Electronics N.V. Dolby and the double-D symbol are registered trademarks of Dolby Laboratories Licensing Corporation.

–

SCL

BASS

MUTE

PSAVE

VREFOUT

NC

VREFIN

LPC

CIN

COUT

SLOUT

SROUT

FLOUT

FROUT

QXBC4

QXBC3

QXBC2

QXBC1

VCC

QXAC4

QXAC3

QXAC2

QXAC1

BASC1

QS7785PF/CF

I/O

Description

O QEXPANDER C capacitor 4 I QEXPANDER D capacitor 1 O QEXPANDER D capacitor 2 I QEXPANDER D capacitor 3 O QEXPANDER D capacitor 4 – Ground – 4.5 to 5.5V digital supply I Input mode control (HIGH: parallel, LOW: serial) I Enhancement control (HIGH: high spread, LOW: low spread) I Serial data strobe (not applicable to QS7785CF) I Mono-to-stereo convert select (HIGH: mono to stereo mode, LOW: normal mode) I Center output control (HIGH: center on, LOW: center off) I Bypass control (HIGH: bypass, LOW: Qsurround) I/O Serial data input (also serves as ACK signal output for I2C bus) I Surround speaker control (HIGH: surround speaker on, LOW: off) I Serial clock signal input I Bass boost mode control (HIGH: bass boost on, LOW: bass boost off) I Mute signal control (HIGH: mute on, LOW: mute off) I Power save control (HIGH: power save on, LOW: power save off) O VCC/2 reference voltage output – No connection I VCC/2 reference voltage output (biased internally to VCC/2) I Center output lowpass filter I COUT output signal feedback input for front-channel output O Center signal output O Surround left-channel signal output O Surround right-channel signal output O Front left-channel signal output O Front right-channel signal output O QEXPANDER B capacitor 4 I QEXPANDER B capacitor 3 O QEXPANDER B capacitor 2 I QEXPANDER B capacitor 1 – 5 to 13V DC analog supply O QEXPANDER A capacitor 4 I QEXPANDER A capacitor 3 O QEXPANDER A capacitor 2 I QEXPANDER A capacitor 1 I Bass boost right-channel signal input

随身听皮带规格