CPC5620_5621

远程终端单元通信单元560CMR01说明书

Communication Unit 560CMR01RTU560 product line Remote Terminal Units - Data sheetRTU560 product lineCommunication module for RTU560 with 32 bitCPU•2x serial communication interface (RS-232 or RS-485) for remote communication •2x Ethernet interface (10/100BaseT)•1x USB port•1x serial peripheral bus•Battery buffered real time clockApplicationThe 560CMR01 communication unit is one of the CMU modules of the RTU560 product line.The essential tasks are:•Managing and controlling of the I/O modules via theinterface to the serial I/O bus.•Reading Process events from the input modules.•Send commands to the output modules.•Communicating with control systems and local HMIsystems via the serial interfaces (RS232) and the Ethernet 10/100BaseT interfaces.•Communication with Sub-RTU’s, IED’s or multimeterdevices via the interfaces (RS485) and the Ethernet interfaces.•Managing the time base for the RTU560 product linestation and synchronizing the I/O modules.•Handling the dialog between RTU560 product line andWeb-Browser via the LAN interfaces.Within the RTU560 racks the board occupies . Thecommunication unit is able to handle Ethernet- and UART-character based communication protocols.The unit has a battery buffered real time clock (RTC).The unit is available in 2 versions:•R0001: with standard cyber security functions•R0002: with security chip for advanced cyber securityfunctionsFigure 1: Block diagram 560CMR01CharacteristicsOn the applied ARM cortex A8 controller AM3352 a real-time operating system is implemented. The 560CMR01is responsible for the interface management, the event handling, the time base and the internal data base. The controller acts as master for the SPB I/O bus (serial peripheral bus). RTU560 synchronizes itself to the timereferences supplied by 560RTC0x. The time information of the 560RTC0x is provided to the 560CMR01 on the backplane of the sub-rack.System relevant configuration files are stored in the non-volatile flash memory card (removable SD-card™) in order to guarantee a valid system configuration after Power on Reset (PoR).A battery buffered RTC is used to keep an exact time during power off state.The communication unit provides the following interfaces:•Communication Port 1 and 2 (CP1 & CP2): serial interfaces according RS232C or RS485 with RJ45connectors. The communication ports can beconfigured independant as SPB I/O bus interface tothe front.•Ethernet interface 1 and 2 (E1 & E2): 10/100BaseT with RJ45 connector.•USB 2.0 device interface for diagnosis andmaintenance purposes.•The SPB I/O bus is directly connected to the backplane connector.Technical dataIn addition to the RTU500 series general technical data, the following applies:Main Processing Unit MPUCPU ARM cortex A8, AM3352 @800 MHzRAM128 MByteBoot Flash8 MByteSD cardConnector SD card slot (push push) Type SD 2.0, class 2Capacity 4 GByteReal time clock RTC (Backup)Battery Lithium 3 V DC, CR2032 Time resolution 1 sec, 1ms with timesync Battery lifetime> 10 yearsFree running± 50 ppmSerial interfaces CP1 and CP2Connector RJ45Type RS232C or RS485RS232C:Bit rate200 bit/s - 38.4 kbit/sSignal lines GNDTxDRxDRTSCTSDTRDCD E2/102 D1/103 D2/104 S2/105 M2/106 S1.2/108 M5/109Level typical: ± 6VRS485:Bit rate200 bit/s - 38.4 kbit/s Level typical: ± 6VEthernet interface E1 and E2Connector RJ45Type IEEE 802.3, 10/100BaseTUSB interfaceConnector micro USB Type AB(female)Type USB 2.0 device, low, fulland high speed (max. 480MBit/s)Cable type to PC USB Type A <-> micro USBType B Current consumption for power supplied via RTU560 backplane5 V DC500 mA24 V DC 3 mASignaling by LEDsERR (red)ON: RTU in error stateFlashing: RTU in warningstateFor more details seeRTU500 series FunctionDescriptionRUN (green)Communication module inoperationT Transmit data on serialcommunication ports CPR Receive data on serialcommunication ports CPS Ethernet communicationspeed:ON: 100 Mbit/sOFF: 10 Mbit/sL Link up (ON) / Activity(Flashing) on Ethernetinterface EMechanical layoutDimensions160 mm x 100 mm, 3HEeuro card format4R (20 mm) front panel Housing type Printed circuit board Mounting for mounting in RTU560racksWeight0.14 kgConnection typeRTU560 backplaneconnector48 pole type F DIN 41612Immunity testElectrostatic dischargeIEC 61000-4-28 kV air / 6 kV contact (level3)Performance criteria A Radiated Radio-FrequencyElectromagnetic FieldIEC 61000-4-310 V/m (level 3)Performance criteria A Electrical Fast Transient /BurstIEC 61000-4-44 kV (level X)Performance criteria A SurgeIEC 61000-4-52 kV (level 3)Performance criteria A Conducted Disturbances,induced by Radio-Frequency FieldsIEC 61000-4-610 V (level 3)Performance criteria AImmunity testDamped oscillatory wave IEC 61000-4-182.5 / 1 kV (level 3) Performance criteria AEnvironmental conditions - climatic Operating temperatureEN 60068-2-14-25 °C ... 70 °CStart upEN 60068-2-1-40 °CMax. operating temperature,max. 96hEN 60068-2-2+85 °CRelative humidity EN 60068-2-305 ... 95 % (non condensing)Ordering information560CMR01 R00011KGT036200R0001 560CMR01 R00021KGT036200R0002ABB Power Grids Germany AG P.O. Box 10 03 5168128 Mannheim, Germany /rtu We reserve the right to make technicalchanges or modify the contents of thisdocument without prior notice. With regardto purchase orders, the agreed particularsshall prevail. Hitachi ABB Power Grids doesnot accept any responsibility whatsoeverfor potential errors or possible lack ofinformation in this document.We reserve all rights in this document and in thesubject matter and illustrations contained therein.Any reproduction, disclosure to third parties orutilization of its contents – in whole or in parts – isforbidden without prior written consent of HitachiABB Power Grids.© 2020 Hitachi Power GridsAll rights reservedABB is a registered trademark of ABBAsea Brown Boveri Ltd. Manufactured by/for a Hitachi Power Grids company.1KGT15915V71。

ALC5621_DataSheet_1.0

ALC5621I2S AUDIO CODEC + 1.3W CLASS AB/D MONO SPEAKER AMPLIFIERDATASHEETRev. 1.027 December 2007Track ID: JATR-1076-21Realtek Semiconductor Corp.No. 2, Innovation Road II, Hsinchu Science Park, Hsinchu 300, TaiwanTel.: +886-3-578-0211. Fax: +886-3-577-6047I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifierii Track ID: JATR-1076-21 Rev. 1.0COPYRIGHT ©2007 Realtek Semiconductor Corp. All rights reserved. No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, or translated into any language in any form or by any means without the written permission of Realtek Semiconductor Corp.DISCLAIMERRealtek provides this document “as is”, without warranty of any kind, neither expressed nor implied, including, but not limited to, the particular purpose. Realtek may make improvements and/or changes in this document or in the product described in this document at any time. This document could include technical inaccuracies or typographical errors.TRADEMARKSRealtek is a trademark of Realtek Semiconductor Corporation. Other names mentioned in this document are trademarks/registered trademarks of their respective owners.USING THIS DOCUMENTThis document is intended for the hardware and software engineer’s general information on the Realtek ALC5621 Audio Codec IC.Though every effort has been made to ensure that this document is current and accurate, more information may have become available subsequent to the production of this guide. In that event, please contact your Realtek representative for additional information that may help in the development process. REVISION HISTORYRevision Release Date Summary1.0 2007/12/27 First releaseTable of Contents1.GENERAL DESCRIPTION (1)2.FEATURES (2)3.SYSTEM APPLICATIONS (2)4.BLOCK DIAGRAMS (3)4.1.F UNCTION B LOCK (3)4.2.A UDIO M IXER P ATH (4)5.PIN ASSIGNMENTS (5)5.1.G REEN P ACKAGE AND V ERSION I DENTIFICATION (5)6.PIN DESCRIPTIONS (6)6.1.D IGITAL I/O P INS (6)6.2.A NALOG I/O P INS (6)6.3.F ILTER/R EFERENCE (7)6.4.P OWER/G ROUND (7)7.FUNCTIONAL DESCRIPTION (8)7.1.P OWER (8)7.2.R ESET (8)7.2.1.Power-On Reset (POR) (8)7.3.C LOCKING (9)7.3.1.Phase-Locked Loop (9)7.3.2.I2C and Stereo I2S (10)7.4.D IGITAL D ATA I NTERFACE (11)7.4.1.Stereo I2S/PCM Interface (11)7.5.A UDIO D ATA P ATH (14)7.5.1.Vref (14)7.5.2.Stereo ADC (14)7.5.3.Stereo DAC (14)7.6.M IXERS (15)7.6.1.Headphone Mixer (15)7.6.2.MONO Mixer (16)7.6.3.Speaker Mixer (16)7.6.4.ADC Record Mixer (17)7.7.A NALOG A UDIO I NPUT P ATH (18)7.7.1.Line Input (18)7.7.2.AUXiliary Input (18)7.7.3.Microphone Input (18)7.8.A NALOG A UDIO O UTPUT D ATA P ATH (19)7.8.1.Speaker Output (19)7.8.2.Headphone Output (20)7.8.3.MONO Output (20)7.9.AVC C ONTROL (21)7.10.H ARDWARE S OUND E FFECTS (23)7.10.1.Equalizer Block (23)7.10.2.Pseudo Stereo and Spatial 3D Sound (23)7.11.I2C C ONTROL I NTERFACE (24)7.11.1.Addressing Setting (24)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iii Track ID: JATR-1076-21 Rev. 1.0plete Data Transfer (24)7.12.O DD-A DDRESSED R EGISTER A CCESS (25)7.13.P OWER M ANAGEMENT (25)7.14.GPIO AND J ACK D ETECT F UNCTION (26)7.15.I NTERNAL E VENT S IGNAL I NTERRUPTS (27)7.16.H EADPHONE D EPOP (27)8.MIXER REGISTERS LIST (28)8.1.R EG-00H:R ESET (28)8.2.R EG-02H:S PEAKER O UTPUT V OLUME (28)8.3.R EG-04H:H EADPHONE O UTPUT V OLUME (29)8.4.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)8.5.R EG-08H:AUXIN V OLUME (30)8.6.R EG-0A H:LINE_IN V OLUME (31)8.7.R EG-0C H:STEREO DAC V OLUME (31)8.8.R EG-0E H:MIC V OLUME (32)8.9.R EG-10H:MIC R OUTING C ONTROL (32)8.10.R EG-12H:ADC R ECORD G AIN (33)8.11.R EG-14H:ADC R ECORD M IXER C ONTROL (33)8.12.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)8.13.R EG-1C H:O UTPUT M IXER C ONTROL (34)8.14.R EG-22H:M ICROPHONE C ONTROL (35)8.15.R EG-34H:D IGITAL A UDIO I NTERFACE C ONTROL (35)8.16.R EG-36A H:S TEREO AD/DA C LOCK C ONTROL (36)8.17.R EG-38H:C OMPANDING C ONTROL (37)8.18.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)8.18.1.Headphone Output Amplifier Configuration (38)8.18.2.Auxiliary Output Amplifier Configuration (38)8.19.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)8.20.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)8.21.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)8.22.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)8.23.R EG-44H:PLL C ONTROL R EGISTER (42)8.23.1.Reg-44h: PLL Control Register (42)8.23.2.PLL Clock Setting Table for 48K: (Unit: MHz) (43)8.23.3.PLL Clock Setting Table for 44.1K: (Unit: MHz) (43)8.24.R EG-4A H:GPIO_O UTPUT P IN C ONTROL (43)8.25.R EG-4C H:GPIO P IN C ONFIGURATION (44)8.26.R EG-4E H:GPIO P IN P OLARITY (44)8.27.R EG-50H:GPIO P IN S TICKY (45)8.28.R EG-52H:GPIO P IN W AKE-U P (45)8.29.R EG-54H:GPIO P IN S TATUS (46)8.30.R EG-56H:P IN S HARING (46)8.31.R EG-58H:O VER-C URRENT S TATUS (47)8.32.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)8.33.R EG-5E H:MISC C ONTROL (48)8.34.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)8.35.R EG-62H:EQ C ONTROL (50)8.36.R EG-66H:EQ M ODE C HANGE E NABLE (51)8.37.R EG-68H:AVC C ONTROL (51)8.38.R EG-6A H:I NDEX A DDRESS (52)8.39.R EG-6C H:I NDEX D ATA (52)8.40.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)8.41.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)8.42.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier iv Track ID: JATR-1076-21 Rev. 1.08.43.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)8.44.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)8.45.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)8.46.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)8.47.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)8.48.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)8.49.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)8.50.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)8.51.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)8.52.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)8.53.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)8.54.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)8.55.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)8.56.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)8.57.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)8.58.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)8.59.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)8.60.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)8.61.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)8.62.R EG-7C H:VENDOR ID1 (58)8.63.R EG-7E H:VENDOR ID2 (58)9.ELECTRICAL CHARACTERISTICS (59)9.1.DC C HARACTERISTICS (59)9.1.1.Absolute Maximum Ratings (59)9.1.2.Recommended Operating Conditions (59)9.1.3.Static Characteristics (59)9.2.A NALOG P ERFORMANCE C HARACTERISTICS (60)9.3.S IGNAL T IMING (62)9.3.1.I2C Control Interface (62)9.3.2.I2S Master Mode (63)9.3.3.I2S Slave Mode (64)10.APPLICATION CIRCUIT (65)11.MECHANICAL DIMENSIONS (66)12.APPENDIX A: STEREO I2S CLOCK TABLE (68)13.ORDERING INFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier v Track ID: JATR-1076-21 Rev. 1.0List of TablesT ABLE 1.D IGITAL I/O P INS (6)T ABLE 2.A NALOG I/O P INS (6)T ABLE 3.F ILTER/R EFERENCE (7)T ABLE 4.P OWER/G ROUND (7)T ABLE 5.R ESET O PERATION (8)T ABLE 6.P OWER-O N R ESET V OLTAGE (8)T ABLE 7.C LOCK S ETTING T ABLE FOR 48K(U NIT:MH Z) (9)T ABLE 8.C LOCK S ETTING T ABLE FOR 44.1K(U NIT:MH Z) (10)T ABLE 9.MONO/AUXOUT O UTPUT S IGNAL T ABLE (20)T ABLE 10.A DDRESSING S ETTING (24)T ABLE 11.W RITE WORD P ROTOCOL (25)T ABLE 12.R EAD WORD P ROTOCOL (25)T ABLE 13.R EG-00H:R ESET (28)T ABLE 14.R EG-02H:S PEAKER O UTPUT V OLUME (28)T ABLE 15.R EG-04H:H EADPHONE O UTPUT V OLUME (29)T ABLE 16.R EG-06H:MONO_OUT/AUXOUT V OLUME (30)T ABLE 17.R EG-08H:AUXIN V OLUME (30)T ABLE 18.R EG-0A H:LINE_IN V OLUME (31)T ABLE 19.R EG-0C H:STEREO DAC V OLUME (31)T ABLE 20.R EG-0E H:MIC V OLUME (32)T ABLE 21.R EG-10H:MIC R OUTING C ONTROL (32)T ABLE 22.R EG-12H:ADC R ECORD G AIN (33)T ABLE 23.R EG-14H:ADC R ECORD M IXER C ONTROL (33)T ABLE 24.R EG-16H:A VOL S OFT V OLUME C ONTROL T IME (34)T ABLE 25.R EG-1C H:O UTPUT M IXER C ONTROL (34)T ABLE 26.R EG-22H:M ICROPHONE C ONTROL (35)T ABLE 27.R EG-34H:A UDIO I NTERFACE (35)T ABLE 28.R EG-36H:S TEREO AD/DA C LOCK C ONTROL (36)T ABLE 29.R EG-38H:C OMPANDING C ONTROL (37)T ABLE 30.R EG-3A H:P OWER M ANAGEMENT A DDITION 1 (37)T ABLE 31.H EADPHONE O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 32.A UXILIARY O UTPUT A MPLIFIER C ONFIGURATION (38)T ABLE 33.R EG-3C H:P OWER M ANAGEMENT A DDITION 2 (39)T ABLE 34.R EG-3E H:P OWER M ANAGEMENT A DDITION 3 (40)T ABLE 35.R EG-40H:A DDITIONAL C ONTROL R EGISTER (41)T ABLE 36.R EG-42H:G LOBAL C LOCK C ONTROL R EGISTER (42)T ABLE 37.R EG-44H:PLL C ONTROL R EGISTER (42)T ABLE 38.PLL C LOCK S ETTING T ABLE FOR 48K:(U NIT:MH Z) (43)T ABLE 39.PLL C LOCK S ETTING T ABLE FOR 44.1K:(U NIT:MH Z) (43)T ABLE 40.R EG-4C H:GPIO_O UTPUT P IN C ONTROL (43)T ABLE 41.R EG-4C H:GPIO P IN C ONFIGURATION (44)T ABLE 42.R EG-4E H:GPIO P IN P OLARITY (44)T ABLE 43.R EG-50H:GPIO P IN S TICKY (45)T ABLE 44.R EG-52H:GPIO P IN W AKE-U P (45)T ABLE 45.R EG-54H:GPIO P IN S TATUS (46)T ABLE 46.R EG-56H:P IN S HARING (46)T ABLE 47.R EG-58H:O VER-C URRENT S TATUS (47)T ABLE 48.R EG-5A H:J ACK D ETECT C ONTROL R EGISTER (47)T ABLE 49.R EG-5E H:MISC C ONTROL (48)T ABLE 50.R EG-60H:S TEREO AND S PATIAL E FFECT B LOCK C ONTROL (49)T ABLE 51.R EG-62H:EQ C ONTROL (50)T ABLE 52.R EG-66H:EQ M ODE C HANGE E NABLE (51)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vi Track ID: JATR-1076-21 Rev. 1.0T ABLE 53.R EG-68H:AVC C ONTROL (51)T ABLE 54.R EG-6A H:I NDEX A DDRESS (52)T ABLE 55.R EG-6C H:I NDEX D ATA (52)T ABLE 56.I NDEX-00H:EQ B AND-0C OEFFICIENT (LP0: A1) (52)T ABLE 57.I NDEX-01H:EQ B AND-0G AIN (LP0:H O) (52)T ABLE 58.I NDEX-02H:EQ B AND-1C OEFFICIENT (BP1: A1) (53)T ABLE 59.I NDEX-03H:EQ B AND-1C OEFFICIENT (BP1: A2) (53)T ABLE 60.I NDEX-04H:EQ B AND-1G AIN (BP1:H O) (53)T ABLE 61.I NDEX-05H:EQ B AND-2C OEFFICIENT (BP2: A1) (53)T ABLE 62.I NDEX-06H:EQ B AND-2C OEFFICIENT (BP2: A2) (54)T ABLE 63.I NDEX-07H:EQ B AND-2G AIN (BP2:H O) (54)T ABLE 64.I NDEX-08H:EQ B AND-3C OEFFICIENT (BP3: A1) (54)T ABLE 65.I NDEX-09H:EQ B AND-3C OEFFICIENT (BP3: A2) (54)T ABLE 66.I NDEX-0A H:EQ B AND-3G AIN (BP3:H O) (55)T ABLE 67.I NDEX-0B H:EQ B AND-4C OEFFICIENT (HPF: A1) (55)T ABLE 68.I NDEX-0C H:EQ B AND-4G AIN (HPF:H O) (55)T ABLE 69.I NDEX-11H:EQ I NPUT V OLUME C ONTROL (55)T ABLE 70.I NDEX-12H:EQ O UTPUT V OLUME C ONTROL (56)T ABLE 71.I NDEX-21H:A UTO V OLUME C ONTROL R EGISTER 1 (56)T ABLE 72.I NDEX-22H:A UTO V OLUME C ONTROL R EGISTER 2 (56)T ABLE 73.I NDEX-23H:A UTO V OLUME C ONTROL R EGISTER 3 (56)T ABLE 74.I NDEX-24H:A UTO V OLUME C ONTROL R EGISTER 4 (57)T ABLE 75.I NDEX-25H:A UTO V OLUME C ONTROL R EGISTER 5 (57)T ABLE 76.I NDEX-39H:D IGITAL I NTERNAL R EGISTER (57)T ABLE 77.I NDEX-46H:C LASS D I NTERNAL R EGISTER (58)T ABLE 78.R EG-7C H:VENDOR ID1 (58)T ABLE 79.R EG-7E H:VENDOR ID2 (58)T ABLE 80.A BSOLUTE M AXIMUM R ATINGS (59)T ABLE 81.R ECOMMENDED O PERATING C ONDITIONS (59)T ABLE 82.S TATIC C HARACTERISTICS (59)T ABLE 83.A NALOG P ERFORMANCE C HARACTERISTICS (60)T ABLE 84.I2C T IMING (62)T ABLE 85.T IMING OF I2S M ASTER M ODE (63)T ABLE 86.I2S S LAVE M ODE T IMING (64)T ABLE 87.O RDERING I NFORMATION (69)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier vii Track ID: JATR-1076-21 Rev. 1.0List of FiguresF IGURE 1.B LOCK D IAGRAM (3)F IGURE 2.A UDIO M IXER P ATH (4)F IGURE 3.P IN A SSIGNMENTS (5)F IGURE 4.A UDIO SYSCLK (9)F IGURE 5.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (11)F IGURE 6.PCM M ONO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=1, PCM_MODE_SEL=0) (11)F IGURE 7.PCM M ONO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 8.PCM S TEREO D ATA M ODE A F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=0) (12)F IGURE 9.PCM S TEREO D ATA M ODE B F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0, PCM_MODE_SEL=1) (12)F IGURE 10.I2S D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 11.L EFT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 12.R IGHT J USTIFIED D ATA F ORMAT (STEREO_I2S_BCLK_POLARITY_CTRL=0) (13)F IGURE 13.A UTO V OLUME C ONTROL B LOCK D IAGRAM (22)F IGURE 14.AVC B EHAVIOR (22)F IGURE 15.D ATA T RANSFER O VER I2C C ONTROL I NTERFACE (24)F IGURE 16.GPIO I MPLEMENTATION (26)F IGURE 17.J ACK D ETECT AND IRQ L OGIC (27)F IGURE 18.P OWER C ONTROL TO MIC I NPUT (41)F IGURE 19.J ACK-I NSERT-D ETECT P ULL U P R ESISTER I MPLEMENTED VIA AN E XTERNAL C IRCUIT (49)F IGURE 20.I2C C ONTROL I NTERFACE (62)F IGURE 21.T IMING OF I2S M ASTER M ODE (63)F IGURE 22.I2S S LAVE M ODE T IMING (64)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier viii Track ID: JATR-1076-21 Rev. 1.01.General DescriptionThe ALC5621 is a highly-integrated I2S/PCM interface audio codec with multiple input/output ports and is designed for mobile computing and communications. It provides a Stereo Hi-Fi DAC for playback and Stereo ADC for recording via the I2S/PCM interface.To reduce component count, the device can connect directly to:•MONO or stereo differential analog inputs•LINE_IN stereo Single-Ended analog inputs•AUX_IN Single-Ended analog inputs•Stereo Headphone Output•Single-end stereo configurable to AUXOUT or BTL MONO_OUT•MONO or Stereo Bridge-Tied Load (BTL) speakerMultiple analog input and output pins are provided for seamless integration with analog connected wireless communication devices. Differential input/output connections efficiently reduce noise interference, providing better sound quality. Class AB or Class D amplifiers are easily swapped via simple register configuration, and the 1.3 Watt Mono speaker removes the need for an additional amplifier, further cutting both cost and required board area. Additionally, a flexible hardware 5-band equalizer with configurable gain, bandwidth, and center frequency, enriches the sound experience.The ALC5621 AVDD operates at supply voltages from 2.3V to 3.6V. DVDD operates from 1.71 to 3.6V, and SPKVDD operates from 2.3 to 5V. To extend battery life, each section of the device can be powered down individually under software control. Leakage current in maximum power saving state is less than 10µA.The ALC5621 is available in a 5x5mm ‘Green’ QFN-32 package, making it ideal for use in handheld portable systems.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 1Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 2Track ID: JATR-1076-21 Rev. 1.0 2. FeaturesDigital-to-Analog Converter with 92dB SNR and –85dB THD+N Analog-to-Digital Converter with 85dB SNR and –80dB THD+N Two analog stereo single-ended inputs, LINE-IN_L/R and AUXIN_L/R Stereo differential analog microphone inputs, with boost pre-amplifiers (+20/+30/+40dB) BTL (Bridge-Tied Load) Speaker output with on-chip 1.3W speaker driver (SPKVDD=5V, 4.7Ω load with THD+N=40dB) Mono Speaker output supports Class AB or Class D optional Stereo headphone output with on-chip 45mW headphone driver (AVDD=3.3V, 16Ω load) 25mW SE or 75mW BTL Single-Ended differential MONO_OUT configurable to AUXOUT (AVDD=3.3V, 32Ω load)Audio jack insert detection and microphoneswitch detectionPower management and enhanced powersavingSupports digital 5-band equalizer (EQ) Supports digital spatial sound and pseudostereo effectSupports pop noise suppressionInternal PLL can receive wide range of clockinputDigital power supplies from 1.71V to 3.6V;speaker amplifier power supplies from 2.3V to 5VAnalog power and headphone power suppliedfrom 2.3V to 3.6VSupports soft-mute function32-pin QFN package3. System Applications Tablet PC system/Ultra-Mobile PC (UMPC) Personal Digital Assistants (PDA) or PDA Phone Multimedia Phone ApplicationsPortable Navigation Device (PND)Bluetooth HeadphoneI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier3Track ID: JATR-1076-21 Rev. 1.04.Block Diagrams4.1.Function BlockMICBIASSDAM C L KSCLK SPK_OUT_NSPK_OUT AUXOUT_RAUXOUT_L LINE_IN_R LINE_IN_L MIC1P MIC1N MIC2P MIC2N ALC5621D A C D A TA D C D A TB C L KL R C KAUXIN_L AUXIN_RG P I O /I R QPLL_OUTFigure 1. Block DiagramI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 4Track ID: JATR-1076-21 Rev. 1.04.2.Audio Mixer Path)10[1210[4]5]L +R+RR+RFigure 2. Audio Mixer PathI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 5Track ID: JATR-1076-21 Rev. 1.0M I C 1PM I C 2PM I C 1NL I N E _I N _L /J D 1M I C 2NL I N E _I N _R /J D 2L R C KB C L KADCDATDACDAT MCLK DGND DCVDD DBVDD GPIO/IRQ/PLL_OUT SCLKS D AC d e p o pA U X I N _LA U X I N _RA U X O U T _L /M O N O _O U TA U X O U T _R /M O N O _O U T _NS P K _O U TS P K G N DSPKVDD SPK_OUT_NVREF AGND HP_OUT_R HP_OUT_LAVDD MICBIASN C /Figure 3. Pin Assignments5.1. Green Package and Version IdentificationGreen package is indicated by a ‘G’ in the location marked ‘T’ in Figure 3. The version number is shownin the location marked ‘V’.6.1.Digital I/O PinsTable 1. Digital I/O PinsName Type Pin Description Characteristic DefinitionLRCK IO7DigitalAudioSynchronousSignal Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerBCLK IO8DigitalAudioSerialClock Master:V OL =0.1*DVDD, V OH =0.9*DVDDSlave: Schmitt triggerADCDAT O 9 SerialADCDataOutput V OL =0.1*DVDD, V OH =0.9*DVDD DACDAT I 10 Serial DAC Data Input Schmitt triggerMCLK I 11 Master Clock Input Schmitt triggerGPIO/ IRQ/PLL_OUT IO/O/O15 General Purpose Input And Output/Interrupt Output/PLL OutputGPIO: Input/OutputIRQOUT: OutputPLL_OUT: OutputSCLK I16I2C Clock Schmitt triggerSDA IO17I2C Data Schmitt triggerTotal: 8 Pins6.2.Analog I/O PinsTable 2. Analog I/O PinsName Type Pin Description Characteristic Definition MIC1P I 1 First Mic Positive Input Analog Input (1Vrms) MIC1N I 2 First Mic Negative Input Analog Input (1Vrms) LINE_IN_L/JD1 I 3 Line Input Left Channel/Jack DetectInput_1Analog Input (1Vrms) MIC2P I 4 Second Mic Positive Input Analog Input (1Vrms) MIC2N I 5 Second Mic Negative Input Analog Input (1Vrms) LINE_IN_R/JD2 I 6 Line Input Right Channel/Jack DetectInput_2Analog Input (1Vrms) AUXIN_L I 19 Auxiliary Input Left Channel Analog Input (1Vrms) AUXIN_R I 20 Auxiliary Input Right Channel Analog Input (1Vrms)AUXOUT_L/ MONO_OUT O 21 Positive Mono Output/AuxiliaryOutput Left ChannelAnalog Output (1Vrms)AUXOUT_R/ MONO_OUT_N O 22 Negative Mono Output/AuxiliaryOutput Right ChannelAnalog Output (1Vrms)SPK_OUT O 23 Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) SPK_OUT_N O 25 Negative Speaker Output Analog Output (1.5Vrms, SPKVDD=5V) HP_OUT_R O 29 Headphone Output Right Channel Analog Output (1Vrms)HP_OUT_L O 30 Headphone Output Left Channel Analog Output (1Vrms)Total: 14 PinsI S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 6Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 7Track ID: JATR-1076-21 Rev. 1.06.3. Filter/ReferenceTable 3. Filter/ReferenceName Type Pin Description Characteristic Definition NC/Cdepop IO 18 NC/De-Pop Capacitor 1µf capacitor to analog ground VREF O 27 Internal Reference V oltage 1µf capacitor to analog ground MICBIAS O 32 MIC BIAS V oltage Output Programmable Analog DC output with 3mA drive Total: 3 Pins6.4. Power/GroundTable 4. Power/Ground Name Type Pin Description Characteristic Definition DGND P 12 Digital GND - DCVDD P 13 Digital VDD 1.71V~3.6V (Core) DBVDD P 14 Digital VDD 1.71V~3.6V (IO Buffer) SPKGND P 24 Analog GND for Speaker Amps - SPKVDD P 26 Analog VDD for Speaker Amps 2.3V~5V AGND P 28 Analog GND - A VDD P 31 Analog VDD 2.3V~3.6V Total: 7 Pins7.Functional Description7.1.PowerThe ALC5621 has many power blocks. SPKVDD operates between 2.3V and 3.0V for weak Class AB amplifiers, and between 3.0V and 5V for strong Class AB amplifiers. The full range is available for ClassD amplifiers.AVDD operates between 2.3V and 3.6V. DBVDD and DCVDD operate between 1.71V and 3.6V. TheALC5621 must handle ratio control between the different power blocks. The power supplier limit conditions are DBVDD ≥ DCVDD, and SPKVDD ≥ AVDD ≥ DCVDD.7.2.ResetThere are two types of reset operation: Power-On Reset (POR) and Register reset.Table 5. Reset OperationReset Type Trigger Condition CODEC ResponsePOR Monitor digital power supply voltage reach V POR Reset all hardware logic and all registers to defaultvalues.Register Reset Write Reg-00h Reset all registers to default values except PLLrelated register7.2.1.Power-On Reset (POR)When powered on, DCVDD passes through the V POR band of ALC5621 (V PORH ~V PORL). A Power-On Reset (POR) will generate an internal reset signal (POR reset ‘LOW’) to reset the whole chip.Table 6. Power-On Reset VoltageSymbol Min Typical Max UnitV POR_ON 1.0 - 1.6 V V POR_OFF- 1.3 - V Note: V POR_OFF must be below V POR_ON.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 8Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 9Track ID: JATR-1076-21 Rev. 1.07.3. ClockingThe Audio SYSCLK can be selected from MCLK or PLL. The clock source of PLL can be selected from MCLK or BCLK. The ALC5621 only supports 256Fs or 384Fs as Audio SYSCLK (used as Stereo I 2Sclock).Figure 4. Audio SYSCLK7.3.1. Phase-Locked LoopA Phase-Locked Loop (PLL) is used to provide a flexible input clock from 2.048MHz to 40MHz. Typicalchoices are 2.048MHz, 4.096MHz, and 13MHz. The source of the PLL can be set to MCLK or BCLK by setting pll_sour_sel (Reg42[14]).The source clock of MCLK must be able to drive I 2C, and F/W can setup PLL to output the desired frequency as the SYSCLK.The PLL transmit formula is: F OUT = (MCLK * (N+2)) / ((M+2) * (K+2)) {Typical K=2}Table 7. Clock Setting Table for 48K (Unit: MHz)MCLK N M F VCO K F OUT13 66 7 98.222 2 24.555 3.6864 78 1 98.304 2 24.576 2.048 94 0 98.304 2 24.576 4.096 70 1 98.304 2 24.576 12 80 8 98.4 2 24.6 15.36 81 11 98.068 2 24.517 16 78 11 98.462 2 24.615 19.2 80 14 98.4 2 24.6 19.68 78 14 98.4 2 24.6Table 8. Clock Setting Table for 44.1K (Unit: MHz)MCLK N M F VCO K F OUT13 68 8 91 2 22.753.6864 72 1 90.931 2 22.7332.048 86 0 90.112 2 22.5284.096 64 1 90.112 2 22.52812 66 7 90.667 2 22.66715.36 63 9 90.764 2 22.69116 66 10 90.667 2 22.66719.2 64 12 90.514 2 22.62919.68 67 13 90.528 2 22.632 After a Cold Reset, PLL related Registers are reset to default values, however, they are not reset to default values after a soft-reset (write Reg00).7.3.2.I2C and Stereo I2SThe ALC5621 supports the I2S digital interface for Stereo Audio. The stereo audio digital interface is used to input data to the stereo DAC or output data from the stereo ADC. The Stereo Audio Digital Interface can be configured as Master mode or Slave mode. For the Stereo I2S Interface, the source system clock is always input from MCLK. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for details.Master ModeIn master mode (stereo_i2s_mode_sel=0), BCLK and LRCK are configured as output. Whensel_sysclk=0, MCLK is used as Stereo SYSCLK. When PLL is enabled and sel_sysclk=1, MCLK is suggested to provide frequencies shown in Table 7 Clock Setting Table for 48K (Unit: MHz) and Table 8 Clock Setting Table for 44.1K (Unit: MHz). PLL can be configured to support 44.1K and 48K base sampling rate.Slave ModeIn slave mode (stereo_i2s_mode_sel=1), BCLK/LRCK is configured as input. MCLK should provide the BCLK synchronized clock externally as the Stereo_SYSCLK.Note: The ALC5621 does not support different sample rates between SDAC and ADC in Stereo_I2S/PCM.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 10Track ID: JATR-1076-21 Rev. 1.0I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 11Track ID: JATR-1076-21 Rev. 1.07.4.Digital Data Interface7.4.1.Stereo I 2S/PCM InterfaceThe stereo I 2S/PCM interface can be configured as Master mode or Slave mode. Four audio data formats are supported: • PCM mode • Left justified mode • Right justified mode • I 2S modeFigure 5. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 6. PCM Mono Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=1, pcm_mode_sel=0)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 12Track ID: JATR-1076-21 Rev. 1.0Figure 7. PCM Mono Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)Figure 8. PCM Stereo Data Mode A Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=0)Figure 9. PCM Stereo Data Mode B Format (stereo_i2s_bclk_polarity_ctrl=0, pcm_mode_sel=1)I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier13Track ID: JATR-1076-21 Rev. 1.0Figure 10. I 2S Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 11. Left Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)Figure 12. Right Justified Data Format (stereo_i2s_bclk_polarity_ctrl=0)7.5.Audio Data Path7.5.1.VrefVref is the reference voltage for all analog blocks. An external 1µF Capacitor connected to AGND is required. The default status of Vref is enabled after power on. Driver can set Index-39[11]=0b in order to enable power control bit of Reg-3C[13]:pow_vref.7.5.2.Stereo ADCThe stereo ADC is used for recording stereo sound. The sample rate of the stereo ADC is independent of the stereo DAC sample rate. In order to save power, the left and right ADC can be powered down separately by setting adc_l_vol & adc_r_volThe sample rate of the Stereo ADC is the same as the sample rate of Stereo DAC (described in the following section).7.5.3.Stereo DACThe stereo DAC can be configured to different sample rates by driving 256Fs/384Fs into audio SYSCLK with setting divider properly (Reg36). adda_osr is used to control the over sample rate clock divider of the DA filter to 128Fs or 64Fs.Performance of 128Fs is better than 64Fs but with much higher power consumption. Refer to section 12 Appendix A: Stereo I2S Clock Table, page 68 for detailed settings.dac_l_vol & dac_r_vol can be used to control the DAC output volume.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 14Track ID: JATR-1076-21 Rev. 1.07.6.MixersThe ALC5621 supports four mixers for all audio function requirements:•Headphone mixer for 2 channels•MONO mixer•Speaker mixer•ADC record mixer7.6.1.Headphone MixerThe headphone mixer is used to drive stereo output, including HP_OUT_L/R, SPK_OUT, and MONO_OUT (AUXOUT_L/R). The output of the headphone mixer can be input to the ADC record mixer.The following signals can be mixed into the headphone mixer:•LINE-IN_L/R (Controlled by Reg0A)•PHONEP/N (Controlled by Reg08)•MIC1P/N and MIC2P/N (Controlled by Reg22 & Reg10)•Stereo DAC output (Controlled by Reg0C)•ADC record mixer output (Controlled by Reg12 & Reg14).When the SPK_OUT source is from the HP_mixer, SPK_OUT can be configured to L/R, L+R, and L/LN by setting spk_outn_source. The headphone mixer can be powered down by setting pow_mix_hp_l & pow_mix_hp_r.I S Audio Codec + 1.3W Class AB/D Mono Speaker Amplifier 15Track ID: JATR-1076-21 Rev. 1.0。

中电科二十二所(青岛)天博信息科技公司所投产品清单

3.施工方式:人工开挖,注意保护路下管线

602.65

14.12

8509.42

拆除基层

1.拆除人行道下基层混凝土

2.施工方式及外运自行考虑,注意保护路下管线

20.35

56.48

1149.37

填方

1.填方材料品种:回填土

2.密实度:夯填

427.39

14.12

6034.75

填中粗砂

1.填方材料品种:回填中粗砂

2.:敷设方式:暗敷

12295

2.54

31248.97

电气配线

天诚RVV4×1.5

1.型号:控制线RVV4×1.5

2.敷设方式:暗敷

16846

8.19

137962.00

光纤布线

长飞GYTA-4B1

1.内容:4芯单模光纤,包含熔接盒、耦合器、光纤跳线、光纤尾纤、光纤熔接测试及相关附件

21227

14.12

2.部位:手孔井井盖周边

3.含模板、运输费、冬季施工增加费

6.54

423.60

2770.34

过路顶管

1.部位:十字路口过路顶管(水平管长)

2.工作内容:电缆光纤顶管

3.安装方式:PE DE75一次顶进两根

4.说明:顶管长度4282米,单管长8564米,一次顶两根

4282

112.96

483694.72

2578.11

42.36

109208.74

拆除基层

定制

1.拆除人行道下基层混凝土

2.施工方式自行考虑,注意保护路下管线

3.运距5km包干

257.81

56.48

14561.11

AD5621资料

REVISION HISTORY Revision PrC: Preliminary Version

Preliminary Technical Data

Input Shift Register .................................................................... 13 SYNC Interrupt .......................................................................... 14 Power-On Reset.......................................................................... 14 Power-Down Modes .................................................................. 14 Microprocessor Interfacing....................................................... 14 Applications..................................................................................... 16 Choosing a Reference as Power Supply for AD5601/AD5611/AD5621 ....................................................... 16 Bipolar Operation Using the AD5601/ AD5611/AD5621 .... 16 Using AD5601/AD5611/AD5621 with an Opto-Isolated Interface ....................................................................................... 17 Power Supply Bypassing and Grounding................................ 17 Outline Dimensions ....................................................................... 18 Ordering Guide .......................................................................... 18

6_华为设备介绍

EPBD GPBD

ETHB

TOPA (O2CE扣板)

单框16000用户——机房减少三分之二

8

率先支持 8PON板

40

Class C+光 模块,传输可 达40Km

16000

128

率先支持 1:128分光比

单框支持1.6万 FTTH用户(每 用户20M)

大容量,少局所,西安端局网改从45个降为15个

N*8GE跨板聚合——灵活扩带宽,上行无阻塞

组播服务器

网管

IP网络

BRAS

组播报文处理点 组播报文

主控板

业

业

务

务

单

单

板

板

ONU ONU

}集中式组播——

¾主控板上集中处理组播协议报文

业

¾处理速度慢,性能受主控板性能限制

务 单 板

}分布式组播处理机制——

¾ 组播协议/报文处理分布到各个业务板上 ¾ 减轻了主控板的处理压力,大大提高了组

播报文处理性能

SIP, H.248

1588V2, 同步以太网

AC

自然散热

电源、FE达6kV防雷,POTS口 4kV防雷

F CCUB

2U

A

PWX

N

16/24 VDSL2 16/24 VDSL2 16/24 VDSL2 16/24 VDSL2

64 VDSL2 (30A)

96 VDSL2 (17A)

• ADSL2端口线速转发 • VDSL2 端口平均带宽50M

可以支持更多新兴业务

Page 19

MA5616应用场景: 高密度、多业务接入

MA5612:

•EPON/GPON/EPON/GE •32POTS/24FE/8E1/RF

惠普最新参数一表

惠普最新参数一览表(2010.11)目录激光黑白打印机 (2)激光彩色打印机 (10)激光多功能一体机 (19)激光专业型多功能/数码复合机 (24)扫描仪 (32)彩色商用喷墨打印机 (35)喷墨一体机 (37)大幅面打印机 (43)蓝色机型为较新的机型新增Laserjet Pro M1216nfh ;Laserjet Pro M1536dnfColor Laserjet Pro CM1415fn/CM1415fnw CP5525n/dn/xh Scanjet Professional 3000 SCANJET ENTERPRISE 7500 Officejet 6500A eAIO、Officejet 7500A eAIO、Officejet 8500A eAIO Color Laserjet Pro CM4540/f/fskm 即将上市Deskjet 2060(注:除特殊说明,报价均为MAP价格或媒体价)EOL 停产产品1 of 57 Pages激光黑白打印机2 of 57 Pages3 of 57 Pages4 of 57 Pages5 of 57 Pages6 of 57 Pages7 of 57 Pages8 of 57 Pages9 of 57 Pages激光彩色打印机10 of 57 Pages11 of 57 Pages内存:配自动双面打印;月打印负荷:入式网络打印服务器;打印语言:耗材型号:黑色保修:12 of 57 Pages13 of 57 Pages14 of 57 Pages15 of 57 Pages16 of 57 Pages17 of 57 Pages月打印负荷:PCL 5c耗材型号:碳粉,黑色成像鼓,四色保修:A3首页输出时间:大内存:18 of 57 Pages激光多功能一体机19 of 57 Pages20 of 57 Pages21 of 57 Pages22 of 57 Pages23 of 57 Pages激光专业型多功能/数码复合机24 of 57 Pages25 of 57 Pages26 of 57 Pages27 of 57 Pages28 of 57 Pages29 of 57 Pages30 of 57 Pages31 of 57 Pages扫描仪32 of 57 Pages33 of 57 Pages34 of 57 Pages彩色商用喷墨打印机35 of 57 Pages36 of 57 Pages喷墨一体机–达扫描规格:复印规格:12537 of 57 Pages4800 x 1200 dpi扫描规格:复印规格:80Photosmart4800 x 1200 dpi扫描规格:复印规格:HP Deskjet Deskjet 2060 AiO打印速度(草稿模式、分辨率;复印规格:分辨率达扫描规格:传真38 of 57 PagesAIO Printer - 达扫描规格:复印规格:125标配内存打印速度(黑白、草稿模式、页复印规格:黑白传真:调制解调器分辨率;月打印负荷复印规格:黑白传真:调制解调器39 of 57 Pages复印规格:黑白传真:调制解调器32MBCD972AA HP 920XL Officejet复印规格:黑白传真:调制解调器64MBWide Format A3+荷扫描规格:复印规格:黑白40 of 57 Pages扫描规格:复印规格:黑白传真:调制解调器64MBC4907AA HP 940XL Officejet扫描规格:复印规格:黑白传真:调制解调器64MBCD972AA HP 920XL Officejet41 of 57 Pages页扫描规格:复印规格:黑白传真:调制解调器扫描规格:复印规格:黑白传真:调制解调器扫描规格:复印规格:黑白传真:调制解调器42 of 57 Pages大幅面打印机43 of 57 Pages44 of 57 Pages)45 of 57 Pages46 of 57 Pages47 of 57 Pages48 of 57 Pages。

中兴通讯xPON ONU&ONT介绍

Service Function

802.1Q 802.1P IGMP snooping VLAN translation Battery management SNMP & OMCI /OAM QoS

Physical Performance

Power consumption: < 45 W Dimensions:482.6 mm(W) × 43.6 mm(H) ×240mm(D) Working temperature: -30°C ~ 55°C Working humidity: 5% ~ 95% Weight: < 4.5 kg Power supply: -48V DC or 110/220V AC Battery: Optional

IP Network

9806H OLT splitter Phone

TG

V5/E1/STM-1/STM-4 V5/E1 PSTN/TDM

Commercial District VDSL 2+ Modem

NetNumen 9806H

Phone

ZTE MDU for FTTC

GPON ONU: 9806H EPON ONU: 9806H、5200

FE POTS

IP Network

GE/10GE

CDN

Video Combiner

POTS

SFU NetNumen

Home

WIFI

SFU for FTTH

GPON ONU: F600, F601, F620, F625, F627, F628 EPON ONU: F400, F401, D402, F420, D421, D422, F425

内容提纲

华为MA562X安装说明

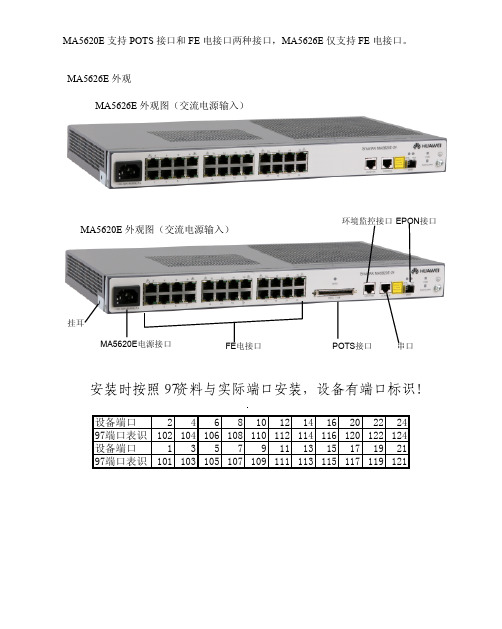

MA5626E 外观 MA5626E 外观图(交流电源输入)

MA5620E 外观图(交流电源输入)

环境监控接口 EPON接口

挂耳 MA5620E电源接口 FE电接口 POTS接口 串口

安装时按照97资料与实际端口安装,设备有端口标识!

设备端口 2 4 6 8 10 12 14 16 20 22 24 97端口表识 102 104 106 108 110 112 114 116 120 122 124 设备端口 1 3 5 7 9 11 13 15 17 19 21 97端口表识 101 103 105 107 109 111 113 115 117 119 121

表 2-1 MA5620E/MA5626E 指示灯及说明 指示灯 FE 电接口状态指示灯 绿灯亮 绿灯灭 黄灯闪烁 黄灯灭 端口建立连接 端口无连接 端口有数据传输 端口无数据传输 状态说明

POTS 接口状态指示灯(仅 MA5620E 支持此接口和指示灯) 绿灯亮 绿灯灭 EPON 接口状态指示灯 LINK:绿灯常亮 LINK:绿灯常灭 REG:绿灯常亮 REG:绿灯闪烁 REG:绿灯常灭 PWR:电源状态指示灯 绿灯常亮 绿灯常灭 RUN/ALARM:运行状态指示灯 绿灯 0.25s 亮 0.25s 灭周期闪烁 绿灯 1s 亮 1s 灭周期闪烁 红灯常亮 设备启动中 设备工作正常 设备运行故障 设备正常上电 设备掉电 EPON 接口收到下行光信号 EPON 接口没有收到下行光信号 设备注册成功 设备正在进行注册 设备注册失败 至少有一个业务端口激活 无业务端口激活

动芯 5601 DCC 附件解码器说明书

动芯5601 DCC附件解码器说明书(使用声明:此版说明书适用于5601附件解码器第10软件版本,使用前请确认版本号)注意事项 (2)1.功能特性 (3)1.1功能描述 (3)1.2技术参数 (3)1.3产品清单 (4)2.使用前准备 (4)3.安装与连接 (7)3.1 安装5601附件解码器 (7)3.2与外部设备连接 (8)3.2.1电磁转辙机 (11)3.2.2信号灯 (12)3.2.3舵机 (12)3.2.4场景灯开关 (13)3.2.4金属道岔叉芯 (14)3.3终端接口内部接线工作原理 (15)4.与控制器连接 (16)4.1与DCC控制器连接 (16)4.2与动芯控制器连接 (17)5.5601扩展模块 (18)6.CV值列表 (20)6.1CV值列表说明 (23)7.售后支持 (23)注意事项:1、安装本产品之前,请仔细阅读说明书,避免因使用不当造成产品损坏。

2、本产品不是儿童玩具,禁止14岁以下儿童操作。

3、本产品不要暴露在雨、潮湿、火、阳光直晒以及腐蚀性化学物品的环境中。

4、本产品合适工作温度在0-80°C。

5、强烈的电磁波会对本产品正常工作有影响。

7、请勿擅自拆装本产品,避免因此造成产品损坏。

8、请勿擅自对本产品进行清洗。

9、安装连接本产品时请确保电源处于关闭的状态。

10、连接其他配件时,请仔细阅读并遵循说明说要求,避免因此造成产品损坏。

1.功能特性1.1功能描述动芯5601附件控制器具有4组输出,可分别独立控制4组道岔、信号机或者舵机。

DCC与DXDCNet双协议控制,可由标准DCC控制器或动芯拾型控制器控制。

每组输出口都可以单独配置工作模式(通过CV),并配置了防过载和短路保护。

1)四组附件控制输出口。

2)电源接口。

3)控制器接口/数码系统电源接口,获取DCC控制指令/连接电源。

4)DXDCNet总线输出/输入接口。

5)解码器显示屏,显示解码器工作状态。

6)附件解码器的扩展接口。

3.MA5620E&MA5626E 产品描述-v1.0

1.2.3

MA5620E/MA5626E支持良好的管理、维护和监控功能,便于日常管理和故障诊断。

支持Telnet命令行和SNMP(Simple Network Management Protocol)网管的维护方式,支持带内和带外两种维护通道。

MA5620E最大提供24路以太网接入和24路POTS接入。

MA5626E最大提供24路以太网接入。

机箱尺寸只有442mm×220mm×43.6mm(宽×深×高)。

1.2.2

MA5620E/MA5626E支持远程配置下发,设备上电注册成功之后即可建立管理通道和业务通道,无需人工现场配置,即插即用。

MA5620E/MA5626E与OLT之间建立业务发放通道,通过OLT的业务自动发放接口实现业务的下发;大大缩短了用户业务开通所需的时间,并且后续的日常维护和故障定位等运营成本也将大大降低。

安装调测工程师

现场维护工程师

网络监控工程师

系统维护工程师

数据配置工程师

应用开发人员

1

关于本章

通过阅读本部分内容,可以了解MA5620E/MA5626E产品的网络定位,以及丰富的功能特性。

1.1产品定位

MA5620E/MA5626E在EPON接入系统中作为MDU(Multi-Dwelling Unit)设备,上行方向与OLT配合提供高速率和高质量的数据、语音和视频业务,实现FTTB接入。

支持通过OLT下发OAM消息配置MA5620E/MA5626E的IP地址和子网掩码等信息。

支持通过OLT下发OAM消息配置MA5620E/MA5626E的SNMP参数配置,包括SNMP版本、团体名和权限等信息。

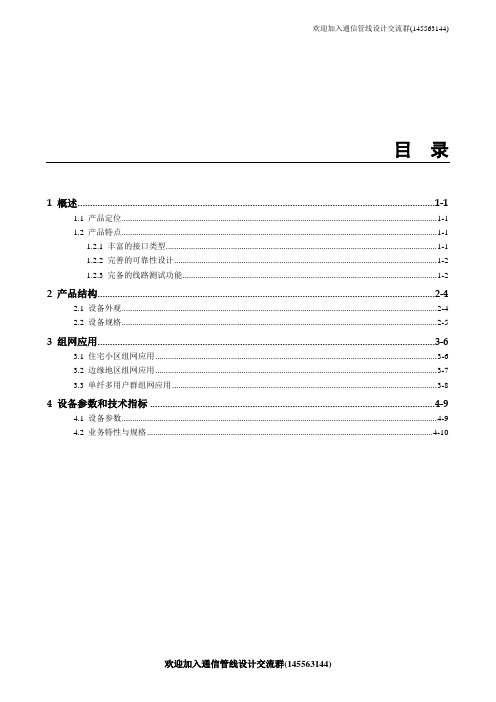

烽火接入网全系列ONU设备简介

烽火接入网全系列O N U设备简介(总14页)-CAL-FENGHAI.-(YICAI)-Company One1-CAL-本页仅作为文档封面,使用请直接删除FiBOOM系列FTTx产品AN5516-01 FTTx局端设备AN5516-01是烽火通信公司推出的一款新一代智能型电信级EPON/GPON一体化接入产品。

AN5516-01是一款电信级FTTx 局端设备,可搭建EPON/GPON/10G EPON/WDM PON/P2P通用平台,支持三层汇聚功能,具备小体积、大容量、高密度、高性能的特点,为固网宽带接入、移动基站传输、商务楼宇电子商务等提供可发展性的优质解决方案。

AN5516-01 通常摆放在小区或局端机房内。

在网络侧,AN5516-01 可以提供千兆或者万兆上联接口与IP 网络连接,也可以提供STM-1 光接口或者E1 电口与SDH 或传统的PDH 设备连接。

在用户侧,AN5516-01 设备通过ODN 网络为用户在单根光纤上提供数据、VoIP、IPTV、CATV、TDM 等多种业务。

功能特点:丰富的接口类型·AN5516-01 设备支持多种物理接口种类,上联接口包括:10GE 光接口、GE 光接口、GE 电接口、E1 电接口STM-1 光接口;用户接口包括:EPON 光接口、GPON 光接口;另外还提供各类管理接口、干接点接口及时钟告警接口等。

强大的 EPON/GPON 一体化接入能力·AN5516-01 是一款EPON/GPON 一体化接入设备,可实现EPON 和GPON 业务的混合接入。

支持IEEE 802.3ah-2005 标准规定的EPON 功能,严格符合ITU-T G.984 系列标准;具备良好的互操作性支持扩展的OAM 功能,具有良好的向下兼容性,支持多种类型ONU,例如:SFU、盒式MDU(包括LAN 型和xDSL 型)、插卡式MDU 以及HGU 型ONU 等,提供大容量PON 传输带宽。

建荣蓝牙ic CW6621A SSOP28 BT MP3 BOOMBOX V1.0

TF_CLK TP1

B

TF_CMD/IIC_CLK

TP2

TF_DAT/IIC_DAT TP3

P30/P31/P32是FCC,BQB认证用到的IO, 无TF卡方案请预留测试点,避免悬空。

GND

RTC6218/QN8065兼容注意事项:

1.RTC6218 与 QN8065 引脚兼容;

2.天线参数不相同,RTC6218建议使用220nH,QN8065建议使用470nH;

R2 TF_CLK 需要拨到MP3模式。

VDDHP

R13 6.8K

C30 MICIN

104 +

MIC

AGND

MIC

D

PA

DACR

AGND C36 104

MUTE C29 105

R25 10K

GND

U3

LN4911

1 2 3 4

SD BYP IN+ IN-

VO2 GND VDD VO1

Sheet:

Approved by:

Date:

2015-06-03

Size: A3

6

7

8

3

FM

VDDIO GND

J2

TF3

1

2

TF_CMD/IIC_CLK 3

4

TF_CLK

5

6

TF_DAT/IIC_DAT 7

8

R5

2K

9

10

SD2 SD3 SCMD VDD SCLK VSS SD0 SD1 CD SHEET

GND

VDDIO

ADKEY

R9 10K R10

R11

R12

R18

0R 2K 5.1K 10K

《基于CPCI总线的国产化RS422通讯模块研制》范文

《基于CPCI总线的国产化RS422通讯模块研制》篇一一、引言随着科技的快速发展,通信技术在各行各业的应用越来越广泛。

其中,RS422通信协议以其高效率、低成本、抗干扰能力强等优点,在工业控制、数据采集等领域得到了广泛应用。

然而,目前市场上的RS422通讯模块大多依赖于进口,这不仅增加了成本,还可能因为技术受制于人而影响使用。

因此,基于CPCI总线的国产化RS422通讯模块的研制具有重要的现实意义。

二、CPCI总线与RS422通信协议简介CPCI总线(CompactPCI),又称工业级PCI总线,具有高速、稳定、可靠等特点,广泛应用于工业控制、数据采集等领域。

而RS422通信协议是一种平衡电压数字多路通信链路,具有长距离传输、高抗干扰能力等特点,常用于工业环境的串行通信。

三、国产化RS422通讯模块研制1. 硬件设计硬件设计是RS422通讯模块研制的关键。

首先,选择与CPCI总线兼容的芯片组作为硬件核心,以确保通讯模块的稳定性和可靠性。

其次,设计合理的电路,包括电源电路、信号处理电路等,以满足RS422通信协议的要求。

最后,进行模块的封装和测试,确保其满足工业环境的使用要求。

2. 软件设计软件设计是实现RS422通讯模块功能的重要环节。

首先,编写驱动程序,实现CPCI总线与RS422通讯模块的通信。

其次,编写应用程序接口(API),方便用户使用和开发。

最后,进行软件测试和优化,确保通讯模块的稳定性和可靠性。

四、研制成果及优势经过研发和测试,基于CPCI总线的国产化RS422通讯模块已成功研制并投入使用。

该模块具有以下优势:1. 成本低:国产化后降低了成本,提高了竞争力。

2. 稳定性好:采用优质芯片和合理的设计,保证了模块的稳定性和可靠性。

3. 兼容性强:支持多种CPCI总线接口,方便用户使用和开发。

4. 抗干扰能力强:采用RS422通信协议,具有长距离传输、高抗干扰能力等特点,适用于工业环境。

五、应用前景与展望基于CPCI总线的国产化RS422通讯模块的研制成功,为工业控制、数据采集等领域提供了更加稳定、可靠的通信解决方案。

5621卡连接方式讲解

工控机通过CP5611实现PLC系统与WINCC的通讯,使用STEP7编程软件能够通过MPI正常连接PLC。

STEP7侧陈工已经完成MPI参数的设置,WINCC侧需要经过如下设置:(1).添加驱动程序和系统参数设置打开WINCC工程在Tag Management-->SIMATIC S7 PROTOCOL SUITE->MPI右键单击MPI,在弹出菜单中点击System Parameter,弹出System Parameter-MPI对话框,选择Unit标签,查看Logic device name(逻辑设备名称)。

默认安装后,逻辑设备名为MPI (2).设置Set PG/PC Interface进入操作系统下的控制面板,双击Set PG/PC Interface图标。

在Access Point of the Application:的下拉列表中选择MPI (WINCC),而后在Interface Parameter Assignment Used:的列表中,点击CP5611(MPI),而后在Access Point of the Application:的下拉列表中显示:MPI (WINCC) CP5611(MPI),如下图所示:接着设置CP5611的通讯参数,点击Proerties….按钮,弹出Properties-CP5611(MPI)属性对话框,设置参数,重要的参数如下所示:Address:CP5611的地址(MPI地址必须唯一,设置为0)Transmission Rate:MPI网络的传输速率(默认为187.5Kbps)Highest Station Address:MPI网络的最高站地址(必须和PLC的MPI网络参数设置相同)(3).添加通道与连接设置打开WINCC工程在Tag Management-->SIMATIC S7 PROTOCOL SUITE->MPI,右键单击MPI,在下拉菜单中,点击New Driver Connection,在弹出的Connection properties对话框中点击Properties按钮,弹出Connection parameters-MPI属性对话框。

tplink5620参数

tplink5620参数TP-LINK Archer C5620是一款高性能的双频无线路由器,为用户提供稳定可靠的无线网络连接。

它采用了最新的5GHz和2.4GHz无线技术,支持MU-MIMO和Beamforming+技术,能够同时连接多个设备并提供更快的速度和更好的覆盖范围。

此外,Archer C5620还具有丰富的网络管理和安全功能,使用户能够轻松配置和管理网络。

首先,Archer C5620支持双频并行工作,5GHz频段能够提供更高的速度和稳定性,适合高带宽的应用,如在线游戏和高清视频流媒体。

2.4GHz频段提供较广的覆盖范围,适合移动设备和老旧设备的连接。

用户可以根据实际需求选择使用不同的频段,以获得最佳的性能和连接体验。

其次,Archer C5620支持MU-MIMO技术,能够同时为多个设备提供独立的无线带宽,避免因设备过多而导致的网络拥塞和速度下降。

Beamforming+技术则能够根据设备的位置和信号强度调整信号的方向和强度,提供更稳定和更远的无线覆盖范围。

Archer C5620还具有强大的网络管理和安全功能。

用户可以通过Web界面或TP-LINK的Tether应用进行路由器的配置和管理,包括网络名称、密码、访客网络、家长控制、QoS和端口转发等各种设置。

路由器还具有防火墙和DoS攻击防护功能,保护网络的安全性。

另外,Archer C5620还支持IPv6协议,能够适应未来的网络发展趋势。

它还具有USB接口,可以通过连接USB存储设备或打印机,实现共享文件和打印功能。

总结起来,TP-LINK Archer C5620是一款功能强大的双频无线路由器,提供稳定的无线网络连接,适用于家庭和办公场所。

它的双频并行工作、MU-MIMO和Beamforming+技术、丰富的网络管理和安全功能,以及对IPv6的支持,使得用户能够享受到更快速的无线网络和更好的连接体验。

无论是用于网上冲浪、游戏还是高清视频流媒体,Archer C5620都能满足用户的需求。

华为ONU设备MA5626E(MA5620E) 产品描述

2.1 设备外观......................................................................................................................................................2-4 2.2 设备规格......................................................................................................................................................2-5

4 设备参数和技术指标 ..................................................................................................................4-9

4.1 设备参数......................................................................................................................................................4-9 4.2 业务特性与规格........................................................................................................................................4-10

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

LITELINK™ III Phone Line Interface IC (DAA)

Features

• Superior voice solution with high power option, low noise, no automatic gain control circuit, and excellent part-to-part gain accuracy • Data access arrangement (DAA) solution for modems at speeds up to V.92 • 3.3 or 5 V power supply operation • Caller ID signal reception function • Easy interface with modem ICs and voice CODECs • Worldwide dial-up telephone network compatibility • Supplied application circuit complies with the requirements of TIA/EIA/IS-968 (FCC part 68), UL1950, UL60950, EN60950, IEC60950, EN55022B, CISPR22B, EN55024, and TBR-21 • Complies with UL1577 • Line-side circuit powered from telephone line • Compared to other silicon DAA solutions, LITELINK: - Uses fewer passive components - Takes up less printed-circuit board space - Uses less telephone line power - Offers simplified operation - Is a single-chip solution

Applications

• • • • • • •

Computer telephony and gateways, such as VoIP PBXs Satellite and cable set-top boxes V.92 (and other standard) modems Fax machines Voicemail systems Embedded modems for POS terminals, automated banking, remote metering, vending machines, security, and surveillance

Description

LITELINK III is a single-package silicon phone line interface/DAA used in voice and data communication applications to make connections between host equipment and telephone networks. LITELINK provides a high-voltage isolation barrier, AC and DC phone line termination, switchhook, 2-wire to 4-wire hybrid, ring detection, and on-hook signal detection. LITELINK can be used in both differential and single-ended signal applications. LITELINK uses on-chip optical components and a few inexpensive external components to form a complete voice or high-speed data phone line interface. LITELINK eliminates the need for the large isolation transformers or capacitors used in other interface configurations. It incorporates the required high-voltage isolation barrier in the surface-mount SOIC package. The CPC5620 (half-wave ring detect) and CPC5621 (full-wave ring detect) PLIs build upon Clare’s LITELINK II line, with improved insertion loss control, improved noise performance, and lower minimum current draw from the phone line.

Figure 1. CPC5620/CPC5621 Block Diagram

TIP+

Pr

Tx+ TxTransmit Diff. Amplifier MODE OH RING CID Rx+ RxReceive Diff. Amplifier

DS-CPC5620/5621-R0.E

ar

VI Slope Control Current Limit Control RING-

y

AC Impedance Control

1

CPC5620/CPC5621

1 Electrical Specifications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.1 Absolute Maximum Ratings. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.2 Performance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 Application Circuits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.1 Resistive Termination Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.1.1 Resistive Termination Application Circuit Part List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.2 Reactive Termination Application Circuit. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.2.1 Reactive Termination Application Circuit Part List . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 Using LITELINK . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.1 Switch Hook Control (On-hook and Off-hook States) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2 On-hook Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.1 Ring Signal Reception via the Snoop Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.2 Polarity Reversal Detection with CPC5621 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.3 On-hook Caller ID Signal Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3 Off-Hook Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3.1 Receive Signal Path. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3.2 Transmit Signal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.4 Start-up Requirements . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.5 DC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.5.1 Non-Current Limited Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.5.2 Current Limited Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6 AC Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6.1 Resistive Termination Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6.2 Reactive Termination Applications. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.6.3 Mode Pin Usage. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3 3 3 5 6 6 7 8 9