VHDL语言实例

vhdl基础及经典实例开发pdf

vhdl基础及经典实例开发pdf VHDL是一种硬件描述语言,它用于描述和设计数字电路。

VHDL的全称是Very High Speed Integrated Circuit Hardware Description Language,它源于20世纪80年代的美国国防部,是一种为了描述硬件而设计的开发语言。

VHDL的基础知识包括语法、数据类型和结构体。

语法方面,VHDL 有自己的语法规则和词法规则,要正确地描述一个硬件电路,我们需要熟悉这些规则。

数据类型方面,VHDL内置了基本的数据类型,如bit、bit vector、integer等,这些数据类型可以用来描述电路的输入输出和中间信号。

结构体方面,VHDL支持设计者自定义类型,比如用record来描述一个复杂的数据结构。

在VHDL开发中,经典实例是不可或缺的。

经典实例可以帮助我们更好地理解VHDL的使用方法和特点,也可以让我们更好地掌握VHDL的编程技巧。

下面是一些经典实例的介绍。

1.二进制加法器(Binary Adder):二进制加法器可以实现两个二进制数的加法运算。

它是数字电路中常用的基本模块,很多其他的电路都需要用到它。

通过构建一个二进制加法器的实例,我们可以学习到VHDL的语法规则、数据类型的使用以及模块化设计的思想。

2.时钟分频器(Clock Divider):时钟分频器可以将输入的时钟信号分频为较低频率的信号。

在数字电路中,时钟分频器是非常常见的一个模块,它可以用于控制其他电路的时序。

通过构建一个时钟分频器的实例,我们可以学习到VHDL的状态机设计、时序逻辑的实现以及对时钟信号的处理。

3.多路选择器(Multiplexer):多路选择器可以根据选择信号选择其中的一个输入信号输出。

在数字电路中,多路选择器可以用于实现多个输入的选择和切换。

通过构建一个多路选择器的实例,我们可以学习到VHDL的条件语句的使用、信号赋值的方法以及对多个输入信号的处理。

vhdl语言编程实例

实现各种逻辑功能:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY louji1a ISPORT(S: IN STD_LOGIC_VECTOR(2 DOWNTO 0);C: IN STD_LOGIC;A: IN STD_LOGIC_VECTOR(4 DOWNTO 0);B: IN STD_LOGIC_VECTOR(4 DOWNTO 0);F: OUT STD_LOGIC_VECTOR(4 DOWNTO 0) );END ENTITY louji1a;ARCHITECTURE ONE OF louji1a ISBEGINF<=A WHEN S="000" ELSEA-B WHEN S="001" ELSEA-1 WHEN (S="010" AND C='0') ELSEA+1 WHEN (S="011" AND C='0') ELSEA ANDB WHEN S="100" ELSEA ORB WHEN S="101" ELSEA XORB WHEN S="110" ELSENOT A WHEN S="111" ELSENULL;END ARCHITECTURE ONE;38译码器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY yimaqi1a ISPORT(A: IN STD_LOGIC_VECTOR(3 DOWNTO 0);B: OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END ENTITY yimaqi1a;ARCHITECTURE one OF yimaqi1a IS--SIGNAL abc:STD_LOGIC_VECTOR(3 DOWNTO 0); --SIGNAL def:STD_LOGIC_VECTOR(6 DOWNTO 0); BEGIN--abc<=A3&A2&A1&A0;--def<=g&f&e&d&c&b&a;PROCESS (A)case A ISWHEN"0000"=>B<="0111111";WHEN"0001"=>B<="0000110";WHEN"0010"=>B<="1011011";WHEN"0011"=>B<="1001111";WHEN"0100"=>B<="1100110";WHEN"0101"=>B<="1101101";WHEN"0110"=>B<="1111101";WHEN"0111"=>B<="0000111";WHEN"1000"=>B<="1111111";WHEN"1001"=>B<="1101111";WHEN"1010"=>B<="1110111";WHEN"1011"=>B<="1111100";WHEN"1100"=>B<="0111001";WHEN"1101"=>B<="1011110";WHEN"1110"=>B<="1111001";WHEN"1111"=>B<="1110001";WHEN OTHERS =>NULL;END CASE ;END PROCESS;END ARCHITECTURE ONE;十进制计数器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY jishuqi1a ISPORT(CLK,EN,CTRL,CLR:IN STD_LOGIC;Q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);CO:OUT STD_LOGIC);END ENTITY jishuqi1a;ARCHITECTURE BHV OF jishuqi1a ISSIGNAL QQ :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(CLK,EN,CTRL,CLR)--V ARIABLE QQ :STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF CLR='0' THEN QQ<="0000";ELSIF CTRL='0' THEN QQ<="0000";ELSIF CLK'EVENT AND CLK='1'THEN IF EN='1' THEN IF QQ<9 THEN QQ<=QQ+1;ELSE QQ<="0000";END IF;END IF;IF QQ="0000" THEN CO<='1';ELSE CO<='0';END IF;END PROCESS ;Q<=QQ;END ARCHITECTURE BHV;实现六十进制计数器:1.实现任何计数器:2.library ieee;use ieee.std_logic_1164.all;--use ieee.std_logic_unsigned.all;entity ncount isgeneric(n: integer :=6);port(clk : in std_logic;clr : in std_logic;--updown : in std_logic;en : in std_logic;ctrl : in std_logic;d : in INTEGER range n-1 downto 0;q : out INTEGER RANGE n-1 DOWNTO 0;C : OUT STD_LOGIC);end entity;architecture rtl of ncount is-- Declare the shift register signalsignal qq : INTEGER RANGE n-1 DOWNTO 0;beginprocess (clk,en,ctrl,clr,qq)beginif (clr = '0') then qq <= 0;elsif (rising_edge(clk)) thenif (en = '1') thenif (ctrl = '1') then qq <= d;--elsif (updown = '1') thenelse if ( qq < n-1 ) thenqq <= qq+1;elseqq <= 0;end if;--elsif ( qq > 0 ) then-- qq <= qq-1;-- else-- qq <= n-1;end if;end if;end if;if ( qq = 0 ) thenc<='1';elsec<='0';end if;q<=qq;end process;end rtl;六进制:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sixcount is(n: integer :=3);port(clk : in std_logic;clr : in std_logic;en : in std_logic;ctrl : in std_logic;d : in std_logic_vector (n-1 downto 0);q : out std_logic_vector (n-1 downto 0);C : OUT STD_LOGIC);end entity;architecture rtl of sixcount is-- Declare the shift register signalsignal qq : std_logic_vector (n-1 downto 0);beginprocess (clk,en,ctrl,clr,qq)beginif (clr = '0') then qq <= "000";elsif (rising_edge(clk)) thenif (en = '1') thenif (ctrl = '1') then qq <= d;--elsif (updown = '1') thenelse if ( qq < "101" ) thenqq <= qq+1;elseqq <= "000";end if;--elsif ( qq > 0 ) then-- qq <= qq-1;-- else-- qq <= n-1;end if;end if;if ( qq = "000" ) thenc<='1';elsec<='0';end if;q<=qq;end process;end rtl;十进制:generic(n: integer :=4);port(clk : in std_logic;clr : in std_logic;--updown : in std_logic;en : in std_logic;ctrl : in std_logic;d : in std_logic_vector (n-1 downto 0);q : out std_logic_vector (n-1 downto 0);C : OUT STD_LOGIC);end entity;architecture rtl of tencount is-- Declare the shift register signalsignal qq : std_logic_vector (n-1 downto 0);beginprocess (clk,en,ctrl,clr,qq)beginif (clr = '0') then qq <="0000";elsif (rising_edge(clk)) thenif (en = '1') thenif (ctrl = '1') then qq <= d;--elsif (updown = '1') thenelse if ( qq < "1001" ) thenqq <= qq+1;elseqq <= "0000";end if;--elsif ( qq > 0 ) then-- qq <= qq-1;-- else-- qq <= n-1;end if;end if;end if;if ( qq = "0000" ) thenc<='1';elsec<='0';end if;q<=qq;end process;end rtl;还需用译码器:library ieee ;use IEEE.STD_LOGIC_1164.ALL;ENTITY TRANS ISPORT(A3,A2,A1,A0 :IN STD_LOGIC;--A,B,C,D,E,F,G:OUT STD_LOGIC;Q :OUT STD_LOGIC_VECTOR(6 DOWNTO 0) );END ENTITY TRANS ;ARCHITECTURE A OF TRANS ISSIGNAL AA:STD_LOGIC_VECTOR(3 DOWNTO 0); --SIGNAL Q:STD_LOGIC_VECTOR(6 DOWNTO 0);BEGINAA <= A3&A2&A1&A0;--Q <= G&F&E&D&C&B&A;PROCESS(AA)BEGINCASE AA ISWHEN "0000" => Q<="0111111";WHEN "0001" => Q<="0000110";WHEN "0010" => Q<="1011011";WHEN "0011" => Q<="1001111";WHEN "0100" => Q<="1100110";WHEN "0101" => Q<="1101101";WHEN "0110" => Q<="1111101";WHEN "0111" => Q<="0000111";WHEN "1000" => Q<="1111111";WHEN "1001" => Q<="1101111";WHEN "1010" => Q<="1110111";WHEN "1011" => Q<="1111100";WHEN "1100" => Q<="0111001";WHEN "1101" => Q<="1011110";WHEN "1110" => Q<="1111001";WHEN "1111" => Q<="1110001";WHEN OTHERS => NULL;END CASE;END PROCESS;END ARCHITECTURE A ;将十进制,六进制组成六十进制:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity stencount is(clk1 : in std_logic;clr1 : in std_logic;--updown1 : in std_logic;en1 : in std_logic;ctrl1 : in std_logic;--ctrl2 : in std_logic;dd1 : in INTEGER RANGE 9 DOWNTO 0;dd2 : in INTEGER RANGE 5 DOWNTO 0;q1 : out INTEGER RANGE 59 DOWNTO 0;C1 : OUT STD_LOGIC);end entity;architecture rtl of stencount iscomponent ncountgeneric(n: integer);port(clk : in std_logic;clr : in std_logic;-- updown : in std_logic;en : in std_logic;ctrl : in std_logic;d : in INTEGER range n-1 downto 0;q : out INTEGER RANGE n-1 DOWNTO 0;c : OUT STD_LOGIC);end component;-- Declare the shift register signalsignal aa : std_logic;signal qq1 : INTEGER RANGE 9 DOWNTO 0;signal qq2 : INTEGER RANGE 5 DOWNTO 0;signal cctrl1,cctrl2 : std_logic;begincctrl2<=ctrl1;--qq1<=q1(3)&q1(2)&q1(1)&q1(0);--qq2<=q1(6)&q1(5)&q1(4);U1 :ncount GENERIC MAP(n=>10)PORT MAP( clk=>clk1,en=>en1 ,c=>aa,ctrl =>cctrl1,clr=>clr1,q=>qq1,d=>dd1);U2 :ncount GENERIC MAP(n=>6)PORT MAP( clk=>aa ,en=>en1 ,ctrl =>cctrl2,clr=>clr1,q=>qq2,d=>dd2);q1<=qq2*10+qq1;process (qq1,qq2)beginif ( qq2*10+qq1 = 0 ) thenc1<='1';elsec1<='0';end if;end process;end rtl;锁存器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY keep ISPORT (CTRL:IN STD_LOGIC;DIN:IN STD_LOGIC_VECTOR(3 DOWNTO 0);DOUT: OUT STD_LOGIC_VECTOR(3 DOWNTO 0) ); END keep;ARCHITECTURE one OF keep ISBEGINPROCESS(CTRL,DIN)beginDOUT<=DIN;END IF;END PROCESS;END one;分频器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY pinlvji ISPORT(CLK:IN STD_LOGIC;RST_CNT:OUT STD_LOGIC;CNT_EN:OUT STD_LOGIC;LOAD:OUT STD_LOGIC);END ENTITY pinlvji;ARCHITECTURE beh1 OF pinlvji ISSIGNAL AA:STD_LOGIC ;BEGINPROCESS(CLK)BEGINIF CLK'EVENT AND CLK='1' THEN AA<=NOT AA; END IF;END PROCESS;PROCESS (CLK,AA)BEGINIF CLK='0' AND AA='0' THEN CNT_EN<='1'; ELSE CNT_EN<='0';END IF;END PROCESS;LOAD<=NOT AA;RST_CNT<=AA;END BEH1;。

VHDL语言编写经典常用实例

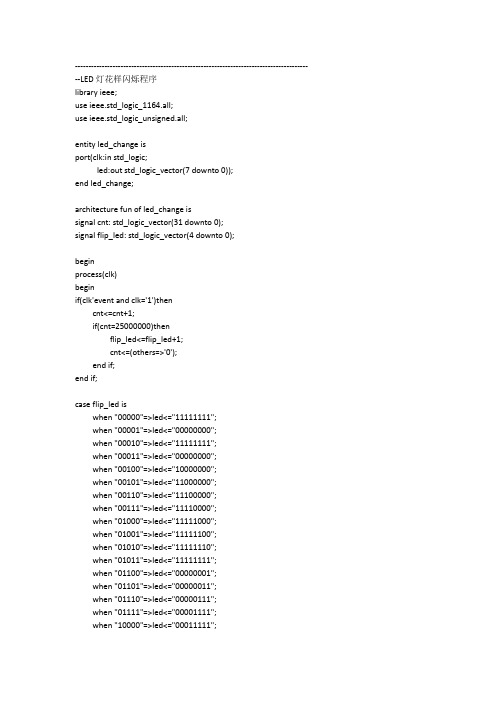

--------------------------------------------------------------------------------------- --LED灯花样闪烁程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led_change isport(clk:in std_logic;led:out std_logic_vector(7 downto 0));end led_change;architecture fun of led_change issignal cnt: std_logic_vector(31 downto 0);signal flip_led: std_logic_vector(4 downto 0);beginprocess(clk)beginif(clk'event and clk='1')thencnt<=cnt+1;if(cnt=25000000)thenflip_led<=flip_led+1;cnt<=(others=>'0');end if;end if;case flip_led iswhen "00000"=>led<="11111111";when "00001"=>led<="00000000";when "00010"=>led<="11111111";when "00011"=>led<="00000000";when "00100"=>led<="10000000";when "00101"=>led<="11000000";when "00110"=>led<="11100000";when "00111"=>led<="11110000";when "01000"=>led<="11111000";when "01001"=>led<="11111100";when "01010"=>led<="11111110";when "01011"=>led<="11111111";when "01100"=>led<="00000001";when "01101"=>led<="00000011";when "01110"=>led<="00000111";when "01111"=>led<="00001111";when "10000"=>led<="00011111";when "10001"=>led<="00111111";when "10010"=>led<="01111111";when "10011"=>led<="11111111";when "10100"=>led<="00000000";when others =>led<="ZZZZZZZZ";end case;if(flip_led>"10100")thenflip_led<="00000";end if;end process;end fun;--拨码开关控制LED程序library ieee;use ieee.std_logic_1164.all;entity switch_led isport(key : in std_logic_vector(1 downto 0);led : out std_logic_vector(7 downto 0)); --八个led灯end switch_led;architecture fun of switch_led isbeginprocess(key)begincase key iswhen "00" => led <="00000000"; -- // "0"when "01" => led <="00001111"; -- // "1"when "10" => led <="11110000"; -- // "2"when "11" => led <="11111111"; -- // "3"when others => led <="ZZZZZZZZ";end case;end process;end;--按键消抖控制LED程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity stable_key isport(clk :in std_logic;key_in:in std_logic;key_out: out std_logic);end ;architecture fun of stable_key issignal cnt : integer range 0 to 1999999;signal key ,key_d : std_logic;beginprocess(clk)beginif clk'event and clk='1' thenif key /= key_in then -----键值变化开始计时10ms key_d <= key_in;cnt <= 0;elsif cnt=1999999 then ---10mskey_out <= not key_d;cnt <= 0;elsecnt <= cnt + 1 ;end if ;key<= key_in;end if ;end process;end ;--蜂鸣器电子琴程序library ieee;use ieee.std_logic_1164.all;entity digital_piano isport(key : in std_logic_vector(7 downto 0); --定义8个按键key1~key8clk : in std_logic; --时钟输入端50Mhzbeep: out std_logic); --蜂鸣器输出端end digital_piano;architecture fun of digital_piano issignal freq : integer range 0 to 50000;signal beep_reg: std_logic;beginbeep_process: process(clk,freq) --分频进程--本工程内核心进程,计数器的大小由counter决定variable cnt : integer range 0 to 50000;beginif clk'event and clk='1' thenif cnt < freq thencnt := cnt + 1;elsecnt := 0 ;beep_reg <=not beep_reg;end if;end if;end process beep_process;freq_process: process(key)begincase key iswhen "11111110" => freq <= 47774; ---------------------------------counter 计算公式:中音do的频率为523.3hz,为了在上个beep_pro进程中得到523的频率counter= 50*1000000/(523*2)when "11111101" => freq <= 42568; --中音re的频率为587.3hzwhen "11111011" => freq <= 37919; --中音mi的频率为659.3hzwhen "11110111" => freq <= 35791; --中音fa的频率为698.5hzwhen "11101111" => freq <= 31888; --中音sol的频率为784hzwhen "11011111" => freq <= 28409; --中音la的频率为880hzwhen "10111111" => freq <= 25309; --中音si的频率为987.8hzwhen "01111111" => freq <= 23912; --高音do的频率为1045.5hzwhen "01111101" => freq <= 21282; --高音re的频率为1174.7hzwhen "01111011" => freq <= 18961; --高音mi的频率为1318.5hzwhen "01110111" => freq <= 17897; --高音fa的频率为1396.9hzwhen "01101111" => freq <= 15944; --高音sol的频率为1568hzwhen "01011111" => freq <= 14205; --高音la的频率为1760hzwhen "00111111" => freq <= 12605; --高音si的频率为1975.5hzwhen others => freq <= 0;end case;end process freq_process;beep <= beep_reg;end;--数码管静态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity static_segled isport(clk : in std_logic;data:out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0));end ;architecture fun of static_segled issignal num : std_logic_vector(3 downto 0);signal cnt : integer range 0 to 12499999 ;beginsel <= "00000000"; --静态显示,全部位选中process(clk)beginif clk'event and clk='1' then --每四秒改变一次数字if cnt=12499999 thencnt<=0;num<= num + 1;elsecnt<= cnt + 1 ;end if ;end if ;end process;process(num)begincase num iswhen "0000" => data<=x"c0"; -- // "0"when "0001" => data<=x"f9"; -- // "1"when "0010" => data<=x"a4"; -- // "2"when "0011" => data<=x"b0"; -- // "3"when "0100" => data<=x"99"; -- // "4"when "0101" => data<=x"92"; -- // "5"when "0110" => data<=x"82"; -- // "6"when "0111" => data<=x"f8"; -- // "7"when "1000" => data<=x"80"; -- // "8"when "1001" => data<=x"90"; -- // "9"when "1010" => data<=x"88"; -- // "a"when "1011" => data<=x"83"; -- // "b"when "1100" => data<=x"c6"; -- // "c"when "1101" => data<=x"a1"; -- // "d"when "1110" => data<=x"86"; -- // "e"when "1111" => data<=x"8e"; -- // "f"when others => data<=x"ff";end case;end process;end ;--数码管动态扫描library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity dynamic_segled isport(clk : in std_logic;data: out std_logic_vector(7 downto 0);sel:out std_logic_vector(7 downto 0) );end ;architecture fun of dynamic_segled issignal cnt: integer range 0 to 62449;signal flip_led: integer range 0 to 7;beginprocess(clk)beginif clk'event and clk='1' then ----- 动态扫描if cnt=62499 thencnt<=0;flip_led<=flip_led+1; -- 数据改变elsecnt<=cnt + 1;end if ;end if ;end process;process(flip_led)begincase flip_led is ---译码显示when 0 =>sel<="01111111";data<=x"c0";when 1 =>sel<="10111111";data<=x"f9";when 2 =>sel<="11011111";data<=x"a4";when 3 =>sel<="11101111";data<=x"b0";when 4 =>sel<="11110111";data<=x"99";when 5 =>sel<="11111011";data<=x"92";when 6 =>sel<="11111101";data<=x"82";when 7 =>sel<="11111110";data<=x"f8";when others=>sel<="11111111";data<=x"ff"; end case;end process;end ;。

VHDL电子琴实验报告

VHDL电子琴实验报告

实验目的:

本实验的目的是设计一个VHDL电子琴,通过FPGA实现,实现按键发出不同的音调,并通过扬声器输出对应的音频信号,达到模拟真实电子琴的效果。

实验原理:

VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路的行为和结构。

在本实验中,我们将使用VHDL语言描述电子琴的按键和音调的对应关系,通过FPGA实现电子琴的功能。

电子琴实验主要包含两个部分:输入部分和输出部分。

输入部分是按键,按下不同的按键会发出不同的音调。

输出部分是扬声器,通过扬声器输出对应的音频信号。

实验步骤:

1.确定电子琴的按键数量和对应的音调。

2.使用VHDL语言描述电子琴的按键和音调的对应关系。

3.将VHDL代码综合成逻辑电路网表。

4.将逻辑电路网表烧录到FPGA中。

5.连接扬声器到FPGA输出引脚。

6.按下不同的按键,测试扬声器输出的音频信号是否正确。

实验结果:

经过实验测试,我们成功实现了一个简单的VHDL电子琴。

按下不同的按键,扬声器输出对应的音调。

通过调整VHDL代码中的音频频率,可以改变电子琴的音调高低。

实验总结:

通过本实验,我们深入理解了VHDL语言的应用和FPGA的原理。

电子琴作为一个实际应用案例,充分展示了数字电路设计的魅力。

在今后的学习和工作中,我们将能更加熟练地应用VHDL语言和FPGA技术,设计更加复杂的数字电路系统。

vhdl语言100例程序

vhdl语言100例程序以下是100个关于VHDL语言的程序示例:1. 用VHDL编写一个计数器模块2. 用VHDL编写一个SR-Latch模块3. 用VHDL编写一个JK-Flip Flop模块4. 用VHDL编写一个D-Flip Flop模块5. 用VHDL编写一个T-Flip Flop模块6. 用VHDL编写一个复位计数器模块7. 用VHDL编写一个移位寄存器模块8. 用VHDL编写一个状态机模块9. 用VHDL编写一个MUX模块10. 用VHDL编写一个DeMUX模块11. 用VHDL编写一个加法器模块12. 用VHDL编写一个减法器模块13. 用VHDL编写一个乘法器模块14. 用VHDL编写一个除法器模块15. 用VHDL编写一个比较器模块16. 用VHDL编写一个位逻辑模块17. 用VHDL编写一个字逻辑模块18. 用VHDL编写一个数据选择器模块19. 用VHDL编写一个FIFO队列模块20. 用VHDL编写一个LIFO栈模块21. 用VHDL编写一个流水线模块22. 用VHDL编写一个中断控制器模块23. 用VHDL编写一个时钟分频器模块24. 用VHDL编写一个IO控制器模块25. 用VHDL编写一个SPI通信控制器模块26. 用VHDL编写一个I2C通信控制器模块27. 用VHDL编写一个UART通信控制器模块28. 用VHDL编写一个哈希函数模块29. 用VHDL编写一个随机数产生器模块30. 用VHDL编写一个CRC校验器模块31. 用VHDL编写一个AES加密算法模块32. 用VHDL编写一个DES加密算法模块33. 用VHDL编写一个SHA加密算法模块34. 用VHDL编写一个MD5加密算法模块35. 用VHDL编写一个RSA加密算法模块36. 用VHDL编写一个卷积滤波器模块37. 用VHDL编写一个峰值检测器模块38. 用VHDL编写一个平滑滤波器模块39. 用VHDL编写一个中值滤波器模块40. 用VHDL编写一个微处理器模块41. 用VHDL编写一个信号发生器模块42. 用VHDL编写一个信号采集器模块43. 用VHDL编写一个频率计算器模块44. 用VHDL编写一个相位计算器模块45. 用VHDL编写一个时序分析器模块46. 用VHDL编写一个正弦波产生器模块47. 用VHDL编写一个余弦波产生器模块48. 用VHDL编写一个数字滤波器模块49. 用VHDL编写一个数字信号处理器模块50. 用VHDL编写一个数字识别模块51. 用VHDL编写一个自动售货机模块52. 用VHDL编写一个二进制加法器模块53. 用VHDL编写一个二进制减法器模块54. 用VHDL编写一个二进制乘法器模块55. 用VHDL编写一个二进制除法器模块56. 用VHDL编写一个自然对数模块57. 用VHDL编写一个指数函数模块58. 用VHDL编写一个三角函数模块59. 用VHDL编写一个高斯滤波器模块60. 用VHDL编写一个激光传感器模块61. 用VHDL编写一个超声波传感器模块62. 用VHDL编写一个光电传感器模块63. 用VHDL编写一个温度传感器模块64. 用VHDL编写一个气压传感器模块65. 用VHDL编写一个陀螺仪模块67. 用VHDL编写一个电流传感器模块68. 用VHDL编写一个电容传感器模块69. 用VHDL编写一个磁场传感器模块70. 用VHDL编写一个通信电缆模块71. 用VHDL编写一个电源控制器模块72. 用VHDL编写一个电机控制器模块73. 用VHDL编写一个汽车控制器模块74. 用VHDL编写一个飞机控制器模块75. 用VHDL编写一个摄像头模块76. 用VHDL编写一个音频控制器模块77. 用VHDL编写一个扬声器控制器模块78. 用VHDL编写一个拨号器模块79. 用VHDL编写一个振动控制器模块80. 用VHDL编写一个压力控制器模块81. 用VHDL编写一个过滤器模块82. 用VHDL编写一个微波发射模块84. 用VHDL编写一个智能电表模块85. 用VHDL编写一个闹钟模块86. 用VHDL编写一个计时器模块87. 用VHDL编写一个时间戳模块88. 用VHDL编写一个脉冲宽度模块89. 用VHDL编写一个电路仿真模块90. 用VHDL编写一个电路控制模块91. 用VHDL编写一个电路测试模块92. 用VHDL编写一个电路优化模块93. 用VHDL编写一个电路布局模块94. 用VHDL编写一个电路验证模块95. 用VHDL编写一个数字信号发生器模块96. 用VHDL编写一个数字信号反演器模块97. 用VHDL编写一个数字信号滤波器模块98. 用VHDL编写一个数字信号加速器模块99. 用VHDL编写一个数字信号降噪器模块100. 用VHDL编写一个数字信号解调器模块VHDL语言是一种硬件描述语言,它用于描述数字电路和系统。

vhdl条件赋值语句

vhdl条件赋值语句vhdl是一种硬件描述语言,用于描述硬件电路的行为和结构。

在vhdl中,条件赋值语句是一种常用的语法结构,用于根据特定条件给变量赋值。

下面列举了10个关于vhdl条件赋值语句的例子。

1. 当输入信号X为1时,将输出信号Y赋值为0;否则将Y赋值为1。

```vhdlprocess (X)beginif X = '1' thenY <= '0';elseY <= '1';end if;end process;```2. 当输入信号A为0时,将输出信号B赋值为C的值;否则将B赋值为D的值。

```vhdlprocess (A, C, D)beginif A = '0' thenB <= C;elseB <= D;end if;end process;```3. 根据输入信号Sel的值,选择对应的输入信号并赋值给输出信号Out。

```vhdlprocess (Sel, In1, In2, In3)begincase Sel iswhen "00" =>Out <= In1;when "01" =>Out <= In2;when "10" =>Out <= In3;when others =>Out <= "0000";end case;end process;```4. 如果输入信号X大于等于Y,则将输出信号Z赋值为1;否则将Z赋值为0。

```vhdlprocess (X, Y)beginif X >= Y thenZ <= '1';elseZ <= '0';end if;end process;```5. 当输入信号Valid为1且输入信号Data的值为偶数时,将输出信号Even赋值为1;否则将Even赋值为0。

vhdl编程实例

vhdl编程实例VHDL编程实例- 设计与实现一个4位的全加器在本篇文章中,我们将一步一步地回答如何设计和实现一个4位的全加器。

VHDL编程语言将是我们用于描述和模拟这个电路的工具。

第一步:理解全加器的原理在编写代码之前,我们首先需要理解全加器的原理。

全加器是一种用于对两个二进制数字进行相加的电路。

它接收三个输入信号:两个位的输入(A 和B)以及一个进位输入(C_in)。

全加器的输出结果为一个位的和(S)和一个进位输出(C_out)。

我们可以使用如下的真值表来描述全加器的输出结果:输入信号输出结果A B C_in S C_out0 0 0 0 00 0 1 1 00 1 0 1 00 1 1 0 11 0 0 1 01 0 1 0 11 1 0 0 11 1 1 1 1了解了全加器的工作原理后,我们可以开始编写代码了。

第二步:编写全加器的VHDL代码我们将使用VHDL语言来描述和模拟全加器。

下面是一个简单的4位全加器的VHDL代码实现:vhdlEntity声明entity full_adder isport (A, B : in std_logic_vector(3 downto 0);C_in : in std_logic;S : out std_logic_vector(3 downto 0);C_out : out std_logic);end full_adder;Architecture声明architecture Behavioral of full_adder isbeginprocess(A, B, C_in)variable carry : std_logic;begincarry := C_in;for i in 0 to 3 loopS(i) <= A(i) xor B(i) xor carry;carry := (A(i) and B(i)) or (carry and (A(i) xor B(i)));end loop;C_out <= carry;end process;end Behavioral;在此代码中,我们首先声明了一个实体(entity)和一个架构(architecture)。

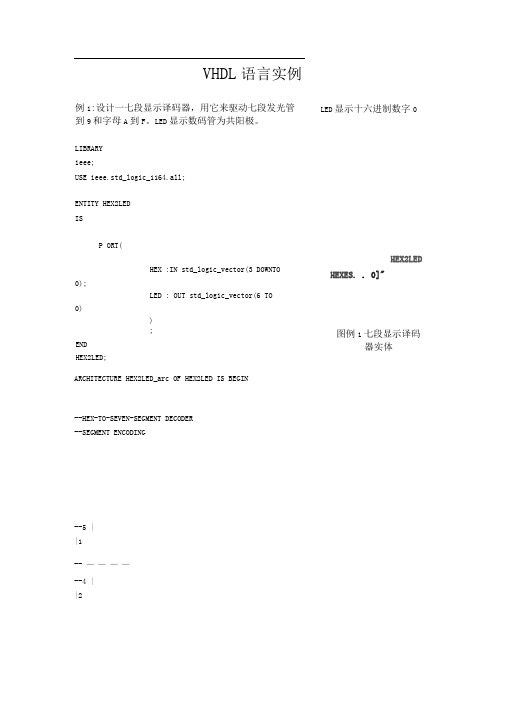

VHDL语言实例

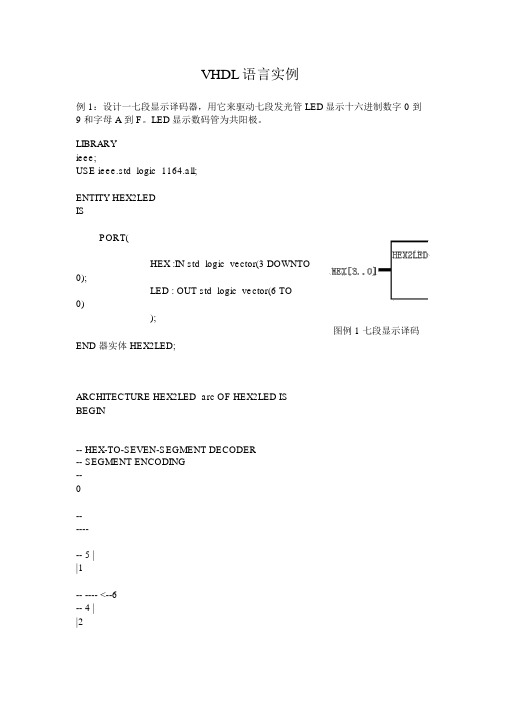

VHDL 语言实例例1:设计一七段显示译码器,用它来驱动七段发光管 到9和字母A 到F 。

LED 显示数码管为共阳极。

LIBRARY ieee;USE ieee.std_logic_1164.all; ENTITY HEX2LED ISP ORT(LED : OUT std_logic_vector(6 TO图例1七段显示译码器实体ARCHITECTURE HEX2LED_arc OF HEX2LED IS BEGIN--HEX-TO-SEVEN-SEGMENT DECODER --SEGMENT ENCODING--5 | |1-- — — — — --4 | |20);HEX2LEDHEX :IN std_logic_vector(3 DOWNTO HEXES. . 0]"0) );LED 显示十六进制数字0ENDHEX2LED;WITH HEX SELECTLED<= "1111001" when "0001","0100100" when "0010","0110000" when "0011","0011001" when "0100","0010010" when "0101","0000010" when "0110","1111000" when "0111","0000000" when "1000","0010000" when "1001","0001000" when "1010","0000011" when "1011","1000110" when "1100","0100001" when "1101","0000110" when "1110","0001110" when "1111","1000000" when others;END HEX2LED_arc;例 2 :设计一个八选一数据选择器1)s 是通道选择信号,d0,d1,d2,d3,d4,d5,d6,d7 数据输入out1 是数据输出ENTITY sels ISP ORT(d0,d1,d2,d3,d4,d5,d6,d7:IN BIT;s :INTEGERRANGE0 TO 7;END sels;ARCHITECTURE sels_arc OF sels IS BEGINWITH s SELECTout1 <= d0 WHEN 0, d1 WHEN 1, d2 WHEN 2, d3 WHEN 3,d4 WHEN 4,d5 WHEN 5, d6 WHEN 6, d7 WHEN 7;END sels_arc;LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux8 ISPORT(IO,I1,I2,I3,I4,I5,I6,I7,A,B,C:IN std_logic; END mux8;sels图例2 (a)八选一数据选择器实体图例2 (b)八选一数据选择器实体out1 :OUT BIT);2)A,B,C 是通道选择信号,据输出10,11,12,13,14,15,16,17数据输入 Q 是数Q :OUT std_logic);ARCHITECTURE mux8_arc OF mux8 ISSIGNAL sel :INTEGER ;BEGINQ <= 10 AFTER 10 ns WHEN sel= 0 ELSE11 AFTER 10 ns WHEN sel= 1 ELSE 12 AFTER 10 ns WHEN sel= 2 ELSE 13 AFTER 10 ns WHEN sel= 3 ELSE 14 AFTER 10 ns WHEN sel= 4 ELSE 15 AFTER 10 ns WHEN sel= 5 ELSE 16 AFTER 10 ns WHEN sel= 6 ELSE 17 AFTER 10 ns ;sel <= 0 WHEN A=‘ 0' AND B= ‘ 0' AND C= ‘ 0' ELSE1 WHEN A= '1' AND B= ‘ 0'AND C='0' ELSE2 WHEN A='0' AND B=‘1' AND C= '0' ELSE3 WHEN A='1' AND B=‘1' AND C='0' ELSE4 WHEN A='0' AND B=‘ 0'AND C= '1' ELSE5 WHEN A='1' AND B=‘ 0'AND C= '1' ELSE6 WHEN A='0' AND B=‘ 0'AND C= '1' ELSE7;END mux8_arc;例3:设计一 D 触发器 d 是输入端,clk 是时钟信号控制端,q 是触发器的输出端。

vhdl语言常用实例 -回复

vhdl语言常用实例-回复VHDL语言常用实例VHDL是一种硬件描述语言,广泛应用于数字系统的设计与验证中。

它提供了一种结构化的方式来描述电子系统的行为和结构。

在本篇文章中,将详细介绍VHDL语言的常用实例,并一步一步回答与之相关的内容。

1. VHDL的简介VHDL(VHSIC(Very High-Speed Integrated Circuit)Hardware Description Language)是一种用于描述和设计数字电路的硬件描述语言。

它是由美国国防部在20世纪80年代初提出并发展起来的,旨在解决高速集成电路设计的问题。

2. VHDL实例的编写步骤在编写VHDL实例之前,首先需要确定所要设计的电路的功能和结构。

接下来,可以根据电路的需求使用VHDL语言的各种特性来编写代码。

编写的过程可分为以下步骤:步骤一:定义实体在VHDL中,实体(Entity)用于描述电路的接口和输入输出信号的属性。

在定义实体时,需要指定实体的名称、输入输出端口以及信号类型。

步骤二:定义体(Architecture)定义体(Architecture)用于描述电路的功能和行为。

在定义体时,需要使用VHDL语言提供的语法和特性来描述所需的功能。

步骤三:模块化设计在VHDL中,可以使用模块化设计来实现复杂电路的描述和功能。

可以将电路划分为多个不同的模块,每个模块负责实现不同的功能。

通过将这些模块连接在一起,可以构建复杂的电路。

步骤四:仿真和验证在编写完VHDL代码后,可以使用仿真工具对代码进行验证。

通过仿真,可以模拟出电路的行为并检查其功能是否符合预期。

3. VHDL语言常用实例VHDL语言提供了丰富的语法和特性,可用于描述各种不同的电路和功能。

以下是几个常用的VHDL语言实例的示例:实例一:2-to-1多路选择器该实例描述了一个基本的2-to-1多路选择器电路。

此电路有两个输入信号A和B,一个选择信号S,一个输出信号Y。

(完整word版)VHDL语言实例

VHDL语言实例例 1:设计一七段显示译码器,用它来驱动七段发光管 LED显示十六进制数字 0 到9 和字母 A 到 F。

LED显示数码管为共阳极。

LIBRARYieee;USE ieee.std_logic_1164.all;ENTITY HEX2LEDISPORT(HEX :IN std_logic_vector(3 DOWNTO0);LED : OUT std_logic_vector(6 TO0));图例 1 七段显示译码END 器实体 HEX2LED;ARCHITECTURE HEX2LED_arc OF HEX2LED ISBEGIN--HEX-TO-SEVEN-SEGMENT DECODER--SEGMENT ENCODING----------5 ||1------ <--6--4 ||2--------3WITH HEX SELECTLED<= "1111001" when "0001","0100100" when "0010","0110000" when "0011","0011001" when "0100","0010010" when "0101","0000010" when "0110","1111000" when "0111","0000000" when "1000","0010000" when "1001","0001000" when "1010","0000011" when "1011","1000110" when "1100","0100001" when "1101","0000110" when "1110","0001110" when "1111","1000000" when others;END HEX2LED_arc;例 2:设计一个八选一数据选择器1)s 是通道选择信号 ,d0,d1,d2,d3,d4,d5,d6,d7数据输入out1 是数据输出ENTITY sels ISPORT(d0,d1,d2,d3,d4,d5,d6,d7:INBIT;s :INTEGERRANGE0TO7;out1 :OUT BIT);END sels;图例 2(a)八选一数据选择器实体ARCHITECTURE sels_arc OF sels ISBEGINWITH s SELECTout1 <= d0 WHEN 0,d1 WHEN 1,d2 WHEN 2,d3 WHEN 3,d4 WHEN 4,d5 WHEN 5,d6 WHEN 6,d7 WHEN 7;END sels_arc;2)A,B,C 是通道选择信号 ,I0,I1,I2,I3,I4,I5,I6,I7数据输入Q 是数据输出LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux8 ISPORT(I0,I1,I2,I3,I4,I5,I6,I7,A,B,C:INstd_logic;Q :OUT std_logic);END mux8;图例2(b) 八选一数据选择器实体ARCHITECTURE mux8_arc OF mux8 ISSIGNAL sel :INTEGER;BEGINQ <= I0 AFTER 10 ns WHEN sel= 0 ELSEI1 AFTER 10 ns WHEN sel= 1 ELSEI2 AFTER 10 ns WHEN sel= 2 ELSEI3 AFTER 10 ns WHEN sel= 3 ELSEI4 AFTER 10 ns WHEN sel= 4 ELSEI5 AFTER 10 ns WHEN sel= 5 ELSEI6 AFTER 10 ns WHEN sel= 6 ELSEI7 AFTER 10 ns ;sel <= 0 WHEN A= ‘0’ AND B= ‘0’ AND C= ‘0’ ELSE1 WHEN A=‘1’ AND B= ‘0’ AND C= ‘0’ ELSE2 WHEN A=‘0’ AND B= ‘1’ AND C= ‘0’ ELSE3 WHEN A=‘1’ AND B= ‘1’ AND C= ‘0’ ELSE4 WHEN A=‘0’ AND B= ‘0’ AND C= ‘1’ ELSE5 WHEN A=‘1’ AND B= ‘0’ AND C= ‘1’ ELSE6 WHEN A=‘0’ AND B= ‘0’ AND C= ‘1’ ELSE7;END mux8_arc;例 3:设计一 D触发器d 是输入端, clk 是时钟信号控制端, q 是触发器的输出端。

VHDL语言简单例子

VHDL语言简单例子4位二进制减计数器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY MIN ISPORT(clk,reset:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END MIN;ARCHITECTURE struc OF MIN ISSIGNAL q_temp:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk)BEGINIF(clk'EVENT AND clk='1')THENIF reset='0'THENq_temp<="1111";ELSIF q_temp<="0000" THENq_temp<="1111";ELSEq_temp<=q_temp-1;END IF;END IF;END PROCESS;q<=q_temp;END struc;从状态‘1111’到状态‘0000’,然后再跳回‘1111’。

异步复位不需要跟随脉冲变化,要立即复位。

8421码十进制计数器:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY TEN ISPORT(clk,reset:IN STD_LOGIC;q:OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END TEN;ARCHITECTURE struc OF TEN ISSIGNAL q_temp:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(clk)BEGINIF(clk'EVENT AND clk='1')THENIF reset='1'THENq_temp<="0000";ELSIF q_temp="1001"THENq_temp<="0000";ELSEq_temp<=q_temp+1;END IF;END IF;END PROCESS;q<=q_temp;END struc;从状态‘0000’到状态‘1001’,然后再跳回‘0000’,异步复位要立即复位。

vhdl设计实例

vhdl设计实例VHDL设计实例:数字电子钟引言:数字电子钟是一种常见的电子设备,用于显示当前时间。

本文将介绍如何使用VHDL设计一个简单的数字电子钟。

一、设计概述数字电子钟由时钟模块、数码管显示模块和控制模块组成。

时钟模块用于生成计时脉冲,数码管显示模块用于将时钟模块输出的计时脉冲转换为对应的数字显示,控制模块用于调整时钟和设置时间。

二、时钟模块设计时钟模块是整个电子钟的核心,它需要能够精确地生成计时脉冲。

使用VHDL语言,可以使用计数器和时钟分频器实现时钟模块。

计数器用于计数,时钟分频器用于将计数器的输出分频为1秒钟一次的脉冲。

三、数码管显示模块设计数码管显示模块用于将时钟模块输出的计时脉冲转换为数字显示。

在数码管显示模块中,每个数码管对应一个数字显示,通过切换不同的数码管,可以实现显示小时、分钟和秒钟。

使用VHDL语言,可以使用多路复用器和BCD转换器实现数码管显示模块。

四、控制模块设计控制模块用于调整时钟和设置时间。

通过增加按钮和减少按钮,可以实现调整时钟的功能。

通过设置按钮,可以进入设置时间的模式,并通过增加按钮和减少按钮设置小时、分钟和秒钟。

使用VHDL语言,可以使用状态机实现控制模块。

五、测试与验证在设计完成后,需要进行测试和验证。

可以使用仿真工具对设计的各个模块进行仿真,验证其功能是否正常。

同时,还可以将设计烧录到FPGA开发板上进行实际测试,确保数字电子钟能够正常工作。

六、总结本文以VHDL设计实例为题,详细介绍了数字电子钟的设计过程。

通过时钟模块、数码管显示模块和控制模块的设计,实现了一个简单的数字电子钟。

通过测试和验证,确保了设计的正确性和可靠性。

希望本文对读者理解VHDL设计实例并进行创作有所帮助。

通过自己的实践和研究,不断探索和创新,可以设计出更多实用的数字电子设备。

让我们一起努力,推动数字电子技术的发展!。

vhdl语言常用实例 -回复

vhdl语言常用实例-回复VHDL语言常用实例引言:VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,广泛应用于数字电路设计。

它提供了一种结构化的方法来描述电路的行为和功能,可以用来设计、模拟和验证数字电路。

本文将以VHDL语言常用实例为主题,逐步回答与VHDL语言相关的问题,帮助读者更好地理解和应用VHDL语言。

第一部分:VHDL语言基础1. 什么是VHDL语言?VHDL语言是一种硬件描述语言,用于描述和设计数字电路。

它提供了一种结构化的方法来描述电路的行为和功能,可以用于设计、模拟和验证数字电路。

2. VHDL语言有哪些基本元素?VHDL语言的基本元素有实体(Entity)、体(Architecture)、信号(Signal)、过程(Process)、端口(Port)等。

3. 如何定义VHDL的实体和体?VHDL的实体(Entity)负责描述电路的输入输出端口,类似于一个接口。

VHDL的体(Architecture)用于定义电路的内部工作原理,描述了电路的行为和功能。

第二部分:VHDL语言实例4. 如何使用VHDL语言实现一个简单的加法器?首先,在实体部分定义输入输出端口,例如:entity adder is port(a, b: in std_logic_vector(3 downto 0); sum: out std_logic_vector(3 downto 0));。

然后,在体部分用过程描述加法器的功能,例如:process(a, b) begin sum <= a + b; end process;。

5. 如何使用VHDL语言实现一个简单的寄存器?首先,在实体部分定义输入输出端口,例如:entity register is port(d: in std_logic_vector(7 downto 0); q: out std_logic_vector(7 downto 0); clk: in std_logic; rst: in std_logic);然后,在体部分用过程描述寄存器的功能,例如:process(clk, rst) begin if rst = '1' then q <= (others => '0'); elsif rising_edge(clk) then q <= d; end if; end process;。

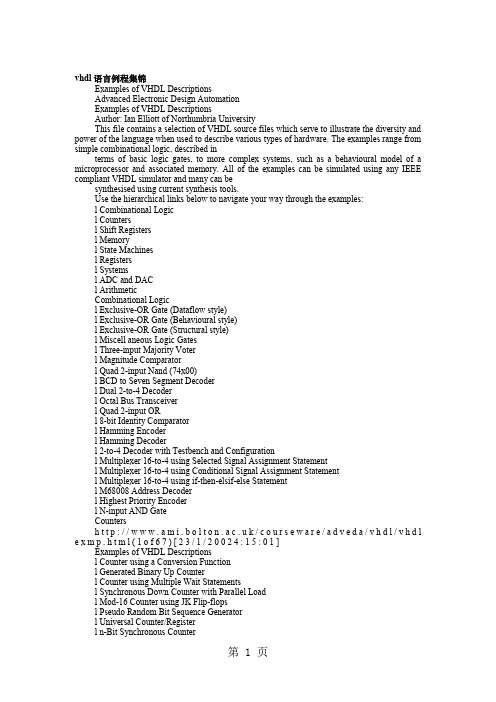

vhdl语言例程集锦共68页word资料

vhdl语言例程集锦Examples of VHDL DescriptionsAdvanced Electronic Design AutomationExamples of VHDL DescriptionsAuthor: Ian Elliott of Northumbria UniversityThis file contains a selection of VHDL source files which serve to illustrate the diversity and power of the language when used to describe various types of hardware. The examples range from simple combinational logic, described interms of basic logic gates, to more complex systems, such as a behavioural model of a microprocessor and associated memory. All of the examples can be simulated using any IEEE compliant VHDL simulator and many can besynthesised using current synthesis tools.Use the hierarchical links below to navigate your way through the examples:l Combinational Logicl Countersl Shift Registersl Memoryl State Machinesl Registersl Systemsl ADC and DACl ArithmeticCombinational Logicl Exclusive-OR Gate (Dataflow style)l Exclusive-OR Gate (Behavioural style)l Exclusive-OR Gate (Structural style)l Miscell aneous Logic Gatesl Three-input Majority Voterl Magnitude Comparatorl Quad 2-input Nand (74x00)l BCD to Seven Segment Decoderl Dual 2-to-4 Decoderl Octal Bus Transceiverl Quad 2-input ORl 8-bit Identity Comparatorl Hamming Encoderl Hamming Decoderl 2-to-4 Decoder with Testbench and Configurationl Multiplexer 16-to-4 using Selected Signal Assignment Statementl Multiplexer 16-to-4 using Conditional Signal Assignment Statementl Multiplexer 16-to-4 using if-then-elsif-else Statementl M68008 Address Decoderl Highest Priority Encoderl N-input AND GateCountersh t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 1 ]Examples of VHDL Descriptionsl Counter using a Conversion Functionl Generated Binary Up Counterl Counter using Multiple Wait Statementsl Synchronous Down Counter with Parallel Loadl Mod-16 Counter using JK Flip-flopsl Pseudo Random Bit Sequence Generatorl Universal Counter/Registerl n-Bit Synchronous CounterShift Registersl Universal Shift Register/Counterl TTL164 Shift Registerl Behavioural description of an 8-bit Shift Registerl Structural Description of an 8-bit Shift RegisterMemoryl ROM-based Waveform Generatorl A First-in First-out Memoryl Behavioural model of a 16-word, 8-bit Random Access Memoryl Behavioural model of a 256-word, 8-bit Read Only MemoryState Machinesl Classic 2-Process State Machine and Test Benchl State Machine using Variablel State Machine with Asynchronous Resetl Pattern Detector FSM with Test Benchl State Machine with Moore and Mealy outputsl Moore State Machine with Explicit State encodingl Mealy State Machine with Registered Outputsl Moore State Machine with Concurrent Output LogicSystemsl Pelican Crossing Controllerl Simple Microprocessor Systeml Booth Multiplierl Lottery Number Generatorl Digital Delay Unitl Chess ClockADC and DACl Package defining a Basic Analogue typel 16-bit Analogue to Digital Converterl 16-bit Digital to Analogue Converterl 8-bit Analogue to Digital Converterl 8-bit Unipolar Successive Approximation ADCh t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 2 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 7 ]Examples of VHDL DescriptionsArithmeticl 8-bit Unsigned Multiplierl n-bit Adder using the Generate Statementl A Variety of Adder Stylesl Booth MultiplierRegistersl Universal Registerl Octal D-Type Register with 3-State Outputsl Quad D-Type Flip-flopl 8-bit Register with Synchronous Load and ClearUniversal RegisterDescription - This design is a universal register which can be used as a straightforward storage register, a bi-directional shift register, an up counter and a down counter. The register can be loaded from a set of parallel data inputsand the mode is controlled by a 3-bit input. The 'termcnt' (terminal count) output goes high when the register contains zero.LIBRARY ieee;USE ieee.Std_logic_1164.ALL;USE ieee.Std_logic_unsigned.ALL;ENTITY unicntr ISGENERIC(n : Positive := 8); --size of counter/shifterPORT(clock, serinl, serinr : IN Std_logic; --serial inputsmode : IN Std_logic_vector(2 DOWNTO 0); --mode controldatain : IN Std_logic_vector((n-1) DOWNTO 0); --parallel inputsdataout : OUT Std_logic_vector((n-1) DOWNTO 0); --parallel outputstermcnt : OUT Std_logic); --terminal count outputEND unicntr;ARCHITECTURE v1 OF unicntr ISSIGNAL int_reg : Std_logic_vector((n-1) DOWNTO 0);BEGINmain_proc : PROCESSBEGINWAIT UNTIL rising_edge(clock);CASE mode IS--resetWHEN "000" => int_reg <= (OTHERS => '0');--parallel loadWHEN "001" => int_reg <= datain;--count upWHEN "010" => int_reg <= int_reg + 1;--count downWHEN "011" => int_reg <= int_reg - 1;--shift leftWHEN "100" => int_reg <= int_reg((n-2) DOWNTO 0) & serinl;--shift rightWHEN "101" => int_reg <= serinr & int_reg((n-1) DOWNTO 1);--do nothingWHEN OTHERS => NULL;END CASE;END PROCESS;det_zero : PROCESS(int_reg) --detects when count is 0BEGINtermcnt <= '1';FOR i IN int_reg'Range LOOPh t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 3 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL DescriptionsIF int_reg(i) = '1' THENtermcnt <= '0';EXIT;END IF;END LOOP;END PROCESS;--connect internal register to dataout portdataout <= int_reg;END v1;Octal D-Type Register with 3-State OutputsSimple model of an Octal D-type register with three-state outputs using two concurrent statements.LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY ttl374 ISPORT(clock, oebar : IN std_logic;data : IN std_logic_vector(7 DOWNTO 0);qout : OUT std_logic_vector(7 DOWNTO 0));END ENTITY ttl374;ARCHITECTURE using_1164 OF ttl374 IS--internal flip-flop outputsSIGNAL qint : std_logic_vector(7 DOWNTO 0);qint <= data WHEN rising_edge(clock); --d-type flip flopsqout <= qint WHEN oebar = '0' ELSE "ZZZZZZZZ"; --three-state buffersEND ARCHITECTURE using_1164;Exclusive-OR Gate (Dataflow style)-- 2 input exclusive or-- Modeled at the RTL level.entity x_or isport (in1 : in bit ;in2 : in bit ;out1 : out bit);end x_or;architecture rtl of x_or isbeginout1 <= in1 xor in2 after 10 ns;end rtl;Exclusive-OR Gate (Behavioural style)-- Exclusive or gate-- modeled at the behavioral level.entity x_or isport (in1 : in bit ;in2 : in bit ;out1 : out bit) ;end x_or;architecture behavior of x_or ish t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 4 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionsbeginprocess(in1, in2)beginif in1 = in2 thenout1 <= '0' after 10 ns;else out1 <= '1' after 10 ns;end if;end process;end behavior;Exclusive-OR Gate (Structural style)-- 2 input exclusive-or gate.-- Modeled at the structural level.entity x_or isport (in1 : in bit ;in2 : in bit ;out1 : out bit) ;end x_or;entity and_gate isport (a : in bit ;b : in bit ;c : out bit) ;end and_gate;architecture behavior of and_gate isbeginprocess(a,b)c <= a and b after 5 ns;end process;end behavior;entity or_gate isport (d : in bit ;e : in bit ;f : out bit) ;end or_gate;architecture behavior of or_gate isbeginprocess(d,e)beginf <= d or e after 4 ns;end process;end behavior;entity inverter isport (g : in bit ;h : out bit) ;end inverter;architecture behavior of inverter isbeginprocess(g)beginh <= not g after 3 ns;end process;end behavior;h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 5 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionsarchitecture structural of x_or is-- signal declarationssignal t1, t2, t3, t4 : bit;-- local component declarationscomponent and_gateport (a, b : in bit; c : out bit) ;end component;component or_gateport (d, e : in bit; f : out bit) ;end component;component inverterport (g : in bit; h : out bit) ;end component;begin-- component instantiation statementsu0: and_gate port map ( a => t1, b => in2, c => t3);u1: and_gate port map ( a => in1, b => t2, c => t4);u2: inverter port map ( g => in1, h => t1);u3: inverter port map ( g => in2, h => t2);u4: or_gate port map ( d => t3, e => t4, f => out1);end structural;Three-input Majority VoterThe entity declaration is followed by three alternative architectures which achieve the same functionality in different ways.ENTITY maj ISPORT(a,b,c : IN BIT; m : OUT BIT);END maj;--Dataflow style architectureARCHITECTURE concurrent OF maj ISBEGIN--selected signal assignment statement (concurrent)WITH a&b&c SELECTm <= '1' WHEN "110"|"101"|"011"|"111",'0' WHEN OTHERS;END concurrent;--Structural style architectureARCHITECTURE structure OF maj IS--declare components used in architectureCOMPONENT and2 PORT(in1, in2 : IN BIT; out1 : OUT BIT);END COMPONENT;COMPONENT or3 PORT(in1, in2, in3 : IN BIT; out1 : OUT BIT);END COMPONENT;--declare local signalsSIGNAL w1, w2, w3 : BIT;BEGIN--component instantiation statements.--ports of component are mapped to signals--within architecture by position.gate1 : and2 PORT MAP (a, b, w1);gate2 : and2 PORT MAP (b, c, w2);gate3 : and2 PORT MAP (a, c, w3);gate4 : or3 PORT MAP (w1, w2, w3, m);h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 6 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL DescriptionsEND structure;--Behavioural style architecture using a look-up tableARCHITECTURE using_table OF maj ISBEGINPROCESS(a,b,c)CONSTANT lookuptable : BIT_VECTOR(0 TO 7) := "00010111";VARIABLE index : NATURAL;BEGINindex := 0; --index must be cleared each time process executesIF a = '1' THEN index := index + 1; END IF;IF b = '1' THEN index := index + 2; END IF;IF c = '1' THEN index := index + 4; END IF;m <= lookuptable(index);END PROCESS;END using_table;Magnitude Comparator--VHDL description of a 4-bit magnitude comparator with expansion inputs--first architecture demonstrates use of relational operators on--bit vectors (=,>,<).Second architecture shows sequential behaviour--description.Both descriptions do not fully model behaviour of real--device for all possible combinations of inputs.ENTITY mag4comp ISGENERIC(eqdel,gtdel,ltdel : TIME := 10 ns); --output delay parametersPORT(a,b : IN BIT_VECTOR(3 DOWNTO 0); --input words, DOWNTO orderingneeded for comparison operatorsaeqbin,agtbin,altbin : IN BIT; --expansion inputsaeqbout,agtbout,altbout : OUT BIT); --outputsEND mag4comp;ARCHITECTURE dataflow OF mag4comp IS--this architecture assumes that only one of the expansion inputs--is active at any time,if more than one expansion input is active,--more than one output may be active.BEGINaeqbout <= '1' AFTER eqdel WHEN ((a = b) AND (aeqbin = '1'))ELSE '0' AFTER eqdel;agtbout <= '1' AFTER gtdel WHEN ((a > b) OR ((a = b) AND (agtbin = '1')))ELSE '0' AFTER gtdel;altbout <= '1' AFTER ltdel WHEN ((a < b) OR ((a = b) AND (altbin = '1')))ELSE '0' AFTER ltdel;END dataflow;ARCHITECTURE behaviour OF mag4comp ISBEGINPROCESS(a,b,aeqbin,agtbin,altbin)BEGINIF (a > b) THENagtbout <= '1' AFTER gtdel;aeqbout <= '0' AFTER eqdel;altbout <= '0' AFTER ltdel;ELSIF (a < b) THENaltbout <= '1' AFTER ltdel;aeqbout <= '0' AFTER eqdel;agtbout <= '0' AFTER gtdel;ELSE --a=b,expansion inputs have priority orderingIF (aeqbin = '1') THENaeqbout <= '1' AFTER eqdel;agtbout <= '0' AFTER gtdel;altbout <= '0' AFTER ltdel;ELSIF (agtbin = '1') THENagtbout <= '1' AFTER gtdel;altbout <= '0' AFTER ltdel;h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 7 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionsaeqbout <= '0' AFTER eqdel;ELSIF (altbin = '1') THENagtbout <= '0' AFTER gtdel;altbout <= '1' AFTER ltdel;aeqbout <= '0' AFTER eqdel;ELSEagtbout <= '0' AFTER gtdel;altbout <= '0' AFTER ltdel;aeqbout <= '0' AFTER eqdel;END IF;END IF;END PROCESS;END behaviour;8-bit Register with Synchronous Load and ClearThe design entity shows the standard way of describing a register using a synchronous process, ie. a process containing a single wait statement which is triggered by a rising edge on the clock input.library ieee;use ieee.std_logic_1164.all;entity reg8 isport(clock, clear, load : in std_logic;d : in std_logic_vector(7 downto 0);q : out std_logic_vector(7 downto 0));end entity reg8;architecture v1 of reg8 isbeginreg_proc : processbeginwait until rising_edge(clock);if clear = '1' thenq <= (others => '0');elsif load = '1' thenq <= d;end if;end process;end architecture v1;BCD to Seven Segment DecoderThe use of the std_logic literal '-' (don't care) is primarily for the synthesis tool. This example illustrates the use of the selected signal assignment.LIBRARY ieee;USE ieee.std_logic_1164.ALL;ENTITY seg7dec ISPORT(bcdin : IN std_logic_vector(3 DOWNTO 0);segout : OUT std_logic_vector(6 DOWNTO 0));END seg7dec;ARCHITECTURE ver3 OF seg7dec ISBEGINWITH bcdin SELECTsegout <= "1000000" WHEN X"0","1100111" WHEN X"1","1101101" WHEN X"2","0000011" WHEN X"3","0100101" WHEN X"4","0001001" WHEN X"5","0001000" WHEN X"6","1100011" WHEN X"7","0000000" WHEN X"8",h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 8 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptions"0000001" WHEN X"9","-------" WHEN OTHERS;END ver3;2-to-4 Decoder with Testbench and ConfigurationThis set of design units illustrates several features of the VHDL language including:l Using generics to pass time delay v alues to design entities.l Design hierarchy using instantiated components.l Test benches for design verification.l Configuration declaration for binding components to design entities and setting delay v alues.--ANATOMY OF A VHDL MODEL--This VHDL source description illustrates the use--of the basic constructs of VHDL.--The model describes a 2-input/4-output decoder--comprising two behavioural primitives 'inv' and 'and3'--instanced in a structure.ENTITY inv ISGENERIC(tplh,tphl,tplhe,tphle : TIME := 1 ns);PORT(a : IN BIT; b : OUT BIT);END inv;ARCHITECTURE behaviour OF inv ISBEGINPROCESS(a)VARIABLE state : BIT;BEGINstate := NOT(a);IF state = '1' THENb <= state AFTER (tplh + tplhe);ELSEb <= state AFTER (tphl + tphle);END IF;END PROCESS;END behaviour;ENTITY and3 ISGENERIC(tplh,tphl,tplhe,tphle : TIME := 1 ns);PORT(a1,a2,a3 : IN BIT; o1 : OUT BIT);END and3;ARCHITECTURE behaviour OF and3 ISBEGINPROCESS(a1,a2,a3)VARIABLE state : BIT;BEGINstate := a1 AND a2 AND a3;IF state = '1' THENo1 <= state AFTER (tplh + tplhe);ELSEo1 <= state AFTER (tphl + tphle);END IF;END PROCESS;END behaviour;ENTITY dec2to4 ISPORT(s0,s1,en : IN BIT; y0,y1,y2,y3 : OUT BIT);END dec2to4;ARCHITECTURE structural OF dec2to4 ISCOMPONENT invh t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 9 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL DescriptionsPORT(a : IN BIT; b : OUT BIT); END COMPONENT;COMPONENT and3PORT(a1,a2,a3 : IN BIT; o1 : OUT BIT); END COMPONENT;SIGNAL ns0,ns1 : BIT;BEGINi1 : inv PORT MAP(s0,ns0);i2 : inv PORT MAP(s1,ns1);a1 : and3 PORT MAP(en,ns0,ns1,y0);a2 : and3 PORT MAP(en,s0,ns1,y1);a3 : and3 PORT MAP(en,ns0,s1,y2);a4 : and3 PORT MAP(en,s0,s1,y3);END structural;ENTITY dec2to4_stim ISPORT(stimulus : OUT BIT_VECTOR(0 TO 2); response : IN BIT_VECTOR(0 TO 3));END dec2to4_stim;ARCHITECTURE behavioural OF dec2to4_stim ISBEGINstimulus <= TRANSPORT "000" AFTER 0 ns,"100" AFTER 100 ns,"010" AFTER 200 ns,"110" AFTER 300 ns,"001" AFTER 400 ns,"101" AFTER 500 ns,"011" AFTER 600 ns,"111" AFTER 700 ns;END behavioural;ENTITY dec2to4_bench ISEND dec2to4_bench;ARCHITECTURE structural OF dec2to4_bench ISCOMPONENT dec2to4PORT(s0,s1,en : IN BIT; y0,y1,y2,y3 : OUT BIT);END COMPONENT;COMPONENT dec2to4_stimPORT(stimulus : OUT BIT_VECTOR(0 TO 2); response : IN BIT_VECTOR(0 TO 3));END COMPONENT;SIGNAL stimulus : BIT_VECTOR(0 TO 2);SIGNAL response : BIT_VECTOR(0 TO 3);BEGINgenerator : dec2to4_stim PORT MAP(stimulus,response);circuit : dec2to4 PORT MAP(stimulus(1),stimulus(2),stimulus(0),response(0),response(1),response(2),response(3));END structural;CONFIGURATION parts OF dec2to4_bench ISFOR structuralFOR generator : dec2to4_stimUSE ENTITY work.dec2to4_stim(behavioural);END FOR;FOR circuit : dec2to4USE ENTITY work.dec2to4(structural);FOR structuralFOR ALL : invUSE ENTITY work.inv(behaviour)GENERIC MAP(tplh => 10 ns,h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 0 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionstphl => 7 ns,tplhe => 15 ns,tphle => 12 ns);END FOR;FOR ALL : and3USE ENTITY work.and3(behaviour)GENERIC MAP(tplh => 8 ns,tphl => 5 ns,tplhe => 20 ns,tphle => 15 ns);END FOR;END FOR;END FOR;END FOR;END parts;Generated Binary Up CounterThe first design entity is a T-type flip-flop. The second is an scalable synchronous binary up counter illustrating the use of the generate statement to produce regular structures of components.library ieee;use ieee.std_logic_1164.all;entity tff isport(clk, t, clear : in std_logic; q : buffer std_logic);end tff;architecture v1 of tff isbeginprocess(clear, clk)beginif clear = '1' thenq <= '0';elsif rising_edge(clk) thenif t = '1' thenq <= not q;elsenull;end if;end if;end process;end v1;library ieee;use ieee.std_logic_1164.all;entity bigcntr isgeneric(size : positive := 32);port(clk, clear : in std_logic;q : buffer std_logic_vector((size-1) downto 0));end bigcntr;architecture v1 of bigcntr iscomponent tff isport(clk, t, clear : in std_logic; q : buffer std_logic);end component;signal tin : std_logic_vector((size-1) downto 0);begingenttf : for i in (size-1) downto 0 generatettype : tff port map (clk, tin(i), clear, q(i));end generate;genand : for i in 0 to (size-1) generatet0 : if i = 0 generateh t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 1 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionstin(i) <= '1';end generate;t1_size : if i > 0 generatetin(i) <= q(i-1) and tin(i-1);end generate;end generate;end v1;Counter using Multiple Wait StatementsThis example shows an inefficient way of describing a counter.--vhdl model of a 3-state counter illustrating the use--of the WAIT statement to suspend a process.At each wait--statement the simulation time is updated one cycle,transferring--the driver v alue to the output count.--This architecture shows that there is no difference between--WAIT UNTIL (clock'EVENT AND clock = '1') and WAIT UNTIL clock = '1'ENTITY cntr3 ISPORT(clock : IN BIT; count : OUT NATURAL);END cntr3;ARCHITECTURE using_wait OF cntr3 ISBEGINPROCESSBEGIN--WAIT UNTIL (clock'EVENT AND clock = '1');WAIT UNTIL clock = '1';count <= 0;--WAIT UNTIL (clock'EVENT AND clock = '1');WAIT UNTIL clock = '1';count <= 1;--WAIT UNTIL (clock'EVENT AND clock = '1');WAIT UNTIL clock = '1';count <= 2;END PROCESS;END using_wait;Counter using a Conversion FunctionThis counter uses a natural number to hold the count v alue and converts it into a bit_vector for output. Illustrates the use of a function.--4-bit binary up counter with asynchronous reset 2/2/93ENTITY cntr4bit ISPORT(reset,clock : IN BIT; count : OUT BIT_VECTOR(0 TO 3));END cntr4bit;ARCHITECTURE dataflow OF cntr4bit IS--interface function to generate output bit_vector from--internal count v alue.FUNCTION nat_to_bv(input : NATURAL; highbit : POSITIVE)RETURN BIT_VECTOR ISVARIABLE temp : NATURAL := 0;VARIABLE output : BIT_VECTOR(0 TO highbit);BEGINtemp := input;--check that input fits into (highbit+1) bitsASSERT (temp <= (2**(highbit + 1) - 1))REPORT "input no. is out of range" SEVERITY ERROR;h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 2 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptions--generate bit v aluesFOR i IN highbit DOWNTO 0 LOOPIF temp >= (2**i)THEN output(i) := '1';temp := temp - (2**i);ELSE output(i) := '0';END IF;END LOOP;RETURN output;END nat_to_bv;--signal to hold current count v alueSIGNAL intcount : NATURAL := 0;BEGIN--conditional natural signal assignment models counterintcount <= 0 WHEN (reset = '1') ELSE((intcount + 1) MOD 16) WHEN (clock'EVENT AND clock = '1')ELSE intcount;--interface function converts natural count to bit_vector countcount <= nat_to_bv(intcount,3);END;Quad 2-input NandSimple concurrent model of a TTL quad nand gate.--uses 1993 std VHDLlibrary IEEE;use IEEE.Std_logic_1164.all;entity HCT00 isport(A1, B1, A2, B2, A3, B3, A4, B4 : in std_logic;Y1, Y2, Y3, Y4 : out std_logic);end HCT00;architecture VER1 of HCT00 isbeginY1 <= A1 nand B1 after 10 ns;Y2 <= A2 nand B2 after 10 ns;Y3 <= A3 nand B3 after 10 ns;Y4 <= A4 nand B4 after 10 ns;end VER1;Dual 2-to-4 DecoderA set of conditional signal assignments model a dual 2-to-4 decoder--uses 1993 std VHDLlibrary IEEE;use IEEE.Std_logic_1164.all;entity HCT139 isport(A2, B2, G2BAR, A1, B1, G1BAR : in std_logic;Y20, Y21, Y22, Y23, Y10, Y11, Y12, Y13 : out std_logic);end HCT139;architecture VER1 of HCT139 isbeginY10 <= '0' when (B1 = '0') and ((A1 = '0') and (G1BAR = '0')) else '1';Y11 <= '0' when (B1 = '0') and ((A1 = '1') and (G1BAR = '0')) else '1';Y12 <= '0' when (B1 = '1') and ((A1 = '0') and (G1BAR = '0')) else '1';Y13 <= '0' when (B1 = '1') and ((A1 = '1') and (G1BAR = '0')) else '1';Y20 <= '0' when (B2 = '0') and ((A2 = '0') and (G2BAR = '0')) else '1';h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 3 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL DescriptionsY21 <= '0' when (B2 = '0') and ((A2 = '1') and (G2BAR = '0')) else '1';Y22 <= '0' when (B2 = '1') and ((A2 = '0') and (G2BAR = '0')) else '1';Y23 <= '0' when (B2 = '1') and ((A2 = '1') and (G2BAR = '0')) else '1';end VER1;Quad D-Type Flip-flopThis example shows how a conditional signal assignment statement could be used to describe sequential logic (it is more common to use a process). The keyword 'unaffected' is equivalent to the 'null' statement in the sequential partof the language. The model would work exactly the same without the clause 'else unaffected' attached to the end of the statement.--uses 1993 std VHDLlibrary IEEE;use IEEE.Std_logic_1164.all;entity HCT175 isport(D : in std_logic_vector(3 downto 0);Q : out std_logic_vector(3 downto 0);CLRBAR, CLK : in std_logic);end HCT175;architecture VER1 of HCT175 isbeginQ <= (others => '0') when (CLRBAR = '0')else D when rising_edge(CLK)else unaffected;end VER1;Octal Bus TransceiverThis example shows the use of the high impedance literal 'Z' provided by std_logic. The aggregate '(others => 'Z')' means all of the bits of B must be forced to 'Z'. Ports A and B must be resolved for this model to work correctly (hence std_logic rather thanstd_ulogic).library IEEE;use IEEE.Std_logic_1164.all;entity HCT245 isport(A, B : inout std_logic_vector(7 downto 0);DIR, GBAR : in std_logic);end HCT245;architecture VER1 of HCT245 isbeginA <=B when (GBAR = '0') and (DIR = '0') else (others => 'Z');B <= A when (GBAR = '0') and (DIR = '1') else (others => 'Z');end VER1;Quad 2-input OR--uses 1993 std VHDLlibrary IEEE;use IEEE.Std_logic_1164.all;entity HCT32 isport(A1, B1, A2, B2, A3, B3, A4, B4 : in std_logic;Y1, Y2, Y3, Y4 : out std_logic);end HCT32;architecture VER1 of HCT32 isbeginY1 <= A1 or B1 after 10 ns;Y2 <= A2 or B2 after 10 ns;Y3 <= A3 or B3 after 10 ns;Y4 <= A4 or B4 after 10 ns;h t t p : / / w w w . a m i . b o l t o n . a c . u k / c o u r s e w a r e / a d v e d a / v h d l / v h d l e x m p . h t m l ( 1 4 o f 6 7 ) [ 2 3 / 1 / 2 0 0 2 4 : 1 5 : 0 8 ]Examples of VHDL Descriptionsend VER1;8-bit Identity Comparator--uses 1993 std VHDLlibrary IEEE;use IEEE.Std_logic_1164.all;entity HCT688 isport(Q, P : in std_logic_vector(7 downto 0);GBAR : in std_logic; PEQ : out std_logic);end HCT688;architecture VER1 of HCT688 isbeginPEQ <= '0' when ((To_X01(P) = To_X01(Q)) and (GBAR = '0')) else '1';end VER1;Hamming EncoderA 4-bit Hamming Code encoder using concurrent assignments. The output vector is connected to the individual parity bits using an aggregate assignment.ENTITY hamenc ISPORT(datain : IN BIT_VECTOR(0 TO 3); --d0 d1 d2 d3hamout : OUT BIT_VECTOR(0 TO 7)); --d0 d1 d2 d3 p0 p1 p2 p4END hamenc;ARCHITECTURE ver2 OF hamenc IS。

第三章VHDL程序设计案例

第三章VHDL程序设计案例

37

带允许端的十二进制计数器

第三章VHDL程序设计案例

38

可逆计数器(加减计数器)

第三章VHDL程序设计案例

39

可逆计数器仿真结果:

第三章VHDL程序设计案例

40

例:六十进制(分、秒)计数器

第三章VHDL程序设计案例

end decoder;

architecture rtl of decoder is

begin

process(inp)

begin

outp<=(others=>’0’);

outp(conv_integer(inp))<=‘1’;

end process;

end rtl;

第三章VHDL程序设计案例

sel=000 sel =001 sel =010 sel =011 sel =100 sel =101 sel =110 sel =111

第三章VHDL程序设计案例

25

clock sig_in reset 同步复位 sig_out1 异步复位 sig_out2

第三章VHDL程序设计案例

26

二) 常用时序电路设计

1、触发器(Flip_Flop) 1)D触发器

第三章VHDL程序设计案例

27

异步置位/复位D触发器

第三章VHDL程序设计案例

1)“”序列发生器

第三章VHDL程序设计案例

49

第三章VHDL程序设计案例

50

第三章VHDL程序设计案例

51

仿真结果:

第三章VHDL程序设计案例

52

2)序列信号检测器的状态机设计与实现, 检测“”

第6讲vhdl语言实际举例

数据选择器

四路数据选择器说明WITH语句用法 语句用法 四路数据选择器说明

ENTITY sels IS PORT(d0,d1,d2,d3:IN BIT; s :IN INTEGER RANGE 0 TO 3; out1 :OUT BIT); END sels; ARCHITECTURE sels_arc OF sels IS BEGIN WITH s SELECT d0 d1 out1 <= d0 WHEN 0, d2 d1 WHEN 1, d3 s d2 WHEN 2, d3 WHEN 3; END sels_arc;

.. .. .. Y7

IF (G1=1 and G2a=0 and G2b=0 ) CASE indata IS WHEN “000” => Y <= “11111110”; WHEN “001” => Y <= “11111101”; WHEN “010” => Y <= “11111011”; WHEN “011” => Y <= “11110111”; WHEN “100” => Y <= “11101111”; WHEN “101” => Y <= “11011111”; WHEN “110” => Y <= “10111111”; WHEN “111” => Y <= “01111111”; WHEN OTHERS => Y <= NULL; END CASE; ELSE Y <= “11111111” ; END IF; END PROCESS; END decoder_arc;

D触发器说明时钟边沿描述的用法 触发器说明时钟边沿描述的用法

ENTITY DFF1 IS PORT(clk:IN STD_LOGIC; D :IN STD_LOGIC; Q:OUT STD_LOGIC); END DFF1; ARCHITECTURE DFF_arc OF DFF1 IS BEGIN

第4章-VHDL应用实例

indata<=c&b&a; process(indata,g1,g2a,g2b)

begin if(g1='1' and g2a='0' and g2b='0') then case indata is

end case;

else y<="11111111"; end if;

LIBRARY ieee; USE ieee.std_logic_1164.all; entity decoder38 is port(a,b,c,g1,g2a,g2b:in std_logic;

y:out std_logic_vector(7 downto 0)); end decoder38; architecture behave38 OF decoder38 is signal indata:std_logic_vector(2 downto 0); begin

entity nor2 is

port(a,b:in std_logic; y:out std_logic);

end nor2;

architecture ቤተ መጻሕፍቲ ባይዱor_behave of nor2 is

begin

y<=a nor b; end nor_behave; 【例4.3】2输入异或门电路 library ieee; use ieee.std_logic_1164.all;

when "010"=>y<="11111011";

when "011"=>y<="11110111"; when "100"=>y<="11101111"; when "101"=>y<="11011111"; when "110"=>y<="10111111"; when "111"=>y<="01111111";

vhdl with select语句

vhdl with select语句VHDL(Very High Speed Integrated Circuit Hardware Description Language)是一种硬件描述语言,用于描述数字电路的行为和结构。

在VHDL中,select语句是一种条件语句,用于根据给定条件选择执行不同的操作。

下面将列举10个使用select语句的VHDL示例。

1. 使用select语句实现一个简单的多路选择器。

该多路选择器有4个输入信号和2个选择信号,根据选择信号的值选择相应的输入信号作为输出。

```vhdlentity mux isport (a, b, c, d : in bit;sel1, sel2 : in bit;out : out bit);end entity mux;architecture behavioral of mux isbeginprocess (sel1, sel2, a, b, c, d)begincase sel1 & sel2 iswhen "00" => out <= a;when "01" => out <= b;when "10" => out <= c;when "11" => out <= d;when others => out <= 'X';end case;end process;end architecture behavioral;```2. 使用select语句实现一个4位二进制加法器。

该加法器有两个4位输入信号和一个进位信号,根据进位信号的值选择使用全加器或半加器进行相应位的加法运算。

```vhdlentity adder isport (a, b : in std_logic_vector(3 downto 0);cin : in std_logic;sum : out std_logic_vector(3 downto 0);cout : out std_logic);end entity adder;architecture structural of adder iscomponent full_adder isport (a, b, cin : in std_logic;sum, cout : out std_logic);end component full_adder;component half_adder isport (a, b : in std_logic;sum, cout : out std_logic);end component half_adder;beginprocess (a, b, cin)beginfor i in 0 to 3 loopcase cin iswhen '0' =>sum(i) <= half_adder(a(i), b(i), sum(i), cout(i));when '1' =>sum(i) <= full_adder(a(i), b(i), sum(i), cout(i));end case;end loop;end process;end architecture structural;```3. 使用select语句实现一个优先级编码器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

VHDL语言实例例1:设计一七段显示译码器,用它来驱动七段发光管LED显示十六进制数字0到9和字母A到F。

LED显示数码管为共阳极。

LIBRARYieee;USE ieee.std_logic_1164.all;ENTITY HEX2LEDISPORT(HEX :IN std_logic_vector(3 DOWNTO0);LED : OUT std_logic_vector(6 TO0));ENDHEX2LED; 图例1 七段显示译码器实体ARCHITECTURE HEX2LED_arc OF HEX2LED IS BEGIN-- HEX-TO-SEVEN-SEGMENT DECODER-- SEGMENT ENCODING---------- 5 ||1-- ---- <--6-- 4 ||2--------3WITH HEX SELECTLED<= "1111001" when "0001","0100100" when "0010","0110000" when "0011","0011001" when "0100","0010010" when "0101","0000010" when "0110","1111000" when "0111","0000000" when "1000","0010000" when "1001","0001000" when "1010","0000011" when "1011","1000110" when "1100","0100001" when "1101","0000110" when "1110","0001110" when "1111","1000000" when others;END HEX2LED_arc;例2:设计一个八选一数据选择器1)s是通道选择信号, d0,d1,d2,d3,d4,d5,d6,d7数据输入 out1是数据输出ENTITY sels ISPORT(d0,d1,d2,d3,d4,d5,d6,d7:INBIT;s :INTEGER RANGE0 TO 7;out1 :OUT BIT);END sels;图例2(a) 八选一数据选择器实体ARCHITECTURE sels_arc OF sels ISBEGINWITH s SELECTout1 <= d0 WHEN 0,d1 WHEN 1,d2 WHEN 2,d3 WHEN 3,d4 WHEN 4,d5 WHEN 5,d6 WHEN 6,d7 WHEN 7;END sels_arc;2)A,B,C是通道选择信号, I0,I1,I2,I3,I4,I5,I6,I7数据输入 Q是数据输出LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY mux8 ISPORT(I0,I1,I2,I3,I4,I5,I6,I7,A,B,C:INstd_logic;Q :OUT std_logic);END mux8;图例2(b) 八选一数据选择器实体SIGNAL sel :INTEGER ;BEGINQ <= I0 AFTER 10 ns WHEN sel= 0 ELSEI1 AFTER 10 ns WHEN sel= 1 ELSEI2 AFTER 10 ns WHEN sel= 2 ELSEI3 AFTER 10 ns WHEN sel= 3 ELSEI4 AFTER 10 ns WHEN sel= 4 ELSEI5 AFTER 10 ns WHEN sel= 5 ELSEI6 AFTER 10 ns WHEN sel= 6 ELSEI7 AFTER 10 ns ;sel <= 0 WHEN A= ‘0’ AND B= ‘0’ AND C= ‘0’ ELSE1 WHEN A= ‘1’ AND B= ‘0’ AND C= ‘0’ ELSE2 WHEN A= ‘0’ AND B= ‘1’ AND C= ‘0’ ELSE3 WHEN A= ‘1’ AND B= ‘1’ AND C= ‘0’ ELSE4 WHEN A= ‘0’ AND B= ‘0’ AND C= ‘1’ EL SE5 WHEN A= ‘1’ AND B= ‘0’ AND C= ‘1’ ELSE6 WHEN A= ‘0’ AND B= ‘0’ AND C= ‘1’ ELSE7;END mux8_arc;例3:设计一D触发器d是输入端,clk是时钟信号控制端,q是触发器的输出端。

其程序如下:LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY reg ISPORT(d,clk:IN BIT;q:OUTBIT);END reg;图例3 D触发器实体BEGINPROCESSBEGINWAIT UNTIL clk= ‘1’;q <= d;END PROCESS;PROCESSEND reg_arc;例4:设计一基本RS触发器r、s为触发器的输入信号,q、not_q为触发器的输出信号。

LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY RSFF ISPORT(r,s:IN BIT;q,not_q:OUTBIT);END RSFF;图例4 基本RS触发器实体ARCHITECTURE RSFF_arc OF RSFF ISBEGINPROCESS(r,s)VARIABLE last_state:BIT:= ‘0’;BEGINASSERT NOT(r= ‘1’ AND s= ‘1’)REPORT “Both r AND s equal to ‘1’”SEVERITY error;IF r= ‘0’ AND s= ‘0’ THENlast_state:= last_state ;ELSIF r= ‘1’ AND s= ‘0’ THENlast_state:= ‘0’;ELSE -- r= ‘0’ AND s= ‘1’last_state:= ‘1’;END IF;q <= last_state AFTER 10 ns;not_q <= NOT(last_state) AFTER 20 ns;END PROCESS;END RSFF_arc;当r和s同时等于1时,触发器处于不定状态。

程序设计中设置了断言语句是为了判断r和s都等于1时,输出终端将显示报告“Both r AND s equal to ‘1’”,同时终止模拟过程,并显示错误的严重error,以便设计者调试和修正模块程序。

从IF到END IF是条件语句,用到了可选项ELSIF和ELSE来判别RS触发器的其它三种情况。

IF语句后面是一赋值语句,将IF语句中赋值的中间变量lsat_state 经10 ns后送到q端。

图8-12是RS触发器的逻辑电路图。

例5:设计一个带有异步清零、同步置数、使能控制的四位二进制计数器LIBRARY ieee;USE ieee.std_logic_1164.all;ENTITY COUNT2 ISPORT(A: IN INTEGER RANGE0 TO 3;CLK: INSTD_LOGIC;CLR: INSTD_LOGIC;EN: INSTD_LOGIC;LD: IN图例5 四位二进制计数器实体STD_LOGIC;Cout: OUTINTEGER RANGE 0 TO 3);END COUNT2;ARCHITECTURE COUNT2_arc OF COUNT2 ISSIGNAL SIG: INTEGER RANGE 0 TO 3;BEGINPROCESS (CLK, CLR)BEGINIF CLR = '0' THENSIG <= 0;ELSIF (CLK'EVENT AND CLK = '1') THENIF LD = '1' THENSIG <= A;ELSEIF EN = '1' THENSIG <= SIG + 1;ELSESIG <= SIG;END IF;END IF;END IF;END PROCESS;Cout <= SIG;END COUNT2_arc例6:设计一个存储容量为28×8的RAM。

CS为RAM的片选信号,WR为RAM的写信号,RD为RAM读信号,ADR:八位地址信号,Din:八位数据输入线,Dout为八位数据输出线。

library IEEE;use IEEE.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity RAM isport (WR: in STD_LOGIC;RD:in STD_LOGIC;ADR:in STD_LOGIC_VECTOR (7 downto 0);CS:in STD_LOGIC;Din:in STD_LOGIC_VECTOR (7 downto 0);图例6 RAM实体Dout:out STD_LOGIC_VECTOR (7 downto 0));end RAM;architecture RAM_arch of RAM issubtype word is std_logic_vector(7 downto 0);type memory is array (0 to 15)of word;signal adr_in:integer range 0 to 15;signal sram:memory;beginadr_in<=conv_integer(ADR);process(wr)beginif(wr'event and wr='1')thenif(cs='1'and wr='1')thensram(adr_in)<=din after 2 ns;end if;end if;end process;process(rd,cs)beginif(rd='0'and cs='1')thendout<=sram(adr_in)after 3 ns;elsedout<="ZZZZZZZZ"after 4 ns;end if;end process;end RAM_arch;例7:利用枚举类型设计一个状态机,用灯的颜色代表相应的状态名。