1SMA5934BT3中文资料

无线AP参数指标

支持IPSec VPN、L2TP VPN、GRE VPN、L2TP over IPSec VPN、GRE over IPSec VPN等VPN组网;

虚拟防火墙

支持虚拟防火墙功能,可划分的虚拟防火墙数量≥5个;

网络地址转换(NAT)

支持完善的网络地址转换功能,包括源IP地址转换、目的IP地址转换、端口地址转换、静态IP地址转换、IP地址池转换等;支持扩展NAT功能,可实现单个公网IP的无限地址转换;支持FTP、H.323、SIP等各种应用协议;

*URL过滤

提供URL过滤豁免IP列表;提供URL黑白名单功能;支持前缀匹配,后缀匹配,关键字匹配等,URL支持到page;支持用户自定义URL分类;URL过滤响面内容可自定义;支持URL访问日志记录,支持日志归并;

双机热备

支持双机热备及会话同步;支持热补丁技术,系统升级时不中断业务;

*电源模块

配置双冗余电源且支持热插拔;

性能指标

防火墙吞吐量

大包(1024及以上字节)吞吐量≥3Gbps;

*小包(64字节)吞吐量≥1Gbps;

最大并发连接数

最大并发连接数≥300万;

*每秒新建连接数

每秒新建连接数≥5万;

功能要求

状态检测包过滤

能够基于源IP地址、源端口、目的IP地址、目的端口、协议类型、方向、时间等多个元素进行访问控制;支持状态检测和深度报文检测;支持静态黑名单和动态黑名单;

具有中国人民解放军信息安全测评认证中心颁发的《军用信息安全产品认证证书》

*具有中国国家保密局测评中心颁发的《涉密信息系统产品检测证书》

具有国家版权局颁发的《计算机软件著作权登记证书》

厂商资质

*国内厂商,注册资金≥6000万

AD5933应用

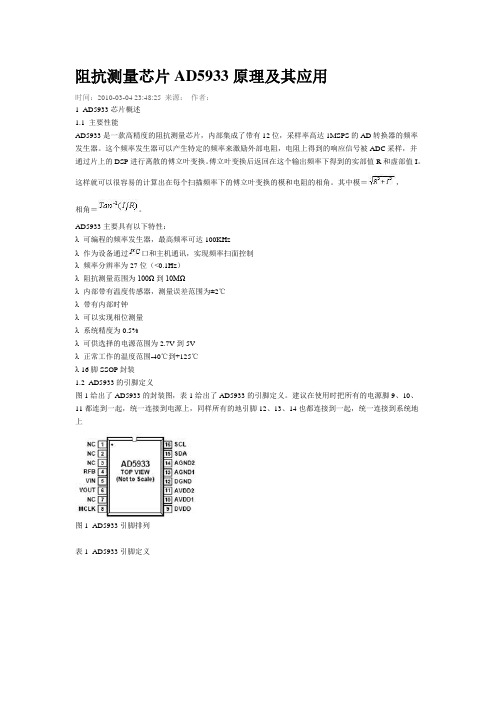

阻抗测量芯片AD5933原理及其应用时间:2010-03-04 23:48:25 来源:作者:1 AD5933芯片概述1.1 主要性能AD5933是一款高精度的阻抗测量芯片,内部集成了带有12位,采样率高达1MSPS的AD转换器的频率发生器。

这个频率发生器可以产生特定的频率来激励外部电阻,电阻上得到的响应信号被ADC采样,并通过片上的DSP进行离散的傅立叶变换。

傅立叶变换后返回在这个输出频率下得到的实部值R和虚部值I。

这样就可以很容易的计算出在每个扫描频率下的傅立叶变换的模和电阻的相角。

其中模=,相角=。

AD5933主要具有以下特性:λ可编程的频率发生器,最高频率可达100KHzλ作为设备通过口和主机通讯,实现频率扫面控制λ频率分辨率为27位(<0.1Hz)λ阻抗测量范围为100Ω到10MΩλ内部带有温度传感器,测量误差范围为±2℃λ带有内部时钟λ可以实现相位测量λ系统精度为0.5%λ可供选择的电源范围为2.7V到5Vλ正常工作的温度范围-40℃到+125℃λ 16脚SSOP封装1.2 AD5933的引脚定义图1给出了AD5933的封装图,表1给出了AD5933的引脚定义。

建议在使用时把所有的电源脚9、10、11都连到一起,统一连接到电源上,同样所有的地引脚12、13、14也都连接到一起,统一连接到系统地上图1 AD5933引脚排列表1 AD5933引脚定义1.3 主要应用AD5933可以广泛的应用在电化学分析、生物电极阻抗测量、阻抗谱分析、复杂阻抗测量、腐蚀监视和仪器保护、生物医学和自动控制传感器、无创检测、原材料性能分析以及燃料和电池状态监测等众多领域。

为阻抗的测量提供了很大的方便,单片集成技术大大的减小了仪器的体积,使得仪器使用更加方便。

简单的I2C通讯方式,方便用户操作,减小了用户编程的困难。

由于它给出的直接是变换后阻抗的实部和虚部数据,大大的简化了用户编程过程,节省了开发时间。

1SMA5940BT3中文资料(motorola)中文数据手册「EasyDatasheet - 矽搜」

单元

Watts mW/°C

mW mW/°C °C/W

°C/W

Amps Watts Watts

°C

REV 1

©

1

芯片中文手册,看全文,戳

电气特性 设备

额定齐纳

电压 VZ @ IZT伏 特

(VF = 1.5伏特@ IF = 200 mA时所有类型)

最大齐纳阻抗

测试

当前

ZZT @ IZT

TP,脉冲宽度(毫秒)

图 6.电容曲线

图 7.典型脉冲额定值曲线

120

= 10µs 100

TA = 25°C PW(ID),被定义为

点峰值电流

峰值衰减到伊普50%.

80

Ippm

60

半值 - IPP / 2

40 IPPM,峰值脉冲电流(%)

20 td

10/1000µs波形 AS定义R.E.A.

0

0

1

2

6.2

79.8

5.0

73.5

4.0

66.9

2.0

60.5

2.0

1SMA5921BT3

6.8

1SMA5922BT3

7.5

1SMA5923BT3

8.2

1SMA5924BT3

9.1

55.1

2.5

50

3.0

45.7

3.5

41.2

4.0

1SMA5925BT3

10

1SMA5926BT3

11

1SMA5927BT3

27

1SMA5936BT3

30

17

17.5

15.6

19

13.9

23

12.5

焊接件丝印参照表

107

芯片 LM4040DIM3-2.5

108

芯片 S818A33AMC

109

芯片 74HC4052D

110

ISMB5934BT3

111

B0505LS-1W

DC 模块

24PIN-QEN SOT-23 5PIN SO-16 2PIN

b0505ls

MORNSUN SILABS

TI SII NXP

MICRODC

SO-8

MAXIM

87

芯片 74HC14D

14PIN

NXP

88

芯片 AD8628ART

5PIN

AD

89

芯片 IRF7416

8PIN

IRF

90

芯片 AD712JR

SO-8

ADI

91

芯片 ADUM1400CRW

16PIN

AD

92

芯片 MAX1680

8PIN

MAXIM

93

芯片 TL431ACDBZR

SOT-23

8PIN

166

芯片 OP2347

8PIN

167

芯片 OPA2227

8PIN

168

芯片 TL061

8PIN

169

芯片 ADM101E

10PIN

170

芯片 TPS76950DBVT

5PIN

171

芯片 TPS76350

5PIN

172

芯片 C8051F064

100PIN

173

C8051F069

174

芯片 OPA350

ALTERA

69

芯片 IS62WV5128BLL-55H1I

1SMA4734A中文资料

Maximum DC Zener Current IZM (mA) 276 252 234 217 193 178 162 146 133 121 110 100 91 83 76 69 61 57 50 45 41 38 34 30 27 25 23 22 19 18 16 14 13 12 11 10 9.0

Maximum Surge Current IRM(2) (mApk) 1380 1260 1190 1070 970 890 810 730 660 605 550 500 454 414 380 344 305 285 250 225 205 190 170 150 135 125 115 110 95 90 80 70 65 60 55 50 45

MAXIMUM CONTINUOUS POWER DERATING

P.C.B. Mounted on 0.31x0.31x0.08" (8x8x2mm) copper areas pads

25

50

75

100

125

150

175

TL, LEAD TEMPERATURE (°C)

Page 1 of 2

Rev. 02 : April 1, 2005

ZZT @ IZT ZZK @ IZK (Ω) 10 10 9.0 9.0 8.0 7.0 5.0 2.0 3.5 4.0 4.5 5.0 7.0 8.0 9.0 10 14 16 20 22 23 25 35 40 45 50 60 70 80 95 110 125 150 175 200 250 350 (Ω) 400 400 400 400 500 550 600 700 700 700 700 700 700 700 700 700 700 700 750 750 750 750 750 1000 1000 1000 1000 1500 1500 1500 2000 2000 2000 2000 3000 3000 3000

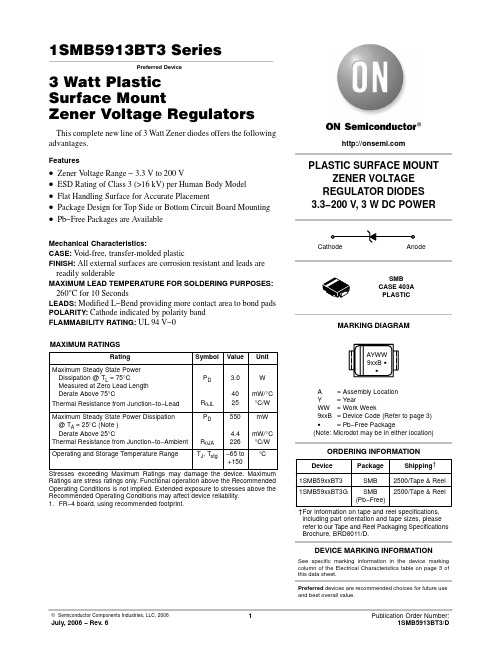

1SMB5956BT3G中文资料

550 mW

4.4 mW/°C 226 °C/W

Operating and Storage Temperature Range

TJ, Tstg −65 to °C +150

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability. 1. FR−4 board, using recommended footprint.

Preferred devices are recommended choices for future use and best overall value.

Publication Order Number: 1SMB5913BT3/D

元器件交易网

1SMB5913BT3 Series

5.5

550

0.25

1

1SMB5927BT3, G 927B

11.4

12

12.6 31.2

6.5

550

0.25

1

1SMB5928BT3, G 928B 12.35 13 13.65 28.8

7

550

0.25

1

5.2

220

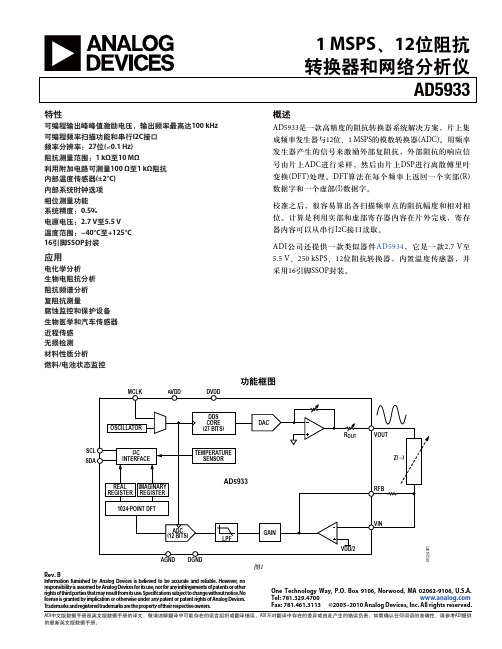

AD5933

AD5933特征50KHz 最大励磁输出1k-20M 阻抗范围,12位分辨率 可从以下:系统时钟锁相环、RC 震荡器、外部时钟 DSP 真实和想象的计算(FFT) 自带3V 电源,可编程Sinewave 输出27位频率分辨率(< 0.1Hz) 扫频能力 12点采样ADCADC 采样1MSPS INL + / - 1LSB 最大值。

对芯片温度传感器允许+ /-2(℃)的准确性 加载I2C 串行16 -40-125℃ SSOP 温度范围 应用复数阻抗测量 阻抗谱生物医学和汽车传感器 接近传感器 FFT 处理总体描述AD5933是一种高精度的阻抗变换器系统的解决方案,它集在船上频率1MSPS 发电机与一个12位a / d 转换器。

发电机的频率,允许一个外部的复数阻抗兴奋与一个已知的频率。

从阻抗响应信号的采样ADC 和FFT 处理机上由机载DSP 引擎。

返回一个真正的FFT 算法实部(R)和虚部(I)数据的话,允许阻抗是方便计算。

阻抗大小和阶段是很容易计算使用下列方程: 大小=IR22+相位=)/(Tan1R I -决定实际真正的阻抗值Z(W),一般一扫频被执行。

阻抗可以计算在每一个点和频率与大小可以被创建。

该系统允许用户程序PK-PK 正弦信号作为一个2V 激励一个外部负载。

500mV 输出1V 的适用范围,200mV,也可编程。

提供关于芯片的信号,利用DDS 技术。

频率分辨率的27位(少于0.1HZ)就可以实现。

DDS 的时钟可以产生从外部基准时钟,一种内在的RC 振荡器或一个内部锁相环。

锁相环增益的阶段,一般需要一个512 32KHz 基准时钟上的MCLK 别针。

履行扫频,用户必须首先程序所需的条件下,三角洲横扫,起动频率频率、频率步等。

一开始的命令被要求开始打扫一下。

在每一个点上扫了ADC 将1024样品和计算离散傅里叶变换提供真实和想象的波形数据。

真实与虚构的数据可以被用户通过12C 接口。

1SMA4744A中文资料

Rating at 25 °C ambient temperature unless otherwise specified Nominal Zener

Maximum Zener Impedance IZK (mA) 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 0.5 0.5 0.5 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25

Maximum Surge Current IRM(2) (mApk) 1380 1260 1190 1070 970 890 810 730 660 605 550 500 454 414 380 344 305 285 250 225 205 190 170 150 135 125 115 110 95 90 80 70 65 60 55 50 45

Page 2 of 2

Rev. 02 : April 1, 2005

元器件交易网

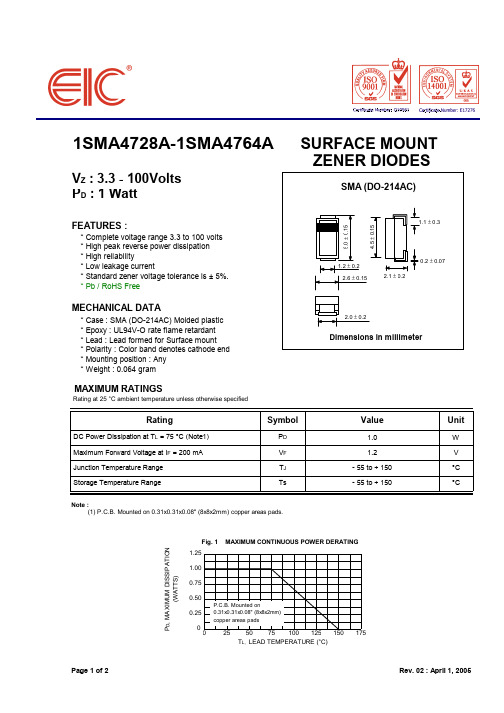

1SMA4728A-1SMA4764A

VZ : 3.3 - 100Volts PD : 1 Watt

FEATURES :

* Complete voltage range 3.3 to 100 volts * High peak reverse power dissipation * High reliability * Low leakage current * Standard zener voltage tolerance is ± 5%. * Pb / RoHS Free

AD5933(中文版)

ADI Ӳ Ӳ Lj LjADI փ ă Lj ADI Ӳ ă1 MSPS Ă12AD5933Rev. BInformation furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, N orwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2005–2010 Analog Devices, Inc. All rights reserved.05 1Պ Lj 100 kHz Պ I2C Ր ǖ27 (<0.1 Hz) ǖ1 kΩ 10 MΩ100 Ω 1 kΩ և (±2°C) և ǖ0.5%ǖ2.7 V 5.5 V ǖ−40°C +125°C 16 SSOPԍ Ԣ/AD5933 ӄLj 12 Ă1 MSPS (ADC)ă և Lj և ADC Lj DSP Վ (DFT) ăDFT և(R) և(I) ăLj ă և և Lj I2C ăADI AD5934Lj 2.7 V 5.5 V Ă250 kSPS Ă12 Lj Ljժ 16 SSOP ăAD5933Rev. B | Page 2 of 44................................................................................................... 1 ................................................................................................... 1 ................................................................................................... 1 ........................................................................................... 1 ........................................................................................... 3 ........................................................................................... 4!I 2C ........................................................... 6 ............................................................................. 7!ESD (7)..................................................................... 8 .................................................................................. 9 ................................................................................................. 12 ........................................................................................ 13! .................................................................................... 14! .............................................................. 15! .................................................................................... 15!DFT ................................................................................ 15! ................................................................................ 16! ............................................................................ 16! ....................................................................... 16! ....................................................................... 16! ....................................................................... 16 . (17)! ................................................................................ 17! ....................................................................... 17! ............................................. 17! Վ ...................................................... 17! ................................................................................ 18! .............................................................. 18! .............................................................. 18! .............................................................. 18! Վ .......................................................... 19! ................................................................................ 19! (21)................................................................................ 23 . (24)! ( 0x 80Ă 0x81) (24)!( 0x82Ă 0x83Ă 0x84) .................................................................. 25! ( 0x85Ă 0x86Ă 0x87) .................................................................. 26! ( 0x88Ă 0x89) ........................................................................................ 26! ( 0x8A Ă 0x8B) ....................................................................................... 26! ( 0x8F) .......................................... 27! (16 — 0x92Ă 0x93) ........................................................................................ 27!(16 — 0x94Ă 0x95Ă 0x96Ă 0x97) .............. 27 .. (28)! I 2C .......................................................................... 28! AD5933 .......................................................................... 29! .................................................................................... 29! .................................................................................... 30 . (31)! ............................................................................ 31! ǖ ........................................ 33! / ............................................................. 33! ................................................................... 34 AD5933 ................................................ 35ք .................................................................................... 36! ................................................................... 36 ӱ (37)! ӱ ............................................................................ 37! ....................................................................... 37! (XO) և .......................................................... 37! .................................................................................... 38! ................................................................................ 42 . (43)! (43)AD5933Rev. B | Page 3 of 442010 2 — ӲA ӲB “ ”և .............................................................................. 12008 5 — Ӳ0 ӲA ք .................................................................................... 1 ............................................................................................. 1 1 ............................................................................................. 4 17 ......................................................................................... 13 “ ”և ................................................................... 13 19 .. (14)24 ......................................................................................... 18 “ ”և ................................................................... 19 “ ”և ........................................................... 21 “ ”և ................................................................... 24 “ ”և ............................................................... 31 18 ......................................................................................... 35 “ ӱ”և ........................................................................ 37 “ ”և ................................................................... 432005 9 — Ӳ0ǖ ӲAD5933Rev. B | Page 4 of 441Y 1 /1 K10 MΩ100 Ω 1 kΩ Lj և0.5 % 2 V Lj30 kHz Lj200 kΩ5 630 ppm/°C21100 kHzՐ 0.1 Hz DDS 0.1 Hz Ր MCLK16.776 MHz և 316.776 MHz ևև 30 ppm/°C141.98 V p-p ք 451.48 V Ǘ5200 Ω T A = 25°C VOUT ±5.8 mA T A = 25°C 24 0.97 V p-p 650.76 V Ǘ72.4 kΩ VOUT ±0.25 mA 340.383 V p-p 8 50.31 V Ǘ91 kΩ VOUT ±0.20 mA 440.198 V p-p 1050.173 V Ǘ11600 Ω VOUT ±0.15 mA Բ60 dB հ −52 dB (0 MHz 1 MHz)−56 dB (±5 kHz)−85 dBLjVDD = 3.3 V LjMCLK = 16.776 MHz Lj2 V Lj30 kHz Lj200 kΩ 5 6 Lj 200 kΩ 4 5 LjPGA = ×1ăAD5933Rev. B | Page 5 of 44Y 1/1 nA VIN 60.01 pF VIN GND (C FB ) 3 pF Ǘժ6Ր 12250 kSPS ADC±2.0 °C −40°C +125°C Ր0.03 °C800(V IH )0.7 × VDD(V IL )0.3 × VDD 7 1 μA T A = 25°C 7 pF T A = 25°CVDD2.7 5.5 VIDD( )10 15 mA VDD = 3.3 V 17 25 mA VDD = 5.5 VIDD( )11 mA VDD = 3.3 V Ǘ( 0X80Ă 0X81)և16 mA VDD = 5.5 V IDD( )0.7 5 μA VDD = 3.3 V 1 8 μA VDD = 5.5 V1 Y −40°C +125°C Lj 25°C ă2AD5933 Lj ă3փ և ք Lj 14Ă 15 16ă4Բ Lj ǖ(V p-p) = [2/3.3] × VDDVDD ă 5Բ Lj ǖ (V) = [2/3.3] × VDD VDD ă6 ԍ Lj ăVOUT ă78Ă 15 16 ăAD5933Rev. B | Page 6 of 44I 2CLjVDD = 2.7 V 5.5 V Lj T MIN T MAX ă122T MIN ĂT MAXf SCL 400 kHz Lj SCL t 1 2.5 μs Lj SCLt 2 0.6 μs Lj t HIGH LjSCL t 3 1.3 μs Lj t LOW LjSCLt 4 0.6 μs Lj t HD, STA Lj / ԍ t 5 100 μs Lj t SU, DAT Lj t 63 0.9 μs Ljt HD, DAT Lj ԍ 0 μs Ljt HD, DAT Lj ԍ t 7 0.6 μs Lj t SU, STA Lj t 8 0.6 μs Lj t SU, STO Ljt 9 1.3 μs Lj t BUF Lj t 10 300 nsLjt F Lj SDA0 ns Ljt R Lj (CMOS )SCL SDA t 11 300 ns Ljt F Lj SCL SDA0 ns Lj t F Lj (CMOS )SDA 250 ns Lj t F Lj SDA20 + 0.1 C b 4 ns Ljt F Lj SCL SDA C b 400 pF Lj1 2ă2 ԍ Lj ă3SDA ( SCL V IH MIN ) SCL Lj Ղ 300 ns ԍ ă4C b ( ǖpF)ă Ljt R t F 0.3 VDD 0.7 VDD ăSCLSDA05324-002START CONDITIONREPEATED START CONDITIONSTOP CONDITION2. I 2CAD5933Rev. B | Page 7 of 44LjT A = 25°C ă3DVDD GND −0.3 V +7.0 V AVDD1 GND −0.3 V +7.0 VAVDD2 GND −0.3 V +7.0 VSDA/SCL GND −0.3 V VDD + 0.3 VVOUT GND −0.3 V VDD + 0.3 VVIN GND −0.3 V VDD + 0.3 VMCLK GND −0.3 V VDD + 0.3 V(Y )−40°C +125°C−65°C +160°C 150°C SSOP LjθJA 139°C/W θJC W /C °631 ( )! 260°C 10 40ESDLjă Ljփ Ԩ և Lj ăăESD( ) ă ӱ ă Ԩ ԍ Lj ESD Lj ă LjESD Lj Ն ăAD5933Rev. B | Page 8 of 44NCNC NC RFB VOUT NC MCLK NC = NO CONNECT05324-003IT IS RECOMMENDED TO TIE ALL SUPPLY CONNECTIONS (PIN 9, PIN 10,AND PIN 11)AND RUN FROM A SINGLE SUPPLY BETWEEN 2.7V AND 5.5V. IT IS ALSO RECOMMENDED TO CONNECT ALL GROUND SIGNALS TOGETHER (PIN 12, PIN 13,AND PIN 14).NOTES:1.3.4.Պ 1, 2, 3, 7 NC փ ă4 RFB և ă 45 Ljă5 VIN ă VDD/2 ă6 VOUT ă8 MCL Kă9 DVDD ă10 AVDD1 1ă11 AVDD2 2ă12 DGND ă13 AGND1 1ă14 AGND2 2ă15 SDA I 2C ă Lj 10 kΩ VDD ă16 SCL I 2C ă Lj 10 kΩ VDD ăAD5933Rev. B | Page 9 of 44350N U M B E R O F D E V I C E S30252015105 2.06VOLTAGE (V)1.921.94 1.96 1.982.00 2.022.0405324-0040.680.86VOLTAGE (V)0.700.720.740.760.780.800.820.84300N U M B E R O F D E V I C E S25201510505324-0074. 1 քLjVDD = 3.3 V7. 2 քLjVDD = 3.3 V1.30 1.75VOLTAGE (V)1.35 1.40 1.45 1.50 1.55 1.60 1.65 1.700N U M B E R O F D E V I C E S3025201510505324-0053000.3700.400VOLTAGE (V)N U M B E R O F D E VI C E S2520151050.3750.3800.3850.3900.39505324-0085. 1 քLjVDD = 3.3 V8. 3 քLjVDD = 3.3 V300N U M B E R O F D E V I C ES252015105VOLTAGE (V)0.950.960.970.980.99 1.00 1.01 1.0205324-0060.2900.320VOLTAGE (V)0.2950.3000.3050.3100.315300N U M B E R O F D E V I C E S25201510505324-0096. 2 քLjVDD = 3.3 V9. 3 քLjVDD = 3.3 VAD5933Rev. B | Page 10 of 44VOLTAGE (V)0.1920.1940.1960.1980.2000.2020.2040.206300N U M B E R O F D E V I C E S25201510505324-01010. 4 քLjVDD = 3.3 V0.1600.205VOLTAGE (V)0.1650.1700.1750.1800.1850.1900.1950.20030N U M B E R O F D E V I C E S25201510505324-01111. 4 քLjVDD = 3.3 V15.810.8018MCLK FREQUENCY (MHz)I D D (m A )15.314.814.313.813.312.812.311.811.324681012141605324-01212. MCLK–1.00400PHASE (Degrees)P H A S E E R R O R (D e g r e e s )–0.2–0.4–0.6–0.85010015020025030035005324-01313.16.416.616.817.017.2OSCILLATOR FREQUENCY (MHz)C O U N T05324-0142468101216.416.616.817.017.2OSCILLATOR FREQUENCY (MHz)C O U N T05324-0162468101214. −40°C և ք16. 125°C և ք160246810121416.416.616.817.017.2OSCILLATOR FREQUENCY (MHz)C O U N T05324-01515. 25°C և ք2.7 V 5.5 V LjAD5933 Lj 0.5%ă(SFDR)DDS փ Ք Lj հ հ ă Ք հ ă SFDR 0 Hz հ հ Բă SFDR ±200 kHz հ հ ă Բ(SNR)SNR հ ԲLj Ԟ(dB) ăհ (THD)THD հ հ Բ Lj V1 հ LjV2ĂV3ĂV4ĂV5 V6 հ ă AD5933LjTHDV12V3V4V V6VTHD25)Bd(02g o l+2+222+=5324-1717.FREQUENCYIMPEDANCE5324-1818.5. 3.3 V1 1.98 V p-p 1.48 V2 0.97 V p-p 0.76 V3 383 mV p-p 0.31 V4 198 mV p-p 0.173 VAD5933 ӄLj12 Ă1 MSPS ADCăև Lj և ADCLj DSP DFT ăDFTև(R) և(I)ă ǖ! =! = tan−1(I/R) Z(ω)Lj Lj18 ă22IR+AD5933 Ă Րă Lj Պհ Lj VOUTVIN և ă5 3.3 Vă VDD Բ ă Lj5 V ǖ1 = 1.98 × =3V p-p1 = 1.48 × =2.24V p-p3.30.53.30.5DDS LjSub-Hz Ր ăLj Lj ăDDSMCLK և Ljև ăDDS D3( և 0x81)ăVOUT05324-01919.19 LjAD5933 Ԉ 27 DDS Lj ă ( 0x82Ă 0x83 0x84)ă 27 Ր Lj (MSB) և 0Lj Lj 24 Պ ăAD5933 0.1 Hz Պ Ր ăՊ 24 I 2C ăǖ Ă ă24 LjՊ RAM 0x82Ă 0x83 0x84( և )ă DDS Lj 1 ă !=(1) Lj 30 kHz Ljժ 16 MHz MCLK Lj Պ ǖ!= 0x0F5C28 0x0F Պ 0x82Lj 0x5C Պ 0x83Lj 0x28 Պ 0x84ă24 LjՊ RAM 0x85Ă 0x86 0x87( և )ă DDS Lj 2 ă !=!!!!!! (2) Lj Ր 10 Hz Ljժ 16 MHzMCLK Lj Պ ǖ!= 0x00014F 0x00 Պ 0x85Lj 0x01 Պ 0x86Lj 0x4F Պ 0x87ă9 Lj ă Պ RAM 0x88 0x89( և )ă Պ 511ăLj 150 Lj 0x00 Պ 0x88Lj 0x96 Պ 0x89ăՊ Lj ( 0x80 0x81Lj և ) ă ( 0x8F) D2 ă ă ǖ0x94Ă0x95( և ) 0x96Ă0x97( և )Ǘ ă Lj ă Lj ă Lj D3 1Lj ă 1Lj օ ă2724×⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛MCLK ≡⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛16MHz 10Hz ≡×⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛272416MHz 30kHz 2724×⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛MCLK05324-02020.!LjՂ Ӏ ǖ1. ă LjՂ( 0x80 0x81) Lj ă LjVOUT VIN փ ă2. ă ӯ Lj Qă Lj Lj ă !Lj ă Lj Պ Lj փ ă Lj Lj ă3. ăLjADC ă Lj ( )Պ 0x8A 0x8B( 34)ăDDS Պ Lj 5 ă D10 D9 ( “ ( 0x80Ă 0x81)”և )Ljժ VOUT ăĂ Պ (PGA)Ă հ ADC ă 20 ă VOUT VIN ă VIN VDD/2 ă VIN Ljժ ă 4(RFB) 5 (VIN) ă Ղ PGA ԍ ADC (0 V VDD) ă PGA 5Ԡ 1ԠLj D8 ( և 0x80)ă հ Lj 12 Ă1 MSPS ADC ăADC ԥ AD5933 DSP Lj DFT ăDFTLj DFT ăAD5933 DFT ǖǖX(f) f ă x(n) ADC ăcos(n ) sin(n ) DDS f ă 1024 Ԩ Lj 16 Lj ՚ և ևă ց ă∑−−=10230)))sin())(cos((()(n n j n n x f X6.D13…D0−40°C 11, 1011, 0000, 0000 −30°C 11, 1100, 0100, 0000 −25°C 11, 1100, 1110, 0000 −10°C11, 1110, 1100, 0000 −0.03125°C 11, 1111, 1111, 1111 0°C00, 0000, 0000, 0000 +0.03125°C 00, 0000, 0000, 0001 +10°C 00, 0001, 0100, 0000 +25°C 00, 0011, 0010, 0000 +50°C 00, 0110, 0100, 0000 +75°C 00, 1001, 0110, 0000 +100°C 00, 1100, 1000, 0000 +125°C 00, 1111, 1010, 0000 +150°C01, 0010, 1100, 0000D I G I T A L O U T P U T–40°C–0.03125°C –30°C11,1111,1111,111111,1100, 0100, 000011, 1011, 0000, 0000TEMPERATURE (°C)75°C150°C01, 0010,1100, 000000, 1001, 0110, 000000, 0000, 0000, 000105324-02121.AD5933 ă և (MCLK) ă LjAD5933 16.776 MHz և ă( 0x81Lj 11) D3Պ Lj ă և ăփ և ք Lj 14Ă 15 16ă13 Lj 14 ă ă −40°C +125°C ă (+150°C) Lj Վ ă ±2°C ăև Lj Ljփ և ă Lj և ăă Lj ( 0x80 0x81) ă ( 800 μs)Lj Lj ă ( 0x8F)Lj Ǘ 0x92 0x93 ( և )ă16 Lj 14 ց ADC ă MSB ăD13 ă և ԍ –40°C Lj +150°C ă Lj 0x92 0x93 6 ă 21 ă! = ADC (D)/32!= (ADC (D) – 16384)/32“ADC ” 14 LjԈ ă != (ADC (D) – 8192)/32“ADC (D)” D13Lj ADC ă101.598.55466FREQUENCY (kHz)I M P E D A N C E (k )101.0100.5100.099.599.0565860626405324-02222.օ DFT ă DFT ǖ != ǖR 0x94 0x95 ă I 0x96 0x97 ă Lj ǖ ! = 0x038B = 907( )! = 0x0204 = 516( )!= =1043.506 LjՂ Բ ă VOUT VIN ăLj VOUT VIN ăLj Lj ǖ ! = 2 V p-p !Z CALIBRATION = 200 kΩPGA = ×1 ! = 200 kΩ != 30 kHzLj ǖ ! = 0xF064 = −3996( )! = 0x227E = +8830( )!= =9692.106 != 22I R +)516907(22+)8830()3996(22+− ⎟⎠⎞⎜⎝⎛=⎟⎠⎞⎜⎝⎛1!= =515.819×1012ăԨ Lj = 510 kΩă30 kHz Lj ǖ ! = 0xFA3F = −1473( )! = 0x0DB3 = +3507( )!= =3802.863 ǖ !==ՎAD5933 Lj Վ ă Վ ă 22 ă Lj ă⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛Ω200k 1))3507()1473((22+−×1Ω=Ω××−k 791.509863.380210819273.515112101.598.55466FREQUENCY (kHz)I M P E D A N C E (k )101.0100.5100.099.599.0565860626405324-02323.CURRENT-TO-VOLTAGE 05324-02424.Lj Վ Ljժ Lj ă 23 ăLj Ղ ă Ă PGA ăLj ǖ ! = 2 V (p-p) !Z UNKNOWN = 100.0 kΩPGA = ×1 ! = 3.3 V! = 100 kΩ != 55 kHz 65 kHzǖ ! 55 kHz 1.031224E-09 ! 65 kHz 1.035682E-09!(ΔGF) 1.035682E-09 − 1.031224E-09 = 4.458000E-12 !(ΔF) = 10 kHzLj60 kHz ǖ1.033453E-9ă ă9-10031224.15kHz 10kHz 12-4.458000E ×+⎟⎠⎞⎜⎝⎛× 24 ǖ !×Ԩ Lj ǖ VDD = 3.3 V! = 200 kΩZ UNKNOWN = 200 kΩPGA = ×1ADC 2 V p-p ăփ Lj PGA ×5Lj ADC ԏ ăՎ Lj Ղ ǖ t t t1("PGA Z UNKNOWN×101.598.55466FREQUENCY (kHz)I M P E D A N C E (k )101.0100.5100.099.599.0565860626405324-02525. Վ7010FREQUENCY (kHz)% I M P E D A N C E E R R O R654321356010005324-02626. 1 ӥ Բ2.0010FREQUENCY (kHz)% I M P E D A N C E E R R O R35601001.81.61.41.21.00.80.60.40.205324-02727. 2 ӥ ԲՎՎ 30 ppm/°C ă 25100 kΩ Վ ă2(1 kΩ 10 kΩ)Lj 27 ǖ! = 2 V p-p! ZCALIBRATION = 1 kΩ PGA = ×1! = 3.3 V!= 1 kΩAD5933 ă AD5933 փ ă ă Lj 2 V p-p LjR OUT 200 ΩăLjR OUT ă 26 31 Lj 4 MHz 10 kHz ă1(0.1 kΩ 1 kΩ)Lj 26 ǖ ! = 2 V p-p ! Z CALIBRATION = 100 Ω PGA = ×1! = 3.3 V!= 100 Ω0.3–0.310FREQUENCY (kHz)% I M P E D A N C E E R R O R35601000.20.10–0.1–0.205324-0283–910FREQUENCY (kHz)% I M P E D A N C E E R R O R35601001–1–3–5–705324-03028. 3 ӥ Բ 30. 5 ӥ Բ1.0–3.510FREQUENCY (kHz)% I M P E D A N C E E R R O R35601000.50–0.5–1.0–1.5–2.0–2.5–3.005324-02929. 4 ӥ Բ 4–1010FREQUENCY (kHz)% I M P E D A N C E E R R O R20–2–4–6–8356010005324-03131. 6 ӥ Բ3(10 kΩ 100 kΩ)Lj 28 ǖ ! = 2 V p-p ! Z CALIBRATION = 10 kΩ PGA = ×1 ! = 3.3 V!= 10 kΩ5(1 MΩ 2 MΩ)Lj 30 ǖ ! = 2 V p-p ! Z CALIBRATION = 100 Ω PGA = ×1! = 3.3 V!= 100 kΩ6(9 MΩ 10 MΩ)Lj 31 ǖ ! = 2 V p-p ! Z CALIBRATION = 9 MΩ PGA = ×1! = 3.3 V!= 9 MΩ4(100 kΩ 1 MΩ)Lj 29 ǖ ! = 2 V p-p ! Z CALIBRATION = 100 kΩ PGA = ×1 ! = 3.3 V!= 100 kΩAD5933 և և ă Lj և 0x94 0x95 Lj և 0x96 0x97 ă DFT և ևLj փ ăLj ǖ RC Lj 0x94 0x95 0x96 0x97 ՚ ă Lj փ Lj (|Z|) DFT և և Lj ǖ != Lj ժ ă Lj ǖ !=ǖ != Ղ AD5933Lj Lj ă Lj Ք Lj Ղ (Z UNKNOWN ) ă AD5933 Ljժ ă AD5933 Lj ADC ă AD5933 և և Lj AD5933 ă ǖ !(rads) = tan −1(I/R )(3)3 ǖ DDS AD5933 և հ Lj AD5933 VOUT VIN ă22I R +×1⎟⎠⎞⎜⎝⎛=⎟⎠⎞⎜⎝⎛1 (|Z UNKNOWN |) (ZØ)ă (ZØ) օăօ AD5933 Lj AD5933 VOUT VIN Ljժ 3 ă VOUT VIN LjAD5933 Սփ Lj AD5933 և Lj ăLj օՍ AD5933 VIN VOUT Lj (Ԉ )Lj ă (ZØ) ǖ Z Ø = (Φunknown - ∇system )ǖ∇system VIN VOUT ăΦunknown VIN VOUT ăZØ Lj ăLj AD5933 VOUT VIN Lj ժ Lj (ZØ)ăLj −90°ă Lj −90° ăLj (ZØ)Lj Ղ (∇system)Lj VOUT VIN (Φunknown) ă2001801601401201008060402015k30k45k 60k 75k 90k105k120kFREQUENCY (Hz)S Y S T E M P H A S E (D e g r e e s )05324-03232.–100–90–80–70–60–50–40–30–20–1015k30k45k 60k 75k 90k105k120kFREQUENCY (Hz)P H A S E (D e g r e e s )05324-03333.32 220 kΩ (R FB = 220 kΩĂPGA = ×1) AD5933 10 pF ă32 LjՂ ǖ Lj Lj Ղ ă( ZØ) ZØ( 33)ăLj Lj ă Lj Ք Lj Ք ăՔ x ă և Lj և Lj Lj Lj 180° Ք ă Lj և և Lj Lj Lj 180° Ք ă Lj և Lj և Lj Lj Lj 360° ăLj Ք և և Lj 7ă(|Z|) )ZØLj * LjՍ և և Lj (Z UNKNOWN ) և) * և) * Ǘ ǖ և ǖ|Z REAL | = |Z | × cos (ZØ)և ǖ|Z IMAG | = |Z | × sin (ZØ)34.9. (D15 D12)D15 D14 D13 D12 0 0 0 00 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 110. (D10 D9)D10 D9 Պ0 0 1 2.0 V p-p 0 1 4 200 mV p-p 1 0 3 400 mV p-p 1 1 21.0 V p-p( 0x80Ă 0x81)AD5933 16 ( 0x80 0x81)Lj AD5933 ă ǖD15 D0 0xA000ă 4 MSB Lj ǖ Ă ă0x80Lj փ Վ 0x81 ă Lj փ և ă ă փ Պ ( Ă )ă LjՂ Lj ( 34)ă11. (D11ĂD8 D0)D11D8 PGA Ǘ0 = ×5Lj1 = ×1D7 ԍ Lj 0D6 ԍ Lj 0D5 ԍ Lj 0D4D3 և Lj 1և Lj 0D2 ԍ Lj 0D1 ԍ Lj 0D0 ԍ Lj 0!!DDSփ Պ ă օ ă Lj Lj Ղ Lj Ս ăLj LjADC ă Lj ( )Պ 0x8A 0x8B( 34)ă!օ ă օ Թժ DSP ă AD5933 Lj Պ Lj ADC ă!Lj ă Lj ăă Lj ă Lj Lj ă 14 ց 0x92 0x93 ăAD5933 ă Ԉ 1010,0000,0000,0000 (0xA000)ă LjVOUT VIN և GNDăӯ ă LjVIN VOUT և ăՊ VOUT ăPGAPGA ADC 5Ԡ 1Ԡăă Ă փ ԥ ă LjՂ ă( 0x82Ă 0x83Ă 0x84)ǖD23 D0 փ ă Lj փ ăԈ 24 ă Lj 30 kHz ( 16.0 MHz )Lj 0x0F Պ 0x82Lj 0x5C Պ 0x83Lj 0x28 Պ 0x84ă ԍ 30 kHz ăՊ ǖ= 0x0F5C28≡×⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛272416MHz30kHz12.0x88 D15 D9/D8/ 0x89 D8 D0/13.0x8A D15 D11/D10 D9 2D10 D9 0 0 0 1 × 21 0 ԍ1 1× 4D8 MSB0x8B D7 D0/( 0x85Ă 0x86Ă 0x87)ǖD23 D0 փ ă Lj փ ăԈ 24 ă Lj 16.0 MHz Lj օ 10 Hz Lj 0x00 Պ 0x85Lj 0x01 Պ 0x86Lj 0x4F Պ 0x87ă ǖ= 0x00014F 0x00Պ 0x85Lj 0x01Պ 0x86Lj 0x4F Պ 0x87ă( 0x88Ă 0x89)ǖD8 D0 փ ă Lj փ ă≡×⎟⎟⎟⎟⎠⎞⎜⎜⎜⎜⎝⎛⎟⎠⎞⎜⎝⎛27216MHz 10Hz ă 9 D8 D0 ăD15 D9 ă ă Պ 511ă( 0x8A Ă 0x8B)ǖD10 D0 փ ă Lj փ ( 13)ăĂ Lj ADC Lj ă / / ADC ă 9 D8 D0 ăՊ 2Ԡ 4ԠLj D10 D9 ă5 D15 D11 ă Պ 511 × 4 = 2044 ă Lj 30 kHz LjՊ ADC 511 × 4 × 33.33 μs = 68.126 ms ăADC 1024 ԨLj 0x94 0x97 ă 16.777 MHz Lj 1 ms ă14. ( 0x8F)0000 0001 0000 0010 / 0000 0100 0000 1000 ԍ 0001 0000 ԍ 0010 0000 ԍ 0100 0000 ԍ 1000 0000ԍ( 0x8F)ă D7 D0 AD5933 ăD0 D4 D7 Ljփ ă D1 ă AD5933 Lj 1ă 0x94 0x97 ă Ă Ă Lj ă ăD2 Պ ă Պ և Lj 1ă ă/LjD1 1Lj ă / / DDS / / LjD1 ă LjD1 0ăLjD2 1ă Lj ă Lj ă(16 — 0x92Ă 0x93)Ԉ AD5933 ă 16 ց ăD15 D14 ăD13 ă Lj “ ”և ă(16 — 0x94Ă 0x95Ă 0x96Ă 0x97)ǖփ ă Lj D1 1 Lj Lj ăԈ և և ă 16 ց ă LjՂ (√(Real2 + Imaginary2)) / ( )Lj Lj ă փ ăLj Lj 0x92 0x93 ă ( 0x80 0x81) Lj Lj ă111R/WD7D6D5D4D3D2D1D0START CONDITIONBY MASTERACKNOWLEDGE BYAD5933SLAVE ADDRESS BYTEACKNOWLEDGE BY MASTER/SLAVESCLSDAREGISTER ADDRESS05324-03535.AD5933 I 2C ă Lj ăAD5933 7 ă Lj 0001101 (0x0D)ăI 2C35 I 2C ӯ ă Ǘ (SDA) Lj (SCL)ԍ ă Lj ă Lj 8 LjԈ 7 (MSB ) R/W Lj Lj (0 = Lj1 = )ăLj 9 ( ) Ljժ ԍ ă Lj ԍ ă R/W 0Lj ă R/W 1Lj ă9 ǖ8 ă Ղ Ljժ ԍ Lj ԥ ă Lj Lj ă Lj Lj Lj ă R/W Lj ă Lj Lj / ăLj ă Lj 10 Lj ă Lj 9 SDA Lj փ Lj փ ă 10 Lj 10 Lj ă05324-036A SA A W PPOINTER COMMAND 1011 0000SLAVE ADDRESSREGISTER ADDRESS TO POINT TO05324-037216.1010 0000RAM Ǘև ă1010 0001RAM/ Ǘ և ă 1011 0000ă Ԉ ă36.37.05324-03838.AD5933փ փ ăԨև AD5933 ăԨև 15 ă ( 37)Lj Ս Lj ăLj ǖ 1. SDA ă2. 7 ( )ă3. SDA ă4. ( 16Ǘ = 10110000)ă5. SDA ă6. ( )ă7. SDA ă8. SDA ăLj ( 38)ă Ղ ă AD5933Lj ă 1. SDA ă2. 7 ( )ă3. SDA ă4. 8 (1010 0000)Ljă5. SDA ă6. Ljă7. SDA ă 8. ă9. Lj SDA ă 10. SDA ă!16 ăԨև Lj Ս ă /Lj ă Lj ă Lj ( 36)ǖ 1. SDA ă2. 7 ( )ă3. SDA ă4. ă5. SDA ă6. ă7. SDA ă8.SDA ă05324-03939.05324-04040.AD5933 I 2C ǖ ăAD5933 Lj Lj ăLj Lj ( 39)ǖ1. SDA ă2. 7 ( )ă3. SDA ă4. ă5. SDA փ ()ă6. SDA Lj ăLj ( 40)ă Ղ ă 1. SDA ă2. 7 ( )ă3. SDA ă4. (1010 0001)Ljă5. SDA ă6. Ljă7. SDA ă8. SDA ăՂ ă9. 7 ( )ă 10. SDA ă11. ă12. Lj SDA ă 13. Lj փ Lj ă 14. SDA ă05324-0482V p-p41. ևՔ Lj AD5933 10 MΩ ăLj VOUT VIN ( Ք ≤500 Ω)Lj Lj Վ ăVOUT ă I-V ԍ Lj Ӏ “ ”և ă I-V Lj VIN VDD/2ă I-V / փ Lj ă(Z UNKNOWN ) LjՂ VOUT ROUT( 41( Lj (Z UNKNOWN ) ă Lj ( ) R OUT Lj Lj Բ ăVOUT Lj Lj ă 17 ă Lj AD5933 LjՂ Lj Lj R OUT Lj ( “ ”և )ă Lj R OUT VOUT Lj ( ±2 mA)Lj Վ ă I-V ( 1/ ) ă 41 ă և Lj AD5933 ă և (R1 R2) VOUT Lj Ljժ ă41 LjZ UNKNOWN ՚ և Lj 1 ΩLj ( AD820ĂAD8641ĂAD8531 )Ă Ă ăLj VOUT (ROUT) ԲLj 41 և (ZUNKNOWN)ă և ROUTLjժZUNKNOWNăLj ZUNKNOWN30 kHz 32 kHz 90 Ω 110 Ω LjROUTă Lj AD5933 41 և ă Ղ ԍ և Ք Բ ( Lj /opamps)ăADI փ Կ Lj Ք ăǖVDD = 3.3 VVOUT = 2 V p-pR2 = 20 kΩR1 = 4 kΩ= 500 ΩZUNKNOWN= 100 ΩPGA = ×1 R1/R2Բ Lj VOUT ă R1 = 4 kΩ R2 = 20 kΩ Lj 1/5Lj 2 V p-p Lj 400 mVă 400 mV/ 90 Ω = 4.4 mAă100 Ω Ă Lj ă RFB I-V Lj AD5933 ă Lj RFB I-V Lj ADC 400 mV (RFB = 100 Ω) 2 V p-p (RFB = 500 Ω)ă100 Ω VOUT VIN Lj և փ ă41 Lj AD5933 VDD/2ă Lj և ( AD5933 1 ) AD5933 ԏ LjՂ VDD/2 և ă05324-04142. թFREQUENCY (Hz)05324-04243. Վǖթ թ Lj Lj Վă փ Lj թ ă Lj թ Lj փ ă Lj փ թ Lj փ ăAD5933 Ԣ27 Lj Sub-Hz ăAD5933 Lj Lj ăAD5933 Lj ă/RLC Վ Lj RLC Վ Lj 43 ă RLC ă LjRLC ă Lj Պ LjAD5933 Ԣ ăă Վ Lj Վ ă Lj ăAD5933 ă AD5933Lj ăփ LjAD5933 80 kHz 100 kHz ă ă ă Lj Lj Վ Lj AD5933 ă100k 100.1FREQUENCY (Hz)M O D U L U SP H A S E A N G L E100k05324-0431101001k 10k1001k10k44. հAD5933 ă Lj Ă ă փ Lj Lj ă Lj Lj Lj Ԩă Ljփ Lj Ăӆ Lj փ ă ă ԨLj Lj և ă (EIS) ԥ Ljփ ăAD5933 ӄLj և Lj ăRC Lj RC (R S ) ժ (R P C P ) ă ǖR S 10 Ω 10 kΩLjR P 1 kΩ 1 MΩLjC P 5 μF 70 μF ă 44 հ Ă ăLj 0.1 Hz 100 kHz ă ԍ Ԩ փ LjՂ Lj ±20 mV ă ( ADuC702x) 10 0.1 kHz 100 kHz Ljժ ă 0.1 kHz 1 kHz Lj 16.776 MHz Ք 500 kHz ă AD9834 և Lj Պ Lj MCLK Lj ăAD593318. AD5933 (mV Lj ) (V) (ppm/°C Lj )0.1 Hz 10 Hz (μV p-p Lj )ADR433B ±1.5 3. 0 3 3.75ADR433A ±4 3. 0 10 3.75 ADR434B ±1.5 4. 096 3 6.25ADR434A ±5 4. 096 10 6.25 ADR435B ±2 5.0 3 8 ADR435A ±6 5.0 10 8 ADR439B ±2 4.5 3 7.5 ADR439A±5.5 4.5 107.5AD5933 Lj ăAD5933 ǖAVDD1ĂAVDD2 DVDD ă ă Lj ǖ Ăppm Ă ă Lj ă Lj Lj ADR43x Lj Ք Lj Ս ă ăAD5933 Lj ă Lj ADR395Lj 100 μA Lj Lj 0.1 Hz 10 Hz 8 μV p-p ăă ԍ ӄ ԍ ă Lj ăLj ă Ր Lj ăADR433 0.1 Hz 10 Hz ă18 AD5933 ăք!Lj ӱ ք ă AD5933 ӱ և և Lj և ӱ ă AD5933 AGND DGND Lj ă AD5933ăAD5933 10 μF 0.1 μF ă Lj0.1 μF ă10 μF ă0.1 μF Ղ (ESR) (ESI)Lj ă և Lj 0.1 μF ăԨ Lj Ljժ ă Ը Lj փ ӱ ă Ն ă ӱ Lj ԍ Ե Lj ӱ ă ӱք Lj ӱ Lj ք ă Lj ӱ Ղ ăӱAD5933 ӱLj փ AD5933ăӱ PC USB Lj USB ӱ ăԈ ժ AD5933 ӱăEVAL-AD5933EB Ҿ CD ăPC ӱ ăMicrosoft® Windows® 2000 Windows XPăӱ 45 46ă ӱAD5933 ӱ AD5933 ă ӱ ӱ Lj Ԉ ӱ ă ăӱ Lj ă Ս ă (XO) ևӱ 16 MHz ăփ Lj Ǘ Lj ևCMOS ă05324-04445. EVAL-AD5933EBZ USB05324-04546. EVAL-AD5933EBZ05324-04647. EVAL-AD5933EB ӱAD593305324-04748. EVAL-AD5933EB ӱAD593319Ք SMD 150 V X7R SMD Lj0.1 μFLj0603FEC 1301804C1, C3, C5 C9, C11,C15, C16, C 18 C22,C24, C26 C28, C32,C34, C36, C37, C39X5R Lj10 μFLj0805FEC 9402136C2, C4, C12 C14, C25,C30, C31, C33, C38, C40C10, C17 50 V X7R SMD Lj22 pFLj0603FEC 722-005C23 6.3 V X5R SMD Lj2.2 μFLj0603FEC 9402101C29, C35 16 V Lj10 μFLjCAP\TAJ_B FEC 498-737C41 (×2)LjCAP-7.5 MMC42 50 V NPO SMD Lj15 pFLj0603FEC 721-980C43 16 V X7R SMD Lj1 μFLj0603FEC 1310220CLK1, CLK2 SMB Lj50 ΩFEC 1111349D4 Lj0805FEC 1318243J1 USB Mini-B (USB-OTG)FEC 9786490J2 J6 / ӱDŽ5 mm DžFEC 151-789LK1 LK14 ӱLj 0.1" SIP-2P FEC 1022247/FEC 150-411 R1 SMD 50 ΩLj0603FEC 11706589341501 R2 Lj Lj200 kΩ R1/8WA2 FECR33 4 kΩ 4R43 20 kΩ 4R5, R6 SMD 100 kΩLj0603FEC 9330402R7 SMD 0 ΩLj0603FEC 9331662R8, R9 SMD 2.2 kΩLj0603FEC 9330810R10 SMD 10 kΩLj0603FEC 9330399R11 SMD 1 kΩLj0805FEC 9332383R12, R13 SMD 20 kΩLj0603FEC 9330771T1 T3, T5 T8 FEC 8731128VIN, VOUT SMB 50 ΩFEC 1111349U1 OP97 SO8NBU2 24LC64 IC EEPROM 64 KB 2.5 V SOIC8 SO8NB FEC 9758070U3 CY7C68013-CSP USB Cypress CY7C68013A-56LFXC LFCSP-56Digi-Key 428-1669-NDU4 ADR435 5 V SOIC-8ADR435ARZU5 ADP3303-3.3 SO-8NB ADP3303ARZ-3.3U6 AD5933/34 SSOP-16AD5933YRSZ/AD5934YRSZ Y1 XTAL-CM309S CM309S SMD crystal 24 MHz, XTAL_CM309S FEC 9509658Y2 3.3 VĂ16 MHz AEL-4313×4FEC 651-813ԈLjӱ Ԉ Ԉ FEC 522-764A Mini-B Digi-Key 167-1011-NDUSB1 FEC = Farnell Electronics.2 Lj ă3 R3 R4 փ ă4 ă。

SMA-C04产品规格书说明书

SMA-C04 产品规格书版本V1.0版权© 2018关于本手册本手册介绍了SMA-C04模块产品特性、电气特性、管脚布局及定义、功能描述、射频指标、尺寸图,包含以下章节。

章标题内容第1章产品简介概述SMA-C04模块的特点和应用第2章产品展示展示实际产品图片及特性说明第3章电气特性列出产品的基本参数第4章管脚定义提供管脚布局、定义及管脚功能说明第5章功能描述模块功能描述及具体说明第6章射频指标提供模块射频特性表第7章尺寸图提供了模块的尺寸图发布说明日期标题发布说明编制审核2018.3.24 V1.0 首次发布张少茹武鹏飞1. 产品简介SMA-C04是一款基于ESP8285的超低功耗的Wi-Fi四通道开关模块,拥有业内极富竞争力的封装尺寸和超低能耗技术,专为移动设备和物联网应用设计,可将用户的物理设备连接到Wi-Fi无线网络上,进行互联网或局域网通信,实现联网功能。

该模块可以作为4个家用电器的开关控制。

既可以通过本地的按键控制,也可以通过连接APP (易微联)远程控制。

SMA-C04可广泛应用于智能电网、智能交通、智能家具、手持设备、工业控制等领域。

2. 产品展示图 1 SMA-C04正面展示图 2 SMA-C04反面展示产品特性● 3.3VDC供电,最大工作电流210mA;●内置32位MCU,可兼作应用处理器;●支持无线802.11 b/g/n 标准;●************,支持WPA/WPA2 安全模式;●802.11b 模式下+20.5dBm的输出功率;●四通道控制;●支持本地硬件开关控制;●支持Wi-Fi远程控制;●APP支持安卓、iOS系统;●主要应用领域:智能电网、智能交通、智能家居、手持设备及工控领域。

3. 电气特性3.1 额定参数条件:VDD=3.3V±10%,GND=0V;室温25°C下测试。

表 1 额定参数说明类型参数模块型号SMA-C04主芯片ESP8285硬件参数硬件接口UART,GPIO工作电压 2.7V~3.6VGPIO驱动能力Max:12mA工作电流平均电流:≈80mA最大工作电流:210mA待机:<200uA工作温度-40℃~125℃存储环境温度:<40℃,相对湿度:<90%RH 尺寸大小15mm×15mm×1.0mm软件参数无线网络类型STA/AP/STA+AP安全机制WEP/WPA-PSK/WPA2-PSK 加密类型WEP64/WEP128/TKIP/AES 固件升级OTA远程升级3.2 Wi-Fi参数条件:VDD=3.3V±10%,GND=0V;室温25°C下测试。

apl5930引脚参数

apl5930引脚参数摘要:1.Apl5930芯片简介2.Apl5930引脚参数概述3.引脚功能详细说明a.电源引脚b.数据输入引脚c.数据输出引脚d.控制引脚e.其他引脚4.引脚参数对性能的影响5.引脚连接注意事项6.结论正文:【1.Apl5930芯片简介】Apl5930是一款高性能的电源管理芯片,广泛应用于各种电子产品中,以实现高效的电源转换和管理。

它具有高度集成的特点,可提供多种功能,如电压基准、电压监控、电源开关等。

为了实现这些功能,Apl5930具有多个引脚,每个引脚都有特定的功能和参数。

【2.Apl5930引脚参数概述】Apl5930引脚参数包括电源引脚、数据输入引脚、数据输出引脚、控制引脚和其他引脚。

这些引脚的参数对于芯片的性能和功能至关重要。

【3.引脚功能详细说明】【a.电源引脚】电源引脚是Apl5930的关键部分,为芯片提供稳定的电压。

通常,有两个电源引脚:VCC和VSS。

VCC用于接收输入电压,而VSS用于提供参考电压或地。

电源引脚的参数,如电压范围、电流等,对于芯片的稳定性和性能至关重要。

【b.数据输入引脚】数据输入引脚用于接收外部信号,以便Apl5930能够根据这些信号执行相应的操作。

数据输入引脚的参数,如输入电压范围、输入电流等,直接影响信号的质量和芯片的处理能力。

【c.数据输出引脚】数据输出引脚用于输出由Apl5930处理后的信号。

这些信号可能包括电压、电流或控制信号。

数据输出引脚的参数,如输出电压范围、输出电流等,对于芯片的性能和所连接负载的稳定性至关重要。

【d.控制引脚】控制引脚用于接收外部控制信号,以便Apl5930能够根据这些信号执行相应的操作。

控制引脚的参数,如输入电压范围、输入电流等,直接影响控制信号的质量和芯片的响应能力。

【e.其他引脚】除了上述引脚外,Apl5930还有一些其他引脚,如复位引脚、使能引脚等。

这些引脚的参数对于芯片的正常工作和特定功能的实现至关重要。

WP3DP3BT;中文规格书,Datasheet资料

Absolute Maximum Ratings at TA=25°C

Parameter Collector-to-Emitter Voltage Emitter-to-Collector Voltage Power Dissipation at (or below) 25°C Free Air Temperature Operating Temperature Storage Temperature Lead Soldering Temperature (>5mm for 5sec) Max.Ratings 30V 5V 100mW -40°C To +85°C -40°C To +85°C 260°C

DATE: FEB/07/2012 DRAWN: D.M.Su

PAGE: 5 OF 5 ERP: 1101003911

htБайду номын сангаасp:///

分销商库存信息:

KINGBRIGHT WP3DP3BT

SPEC NO: DSAH7501 APPROVED: WYNEC

REV NO: V.3 CHECKED: Allen Liu

DATE: FEB/07/2012 DRAWN: D.M.Su

PAGE: 2 OF 5 ERP: 1101003911

/

PACKING & LABEL SPECIFICATIONS

PHOTOTRANSISTOR

Part Number: WP3DP3BT

Features

z Mechanically and spectrally matched to the infrared emitting LED lamp. z Blue transparent lens. z RoHS compliant.

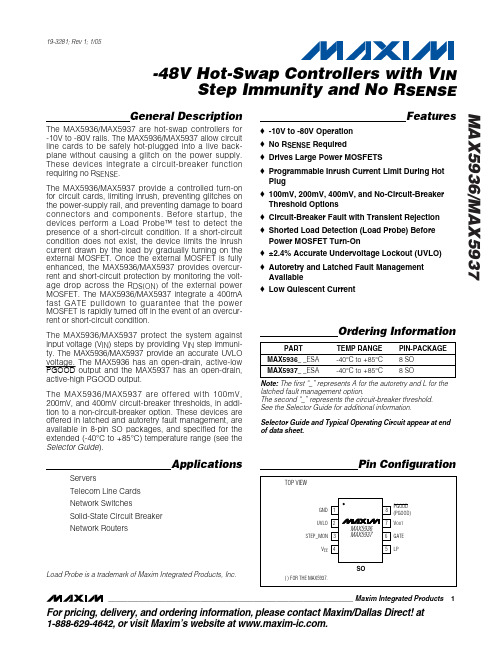

MAX5937LBESA+中文资料

MAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE________________________________________________________________Maxim Integrated Products 119-3281; Rev 1; 1/05For pricing, delivery, and ordering information,please contact Maxim/Dallas Direct!at 1-888-629-4642, or visit Maxim’s website at .General DescriptionThe MAX5936/MAX5937 are hot-swap controllers for -10V to -80V rails. The MAX5936/MAX5937 allow circuit line cards to be safely hot-plugged into a live back-plane without causing a glitch on the power supply.These devices integrate a circuit-breaker function requiring no R SENSE .The MAX5936/MAX5937 provide a controlled turn-on for circuit cards, limiting inrush, preventing glitches on the power-supply rail, and preventing damage to board connectors and components. Before startup, the devices perform a Load Probe™ test to detect the presence of a short-circuit condition. If a short-circuit condition does not exist, the device limits the inrush current drawn by the load by gradually turning on the external MOSFET. Once the external MOSFET is fully enhanced, the MAX5936/MAX5937 provides overcur-rent and short-circuit protection by monitoring the volt-age drop across the R DS(ON)of the external power MOSFET. The MAX5936/MAX5937 integrate a 400mA fast G ATE pulldown to guarantee that the power MOSFET is rapidly turned off in the event of an overcur-rent or short-circuit condition.The MAX5936/MAX5937 protect the system against input voltage (V IN ) steps by providing V IN step immuni-ty. The MAX5936/MAX5937 provide an accurate UVLO voltage. The MAX5936 has an open-drain, active-low PGOOD output and the MAX5937 has an open-drain,active-high PGOOD output.The MAX5936/MAX5937 are offered with 100mV,200mV, and 400mV circuit-breaker thresholds, in addi-tion to a non-circuit-breaker option. These devices are offered in latched and autoretry fault management, are available in 8-pin SO packages, and specified for the extended (-40°C to +85°C) temperature range (see the Selector Guide ).ApplicationsServersTelecom Line Cards Network Switches Solid-State Circuit Breaker Network RoutersFeatures♦-10V to -80V Operation ♦No R SENSE Required♦Drives Large Power MOSFETS♦Programmable Inrush Current Limit During Hot Plug ♦100mV, 200mV, 400mV, and No-Circuit-Breaker Threshold Options ♦Circuit-Breaker Fault with Transient Rejection ♦Shorted Load Detection (Load Probe) Before Power MOSFET Turn-On ♦±2.4% Accurate Undervoltage Lockout (UVLO)♦Autoretry and Latched Fault Management Available ♦Low Quiescent CurrentPin ConfigurationLoad Probe is a trademark of Maxim Integrated Products, Inc.Ordering InformationNote:The first “_” represents A for the autoretry and L for the latched fault management option.The second “_” represents the circuit-breaker threshold. See the Selector Guide for additional information.Selector Guide and Typical Operating Circuit appear at end of data sheet.M A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE 2_______________________________________________________________________________________ABSOLUTE MAXIMUM RATINGSStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.V EE , V OUT , PGOOD (PGOOD ), LP,STEP_MON to GND............................................+0.3V to -85V PGOOD (PGOOD ) to V OUT ....................................-0.3V to +85V PGOOD (PGOOD ), LP, STEP_MON to V EE ............-0.3V to +85V GATE to V EE ...........................................................-0.3V to +20V UVLO to V EE .............................................................-0.3V to +6V Input CurrentLP (internally, duty-cycle limited).........................................1A PGOOD (PGOOD ) (continuous).....................................80mAGATE (during 15V clamp, continuous)...........................30mA GATE (during 2V clamp, continuous).............................50mA GATE (during gate pulldown, continuous)......................50mA Continuous Power Dissipation (T A = +70°C)8-Pin SO (derate 5.9mW/°C above +70°C)..................471mW Operating Temperature Range ...........................-40°C to +85°C Junction Temperature .....................................................+150°C Storage Temperature Range ............................-65°C to +150°C Lead Temperature (soldering, 10s) ................................+300°CELECTRICAL CHARACTERISTICS(V= -10V to -80V, V = GND - V , V =V , R = 200Ω, UVLO open, T = -40°C to +85°C, unless otherwise noted.MAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSEELECTRICAL CHARACTERISTICS (continued)M A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE 4_______________________________________________________________________________________Note 2:All limits are 100% tested at +25°C and +85°C. Limits at -40°C and -10°C are guaranteed by characterization.Note 3:Delay time from a valid on-condition until the load probe test begins.Note 4:V EE or UVLO voltages below V UVLO,F or V UVLO_REF,F , respectively, are ignored during this time.Note 5:The time (V OUT - V EE ) > V SC + overdrive until (V GATE - V EE ) drops to approximately 90% of its initial high value.Note 6:The time when the PGOOD (PGOOD ) condition is met until the PGOOD (PGOOD ) signal is asserted.ELECTRICAL CHARACTERISTICS (continued)MAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE_______________________________________________________________________________________5SUPPLY CURRENT vs. INPUT VOLTAGEM A Z 5936 t o c 01INPUT VOLTAGE (V)S U P P L Y C U R R E N T (m A )7060405030200.20.40.60.81.01.21.41.61.82.001080SUPPLY CURRENT vs. TEMPERATURETEMPERATURE (°C)S U P P L Y C U R R E N T (m A )603510-150.20.40.60.81.01.20-4085GATE-DRIVE VOLTAGE vs. INPUT VOLTAGEM A X 536 t o c 03INPUT VOLTAGE (V)G A T E -D R I V E V O L T A G E (V )7060405030206.57.07.58.08.59.09.510.010.56.01080GATE PULLDOWN CURRENTvs. GATE VOLTAGEM A X 5936 t o c 04V GATE (V)G A T E P U L L D O W N C U R R E N T (m A )986723451501001502002503003504004505000010RETRY TIME vs. TEMPERATURETEMPERATURE (°C)R E T R Y T I M E (s )603510-153.13.23.33.43.53.63.73.83.94.03.0-4085STARTUP WAVEFORMMAX5936 toc0640ms/divV IN 50V/div V GATE 10V/div V OUT 50V/div I IN 2A/divV PGOOD 50V/div MAX5936_A CIRCUIT-BREAKER EVENTMAX5936 toc071ms/divV GATE 10V/divV OUT 50V/divI IN 2A/divV PGOOD 50V/div Typical Operating Characteristics(V EE = -48V, GND = 0V, V IN = GND - V EE , all voltages are referenced to V EE , T A = +25°C, unless otherwise noted.)M A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE 6_______________________________________________________________________________________MAX5936_A SHORT-CIRCUIT EVENTMAX5936 toc08400ns/divV GATE 10V/divV OUT 50V/div I IN10A/divV PGOOD 50V/divNORMALIZED CIRCUIT-BREAKER THRESHOLD vs. TEMPERATUREM A X 5936 t o c 09TEMPERATURE (°C)N O R M A L I Z E D C I R C U I T -B R E A K E R T H R E S H O L D (%)603510-150.60.81.01.21.41.60.4-4085V OUT SLEW RATE vs. TEMPERATURETEMPERATURE (°C)S L E W R A T E (V /m s )603510-155.56.0 6.57.07.58.08.59.09.510.05.0-4085MAX5936_A INPUT VOLTAGE STEP EVENT (NO FAULT)4ms/divGATE OUT IN V PGOOD IN R LOAD = 75ΩMAX5936_A INPUT VOLTAGESTEP EVENT (FAULT)4ms/divGATE OUT IN V PGOODIN R LOAD = 75ΩGATE TO V EE CLAMP VOLTAGEAT POWER OFFI SINK (mA)G A T E C L A M P I N G V O L T A G E (V )181614121086420.51.01.52.02.53.00020GATE TO V EE CLAMP VOLTAGE MOSFET FULLY ENHANCEDI SINK (mA)G A T E C L A M P I N G V O L T A G E (V )1816121446810291011121314151617188020Typical Operating Characteristics (continued)(V EE = -48V, GND = 0V, V IN = GND - V EE , all voltages are referenced to V EE , T A = +25°C, unless otherwise noted.)MAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE_______________________________________________________________________________________7Detailed DescriptionThe MAX5936/MAX5937 hot-swap controllers incorpo-rate overcurrent fault management and are intended for negative-supply-rail applications. The MAX5936/MAX5937 eliminate the need for an external R SENSE and include V IN input-step protection and load probe,which prevents powering up into a shorted load. They are intended for negative 48V telecom power systems where low cost, flexibility, multifault management, and compact size are required. The MAX5936/MAX5937 are ideal for the widest range of systems from those requiring low current with small MOSFETs to high-current systems requiring large power MOSFETs and low on-resistance.The MAX5936/MAX5937 control an external n-channel power MOSFET placed in the negative supply path of an external load. When no power is applied, the GATE output of the MAX5936/MAX5937 clamps the V GS of the MOSFET to 2V, keeping the MOSFET turned off. When power is applied to the MAX5936/MAX5937, the 2Vdown device pulling G ATE to V EE and the V GS of the MOSFET to 0V. As shown in Figure 2, this transition enables the MAX5936/MAX5937 to keep the power MOSFET continually off during the board insertion phase when the circuit board first makes contact with the backplane. Without this clamp, the GATE output of a powered-down controller would be floating and the MOSFET reverse transfer capacitance (gate-to-drain)would pull up and turn on the MOSFET gate when the MOSFET drain is rapidly pulled up by the V IN step dur-ing backplane contact. The MAX5936/MAX5937 G ATE clamp can overcome the gate-to-drain capacitance of large power MOSFETs with added slew-rate control (C SLEW ) capacitors while eliminating the need for addi-tional gate-to-source capacitance. The MAX5936/MAX5937 will keep the MOSFET off indefinitely if the supply voltage is below the user-set UVLO threshold or if a short circuit is detected in the load connected to the drain of the power MOSFET.M A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE 8_______________________________________________________________________________________The MAX5936/MAX5937 conduct a load-probe test after contact transients from the hot plug-in have settled. This follows the MAX5936/MAX5937 power-up (when the UVLO condition has been met for 220ms (t LP )) and prior to the turn-on of the power MOSFET. This test pulls a user-programmable current through the load (1A, max)for up to 220ms and tests for a voltage of 200mV across the load at V OUT . This current is set by an external resis-tor, R LP , between V OUT and LP (Figure 14). When the voltage across the load exceeds 200mV, the test is trun-cated and the GATE turn-on sequence is started. If at the end of the 220ms test period the voltage across the load has not reached 200mV, the load is assumed to be short-ed and the current to the load from the LP pin is shut off.The MAX5936A_/MAX5937A_ will timeout for 16 x t LP then retry the load-probe test. The MAX5936L_/MAX5937L_ will latch the fault condition indefinitely untilthe UVLO is brought below 1.125V for 1.5ms or the power is recycled. See the Applications Information section for recommendations on selecting R LP to set the current level.Upon successful completion of the load-probe test, the MAX5936/MAX5937 enter the power-up GATE cycle and begin ramping the G ATE voltage with a 52µA current source. This current source is restricted if V OUT begins to ramp down faster than the default 9V/ms slew rate.Charging up G ATE enhances the power MOSFET in a controlled manner and ramping V OUT at a user-settable rate controls the inrush current from the backplane. The MAX5936/MAX5937 continue to charge up the G ATE until one of two events occurs: a normal power-up GATE cycle is completed or a power-up to fault management is detected (see the GATE Cycles section in Appendix A ).Figure 1. Functional Block DiagramMAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE_______________________________________________________________________________________9In a normal power-up GATE cycle, the voltage at V OUT (referenced to V EE ) ramps to below 72% of the circuit-breaker threshold voltage, V CB . At this time, the remaining GATE voltage is rapidly pulled up to full enhancement.PGOOD is asserted 1.26ms after GATE is fully enhanced (see Figure 4). If the voltage at V OUT remains above 72%of the V CB (when GATE reaches 90% of full enhance-ment), then a power-up to fault management fault has occurred (see Figure 5). GATE is rapidly pulled to V EE ,turning off the power MOSFET and disconnecting the load. PGOOD remains deasserted and the MAX5936/MAX5937 enter the fault management mode.When the power MOSFET is fully enhanced, the MAX5936/MAX5937 monitor the drain voltage (V OUT ) for circuit-breaker and short-circuit faults. The MAX5936/MAX5937 make use of the power MOSFET’s R DS(ON) as the current-sense resistance to detect excessive current through the load. The short-circuit threshold voltage,V SC , is twice V CB (V SC = 2 x V CB ) and is available in 100mV, 200mV, and 400mV thresholds. V CB and V SC are temperature-compensated (increasing with tempera-ture) to track the normalized temperature coefficient of R DS(ON) for typical power MOSFETs.When the load current is increased during full enhance-ment, this causes V OUT to exceed V CB but remains less than V SC , and starts the 1.2ms circuit-breaker glitch rejection timer. At the end of the glitch rejection period,if V OUT still exceeds V CB , the G ATE is immediately pulled to V EE (330ns), PGOOD (PGOOD ) is deasserted,and the part enters fault management. Alternatively,during full enhancement when V OUT exceeds V SC ,there is no glitch rejection timer. G ATE is immediately pulled to V EE , PG OOD is deasserted, and the part enters fault management.Figure 3. Load Probe Test During Initial Power-Up40ms/divV 20V/divV 20V/divV 20V/divALL VOLTAGESREFERENCED TO GND Figure 2. GATE Voltage Clamp During Power-Up 4ms/divC IN = 100µFFigure 4. MAX5936 Normal Condition 40ms/divFigure 5. MAX5936 Startup in Fault Condition40ms/divM A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE10______________________________________________________________________________________The V IN step immunity provides a means for transition-ing through a large step increase in V IN with minimal backplane inrush current and without shutting down the load. Without V IN step immunity (when the power MOSFET is fully enhanced), a step increase in V IN will result in a high inrush current and a large step in V OUT ,which can trip the circuit breaker. With V IN step immu-nity, the STEP_MON input detects the step before a short circuit is detected at V OUT and alters the MAX5936/MAX5937 response to V OUT exceeding V SC due to the step. The 1.25V voltage threshold at STEP_MON and a 10µA current source at STEP_MON allow the user to set the sensitivity of the step detection with an external resistor to V EE . A capacitor is placed between GND and the STEP_MON input, which, in con-junction with the resistor, sets the STEP_MON time con-stant. When a step is detected by the STEP_MON input to rise above its threshold (STEP TH ), the overcurrent fault management is blocked and remains blocked as long as STEP TH is exceeded. When STEP TH is exceed-ed, the MAX5936/MAX5937 take no action until V OUT rises above V SC or above V CB for the 1.2ms circuit-breaker glitch rejection period. When either of these conditions occurs, a step G ATE cycle begins and the GATE is immediately brought to V EE , which turns off the power MOSFET to minimize the resulting inrush current surge from the backplane and PGOOD remains assert-ed. GATE is held at V EE for 350µs, and after about 1ms,begins to ramp up thereby enhancing the power MOSFET in a controlled manner as in the power-up G ATE cycle. This provides a controlled inrush current to charge the load capacitance to the new supply volt-age (see the GATE Cycles section in Appendix A ).As in the case of the power-up G ATE cycle, if V OUT drops to less than 72% of the programmed V CB , inde-pendent of the state of STEP_MON, the G ATE voltageis rapidly pulled to full enhancement. PGOOD remains asserted throughout the step. Otherwise, if the STEP_MON input has decayed below its threshold but V OUT remains above 72% of the programmed V CB (when G ATE reaches 90% of full enhancement), (a step-to-fault management fault has occurred). GATE is rapidly pulled to V EE , turning off the power MOSFET and disconnecting the load, PG OOD (PGOOD ) is deasserted, and the MAX5936/MAX5937 enter the fault management mode.Fault ManagementFault management can be triggered by the following conditions:•V OUT exceeds 72% of V CB during G ATE ramp at 90% of full enhancement,•V OUT exceeds the V CB for longer than 1.2ms during full enhancement,•V OUT exceeds the V SC during full enhancement, and •Load-probe test fails.Once in the fault management mode, GATE will always be pulled to V EE to turn off the external MOSFET and PG OOD (PGOOD ) will always be deasserted. The MAX5936A_/MAX5937A_ have automatic retry following a fault while the MAX5936L_/MAX5937L remain latched in the fault condition.Autoretry Fault Management(MAX5936A_/MAX5937A_)If the MAX5936A_/MAX5937A_entered fault management due to circuit-breaker and short-circuit faults, the autoretry timer starts immediately. The timer times out in 3.5s (typ) and at the end of the timeout, the sequencer initiates a load-probe test. If this is successful, it starts a normal power-up GATE cycle.Figure 6. MAX5936 Response to a Step Input (V OUT < 0.74V CB )2ms/divC LOAD = 100µF R LOAD = 100ΩFigure 7. MAX5936 Response to a Step Input (V OUT > 0.74V CB )4ms/div40V 20VC LOAD = 100µF R LOAD = 20ΩMAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE______________________________________________________________________________________11Latched Fault Management (MAX5936L_/MAX5937L_)When the MAX5936L_/MAX5937L_ enter fault manage-ment, they remain in this condition indefinitely until the power is recycled or until UVLO is brought below 1.125V for 1.5ms (typ) (when the short-circuit or circuit-breaker fault has cleared, the sequencer initiates a load-probe test). If this is successful, it starts a normal power-up GATE cycle. A manual reset circuit (Figure 8)can be used to clear the latch.Circuit-Breaker ThresholdsThe MAX5936/MAX5937 are available with 100mV,200mV, and 400mV circuit-breaker thresholds. The short-circuit voltage threshold (V SC ) is twice the circuit-breaker threshold voltage (V CB ). In the MAX5936/MAX5937, V CB and V SC are temperature-compensated (increasing with temperature) to track the normalized temperature gradient of typical power MOSFETs.The proper circuit-breaker threshold for an application depends on the R DS(ON) of the external power MOSFET and the maximum current the load is expected to draw.To avoid false fault indication and dropping of the load,the designer must take into account the load response to voltage ripples and noise from the backplane power supply, as well as switching currents in the downstream DC-DC converter that is loading the circuit. While the circuit-breaker threshold has glitch rejection that ignores ripples and noise lasting less than 1.2ms, the short-circuit detection is designed to respond very quickly (less than 330ns) to a short circuit. V SC and V CB must be selected from the three available rangeswith an adequate margin to cover all possible ripples,noise, and system current transients.The short-circuit and circuit-breaker voltages are sensed at V OUT , which is the drain of the power MOSFET. The R DS(ON)of the MOSFET is the current-sense resis-tance, so the total current through the load and load capacitance is the drain current of the power MOSFET.Accordingly, the voltage at V OUT as a function of MOSFET drain current is:V OUT = I D,MOSFET x R DS(ON)The temperature compensation of the MAX5936/MAX5937 is designed to track the R DS(ON) of the typi-cal power MOSFET. Figure 9 shows the typical normal-ized tempco of the circuit-breaker threshold along with the normalized tempco of R DS(ON) for two typical power MOSFETS. When determining the circuit-breaker threshold in an application, go to the data sheet of the power MOSFET and locate the manufacturer’s maxi-mum R DS(ON)at +25°C with a V GS of 10V. Next, find the figure presenting the tempco of normalized R DS(ON)or on-resistance vs. temperature. Because this curve is in normalized units typically with a value of 1 at +25°C,it is possible to multiply the curve by the drain voltage at +25°C and convert the curve to drain voltage. Now compare this curve to that of the MAX5936/MAX5937 normalized tempco of the circuit-breaker threshold to make a determination of the tracking error in mV between the power MOSFET [I D,MOSFET x R DS(ON)]and the MAX5936/MAX5937 over the application’s operating temperature range. If the tempco of the power MOSFET is greater than that of the MAX5936/MAX5937, then additional margin will be required in selecting the circuit-breaker and short-circuit voltages at higher temperatures as compared to +25°C. When dissipation in the power MOSFET is expected to lead to local temperature elevation relative to ambient condi-tions, then it becomes imperative that the MAX5936/MAX5937 be located as close as possible to the power MOSFET. The marginal effect of temperature differ-ences on circuit-breaker and short-circuit voltages can be estimated from a comparative plot such as Figure 9.MAX5936LN and MAX5937LNThe MAX5936LN and MAX5937LN do not have circuit-breaker and short-circuit thresholds and these faults are ignored. For these devices PG OOD (PGOOD )asserts 1.26ms after G ATE has ramped to 90% of full enhancement. The step detection function of the MAX5936LN and MAX5937LN responds to V IN and V OUT steps with the same voltage thresholds as the MAX5936_C and MAX5937_C.Figure 8. Resetting MAX5936L/MAX5937L after a Fault Condition Using a Push-Button SwitchM A X 5936/M A X 5937-48V Hot-Swap Controllers with V IN Step Immunity and No R SENSE12______________________________________________________________________________________PGOOD (PGOOD ) Open-Drain OutputThe power-good outputs, PG OOD (PGOOD ), are open drain and are referenced to V OUT . They assert and latch if V OUT ramps below 72% of V CB , and with the built-in delay this occurs 1.26ms after the external MOSFET becomes fully enhanced. PG OOD (PGOOD ) deasserts any time the part enters fault management. PG OOD (PGOOD ) has a delayed response to UVLO. The GATE goes to V EE when UVLO is brought below 1.125V for 1.5ms. This turns off the power MOSFET and allows V OUT to rise depending on the RC time constant of the load. PG OOD (PGOOD ), in this situation, deasserts when V OUT rises above V CB for more than 1.4ms or above V SC , whichever occurs first (see Figure 12b).Due to the open-drain driver, PG OOD (PGOOD )requires an external pullup resistor to GND. Due to this external pullup, PG OOD will not follow positive V IN steps as well as if it were driven by an active pullup. As a result, when PG OOD (PGOOD) is asserted high, an apparent negative glitch appears at PGOOD (PGOOD )during a positive V IN step. This negative glitch is a result of the RC time constant of the external resistor and the PGOOD pin capacitance lagging the V IN step.It is not due to switching of the internal logic. To mini-mize this negative transient, it may be necessary to increase the pullup current and/or to add a small amount of capacitance from PGOOD (PGOOD ) to GND to compensate for the pin capacitance.WARNING:For the MAX5936_N/MAX5937_N, PGOOD (PGOOD ) asserts 1.26ms after the power MOSFET is fully enhanced, independent of V OUT . Once the MOSFET is fully enhanced and UVLO is pulled below its respective threshold, G ATE pulls to V EE to turn off the power MOSFET and disconnect the load. When UVLO is cycled low, PG OOD (PGOOD ) is deasserted. In sum-mary, once the MOSFET is fully enhanced, the MAX5936_N/ MAX5937_N ignore V OUT and deassert PG OOD (PGOOD ) when UVLO goes low or when the power to the MAX5936_N/ MAX5937_N is fully recy-cled.Undervoltage Lockout (UVLO)UVLO provides an accurate means to set the turn-on volt-age level for the MAX5936/MAX5937. Use a resistor-divider network from G ND to V EE to set the desired turn-on voltage (Figure 11). UVLO has hysteresis with a rising threshold of 1.25V and a falling threshold of 1.125V.A startup delay of 220ms allows contacts and voltages to settle prior to initiating the startup sequence (Figure 12a).Figure 9. MAX5936/MAX5937 Normalized Circuit-Breaker Threshold (V CB )Figure 10. Circuit-Breaker Voltage Margin for High and Low Tempco Power MOSFETSMAX5936/MAX5937-48V Hot-Swap Controllers with V INStep Immunity and No R SENSE______________________________________________________________________________________13This startup delay is from a valid UVLO condition until the start of the load-probe test. There is glitch rejection on UVLO going low, which requires that V UVLO remains below its falling threshold for 1.5ms to turn off the part (Figure 12b). Use the following formula to calculate the MAX5936/MAX59337 turn-on voltage:Where V ON is the desired turn-on voltage of theMAX5936/MAX5937 and V UVLO_REF,R is the 1.25V UVLO rising threshold.Output Voltage (V OUT )Slew-Rate ControlThe V OUT slew rate controls the inrush current required to charge the load capacitor. The MAX5936/MAX5937have a default internal slew rate set for 9V/ms. The inter-nal circuit establishing this slew rate accommodates up to about 1000pF of reverse transfer capacitance (miller capacitance) in the external power MOSFET without effecting the default slew rate. Using the default slew rate, the inrush current required to charge the load capacitance is given by:I INRUSH (mA) = C LOAD (µF) x SR (V/ms)where SR = 9V/ms (default, typ).Applications InformationSelecting Resistor and Capacitorfor Step MonitorWhen a positive V IN step or ramp occurs, the V IN increase results in a voltage rise at both STEP_MON and V OUT relative to V EE . When the voltage at STEP_MON is above STEP TH the MAX5936/MAX5937block short-circuit and circuit-breaker faults. During this STEP_MON high condition, if V OUT rises above V SC , the MAX5936/MAX5937 immediately and very rapidly pull GATE to V EE . This turns off the power MOSFET to avoid inrush current spiking. G ATE is held low for 350µs.About 1ms after the start of G ATE pulldown, the MAX5936/MAX5937 begin to ramp GATE up to turn on the MOSFET in a controlled manner, which results in ramping V OUT down to the new supply level (see the GATE Cycles section in Appendix A ).Figure 11. Setting the MAX5936/MAX5937 Turn-On VoltageFigure 12. UVLO Timing Diagram。

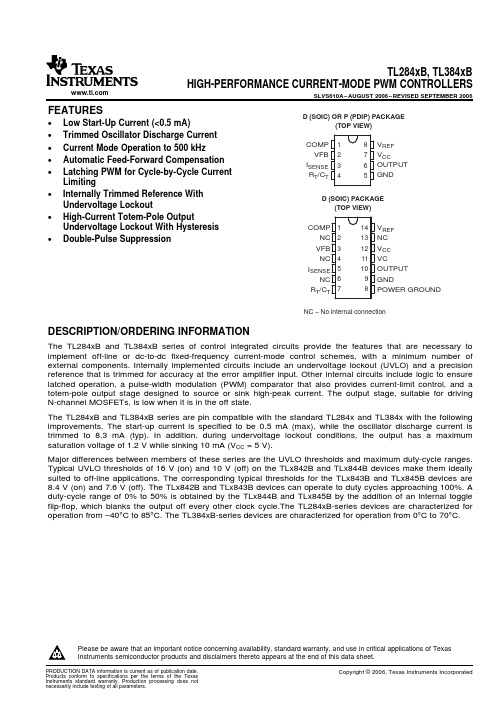

3843B中文资料

TL284xB, TL384xB HIGH-PERFORMANCE CURRENT-MODE PWM CONTROLLERS

SLVS610A – AUGUST 2006 – REVISED SEPTEMBER 2006

FEATURES

• Low Start-Up Current (<0.5 mA) • Trimmed Oscillator Discharge Current • Current Mode Operation to 500 kHz • Automatic Feed-Forward Compensation • Latching PWM for Cycle-by-Cycle Current

TOP-SIDE MARKING TL2842BP TL2843BP TL2844BP TL2845BP 2842B

2843B

2844B

2845B

TL2842B

TL2843B

TL2844B

TL2845B TL3842BP TL3843BP TL3844BP TL3845BP 3842B

3843B

3844B

FUNCTIONAL BLOCK DIAGRAM

34 V NOM 5 GND

−+

UVLO

5-V VREF EN

8 VREF

RT/CT 4

2.5 V OSC

VREF Good

Logic

Internal Bias

6 OUTPUT

T

2 VFB COMP 1

Error Amplifier

+ −

2R

R

1V

ISENSE 3 A. Pin numbers shown are for the 8-pin D package.

1SMA5930BT3中文资料

1. FR4 Board, using Motorola minimum recommended footprint, as shown in case 403B outline dimensions spec. 2. Non–repetitive current pulse. 3. Measured on 8.3 ms single half sine–wave or equivalent square wave, duty cycle = 4 pulse per minute maximum.

元器件交易网

Rating and Typical Characteristic Curves (TA = 25°C)

4 100

PD , MAXIMUM POWER DISSIPATION (WATTS)

IZ, ZENER CURRENT (mA) 125 150

3.2

10

813B 814B 815B 816B 817B 818B 819B 820B 821B 822B 823B 824B 825B 826B 827B 828B 829B 830B 831B 832B 833B 834B 835B 836B 837B 838B 839B 840B 841B 842B 843B 844B 845B

NOTE: Tolerance and Voltage Designation Tolerance designation – The type number listed indicates a tolerance of ±5%.

MOTOROLA 2

1SMA5913BT3 through 1SMA5945BT3

1SMA5913BT3 1SMA5914BT3 1SMA5915BT3 1SMA5916BT3 1SMA5917BT3 1SMA5918BT3 1SMA5919BT3 1SMA5920BT3 1SMA5921BT3 1SMA5922BT3 1SMA5923BT3 1SMA5924BT3 1SMA5925BT3 1SMA5926BT3 1SMA5927BT3 1SMA5928BT3 1SMA5929BT3 1SMA5930BT3 1SMA5931BT3 1SMA5932BT3 1SMA5933BT3 1SMA5934BT3 1SMA5935BT3 1SMA5936BT3 1SMA5937BT3 1SMA5938BT3 1SMA5939BT3 1SMA5940BT3 1SMA5941BT3 1SMA5942BT3 1SMA5943BT3 1SMA5944BT3 1SMA5945BT3

SI5938DU-T1-E3;中文规格书,Datasheet资料

Vishay SiliconixSi5938DUDocument Number: Dual N-Channel 20-V (D-S) MOSFETPRODUCT SUMMARYV DS (V)R DS(on) (Ω)I D (A)aQ g (Typ.)200.039 at V GS = 4.5 V 6 6 nC 0.045 at V GS = 2.5 V 60.055 at V GS = 1.8 V6Si5938DU-T1-GE3 (Lead (Pb)-free and Halogen-free)Notes:a.Package limited.b.Surface Mounted on 1" x 1" FR4 board.c.t = 5 s.d.See Solder Profile (/ppg?73257). The PowerPAK ChipFET is a leadless package. The end of the lead terminal is exposed copper (not plated) as a result of the singulation process in manufacturing. A solder fillet at the exposed copper tip cannot be guaranteed and is not required to ensure adequate bottom side solder interconnection.e.Rework Conditions: manual soldering with a soldering iron is not recommended for leadless components.f.Maximum under Steady State conditions is 105 °C/W. ABSOLUTE MAXIMUM RATINGS T A = 25 °C, unless otherwise notedParameter Symbol Limit UnitDrain-Source VoltageV DS 20VGate-Source VoltageV GS ± 8Continuous Drain Current (T J = 150 °C)T C = 25 °C I D 6a A T C = 70 °C 6a T A = 25 °C 7.2b, c T A = 70 °C 5.8b, cPulsed Drain Current I DM 20Continuous Source-Drain Diode CurrentT C = 25 °C I S 6.9T A = 25 °C 1.9b, c Maximum Power DissipationT C = 25 °C P D 8.3W T C = 70 °C 5.3T A = 25 °C 2.3b, c T A = 70 °C 1.5b, cOperating Junction and Storage T emperature Range T J , T stg - 55 to 150°C Soldering Recommendations (Peak Temperature)d, e 260THERMAL RESISTANCE RATINGSParameter Symbol Typical Maximum UnitMaximum Junction-to-Ambient b, ft ≤ 5 s R thJA 4555°C/WMaximum Junction-to-Case (Drain)Steady State R thJC 1215FEATURES•Halogen-free•TrenchFET ® Power MOSFET•New Thermally Enhanced PowerPAK ®ChipFET ® Package - Small Footprint Area - Low On-Resistance - Thin 0.8 mm ProfileAPPLICATIONS•Load Switch for Portable Applications • Document Number: 73463Vishay SiliconixSi5938DUNotes:a. Pulse test; pulse width ≤ 300 µs, duty cycle ≤ 2 %.b. Guaranteed by design, not subject to production testing.Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.SPECIFICATIONS T J = 25 °C, unless otherwise notedParameter Symbol Test Conditions Min.Typ.Max.UnitStaticDrain-Source Breakdown Voltage V DS V GS = 0 V, I D = 250 µA20V V DS Temperature Coefficient ΔV DS /T J I D = 250 µA 17.4mV/°C V GS(th) Temperature Coefficient ΔV GS(th)/T J - 2.6Gate-Source Threshold Voltage V GS(th) V DS = V GS , I D = 250 µA 0.4 1.0VGate-Source LeakageI GSS V DS = 0 V , V GS = ± 8 V ± 100 nsZero Gate Voltage Drain Current I DSS V DS = 20 V , V GS = 0 V - 1µA V DS = 20 V , V GS = 0 V , T J = 55 °C- 10On-State Drain Current aI D(on) V DS ≤ 5 V , V GS = 4.5 V - 20ADrain-Source On-State Resistance a R DS(on) V GS = 4.5 V , I D = 4.4 A 0.0320.039ΩV GS = 2.5 V , I D = 4.1 A 0.0370.045V GS = 1.8 V , I D = 1.8 A 0.04550.055Forward T ransconductance a g fsV DS = 10 V , I D = 4.4 A22S Dynamic bInput Capacitance C iss V DS = 10 V , V GS = 0 V , f = 1 MHz520pFOutput CapacitanceC oss 100Reverse Transfer Capacitance C rss 60Total Gate Charge Q g V DS = 10 V , V GS = 8 V , ID = 4.4 A 10.516nC V DS = 10 V, V GS = 4.5 V , I D = 4.4 A 69Gate-Source Charge Q gs 0.91Gate-Drain Charge Q gd 0.7Gate Resistance R g f = 1 MHz1.9ΩTurn-On Delay Time t d(on) V DD = 10 V , R L = 2.8 Ω I D ≅ 3.6 A, V GEN = 4.5 V , R g = 1 Ω2030ns Rise Timet r 65100Turn-Off Delay Time t d(off) 4060Fall Timet f 1015Turn-On Delay Time t d(on) V DD = 10 V , R L = 2.8 ΩI D ≅ 3.6 A, V GEN = 8 V, R g = 1 Ω510Rise Timet r 1220Turn-Off Delay Time t d(off) 2640Fall Timet f815Drain-Source Body Diode Characteristics Continuous Source-Drain Diode Current I S T C = 25 °C14.8A Pulse Diode Forward Current I SM 20Body Diode VoltageV SD I S = 1.2 A, V GS = 0 V0.8 1.2V Body Diode Reverse Recovery Time t rr I F = 1.2 A, dI/dt = 100 A/µs, T J = 25 °C4570ns Body Diode Reverse Recovery Charge Q rr 2132nC Reverse Recovery Fall Time t a 29nsReverse Recovery Rise Timet b16Document Number: Si5938DUVishay SiliconixTYPICAL CHARACTERISTICS 25°C, unless otherwise noted ArraySource-Drain Diode Forward VoltageSingle Pulse Power, Junction-to-Ambient Document Number: 73463Document Number: Vishay SiliconixSi5938DUTYPICAL CHARACTERISTICS 25°C, unless otherwise noted* The power dissipation P D is based on T J(max) = 150 °C, using junction-to-case thermal resistance, and is more useful in settling the upper dissipation limit for cases where additional heatsinking is used. It is used to determine the current rating, when this rating falls below the package limit.Current Derating*Power Derating Document Number: 73463Vishay SiliconixSi5938DUTYPICAL CHARACTERISTICS 25°C, unless otherwise notedVishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see /ppg?73463.Normalized Thermal Transient Impedance, Junction-to-AmbientNormalized Thermal Transient Impedance, Junction-to-CaseApplication Note 826Vishay SiliconixA P P L I C A T I O N N O T ERECOMMENDED MINIMUM PADS FOR PowerPAK ® ChipFET ® DualReturn to IndexLegal Disclaimer Notice VishayDisclaimerALL PRODU CT, PRODU CT SPECIFICATIONS AND DATA ARE SU BJECT TO CHANGE WITHOU T NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively,“Vishay”), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.Statements regarding the suitability of products for certain types of applications are based on Vishay’s knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer’s responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer’s technical experts. Product specifications do not expand or otherwise modify Vishay’s terms and conditions of purchase, including but not limited to the warranty expressed therein.Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk and agree to fully indemnify and hold Vishay and its distributors harmless from and against any and all claims, liabilities, expenses and damages arising or resulting in connection with such use or sale, including attorneys fees, even if such claim alleges that Vishay or its distributor was negligent regarding the design or manufacture of the part. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.Material Category PolicyVishay Intertechnology, Inc. hereb y certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.Revision: 12-Mar-121Document Number: 91000分销商库存信息: VISHAYSI5938DU-T1-E3。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

元器件交易网

Rating and Typical Characteristic Curves (TA = 25°C)

4 100

PD , MAXIMUM POWER DISSIPATION (WATTS)

IZ, ZENER CURRENT (mA) 125 150

3.2

10

1. FR4 Board, using Motorola minimum recommended footprint, as shown in case 403B outline dimensions spec. 2. Non–repetitive current pulse. 3. Measured on 8.3 ms single half sine–wave or equivalent square wave, duty cycle = 4 pulse per minute maximum.

813B 814B 815B 816B 817B 818B 819B 820B 821B 822B 823B 824B 825B 826B 827B 828B 829B 830B 831B 832B 833B 834B 835B 836B 837B 838B 839B 840B 841B 842B 843B 844B 845B

Max Zener Impedance Device Nominal Zener Voltage VZ @ IZT Volts 3.3 3.6 3.9 4.3 4.7 5.1 5.6 6.2 6.8 7.5 8.2 9.1 10 11 12 13 15 16 18 20 22 24 27 30 33 36 39 43 47 51 56 62 68 Test Current IZT mA 113.6 104.2 96.1 87.2 79.8 73.5 66.9 60.5 55.1 50 45.7 41.2 37.5 34.1 31.2 28.8 25 23.4 20.8 18.7 17 15.6 13.9 12.5 11.4 10.4 9.6 8.7 8.0 7.3 6.7 6.0 5.5 ZZT @ IZT Ohms 10 9.0 7.5 6.0 5.0 4.0 2.0 2.0 2.5 3.0 3.5 4.0 4.5 5.5 6.5 7.0 9.0 10 12 14 17.5 19 23 26 33 38 45 53 67 70 86 100 120 ZZK Ohms 500 500 500 500 500 350 250 200 200 400 400 500 500 550 550 550 600 600 650 650 650 700 700 750 800 850 900 950 1000 1100 1300 1500 1700 IZK mA 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 1.0 0.5 0.5 0.5 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 0.25 Max Reverse Leakage Current IR µA 50 35.5 12.5 2.5 2.5 2.5 2.5 2.5 2.5 2.5 2.5 2.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 0.5 VR Volts 1.0 1.0 1.0 1.0 1.5 2.0 3.0 4.0 5.2 6.5 6.8 7.0 8.0 8.4 9.1 9.9 11.4 12.2 13.7 15.2 16.7 18.2 20.6 22.8 25.1 27.4 29.7 32.7 35.8 38.8 42.6 47.1 51.7 Max DC Zener Current IZM mAdc 455 417 385 349 319 294 268 242 221 200 183 165 150 136 125 115 100 94 83 75 68 63 56 50 45 42 38 35 32 29 27 24 22 Devce Marking

1SMA5945BT3

PLASTIC SURFACE MOUNT ZENER DIODES 1.5 WATTS 3.3–68 VOLTS

SMA CASE 403B–01 PLASTIC

MAXIMUM RATINGS AND CHARACTERISTICS

Rating DC Power Dissipation @ TL = 75°C (Note 1) Derate above 75°C DC Power Dissipation @ TA = 25°C (Note 1) Derate above 25°C Thermal Resistance from Junction to Lead Thermal Resistance from Junction to Ambient Peak Forward Surge @ TA = 25°C, (JEDEC Method, Note 3) Typical Ppk Dissipation @ TL < 25°C, (Note 2, PW–10/1000 µs per Figure 8) Typical Ppk Dissipation @ TL < 25°C, (Note 2, PW–8/20 µs per Figure 9) Operating and Storage Junction Temperature Range Symbol PD PD RθJL RθJA IFSM Ppk Ppk TJ, Tstg Value 1.5 20 900 7.2 29 111 20 200 1000 150 Unit Watts mW/°C mW mW/°C °C/W °C/W Amps Watts Watts °C

NOTE: Tolerance and Voltage Designation Tolerance designation – The type number listed indicates a tolerance of ±5%.

MOTOROLA 2

1SMA5913BT3 through 1SMA5945BT3

This complete new line of 1.5 Watt Zener Diodes offers the following advantages. Specification Features: • Voltage Range – 3.3 to 68 V • ESD Rating of Class 3 (>16 kV) per Human Body Model • Flat Handling Surface for Accurate Placement • Package Design for Top Side or Bottom Circuit Board Mounting • Low Profile Package • Available in Tape and Reel • Ideal Replacement for MELF Packages Mechanical Characteristics: • Case: Void–free, transfer-molded plastic • Maximum Case Temperature for Soldering Purposes: 260°C for 10 seconds • Finish: All external surfaces are corrosion resistant with readily solderable leads • Polarity: Cathode indicated by molded polarity notch • Mounted Position: Any

8 6 4 2 0 –2 –4 2

VZ @ IZT

θVZ , TEMPERATURE COEFFICIENT (mV/ °C)

θVZ , TEMPERATURE COEFFICIENT (mV/ °C)

10

100 VZ @ IZT

4

6 8 VZ, ZENER VOLTAGE (VOLTS)

10

12

10 10 VZ, ZENER VOLTAGE (VOLTS)

2.4 TL 1.6

1

0.8 0 0 25

TA

0.1 50 75 100 T, TEMPERATURE (°C) 0 2 4 6 VZ, ZENER VOLTAGE (VOLTS) 8 10

Figure 1. Steady State Power Derating

Figure 2. VZ – 3.3 thru 10 Volts

100

Figure 3. Zener Voltage – 3.3 to 12 Volts

Figure 4. Zener Voltage – 14 to 68 Volts

ZZ, DYNAMIC IMPEDANCE (OHMS)

100 IZ(dc) = 1 mA

10

10 mA IZ(rms) = 0.1 IZ(dc) 100 VZ, ZENER VOLTAGE (VOLTS)

REV 1

© Motorola, Inc. 1996

1SMA5913BT3 through 1SMA5945BT3

MOTOROLA 1

元器件交易网

ELECTRICAL CHARACTERISTICS (VF = 1.5 Volts @ IF = 200 mA for all types)

20 mA 10

Figure 5. Effect of Zener Voltage

1SMA5913BT3 through 1SMA5945BT3