LM48556TLX中文资料

W9864G6IH-6中文资料

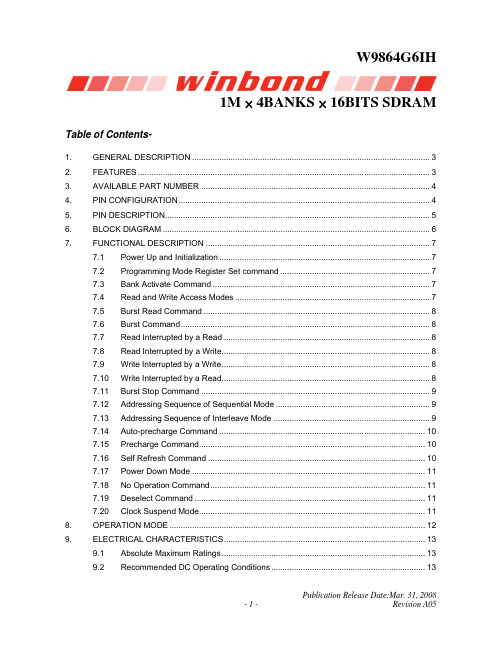

1M × 4BANKS × 16BITS SDRAM Table of Contents-1.GENERAL DESCRIPTION (3)2.FEATURES (3)3.AVAILABLE PART NUMBER (4)4.PIN CONFIGURATION (4)5.PIN DESCRIPTION (5)6.BLOCK DIAGRAM (6)7.FUNCTIONAL DESCRIPTION (7)7.1Power Up and Initialization (7)7.2Programming Mode Register Set command (7)7.3Bank Activate Command (7)7.4Read and Write Access Modes (7)7.5Burst Read Command (8)7.6Burst Command (8)7.7Read Interrupted by a Read (8)7.8Read Interrupted by a Write (8)7.9Write Interrupted by a Write (8)7.10Write Interrupted by a Read (8)7.11Burst Stop Command (9)7.12Addressing Sequence of Sequential Mode (9)7.13Addressing Sequence of Interleave Mode (9)7.14Auto-precharge Command (10)7.15Precharge Command (10)7.16Self Refresh Command (10)7.17Power Down Mode (11)7.18No Operation Command (11)7.19Deselect Command (11)7.20Clock Suspend Mode (11)8.OPERATION MODE (12)9.ELECTRICAL CHARACTERISTICS (13)9.1Absolute Maximum Ratings (13)9.2Recommended DC Operating Conditions (13)9.3Capacitance (13)9.4DC Characteristics (14)9.5AC Characteristics and Operating Condition (15)10.TIMING WAVEFORMS (18)10.1Command Input Timing (18)10.2Read Timing (19)10.3Control Timing of Input/Output Data (20)10.4Mode Register Set Cycle (21)11.OPERATINOPERATING TIMING EXAMPLE (22)11.1Interleaved Bank Read (Burst Length = 4, CAS Latency = 3) (22)11.2Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge) (23)11.3Interleaved Bank Read (Burst Length = 8, CAS Latency = 3) (24)11.4Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge) (25)11.5Interleaved Bank Write (Burst Length = 8) (26)11.6Interleaved Bank Write (Burst Length = 8, Auto-precharge) (27)11.7Page Mode Read (Burst Length = 4, CAS Latency = 3) (28)11.8Page Mode Read/Write (Burst Length = 8, CAS Latency = 3) (29)11.9Auto-precharge Read (Burst Length = 4, CAS Latency = 3) (30)11.10Auto-precharge Write (Burst Length = 4) (31)11.11Auto Refresh Cycle (32)11.12Self Refresh Cycle (33)11.13Bust Read and Single Write (Burst Length = 4, CAS Latency = 3) (34)11.14Power-down Mode (35)11.15Auto-precharge Timing (Write Cycle) (36)11.16Auto-precharge Timing (Read Cycle) (37)11.17Timing Chart of Read to Write Cycle (38)11.18Timing Chart of Write to Read Cycle (38)11.19Timing Chart of Burst Stop Cycle (Burst Stop Command) (39)11.20Timing Chart of Burst Stop Cycle (Precharge Command) (39)11.21CKE/DQM Input Timing (Write Cycle) (40)11.22CKE/DQM Input Timing (Read Cycle) (41)12.PACKAGE SPECIFICATION (42)12.154L TSOP (II)-400 mil (42)13.REVISION HISTORY (43)1. GENERAL DESCRIPTIONW9864G6IH is a high-speed synchronous dynamic random access memory (SDRAM), organized as 1M words × 4 banks × 16 bits. W9864G6IH delivers a data bandwidth of up to 200M words per second. For different application, W9864G6IH is sorted into the following speed grades: -5, -6, -7/-7S. The -5 parts can run up to 200MHz/CL3. The -6 parts can run up to 166MHz/CL3. The -7/-7S parts can run up to 143MHz/CL3. And the grade of -7S with t RP = 18nS.Accesses to the SDRAM are burst oriented. Consecutive memory location in one page can be accessed at a burst length of 1, 2, 4, 8 or full page when a bank and row is selected by an ACTIVE command. Column addresses are automatically generated by the SDRAM internal counter in burst operation. Random column read is also possible by providing its address at each clock cycle.The multiple bank nature enables interleaving among internal banks to hide the precharging time.By having a programmable Mode Register, the system can change burst length, latency cycle, interleave or sequential burst to maximize its performance. W9864G6IH is ideal for main memory in high performance applications.2. FEATURES• 3.3V± 0.3V for -5/-6 speed grades power supply• 2. 7V~3.6V for -7/-7S speed grades power supply• 1,048,576 words × 4 banks × 16 bits organization•Self Refresh Current: Standard and Low Power•CAS Latency: 2 & 3•Burst Length: 1, 2, 4, 8 and full page•Sequential and Interleave Burst•Byte data controlled by LDQM, UDQM•Auto-precharge and controlled precharge•Burst read, single write operation•4K refresh cycles/64mS• Interface: LVTTL•Packaged in TSOP II 54-pin, 400 mil using Lead free materials with RoHS compliant3. AVAILABLE PART NUMBERPART NUMBERSPEEDSELF REFRESH CURRENT (MAX.)OPERATING TEMPERATUREW9864G6IH-5 200MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-6 166MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-7 143MHz/CL3 2 mA 0°C ~ 70°C W9864G6IH-7S 143MHz/CL32 mA0°C ~ 70°C4. PIN CONFIGURATION5. PIN DESCRIPTION6. BLOCK DIAGRAM7. FUNCTIONAL DESCRIPTION7.1 Power Up and InitializationThe default power up state of the mode register is unspecified. The following power up and initialization sequence need to be followed to guarantee the device being preconditioned to each user specific needs.During power up, all V DD and V DDQ pins must be ramp up simultaneously to the specified voltage when the input signals are held in the "NOP" state. The power up voltage must not exceed V DD + 0.3V on any of the input pins or V DD supplies. After power up, an initial pause of 200 µS is required followed by a precharge of all banks using the precharge command. To prevent data contention on the DQ bus during power up, it is required that the DQM and CKE pins be held high during the initial pause period. Once all banks have been precharged, the Mode Register Set Command must be issued to initialize the Mode Register. An additional eight Auto Refresh cycles (CBR) are also required before or after programming the Mode Register to ensure proper subsequent operation.7.2 Programming Mode Register Set commandAfter initial power up, the Mode Register Set Command must be issued for proper device operation. All banks must be in a precharged state and CKE must be high at least one cycle before the Mode Register Set Command can be issued. The Mode Register Set Command is activated by the low signals of RAS, CAS, CS and WE at the positive edge of the clock. The address input data during this cycle defines the parameters to be set as shown in the Mode Register Operation table. A new command may be issued following the mode register set command once a delay equal to t RSC has elapsed. Please refer to the next page for Mode Register Set Cycle and Operation Table.7.3 Bank Activate CommandThe Bank Activate command must be applied before any Read or Write operation can be executed. The operation is similar to RAS activate in EDO DRAM. The delay from when the Bank Activate command is applied to when the first read or write operation can begin must not be less than the RAS to CAS delay time (t RCD). Once a bank has been activated it must be precharged before another Bank Activate command can be issued to the same bank. The minimum time interval between successive Bank Activate commands to the same bank is determined by the RAS cycle time of the device (t RC). The minimum time interval between interleaved Bank Activate commands (Bank A to Bank B and vice versa) is the Bank to Bank delay time (t RRD). The maximum time that each bank can be held active is specified as t RAS(max.).7.4 Read and Write Access ModesAfter a bank has been activated, a read or write cycle can be followed. This is accomplished by setting RAS high and CAS low at the clock rising edge after minimum of t RCD delay. WE pin voltage level defines whether the access cycle is a read operation (WE high), or a write operation (WE low). The address inputs determine the starting column address. Reading or writing to a different row within an activated bank requires the bank be precharged and a new Bank Activate command be issued. When more than one bank is activated, interleaved bank Read or Write operations are possible. By using the programmed burst length and alternating the access and precharge operations between multiple banks, seamless data access operation among many different pages can be realized. Read or Write Commands can also be issued to the same bank or between active banks on every clock cycle.7.5 Burst Read CommandThe Burst Read command is initiated by applying logic low level to CS and CAS while holding RAS and WE high at the rising edge of the clock. The address inputs determine the starting column address for the burst. The Mode Register sets type of burst (sequential or interleave) and the burst length (1, 2, 4, 8, full page) during the Mode Register Set Up cycle. Table 2 and 3 in the next page explain the address sequence of interleave mode and sequence mode.7.6 Burst CommandThe Burst Write command is initiated by applying logic low level to CS, CAS and WE while holding RAS high at the rising edge of the clock. The address inputs determine the starting column address. Data for the first burst write cycle must be applied on the DQ pins on the same clock cycle that the Write Command is issued. The remaining data inputs must be supplied on each subsequent rising clock edge until the burst length is completed. Data supplied to the DQ pins after burst finishes will be ignored.7.7 Read Interrupted by a ReadA Burst Read may be interrupted by another Read Command. When the previous burst is interrupted, the remaining addresses are overridden by the new read address with the full burst length. The data from the first Read Command continues to appear on the outputs until the CAS Latency from the interrupting Read Command the is satisfied.7.8 Read Interrupted by a WriteTo interrupt a burst read with a Write Command, DQM may be needed to place the DQs (output drivers) in a high impedance state to avoid data contention on the DQ bus. If a Read Command will issue data on the first and second clocks cycles of the write operation, DQM is needed to insure the DQs are tri-stated. After that point the Write Command will have control of the DQ bus and DQM masking is no longer needed.7.9 Write Interrupted by a WriteA burst write may be interrupted before completion of the burst by another Write Command. When the previous burst is interrupted, the remaining addresses are overridden by the new address and data will be written into the device until the programmed burst length is satisfied.7.10 Write Interrupted by a ReadA Read Command will interrupt a burst write operation on the same clock cycle that the Read Command is activated. The DQs must be in the high impedance state at least one cycle before the new read data appears on the outputs to avoid data contention. When the Read Command is activated, any residual data from the burst write cycle will be ignored.7.11 Burst Stop CommandA Burst Stop Command may be used to terminate the existing burst operation but leave the bank open for future Read or Write Commands to the same page of the active bank, if the burst length is full page. Use of the Burst Stop Command during other burst length operations is illegal. The Burst Stop Command is defined by having RAS and CAS high with CS and WE low at the rising edge of the clock. The data DQs go to a high impedance state after a delay, which is equal to the CAS Latency in a burst read cycle, interrupted by Burst Stop.7.12 Addressing Sequence of Sequential ModeA column access is performed by increasing the address from the column address which is input to the device. The disturb address is varied by the Burst Length as shown in Table 2.7.14 Auto-precharge CommandIf A10 is set to high when the Read or Write Command is issued, then the auto-precharge function is entered. During auto-precharge, a Read Command will execute as normal with the exception that the active bank will begin to precharge automatically before all burst read cycles have been completed. Regardless of burst length, it will begin a certain number of clocks prior to the end of the scheduled burst cycle. The number of clocks is determined by CAS Latency.A Read or Write Command with auto-precharge cannot be interrupted before the entire burst operation is completed for the same bank. Therefore, use of a Read, Write, or Precharge Command is prohibited during a read or write cycle with auto-precharge. Once the precharge operation has started, the bank cannot be reactivated until the Precharge time (t RP) has been satisfied. Issue of Auto-Precharge command is illegal if the burst is set to full page length. If A10 is high when a Write Command is issued, the Write with Auto-Precharge function is initiated. The SDRAM automatically enters the precharge operation two clocks delay from the last burst write cycle. This delay is referred to as write t WR. The bank undergoing auto-precharge cannot be reactivated until t WR and t RP are satisfied. This is referred to as t DAL, Data-in to Active delay (t DAL = t WR + t RP). When using the Auto-precharge Command, the interval between the Bank Activate Command and the beginning of the internal precharge operation must satisfy t RAS(min).7.15 Precharge CommandThe Precharge Command is used to precharge or close a bank that has been activated. The Precharge Command is entered when CS, RAS and WE are low and CAS is high at the rising edge of the clock. The Precharge Command can be used to precharge each bank separately or all banks simultaneously. Three address bits, A10, BS0, and BS1 are used to define which bank(s) is to be precharged when the command is issued. After the Precharge Command is issued, the precharged bank must be reactivated before a new read or write access can be executed. The delay between the Precharge Command and the Activate Command must be greater than or equal to the Precharge time (t RP).7.16 Self Refresh CommandThe Self Refresh Command is defined by having CS, RAS, CAS and CKE held low with WE high at the rising edge of the clock. All banks must be idle prior to issuing the Self Refresh Command. Once the command is registered, CKE must be held low to keep the device in Self Refresh mode. When the SDRAM has entered Self Refresh mode all of the external control signals, except CKE, are disabled. The clock is internally disabled during Self Refresh Operation to save power. The device will exit Self Refresh operation after CKE is returned high. A minimum delay time is required when the device exits Self Refresh Operation and before the next command can be issued. This delay is equal to the t AC cycle time plus the Self Refresh exit time.If, during normal operation, AUTO REFRESH cycles are issued in bursts (as opposed to being evenly distributed), a burst of 4,096 AUTO REFRESH cycles should be completed just prior to entering and just after exiting the self refresh mode.7.17 Power Down ModeThe Power Down mode is initiated by holding CKE low. All of the receiver circuits except CKE are gated off to reduce the power. The Power Down mode does not perform any refresh operations, therefore the device can not remain in Power Down mode longer than the Refresh period (t REF) of the device.The Power Down mode is exited by bringing CKE high. When CKE goes high, a No Operation Command is required on the next rising clock edge, depending on t CK. The input buffers need to be enabled with CKE held high for a period equal to t CKS(min.) + t CK(min.).7.18 No Operation CommandThe No Operation Command should be used in cases when the SDRAM is in a idle or a wait state to prevent the SDRAM from registering any unwanted commands between operations. A No Operation Command is registered when CS is low with RAS, CAS, and WE held high at the rising edge of the clock. A No Operation Command will not terminate a previous operation that is still executing, such as a burst read or write cycle.7.19 Deselect CommandThe Deselect Command performs the same function as a No Operation Command. Deselect Command occurs when CS is brought high, the RAS, CAS, and WE signals become don't Care.7.20 Clock Suspend ModeDuring normal access mode, CKE must be held high enabling the clock. When CKE is registered low while at least one of the banks is active, Clock Suspend Mode is entered. The Clock Suspend mode deactivates the internal clock and suspends any clocked operation that was currently being executed. There is a one clock delay between the registration of CKE low and the time at which the SDRAM operation suspends. While in Clock Suspend mode, the SDRAM ignores any new commands that are issued. The Clock Suspend mode is exited by bringing CKE high. There is a one clock cycle delay from when CKE returns high to when Clock Suspend mode is exited.8. OPERATION MODEFully synchronous operations are performed to latch the commands at the positive edges of CLK. Table 1 shows the truth table for the operation commands.Table 1 Truth Table (Note (1), (2))Notes:(1) v = valid, x = Don't care, L = Low Level, H = High Level(2) CKEn signal is input leve l when commands are provided.(3) These are state of bank designated by BS0, BS1 signals.(4) Device state is full page burst operation.(5) Power Down Mode can not be entered in the burst cycle.When this command asserts in the burst cycle, device state is clock suspend mode.9. ELECTRICAL CHARACTERISTICS9.1 Absolute Maximum RatingsNOTESUNIT PARAMETER SYMBOLRATINGInput, Column Output Voltage V IN, V OUT-0.3 ~ V DD+ 0.3V 1Power Supply Voltage V DD, V DDQ -0.3 ~ 4.6 V 1Operating Temperature T OPR 0 ~ 70 °C 1Storage Temperature T STG -55 ~ 150 °C 1Soldering Temperature (10s) T SOLDER 260 °C 11 Power Dissipation P D 1 WShort Circuit Output Current I OUT 50 mA1 Note: Exposure to conditions beyond those listed under Absolute Maximum Ratings may adversely affect the life and reliabilityof the device.9.2 Recommended DC Operating Conditions(T A = 0 to 70°C for -5/-6/-7/-7S)UNITNOTESMAX.PARAMETER SYM.MIN.TYP.Supply Voltage (Normal operation) V DD 3.0 3.3 3.6 V 2Supply voltage (for –7/-7S) V DD 2.7- 3.6 V 2 Supply Voltage for I/O Buffer V DDQ 3.0 3.3 3.6 V 2Supply Voltage for I/O Buffer (for -7/-7S) V DDQ 2.7- 3.6 V 2Input High Voltage V IH 2.0- V DD + 0.3 V 2Input Low Voltage V IL -0.3- 0.8 V 2Note: V IH(max) = V DD/ V DDQ+1.5V for pulse width < 5 nSV IL(min) = V SS/ V SSQ-1.5V for pulse width < 5 nS9.3 Capacitance(V DD =3V±0.3V for-5/-6, V DD = 2.7V-3.6V for -7/-7S , T A = 25 °C, f = 1 MHz)Note: These parameters are periodically sampled and not 100% tested9.4 DC Characteristics(V DD = 3V±0.3V for-5/-6 ,V DD = 2.7V-3.6V for -7/-7S on T A = 0 to 70°C)NOTESUNITMIN.PARAMETER SYMBOLMAX.Input Leakage CurrentI I(L) -5 5 µA(0V ≤V IN≤ V DD, all other pins not under test = 0V)Output Leakage Currentl O(L) -5 5 µA(Output disable, 0V ≤ V OUT≤ V DDQ)LVTTL Output ″H″ Level VoltageV OH 2.4 - V(I OUT = -2 mA)LVTTL Output“L″ Level VoltageV OL - 0.4 V(I OUT = 2 mA)9.5 AC Characteristics and Operating Condition(V DD =3V±0.3V for-5/-6, V DD = 2.7V-3.6V for -7/-7S on T A = 0 to 70°C) (Notes: 5, 6)-5 -6 -7 -7SPARAMETER SYM. MIN. MAX. MIN.MAX. MIN.MAX.MIN.MAX.UNIT NOTESRef/Active to Ref/ActiveCommand Period t RC 55 60 65 65 Active to precharge Command Period t RAS 40 10000042 10000045 10000045 100000 Active to Read/Write Command Delay Time t RCD 15 18 20 20 nSRead/Write(a) to Read/ Write(b) Command Periodt CCD 1 1 1 1 t CK Precharge to Active(b) Command Period t RP 15 18 20 18Active(a) to Active(b) Command Periodt RRD 10 12 14 14 nSWrite Recovery TimeCL* = 2CL* = 3t WR2 2 2 2 t CKCLK Cycle TimeCL* = 210 1000 7.5 1000 10 100010 1000 CL* = 3t CK 5 1000 6 1000 7 10007 1000CLK High Levelt CH 2 2 2 29 CLK Low Level t CL 2 2 2 29 Access Time from CLKCL* = 2 - 6 6 6CL* = 3 t AC4.5 55.5 5.5 10 Output Data Hold Time t OH 2 2 2 2 10 Output Data HighImpedance Time t HZ 2 5 2 6 2 7 2 7 7 Output Data Low Impedance Time t LZ 0 0 0 0 10 Power Down Mode Entry Timet SB 0 5 0 6 0 7 0 7 Transition Time of CLK (Rise and Fall) t T 1 1 1 1 Data-in-Set-up Time t DS 1.5 1.5 1.5 1.5 9 Data-in Hold Time t DH 1 1 1 1 9 Address Set-up Time t AS 1.5 1.5 1.5 1.5 9 Address Hold Time t AH 1 1 1 1 9 CKE Set-up Time t CKS 1.5 1.5 1.5 1.5 9 CKE Hold Time t CKH 1 1 1 1 9 Command Set-up Time t CMS 1.5 1.5 1.5 1.5 9 Command Hold Timet CMH 1 1 11nS 9AC Characteristics and Operating Condition, continued-5 -6 -7-7SPARAMETER SYM. MIN. MAX. MIN.MAX.MIN.MAX.MIN.MAX.UNIT NOTESRefresh Time t REF 64 64 64 64 mS Mode Register SetCycle Time t RSC 10 14 14 14 nS Exit self refresh to ACTIVE Commandt XSR 70 72 75 75 nSNotes:1.Operation exceeds “Absolute Maximum Ratings” may cause permanent damage to the devices.2. All voltages are referenced to V SS‧2.7V~3.6V power supply for -7/-7S speed grade.3. These parameters depend on the cycle rate and listed values are measured at a cycle rate with the minimum values of t CK and t RC .4. These parameters depend on the output loading conditions. Specified values are obtained with output open.5. Power up sequence please refer to "Functional Description" section described before.6. AC Test Load diagram.7. t HZ defines the time at which the outputs achieve the open circuit condition and is not referenced to output level.8. These parameters account for the number of clock cycles and depend on the operating frequencyof the clock, as follows the number of clock cycles = specified value of timing/ clock period (count fractions as whole number)(1)t CH is the pulse width of CLK measured from the positive edge to the negative edge referenced to V IH (min.).t CL is the pulse width of CLK measured from the negative edge to the positive edge referenced to V IL (max.).(2)A.C Latency Characteristics9. Assumed input rise and fall time (t T ) = 1nS.If tr & tf is longer than 1nS, transient time compensation should be considered,i.e., [(tr + tf)/2-1]nS should be added to the parameter( The t T maximum can’t be more than 10nS for low frequency application. )10. If clock rising time (t T) is longer than 1nS, (t T/2-0.5)nS should be added to the parameter.10. TIMING WAVEFORMS 10.1 Command Input Timing10.2 Read Timing10.3 Control Timing of Input/Output Data10.4 Mode Register Set Cycle11. OPERATINOPERATING TIMING EXAMPLE11.1 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3)11.2 Interleaved Bank Read (Burst Length = 4, CAS Latency = 3, Auto-precharge)11.3 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3)11.4 Interleaved Bank Read (Burst Length = 8, CAS Latency = 3, Auto-precharge)11.5 Interleaved Bank Write (Burst Length = 8)11.6 Interleaved Bank Write (Burst Length = 8, Auto-precharge)11.7 Page Mode Read (Burst Length = 4, CAS Latency = 3)11.8 Page Mode Read/Write (Burst Length = 8, CAS Latency = 3)11.9 Auto-precharge Read (Burst Length = 4, CAS Latency = 3)11.10 Auto-precharge Write (Burst Length = 4)11.11 Auto Refresh Cycle11.12 Self Refresh Cycle11.13 Bust Read and Single Write (Burst Length = 4, CAS Latency = 3)11.14 Power-down Mode11.15 Auto-precharge Timing (Write Cycle)11.16 Auto-precharge Timing (Read Cycle)11.17 Timing Chart of Read to Write Cycle11.18 Timing Chart of Write to Read Cycle11.19 Timing Chart of Burst Stop Cycle (Burst Stop Command)11.20 Timing Chart of Burst Stop Cycle (Precharge Command)11.21 CKE/DQM Input Timing (Write Cycle)11.22 CKE/DQM Input Timing (Read Cycle)Publication Release Date:Mar. 31, 200812. PACKAGE SPECIFICATION12.1 54L TSOP (II)-400 milPublication Release Date:Mar. 31, 2008Publication Release Date:Mar. 31, 200813. REVISION HISTORYVERSION DATEPAGEDESCRIPTIONP01 Sep. 14, 2007 All Create preliminary data sheet A01 Dec. 12, 2007 AllInitial formal data sheetA02Dec. 24, 20073, 4, 13, 14,15, 16Remove -6I speed grade13Revise overshoot/undershoot pulse widthBefore V IH (max.) = V CC /V CCQ +1.2V for pulse width < 5 nS After V IH (max.) = V CC /V CCQ +1.2V for pulse width < 3 nS Before V IL (min.) = V SS /V SSQ -1.2V for pulse width < 5 nS After V IL (min.) = V SS /V SSQ -1.2V for pulse width < 3 nSA03Jan. 29, 20083, 4, 15Revise -7/-7S parts AC parameter CLK cycle time of CL2 t CK value from 7nS to 7.5nSA04Feb. 26, 200815Revise -6 part AC parameter Access Time from CLK of CL2 t AC value from 5.5nS to 6nS13Revise overshoot/undershoot pulse widthBefore V IH (max.) = V CC /V CCQ +1.2V for pulse width < 3 nS After V IH (max.) = V CC /V CCQ +1.5V for pulse width < 5 nS Before V IL (min.) = V SS /V SSQ -1.2V for pulse width < 3 nS After V IL (min.) = V SS /V SSQ -1.5V for pulse width < 5 nSA05Mar. 31, 200815Revise -7/-7S parts AC parameter CLK cycle time of CL2 t CK value from 7.5nS to 10nSImportant NoticeWinbond products are not designed, intended, authorized or warranted for use as components in systems or equipment intended for surgical implantation, atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, or for other applications intended to support or sustain life. Further more, Winbond products are not intended for applications wherein failure of Winbond products could result or lead to a situation wherein personal injury, death or severe property or environmental damage could occur.Winbond customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Winbond for any damages resulting from such improper use or sales.。

MA46506中文资料

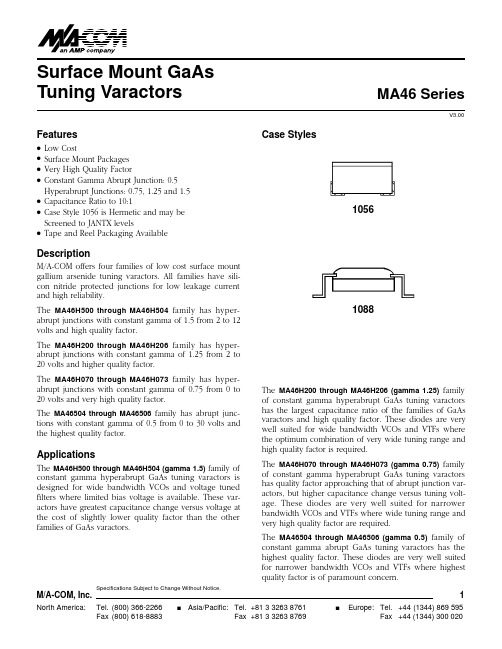

Surface Mount GaAsTuning Varactors MA46 SeriesV3.00 Featuresq Low Costq Surface Mount Packagesq Very High Quality Factorq Constant Gamma Abrupt Junction: 0.5Hyperabrupt Junctions: 0.75, 1.25 and 1.5q Capacitance Ratio to 10:1q Case Style 1056 is Hermetic and may beScreened to JANTX levelsq Tape and Reel Packaging AvailableDescriptionM/A-COM offers four families of low cost surface mountgallium arsenide tuning varactors. All families have sili-con nitride protected junctions for low leakage currentand high reliability.The MA46H500 through MA46H504family has hyper-abrupt junctions with constant gamma of 1.5 from 2 to 12volts and high quality factor.The MA46H200 through MA46H206family has hyper-abrupt junctions with constant gamma of 1.25 from 2 to20 volts and higher quality factor.The MA46H070 through MA46H073family has hyper-abrupt junctions with constant gamma of 0.75 from 0 to 20 volts and very high quality factor.The MA46504 through MA46506family has abrupt junc-tions with constant gamma of 0.5 from 0 to 30 volts and the highest quality factor.ApplicationsThe MA46H500 through MA46H504 (gamma 1.5)family of constant gamma hyperabrupt GaAs tuning varactors is designed for wide bandwidth VCOs and voltage tuned filters where limited bias voltage is available. These var-actors have greatest capacitance change versus voltage at the cost of slightly lower quality factor than the other families of GaAs varactors.The MA46H200 through MA46H206 (gamma 1.25)family of constant gamma hyperabrupt GaAs tuning varactors has the largest capacitance ratio of the families of GaAs varactors and high quality factor. These diodes are very well suited for wide bandwidth VCOs and VTFs where the optimum combination of very wide tuning range and high quality factor is required.The MA46H070 through MA46H073 (gamma 0.75)family of constant gamma hyperabrupt GaAs tuning varactors has quality factor approaching that of abrupt junction var-actors, but higher capacitance change versus tuning volt-age. These diodes are very well suited for narrower bandwidth VCOs and VTFs where wide tuning range and very high quality factor are required.The MA46504 through MA46506 (gamma 0.5)family of constant gamma abrupt GaAs tuning varactors has the highest quality factor. These diodes are very well suited for narrower bandwidth VCOs and VTFs where highestquality factor is of paramount concern.1088元器件交易网Electrical Specifications @ 25°CGamma 0.5 Abrupt Tuning VaractorsBreakdown Voltage @ 10 µA = 30 V minimum Reverse Current @ 24 V = 100 nA maximum Gamma = 0.48 - 0.50, V R = 0 to 30 VElectrical Specifications @ 25°CGamma 0.75 Hyperabrupt Tuning VaractorsBreakdown Voltage @ 10 µA = 20 V minimum Reverse Current @ 16 V = 100 nA maximum Gamma = 0.68 - 0.83, V R = 0 to 20 VAbsolute Maximum Ratings @ 25°CCAPACITANCE vs REVERSE VOLTAGEREVERSE VOLTAGE (VOLTS).1101100T O T A L C A P A C I T A N C E (p F )Typical Performance CurvesCAPACITANCE vs REVERSE VOLTAGE65006503REVERSE VOLTAGE (VOLTS)1001010.1T O T A L C A P A C I T A N C E (p F )CathodeBottom ViewBNot to ScaleTop ViewCathodeTyp.Ordering InformationThese GaAs tuning varactors are available in either case style as shown. When ordering, specify the desired case style by adding the case designation as a suffix to the model number. For example, a MA46H200-1088 speci-fies a 1.25 gamma hyperabrupt tuning diode in case style 1088.Case Styles 1056INCHESMILLIMETERS DIM.MIN.MAX.MIN.MAX.A 0.1750.195 4.44 4.95B 0.0400.050 1.02 1.27C0.0850.095 2.16 2.41D 0.0150.0250.380.64E 0.0100.0150.250.38F 0.0150.0200.380.51G0.0040.0060.100.15H 0.0200.0300.510.76J 0.0130.0330.330.84K0.0030.0050.080.13INCHESMILLIMETERS DIM.MIN.MAX.MIN.MAX.A 0.0650.075 1.72 1.90B 0.0340.0410.86 1.04C 0.0300.0360.760.91D0.0130.0170.330.44E 0.0100.0140.250.36F0.0430.0531.091.35Package Capacitance: 0.15 pF Typical Package Inductance: 0.45 nH TypicalPackage Capacitance: 0.13 pF Typical Package Inductance: 0.50 nH Typical1088。

LM6364中文资料

LM6164/LM6264/LM6364High Speed Operational AmplifierGeneral DescriptionThe LM6164family of high-speed amplifiers exhibits an ex-cellent speed-power product in delivering 300V per µs and 175MHz GBW (stable down to gains as low as +5)with only 5mA of supply current.Further power savings and applica-tion convenience are possible by taking advantage of the wide dynamic range in operating supply voltage which ex-tends all the way down to +5V.These amplifiers are built with National’s VIP ™(Vertically In-tegrated PNP)process which produces fast PNP transistors that are true complements to the already fast NPN devices.This advanced junction-isolated process delivers high speed performance without the need for complex and expensive di-electric isolation.Featuresn High slew rate:300V/µs n High GBW product:175MHz n Low supply current:5mA n Fast settling:100ns to 0.1%n Low differential gain:<0.1%n Low differential phase:<0.1˚n Wide supply range: 4.75V to 32V nStable with unlimited capacitive loadApplicationsn Video amplifiern Wide-bandwidth signal conditioning n Radar nSonarConnection DiagramsVIP ™is a trademark of National Semiconductor Corporation.DS009153-8NS Package Number J08A,M08A or N08E10-Lead FlatpakDS009153-15Top ViewNS Package Number W10AMay 1999LM6164/LM6264/LM6364High Speed Operational Amplifier©1999National Semiconductor Corporation Connection Diagrams(Continued)Temperature Range Package NSCDrawing Military Industrial Commercial−55˚C≤T A≤+125˚C−25˚C≤T A≤+85˚C0˚C≤T A≤+70˚CLM6264N LM6364N8-Pin Molded DIP N08E LM6164J/8838-Pin Ceramic DIP J08A5962-8962401PALM6364M8-Pin Molded Surface Mt.M08A LM6164WG/88310-Lead Ceramic SOIC WG10A 5962-8962401XALM6164W/88310-Pin W10A5962-8962401HA Ceramic Flatpak2Absolute Maximum Ratings(Note1)If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.Supply Voltage(V+−V−)36V Differential Input Voltage(Note7)±8V Common-Mode Input Voltage(Note11)(V+−0.7V)to(V−+0.7V) Output Short Circuit to Gnd(Note2)Continuous Soldering InformationDual-In-Line Package(N,J)Soldering(10sec.)260˚C Small Outline Package(M)Vapor Phase(60sec.)215˚C Infrared(15sec.)220˚CSee AN-450“Surface Mounting Methods and Their Effect on Product Reliability”for other methods of soldering surface mount devices.Storage Temperature Range−65˚C to+150˚C Max Junction Temperature(Note3)150˚C ESD Tolerance(Notes7,8)±700V Operating RatingsTemperature Range(Note3)LM6164−55˚C≤T J≤+125˚C LM6264−25˚C≤T J≤+85˚C LM63640˚C≤T J≤+70˚C Supply Voltage Range 4.75V to32V Note1:“Absolute Maximum Ratings”indicate limits beyond which damage to the device may occur.Operating Ratings indicate conditions for which the device is functional,but do not guarantee specific performance limits.DC Electrical CharacteristicsThe following specifications apply for Supply Voltage=±15V,V CM=0,R L≥100kΩand R S=50Ωunless otherwise noted. Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.LM6164LM6264LM6364Symbol Parameter Conditions Typ Limit Limit Limit Units(Notes4,12)(Note4)(Note4)V OS Input Offset Voltage2449mV6611maxV OS Input Offset Voltage6µV/˚C Drift Average DriftI b Input Bias Current 2.5335µA656maxI OS Input Offset Current1503503501500nA8006001900maxI OS Input Offset Current0.3nA/˚C Drift Average DriftR IN Input Resistance Differential100kΩC IN Input Capacitance 3.0pFA VOL Large Signal V OUT=±10V,R L=2kΩ 2.5 1.8 1.8 1.3V/mVVoltage Gain(Note10)0.9 1.2 1.1minR L=10kΩ9V CM Input Common-Mode Supply=±15V+14.0+13.9+13.9+13.8V Voltage Range+13.8+13.8+13.7min−13.5−13.3−13.3−13.2V−13.1−13.1−13.1minSupply=+5V 4.0 3.9 3.9 3.8V(Note5) 3.8 3.8 3.7min1.5 1.7 1.7 1.8V1.9 1.9 1.9max CMRR Common-Mode−10V≤V CM≤+10V105868680dB Rejection Ratio808278min PSRR Power Supply±10V≤V±≤±16V96868680dB Rejection Ratio808278min3DC Electrical Characteristics(Continued)The following specifications apply for Supply Voltage=±15V,V CM=0,R L≥100kΩand R S=50Ωunless otherwise noted.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.LM6164LM6264LM6364Symbol Parameter Conditions Typ Limit Limit Limit Units(Notes4,12)(Note4)(Note4)V O Output Voltage Supply=+5V+14.2+13.5+13.5+13.4V Swing and R L=2kΩ+13.3+13.3+13.3min−13.4−13.0−13.0−12.9V−12.7−12.8−12.8minSupply=+5V 4.2 3.5 3.5 3.4Vand R L=2kΩ 3.3 3.3 3.3min(Note10) 1.3 1.7 1.7 1.8V2.0 1.9 1.9maxOutput Short Source65303030mA Circuit Current202525minSink65303030mA202525minI S Supply Current 5.0 6.5 6.5 6.8mA6.8 6.7 6.9min AC Electrical CharacteristicsThe following specifications apply for Supply Voltage=±15V,V CM=0,R L≥100kΩand R S=50Ωunless otherwise noted.Boldface limits apply for T A=T J=T MIN to T MAX;all other limits T A=T J=25˚C.LM6164LM6264LM6364Symbol Parameter Conditions Typ Limit Limit Limit Units(Notes4,12)(Note4)(Note4)GBW Gain-Bandwidth F=20MHz175140140120MHzmin Product100120100Supply=±5V120SR Slew Rate A V=+5(Note9)300200200200V/µsmin180180180Supply=±5V200PBW Power Bandwidth V OUT=20V PP 4.5MHzT S Settling Time10V Step to0.1%100nsA V=−4,R L=2kΩφm Phase Margin A V=+545DegA D Differential Gain NTSC,A V=+10<0.1%φD Differential Phase NTSC,A V=+10<0.1Dege np-p Input Noise F=10kHz8Voltagei np-p Input Noise F=10kHz 1.5CurrentNote2:Continuous short-circuit operation at elevated ambient temperature can result in exceeding the maximum allowed junction temperature of150˚C.Note3:The typical junction-to-ambient thermal resistance of the molded plastic DIP(N)is105˚C/Watt,the molded plastic SO(M)package is155˚C/Watt,and the cerdip(J)package is125˚C/Watt.All numbers apply for packages soldered directly into a printed circuit board.Note4:Limits are guaranteed by testing or correlation.Note5:For single supply operation,the following conditions apply:V+=5V,V−=0V,V CM=2.5V,V OUT=2.5V.Pin1&Pin8(V OS Adjust)are each connected to Pin4(V−)to realize maximum output swing.This connection will degrade V OS.Note6:C L≤5pF.Note7:In order to achieve optimum AC performance,the input stage was designed without protective clamps.Exceeding the maximum differential input voltage re-sults in reverse breakdown of the base-emitter junction of one of the input transistors and probable degradation of the input parameters(especially V OS,I OS,and Noise).Note8:The average voltage that the weakest pin combinations(those involving Pin2or Pin3)can withstand and still conform to the datasheet limits.The test circuit used consists of the human body model of100pF in series with1500Ω.4AC Electrical Characteristics(Continued)Note9:V IN=4V step.For supply=±5V,V IN=1V step.Note10:Voltage Gain is the total output swing(20V)divided by the input signal required to produce that swing.Note11:The voltage between V+and either input pin must not exceed36V.Note12:A military RETS electrical test specification is available on request.At the time of printing,the LM6164J/883RETS spec complied with the Boldface limits in this column.The LM6164J/883may also be procured as Standard Military Drawing#5962-8962401PA.Typical Performance Characteristics(RL =10kΩ,TA=25˚C unless otherwise specified)Supply Current vsSupply VoltageDS009153-16Common-ModeRejection RatioDS009153-17Power SupplyRejection RatioDS009153-18Gain-BandwidthProductDS009153-19Propagation DelayRise and Fall TimeDS009153-20Gain-Bandwidth Productvs Load CapacitanceDS009153-21Slew Rate vsLoad CapacitanceDS009153-22Overshoot vsLoad CapacitanceDS009153-23Slew RateDS009153-24 5Typical Performance Characteristics(R L =10k Ω,T A =25˚C unless otherwisespecified)(Continued)Voltage Gain vs Load ResistanceDS009153-25Gain vs Supply VoltageDS009153-26Differential Gain (Note 13)DS009153-6Differential Phase (Note 13)DS009153-7Note 13:Differential gain and differential phase measured for four series LM6364op amps in series with an LM6321buffer.Error added by LM6321is negligible.Test performed using Tektronix Type 520NTSC test system.Configured with a gain of +5(each output attenuated by 80%)Step Response;Av =+5TIME (50 ns /div)I n p u t (1v /d i v ) O u t p u t (5v /d i v )DS009153-1 6Typical Performance Characteristics(RL =10kΩ,TA=25˚C unless otherwisespecified)(Continued)Input Noise VoltageDS009153-27Input Noise CurrentDS009153-28Power BandwidthDS009153-29Open-LoopFrequency ResponseDS009153-30Open-LoopFrequency ResponseDS009153-31Output ResistanceOpen-LoopDS009153-32Common-Mode InputSaturation VoltageDS009153-33Output Saturation VoltageDS009153-34Bias Current vsCommon-Mode VoltageDS009153-35 7Simplified Schematic Applications TipsThe LM6364has been compensated for gains of5or greater (over specified ranges of temperature,power supply voltage, and load).Since this compensation involved adding emitter-degeneration resistors in the op amp’s input stage, the open-loop gain was reduced as the stability increased. Gain error due to reduced A VOL is most apparent at high gains;thus,the uncompensated LM6365is appropriate for gains of25or more.If unity-gain operation is desired,the LM6361should be used.The LM6361,LM6364,and LM6365have the same high slew rate(typically300V/µs), regardless of their compensation.The LM6364is unusually tolerant of capacitive loads.Most op amps tend to oscillate when their load capacitance is greater than about200pF(in low-gain circuits).However, load capacitance on the LM6364effectively increases its compensation capacitance,thus slowing the op amp’s re-sponse and reducing its bandwidth.The compensation is not ideal,though,and ringing or oscillation may occur in low-gain circuits with large capacitive loads.To overcompen-sate the LM6364for operation at gains less than5,a series resistor-capacitor network should be added between the in-put pins(as shown in the Typical Applications,Noise Gain Compensation)so that the high-frequency noise gain rises to at least5.Power supply bypassing will improve the stability and tran-sient response of the LM6364,and is recommended for ev-ery design.0.01µF to0.1µF ceramic capacitors should be used(from each supply“rail”to ground);if the device is far away from its power supply source,an additional2.2µF to 10µF(tantalum)may be required for extra noise reduction. Keep all leads short to reduce stray capacitance and lead in-ductance,and make sure ground paths are low-impedance, especially where heavier currents will be flowing.Stray ca-pacitance in the circuit layout can cause signal coupling be-tween adjacent nodes,so that circuit gain unintentionally varies with frequency.Breadboarded circuits will work best if they are built using generic PC boards with a good ground plane.If the op amps are used with sockets,as opposed to being soldered into the circuit,the additional input capacitance may degrade circuit performance.DS009153-38Typical ApplicationsOffset Voltage AdjustmentDS009153-10Video-Bandwidth AmplifierDS009153-12Noise-Gain Compensation for Gains ≤5DS009153-11R X C X ≥(2π•25MHz)−15R X =R 1+R F (1+R 1/R 2)9Physical Dimensions inches(millimeters)unless otherwise notedCeramic Dual-In-Line Package(J)Order Number LM6164J/883NS Package Number J08AMolded Package SO(M)Order Number LM6364MNS Package Number M08A 10Physical Dimensions inches(millimeters)unless otherwise noted(Continued)Molded Dual-In-Line Package(N)Order Number LM6264N or LM6364NNS Package Number N08E10-Pin Ceramic FlatpakOrder Number LM6164W/883NS Package Number W10A11NotesLIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION.As used herein:1.Life support devices or systems are devices or systems which,(a)are intended for surgical implant into the body,or (b)support or sustain life,and whose failure to perform when properly used in accordance with instructions for use provided in the labeling,can be reasonably expected to result in a significant injury to the user.2.A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system,or to affect its safety or effectiveness.National Semiconductor Corporation AmericasTel:1-800-272-9959Fax:1-800-737-7018Email:support@National Semiconductor EuropeFax:+49(0)180-5308586Email:europe.support@Deutsch Tel:+49(0)180-5308585English Tel:+49(0)180-5327832Français Tel:+49(0)180-5329358Italiano Tel:+49(0)180-5341680National Semiconductor Asia Pacific Customer Response Group Tel:65-2544466Fax:65-2504466Email:sea.support@National Semiconductor Japan Ltd.Tel:81-3-5639-7560Fax:81-3-5639-7507L M 6164/L M 6264/L M 6364H i g h S p e e d O p e r a t i o n a l A m p l i f i e rNational does not assume any responsibility for use of any circuitry described,no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.。

LTC4555资料

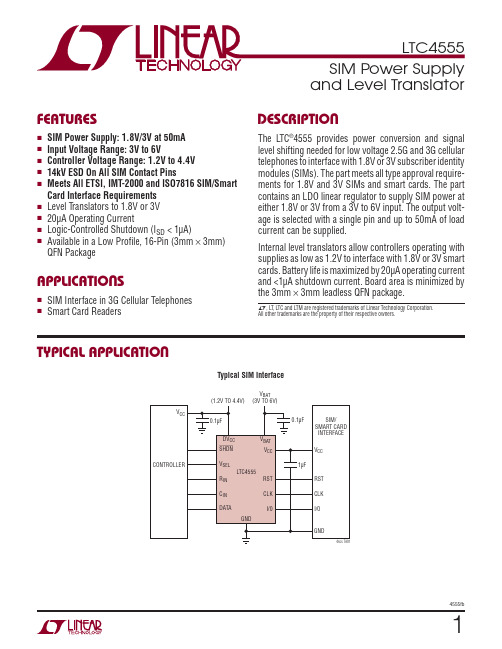

14555fbT YPICAL APPLICATIOND ESCRIPTION and Level TranslatorThe L TC ®4555 provides power conversion and signallevel shifting needed for low voltage 2.5G and 3G cellular telephones to interface with 1.8V or 3V subscriber identity modules (SIMs). The part meets all type approval require-ments for 1.8V and 3V SIMs and smart cards. The part contains an LDO linear regulator to supply SIM power at either 1.8V or 3V from a 3V to 6V input. The output volt-age is selected with a single pin and up to 50mA of load current can be supplied.Internal level translators allow controllers operating with supplies as low as 1.2V to interface with 1.8V or 3V smart cards. Battery life is maximized by 20μA operating current and <1μA shutdown current. Board area is minimized by the 3mm × 3mm leadless QFN package.Typical SIM InterfaceL , L T , L TC and L TM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.F EATURESA PPLICATIONS nSIM Power Supply: 1.8V/3V at 50mA n Input Voltage Range: 3V to 6Vn Controller Voltage Range: 1.2V to 4.4V n 14kV ESD On All SIM Contact PinsnMeets All ETSI, IMT-2000 and ISO7816 SIM/Smart Card Interface Requirements n Level T ranslators to 1.8V or 3V n 20μA Operating Currentn Logic-Controlled Shutdown (I SD < 1μA)n Available in a Low Profi le, 16-Pin (3mm × 3mm) QFN PackagenSIM Interface in 3G Cellular Telephones n Smart Card ReadersV BAT24555fbV BAT , DV CC , V CC to GND ............................–0.3V to 6.5V Digital Inputs to GND ................................–0.3V to 6.5V CLK, RST , I/O to GND .......................–0.3V to V CC + 0.3VV CC Short-Circuit Duration ...................................Infinite Operating Temperature Range (Note 2)....–40°C to 85°C Junction Temperature ...........................................125°C Storage Temperature Range ...................–65°C to 125°C(Note 1)161514135678TOP VIEW 17UD PACKAGE16-LEAD (3mm s 3mm) PLASTIC QFN91011124321SHDN V SEL DV CC NC NCCLK GND RSTN CD A T AR I NC I NV B A TN CV C CI /OT JMAX = 125°C, θJA = 68°C/W , θJC = 4.2°C/WEXPOSED PAD (PIN 17) IS GND, MUST BE SOLDERED TO PCBORDER INFORMATIONLEAD FREE FINISH TAPE AND REEL PART MARKING PACKAGE DESCRIPTIONTEMPERATURE RANGE L TC4555EUD#PBFL TC4555EUD#TRPBFLAAA16-Lead (3mm × 3mm) Plastic QFN–40°C to 85°CConsult L TC Marketing for parts specifi ed with wider operating temperature ranges.Consult L TC Marketing for information on non-standard lead based fi nish parts.For more information on lead free part marking, go to: http://www.linear .com/leadfree/ For more information on tape and reel specifi cations, go to: http://www.linear .com/tapeandreel/P IN CONFIGURATIONA BSOLUTE MAXIMUM RATINGS E LECTRICAL CHARACTERISTICS The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C.PARAMETER CONDITIONSMIN TYP MAX UNITSV BAT Operating Voltage l36V V BAT Operating Current I CC = 0mAl 2030μA V BAT Shutdown Current SHDN = 0V , V BAT = 4.5V l 1μA DV CC Operating Voltage l1.24.4V DV CC Operating Current f CLK = 1MHz l 510μA DV CC Shutdown Current SHDN = 0Vl 1μA DV CC Undervoltage Lockout l 0.5 1.1V V CC Output VoltageV SEL = DV CC , V BAT = 3V , I VCC = 50mAV SEL = DV CC , V BAT = 3.3V to 6V , I VCC = 0mA to 50mA V SEL = 0, V BAT = 2.6V to 6V , I VCC = 0mA to 50mA l l2.81.7 2.83.01.8 3.21.9VV V V CC Short-Circuit Current V CC Shorted to GND 60110175mA Controller Inputs/Outputs Input Voltage Range SHDN , V SEL , R IN , C IN , DATA 0DV CC V Input Current (I IH /I IL )SHDN , V SEL , R IN , C IN l –100100nA High Input Threshold Voltage (V IH )R IN , C IN l 0.7 × DV CCV Low Input Threshold Voltage (V IL )R IN , C IN l 0.2 × DV CCV High Input Threshold Voltage (V IH )SHDN , V SEL l 1V Low Input Threshold Voltage (V IL )SHDN , V SELl0.4V34555fbE LECTRICAL CHARACTERISTICS Note 1: Stresses beyond those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.Note 2: The L TC4555E is guaranteed to meet performance specifi cations from 0°C to 85°C. Specifi cations over the –40°C to 85°C operatingtemperature range are assured by design, characterization and correlation with statistical process controls.The l denotes the specifi cations which apply over the full operatingtemperature range, otherwise specifi cations are at T A = 25°C.PARAMETERCONDITIONS MIN TYP MAX UNITS High Level Input Current (I IH )DATAl –2020μA Low Level Input Current (I IL ) DATAl 1mA High Level Output Voltage (V OH )DATA I OH = 20μA, I/O = V CC l 0.7 × DV CCV Low Level Output Voltage (V OL )DATAI OL = –200μA, I/O = 0V l0.4V DATA Pull-Up Resistance Between DATA and DV CC 132030kΩSIM Inputs/Outputs (V CC = 3V)High Level Output Voltage (V OH )I/O, I OH = 20μA, DATA = DV CC l 0.8 × V CCVLow Level Output Voltage (V OL )I/O, I OL = –1mA, DATA = 0V l 0.4V High Level Output Voltage (V OH )RST , CLK, I OH = 20μA l 0.9 × V CCV Low Level Output Voltage (V OL ) RST , CLK, I OL = –200μA l 0.4V I/O Pull-Up Resistance Between I/O and V CC6.51014kΩSIM Inputs/Outputs (V CC = 1.8V)High Level Output Voltage (V OH )I/O, I OH = 20μA, DATA = DV CC l 0.8 × V CCV Low Level Output Voltage (V OL )I/O, I OL = –1mA, DATA = 0V l 0.3V High Level Output Voltage (V OH )RST , CLK, I OH = 20μA l 0.9 × V CCV Low Level Output Voltage (V OL ) RST , CLK, I OL = –200μA l 0.2 × V CCV I/O Pull-Up Resistance Between I/O and V CC6.51014kΩSIM Timing Parameters CLK Rise/Fall Time C CLK = 30pF , V CC = 1.8V/3V l 18ns RST , I/O Rise/Fall Time RST , I/O Loaded with 30pF , V CC = 1.8V/3Vl 1μs Max CLK Frequency 5MHz V CC Turn-On Time SHDN = 1, (Note 3)0.5ms V CC Discharge Time to 1VSHDN = 0, (Note 3)0.5msNote 3: Specifi cation is guaranteed by design and not 100% tested in production.44555fbT YPICAL PERFORMANCE CHARACTERISTICS V CC Short-Circuit CurrentI BAT vs V BATP IN FUNCTIONS TEMPERATURE (°C)–40S H O R T -C I R C U I T C U R R E N T (m A )17015013011090705020604555 G01–204080100V BAT (V)2.5I B A T (μA )22201816141210 4.0 5.04555 G023.0 3.54.55.56.0SHDN (Pin 1): Controller Driven Shutdown Pin. This pin should be high (DV CC ) for normal operation and low to activate a low current shutdown mode.V SEL (Pin 2): V CC Voltage Select Pin. A low level selects V CC = 1.8V while driving this pin to DV CC selects V CC = 3V .DV CC (Pin 3): Supply Voltage for the Controller Side I/O Pins (C IN , R IN , DATA). When below 1.1V , the V CC supply is disabled. This pin should be bypassed with a 0.1μF ceramic capacitor close to the pin.NC (Pins 4, 6, 12, 16): No Connect.V BAT (Pin 5): V CC Supply Input. This pin can be between 3V and 6V for normal operation. V BAT quiescent current reduces to <1μA in shutdown. This pin should be bypassed with a 0.1μF ceramic capacitor close to the pin.V CC (Pin 7): SIM Card V CC Supply. A 1μF low ESR capacitor needs to be connected close to the V CC pin for stable opera-tion. This pin is discharged to GND during shutdown.I/O (Pin 8): SIM-Side Data I/O. The SIM card output must be on an open-drain driver capable of sourcing >1mA.RST (Pin 9): Reset Output Pin for the SIM Card.GND (Pin 10): Ground for the SIM and Controller . Proper grounding and bypassing is required to meet 14kV ESD specifi cations. CLK (Pin 11): Clock Output Pin for the SIM Card. This pin is pulled to ground during shutdown. Fast rising and falling edges necessitate careful board layout for the CLK node.C IN (Pin 13): Clock Input from the Controller .R IN (Pin 14): Reset Input from the Controller .DATA (Pin 15): Controller Side Data I/O. This pin is used for bidirectional data transfer . The controller output must be an open-drain confi guration. The open-drain output must be capable of sinking greater than 1mA.Exposed Pad (Pin 17): GND. Must be soldered to PCB.B LOCK DIAGRAMV54555fbA PPLICATIONS INFORMATIONThe L TC4555 provides both regulated power and internal level translators to allow low voltage controllers to interface with 1.8V or 3V SIMs or smart cards. The part meets all ETSI, IMT-2000 and ISO7816 requirements for SIM and smart card interfaces.V CC Voltage RegulatorThe V CC voltage regulator is a 50mA low dropout (LDO) regulator with a digitally selected 1.8V or 3V output. The output voltage is selected via the V SEL pin. The output is internally current limited and is capable of surviving an indefi nite short to GND.The V CC output should be bypassed with a 1μF capacitor. The L TC4555 can use either a low ESR ceramic capacitor or a tantalum electrolytic capacitor on the V CC pin, with no special ESR requirements.V BAT should be bypassed with a 0.1μF ceramic capacitor. Level T ranslatorsAll SIMs and smart cards contain a clock input, a reset input and a bidirectional data input/output. The L TC4555 provides level translators to allow controllers to com-municate with the SIM. The CLK and RST lines to the SIM are level shifted from the controller supply (GND to DV CC) to the SIM supply (GND to V CC). The data input to the SIM requires an open-drain output on the controller. On-chip pull-up resistors are provided for both the DATA and I/O lines.Shutdown ModesThe L TC4555 enters a low current shutdown mode by pulling the SHDN pin low. The SHDN pin is an active low input that the controller can use to directly shut down the part.ESD ProtectionAll pins that connect to the SIM/smart card will withstand 14kV of human body model ESD. In order to ensure proper ESD protection, careful board layout is required. The GND pin should be tied directly to a GND plane. The V CC capacitor should be located very close to the V CC pin and tied directly to the GND plane.64555fb74555fbInformation furnished by Linear Technology Corporation is believed to be accurate and reliable. However , no responsibility is assumed for its use. Linear Technology Corporation makes no representa-tion that the interconnection of its circuits as described herein will not infringe on existing patent rights.P ACKAGE DESCRIPTION UD Package16-Lead Plastic QFN (3mm × 3mm)(Reference LTC DWG # 05-08-1691)RECOMMENDED SOLDER PAD PITCH AND DIMENSIONSNOTE:1. DRAWING CONFORMS TO JEDEC PACKAGE OUTLINE MO-220 VARIATION (WEED-2)2. DRAWING NOT TO SCALE3. ALL DIMENSIONS ARE IN MILLIMETERS4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDEMOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE 5. EXPOSED PAD SHALL BE SOLDER PLATED6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGEBOTTOM VIEW—EXPOSED PAD s 45o CHAMFER84555fbLinear Technology Corporation1630 McCarthy Blvd., Milpitas, CA 95035-7417(408) 432-1900 ● FAX: (408) 434-0507 ● www.linear .com© LINEAR TECHNOLOGY CORPORA TION 2001LT 0109 REV B • PRINTED IN USAR ELATED PARTS PART NUMBER DESCRIPTIONCOMMENTSL TC151450mA, 650kHz, Step-Up/Down Charge Pump withLow-Battery ComparatorV IN = 2.7V to 10V , V OUT = 3V/5V , I Q = 60μA, I SD = 10μA, S8 Package L TC151550mA, 650kHz, Step-Up/Down Charge Pump with Power-On ResetV IN = 2.7V to 10V , V OUT = 3.3V or 5V , I Q = 60μA, I SD < 1μA, S8 PackageL TC1555/L TC1556650kHz,SIM Power Supply and Level T ranslator for 3V/5V SIM CardsV IN = 2.7V to 10V , V OUT = 3V/5V , I Q = 60μA, I SD < 1μA, SSOP-16, SSOP-20 PackagesL TC1555L 1MHz, SIM Power Supply and Level T ranslator for 3V/5V SIM CardsV IN = 2.6V to 6.6V , V OUT = 3V/5V , I Q = 40μA, I SD < 1μA, SSOP-16 PackageL TC1555L-1.81MHz, SIM Power Supply and Level T ranslator for 1.8V/3V/5V SIM CardsV IN = 2.6V to 6.6V , V OUT = 1.8V/3V/5V , I Q = 32μA, I SD < 1μA,SSOP-16L TC1755/L TC1756Smart Card Interface with Serial Control for 3V/5V Smart Card Applications V IN = 2.7V to 7V , V OUT = 3V/5V , I Q = 60μA, I SD < 1μA,SSOP-16, SSOP-24L TC1955Dual Smart Card Interface with Serial Control for 1.8V/3V/5V Smart Card ApplicationsV IN = 3V to 6V , V OUT = 1.8V/3V , I Q = 200μA, I SD < 1μA, QFN-32 PackageL TC1986900kHz, SIM Power Supply for 3V/5V SIM Cards V IN = 2.6V to 4.4V , V OUT = 3V/5V , I Q = 14μA, I SD < 1μA, ThinSOT ™ PackageL TC3250-1.5250mA,1.5MHz, High Effi ciency Step-Down Charge Pump 85% Effi ciency, V IN = 3.1V to 5.5V , V OUT = 1.5V , I Q = 35μA, I SD < 1μA, ThinSOT PackageL TC3251500mA,1MHz to 16MHz, Spread Spectrum, Step-Down Charge Pump85% Effi ciency, V IN = 3.1V to 5.5V , V OUT = 0.9V to 1.6V , I Q = 9μA, I SD < 1μA, MS PackageThinSOT is a trademark of Linear Technology Corporation.。

LM2576中文资料

LM2576中文资料编辑:D z3w.C o m文章来源:网络我们无意侵犯您的权益,如有侵犯请[联系我们]L M2576中文资料L M2576外形图片L M2576/L M2576H V的特性:1)有3.3V、5V、12V、15V和可调电压输出多种系列;中2)输出电压可调范围1.23V-37V (H V型号的可达57V),负载电压的输出容差最大为±4%;3)最少只需要4个外围组件,可达3A的输出大电流应用电路4)较寛的输入电压范围,H V型号甚至可达40V~60V;5)内部振荡器产生52K H z固定频率;6)可用T T L电平关闭输出,低功耗待机模式,典型待机电流为50μA;7)B U C K式降压器,较高的转换效率;8)过热和过流保护;9)可实现B u c k-B o o s t式正-负电压转换器。

L M2576/L M2576H V引脚功能说明:1)V I N—输入电压端,为减小输入瞬间电压和给调节器提供开关电流,此接脚应接旁路电容C I N;2)O U T P U T—稳压输出端,输出高电压为(V I N-V S AT),输出低电压为-0.5V。

3)G N D—电路地;4)F E E D B A C K—反馈端;电子5)O N/O F F—控制端,高电平有效,待机静态电流仅为75μA图1L M2576内部方框电路图L M2576/L M2576H V外围组件的选择:1)输入电容C I N:要选择低E S R的铝或钽电容作为旁路电容,防止在输入端出现大的瞬间电压。

还有,当你的输入电压波动较大,输出电流有较高,容量一定要选用大些,470μF--10000μF都是可行的选择;电容的电流均方根值至少要为直流负载电流的1/2;基于安全考虑,电容的额定耐压值要为最大输入电压的1.5倍。

千万不要选用陶瓷电容,会造成严重的噪音干扰!N i c h i c o n的铝电解电容不错。

2)肖特基二极管:首选肖特基二极管,因为此类二极管开关速度快、正向压降低、反向恢复时间短,千万不要选用1N4000/1N5400之类的普通整流二极管!3)储能电感:可以看d a t a s h e e t中的电感选择曲线,要求有高的通流量和对应的电感值,也就是说,电感的直流通流量直接影响输出电流。

LMV652MM中文资料

45

50

60

mV from

95

110

rail

125

RL = 10 kΩ to V+/2

60

65

75

ISC

Maximum Continuous Output

Sourcing (Note 8)

Current

Sinking (Note 8)

17 mA

25

IS

Supply Current per Amplifier

76

dB

0.3 ≤ VO ≤ 2.7, RL = 10 kΩ to V+/2

86

93

0.4 ≤ VO ≤ 2.6, RL = 10 kΩ to V+/2

83

VO

Output Swing High

RL = 2 kΩ to V+/2

80

95

120

Output Swing Low

RL = 10 kΩ to V+/2 RL = 2 kΩ to V+/2

f = 100 kHz f = 1 kHz f = 1 kHz, AV = 2, RL = 2 kΩ

Min (Note 5)

Typ (Note 4)

0.1 0.15 0.003

Max (Note 5)

Units

pA/ %

5V DC Electrical Characteristics

Unless otherwise specified, all limits are guaranteed for TJ = 25°C, V+ = 5V, V− = 0V,VO = VCM = V+/2, and RL > 1 MΩ. Boldface limits apply at the temperature extremes.

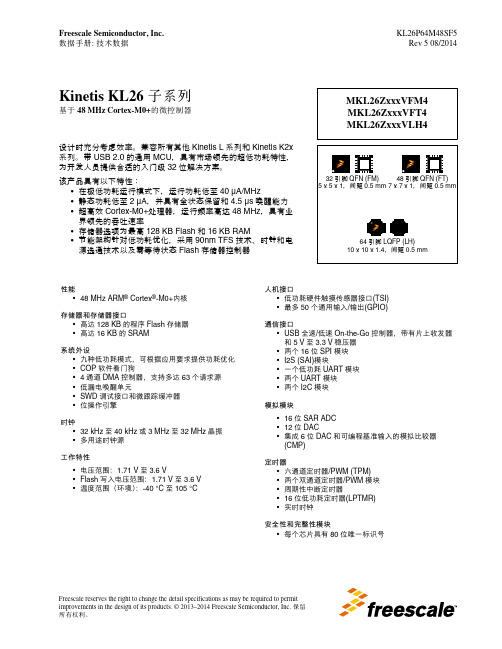

KL26P64M48SF5 中文资料

定时器 • 六通道定时器/PWM (TPM) • 两个双通道定时器/PWM 模块 • 周期性中断定时器 • 16 位低功耗定时器(LPTMR) • 实时时钟

安全性和完整性模块 • 每个芯片具有 80 位唯一标识号

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. © 2013–2014 Freescale Semiconductor, Inc. 保留

所有权利。

器件型号

MKL26Z32VFM4 MKL26Z64VFM4 MKL26Z128VFM4 MKL26Z32VFT4 MKL26Z64VFT4 MKL26Z128VFT4 MKL26Z32VLH4 MKL26Z64VLH4 MKL26Z128VLH4

Flash (KB) 32 64 128 32 64 128 32 64 128

• 在极低功耗运行模式下,运行功耗低至 40 μA/MHz • 静态功耗低至 2 μA,并具有全状态保留和 4.5 μs 唤醒能力 • 超高效 Cortex-M0+处理器,运行频率高达 48 MHz,具有业

界领先的吞吐速率 • 存储器选项为最高 128 KB Flash 和 16 KB RAM • 节能架构针对低功耗优化,采用 90nm TFS 技术、时钟和电

3 外设工作要求与特性......................................................................17 3.1 内核模块................................................................................. 17 3.1.1 SWD 电气特性 ......................................................... 17 3.2 系统模块................................................................................. 18 3.3 时钟模块................................................................................. 18 3.3.1 MCG 特性.................................................................. 18 3.3.2 振荡器电气规格........................................................ 20 3.4 存储器和存储器接口............................................................. 22 3.4.1 Flash 电气规格...........................................................22 3.5 安全性和完整性模块............................................................. 23 3.6 模拟......................................................................................... 24 3.6.1 ADC 电气规格...........................................................24 3.6.2 CMP 和 6 位 DAC 的电气规格................................ 28

ADS8556中文资料

16-, 14-, 12-Bit, 6通道同步采样模数转换器ADS8556/7/8系列包括6个16-, 14-和12-bit模数转换器(ADCs),各自基于连续逼近寄存器原理。

构架是基于充电分配原理,具有一个采样保持功能。

6个模拟输入组成3个通道组。

这些通道组可以并行采样,保留了信号的相对相位信息。

独立的转换开始信号可以控制每个通道的转换,可以是4个通道或者是6个通道一起转换。

器件支持单端,差分模拟输入信号,范围可以是±4VREF或者±2VREF ,最大输入电压可以达到±12V。

器件提供了一个内部的2.5V/3V参考电压源,配合一个10-bit的DA转换器,可以提供2.44mV或2.93mV的步进调整电压。

ADS8556/7/8同样提供一个可选择的并行或串行接口,可以用在硬件模式或软件模式中模拟部分本节讲述模拟输入电路,ADC以及控制信号,以及器件的参考设计模拟输入输入和转换器可以是单端或差分类型,绝对电压范围可以通过使用RANGE引脚进行配置(硬件模式)或控制寄存器(CR)中的RANGE_x位设置为±4V REF或±2V REF。

当使用的参考电压为2.5V时(CR bit C18 = 0),输入电压范围可以是±10V或±5V;当使用的参考电压为3V (CR bit C18 = 1),输入电压范围可以是±12V或±6V。

RANGE引脚在BUSY(如果CR bit C20 = 0)的下降沿锁存。

模拟输入端的输入电流取决于采样率,输入电压和信号的源阻抗。

实质上,模拟输入端的电流仅在采样周期(t ACQ)为内部的电容阵列进行充电。

在最大速率下(280ns),模拟输入电压的源必须能够为10pF的输入电容(±4V REF)或20pF(±2V REF)的输入电容充电。

在转换周期中,没有输入电流,输入阻抗大于1MΩ。

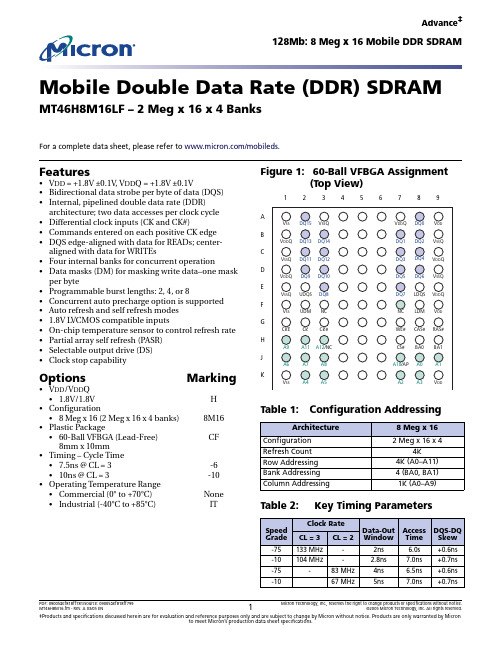

MT46H8M16LF中文资料

128Mb: 8 Meg x 16 Mobile DDR SDRAMAdvance ‡PDF: 09005aef818ff781/Source: 09005aef818ff799Micron Technology, Inc., reserves the right to change products or specifications without notice.MT46H8M16.fm -Rev. A 03/05 EN©2005 Micron Technology, Inc. All rights reserved.Mobile Double Data Rate (DDR) SDRAMMT46H8M16LF – 2 Meg x 16 x 4 BanksFor a complete data sheet, please refer to /mobileds .Features•V DD = +1.8V ±0.1V , V DD Q = +1.8V ±0.1V•Bidirectional data strobe per byte of data (DQS)•Internal, pipelined double data rate (DDR) architecture; two data accesses per clock cycle •Differential clock inputs (CK and CK#)•Commands entered on each positive CK edge •DQS edge-aligned with data for READs; center-aligned with data for WRITEs•Four internal banks for concurrent operation•Data masks (DM) for masking write data–one mask per byte•Programmable burst lengths: 2, 4, or 8•Concurrent auto precharge option is supported •Auto refresh and self refresh modes • 1.8V LVCMOS compatible inputs•On-chip temperature sensor to control refresh rate •Partial array self refresh (PASR)•Selectable output drive (DS)•Clock stop capabilityOptionsMarking•V DD /V DD Q • 1.8V/1.8V H •Configuration•8 Meg x 16 (2 Meg x 16 x 4 banks)8M16•PlasticPackage•60-Ball VFBGA (Lead-Free)8mm x 10mm CF •Timing – Cycle Time •7.5ns @ CL = 3•10ns @ CL = 3-6-10•Operating Temperature Range •Commercial (0° to +70°C)•Industrial (-40°C to +85°C)None ITFigure 1: 60-Ball VFBGA Assignment(Top View)Table 1: Configuration AddressingArchitecture8 Meg x 16Configuration 2 Meg x 16 x 4Refresh Count 4KRow Addressing 4K (A0–A11)Bank Addressing 4 (BA0, BA1)Column Addressing1K (A0–A9)Table 2:Key Timing ParametersSpeed GradeClock RateData-Out Window Access Time DQS-DQ SkewCL = 3CL = 2-75133 MHz -2ns 6.0s +0.6ns -10104 MHz- 2.8ns 7.0ns +0.7ns -75-83 MHz 4ns 6.5ns +0.6ns -1067 MHz 5ns 7.0ns +0.7ns元器件交易网元器件交易网Advance128Mb: 8 Meg x 16 Mobile DDR SDRAM®8000 S. Federal Way, P.O. Box 6, Boise, ID 83707-0006, Tel: 208-368-3900prodmktg@ Customer Comment Line: 800-932-4992Micron, the M logo, and the Micron logo are trademarks of Micron Technology, Inc.All other trademarks are the property of their respective owners.Advance: This data sheet contains initial descriptions of products still under development.元器件交易网Advance128Mb: 8 Meg x 16 Mobile DDR SDRAMRevision History•Original Document, Advance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .03/05。

L4946资料

Min. 50

50

VS = 10.5V to 26V

Check output for AC noise using A weighted filter (2020KHz)

VS = 7V to 26V

IO4 = 0.5 to 100mA

VS = 14V; IO4 = 2mA; VS = 14V; IO4 = 100mA;

IO4 = 100mA Tamb = 25°C all temps

VO4 = 0V

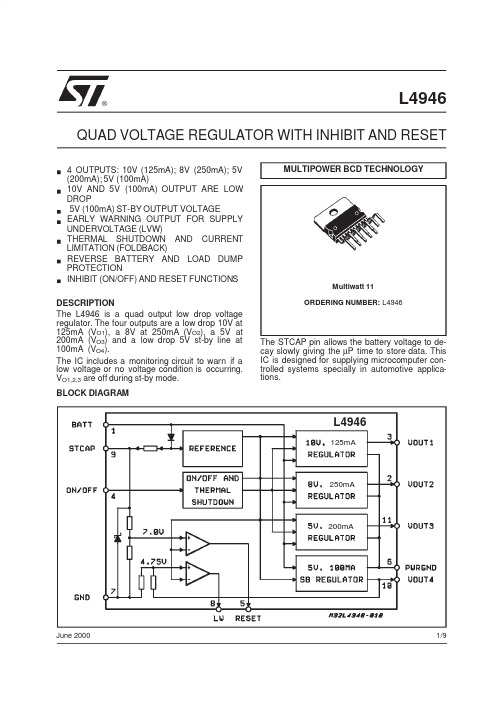

L4946

125mA

250mA

200mA

June 2000

1/9

元器件交易网

L4946

OPERATING CONDITION

Symbol VS IL

Supply Voltage

Load Current IO1 IO2 IO3 IO4

ABSOLUTE MAXIMUM RATINGS

元器件交易网

®

L4946

QUAD VOLTAGE REGULATOR WITH INHIBIT AND RESET

4 OUTPUTS: 10V (125mA); 8V (250mA); 5V (200mA); 5V (100mA) 10V AND 5V (100mA) OUTPUT ARE LOW DROP 5V (100mA) ST-BY OUTPUT VOLTAGE EARLY WARNING OUTPUT FOR SUPPLY UNDERVOLTAGE (LVW) THERMAL SHUTDOWN AND CURRENT LIMITATION (FOLDBACK) REVERSE BATTERY AND LOAD DUMP PROTECTION INHIBIT (ON/OFF) AND RESET FUNCTIONS

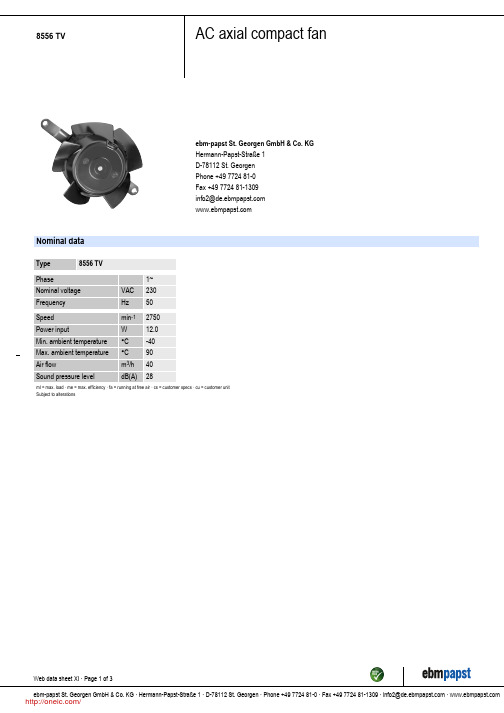

8556TV;中文规格书,Datasheet资料

Web data sheet XI · Page 2 of 3 ebm-papst St. Georgen GmbH & Co. KG · Hermann-Papst-Straße 1 · D-78112 St. Georgen · Phone +49 7724 81-0 · Fax +49 7724 81-1309 · info2@ ·

Nominal data

Type Phase Nominal voltage Frequency Speed Power input Min. ambient temperature Max. ambient temperature Air flow Sound pressure level VAC Hz min-1 W °C °C m3/h dB(A) 8556 TV 1~ 230 50 2750 12.0 -40 90 40 28

/

8556 TV

AC axial compact fan

Technical features

General description AC voltage fan with external rotor shaded-pole motor. Protected from overload by impedance protection. Impeller and mounting bracket made of metal. Air exhaust over mounting bracket. Rotational direction clockwise looking at rotor. Electrical connection to 2 single strands. Strand ends bared and tin-plated. Mass 370 g. Please note our new ACmaxx series. With identical fastening dimensions and voltages, this series achieves higher energy efficiency. 0.370 kg 76 Ø x 37 mm Metal Air exhaust over mounting bracket Right, looking at rotor Ball bearings 52500 h 15000 h 2 single strands AWG 18 Protected from overload using impedance protection VDE, CSA, UL, CE

LM7815中文资料

0˚C ≤ TJ ≤ 125˚C unless otherwise noted.

Output Voltage

Input Voltage (unless otherwise noted)

Symbol

Parameter

Conditions

Short-Circuit Current

Tj = 25˚C

Peak Output Current

VO

Output Voltage

Tj = 25˚C, 5 mA ≤ IO ≤ 1A

4.8 5 5.2 11.5 12 12.5 14.4 15 15.6

PD ≤ 15W, 5 mA ≤ IO ≤ 1A

4.75

5.25 11.4

12.6 14.25

15.75

VMIN ≤ VIN ≤ VMAX

(7.5 ≤ VIN ≤ 20)

Storage Temperature Range Lead Temperature (Soldering, 10 sec.)

TO-3 Package K TO-220 Package T

150˚C 150˚C −65˚C to +150˚C

300˚C 230˚C

Electrical Characteristics LM78XXC (Note 2)

0˚C ≤ TJ ≤ 125˚C unless otherwise noted.

Output Voltage

5V

12V

15V

Input Voltage (unless otherwise noted)

10V

19V

23V

Symbol

Parameter

Conditions

LP8551TLXNOPB;LP8551TLENOPB;中文规格书,Datasheet资料

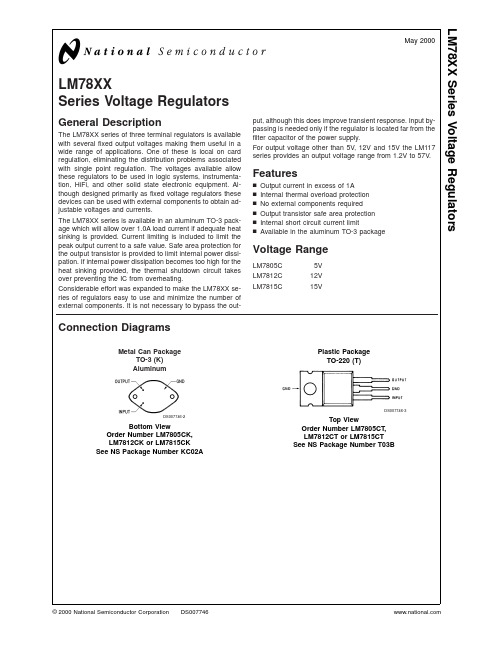

LP8551LP8551 PRODUCT BRIEF High-Efficiency LED Backlight Driver for NotebooksLiterature Number: SNVS673ALP8551 PRODUCT BRIEFHigh-Efficiency LED Backlight Driver for NotebooksGeneral DescriptionThe LP8551 is a white LED driver with integrated boost con-verter. It has four adjustable current sinks which can be controlled by PWM input or with I2C-compatible serial inter-face.The boost converter has adaptive output voltage control based on the LED driver voltages. This feature minimizes the power consumption by adjusting the voltage to lowest suffi-cient level in all conditions.LED outputs have 8-bit current resolution and up to 13-bit PWM resolution to achieve smooth and precise brightness control. Proprietary Phase Shift PWM control is used for LED outputs to reduce peak current from the boost converter, thus making the boost capacitors smaller. The Phase Shifting scheme also eliminates audible noise.Internal EEPROM is used for storing the configuration data. This makes it possible to have minimum external component count and make the solution very small.LP8551 has safety features which make it possible to detect LED outputs with open or short fault. As well low input voltage and boost over-current conditions are monitored and chip is turned off in case of these events. Thermal de-rating function prevents overheating of the device by reducing backlight brightness when set temperature has been reached.LP8551 is available in National's micro SMD-25 package. NOTICE: This document is not a full datasheet. For more information regarding this product or to order samples, please contact your local National Semiconductor sales office or visit /support/dir.html.Features■High-voltage DC/DC boost converter with integrated FET with four switching frequency options: 156/312/625/1250 kHz■ 2.7V – 22V input voltage range to support 1x…5x cell Li-Ion batteries■Programmable PWM resolution 8 to 13 bits■I2C and PWM brightness control■PWM output frequency and LED current set through resistors■ 4 LED outputs with LED fault (short/open) detection■Low input voltage, over-temperature, over-current detection and shutdown■Minimum number of external components■Micro SMD-25 package, 2.466 x 2.466 x 0.6 mm Applications■Notebook and Netbook LCD Display LED Backlight■LED LightingTypical Application (1)30121270© 2010 National Semiconductor 551 PRODUCT BRIEFTypical Application for Low Input Voltage (2)30121271 2L P 8551 P R O D U C T51 PRODUCT BRIEFL P 8551 P R O D U C T BFor more National Semiconductor product information and proven design tools, visit the following Web sites at:ProductsDesign SupportAmplifiers /amplifiers WEBENCH® Tools /webench Audio/audio App Notes /appnotes Clock and Timing /timing Reference Designs /refdesigns Data Converters /adc Samples /samples Interface /interface Eval Boards /evalboards LVDS/lvds Packaging /packaging Power Management /power Green Compliance /quality/green Switching Regulators /switchers Distributors/contacts LDOs /ldo Quality and Reliability /quality LED Lighting /led Feedback/Support /feedback Voltage References /vref Design Made Easy/easy PowerWise® Solutions /powerwiseApplications & Markets /solutions Serial Digital Interface (SDI)/sdiMil/Aero/milaero Temperature Sensors /tempsensors SolarMagic™/solarmagic PLL/VCO/wirelessPowerWise® Design University/trainingTHE CONTENTS OF THIS DOCUMENT ARE PROVIDED IN CONNECTION WITH NATIONAL SEMICONDUCTOR CORPORATION (“NATIONAL”) PRODUCTS. NATIONAL MAKES NO REPRESENTATIONS OR WARRANTIES WITH RESPECT TO THE ACCURACY OR COM PLETENESS OF THE CONTENTS OF THIS PUBLICATION AND RESERVES THE RIGHT TO M AKE CHANGES TO SPECIFICATIONS AND PRODUCT DESCRIPTIONS AT ANY TIM E WITHOUT NOTICE. NO LICENSE, WHETHER EXPRESS,IM PLIED, ARISING BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT.TESTING AND OTHER QUALITY CONTROLS ARE USED TO THE EXTENT NATIONAL DEEM S NECESSARY TO SUPPORT NATIONAL’S PRODUCT WARRANTY. EXCEPT WHERE M ANDATED BY GOVERNM ENT REQUIREM ENTS, TESTING OF ALL PARAM ETERS OF EACH PRODUCT IS NOT NECESSARILY PERFORM ED. NATIONAL ASSUM ES NO LIABILITY FOR APPLICATIONS ASSISTANCE OR BUYER PRODUCT DESIGN. BUYERS ARE RESPONSIBLE FOR THEIR PRODUCTS AND APPLICATIONS USING NATIONAL COM PONENTS. PRIOR TO USING OR DISTRIBUTING ANY PRODUCTS THAT INCLUDE NATIONAL COMPONENTS, BUYERS SHOULD PROVIDE ADEQUATE DESIGN, TESTING AND OPERATING SAFEGUARDS.EXCEPT AS PROVIDED IN NATIONAL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, NATIONAL ASSUMES NO LIABILITY WHATSOEVER, AND NATIONAL DISCLAIM S ANY EXPRESS OR IM PLIED WARRANTY RELATING TO THE SALE AND/OR USE OF NATIONAL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, M ERCHANTABILITY, OR INFRINGEM ENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.LIFE SUPPORT POLICYNATIONAL’S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEV ICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROV AL OF THE CHIEF EXECUTIV E OFFICER AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.National Semiconductor and the National Semiconductor logo are registered trademarks of National Semiconductor Corporation. All other brand or product names may be trademarks or registered trademarks of their respective holders.Copyright© 2010 National Semiconductor CorporationFor the most current product information visit us at National Semiconductor Americas Technical Support CenterEmail: support@ Tel: 1-800-272-9959National Semiconductor Europe Technical Support CenterEmail: europe.support@National Semiconductor Asia Pacific Technical Support Center Email: ap.support@National Semiconductor Japan Technical Support Center Email: jpn.feedback@IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improveme and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products a sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work rig or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rma published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanie by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptiv business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids a express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasona be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their product and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may b provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely a the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such us TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAudio /audio Communications and Telecom /communications Amplifiers Computers and Peripherals /computersData Converters Consumer Electronics /consumer-appsDLP®Products Energy and Lighting /energyDSP Industrial /industrialClocks and Timers /clocks Medical /medicalInterface Security /securityLogic Space,Avionics and Defense /space-avionics-defense Power Mgmt Transportation and Automotive /automotive Microcontrollers Video and Imaging /videoRFID OMAP Mobile Processors /omapWireless Connectivity /wirelessconnectivityTI E2E Community Home Page Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2011,Texas Instruments Incorporated分销商库存信息:NATIONAL-SEMICONDUCTORLP8551TLX/NOPB LP8551TLE/NOPB。

TLP3526中文资料

1.0

1.4

1.8

2.2

2.6

Pulse forward voltage VFP (V)

4

2002-09-25

元器件交易网

Trigger LED current IFT (arbitrary unit)

Peak off-state current IDRM (arbitrary unit)

元器件交易网

TL(Ta = 25°C)

Characteristic

Symbol

Rating

Unit

Forward current

Forward current derating (Ta ≥ 53°C)

LE D

Peak forward current (100µs pulse, 100pps)

Characteristic Trigger LED current Capacitance (input to output) Isolation resistance

Isolation voltage

Fig.1: dv / dt test circuit

Symbol IFT CS RS

BVS

Test Condition

VT = 6V VS = 0, f = 1MHz VS = 500V AC, 1 minute AC, 1 second, in oil DC, 1 minute, in oil

Min.

―

― 5×1010 2500

― ―

Typ.

―

1.5 1014 ― 5000 5000

Max. 10 ―

― ― ― ―

1 5 125 600 1.0 0.7 -14.3

DAC8516中文资料

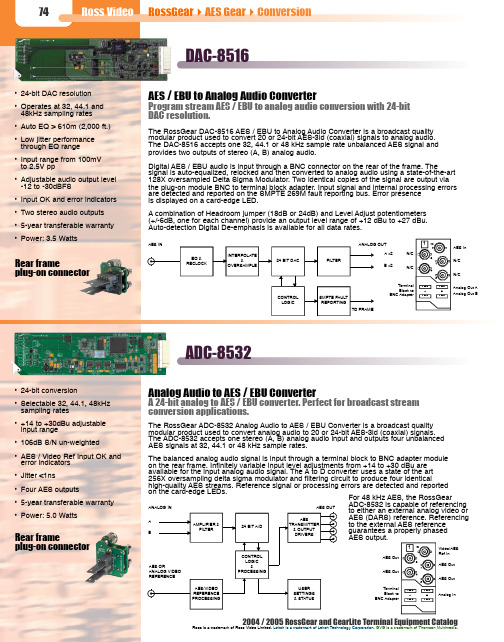

2004 / 2005 RossGear and GearLite Terminal Equipment Catalog

元器件交易网 Ross Video RossGearAES GearConversion 74

DAC-8516

• 24-bit DAC resolution • Operates at 32, 44.1 and 48kHz sampling rates • Auto EQ > 610m (2,000 ft.) • Low jitter performance through EQ range • Input range from 100mV to 2.5V pp • Adjustable audio output level -12 to -30dBFS • Input OK and error indicators • Two stereo audio outputs • 5-year transferable warranty • Power: 3.5 Watts

▼

CONTROL LOGIC SMPTE FAULT REPORTING TO FRAME

Terminal Block to BNC Adapter

-G+ A -G+

Analog Out A Analog Out B

ADC-8532

• 24-bit conversion • Selectable 32, 44.1, 48kHz sampling rates • +14 to +30dBu adjustable input range • 106dB S/N un-weighted • AES / Video Ref Input OK and error indicators • Jitter <1ns • Four AES outputs • 5-year transferable warranty • Power: 5.0 Watts

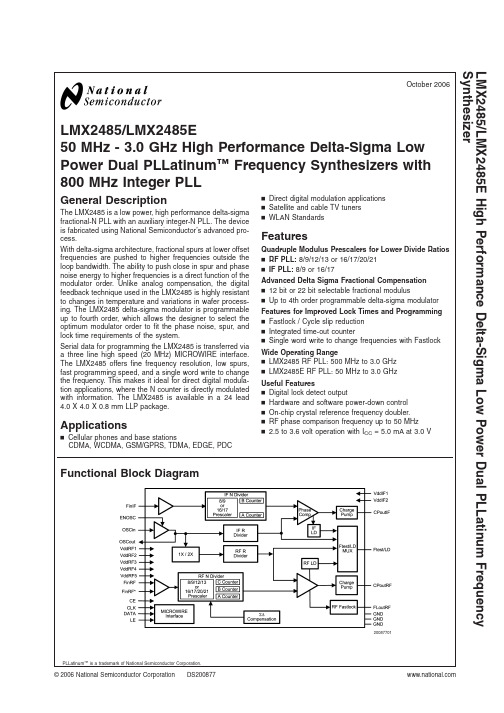

LMX2485ESQX资料

Value

Symbol

Min

Typ

VCC

2.5

3.0

TA

-40

25

Max 3.6 +85

Units

V ˚C

Note 1: “Absolute Maximum Ratings” indicate limits beyond which damage to the device may occur. "Recommended Operating Conditions" indicate conditions for which the device is intended to be functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. The voltage at all the power supply pins of VddRF1, VddRF2, VddRF3, VddRF4, VddRF5, VddIF1 and VddIF2 must be the same. VCC will be used to refer to the voltage at these pins and ICC will be used to refer to the sum of all currents through all these power pins.

LM4816MTX资料