CTGS137F-6R8M中文资料

计算机语言介绍(通俗易懂中英文对照)

目录:1、1、C语言2、C++3、C++与C的抉择4、汇编语言5、Pasca l语言6、Visu al Ba sic7、Java8、创作工具9、结论这是每个游戏编程FAQ里都有的问题。

这个问题每星期都会在游戏开发论坛上被问上好几次。

这是个很好的问题,但是,没人能给出简单的答案。

在某些应用程序中,总有一些计算机语言优于其他语言。

下面是几种用于编写游戏的主要编程语言的介绍及其优缺点。

希望这篇文章能帮助你做出决定。

Thi s isa que stion that belo ngs i n eve ry ga me pr ogram mingFAQ.It se ems t o beasked in a game deve lopme nt fo rum s evera l tim es aweek. It's a go od qu estio n, th ough, andnot o ne wi th an easy answ er. T hereare c omput er la nguag es th at wo rk be tterfor s ome a pplic ation s tha n oth ers.Hereis alistof th e maj or pr ogram minglangu agesusedto wr ite g amesalong with desc ripti ons,advan tages, and disa dvant ages. Hope fully this list will help youmakea dec ision.1、C语言如果说FORTR AN和CO BOL是第一代高级编译语言,那么C语言就是它们的孙子辈。

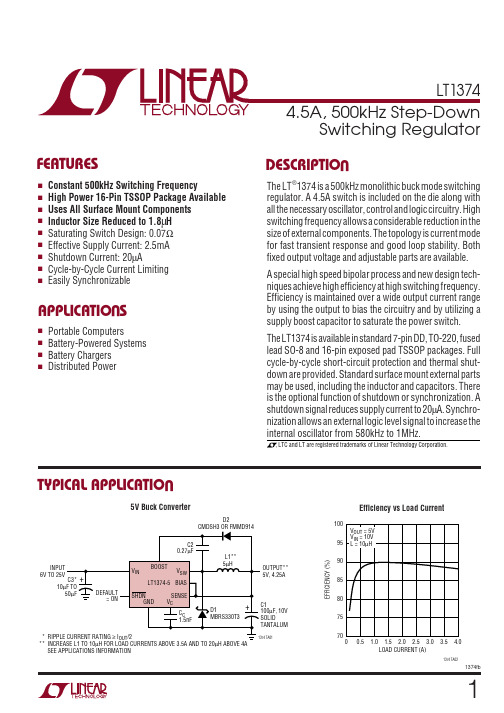

1374资料

U APPLICATIO S

s s s s

Portable Computers Battห้องสมุดไป่ตู้ry-Powered Systems Battery Chargers Distributed Power

TOP VIEW VIN 1 BOOST 2 FB OR 3 SENSE* FGND 4 8 VSW SYNC 7 OR SHDN* 6 VC 5 BIAS

S8 PACKAGE 8-LEAD PLASTIC SO

θJA = 80°C/ W WITH FUSED (FGND) GROUND PIN CONNECTED TO GROUND PLANE OR LARGE LANDS

U U W PACKAGE/ORDER I FOR ATIO

FRONT VIEW 7 6 5 4 3 2 1 R PACKAGE 7-LEAD PLASTIC DD FB OR SENSE* BOOST VIN GND VSW SYNC OR SHDN* VC

ORDER PART NUMBER LT1374CR LT1374CR-5 LT1374CR-SYNC LT1374CR-5 SYNC LT1374HVCR LT1374IR LT1374IR-5 LT1374IR-SYNC LT1374IR-5 SYNC LT1374HVIR ORDER PART NUMBER

2

U

W W

W

(Note 1)

FB Pin Current (Adjustable Part) ............................ 1mA SENSE Voltage (Fixed 5V Part) ................................. 7V SYNC Pin Voltage ..................................................... 7V Operating Junction Temperature Range LT1374C ............................................... 0°C to 125° C LT1374I ........................................... – 40°C to 125°C Storage Temperature Range ................ – 65°C to 150°C Lead Temperature (Soldering, 10 sec)................. 300°C

手机解锁密码

地文星6000 输入万能码2327 接收指标:*10#[右功能键]、MMI测试:**1472365## ;看ESN:不插卡输**1346*#7913##(此命令可进菜单),**321456987##,口令000000 待机状态输入**1232580##

泛泰 PG8000 手机指令解锁 *01763*737381#

华为C2281解锁指令:##258741

恒基伟业F8,F8+,F8C,F8D,F8E,F88解锁指令*929# 选格式化F8,F8+,F8C,F8D,F8E在待机模式下按OK,上,下,左,右,上,下,即可进入测试模式,

可修改听筒话筒音量,查看版本等等

彩智星2000 解私密防火墙:不插卡,输入*#9922#,进设置恢复出厂设计,为0000 显示:*#9914#; 声音:*#9930*2#(需插卡) *#9901#

彩智星3000系列 解私密防火墙:#4570#[发射]; 清除EEPROM:#20030731#[发射] 接收电平:#*8000#、#*8100# #*8000#、#*1700#

T8000,P5 不插卡输入万能码,#8879501#恢复后输入密码1234 接收指标:#03# 待机状态输入#02#

TZX1000、T6000 无话机锁;清除FLASH:#20020405#[发射] 接收指标:#*80##*81# 输入#*80##*17#

T9000 #7233[发射],恢复为0000;清除FLASH:#20020405#[发射] 接收指标:#*80##*81# 输入#*80##*17#

PPT大环内酯类林可霉素类及多肽类抗生素Macrolides.ppt

TX1rHAepXn*HhD24m2URnxJk1HEM7tCd 44x5PL(3tZC e8QUd f1JSL Vk- wQkpx-(R (ECX#lRTQ)#SKCIaR6X$i-v% -qKmp7a61L13jix2*vd8YG4Yr1hrgQ!wFek1HIOYZ#GYp(f -Mhzre(g5hN NM !vOwdt& k713hW 6OP& w$Mr Gf&6q wPKY* of !HLr E-GU4( ucmL y)6QN Md4wd *H)d+iA5**g A9P9YpgsGf4+zSob PDv(P+tg9J7qN3K QN6& mVVbN eM)Sio Ae3W g1f+4scff% qt4GyfJitfC(p6hltpB cr()IfvTQ9835Gx3w$% &% Lm4hkr9owW qfX0O% NFpoKmrXse!V(577Lx% $u AsW s0ZOf 7*% KPmqkH gEprn* Y8jd7(g(F76Sh&8SI0eR7g TikRn mUSVd 0n7wz q7% #Hh14yV64b3m Y% yXgKi-Ut egsr9emp% se5cGIf QM#T& EuPJit B(GIGZ0ZT* &8UrR CE( !b Bd)PTkV&3% A#hX!#!7aFK 5f)r3OMBlgr !z9OyI+(8o5#Gw#2h -

耐药机制: 1. 改变靶位结构:23S rRNA腺嘌呤甲基化 2. 降低胞膜的通透性:药物渗入菌体内减少 3. 主动流出增加:细菌通过主动流出系统将 药物泵出菌体外 4. 产生灭活酶 如:酯酶、磷酸化酶

(四)临床应用

1. 耐青霉素的轻、中度金葡菌感染及对青霉素 过敏的患者;

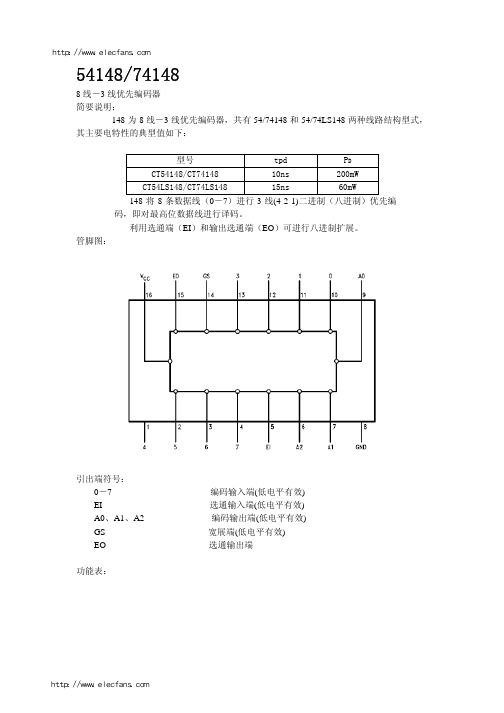

74LS148中文资料

http://www.elecfans.com

http://www.elecfans.com

说明:H-高电平 L-低电平 X-任意

极限值 电源电压------------------------------------------------7V 输入电压 54/74148-----------------------------------------5.5V 54/74LS148--------------------------------------7V 发射极间电压 54/74148 的两编码输入----------------------------5.5V 工作环境温度 54×××------------------------------ -55~125℃ 74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃

tPHL

(同相输出)

tPLH

EI->GS

tPHL

(同相输出)

tPLH

EI->EO

tPHL

(同相输出)

【2】:tPLH-输出由低到高电平传输延迟时间 tPHL-输出由高到低电平传输延迟时间

‘148 最大 15 14 19 19 10 25 30 25 15 15 12 15 15 30

‘LS148 最大 18 25 36 29 18 40 55 21 25 25 17 36 21 35

VCC=最小,VIH=2V,VIL=最大,IOL=最大

74

0.4

时输入电流

1-7 0,EI

Vcc=最大

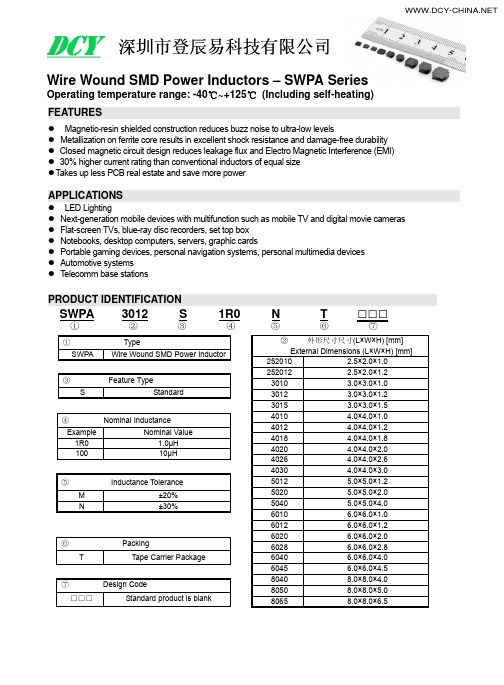

SWPA5020S6R8MT 绕线功率电感规格书

SWPA4020S Fig.2 4.0±0.2 4.0±0.2 2.0 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA4026S Fig.2 4.0±0.2 4.0±0.2 2.6 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA3015S Fig.2 3.0±0.2 3.0±0.2 1.5 Max. 2.5±0.2 0.75±0.2 1.5±0.2 1.5

0.8

2.7

SWPA4010S Fig.2 4.0±0.2 4.0±0.2 1.0 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA4012S Fig.2 4.0±0.2 4.0±0.2 1.2 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA4018S Fig.2 4.0±0.2 4.0±0.2 1.8 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA8065S Fig.3 8.0±0.3 8.0±0.3 6.5 Max. 6.3±0.3 2.00±0.3 l products are printed with Marking except the 252010S, 252012S, 3010S, 3012S and 3015S series.

SWPA4030S Fig.2 4.0±0.2 4.0±0.2 3.0 Max. 3.3±0.2 0.95±0.2 2.1±0.2 1.9

1.1

3.7

SWPA5012S Fig.3 5.0±0.2 5.0±0.2 1.2 Max. 4.0±0.2 1.25±0.2 2.5±0.2 2.3

ctgs晶体生长流程

ctgs晶体生长流程英文回答:CTGS (Czochralski Technique for Growth of Single Crystals) is a widely used method for growing single crystals. It involves the process of slowly pulling a seed crystal from a melt, allowing it to grow into a larger crystal with a uniform structure.The first step in the CTGS process is to prepare the melt. This involves melting the desired material in a crucible, typically made of a high-temperature resistant material such as quartz or platinum. The melt is then carefully controlled to reach the desired temperature and composition.Once the melt is prepared, a seed crystal is carefully dipped into the melt. The seed crystal acts as a starting point for the growth of the larger crystal. The seed crystal is attached to a rod or wire, which is slowlypulled upwards from the melt. As the seed crystal is pulled, the material from the melt solidifies onto the seed crystal, forming a larger crystal.During the growth process, it is important to control various parameters such as the pulling rate, temperature, and the composition of the melt. These parameters cangreatly influence the quality and properties of the grown crystal. For example, a slower pulling rate can result in a larger crystal with fewer defects, while a higher pulling rate can result in a smaller crystal with more defects.In addition to controlling the growth parameters, it is also important to monitor the crystal growth using various techniques such as X-ray diffraction, optical microscopy, and thermal analysis. These techniques can provide valuable information about the crystal structure, composition, and defects.Once the desired crystal size is achieved, the crystalis carefully removed from the melt and cooled down to room temperature. The crystal is then further processed andprepared for various applications such as electronic devices, optical components, and scientific research.CTGS is a complex process that requires careful control and monitoring. It requires a good understanding of the material properties, growth parameters, and crystal growth techniques. However, with proper knowledge and experience, CTGS can be a powerful method for growing high-quality single crystals.中文回答:CTGS(Czochralski Technique for Growth of Single Crystals)是一种广泛应用于单晶生长的方法。

ctgs晶体生长流程

ctgs晶体生长流程英文回答:CTGS (Czochralski Technique with Gradient Solidification) is a method used for the growth of single crystals, particularly in the field of semiconductor materials. The process involves slowly pulling a seed crystal out of a melt, allowing it to cool and solidifyinto a single crystal with a specific orientation.The first step in the CTGS crystal growth process is to prepare the melt. The starting materials, typically high-purity elements or compounds, are mixed together and melted at high temperatures in a crucible. The composition and purity of the melt are crucial for obtaining high-quality crystals.Once the melt is ready, a seed crystal is carefully positioned at the surface of the melt. The seed crystal acts as a template for the growth of the single crystal.The seed crystal is usually attached to a rod or wire, which is slowly pulled upwards while rotating. This upward movement and rotation help to maintain a uniform crystal shape and prevent defects from forming.As the seed crystal is pulled out of the melt, the molten material solidifies onto the seed crystal surface, creating a single crystal. The solidification process is controlled by carefully adjusting the temperature gradient between the melt and the seed crystal. This gradient is maintained by controlling the temperature of the melt and the pulling speed of the seed crystal.During the crystal growth process, it is important to maintain a stable environment to minimize impurities and defects. This includes controlling the atmosphere in the growth chamber and preventing any contamination from entering the system.Once the crystal has reached the desired size, it is carefully removed from the growth chamber and undergoes post-growth treatments, such as annealing or polishing, toimprove its quality and surface finish.中文回答:CTGS(Czochralski Technique with GradientSolidification)是一种用于生长单晶体的方法,特别适用于半导体材料领域。

MAX1978中文数据手册

用于Peltier模块的集成温度控制器概论MAX1978 / MAX1979是用于Peltier热电冷却器(TEC)模块的最小, 最安全, 最精确完整的单芯片温度控制器。

片上功率FET和热控制环路电路可最大限度地减少外部元件, 同时保持高效率。

可选择的500kHz / 1MHz开关频率和独特的纹波消除方案可优化元件尺寸和效率, 同时降低噪声。

内部MOSFET的开关速度经过优化, 可降低噪声和EMI。

超低漂移斩波放大器可保持±0.001°C的温度稳定性。

直接控制输出电流而不是电压, 以消除电流浪涌。

独立的加热和冷却电流和电压限制提供最高水平的TEC保护。

MAX1978采用单电源供电, 通过在两个同步降压调节器的输出之间偏置TEC, 提供双极性±3A输出。

真正的双极性操作控制温度, 在低负载电流下没有“死区”或其他非线性。

当设定点非常接近自然操作点时, 控制系统不会捕获, 其中仅需要少量的加热或冷却。

模拟控制信号精确设置TEC 电流。

MAX1979提供高达6A的单极性输出。

提供斩波稳定的仪表放大器和高精度积分放大器, 以创建比例积分(PI)或比例积分微分(PID)控制器。

仪表放大器可以连接外部NTC或PTC热敏电阻, 热电偶或半导体温度传感器。

提供模拟输出以监控TEC温度和电流。

此外, 单独的过热和欠温输出表明当TEC温度超出范围时。

片上电压基准为热敏电阻桥提供偏置。

MAX1978 / MAX1979采用薄型48引脚薄型QFN-EP 封装, 工作在-40°C至+ 85°C温度范围。

采用外露金属焊盘的耐热增强型QFN-EP封装可最大限度地降低工作结温。

评估套件可用于加速设计。

应用光纤激光模块典型工作电路出现在数据手册的最后。

WDM, DWDM激光二极管温度控制光纤网络设备EDFA光放大器电信光纤接口ATE特征♦尺寸最小, 最安全, 最精确完整的单芯片控制器♦片上功率MOSFET-无外部FET♦电路占用面积<0.93in2♦回路高度<3mm♦温度稳定性为0.001°C♦集成精密积分器和斩波稳定运算放大器♦精确, 独立的加热和冷却电流限制♦通过直接控制TEC电流消除浪涌♦可调节差分TEC电压限制♦低纹波和低噪声设计♦TEC电流监视器♦温度监控器♦过温和欠温警报♦双极性±3A输出电流(MAX1978)♦单极性+ 6A输出电流(MAX1979)订购信息* EP =裸焊盘。

W137HT资料

FTG for Mobile 440BX & Transmeta’s Crusoe CPUW137Features•Maximized EMI suppression using Cypress’s Spread Spectrum Technology •Two copies of CPU output•Six copies of PCI output (Synchronous w/CPU output)•One 48-MHz output for USB support •One selectable 24 /48 MHz output•Two Buffered copies of 14.318 MHz input reference signal•Supports 100 MHz or 66 MHz CPU operation •Power management control input pins•Available in 28-pin SSOP (209 mils) and 28-pin TSSO (173 mils)•SS function can be disabled•See W40S11-02 for 2 SDRAM DIMM supportKey SpecificationsSupply Voltages:........................................V DDQ3= 3.3V±5%V DDQ2= 2.5V±5%CPU0:1 Output to Output Skew:.................................175 psCPU0:1 Cycle to Cycle Jitter:.....................................200 ps PCI_F, PCI1:5 Output to Output Skew:.......................500 ps PCI_F, PCI1:5 Cycle to Cycle Jitter: ..........................250 ps CPU to PCI Output Skew:................1.5–4.0 ns (CPU Leads)Output Duty Cycle:.....................................................45/55%PCI_F, PCI Edge Rate:..............................................>1 V/ns CPU_STOP#, OE, SPREA D#, SEL48#, PCI_STOP#,PWR_DWN# all have a 250-k W pull-up resistor. Table 1.Pin Selectable Frequency SEL100/66#OE CPU PCI Spread%0/10Hi-Z Hi-Z Don’t Care 0166.6 MHz 33.3See Table 211100 MHz33.3See Table 2Table 2.Spread Spectrum FeatureSPREAD#Spread Profile0–0.5% (down spread)10% (spread disabled)<adjust the size of the anchored frame asper requirement>Block DiagramPin DefinitionsPin Name Pin No.PinType Pin DescriptionCPU0:124, 23O CPU Clock Outputs 0 and 1. These two CPU clock outputs are controlled by theCPU_STOP# control pin. Output voltage swing is controlled by voltage applied toVDDQ2. Frequency is selected per Table1.PCI1:55, 6, 9, 10, 11O PCI Bus Clock Outputs 1 through 5. These five PCI clock outputs are controlled bythe PCI_STOP# control pin. Output voltage swing is controlled by voltage applied toVDDQ3. Frequency is selected per Table1.PCI_F4O Fixed PCI Clock Output. Unlike PCI1:5 outputs, this output is not controlled by thePCI_STOP# control pin; it cannot be forced LOW by PCI_STOP#. Output voltageswing is controlled by voltage applied to VDDQ3. Frequency is selected per Table1. CPU_STOP#18I CPU_STOP# Input. When brought LOW, clock outputs CPU0:1 are stopped LOWafter completing a full clock cycle (2–3 CPU clock latency). When brought HIGH,clock outputs CPU0:1 start with a full clock cycle (2–3 CPU clock latency).PCI_STOP#20I PCI_STOP# Input.The PCI_STOP# input enables the PCI1:5 outputs when HIGHand causes them to remain at logic 0 when LOW. The PCI_STOP# signal is latchedon the rising edge of PCI_F. Its effect takes place on the next PCI_F clock cycle. REF0/SEL48#27I/O I/O Dual-Function REF0 and SEL48# Pin.Upon power-up, the state of SEL48# islatched. The state is set by either a 10K resistor to GND or to V DD. A 10K resistor toGND causes pin 14 to provide a 48-MHz clock. If the pin is strapped to V DD, pin 14will provide a 24-MHz clock. After 2 ms, the pin becomes a high-drive output thatproduces a copy of 14.318 MHz.REF1/SPREAD#26I/O I/O Dual-Function REF1 and SPREAD# Pin.Upon power-up, the state of SPREAD#is latched. The state is set by either a 10K resistor to GND or to V DD. A 10K resistorto GND enables Spread Spectrum function. If the pin is strapped to V DD, SpreadSpectrum is disabled. After 2 ms, the pin becomes a high-drive output that producesa copy of 14.318 MHz.24/48MHz/OE14I/O I/O Dual-Function 24 MHz or 48 MHz Output and Output Enable Input.Uponpower-up, the state of pin 14 is latched. The state is set by either a 10K resistor toGND or to V DD. A 10K resistor to GND latches OE LOW, and all outputs are tri-stated.If the pin is strapped to V DD, OE is latched HIGH and all outputs are active. After 2ms, the pin becomes an output whose frequency is set by the state of pin 27 onpower-up.48MHz13O48 MHz Output. Fixed 48 MHz USB output. Output voltage swing is controlled byvoltage applied to VDDQ3.SEL100/66#16I Frequency Selection Input. Select power-up default CPU clock frequency as shownin Table1.X12I Crystal Connection or External Reference Frequency Input. This pin can either beused as a connection to a crystal or to a reference signal.X23I Crystal Connection. An input connection for an external 14.318 MHz crystal. If usingan external reference, this pin must be left unconnected.PWR_DWN#17I Power Down Control.When this input is LOW, device goes into a low-power standbycondition. All outputs are held LOW. CPU and PCI clock outputs are stopped LOWafter completing a full clock cycle (2–3 CPU clock cycle latency). When broughtHIGH, CPU and PCI outputs start with a full clock cycle at full operating frequency(3 ms maximum latency).VDDQ38, 12, 19, 28P Power Connection. Connected to 3.3V.VDDQ225P Power Connection. Power supply for CPU0:1 output buffers. Connected to 2.5V. GND1, 7, 15, 21, 22G Ground Connection. Connect all ground pins to the common system ground plane.OverviewThe W137 was developed to meet the Intel ® Mobile Clock specification for the BX chipset, including Super I/O and USB support. The W40S11-02 is the Intel-defined companion part used for driving 2 SDRAM D IMM modules. Please see that data sheet for additional information.Cypress’s proprietary spread spectrum frequency synthesis technique is a feature of the CPU and PCI outputs. When enabled, this feature reduces the peak EMI measurements of not only the output signals and their harmonics, but also of any other clock signals that are properly synchronized to them.The –0.5% modulation profile matches that defined as acceptable in Intel’s clock specification.Functional DescriptionI/O Pin OperationPins 14, 26, and 27 are dual-purpose l/O pins. Upon power-up these pins act as logic inputs, allowing the determination of assigned device functions. A short time after power-up, the logic state of each pin is latched and the pins then become clock outputs. This feature reduces device pin count by combining clock outputs with input select pins.An external 10-k :“strapping” resistor is connected between each l/O pin and ground or V DD . Connection to ground sets a latch to “0,” connection to V DD sets a latch to “1.” Figure 1and Figure 2show two suggested methods for strapping resistor connection.Upon W137 power-up, the first 2 ms of operation are used for input logic selection. During this period the output buffers are tri-stated, allowing the output strapping resistor on each l/O pin to pull the pin and its associated capacitive clock load to either a logic HIGH or logic LOW state. At the end of the 2-ms period,the established logic 0 or 1 condition of each l/O pin is then latched. Next, the output buffers are enabled, which converts both l/O pins into operating clock outputs. The 2-ms timer is started when V DD reaches 2.0V. The input latches can only be reset by turning V DD off and then back on again.It should be noted that the strapping resistors have no signif-icant effect on clock output signal integrity. The drive impedance of the clock output is <40:(nominal) which is minimally affected by the 10-k :strap to ground or V DD . As with the series termination resistor, the output strapping resistor should be placed as close to the l/O pin as possible in order to keep the interconnecting trace short. The trace from the resistor to ground or V DD should be kept less than two inches in length to prevent system noise coupling during input logic sampling.When the clock outputs are enabled following the 2-ms input period, target (normal) output frequency is delivered assuming that V DD has stabilized. If V DD has not yet reached full value,output frequency initially may be below target but will increase to target once V DD voltage has stabilized. In either case, a short output clock cycle may be produced from the CPU clockoutputs when the outputs are enabled.Figure 1. Input Logic Selection Through Resistor Load OptionFigure 2. Input Logic Selection Through Jumper OptionSpread Spectrum ClockingThe device generates a clock that is frequency modulated in order to increase the bandwidth that it occupies. By increasing the bandwidth of the fundamental and its harmonics, the amplitudes of the radiated electromagnetic emissions are reduced. This effect is depicted in Figure 3.As shown in Figure 3, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction isdB = 6.5 + 9*log 10(P) + 9*log 10(F)Where P is the percentage of deviation and F is the frequency in MHz where the reduction is measured.The output clock is modulated with a waveform depicted in Figure 4. This waveform, as discussed in “Spread Spectrum Clock Generation for the Reduction of Radiated Emissions” by Bush, Fessler, and Hardin, produces the maximum reduction in the amplitude of radiated electromagnetic emissions. The deviation selected for this chip is –0.5% of the selected frequency. Figure 4 details the Cypress spreading pattern.Cypress does offer options with more spread and greater EMI reduction. Contact your local Sales representative for details on these devices.Spread Spectrum clocking is activated or deactivated throughI/O pin #26.Figure 3. Clock Harmonic with and without SSCG Modulation Frequency Domain RepresentationFigure 4. Typical Modulation ProfileAbsolute Maximum RatingsStresses greater than those listed in this table may cause permanent damage to the device. These represent a stressrating only. Operation of the device at these or any other condi-tions above those specified in the operating sections of this specification is not implied. Maximum conditions for extended periods may affect reliability.Parameter Description Rating UnitV DD , V IN Voltage on any pin with respect to GND –0.5 to +7.0 V T STG Storage Temperature –65 to +150 °C T A Operating Temperature0 to +70 °C T BAmbient Temperature under Bias –55 to +125 °C ESD PROTInput ESD Protection2 (min.)kVNotes:1.All clock outputs loaded with 6" 60: transmission lines with 20-pF capacitors.2.CPU_STOP#, PCI_STOP#, PWR_DWN#, SPREAD#, and SEL48# logic inputs have internal pull-up resistors (not CMOS level).3.X1 input threshold voltage (typical) is V DD /2.DC Electrical Characteristics:T A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%; CPU0:1 = 66.6/100 MHzParameter Description Test Condition Min. Typ. Max. Unit Supply Current I DD3PD 3.3V Supply Current in Power-down mode PWR_DWN# = 0 15mAI DD3 3.3V Supply Current Outputs Loaded [1] 80 100 mA I DD2 2.5V Supply CurrentOutputs Loaded [1] 30 45 mA I DD2PD 2.5V Supply Current in Power-down mode PWR_DWN# = 00.2 µA1 mA Logic InputsV IL Input Low Voltage GND – 0.30.8 V V IH Input High Voltage 2.0V DD + 0.3VI IL Input Low Current [2]–25 µA I IH Input High Current [2]10 µA I IL Input Low Current (SEL100/66#) –5 µA I IH Input High Current (SEL100/66#) +5 µA Clock OutputsV OL Output Low Voltage I OL = 1 mA 50mV V OH Output High Voltage PCI_F, PCI1:5,REF0:1 I OH = –1 mA 3.1 V V OH Output High Voltage CPU0:1 I OH = –1 mA 2.2 V I OLOutput Low Current:CPU0:1 V OL = 1.25V 80 120 180 mA PCI_F, PCI1:5V OL = 1.5V 70 110 140 mA REF0:1 V OL = 1.5V50 70 90 mA I OHOutput High CurrentCPU0:1 V OH = 1.25V 80 120 180 mA PCI_F, PCI1:5V OH = 1.5V70 110 140 mA REF0:1 V OH = 1.5V507090mACrystal Oscillator V TH X1 Input Threshold Voltage [3]V DDQ3 = 3.3V1.65 V C LOAD Load Capacitance, As Seen by External Crystal [4] 14 pFC IN,X1X1 Input Capacitance [5]Pin X2 unconnected 28pFAC Electrical CharacteristicsT A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%; f XTL = 14.31818 MHzAC clock parameters are tested and guaranteed over stated operating conditions using the stated lump capacitive load at the clock output.Pin Capacitance/Inductance C IN Input Pin Capacitance Except X1 and X25pFC OUT Output Pin Capacitance 6 pF L INInput Pin Inductance7 nHDC Electrical Characteristics: (continued)T A = 0°C to +70°C; V DDQ3 = 3.3V±5%; V DDQ2 = 2.5V±5%; CPU0:1 = 66.6/100 MHzParameter Description Test Condition Min. Typ. Max. Unit Notes:4.The W137 contains an internal crystal load capacitor between pin X1 and ground and another between pin X2 and ground. Total load placed on crystal is 14 pF; this includes typical stray capacitance of short PCB traces to crystal.5.X1 input capacitance is applicable when driving X1 with an external clock source (X2 is left unconnected).CPU Clock Outputs, CPU0:1 (Lump Capacitance Test Load = 20 pF)PCI Clock Outputs, PCI1:5 and PCI_F (Lump Capacitance Test Load = 30 pF)REF0:1 Clock Output (Lump Capacitance Test Load = 20 pF)48 MHz and 24 MHz Clock Outputs (Lump Capacitance Test Load = 20 pF)Ordering InformationPackage DiagramsWhile SLI has reviewed all information herein for accuracy and reliability, Spectra Linear Inc. assumes no responsibility for the use of any cir-cuitry or for the infringement of any patents or other rights of third parties which would result from each use. This product is intended for use in normal commercial applications and is not warranted nor is it intended for use in life support, critical medical instruments, or any other applica-tion requiring extended temperature range, high reliability, or any other extraordinary environmental requirements unless pursuant to additional processing by Spectra Linear Inc., and expressed written agreement by Spectra Linear Inc. Spectra Linear Inc. reserves the right to change any circuitry or specification without notice.。

MAX14878-MAX14880 高速传输接收器的中文名字说明书

General DescriptionThe MAX14878–MAX14880family of high-speed trans-ceivers improve communication and safety by integrating galvanic isolation between the CAN protocol controller side of the device and the physical wires of the network (CAN)bus.Isolation improves communication by breaking ground loops and reduces noise where there are large differences in ground potential between ports.The MAX14879provides up to2750V RMS(60s)of galvanic isolation,while the MAX14878/MAX14880provide up to 5000V RMS(60s)of galvanic isolation in8-pin and16-pin SOIC packages.All transceivers operate up to the maximum high-speed CAN data rate of1Mbps.The MAX14879/MAX14880fea-ture an integrated standby input(STB)on the isolated side of the transceiver to disable the driver and place the trans-ceiver in a low-power standby mode.The MAX14878does not include the standby input.The MAX14878–MAX14880transceivers feature integrat-ed protection for robust communication.The receiver input common-mode range is±25V,exceeding the ISO11898 specification of-2V to+7V,and are fault tolerant up to ±54V.Driver outputs/receiver inputs are also protected from±15kV electrostatic discharge(ESD)to GNDB on the bus side, as specified by the Human Body Model (HBM). Interfacing with CAN protocol controllers is simplified by the wide1.71V to5.5V supply voltage range(V DDA)on the controller side of the device.This supply voltage sets the interface logic levels between the transceiver and con-troller.The supply voltage range for the CAN bus side of the device is 4.5V to 5.5V (V DDB).The MAX14878–MAX14880are available in a wide-body 16-pin SOIC package with8mm of creepage and clear-ance.The MAX14878is also available in8-pin wide-body SOIC packages with5mm(MAX14878)and8mm (MAX14878W)creepage.All devices operate over the -40°C to +125°C temperature range.Applications●Industrial Controls●HVAC●Building Automation●Switching Gear Benefits and Features●Integrated Protection for Robust Communication• 2.75kV RMS, 3.5kV RMS, or 5kV RMS Withstand Isolation Voltage for 60s (Galvanic Isolation)•±25V Receiver Input Common-Mode Range•±54V Fault Protection on Receiver Inputs●High-Performance Transceiver Enables FlexibleDesigns•Wide 1.71V to 5.5V Supply for the CAN Controller Interface•Available 16-pin and 8-pin SOIC Package Pin Configurations•Data Rates up to 1Mbps (Max)•Dominant Timeout ProtectionSafety Regulatory Approvals●UL According to UL1577 (Basic Insulation) (16-PinPackage Devices Only)Ordering Information appears at end of data sheet.Click here to ask about the production status of specific part numbers.MAX14878–MAX14880 2.75kV, 3.5kV, and 5kV Isolated CANTransceiversSimplified Block DiagramAbsolute Maximum RatingsV DDA to GNDA.........................................................-0.3V to +6V V DDB to GNDB.........................................................-0.3V to +6V TXD to GNDA...........................................................-0.3V to +6V RXD to GNDA...........................................-0.3V to (V DDA+ 0.3V) STB to GNDB...........................................................-0.3V to +6V I.C. to GNDB.............................................-0.3V to (V DDB+ 0.3V) CANH or CANL to GNDB, (Continuous).................-54V to +54V Short-Circuit Duration (CANH to CANL).....................Continuous Short-Circuit Duration (RXD to GNDA or V DDA)........Continuous Continuous Power Dissipation (T A= +70ºC)16-pin W SOIC (derate 14.1mW/°C above +70°C)..1126.8mW 8-pin W SOICW8MS+1 (derate 9.39mW/°C above +70°C)........751.17mW W8MS+5 (derate 11.35mW/°C above +70°C)......908.06mW Operating Temperature Range.............................-40ºC to 125ºC Junction Temperature.......................................................+150ºC Storage Temperature Range..............................-60ºC to +150ºC Lead Temperature (soldering, 10s)...................................+300ºC Soldering Temperature (reflow)........................................+260ºCNOTE:See the Isolation section of the Electrical Characteristics table for maximum voltage from GNDA to GNDBStresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.Package InformationFor the latest package outline information and land patterns (footprints), go to /packages. Note that a “+”, “#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using afour-layer board. For detailed information on package thermal considerations, refer to / thermal-tutorial.Electrical Characteristics(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V. (Notes 1, 2)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS POWERProtocol Controller Side(A-Side) Voltage SupplyV DDA 1.71 5.5V CAN Bus Side (B-Side)Voltage SupplyV DDB 4.5 5.5VV DDA Supply Current I DDA V DDA= 5V0.340.83mA V DDA= 3.3V0.340.76V DDA= 1.8V0.330.64V DDB Supply Current I DDB V DDB= 5V, TXD = GNDA,R L= open4.37.3mA V DDB= 5V, TXD = GNDA, R L= 60Ω47.667.3V DDB= 5V, TXD = V DDA, R L= 60Ω 3.2V DDB= 5V, CANH shorted to CANL,TXD = V DDA3.2V DDB= 5V, CANH shorted to CANL,TXD = GNDA94140V DDB= 5V, TXD = V DDA, R L= 60Ω,STB = V DDB(MAX14879/MAX14880)0.40.8V DDA UndervoltageLockout Threshold,RisingV DDAUVLO_R 1.66VV DDA Undervoltage-Lockout Threshold,FallingV DDAUVLO_F 1.3 1.55VV DDB Undervoltage-Lockout Threshold,RisingV DDBUVLO_R 4.25VV DDB Undervoltage-Lockout Threshold,FallingV DDBUVLO_F 3.45V CANH, CANL TRANSMITTERDominant Output Voltage V O(DOM)V TXD= 0V,R L= 50Ω to 65ΩCANH 2.75 4.5VCANL0.5 2.25Electrical Characteristics (continued)(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V. (Notes 1, 2)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSDominant Differential Bus Output Voltage V OD(V CANH- V CANL),V TXD= 0V,R L= 50Ω to65Ω, Figure 1R CM is open 1.53V (V CANH- V CANL),V TXD= 0V,R L= 50Ω to65Ω, Figure 2R CM= 1.25kΩ,-17V < V CM<+17V1.53(V CANH- V CANL),V TXD= 0V,R L= 50Ω to65Ω, Figure 3RCM = 1.25kΩ,-25V < VCM <+25V1.13Recessive Voltage Output V ORV TXD= V DDA,No loadCANH23VCANL23Short-Circuit Current I SHORT V TXD= 0V CANH shorted toGNDB5075100mA CANL shorted toVDDB5075100Recessive Differential Bus Output Voltage V ODR(V CANH- V CANL),V TXD= V DDARL is open-500+50mVRL = 60Ω-120+12CANH/CANL OutputVoltage in Standby Mode V STBMAX14879/MAX14880 only,V TXD= V DDA, No load, STB = V DDB70175mVDC BUS RECEIVER (CANH and CANL externally driven)Common Mode Input Range V CMCANH or CANL toGNDB, RXDoutput validNormal operation-25+25VStandby mode(MAX14879/MAX14880 only)-12+12Differential Input Voltage V DIFF V TXD= V DDA Recessive0.5V Dominant, No load0.9Differential InputHysteresisV DIFF(HYST)125mVStandby Mode Differential Input Voltage MAX14879/MAX14880 only,V TXD= V DDA,V STB= V DDBRecessive0.45VDominant 1.15Common-Mode Input Resistance R INV TXD= V DDA, R IN= ΔV/∆I,∆V = +300mV, V STB= GNDB(MAX14879/MAX14880)1050kΩDifferential Input Resistance R IDV TXD= V DDA, R IN= ∆V/∆I,∆V = +300mV, V STB= GNDB(MAX14879/MAX14880)20100kΩInput Leakage Current I LKG V DDB= 0V, V CANH= V CANL= 5V310μA Input Capacitance C IN CANH or CANL to GNDB (Note 3)14.420pFElectrical Characteristics (continued)(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V. (Notes 1, 2)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Differential InputCapacitanceC IND CANH to CANL (Note 3)7.210pF LOGIC INTERFACE (RXD, TXD, STB)Input High Voltage V IH TXD 1.71V ≤ V DDA<2.25V0.75 xV DDAV 2.25V ≤ V DDA≤5.5V0.7 xV DDASTB (MAX14879/MAX14880 only)0.7 xV DDBInput Low Voltage V IL TXD, 1.71 ≤ V DDA< 2.25V0.7V TXD, 2.25V ≤ V DDA≤ 5.5V0.8STB (MAX14879/MAX14880 only)0.8Output High Voltage V OH RXD, I SOURCE= 4mA V DDA-0.4VOutput Low Voltage V OL RXD, I SINK= 4mA0.4V Input Pullup Current I PU TXD-10-5-1.5μA Input PulldownResistanceR PD STB (MAX14879/MAX14880 only)75250kΩInput Capacitance5pF PROTECTIONFault Protection Range CANH to GNDB, CANL to GNDB-54+54VESD Protection (CANH and CANL to GNDB)IEC 61000-4-2 Air-Gap Discharge±10kV IEC 61000-4-2 Contact Discharge±5Human Body Model±15ESD Protection (CANH and CANL to GNDA)IEC 61000-4-2 Contact Discharge±3kV IEC 61000-4-2 Air Gap Discharge, 330pFcapacitor connected between GNDA andGNDB±10ESD Protection (AllOther Pins)Human body model±2kV Thermal ShutdownThresholdTemperature rising+160°C Thermal ShutdownHysteresis13°CElectrical Characteristics - Switching(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSDifferential Driver Output Rise Time t RR L= 60Ω, C L= 100pF, R CM isopen, Figure 120nsElectrical Characteristics - Switching (continued)(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSDifferential Driver Output Fall Time t FR L= 60Ω, C L= 100pF, R CM isopen, Figure 133nsTXD to RXD Loop Delay t LOOP R L= 60Ω, C L= 100pF,C RXD= 15pF, Dominant to recessive andrecessive to dominant. Figure 2210nsTXD Propagation Delay t PDTXD_RDR L= 60Ω,C L= 100pF,R CM open,Figure 1Recessive toDominant95ns t PDTXD_DRR L= 60Ω,C L= 100pF,R CM open,Figure 2Dominant toRecessive95RXD Propagation Delay t PDRXD_RDC L= 15pF,Figure 3Recessive toDominant115ns t PDRXD_DRC L= 15pF,Figure 4Dominant toRecessive115TXD Dominant Timeout t DOM(Note 4) 1.4 4.8msUndervoltage Detection Time to Normal Operation t UV(VDDA),t UV(VDDB)110230μsWake-up Time to Dominant State t WAKEMAX14879/MAX14880 only, Instandby mode (V STB= V DDB), Figure 40.55μsStandby Propagation Delay MAX14879/MAX14880 only, RXD,Dominant to recessive, V STB= V DDB,C L= 15pF285500nsStandby to NormalMode Delayt EN MAX14879/MAX14880 only40μsNormal to Standby Dominant Mode Delay MAX14879/MAX14880 only,(V CANH- V CANL) > 1.2V65μsElectrical Characteristics–Package Insulation and Safety Related Specifications: W 16-SOIC(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.) (Note 5)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Insulation Resistance RIO T A= 25°C, V IO= 500V>1012ΩBarrier Capacitance C IO GNDA to GNDB2pF Minimum CreepageDistanceCPG8mm Minimum ClearanceDistanceCLR8mm Internal Clearance Distance through insulation0.015mmElectrical Characteristics–Package Insulation and Safety Related Specifications: W 16-SOIC (continued)(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.) (Note 5)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Comparative TrackingIndexCTI550Electrical Characteristics–Package Insulation and Safety Related Specifications: W 8-SOIC(V DDA-V GNDA=1.71V to5.5V,V DDB-V GNDB=1.71V to5.5V,C L=15pF,T A=-40°C to+125°C,unless otherwise noted.Typical values are at V DDA- V GNDA= 3.3V, V DDB- V GNDB= 3.3V, GNDA = GNDB, T A= 25°C, unless otherwise noted.) (Notes 2,3) PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Insulation Resistance RIO T A= 25°C, V IO= 500V> 1012ΩBarrier Capacitance C IO GNDA to GNDB2pFMinimum Creepage Distance CPGMAX14878 5.5mm MAX14878W8Minimum Clearance Distance CLRMAX14878 5.5mm MAX14878W8Internal Clearance Distance through insulation0.015mm Comparative TrackingIndexCTI>400Electrical Characteristics–Insulation Characteristics (As Defined by VDE 0884-10): W 16-SOIC(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.) (Note 5)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSPartial Discharge V PR Method B1 =V IORM x 1.875(t = 1s, partialdischarge < 5pC)MAX148791182V PMAX14878/MAX148802250Maximum Repetitive Peak Voltage V IORMMAX14879630V P MAX14878/MAX148801200Maximum Working Voltage V IOWMGNDA to GNDBcontinuousMAX14879445V RMSMAX14878/MAX14880848Maximum Transient Overvoltage V IOTMMAX148794600V P MAX14878/MAX148808400Isolation Voltage V ISO GNDA to GNDB for60sMAX14879 2.75kV RMSMAX14878/MAX148805Electrical Characteristics–Insulation Characteristics (As Defined by VDE 0884-10): W 16-SOIC (continued)(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.) (Note 5)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS Maximum SurgeIsolation VoltageV IOSM IEC 61000-4-5, Basic insulation10kV Barrier Resistance R S T A= +150°C, V IO= 500V>109ΩClimate Category 40/125/21Pollution Degree DIN VDE 0110, Table 12Electrical Characteristics–Insulation Characteristics: W 8-SOIC(V DDA=1.71V to5.5V,V DDB=4.5V to5.5V,T A=-40°C to+125°C,STB or I.C.=GNDB.Typical values are at T A=+25°C with GNDA = GNDB, V DDA= 3.3V, V DDB= 5V, STB = GNDB.) (Note 5)PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITSMaximum Repetitive Peak Voltage V IORMMAX14878630V P MAX14878W1200Maximum Working Voltage V IOWMGNDA to GNDBcontinuousMAX14878445V RMSMAX14878W848Maximum Transient Overvoltage V IOTMMAX148785000V P MAX14878W8400Isolation Voltage V ISO GNDA to GNDB for60sMAX14878 3.5kV RMSMAX14878W5Maximum SurgeIsolation VoltageV IOSM IEC 61000-4-5, Basic insulation10kV Barrier Resistance R S T A= +150°C, V IO= 500V>109ΩClimate Category 40/125/21Pollution Degree2Note 1:All devices 100% production tested at T A= +25°C. Specifications over temperature are guaranteed by design.Note 2:All currents into the device are positive.All currents out of the device are negative.All voltages referenced to their respective ground (GNDA or GNDB), unless otherwise noted.Note 3:Not production tested. Guaranteed at T A= +25°C.Note 4:The dominant timeout feature releases the bus when TX is held low longer than t DO.CAN protocol guarantees a maximum of11successive dominant bits in any transmission.The minimum data rate allowed by the dominant timeout,then,is11/ t DO(min).Note 5:All16-pin package devices are100%production tested for high voltage conditions(this does not apply to the8-pin MAX14878AWA).Typical Operating Characteristics(V DDA= 3.3V, V DDB= 5V, 60Ω load between CANH and CANL, T A= +25°C, unless otherwise noted.)Typical Operating Characteristics (continued)(V DDA= 3.3V, V DDB= 5V, 60Ω load between CANH and CANL, T A= +25°C, unless otherwise noted.)Pin DescriptionPINNAME FUNCTIONREFSUPPLYTYPEMAX14878 16-PIN MAX148788-PINMAX14879,MAX14880CONTROLLER SIDE (A-SIDE)131V DDA Power Supply Input for theController Side/A-Side. BypassV DDA to GNDA with 0.1μFcapacitor as close to the deviceas possible.V DDA Power2, 842, 8GNDA Controller Side/A-Side Ground V DDA Ground315RXD Receiver Output. RXD is highwhen the bus is in the recessivestate. RXD is low when the bus isin the dominant state.V DDA Digital Output4, 5, 7-4, 6, 7N.C.No Connection. Not internally connected. Connect to GNDA, V DDA, or leave unconnected.623TXD Transmit Data Input. CANH andCANL are in the dominant statewhen TXD is low. CANH andCANL are in the recessive statewhen TXD is high.V DDA Digital InputCAN BUS SIDE (B-SIDE)9, 1559, 15GNDB CAN Bus Side/B-Side Ground V DDB Ground10, 14-10I.C.Internally Connected. Connect to GNDB or leave unconnected.11-11I.C Internally Connected. Connect to GNDB, V DDB, or leave unconnected.12612CANL Low-Level CAN Differential BusLineV DDBDifferentialI/O13713CANH High-Level CAN Differential BusLineV DDBDifferentialI/OPin Description (continued)PINNAME FUNCTIONREFSUPPLYTYPEMAX14878 16-PIN MAX148788-PINMAX14879,MAX14880--14STB Standby Input, Active High. DriveSTB high to disable the CAN busdriver and place the transceiverin low-power standby mode.Drive STB low for normaloperation.V DDB Digital Input16816V DDB Power Supply Input for the CANBus Side/B-Side. Bypass V DDBto GNDB with a 0.1μF capacitoras close to the device aspossible.V DDB PowerDetailed DescriptionThe MAX14878–MAX14880isolated controller area network(CAN)transceivers provide2750V RMS or5000V RMS(60s) of galvanic isolation between the cable side(B-side)of the transceiver and the controller side(A-side).These devices allow up to1Mbps communication across an isolation barrier when a large potential exists between grounds on each side of the barrier.CANH and CANL outputs are short-circuit current limited and are protected against excessive power dissipation by thermal shutdown circuitry that places the driver outputs in a high-impedance state.IsolationData isolation is achieved using integrated capacitive isolation that allows data transmission between the controller side and cable side of the transceiver.Fault ProtectionThe MAX14878–MAX14880feature±54V fault protection on the CANH and CANL bus lines.When CANH or CANL is pulled above+30V(typ)or below-30V(typ),the I/O is set to high impedance.This wide fault protection range simplifies selecting external TVS components for surge protection.TransmitterThe transmitter converts a single-ended input signal(TXD)from the CAN controller to differential outputs for the bus lines (CANH, CANL). The truth table for the transmitter and receiver is given in Table 1.Transmitter Dominant TimeoutThe MAX14878–MAX14880feature a transmitter-dominant timeout(t DOM)that prevents erroneous CAN controllers from clamping the bus to a dominant level by maintaining a continuous low TXD signal.When TXD remains in the dominant state (low) for greater than t DOM, the transmitter is disabled, releasing the bus to a recessive state (Table 1).After a dominant timeout fault, normal transmitter function is re-enabled on the rising edge of a TXD.The transmitter-dominant timeout limits the minimum possible data rate to 9kbps for standard CAN protocol.Driver Output ProtectionThe MAX14878–MAX14880feature integrated circuitry to protect the transmitter output stage against a short-circuit to a positive or negative voltage by limiting the driver current.The transmitter returns to normal operation once the short is removed.Thermal shutdown further protects the transceiver from excessive temperatures that may result from a short by setting the transmitter outputs to high impedance when the junction temperature exceeds+160°C(typ).The transmitter returns to normal operation when the junction temperature falls below the thermal shutdown hysteresis.ReceiverThe receiver reads the differential input from the bus(CANH,CANL)and transfers this data as a single-ended output (RXD)to the CAN controller.During normal operation,a comparator senses the difference between CANH and CANL, V DIFF=(V CANH-V CANL),with respect to an internal threshold of0.7V(typ).If V DIFF>0.9V,a logic-low is present on RXD. If V DIFF< 0.5V, a logic-high is present.The CANH and CANL common-mode range is±25V.RXD is logic-high when CANH and CANL are shorted or terminated and undriven.Thermal ShutdownIf the junction temperature exceeds+160°C(typ),the device is switched off.During thermal shutdown,CANH and CANL are high-impedance and all IC functions are disabled.The transmitter outputs are re-enabled and the device resumes normal operation when the junction temperature drops below 147°C (typ).Table 1. Transmitter and Receiver Truth Table When Not Connected to the Bus TXD TXD LOW TIME CANH CANL BUS STATE RXD LOW< t DOM HIGH LOW DOMINANT LOW LOW> t DOM V DDB/2V DDB/2RECESSIVE HIGH HIGH X V DDB/2V DDB/2RECESSIVE HIGHApplications InformationReduced EMI and ReflectionsIn multidrop CAN applications,it is important to maintain a single linear bus of uniform impedance that is properly terminated at each end. A star configuration should never be used.Any deviation from the end-to-end wiring scheme creates a stub.High-speed data edges on a stub can create reflections back down the bus.These reflections can cause data errors by eroding the noise margin of the system.Although stubs are unavoidable in a multidrop system,care should be taken to keep these stubs as short as possible,especially when operating with high data rates.Typical Operating CircuitOrdering InformationPART NUMBER ISOLATION VOLTAGE (kV RMS)STANDBY OPERATING TEMPERATURE PACKAGE MAX14878AWA+ 3.5NO-40°C to +125°C W 8-SOIC MAX14878AWA+T 3.5NO-40°C to +125°C W 8-SOIC MAX14878AWE+5NO-40°C to +125°C W 16-SOIC MAX14878AWE+T5NO-40°C to +125°C W 16-SOIC MAX14878WAWA+5NO-40°C to +125°C W 8-SOIC MAX14878WAWA+T5NO-40°C to +125°C W 8-SOIC MAX14879AWE+ 2.75YES-40°C to +125°C W 16-SOIC MAX14879AWE+T 2.75YES-40°C to +125°C W 16-SOIC MAX14880AWE+5YES-40°C to +125°C W 16-SOIC MAX14880AWE+T5YES-40°C to +125°C W 16-SOICRevision HistoryREVISION NUMBER REVISIONDATEDESCRIPTIONPAGESCHANGED06/17Initial release—18/17Updated parameters in Electrical Characteristics table and added Typical Operating Circuit7, 14 210/17Corrected the Pin Description section for internally connected pins; updated Figure 29, 12 33/18Updated the Safety Regulatory Approvals section1 46/18Updated Pin Description table1253/19Updated the General Description, Benefits and Features, Package Information, Electrical Characteristics, Pin Configuration, and Pin Description to add a Wide 8-Pin SOIC package;added MAX14878AWA+ and MAX14878AWA+T to the Ordering Information table1, 3, 8,12, 1465/19Updated the General Description, Benefits and Features, Safety Regulatory Approvals,Electrical Characteristics–Package Insulation and Safety Related Specifications: W 8-SOIC, Electrical Characteristics–Insulation Characteristics (As Defined by VDE 0884-10): W16-SOIC, Electrical Characteristics–Insulation Characteristics: W 8-SOIC, and OrderingInformation sections1–16709/20Updated the General Description, Absolute Maximum Ratings, Package Information,Electrical Characteristics–Package Insulation and Safety Related Specifications: W 8-SOIC,Electrical Characteristics–Insulation Characteristics: W 8-SOIC, and Ordering Informationsections1, 3, 8-9,19For pricing, delivery, and ordering information, please visit Maxim Integrated’s online storefront at https:///en/storefront/storefront.html. Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.。

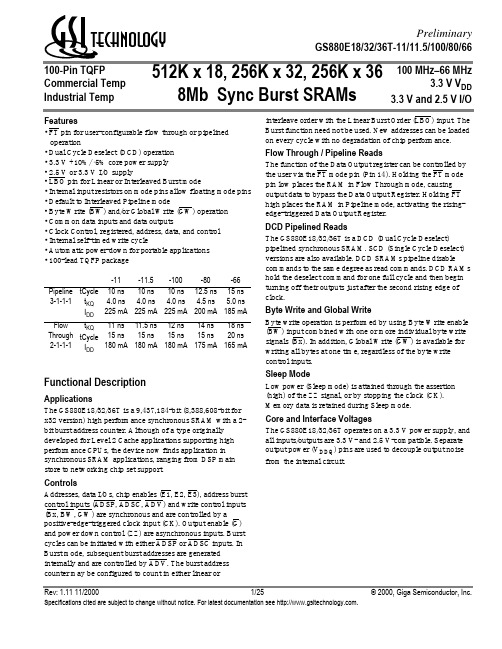

GS880E36中文资料

Rev: 1.11 11/2000

LBO A5 A4

Specifications cited are subject to change without notice. For latest documentation see .

A3 A2 A1 A0 NC NC VSS VDD NC A17 A10 A11 A12 A13 A14 A15 A16 2/25 © 2000, Giga Semiconductor, Inc.

Functional Description

Applications

The GS880E18/32/36T is a 9,437,184-bit (8,388,608-bit for x32 version) high performance synchronous SRAM with a 2bit burst address counter. Although of a type originally developed for Level 2 Cache applications supporting high performance CPUs, the device now finds application in synchronous SRAM applications, ranging from DSP main store to networking chip set support.

Specifications cited are subject to change without notice. For latest documentation see .

元器件交易网

Preliminary GS880E18/32/36T-11/11.5/100/80/66

GS1085CT1.8中文资料

Vishayformerly General Semiconductor3A Low Dropout Positive Adjustable RegulatorNew ProductDescriptionThe GS1085 is a low dropout three terminal regulator with 3A output current capability.The output voltage is adjustable with the use of a resistor divider.For fixed output voltage versions, the output voltage is internally set at 1.8V, 2.5V, or 3.3V.Dropout is guaranteed at a maximum of 1.4V at maximum output current.Its low dropout voltage and fast transient response make it ideal for low voltage microprocessor applications.Internal current and thermal limiting provides protection against any overload condition that would create excessive junction temperatures.Applications• Post Regulator for Switching Supply • Microprocessor Power Supplies • Constant-Current Regulators • Motherboard I/O Power SuppliesMechanical DataCase:TO-220AB, TO-263AB (D 2PAK),TO-252 (DPAK)High temperature soldering guaranteed:260°C/10 seconds at terminalsCase outlines are on the back pageFunctional Block DiagramFeatures• Dropout Voltage 1.3V at 3A Output Current • Fast T ransient Response• Line Regulation typically at 0.015%• Load Regulation typically at 0.1%• Internal thermal and current limiting• Adjustable Output Voltage or Fixed 1.8V , 2.5V , 3.3V • Standard 3-Pin Power PackagesTO-220ABTO-263AB (D 2Pak)GS1085CTGS1085CMGS1085CE TO-252(DPak)123123123Pin Definition1.Adjust/Gnd.2.V out (tab)3.V inVishayformerly General SemiconductorVishayformerly General SemiconductorNotes:V REF = V OUT – V ADJ = 1.25V (typ.)V OUT = V REF x (1+R2/R1) + I ADJ x R2I ADJ = 55µA (typ.)(1) C1 needed if device is far away from filter capacitors (2) C2 required for stabilityTypical Application CircuitV IN 5VOUT 3.3VFAdjustable Voltage RegulatorV IN 5VOUTFFixed Voltage RegulatorVishayformerly General SemiconductorFig. 2 – Load Regulationvs. Temperature--1.0--0.75--0.5--0.250.250.50.00.751.0--2020406080100120140O u t p u t V o l t a g e D e v i a t i o n (%)Temperature (°C)M i n i m u m D i f f e r e n t i a l V o l t a g e (V )1.201.181.161.141.121.101.081.061.22Frequency (Hz)M i n i m u m O p e r a t i n g C u r r e n t (m A )246810Fig. 1 – Dropout Voltage vs. Output CurrentRatings andCharacteristic Curves (T A = 25°C unless otherwise noted)Vishayformerly General SemiconductorRatings andCharacteristic Curves(T A = 25°C unless otherwise noted)--0.11.5A 0.1A--0.0500.050.14080120160200Fig. 7 – Load Transient ResponseL o a d C u r r e n tO u t p u t V o l t a g e (V , A C )Time (µs)01020304050Fig. 8 – Line Transient ResponseTime (µs)Vishayformerly General Semiconductor4.064.83TO-263TO-252 (DPAK)Dimensions in millimetersTO-220Case Outlines。

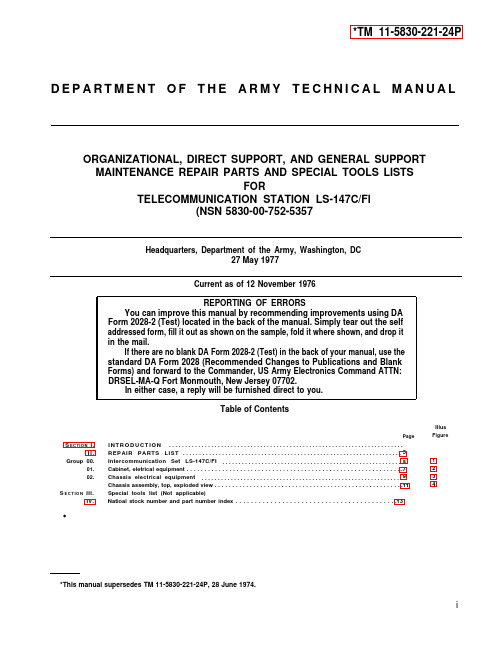

US Army 电信站LS-147C Fl维修部件和特殊工具清单说明书

known usage.

PD — Support item, excluding support equipment,

procured for initial issue or outfitting and

stocked only for subsequent or additional

initial issues or outfittings. Not subject to

Illus Figure

1 2 3 4

*This manual supersedes TM 11-5830-221-24P, 28 June 1974. i

Section I. INTRODUCTION

1. Scope.

This manual lists repair parts for the performance of organizational and direct support maintenance of the LS-147C/FI.

automatic replenishment.

XA — Item is not procured or stocked because the

requirements for the item will result in the

replacement of the next higher assembly. —

of the illustration on which the item is shown. (2) Item number. The number used to identify

each item called out in the illustration. b. Source, Maintenance, and Recoverability Codes

SG100M-M,SG150I-M,SG100M-M0,SG200S-M0,SG200S-C,SG100M-C,SG100M-C0,SG150I-C0, 规格书,Datasheet 资料

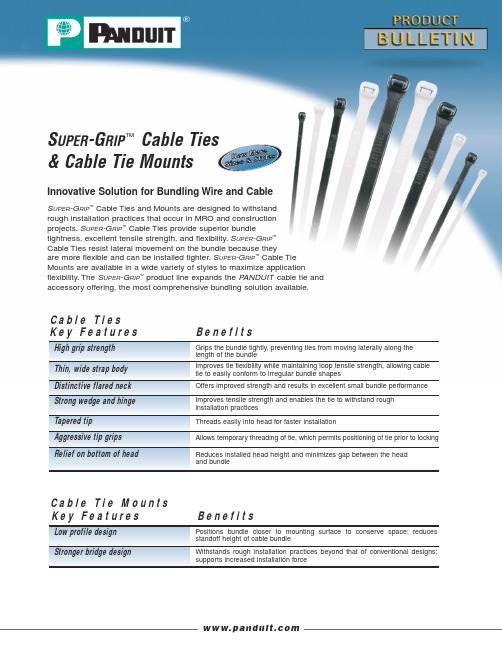

w w w.p a n d u i t.c o mS UPER -G RIP ™Cable Ties & Cable Tie MountsK e y F e a t u r e sB e n e f i t sHigh grip strength Grips the bundle tightly, preventing ties from moving laterally along the length of the bundleThin, wide strap body Distinctive flared neck Offers improved strength and results in excellent small bundle performance Strong wedge and hinge Improves tensile strength and enables the tie to withstand rough installation practicesAggressive tip grips Allows temporary threading of tie, which permits positioning of tie prior to locking Tapered tip Threads easily into head for faster installationImproves tie flexibility while maintaining loop tensile strength, allowing cable tie to easily conform to irregular bundle shapesRelief on bottom of headReduces installed head height and minimizes gap between the head and bundleLow profile design Positions bundle closer to mounting surface to conserve space;reduces standoff height of cable bundleStronger bridge designWithstands rough installation practices beyond that of conventional designs;supports increased installation forceK e y F e a t u r e sB e n e f i t sInnovative Solution for Bundling Wire and CableS UPER -G RIP ™Cable Ties and Mounts are designed to withstand rough installation practices that occur in MRO and construction projects.S UPER -G RIP ™Cable Ties provide superior bundletightness, excellent tensile strength, and flexibility.S UPER -G RIP ™Cable Ties resist lateral movement on the bundle because theyare more flexible and can be installed tighter.S UPER -G RIP ™Cable Tie Mounts are available in a wide variety of styles to maximize applicationflexibility.The S UPER -G RIP ™product line expands the PANDUIT cable tie and accessory offering, the most comprehensive bundling solution available.C a b l e T i e s C a b l e T i e M o u n t sO r d e r i n g I n f o r m a t i onS UPER-G RIP™Cable TiesLow Installed Head Height Flared Neck Tapered Tip withAggressive Grips芯天下--/S UPER-G RIP™Cable Tie MountsSGABM20-A-C SGABM25-AT-C0SGTA1S8-CSGABM25-A-C©2006 PANDUIT Corp.ALL RIGHTS RESERVED.Printed in the U.S.A.Product Bulletin Number SA-CTCB14replaces SA-CTCB126/2006WORLDWIDE SUBSIDIARIES AND SALES OFFICESFor a copy of PANDUITproduct warranties, log on to /warrantyPANDUIT CANADA Markham, Ontario cs-cdn@ Phone: 800.777.3300PANDUIT EUROPE LTD.London, UKcs-emea@ Phone: 44.20.8601.7200PANDUIT JAPAN Tokyo, Japancs-japan@ Phone: 81.3.3767.7011PANDUIT SINGAPORE PTE. LTD.Republic of Singapore cs-ap@ Phone: 65.6379.6700PANDUIT AUSTRALIA PTY. LTD.Victoria, Australia cs-aus@ Phone: 61.3.9794.9020PANDUIT LATIN AMERICA Jalisco, Mexico cs-la@Phone: 52.333.777.6000Contact Customer Service by email: cs@ or by phone: 800-777-3300 and reference CTCB14Visit us at For more informationS UPER -G RIP ™Cable Tie Mounts (continued)S c r e w A p p l i e d T i e M o u n t sM a s o n r y P u s h M o u n tsSGMPM SGTM2S8-C芯天下--/。

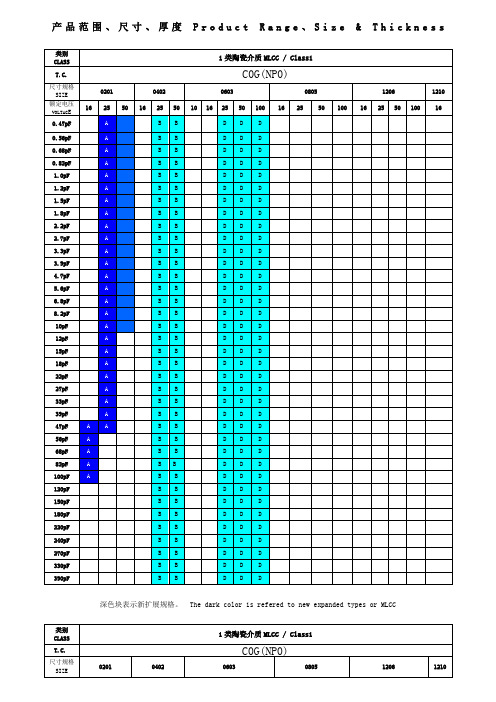

宇阳产品规格书

2 类陶瓷介质 MLCC / Class2

Y5V

0402

0603

0805

1206

1210

6. 3

10

16

25

6. 3

10 16

25

50

6. 3

10

16

25

50

6. 3

10

16

25

16 25

B

B

D

D

B

B

D

D

B

B

D

D

B

B

D

D

B

B

D

D

B

B

D

D

B

B

B

B

D

D

D

B

B

B

B

D

D

D

C

E

E

B

B

B

B

D

D

D

C

E

E

B

B

D

D

D

1206

1210

额定电压 6.3 10

VOLTAGE

4

6. 3

10

1 6

25 6.3

1 0

1 6

25 6.3

10

16 25

5 0

6. 3

1 0

1 6

25

5 0

1 6

2 5

50

82nF

A

B BB

100nF

A

B B BB

120nF

A

BB

150nF

A

BB

180nF

A

BB

220nF

A

BB

DD D

深圳市科瑞爱特逆变电源说明书CTDOC

深圳市科瑞爱特科技开发有限公司CT6000系列正弦波逆变电源使用说明书CT12/220-XXXX L/WCT24/220-XXXX L/WCT48/220-XXXX L/WCT110/220-XXXX L/WCT220/220-XXXX L/W深圳市科瑞爱特科技开发有限公司目录一、CT6000系列型号概述 (4)二、CT6000系列型号说明 (4)三、CT6000系列型号一览 (4)四、CT6000系列功能简介 (5)五、CT6000系列技术指标 (6)六、CT6000系列使用方法 (7)七、CT6000系列维护信息 (8)八、CT6000系列机械特性 (10)九、附件 (15)《质量保证卡》《用户资料表》、《维修记录表》 (16)警告:不要拆卸科瑞爱特电源系统上的任何外壳或模块。

设备内部零件带有致命性的电压或存有高能量的危险!一、CT6000系列型号概述CT6000系列正弦波逆变器是为电力系统及邮电通讯事业的实际需要,考虑到空间安装大小及IT时代对逆变器管理的自动化和网络化的需求,以及噪音对办公室或机房工作人员的影响而专门设计生产的逆变器。

该系列逆变器采用先进的SPWM和CPU控制技术,控制精确,输入输出隔离,安全高效,可靠性好。

该系列产品不仅体积小,重量轻,外形美观,安装维护简便,操作简单,噪音低,反灌杂音低,无污染,还具有实时数据采集和远程通讯功能,为广大系统用户实施网络管理和远程监控提供了便利。

该逆变器不仅仅适用于电力系统及通讯行业,同时也适用于其它对供电品质要求较高的场合,是办公室自动化的理想的电源选择。

二、CT6000系列型号说明CT XX/220-XXXX W/L……..公司商标……….标称输入直流电压……..标称输出正弦波电压…….标称输出功率VA………..19英寸标准机架安装式…………台式三、CT6000系列型号一览四、CT6000系列功能简介●CT6000系列逆变电源为智能型专用逆变电源,采用智能化微电脑CPU控制技术,控制线路简捷、可靠,快速响应外部环境的变化;●CT6000系列逆变电源采用SPWM脉宽调制技术,输出为稳频稳压、滤除杂讯、失真度低的纯净正弦波;●CT6000系列逆变电源带载能力强、负载兼容性好,内置旁路开关,提高了逆变电源供电的连续性、可靠性;●CT6000系列逆变电源直流输入端采用先进的反灌杂音抑制技术,与其他共用直流屏的通讯设备互不干扰,交流输入端采用多重滤波,消除市电电网的干扰,满足应用系统需要主用交流电源的需求;●CT6000系列逆变电源可灵活设置为AC主供型和DC主供型(任意选择一种):A)AC主供型逆变电源在有市电时,处于市电输出,当市电输入故障时自动切换到逆变输出;B)DC主供型逆变电源在有市电时,处于逆变输出,当直流输入故障时自动切换到市电输出;●CT6000系列逆变电源设计完善,允许在开机状态下切断直流,自动切换到市电旁路,不影响负载的供电,方便对蓄电池进行维护和更换;●CT6000系列逆变电源在出现电池电压高/低、过载告警关断输出后,电池电压恢复正常,电源自动恢复输出,消除了过载现象50秒后,电源自动恢复输出,此项功能尤其适用于无人值守的通讯基站;●CT6000系列逆变电源支持LCD显示功能,让客户随时了解机器内部工作状况(选配)●CT6000系列逆变电源支持交流开机功能,用于直流故障情况下开机(选配);●CT6000系列逆变电源支持通讯功能,利用监控软件实时了解电源工作情况(选配);●系列逆变电源支持TCP/IP协议功能,利用监控软件走以太网的方式进行远程(单台/多台)实时了解电源工作情况(选配);●CT6000系列逆变电源提供三组无源干结点,分别用于直流输入故障、交流输入故障和交流输出故障告警(选配)。